单片机多机通信

单片机多机通信实现

单片机多机通信实现随着科技的进步和应用的需求,单片机成为了嵌入式系统中不可或缺的一部分。

在很多应用场景中,我们需要将多个单片机之间进行通信,以实现数据的传输和协同工作。

本文将介绍单片机多机通信的实现方法。

一、串口通信串口通信是最常见和简单的单片机通信方式之一。

单片机通过串口将数据以字节的形式传输给另一个单片机。

常见的串口通信协议有RS232、RS485和UART等。

其中,RS232是单片机与计算机之间的标准通信协议,而RS485适用于单片机与多个设备之间的通信。

串口通信需要注意以下几个方面:1. 波特率的设置:通信双方需要设定相同的波特率,以确保数据的准确传输。

2. 数据格式的规定:包括数据位、校验位和停止位等,通讯双方需要设置相同的数据格式。

3. 通信控制的实现:通过编程控制单片机的串口发送和接收功能,实现数据的传输。

二、I2C通信I2C(Inter-Integrated Circuit)是一种串行总线协议,它可实现多个单片机的通信和协同工作。

I2C通信需要引入一个主设备和多个从设备的概念,主设备控制通信的起止和数据的传输,从设备用于接收和发送数据。

I2C通信需要注意以下几个方面:1. I2C地址的分配:每个从设备通过唯一的地址与主设备进行通信,地址的分配需要事先规划好。

2. 数据的读写操作:通过发送特定的控制信号,主设备可以向从设备发送读或写的命令,并接收从设备返回的数据。

3. 时序的控制:I2C通信依赖于时钟信号和数据信号的同步,通信双方需要根据协议规定好时序的控制。

三、SPI通信SPI(Serial Peripheral Interface)通信是一种全双工、同步的通信协议。

它通过4根线进行通信,包括时钟、数据输入、数据输出和片选信号。

SPI通信适用于多个主设备与多个从设备之间的通信,可以实现数据的传输和设备的控制。

SPI通信需要注意以下几个方面:1. 主从设备的选定:SPI通信中,每次只有一个主设备能够与从设备进行通信,其他设备通过片选信号进行选择。

单片机多机通信

单片机多机通信前言随着工业化要求的提高、分布式系统的发展以及控制设备与监控设备之间通讯的需要,多机通信系统设计的监控系统逐步普及。

本课程设计的目的是应用单片机的串口通信功能实现一个单片机多机通信系统。

此多机通信系统包括一台主机和三台从机,可以实现主机向任意一台从机传递数据的功能。

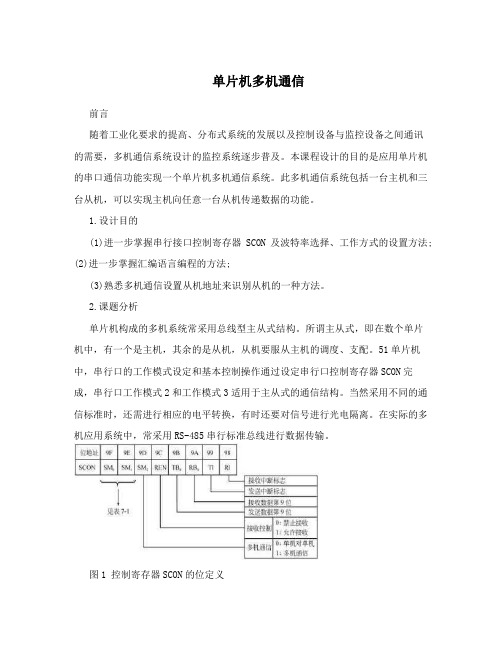

1.设计目的(1)进一步掌握串行接口控制寄存器SCON及波特率选择、工作方式的设置方法;(2)进一步掌握汇编语言编程的方法;(3)熟悉多机通信设置从机地址来识别从机的一种方法。

2.课题分析单片机构成的多机系统常采用总线型主从式结构。

所谓主从式,即在数个单片机中,有一个是主机,其余的是从机,从机要服从主机的调度、支配。

51单片机中,串行口的工作模式设定和基本控制操作通过设定串行口控制寄存器SCON完成,串行口工作模式2和工作模式3适用于主从式的通信结构。

当然采用不同的通信标准时,还需进行相应的电平转换,有时还要对信号进行光电隔离。

在实际的多机应用系统中,常采用RS-485串行标准总线进行数据传输。

图1 控制寄存器SCON的位定义图2 串行口工作模式3.系统设计3.1接口设计MCS-51单片机具有多机通信功能,利用它可以构成分布式系统,电路结构如图3所示图3 多机通信的主从式示意图在图3中,系统采用一台主机和三台从机,主机的Rxd端与所有从机的Txd端连接,主机的Txd端与所有从机的Rxd端相连,主机发送的信息可被各从机接收,而各从机发送的信息只能由主机接收。

3.2多机通信过程(1)所有从机的SM2=1,处于只接收地址帧状态。

(2)主机发送一地址帧信息,其中包含8位地址,第9位为地址/数据标志位,第9位为1,表示发送的是地址信息。

(3)各个从机接收到地址帧后,各自将所接收的地址与本从机的地址相比较。

对于地址相符的从机,使本机的SM2=0以便接收主机随后发来的所有信息;对于地址不相符的从机,仍保持SM2=1状态,对主机随后发来的数据不予理睬,等待主机发送新的地址帧。

单片机多机通信代码

单片机多机通信代码单片机多机通信是指通过单片机实现多个设备之间的数据传输和通信。

在现代的智能家居系统、工业自动化系统以及物联网等领域,单片机多机通信扮演着重要的角色。

为了实现单片机多机通信,需要首先确定通信的方式和协议。

常见的通信方式包括串口通信、SPI通信、I2C通信等。

在选择通信方式时,需要考虑设备之间的距离、通信速率、通信复杂度等因素。

协议方面,可以使用现有的通信协议,如Modbus、CAN、TCP/IP等,也可以根据具体需求自定义通信协议。

在单片机多机通信的实现过程中,首先需要配置单片机的通信接口。

例如,在使用串口通信时,需要设置波特率、数据位数、停止位数等参数。

接下来,需要编写相应的程序代码来实现数据的发送和接收。

发送数据时,可以使用单片机的串口发送函数将数据发送给其他设备;接收数据时,则需要使用单片机的串口接收函数来接收其他设备发送的数据。

在多机通信中,一台设备可以充当主机,负责控制其他设备的工作,也可以充当从机,接收主机发送的指令并执行相应的操作。

主机和从机之间可以通过发送和接收数据来实现通信。

例如,在智能家居系统中,主机可以控制灯光的开关、温度的调节等操作,而从机则负责接收主机发送的指令并执行相应的操作。

在实际应用中,单片机多机通信可以实现设备之间的信息交互和协同工作。

例如,在工业自动化系统中,可以通过多机通信实现各个设备之间的数据共享和协作,提高生产效率和质量。

在物联网中,可以通过多机通信实现各个物联设备之间的联动和互联,实现智能化控制和管理。

单片机多机通信是一种重要的通信方式,可以实现设备之间的数据传输和通信。

通过合理选择通信方式和协议,并编写相应的程序代码,可以实现设备之间的信息交互和协同工作,从而提高系统的功能和性能。

单片机之间多机通信演示电路设计

移位 时钟

发送SBUF(99H)

TI(发送中断)

TXD串行输出

系统总线

接收SBUF(99H) 输入移位寄存器

RXD串行输入 RI(接收中断)

AT89C51串行口寄存器结构

2 单片机串口工作存放器 1.串行通信掌握存放器

SCON掌握存放器,它是一个可寻址的专 用存放器,用于串行数据的通信掌握,单元地 址是98H,其构造格式如下:

返回

2.主机程序设计流程

本系统选用12MHZ晶振,承受2400HZ波特 率。程序流程如图4.9所示,其定时器串行口通 信的初始化步骤如下:

〔1〕确定串口工作于方式3,并允许接收——对 SCON存放器送掌握字C0H 〔SM0=1,SM1=1,REN=1〕;

〔2〕确定定时器T1工作于方式2——对TMOD存 放器送掌握字20H(M1=1,M0=0)

〔规定地址帧的第9位为1,数据帧的第9位为0〕。 假设从机的掌握位SM2=1,则接收的是地址帧时, 数据装入SBUF,并置RI=1,向CPU发出中断恳

求;假设接收的是数据帧,则不产生中断标志, 信息将抛弃。假设SM2=0,则无论是地址帧还是 数据帧都产生RI=1中断标志,数据装入SBUF。

单片机的串口工作原理

2.数码管显示电路

如下图,为两个从机的显示电路,本系统承受的 是一位共阳极数码管作为显示器,当a~g为低电 寻常,发光二极管点亮。其a、b、c、d、e、f、g、 dp八个引脚分别接单片机的,中间加一个330欧 姆的限流电阻。1~9共9个数字,共阳极型LED的 编码分别为: F9H、A4H、B0H、99H、92H、 82H、F8H、80H和90H。

1〕方式2发送

发送时,依据通信协议由软件设置TB8,然后用 指令将要发送的数据写入SBUF,启动发送器。 写SBUF的指令,除了将8位数据送入SBUF外, 同时还将TB8装入发送移位存放器的第9位,并启 动发送掌握器进展一次发送。一帧信息即从TXD 发送出去,在送完一帧信息后,TI被自动置1,在 发送下一帧信息之前,TI必需由中断效劳程序或 查询程序清0.

51单片机多机通信

一、多机通信原理在多机通信中,主机必须要能对各个从机进行识别,在51系列单片机中可以通过SCON 寄存器的SM2位来实现。

当串口以方式2或方式3发送数据时,每一帧信息都是11位,第9位是数据可编程位,通过给TB8置1或置0来区别地址帧和数据帧,当该位为1时,发送地址帧;该位为0时,发送数据帧。

在多机通信过程中,主机先发送某一从机的地址,等待从机的应答,所有的从机接收到地址帧后与本机地址进行比较,若相同,则将SM2置0准备接收数据;若不同,则丢弃当前数据,SM2位不变。

二、多机通信电路图此处,U1作为主机,U2为从机1,U3为从机2。

三、C语言程序(1)主机程序#include<reg51.h>#include<string.h>#define _SUCC_ 0x0f//数据传送成功#define _ERR_ 0xf0//数据传送失败unsigned char Table[9]={0x31,0x32,0x33,0x34,0x35,0x36,0x37,0x38,0x39}; unsigned char Buff[20]; //数据缓冲区unsigned char temp=0xff;sbit KEY1=P1^6;sbit KEY2=P1^7;//unsigned char addr;//延时1ms函数void delay_1ms(unsigned int t){unsigned int x,y;for(x=t;x>0;x--)for(y=110;y>0;y--);}//缓冲区初始化void Buff_init(){unsigned char i; //将Table里的数据放到缓冲区里for(i=0;i<9;i++){Buff[i]= Table[i];delay_1ms(100);}}//串口初始化函数void serial_init(){TMOD=0x20; //定时器1工作于方式2TH1=0xfd;TL1=0xfd; //波特率为9600PCON=0;SCON=0xd0; //串口工作于方式3TR1=1; //开启定时器TI=0;RI=0;}//发送数据函数void SEND_data(unsigned char *Buff){unsigned char i;unsigned char lenth;unsigned char check;lenth=strlen(Buff); //计算数据长度check=lenth;TI=0; //发送数据长度TB8=0; //发送数据帧SBUF=lenth;while(!TI);TI=0;for(i=0;i<lenth;i++) //发送数据{check=check^Buff[i];TB8=0;SBUF=Buff[i];while(!TI);TI=0;}TB8=0; //发送校验字节SBUF=check;while(!TI);TI=0;}//向指定从机地址发送数据void ADDR_data(unsigned addr){while(temp!=addr) //主机等待从机返回其地址作为应答信号{TI=0; //发送从机地址TB8=1; //发送地址帧SBUF=addr;while(!TI);TI=0;RI=0;while(!RI);temp=SBUF;RI=0;}temp=_ERR_; //主机等待从机数据接收成功信号while(temp!=_SUCC_){SEND_data(Buff);RI=0;while(!RI);temp=SBUF;RI=0;}}void main(){Buff_init();serial_init();while(1){if(KEY1==0){delay_1ms(5);if(KEY1==0){while(!KEY1);ADDR_data(0x01);}}if(KEY2==0){delay_1ms(5);if(KEY2==0){while(!KEY2);ADDR_data(0x02);}}}}(2)从机1程序#include<reg51.h>#include<string.h>#define addr 0x01//从机1的地址#define _SUCC_ 0x0f//数据传送成功#define _ERR_ 0xf0//数据传送失败unsigned char aa=0xff;//主机与从机之间通信标志unsigned char Buff[20];//数据缓冲区//串口初始化函数void serial_init(){TMOD=0x20; //定时器1工作于方式2TH1=0xfd;TL1=0xfd; //波特率为9600PCON=0;SCON=0xd0; //串口工作于方式3TR1=1; //开启定时器TI=0;RI=0;}//接收数据函数unsigned char RECE_data(unsigned char *Buff) {unsigned char i,temp;unsigned char lenth;unsigned char check;RI=0; //接收数据长度while(!RI);if(RB8==1) //若接收到地址帧,则返回0xfereturn 0xfe;lenth=SBUF;RI=0;check=lenth;for(i=0;i<lenth;i++) //接收数据{while(!RI);if(RB8==1) //若接收到地址帧,则返回0xfereturn 0xfe;Buff[i]=SBUF;check=check^(Buff[i]);RI=0;}while(!RI); //接收校验字节if(RB8==1) //若接收到地址帧,则返回0xfereturn 0xfe;temp=SBUF;RI=0;check=temp^check; //将从主机接收到的校验码与自己计算的校验码比对if(check!=0) //校验码不一致,表明数据接收错误,向主机发送错误信号,函数返回0xff {TI=0;TB8=0;SBUF=_ERR_;while(!TI);TI=0;return 0xff;}TI=0; //校验码一致,表明数据接收正确,向主机发送成功信号,函数返回0x00 TB8=0;SBUF=_SUCC_;while(!TI);TI=0;return 0;}void main(){serial_init();while(1){SM2=1; //接收地址帧while(aa!=addr) //从机等待主机请求自己的地址{RI=0;while(!RI);aa=SBUF;RI=0;}TI=0; //一旦被请求,从机返回自己的地址作为应答,等待接收数据 TB8=0;SBUF=addr;while(!TI);TI=0;SM2=0; //接收数据帧aa=0xff; //从机接收数据,并将数据保存到数据缓冲区while(aa==0xff){aa=RECE_data(Buff);}if(aa==0xfe)continue;P1=Buff[1]; //查看接收到的数据}}(3)从机2程序#include<reg51.h>#include<string.h>#define addr 0x02//从机2的地址#define _SUCC_ 0x0f//数据传送成功#define _ERR_ 0xf0//数据传送失败unsigned char aa=0xff;//主机与从机之间通信标志unsigned char Buff[20];//数据缓冲区//串口初始化函数void serial_init(){TMOD=0x20; //定时器1工作于方式2TH1=0xfd;TL1=0xfd; //波特率为9600PCON=0;SCON=0xd0; //串口工作于方式3TR1=1; //开启定时器TI=0;RI=0;}//接收数据函数unsigned char RECE_data(unsigned char *Buff){unsigned char i,temp;unsigned char lenth;unsigned char check;RI=0; //接收数据长度while(!RI);if(RB8==1) //若接收到地址帧,则返回0xfereturn 0xfe;lenth=SBUF;RI=0;check=lenth;for(i=0;i<lenth;i++) //接收数据{while(!RI);if(RB8==1) //若接收到地址帧,则返回0xfereturn 0xfe;Buff[i]=SBUF;check=check^(Buff[i]);RI=0;}while(!RI); //接收校验字节if(RB8==1) //若接收到地址帧,则返回0xfereturn 0xfe;temp=SBUF;RI=0;check=temp^check; //将从主机接收到的校验码与自己计算的校验码比对if(check!=0) //校验码不一致,表明数据接收错误,向主机发送错误信号,函数返回0xff {TI=0;TB8=0;SBUF=_ERR_;while(!TI);TI=0;return 0xff;}TI=0; //校验码一致,表明数据接收正确,向主机发送成功信号,函数返回0x00 TB8=0;SBUF=_SUCC_;while(!TI);TI=0;return 0;}void main(){serial_init();while(1){SM2=1; //接收地址帧while(aa!=addr) //从机等待主机请求自己的地址{RI=0;while(!RI);aa=SBUF;RI=0;}TI=0; //一旦被请求,从机返回自己地址作为应答,等待接收数据TB8=0;SBUF=addr;while(!TI);TI=0;SM2=0; //接收数据帧aa=0xff; //从机接收数据,并将数据保存到数据缓冲区while(aa==0xff){aa=RECE_data(Buff);}if(aa==0xfe)continue;P1=Buff[2]; //查看接收到的数据}}。

51单片机的多机通信原理

51单片机的多机通信原理1. 什么是51单片机的多机通信?51单片机的多机通信是指在多个51单片机之间进行数据传输和通信的过程。

通过多机通信,可以实现不同单片机之间的数据共享和协作,从而实现更加复杂的功能。

2. 多机通信的原理是什么?多机通信的原理是通过串口进行数据传输。

在多个单片机之间,可以通过串口进行数据的发送和接收。

通过定义好的协议,可以实现数据的传输和解析,从而实现多机之间的通信。

3. 多机通信的步骤是什么?多机通信的步骤包括以下几个方面:(1)定义好通信协议:在多机通信之前,需要定义好通信协议,包括数据的格式、传输方式等。

(2)设置串口参数:在单片机中,需要设置好串口的参数,包括波特率、数据位、停止位等。

(3)发送数据:在发送数据之前,需要将数据按照协议进行格式化,然后通过串口发送出去。

(4)接收数据:在接收数据之前,需要设置好串口的中断,然后在中断中接收数据,并按照协议进行解析。

(5)处理数据:在接收到数据之后,需要对数据进行处理,包括数据的存储、显示等。

4. 多机通信的应用场景有哪些?多机通信的应用场景非常广泛,包括以下几个方面:(1)智能家居系统:通过多机通信,可以实现智能家居系统中不同设备之间的数据共享和协作。

(2)工业控制系统:在工业控制系统中,多机通信可以实现不同设备之间的数据传输和控制。

(3)智能交通系统:在智能交通系统中,多机通信可以实现不同设备之间的数据共享和协作,从而实现更加智能化的交通管理。

(4)机器人控制系统:在机器人控制系统中,多机通信可以实现不同机器人之间的数据传输和控制,从而实现更加复杂的任务。

5. 多机通信的优缺点是什么?多机通信的优点包括以下几个方面:(1)实现数据共享和协作:通过多机通信,可以实现不同设备之间的数据共享和协作,从而实现更加复杂的功能。

(2)提高系统的可靠性:通过多机通信,可以实现数据的备份和冗余,从而提高系统的可靠性。

(3)提高系统的扩展性:通过多机通信,可以实现系统的模块化设计,从而提高系统的扩展性。

基于51单片机的多机通信系统设计

基于51单片机的多机通信系统设计多机通信系统是指通过一台主机与多台从机之间进行数据交互和通信的系统。

在本设计中,我们将使用51单片机实现一个基于串行通信的多机通信系统。

系统硬件设计如下:1.主机:使用一个51单片机作为主机,负责发送数据和接收数据。

2.从机:使用多个51单片机作为从机,每个从机负责接收数据和发送数据给主机。

3.串口:主机和从机之间通过串口进行通信。

我们可以使用RS232标准通信协议。

系统软件设计如下:1.主机设计:a.初始化串口:设置串口参数,如波特率、数据位、停止位等。

b.发送数据:将需要发送的数据存储在发送缓冲区中,通过串口发送给从机。

c.接收数据:接收从机发送的数据,并存储在接收缓冲区中。

2.从机设计:a.初始化串口:设置串口参数,如波特率、数据位、停止位等。

b.接收数据:接收主机发送的数据,并存储在接收缓冲区中。

c.发送数据:将需要发送的数据存储在发送缓冲区中,通过串口发送给主机。

系统工作流程如下:1.主机启动,执行初始化操作,包括初始化串口。

2.从机启动,执行初始化操作,包括初始化串口。

3.主机发送数据给从机:主机将需要发送的数据存储在发送缓冲区中,通过串口发送给从机。

4.从机接收并处理数据:从机接收主机发送的数据,并存储在接收缓冲区中,对接收到的数据进行处理。

5.从机发送数据给主机:从机将需要发送的数据存储在发送缓冲区中,通过串口发送给主机。

6.主机接收并处理数据:主机接收从机发送的数据,并存储在接收缓冲区中,对接收到的数据进行处理。

7.主机和从机循环执行步骤3-6,实现多机之间的数据交互和通信。

多机通信系统的设计考虑到以下几个方面:1.硬件设计:需要合理选择单片机和串口的类型和参数,确保系统的稳定性和可靠性。

2.软件设计:需要设计适应系统需求的通信协议和数据处理提取方法,保证数据的准确性和完整性。

3.通信协议:需要定义主机和从机之间的通信协议,包括数据的格式、传输方式等,以便实现正确的数据交互。

单片机多机通信的原理

单片机多机通信的原理一、引言随着科技的发展,单片机在各个领域中得到了广泛的应用。

而多机通信作为单片机应用的重要组成部分,对于实现系统的互联互通起着至关重要的作用。

本文将介绍单片机多机通信的原理。

二、单片机多机通信的概念单片机多机通信是指在多个单片机之间进行数据交换和传输的过程。

通过多机通信,不同的单片机可以实现相互之间的数据传输和共享,从而协同工作,提高系统的整体性能。

三、多机通信的基本原理1. 通信协议:多机通信的实现离不开通信协议的支持。

通信协议规定了数据的格式、传输方式和通信规则等,确保数据能够正确、高效地传输。

常见的通信协议有UART、SPI、I2C等。

2. 硬件连接:多机通信需要通过物理连接来实现。

通常使用串口、总线等方式进行连接。

通过连接线将多个单片机连接在一起,形成一个通信网络。

3. 主从模式:多机通信中通常存在主从模式。

主机负责控制整个通信过程,从机负责接收和处理主机发送的数据。

主机发送命令或请求,从机接收并返回响应。

这样可以实现通信的协同工作。

4. 数据传输:在多机通信过程中,数据的传输是核心环节。

主机将数据封装成指令或数据包发送给从机,从机接收到数据后进行解析和处理,然后返回相应的结果给主机。

数据的传输可以通过串口、总线等方式进行。

5. 数据校验:为了确保数据的正确性,在数据传输过程中需要进行校验。

常见的校验方式有奇偶校验、CRC校验等。

通过校验,可以检测出数据传输过程中产生的错误,保证数据的准确性。

四、多机通信的应用场景1. 工业控制:在工业自动化领域中,常常需要多个单片机之间进行数据交换和传输。

通过多机通信,可以实现各个设备之间的协同工作,提高生产效率和质量。

2. 物联网:在物联网应用中,多机通信可以实现各个终端设备之间的数据传输和共享。

通过多机通信,可以实现智能家居、智能交通等应用场景。

3. 军事领域:在军事系统中,多机通信可以实现指挥系统和各个终端之间的数据交互。

通过多机通信,可以实现指挥决策的快速响应和准确执行。

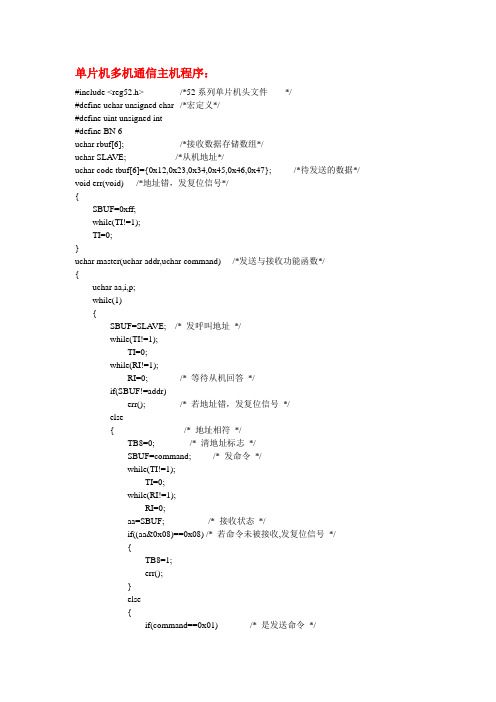

单片机多机通信程序

单片机多机通信主机程序:#include <reg52.h> /*52系列单片机头文件*/#define uchar unsigned char /*宏定义*/#define uint unsigned int#define BN 6uchar rbuf[6]; /*接收数据存储数组*/uchar SLA VE; /*从机地址*/uchar code tbuf[6]={0x12,0x23,0x34,0x45,0x46,0x47}; /*待发送的数据*/ void err(void) /*地址错,发复位信号*/{SBUF=0xff;while(TI!=1);TI=0;}uchar master(uchar addr,uchar command) /*发送与接收功能函数*/{uchar aa,i,p;while(1){SBUF=SLA VE; /* 发呼叫地址*/while(TI!=1);TI=0;while(RI!=1);RI=0; /* 等待从机回答*/if(SBUF!=addr)err(); /* 若地址错,发复位信号*/else{ /* 地址相符*/TB8=0; /* 清地址标志*/SBUF=command; /* 发命令*/while(TI!=1);TI=0;while(RI!=1);RI=0;aa=SBUF; /* 接收状态*/if((aa&0x08)==0x08) /* 若命令未被接收,发复位信号*/{TB8=1;err();}else{if(command==0x01) /* 是发送命令*/{if((aa&0x01)==0x01) /* 从机准备好接收*/{do{p=0; /* 清校验和*/for(i=0;i<BN;i++){SBUF=tbuf[i]; /* 发送一数据*/p+=tbuf[i];while(TI!=1);TI=0;}SBUF=p; /* 发送校验和*/while(TI!=1);TI=0;while(RI!=1);RI=0;}while(SBUF!=0); /* 接收不正确,重新发送*/TB8=1; /* 置地址标志*/return(0);}else{if((aa&0x02)==0x02) /* 是接收命令,从机准备好发送*/{while(1){p=0; /* 清校验和*/for(i=0;i<BN;i++){while(RI!=1);RI=0;rbuf[i]=SBUF; /* 接收一数据*/p+=rbuf[i];}while(RI!=1);RI=0;if(SBUF==p){SBUF=0X00; /* 校验和相同发"00" */while(TI!=1);TI=0;break;}else{SBUF=0xff; /* 校验和不同发"0FF",重新接收*/while(TI!=1);TI=0;}}TB8=1; /* 置地址标志*/P2=rbuf[1];return(0);}}}}}}}void main(){TMOD=0x20; /* T/C1定义为方式2 */TL1=0xfd;TH1=0xfd; /* 置初值,波特率9600,晶振11.0592MHz */PCON=0x00; /*不倍频*/TR1=1; /*启动定时器*/SCON=0xf8; /* 串行口为方式3 */SLAVE=0x01; /*1号从机地址*/master(SLAVE,0x01);master(SLAVE,0x02);SLAVE=0x02; /*2号从机地址*/master(SLAVE,0x01);master(SLAVE,0x02);SLAVE=0x03; /*3号从机地址*/master(SLAVE,0x01);master(SLAVE,0x02);while(1);}单片机多机通信从机程序(以01H从机为例):#include <reg52.h> /*52系列单片机头文件*/#define uchar unsigned char /*宏定义*/#define SLA VE 0x01 /*1号从机地址*/#define BN 6uchar trbuf[6]={0x12,0x13,0x14,0x15,0x16,0x17}; /*发送数据存储数组*/ uchar rebuf[6]; /*接收数据存储数组*/bit tready;bit rready;void str(void); /* 发数据块函数声明*/void sre(void); /* 收数据块函数声明*/void main(void){TMOD=0x20; /*T/C1定义为方式2*/TL1=0xfd;TH1=0xfd; /* 置初值,波特率9600,晶振11.0592MHz */PCON=0x00; /*不倍频*/TR1=1; /*启动定时器*/SCON=0xf0; /*串行口为方式3*/ES=1; /*开串口中断*/EA=1; /*开串行口中断*/while(1){tready=1;rready=1;} /*假定准备好发送和接收*/}void ssio(void) interrupt 4 /*串行口中断*/{uchar a;RI=0;ES=0; /*关串行口中断*/if(SBUF!=SLAVE){ES=1;goto reti;} /*非本机地址,继续监听*/SM2=0; /* 取消监听状态*/SBUF=SLAVE; /* 从本地址发回*/while(TI!=1);TI=0;while(RI!=1);RI =0;if(RB8==1){SM2=1;ES=1;goto reti;}/* 是复位信号,恢复监听*/a=SBUF; /* 接收命令*/if(a==0x01)/* 从主机接收的数据*/{if(rready==1)SBUF=0x01;/* 接收准备好发状态*/ elseSBUF=0x00;while(TI!=1);TI=0;while(RI!=1);RI=0;if(RB8==1){SM2=1;ES=1;goto reti;}sre(); /* 接收数据*/}else{if(a==0x02) /* 从机向主机发送数据*/{if(tready==1)SBUF=0x02; /* 发送准备好发状态*/ elseSBUF=0x00;while(TI!=1);TI=0;while(RI!=1);RI=0;if(RB8==1){SM2=1;ES=1;goto reti;}str();/* 发送数据*/}else{SBUF=0x80; /* 命令非法,发状态*/while(TI!=1);TI=0;SM2=1;ES=1; /* 恢复监听*/}}reti:;}void str(void) /* 发数据块*/{uchar p,i;tready=0 ;do{p=0;/* 清校验和*/for(i=0;i<BN;i++){SBUF=trbuf[i]; /* 发送一数据*/p+=trbuf[i];while(TI!=1);TI=0;}SBUF=p; /* 发送校验和*/while(TI!=1);TI=0;while(RI!=1);RI=0;}while(SBUF!=0);/* 主机接收不正确,重新发送*/SM2=1;ES=1;}void sre(void) /* 接收数据块*/{uchar p,i;rready=0 ;while(1){p=0; /* 清校验和*/for(i=0;i<BN;i++){while(RI!=1);RI=0;rebuf[i]=SBUF; /* 接收数据*/p+=rebuf[i];}while(RI!=1);RI=0;if(SBUF==p){SBUF=0x00;break;} /* 校验和相同发"00"*/else{SBUF=0xff; /* 校验和不同发"0FF",重新接收*/while(TI==0);TI=0;}}P1=rebuf[1];SM2=1;ES=1;}。

简述单片机多机通信的原理

简述单片机多机通信的原理

单片机多机通信的原理主要包括两个方面:通信介质和通信协议。

通信介质:多机通信可以通过不同的物理介质实现,常见的有串行通信、并行通信、以太网通信等。

串行通信是单片机多机通信中常用的一种方式,通过单根信号线进行通信。

串行通信可以分为同步串行通信和异步串行通信,其中异步串行通信在单片机多机通信中较为常见。

通过确保发送和接收的速度一致,可以实现单片机之间的数据通信。

通信协议:通信协议是指单片机多机通信中数据传输的规则和格式。

常用的通信协议包括UART、SPI、I2C等。

UART通信协议是一种异步串行通信协议,通过发送和接收缓冲区来实现数据的传输。

SPI通信协议是一种同步串行通信协议,通过主从结构来进行数据的传输。

I2C通信协议也是一种同步串行通信协议,通过总线结构来实现多个设备之间的通信。

在单片机多机通信中,首先需要确定通信介质,然后根据通信介质选择合适的通信协议。

通信协议中,发送端将数据按照一定的规则封装成数据包发送给接收端,接收端按照相应的规则解析数据包并进行相应的处理。

通过通信介质传输数据,再通过通信协议解析数据,实现了单片机之间的数据传输和通信。

51单片机多机通信程序

51单片机多机通信程序(主机部分) /* multi_m.c *//* 多机通信的主机部分*/#ifndef __MULTI_M_C__#define __MULTI_M_C__#include <AT89X51.H>#include <STRING.H>#define __MAX_LEN_ 64 // 数据最大长度#define _MHZ_ 11 // 设置单片机使用的晶振频率(11.0592MHz) /* 以下为程序协议中使用的握手信号*/#define __SUCC_ 0x0f // 数据传送成功#define __ERR_ 0xf0 // 数据传送错误void init_serial(); // 串口初始化void send_data(unsigned char *buf); // 发送数据void delay10ms(unsigned int count); // 延时子程序(10ms) void main(){char buf[__MAX_LEN_];unsigned char i = 0;unsigned char tmp;unsigned char addr; // 该字节用于保存要通信的从机地址/* 为缓冲区赋初值*/P0 = 0xff;while(P1 != 0) // 每隔100ms从P0口读取,若读取到0则表明数据采集结束{*(buf+i) = P0;delay10ms(10); // 延时100msP0 = 0xff;i++;}*(buf+i) = 0; // 缓冲区最后一个字节为0表示数据结束/* 读要访问的分机地址*/P0 = 0xff;addr = P0;/* 串口初始化*/init_serial(); // 初始化串口EA = 0; // 关闭所有中断/* 发送地址帧并接收应答信息,如果接收的信号与发送的地址信息不同,则重新发送地址帧*/tmp = addr-1;while(tmp != addr){/* 发送从机地址*/TB8 = 1; // 发送地址帧SBUF = addr;while(!TI);TI = 0;/* 接收从机应答*/RI = 0;while(!RI);tmp = SBUF;RI = 0;}/* 发送数据并接收校验信息,如果接收的信号为0FH,表示从机接收成功,否则将重新发送该组数据*/tmp = __ERR_;while(tmp != __SUCC_){send_data(buf); // 发送数据RI = 0;while(!RI);tmp = SBUF;RI = 0;}while(1); // 程序结束,进入死循环}/* 初始化串口*/void init_serial(){TMOD = 0x20; //定时器T1使用工作方式2TH1 = 250; // 设置初值TL1 = 250;TR1 = 1; // 开始计时PCON = 0x80; // SMOD = 1SCON = 0xd0; //工作方式3,9位数据位,波特率9600bps,允许接收}/* 发送数据*/void send_data(unsigned char *buf){unsigned char len; // 保存数据长度unsigned char ecc; // 保存校验字节len = strlen(buf); // 计算要发送数据的长度ecc = len; // 开始进行校验字节计算/* 发送数据长度*/TB8 = 0; // 发送数据帧SBUF = len; // 发送长度while(!TI);TI = 0;/* 发送数据*/for(i=0; i<len; i++){ecc = ecc^(*buf); // 计算校验字节TB8 = 0; // 发送数据帧SBUF = *buf; // 发送数据buf++;while(!TI);TI = 0;}/* 发送校验字节*/TB8 = 0; // 发送数据帧SBUF = ecc; // 发送校验字节while(!TI);TI = 0;}/* 延时10ms,精度较低,参数count为延时时间*/ void delay10ms(unsigned int count){unsigned int i, k;unsigned char j;unsigned int tmp;tmp = (int)((100*_MHZ_)/12);for(i=0; i<count; i++)for(j=0; j<100; j++)for(k=0; k<tmp; k++);}#endif51单片机多机通信程序(从机部分)/* multi_s.c *//* 多机通信的从机部分*/#ifndef __MULTI_S_C__#define __MULTI_S_C__#include <AT89X51.H>#include <STRING.H>#define __MAX_LEN_ 64 // 数据最大长度#define _MHZ_ 11 // 设置单片机使用的晶振频率(11.0592MHz)/* 以下为程序协议中使用的握手信号*/#define __SUCC_ 0x0f // 数据传送成功#define __ERR_ 0xf0 // 数据传送错误void init_serial(); // 串口初始化unsigned char recv_data(unsigned char *buf); // 接收数据void Beep_ok(); // 蜂鸣表示数据接收ok,该函数代码未给出void main() {char buf[__MAX_LEN_];unsigned char i = 0;unsigned char tmp = 0xff;unsigned char addr; // 保存本机地址/* 从P1口读取本机地址*/P1 = 0xff;addr = P1;/* 串口初始化*/init_serial(); // 初始化串口EA = 0; // 关闭所有中断/* 进入设备应答阶段*/while(1){SM2 = 1; // 只接收地址帧/* 如果接收到的地址帧不是本机地址,则继续等待*/ tmp = addr-1;while(tmp != addr){RI = 0;while(!RI);tmp = SBUF;RI = 0;}/* 发送应答信号,并做好接收数据的准备*/TI = 0;TB8 = 0; // 主机不检测该位SBUF = addr;while(!TI);TI = 0;SM2 = 0; // 允许接收数据信息/* 数据接收*/tmp = 0xff;while(tmp == 0xff) // 如果数据校验失败则重新接收数据{tmp = recv_data(buf); // 校验失败返回0xff,检测到地址帧则返回0xfe,接收成功则返回0}if(tmp == 0xfe) // 在数据接收过程中,如果发现地址帧,则重新开始整个接收过程continue;Beep_ok(); // 蜂鸣表示数据接收成功}}/* 初始化串口*/void init_serial(){TMOD = 0x20; //定时器T1使用工作方式2TH1 = 250; // 设置初值TL1 = 250;TR1 = 1; // 开始计时PCON = 0x80; // SMOD = 1SCON = 0xd0; //工作方式3,9位数据位,波特率9600bps,允许接收}/* 接收数据,注意该函数使用buf指向的缓冲区保存数据,在数据末尾使用’\0’表示数据结束* 返回值为0,数据校验成功,返回值为0xfe,接受过程中接收到地址帧,返回值为0xff,数据校验失败*/unsigned char recv_data(unsigned char *buf){unsigned char len; // 该字节用于保存数据长度unsigned char ecc; // 该字节用于保存校验字节unsigned char i,tmp;/* 接收数据长度*/RI = 0;while(!RI);if(RB8 == 1) // 若当前接收为地址帧则返回0xfereturn 0xfe;len = SBUF;RI = 0;/* 使用len的值为校验字节ecc赋初值*/ecc = len;/* 接收数据*/for(i=0; i<len; i++){while(!RI);if(RB8 == 1) // 若当前接收为地址帧则返回0xfe return 0xfe; *buf = SBUF; // 接收数据ecc = ecc^(*buf); // 进行字节校验RI = 0;buf++;}*buf = 0; // 表示数据结束/* 接收校验字节*/while(!RI);if(RB8 == 1) // 若当前接收为地址帧则返回0xfe return 0xfe; tmp = SBUF;RI = 0;/* 进行数据校验*/ecc = tmp^ecc;if(ecc != 0) // 校验失败{*(buf-len) = 0; // 清空数据缓冲区TI = 0; // 发送校验失败信号TB8 = 0;SBUF = __ERR_;while(!TI);TI = 0;return 0xff; // 返回0xff表示校验错误} TI = 0; // 校验成功TB8 = 0;SBUF = __SUCC_;while(!TI);TI = 0;return 0; // 校验成功,返回0}#endif。

简述单片机多机通信原理

简述单片机多机通信原理

单片机多机通信是指通过单片机实现多个设备之间的数据交换和通信。

通常情况下,单片机多机通信的原理可以分为以下几个步骤:

1. 确定通信方式:根据具体的应用场景和需求,选择适合的通信方式,如串行通信、并行通信、SPI通信、I2C通信等。

2. 确定通信协议:确定通信双方之间的数据传输格式和通信协议,如传输数据的长度、起始位、校验位等。

通信协议的选择也受到硬件条件的限制。

3. 硬件连接:通过硬件连接将多个设备与单片机连接起来。

根据选择的通信方式,可以使用串口、并口、GPIO口等进行连接。

4. 初始化设置:在每个设备上设置适当的参数,如波特率、传输模式、中断等。

这些参数设置需要与单片机上的相应设置相匹配。

5. 数据传输:根据通信协议,在发送端将要传输的数据经过编码处理,然后通过通信线路发送给接收端,接收端收到数据后进行解码处理,得到原始数据。

6. 数据处理:单片机接收到数据后,根据需求进行相应的数据处理,如提取有效信息、进行数据计算等。

7. 状态更新:单片机在接收到新数据后,需要更新相应的状态信息,以便下一次数据传输的准备。

通过以上步骤,单片机可以实现多机之间的数据交换和通信,可以用于各种场景,如智能家居、工业自动化、嵌入式系统等。

51单片机多机通信过程

51单片机多机通信过程51单片机具有多机通信的功能,可实现一台主机于多台从机的通信。

多机通信充分利用了单片机内部的多机通信控制位SM2。

当从机SM2,1时,从机只接收主机发出的地址帧(第九位为1),对数据帧(第九位为0)不予理睬;而当SM2=0时,可接收主机发送过来的所有信息。

多机通信的过程如下:(1)所有从机SM2均置1,处于只接收地址帧状态。

(2)主机先发送一个地址帧,其中前8位数据表示地址,第9位为1表示该帧为地址帧。

(3)所有从机接收到地址帧后,进行中断处理,把接收到的地址与自身地址相比较。

地址相符时将SM2清成0,脱离多机状态,地址不相符的从机不作任何处理,即保持SM2,1。

(4)地址相符的从机SM2=0,可以接收到主机随后发来的信息,即主机发送的所有信息。

收到信息TB8=0,则表示是数据帧,而对于地址不符的从机SM2=1,收到信息TB8=0,则不予理睬,这样就实现了主机与地址相符的从机之间的双机通信。

(5)被寻址的从机通信结束后置SM2=1,恢复多机通信系统原有的状态。

主机:设置为SM2=0。

这是双机通信的形式,可以任意的发送和接收发送:以TB8=1发送,将发送到所有SM2=1的分机。

这是呼叫某个从机。

以TB8=0发送,将发送到SM2=0的分机。

这是双机通信的形式。

------从机:先设置为SM2=1。

这是多机通信的形式,只能收到RB8=1的。

接收:仅能收到RB8=1的数据,确认是呼叫本机时,令SM2=0。

设置为SM2=0后,是双机通信的形式。

追问那从机的RB8要怎么设,是需要软件设置还是单片机自己识别,在编程的时候要怎么写, 回答从机的RB8,不需要编程。

从机的RB8,是接收到的,它是主机发送出来的TB8。

想要对TB8进行控制,需要在主机中编程。

单片机多机通讯说明:该程序为多机通讯程序,最多可以挂255个从机。

该程序主机发送端与多个从机的接收端相接,主机的接收端与多个从机的发送端相接。

单片机多机通信的原理

单片机多机通信的原理单片机多机通信是指通过一组单片机进行信息传输和交换的过程。

单片机多机通信可以实现不同单片机之间的数据传输、控制和协调工作。

在多机通信中,每个单片机都有独立的功能和任务,并通过通信方式进行协作完成工作。

1.通信协议:通信协议是单片机多机通信的重要基础。

在多机通信中,需要定义一套协议,规定数据帧的格式,数据的传输方式和操作的流程。

常见的通信协议有SPI、I2C、UART等。

选择合适的通信协议可以根据传输距离、传输速度、设备复杂度等需求来进行选择。

2.总线结构:多机通信中常使用总线结构,将多个单片机连接在同一总线上。

总线结构包括三种类型:并行总线、串行总线和混合总线。

并行总线是指在总线的每条线上同时传输一个单元(八位),速度较快;串行总线是指数据逐位的传输,速度较慢但可以实现长距离传输;混合总线则结合了并行总线和串行总线的优点。

根据具体应用需求,选择合适的总线结构。

3.通信方式:在多机通信中,可以采用半双工通信或者全双工通信方式。

半双工通信是指通信双方交替发送和接收数据,在同一时刻只能进行发送或接收操作;全双工通信是指通信双方可以同时进行发送和接收操作。

根据通信需求和硬件条件,选择合适的通信方式。

4.帧同步:在多机通信中,数据的传输需要进行帧同步,即接收端需要识别出每个数据帧的起始和结束位置。

帧同步可以通过在传输数据中插入特定的起始标识符和结束标识符来实现。

当接收到起始标识符后,接收端开始接收数据帧,直到接收到结束标识符,表示数据帧传输完成。

5.编码和解码:多机通信中,发送数据的单片机需要将数据进行编码,接收数据的单片机需要对接收到的数据进行解码。

编码和解码方式有很多种,如二进制编码、格雷码编码等。

编码和解码的目的是确保数据的可靠传输和正确接收。

6.冲突检测和处理:在多机通信中,由于多个单片机共享同一总线,可能会出现冲突和竞争的情况。

为了避免冲突,需要设计冲突检测和处理机制。

常见的机制有仲裁器、优先级检测和时间片轮转等。

单片机课程设计——多机通信

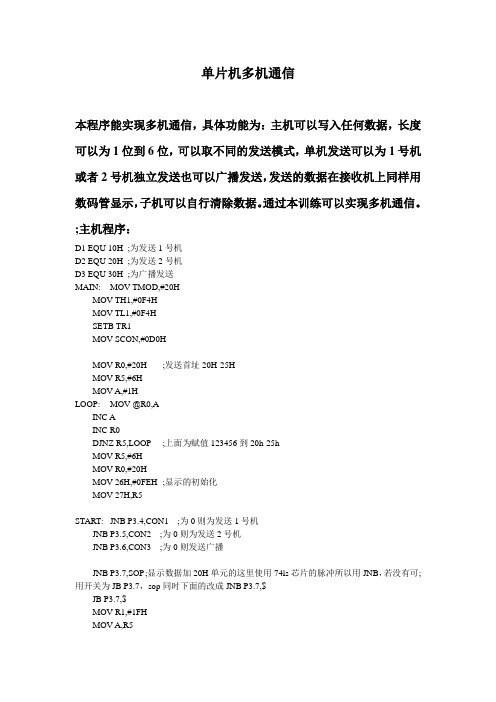

单片机多机通信本程序能实现多机通信,具体功能为:主机可以写入任何数据,长度可以为1位到6位,可以取不同的发送模式,单机发送可以为1号机或者2号机独立发送也可以广播发送,发送的数据在接收机上同样用数码管显示,子机可以自行清除数据。

通过本训练可以实现多机通信。

;主机程序:D1 EQU 10H ;为发送1号机D2 EQU 20H ;为发送2号机D3 EQU 30H ;为广播发送MAIN: MOV TMOD,#20HMOV TH1,#0F4HMOV TL1,#0F4HSETB TR1MOV SCON,#0D0HMOV R0,#20H ;发送首址20H-25HMOV R5,#6HMOV A,#1HLOOP: MOV @R0,AINC AINC R0DJNZ R5,LOOP ;上面为赋值123456到20h-25hMOV R5,#6HMOV R0,#20HMOV 26H,#0FEH ;显示的初始化MOV 27H,R5START: JNB P3.4,CON1 ;为0则为发送1号机JNB P3.5,CON2 ;为0则为发送2号机JNB P3.6,CON3 ;为0则发送广播JNB P3.7,SOP ;显示数据加20H单元的这里使用74ls芯片的脉冲所以用JNB,若没有可;用开关为JB P3.7,sop同时下面的改成JNB P3.7,$JB P3.7,$MOV R1,#1FHMOV A,R5ADD A,R1MOV R1,AINC @R1CJNE @R1,#0AH,SOPMOV @R1,#0HSOP: JB P3.3,STOPJNB P3.3,$INC R5CJNE R5,#7H,STOPMOV R5,#1HSTOP: ACALL DISPLAY ;要传送的数码显示SJMP STARTCON1: JNB P3.4,$ ;下面为发送的机号MOV 28H,#D1SJMP BIGICON2: JNB P3.5,$MOV 28H,#D2SJMP BIGICON3: JNB P3.6,$MOV R1,#D3BIGI: MOV 27H,R5 ;存放长度MOV R0,#20HBIGIN: SETB TB8 ;要置位MOV SBUF,28HWAIT1: JBC TI,TRS0AJMP W AIT1 ;发送机号TRS0: JBC RI,WAIT ;有没有机接到并返回数据SJMP TRS0WAIT: MOV A,SBUFCJNE A,#11H,START ;为11表示有机接到,不为则从头开始TRS1: CLR TB8MOV SBUF,R5 ;发送长度WAIT2: JBC TI,TRS2AJMP W AIT2;*********发送数据*****TRS2: MOV A,@R0CLR TB8 ;要清MOV SBUF,AWAIT3: JBC TI,CONTAJMP W AIT3CONT: DJNZ R5,TRS2;对一些在显示用到的量从新赋值MOV R0,#20HMOV 26H,#0FEHMOV R5,27HSJMP START;下面是显示程序DISPLAY:JB P1.0,DISPL; ACALL CLEANDISPL: MOV P2,#0FFHMOV DPTR,#DABMOV A,@R0MOVC A,@A+DPTRMOV P0,AINC R0MOV A,26HMOV P2,ARL AMOV 26H,AACALL DELAYDJNZ 27H,OUTMOV R0,#20HMOV 26H,#0FEHMOV 27H,R5OUT: RETDELAY: MOV R6,#10HLOP1: MOV R7,#10HLOP2: NOPNOPDJNZ R7,LOP2DJNZ R6,LOP1RETDAB: DB 3FH,06H,5BH,4FH,66H,6DH,7DH,07H,7FH,6FH,00H DB 5EH,79H,71H,73H,3EH,31H,6EH,0FFH,00HEND;通信子机1号D3 EQU 30HSTART: MOV TMOD,#20HMOV TH1,#0F4HMOV TL1,#0F4HSETB TR1MOV 41H,#6HMOV 27H,#6HMAIN: MOV SCON,#0F0H ;SM2为1MOV 26H,#0FEHMOV R0,#20H ;存储首址SETB 7FHSETB 7EHSETB RENWAIT: ACALL DISPLAYJBC RI,READSJMP W AITREAD: MOV A,SBUFCJNE A,#D1,LOP ;检查机号是否对配SJMP BINGINLOP: CJNE A,#D3,EXIT ;检查是否为广播SJMP BINGINEXIT: SETB SM2SJMP W AITBINGIN: MOV R0,#20HMOV A,#11HMOV SBUF,A ;为了能正确接收导数据,因为在接收时不能及时读取RI(显示功能的时间延迟)TT1:JBC TI,BINSJMP TT1BIN: CLR SM2 ;清掉WAIT1: JBC RI,INTSSJMP W AIT1INTS: JB 7FH,CHANGJB 7EH,DATSJMP MAINCHANG: MOV A,SBUFMOV 41H,AMOV 27H,A ;记录长度初值为6CLR 7FHSJMP BINDA T: MOV A,SBUFMOV @R0,AINC R0DJNZ 41H,BINCLR 7EHMOV 41H,27HSJMP MAINDISPLAY:JB P1.0,DISPL ACALL CLEAN DISPL: MOV P2,#0FFH MOV DPTR,#DABMOV A,@R0MOVC A,@A+DPTRMOV P0,AINC R0MOV A,26HMOV P2,ARL AMOV 26H,AACALL DELAYDJNZ 27H,OUTMOV R0,#20HMOV 26H,#0FEHMOV 27H,41H OUT: RETDELAY: MOV R6,#10H LOP1: MOV R7,#10H LOP2: NOPNOPDJNZ R7,LOP2DJNZ R6,LOP1RETCLEAN: MOV 42H,#6HMOV R0,#20H CLEA1: MOV @R0,#00HINC R0DJNZ 42H,CLEA1MOV R0,#20HMOV 26H,#0FEHMOV 27H,41HRETDAB: DB 3FH,06H,5BH,4FH,66H,6DH,7DH,07H,7FH,6FH,00HDB 5EH,79H,71H,73H,3EH,31H,6EH,0FFH,00HEND;通信子机2号D1 EQU 20HD3 EQU 30HSTART: MOV TMOD,#20HMOV TH1,#0F4HMOV TL1,#0F4HSETB TR1MOV 41H,#6HMOV 27H,#6HMAIN: MOV SCON,#0F0H ;SM2为1MOV 26H,#0FEHMOV R0,#20H ;存储首址SETB 7FHSETB 7EHSETB RENWAIT: ACALL DISPLAYJBC RI,READSJMP W AITREAD: MOV A,SBUFCJNE A,#D1,LOP ;检查机号是否对配SJMP BINGINLOP: CJNE A,#D3,EXIT ;检查是否为广播MOV R0,#20H;同样要赋值,下面一行和这一行是不同于1号子机的SJMP BIN;##############是广播时不发送让1号机发EXIT: SETB SM2SJMP W AITBINGIN: MOV R0,#20HMOV A,#11HMOV SBUF,A ;为了能正确接收导数据,因为在接收时不能及时读取RI(显示功能的时间延迟)TT1:JBC TI,BINSJMP TT1BIN: CLR SM2 ;清掉WAIT1: JBC RI,INTSSJMP W AIT1INTS: JB 7FH,CHANGJB 7EH,DATSJMP MAINCHANG: MOV A,SBUFMOV 41H,AMOV 27H,A ;记录长度初值为6CLR 7FHSJMP BINDA T: MOV A,SBUFMOV @R0,AINC R0DJNZ 41H,BINCLR 7EHMOV 41H,27HSJMP MAINDISPLAY:JB P1.0,DISPLACALL CLEANDISPL: MOV P2,#0FFHMOV DPTR,#DABMOV A,@R0MOVC A,@A+DPTRMOV P0,AINC R0MOV A,26HMOV P2,ARL AMOV 26H,AACALL DELAYDJNZ 27H,OUTMOV R0,#20HMOV 26H,#0FEHMOV 27H,41HOUT: RETDELAY: MOV R6,#10HLOP1: MOV R7,#10HLOP2: NOPNOPDJNZ R7,LOP2DJNZ R6,LOP1RETCLEAN: MOV 42H,#6HMOV R0,#20HCLEA1: MOV @R0,#00HINC R0DJNZ 42H,CLEA1MOV R0,#20HMOV 26H,#0FEHMOV 27H,41HRETDAB: DB 3FH,06H,5BH,4FH,66H,6DH,7DH,07H,7FH,6FH,00H DB 5EH,79H,71H,73H,3EH,31H,6EH,0FFH,00HEND下面为参考资料:《单片机多机通讯实验》程序清单; 多机通信主机程序U33CLK EQU 0FFF90HID1 EQU 10ID2 EQU 20ORG 0000HMOV SP,#60HMOV TMOD,#20H ; 定时器1 方式2 定时MOV TL1, #0F4H ; 计数初值MOV TH1, #0F4HSETB TR1MOV SCON, #0D0H ; 方式3, 允许接收, 主机的SM2 为0; load number #00H ~ #0FH into 30H ~ 3FH 单元中MOV R7, #16MOV R0, #30HMOV A, #00HLP: MOV @R0, AINC AINC R0DJNZ R7, LPMOV 20H, #ID1MOV 21H, #ID2MOV DPTR ,#U33CLKLP0:MOV R1, #20HSENDADD:MOV A, @R1 ; send 分机的编号ID SETB TB8 ; TB8 为1MOV SBUF, AWAIT:JBC TI, CONTSJMP WAITCONT:MOV R7, #16MOV R0, #30HSENDDAT: ; start to send data MOV A , @R0CLR TB8 ; TB8 为0MOV SBUF, AWAIT1:JBC TI,RECEIVESJMP WAIT1RECEIVE:JBC RI, REC1SJMP RECEIVEREC1:MOV A, SBUFMOVX @DPTR, A ; send data to LED for displayINC R0 ; R0 point next data to be sentDJNZ R7, SENDDATMOV A,#55H ; SEND END CODECLR TB8MOV SBUF, AWAIT2:JBC TI CONT2SJMP WAIT2CONT2:INC R1CJNE R1, #22H, SENDADD ; 是否循环检查完所有分机MOV R1,#20HLP1:LJMP LP0END; 多机通信从机程序( 编号为10 )CLK273 EQU 0FF90HID EQU 10ORG 0000HMOV SP,#60HMOV TMOD,#20H ; 定时器1 方式2 定时MOV TL1,#0F4H ; 计数初值MOV TH1,#0F4HSETB TR1MOV SCON,#0F0H ; 方式3, 允许接收, 多机通信RECEIVE: ; RECEIVE ADDRESSJBC RI, REC1SJMP RECEIVEREC1:MOV A , SBUFCJNE A,#ID, RECEIVECLR SM2RECDAT: ; START TO RECEIVE DATAJBC RI,REC2SJMP RECDATREC2:MOV A , SBUFCJNE A,#55H , CONTSJMP EXITCONT:MOV DPTR , #CLK273 ; 送LED 显示MOVX @DPTR , ASEND:MOV SBUF,A ; 将接收到的数据再送至主机WAIT: JBC TI,CONT1SJMP WAITCONT1:SJMP RECDAT ; RECEIVE NEXT DATA EXIT: SETB SM2SJMP RECEIVE ; JUMP RECEIVE ADDRESS End ; 程序结束。

MCS-51单片机的多机通信方式

多机通信原理

每台从机一个地址(编号) 系统中的通信总是由主机发起 主机向从机发送的信息分为地址字节和数据字节两种。地址字

节用于寻址从机,数据字节为发给从机的实际数据,二者可以 使用第9位来区分。地址字节帧的第9位为1,数据字节帧的第9 位为0 系统初始化时,将所有从机的SM2位置为1,并允许串行口接收 中断。这样,只有主机送来的地址帧才会被接收

单片机原理与应用

MCS-51单片机的多机通信方式

SCON中的SM2位可以作为多处理机通信位,使单片机方便地 应用于集散式分布系统中

集散式分布系统,或者称为分布式控制系统(DCS),是相对于 集中式控制系统而言的一种新型计算机控制系统,它是在集中 式控制系统的基础上发展、演变而来的。这种系统中,有一台 主机和多台从机。主机负责全局运行情况的监视、统计、控制 等,各从机负责本地信号的采集处理、本地资源的控制。主机 和从机通过通信线路相联系

1.2 通信协议的设计

通信协议中,除规定命令、数据的格式,还有以下一些方面需 要特别考虑

命令的顺序 差错处理 超时处理

单片机原理与应用

ห้องสมุดไป่ตู้

1.1 多机通信原理

主从式多机通信连接方式

多机通信原理

当串行口工作在方式2或3时 若SM2=1,则只有接收到的第9位数据(RB8)为1时,才将数据

送入接收缓冲器SBUF,并置位RI,申请中断,否则丢弃接收 到的数据 若SM2=0,则无论第9位数据(RB8)是1还是0,都将数据装入 SBUF,置位RI,申请中断

51单片机多机通讯汇编语言

6.通讯过程

1)开始时,所有从机的SM2=1,都处于只能接收地址的状态。

2)主机发送地址信息,第9位TB8为1。 3)所有从机接收地址信息,RB8=1,产生中断RI=1

4)从机将接收到的地址信息和本机地址比较,若相同,则清零SM2, (并向主机应答),准备接收数据。

5)主机发送数据信息(TB8 = 0) 6)从机接收数据完成后,置位SM2,回到开始状态。

小组成员: 杜映宝 方冉 韩荣鹏

胡杨

1.51单片机多机通讯原理

随着单片机在工业自动化控制、智能仪器仪表中的广泛应用,单机已 经逐渐不能满足需要,多机协同工作已经成为一个重要的发展趋势, 多机应用的关键就在于多机之间的互相通讯、互传数据信息。

计算机与外部设备的信息传递称为通讯。51单片机多机通讯是指多片 51单片机之间进行通讯。 单片机多机通信的方式可以分为星形、环形、串行总线型和主从式多 机型四种。而其中又以主从式多机通信最为普遍。

串口控制寄存器SCON:

SM0 SM1 SM2 REN TB8 RB9 TI

当选择工作模式2或3时:

RI

主机有发送信息有两种状态:

1)当TB8 = 1,表示发送地址信息 2)当TB8 = 0,表示发送数据信息 从机有两种状态: 1)SM2 = 1, 只能接受地址信息 2)SM2 = 0,能接收地址和数据信息

4.通讯方式

采用串行通讯方式

1)直接采用51单片机中自带的串行接口进行通讯 51串口的工作模式2和3均支持多机通讯,通过SCON寄存器中SM2位

和TB8位的组合使用可以实现多机间的通讯。

2)采用标准串行总线接口方式进行通讯 可用软件模拟I2C协议,实现多机间的I2C协议通讯。

5.使用51串口实现的原理

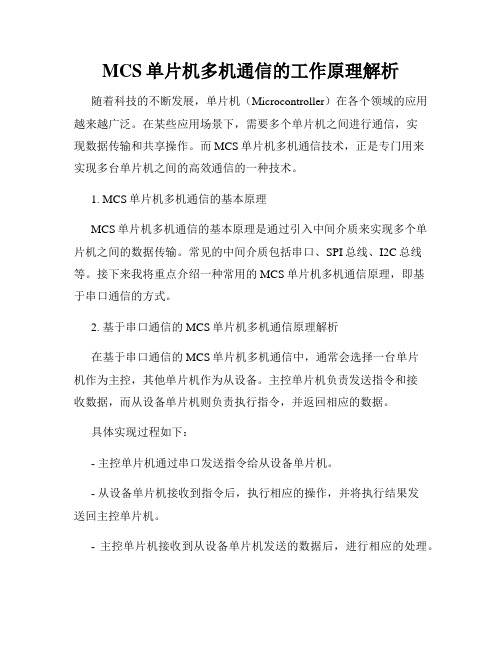

MCS单片机多机通信的工作原理解析

MCS单片机多机通信的工作原理解析随着科技的不断发展,单片机(Microcontroller)在各个领域的应用越来越广泛。

在某些应用场景下,需要多个单片机之间进行通信,实现数据传输和共享操作。

而MCS单片机多机通信技术,正是专门用来实现多台单片机之间的高效通信的一种技术。

1. MCS单片机多机通信的基本原理MCS单片机多机通信的基本原理是通过引入中间介质来实现多个单片机之间的数据传输。

常见的中间介质包括串口、SPI总线、I2C总线等。

接下来我将重点介绍一种常用的MCS单片机多机通信原理,即基于串口通信的方式。

2. 基于串口通信的MCS单片机多机通信原理解析在基于串口通信的MCS单片机多机通信中,通常会选择一台单片机作为主控,其他单片机作为从设备。

主控单片机负责发送指令和接收数据,而从设备单片机则负责执行指令,并返回相应的数据。

具体实现过程如下:- 主控单片机通过串口发送指令给从设备单片机。

- 从设备单片机接收到指令后,执行相应的操作,并将执行结果发送回主控单片机。

- 主控单片机接收到从设备单片机发送的数据后,进行相应的处理。

为了保证通信的稳定性和可靠性,通常会在通信协议中添加数据校验位和帧头帧尾等标志位。

这样可以在通信过程中检测并纠正错误,保证数据的正确传输。

3. MCS单片机多机通信的应用场景MCS单片机多机通信广泛应用于各种领域,其中一些常见的应用场景包括:- 工业控制系统:用于监控设备状态、实现设备间的数据共享和协调控制等。

- 自动化设备:用于实现各个模块之间的数据交换和传输。

- 无线通信系统:用于实现多个无线设备之间的数据传输和通信。

4. 实例分析:电梯控制系统以电梯控制系统为例,介绍MCS单片机多机通信在实际应用中的工作原理。

电梯控制系统通常由一个主控单片机和多个从设备单片机组成,主控单片机负责控制电梯的运行、调度和故障检测等功能,而从设备单片机则负责电梯的各个部件的控制。

在电梯控制系统中,主控单片机通过串口发送指令给从设备单片机,例如指令可以包括电梯的上行、下行、停止等操作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

单片机多机通信在单片机多机通信过程中,PC机将指令打包后发给智能接口单元(以下简称主单片机)。

主单片机收到完整一包后将包解开,按对每个从机的指令分别发送,同时将各从机发给PC机的指令送给PC机。

由于64个从机和主单片机使用同一串口通信线,为避免发生冲突,主单片机处于主动状态,按一定的定时间隔与每一台从机顺序通信。

主单片机在与每一台从机通信过程中先发送地址,从机收到地址后若与自己的地址一致,则继续接收主单片机发来的一个字节的命令码,从机收到命令后,将自己的一个字节的命令发送到主单片机。

主单片机完成与64个从机的通信需要64个定时间隔,只要定时间隔足够短,主单片机与从机基本上可以实现实时通信。

在整个通信过程中,主单片机起着通信枢纽的作用。

单片机多机通信过程安排如下:使所有从机的SM2位置1,处于只接收地址帧的状态;主机发送一帧地址信息,其中包含8位地址,第9位为地址、数据标志位,第9位置1表示发送的是地址;从机接收到地址帧后,各自将所接收的地址与本从机的地址相比较,对于地址相符的从机,使SM2清0以接收主机随后发来的信息,对于地址不相符的从机,仍保持SM2=1状态,对主机随后发送的数据不予理睬,直至发送新的地址帧;主机发送控制指令与数据,给被寻址的从机数据帧的第9位置0,表示发送的是数据。

�单片机程序采用PLM51语言设计,主单片机定时中断服务程序框图如图4所示。

主单片机RS-485串行口接收和发送中段服务程序框图如图5所示。

主单片机RS-232C串行口接收中断服务程序如图6所示。

从单片机RS-485串行口接收和发送中段服务程序框图如图7所示。

主单片机在主程序中以查询方式将各从机送来的数据从内存中读出后顺序发送给上位PC机。

程序清单略。

图1 RS485通信接口原理图2 单片机多机通信硬件电路设计中需注意的问题2.1 电路基本原理某节点的硬件电路设计如图1所示,在该电路中,使用了一种RS-485接口芯片SN75LBC184,它采用单一电源Vcc,电压在+3~+5.5 V范围内都能正常工作。

与普通的RS-485芯片相比,它不但能抗雷电的冲击而且能承受高达8 kV的静电放电冲击,片内集成4个瞬时过压保护管,可承受高达400 V的瞬态脉冲电压。

因此,它能显著提高防止雷电损坏器件的可靠性。

对一些环境比较恶劣的现场,可直接与传输线相接而不需要任何外加保护元件。

该芯片还有一个独特的设计,当输入端开路时,其输出为高电平,这样可保证接收器输入端电缆有开路故障时,不影响系统的正常工作。

另外,它的输入阻抗为RS485标准输入阻抗的2倍(≥24 kΩ),故可以在总线上连接64个收发器。

芯片内部设计了限斜率驱动,使输出信号边沿不会过陡,使传输线上不会产生过多的高频分量,从而有效扼制电磁干扰。

在图1中,四位一体的光电耦合器TLP521让单片机与SN75LBC184之间完全没有了电的联系,提高了工作的可靠性。

基本原理为:当单片机P1.6=0时,光电耦合器的发光二极管发光,光敏三极管导通,输出高电压(+5 V),选中RS485接口芯片的DE端,允许发送。

当单片机P1.6=1时,光电耦合器的发光二极管不发光,光敏三极管不导通,输出低电压(0 V),选中RS485接口芯片的RE端,允许接收。

SN75LBC184的R端(接收端)和D端(发送端)的原理与上述类似。

2.2 RS-485的DE控制端设计在RS-485总线构筑的半双工通信系统中,在整个网络中任一时刻只能有一个节点处于发送状态并向总线发送数据,其他所有节点都必须处于接收状态。

如果有2个节点或2个以上节点同时向总线发送数据,将会导致所有发送方的数据发送失败。

因此,在系统各个节点的硬件设计中,应首先力求避免因异常情况而引起本节点向总线发送数据而导致总线数据冲突。

以MCS51系列的单片机为例,因其在系统复位时,I/O口都输出高电平,如果把I/O口直接与RS-485接口芯片的驱动器使能端DE 相连,会在CPU复位期间使DE为高,从而使本节点处于发送状态。

如果此时总线上有其他节点正在发送数据,则此次数据传输将被打断而告失败,甚至引起整个总线因某一节点的故障而通信阻塞,继而影响整个系统的正常运行。

考虑到通信的稳定性和可靠性,在每个节点的设计中应将控制RS485总线接口芯片的发送引脚设计成DE端的反逻辑,即控制引脚为逻辑“1”时,DE端为“0”;控制引脚为逻辑“0”时,DE端为“1”。

在图1中,将CPU的引脚P1.6通过光电耦合器驱动DE端,这样就可以使控制引脚为高或者异常复位时使SN75LBC184始终处于接收状态,从而从硬件上有效避免节点因异常情况而对整个系统造成的影响。

这就为整个系统的通信可靠奠定了基础。

此外,电路中还有1片看门狗MAX813L,能在节点发生死循环或其他故障时,自动复位程序,交出RS-485总线控制权。

这样就能保证整个系统不会因某一节点发生故障而独占总线,导致整个系统瘫痪。

2.3 避免总线冲突的设计当一个节点需要使用总线时,为了实现总线通信可靠,在有数据需要发送的情况下先侦听总线。

在硬件接口上,首先将RS-485接口芯片的数据接收引脚反相后接至CPU的中断引脚INT0。

在图1中,INT0是连至光电耦合器的输出端。

当总线上有数据正在传输时,SN75LBC184的数据接收端(R端)表现为变化的高低电平,利用其产生的CPU下降沿中断(也可采用查询方式),能得知此时总线是否正“忙”,即总线上是否有节点正在通信。

如果“空闲”,则可以得到对总线的使用权限,这样就较好地解决了总线冲突的问题。

在此基础上,还可以定义各种消息的优先级,使高优先级的消息得以优先发送,从而进一步提高系统的实时性。

采用这种工作方式后,系统中已经没有主、从节点之分,各个节点对总线的使用权限是平等的,从而有效避免了个别节点通信负担较重的情况。

总线的利用率和系统的通信效率都得以大大提高,从而也使系统响应的实时性得到改善,而且即使系统中个别节点发生故障,也不会影响其他节点的正常通信和正常工作。

这样使得系统的“危险”分散了,从某种程度上来说增强了系统的工作可靠性和稳定性。

2.4 RS-485输出电路部分的设计在图1中,VD1~VD4为信号限幅二极管,其稳压值应保证符合RS-485标准,VD1和VD3取12 V,VD2 和VD4取7 V,以保证将信号幅度限定在-7~+12 V之间,进一步提高抗过压的能力。

考虑到线路的特殊情况(如某一节点的RS-485芯片被击穿短路),为防止总线中其他分机的通信受到影响,在SN75LBC184的信号输出端串联了2个20 Ω的电阻R1和R2,这样本机的硬件故障就不会使整个总线的通信受到影响。

在应用系统工程的现场施工中,由于通信载体是双绞线,它的特性阻抗为120 Ω左右,所以线路设计时,在RS485网络传输线的始端和末端应各接1个120 Ω的匹配电阻(如图1中的R3),以减少线路上传输信号的反射。

2.5 系统的电源选择对于由单片机结合RS-485组建的测控网络,应优先采用各节点独立供电的方案,同时电源线不能与RS-485信号线共用同一股多芯电缆。

RS-485信号线宜选用截面积0.75 mm2以上的双绞线而不是平直线,并且选用线性电源TL750L05比选用开关电源更合适。

TL750L05必须有输出电容,若没有输出电容,则其输出端的电压为锯齿波形状,锯齿波的上升沿随输入电压变化而变化,加输出电容后,可以抑制该现象。

3 软件的编程SN75LBC184在接收方式时,A、B为输入,R为输出;在发送方式时,D为输入,A、B为输出。

当传送方向改变一次后,如果输入未变化,则此时输出为随机状态,直至输入状态变化一次,输出状态才确定。

显然,在由发送方式转入接收方式后,如果A、B状态变化前,R为低电平,在第一个数据起始位时,R仍为低电平,CPU认为此时无起始位,直到出现第一个下降沿,CPU才开始接收第一个数据,这将导致接收错误。

由接收方式转入发送方式后,D变化前,若A与B之间为低电压,发送第一个数据起始位时,A与B之间仍为低电压,A、B引脚无起始位,同样会导致发送错误。

克服这种后果的方案是:主机连续发送两个同步字,同步字要包含多次边沿变化(如55H ,0AAH),并发送两次(第一次可能接收错误而忽略) ,接收端收到同步字后,就可以传送数据了,从而保证正确通信。

为了更可靠地工作,在RS485总线状态切换时需要适当延时,再进行数据的收发。

具体的做法是在数据发送状态下,先将控制端置“1”,延时0.5 ms左右的时间,再发送有效的数据,数据发送结束后,再延时0.5 ms,将控制端置“0”。

这样的处理会使总线在状态切换时,有一个稳定的工作过程。

数据通信程序基本流程图如图2所示。

图2 数据通信程序基本流程图单片机通信节点的程序基本上可以分为6个主要部分,分别为预定义部分、初始化部分、主程序部分、设备状态检测部分、帧接收部分和帧发送部分。

预定义部分主要定义了通信中使用的握手信号,用于保存设备信息的缓冲区和保存本节点设备号的变量。

设备状态检测部分应能在程序初始化后,当硬件发生故障时,作出相应的反应。

主程序部分应能接收命令帧,并根据命令的内容作出相应的回应。

为缩短篇幅,这里仅给出主程序部分的代码。

如下所示:/* 单片机多机通信主程序流程 */ while(1) { //主循环 if(recv_cmd(&type)==0) //发生帧错误或帧地址与本机 //地址不符,丢弃当前帧后返回 continue; switch(type) { case __ACTIVE_: //主机询问从机是否存在 send_data(__OK_, 0,dbuf);//发送应答信息break; case __GETDATA_: len = strlen(dbuf);send_data(__STATUS_, len,dbuf);//发送状态信息break; default: break; //命令类型错误,丢弃当前帧后返回 } }4 结论RS-485由于使用了差分电平传输信号,传输距离比RS-232更长,最多可以达到3000 m,因此很适合工业环境下的应用。

但与CAN总线等更为先进的现场工业总线相比,其处理错误的能力还稍显逊色,所以在软件部分还需要进行特别的设计,以避免数据错误等情况发生。

另外,系统的数据冗余量较大,对于速度要求高的应用场所不适宜用RS-485总线。

虽然RS-485总线存在一些缺点,但由于它的线路设计简单、价格低廉、控制方便,只要处理好细节,在某些单片机多机通信应用中仍然能发挥良好的作用。

总之,解决可靠性的关键在于工程开始施工前就要全盘考虑可采取的措施,这样才能从根本上解决问题,而不要等到工程后期再去亡羊补牢。