嵌入式4412开发硬件平台之基础介绍

4412开发板之参数表

UT4412CV02参数 系统配置 Samsung Exynos 4412 ACO,主频1.4Ghz,四核 ARM Cortex-A9 quad-core 2GB DDR3 8GB iNAND 特有的电源管理芯片,ACT8847 接口参数 接口支持不同尺寸、不同型号的液晶,TTL/LVDS均可支持 接口电容屏I2C 接口/ 4 线电阻式触摸接口信号 AC97、IIS 接口,支持音频输入、输出、LIN 2路8位SD通道,或者4路4位TF通道;支持SD/MMC/SDIO 接口USB HOST 2.0,可连接USB设备 接口USB OTG 2.0,作为device使用 4 路串口 PWM 控制信号接口 实时时钟 IIC 总线接口 高速SPI 接口 I2S 总线接口 AD 转换接口 摄像头接口 外部中断信号 通用输入输出接口 16-bit data、addr和控制总线信号 高清输出接口 MIPI信号 标准VGA接口 结构参数 邮票孔特性,焊接固定 67.7mm*55.0mm*3.0mm 1.27mm 1.5mm*0.8mm 188 6层,充分考虑EMC/EMI规则 内置测试点 电气特性 5V 3.3V 1.8V -10--70℃ -40--80℃

[学习引导]4412开发板之嵌入式技术学习步骤及项目案例

![[学习引导]4412开发板之嵌入式技术学习步骤及项目案例](https://img.taocdn.com/s3/m/265bace1aeaad1f346933f9d.png)

嵌入式技术的学习步骤(基于iTOP-4412)北京迅为电子有限公司嵌入式技术的知识体系•适用于iTOP-4412开发板及配套教程的学习步骤•嵌入式的知识面广泛,初学者难于入门•本节阐述嵌入式技术学习步骤,适用于初学者•力图起到提纲挈领的作用,在大量学习资料中有一个比较清晰的脉络•最后会介绍一个实战案例首先要搞明白几个重要文件的意义•学习方法:首先要掌握基础架构•对于架构来说,最基本的东西就是要搞清楚几个概念(几个文件的意义):–bootloader引导程序(UBOOT)–linux操作系统内核(kernel)–文件系统(可能包含2个文件)•推荐大家首先研读:“澄清几个基本概念-迅为精英版聊天记录.doc”–该文件在QQ群共享中•开发编译环境的搭建、源代码的编译和烧写、应用和驱动的建立等等都是围绕这几个文件展开的!第二步:搭建开发编译环境•64位WIN7系统--》虚拟机--》ubuntu•对于初学者,推荐按照教程的要求和步骤来做,这样少走弯路,效率更高•其他系统不是不可以,但可能会遇到各种安装和编译过程的问题•熟练掌握以后,再去创新,这时才可以去做各种不同的尝试•搭建开发环境,有的时候并不顺利,需要克服一些安装问题•迅为已经把安装步骤做了很大程度的简化,比如虚拟机上的ubuntu镜像,直接拷贝进去就可以用了,避免了通过网络安装各种插件•搭建完成,就可以按照教程学习源代码编译和系统的烧写。

•再次强调:这些工作都是围绕那三个文件展开的(实际是4个文件)•Linux或Android系统的编译和烧写都是依赖于这个开发环境的。

第三步:Linux应用程序的设计•学会系统文件的编译和烧写后,应进一步学习嵌入式Linux应用程序开发。

•要按照网盘里的视频目录:“iTOP4412开发板视频教程及其相关”--->“嵌入式Linux视频”,进行该部分的学习。

•初学者要按照该视频教程来学习linux应用开发,有两个方面需要注意:–第一个实验(第0个),制作最小系统。

4412手册

4412手册欢迎使用4412型号的操作手册!这里将为您简单介绍这一型号的基本功能和操作。

1. 硬件规格- 尺寸:100mm x 80mm x 20mm- 重量:150g- 屏幕:2.4英寸TFT彩色屏幕,分辨率240 x 320- 电池:3.7V/800mAh可充电锂电池- 接口:Micro USB充电接口、3.5mm立体声耳机插孔、TF卡插槽(最大可扩展至32GB)2. 基本操作- 开机:按住机身上的“开关”键3秒钟,屏幕将出现开机动画,稍等片刻后进入主界面。

- 关机:长按机身上的“开关”键3秒钟,待屏幕关闭后即可断开电源。

- 返回:在任意页面上按下左下方的“返回”键,即可返回上一个页面。

3. 系统设置- 语言:进入系统设置,在“语言”中选择您所需要的语言。

- 时间:进入系统设置,在“日期和时间”中进行时间、日期的设置。

- 屏幕:进入系统设置,在“屏幕”中进行亮度、背光、屏幕保护等设置。

- 存储:进入系统设置,在“存储”中可以查看机身存储和TF卡存储的使用情况,也可以格式化TF卡。

- 其他设置:包括连接设置、应用程序管理等,可根据需要进行设置。

4. 操作方式- 滑动操作:在主界面或应用页面上,您可以使用手指来上下滑动屏幕,查看更多内容。

- 点击操作:在主界面或应用页面上,您可以通过点击屏幕上的图标或按钮来打开相应的应用或执行相应的操作。

- 按住操作:在主界面或应用页面上,您可以按住屏幕上的图标或按钮,弹出相应的操作菜单。

5. 应用介绍- 音乐播放器:支持MP3、WAV、AAC等格式的音乐文件播放,您可以将音乐文件存储在机身或TF卡中,也可以通过电脑传输文件到设备中。

同时,您可以通过耳机或机身自带的扬声器进行播放。

- 视频播放器:支持AVI、RMVB、MKV、VOB等格式的视频文件播放,您可以将视频文件存储在机身或TF卡中,也可以通过电脑传输文件到设备中。

同时,您可以通过耳机或机身自带的扬声器进行播放。

4412开发板 使用手册

4412开发板使用手册4412开发板使用手册一、引言4412开发板是一款基于SAMSUNG S5PV4412处理器的开发板,具有强大的计算能力和丰富的外设功能。

本手册旨在为用户提供详细的使用说明,帮助用户快速上手和开发。

二、产品概述4412开发板采用ARM Cortex-A9架构的S5PV4412处理器,主频可达1.4GHz。

板载2GB DDR3内存和16GB eMMC闪存,以及多种外设接口,如USB、HDMI、以太网、SD卡等。

此外,开发板还支持Android、Linux等多种操作系统。

三、主要硬件配置1. 处理器:SAMSUNG S5PV4412 Cortex-A9 Quad Core 1.4GHz2. 内存:2GB DDR33. 存储:16GB eMMC闪存4. 外设接口:USB、HDMI、以太网、SD卡、串口等5. 屏幕:7英寸TFT触摸屏,分辨率1024*600四、系统启动1. 准备一张TF卡,将预先制作好的系统镜像文件写入TF卡。

2. 插入TF卡到开发板TF卡插槽上,连接电源和显示器。

3. 开机后,系统会自动从TF卡中启动,进入操作系统。

五、开发环境搭建1. 下载并安装ARM交叉编译工具链,使用该工具链进行代码编译。

2. 配置开发环境的路径和变量,将工具链添加到系统的环境变量中。

3. 配置开发板的网络连接,以便与开发机进行通信和代码烧录。

4. 安装ADB工具,用于连接和调试Android系统。

六、开发工具介绍1. Eclipse:集成开发环境,用于开发和调试应用程序。

2. Android Studio:用于Android应用程序开发的IDE。

3. GNU工具链:用于编译和调试嵌入式应用程序的开发工具。

4. DDMS:Android调试桥,用于监视设备状态和日志。

七、开发步骤1. 配置开发环境:安装和配置Eclipse、Android Studio、GNU工具链等开发工具。

2. 创建项目:在开发环境中创建一个新的Android或Linux项目。

【资源分享】迅为 iTOP-4412开发板平台详解

【资源分享】迅为iTOP-4412开发板平台详解开发板是一个相对复杂的电子系统,请耐心按照本章说明组装,以免造成不必要的损失。

用户最好使用迅为提供的连接线,因为有些部件是专门定制的,可能和市场上购买的其它连接线和部件不匹配,擅自使用市场上购买的接线或者部件可能损伤开发板。

在完全弄清楚开发板接口信号定义之前,如果本文档中没有提到该部件和您在市场上所购买的部件兼容,不要擅自使用自己购买的接线和其它部件,如有疑问请咨询我司技术人员。

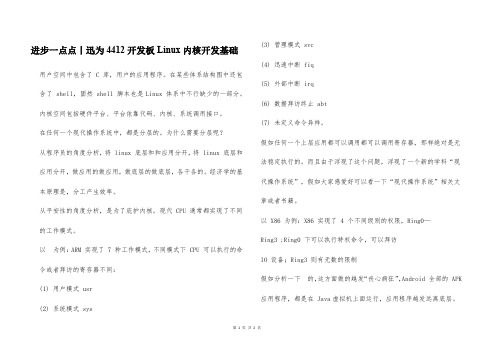

开发板的组装控制台(Console)串口使用串口线连接开发板的COM3 到PC 机的串口,如果PC或笔记本没有串口,就需要准备一条USB转串口的设备。

注意:插拔串口,要在断电的情况下进行,以免带电插拔出现器件损坏。

PC 上对串口的操作软件请参考“3.1 超级终端的安装和使用”。

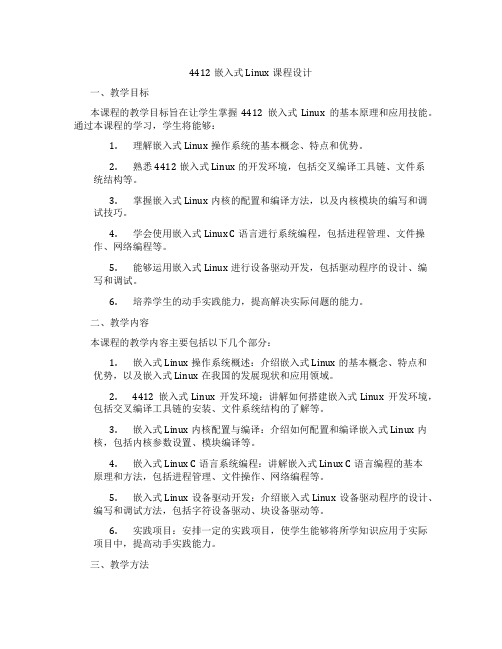

Exynos 4412 共有四个串口,其中CON3 是作为系统的调试串口,如下图所示:屏幕的连接从外观上来看,开发板有2 个HDMI 接口,其实只有一个可以接到HDMI 显示器上。

如下图所示:外形较大的HDMI-A 接口(上图中红色方框内的接口),只能连接迅为提供的7 寸屏幕或者9.7 寸屏幕,里面有5V(或者 3.3V)电源,绝对不能接到HDMI 显示器上。

使用迅为提供的HDMI 线是可以防呆的,不会接错,在用户弄清楚信号之前,不要擅自使用自己购买的HDMI 线!外形较小的HDMI(上图褐色方框内的接口)是标准的HDMI-C 接口(不属于国际标准,但是在很多电器设备中都有使用,属于日本SONY 公司定义的一种HDMI 接口,具体可以百度),建议使用我司的C 口转A 口的HDMI 线连接。

iTOP-4412 精英版除了使用HDMI 线连接屏幕外,也可以通过用户平常使用的软排线的方式来连接,如下图所示:上图中两个红色方框内的LCD 接口信号是自定义的接口,只能连接迅为提供的屏幕,和其它公司的屏幕并不保证完全兼容,这点大家一定要注意!电阻屏的连接(4.3 寸屏幕)iTOP-4412 精英版可支持4.3 寸电阻屏幕,连接方式如下图所示:4.3 寸屏幕的接口是翻盖式的,软排线带有金属触点的一面朝下连接。

进步一点点丨迅为4412开发板Linux内核开发基础

进步一点点丨迅为4412开发板Linux内核开发基础用户空间中包含了 C 库,用户的应用程序。

在某些体系结构图中还包含了 shell,固然 shell 脚本也是Linux 体系中不行缺少的一部分。

内核空间包括硬件平台、平台依靠代码、内核、系统调用接口。

在任何一个现代操作系统中,都是分层的。

为什么需要分层呢?

从程序员的角度分析,将 linux 底层和和应用分开,将 linux 底层和应用分开,做应用的做应用,做底层的做底层,各干各的。

经济学的基本原理是,分工产生效率。

从平安性的角度分析,是为了庇护内核。

现代 CPU 通常都实现了不同的工作模式。

以为例:ARM 实现了 7 种工作模式,不同模式下 CPU 可以执行的命令或者拜访的寄存器不同:

(1) 用户模式 usr

(2) 系统模式 sys (3) 管理模式 svc

(4) 迅速中断 fiq

(5) 外部中断 irq

(6) 数据拜访终止 abt

(7) 未定义命令异样。

假如任何一个上层应用都可以调用都可以调用寄存器,那样绝对是无法稳定执行的。

而且由于浮现了这个问题,浮现了一个新的学科“现代操作系统”,假如大家感爱好可以看一下“现代操作系统”相关文章或者书籍。

以 X86 为例:X86 实现了 4 个不同级别的权限,Ring0—

Ring3 ;Ring0 下可以执行特权命令,可以拜访

IO 设备;Ring3 则有无数的限制

假如分析一下的,这方面做的越发“丧心病狂”,Android 全部的 APK 应用程序,都是在 Java虚拟机上面运行,应用程序越发远离底层。

第1页共2页。

4412嵌入式Linux课程设计

4412嵌入式Linux课程设计一、教学目标本课程的教学目标旨在让学生掌握4412嵌入式Linux的基本原理和应用技能。

通过本课程的学习,学生将能够:1.理解嵌入式Linux操作系统的基本概念、特点和优势。

2.熟悉4412嵌入式Linux的开发环境,包括交叉编译工具链、文件系统结构等。

3.掌握嵌入式Linux内核的配置和编译方法,以及内核模块的编写和调试技巧。

4.学会使用嵌入式Linux C语言进行系统编程,包括进程管理、文件操作、网络编程等。

5.能够运用嵌入式Linux进行设备驱动开发,包括驱动程序的设计、编写和调试。

6.培养学生的动手实践能力,提高解决实际问题的能力。

二、教学内容本课程的教学内容主要包括以下几个部分:1.嵌入式Linux操作系统概述:介绍嵌入式Linux的基本概念、特点和优势,以及嵌入式Linux在我国的发展现状和应用领域。

2.4412嵌入式Linux开发环境:讲解如何搭建嵌入式Linux开发环境,包括交叉编译工具链的安装、文件系统结构的了解等。

3.嵌入式Linux内核配置与编译:介绍如何配置和编译嵌入式Linux内核,包括内核参数设置、模块编译等。

4.嵌入式Linux C语言系统编程:讲解嵌入式Linux C语言编程的基本原理和方法,包括进程管理、文件操作、网络编程等。

5.嵌入式Linux设备驱动开发:介绍嵌入式Linux设备驱动程序的设计、编写和调试方法,包括字符设备驱动、块设备驱动等。

6.实践项目:安排一定的实践项目,使学生能够将所学知识应用于实际项目中,提高动手实践能力。

三、教学方法本课程采用讲授法、讨论法、案例分析法和实验法等多种教学方法,以激发学生的学习兴趣和主动性。

1.讲授法:通过讲解基本概念、原理和方法,使学生掌握嵌入式Linux的基本知识。

2.讨论法:学生进行课堂讨论,分享学习心得和经验,提高学生的思考能力和团队协作能力。

3.案例分析法:分析实际案例,使学生更好地理解嵌入式Linux在实际应用中的作用和价值。

【原创】浅谈4412处理器给开发板行业带来的新机遇

【原创】浅谈4412处理器给开发板行业带来的新机遇三星,对于每一个从事嵌入式技术开发的人来说都不陌生。

中国的嵌入式行业,尤其是在ARM领域,三星的处理器扮演着举足轻重的作用。

相信很多ARM工程师都是在用过51单片机之后入手的三星ARM7S3C44B0处理器。

这款处理器算是ARM中比较早走入人们视线的。

不再向51单片机那样只能跑裸机程序和精简版的uCos,44B0可以运行Linux操作系统。

这一进步让很多刚接触嵌入式的朋友为之一振。

不过当时嵌入式的概念在国内还没有流行开来,以致到现在很多人对44B0比较陌生。

在2007年左右,很多开发板厂家如雨后春笋般陡然出现,一种新的嵌入式学习模式也随之产生。

诸多技术公司开始仿照三星公司ARM9S3C2140/2440DEMO板(公板)设计适合学习使用的板卡,并命名为“2440开发板”。

一方面2440芯片具有MMU即虚拟内存功能,这点相比44B0来说,有着极大的进步。

S3C2440为32位处理器,MMU的存在可以让其寻址空间增至4G。

比如,2440开发板上标配的内存芯片是128M容量,如果没有MMU,那CPU对内存的应用就是实际的128M空间。

有了MMU的存在,可以将128M内存虚拟为4G。

当然,虚拟的是寻址空间,不仅限于内存的使用。

再者,不同于官方公板,开发板的接口更加丰富也更适合学习,比如IIC、AD、GPIO、LED、蜂鸣器、串口、10M网口这类基本接口应有尽有。

资料方面更是百家争鸣,各显神通。

不仅有三星原厂提供的bootloader、测试程序,还有各家根据产品特点编写的开发教程、使用手册、驱动源码甚至系列视频。

也正是这些开发板公司的出现,使中国ARM技术的门槛大大降低。

S3C2410和S3C2440处理器同为ARM9内核,由于2440拥有更好的性能,所以很快取代了2410,成为各开发板和方案公司的首选。

时至今日,2440依然是最受欢迎的学习型ARM 开发板。

荣品电子三星四核4412核心板开发板常用ARM概念介绍(一)

荣品电子三星四核4412核心板开发板常用ARM概念介绍(一) 深圳荣品电子三星四核4412核心板开发板主要有两款内存不同的产品,包括:1G DDR3+4G EMMC和2G DDR3+4G EMMC的这两种。

同时这两款核心板又主要对应两种开发板。

1G DDR3+4G EMMC的荣品三星4412核心板主要是应用在king4412开发板上。

针对于工业级产品的快速研发,产品价格优惠。

2G DDR3+4G EMMC的荣品三星4412核心板主要是应用在RP4412开发板上。

针对于学习使用和企业产品研发,其操作系统包括:Android4.0.4、Android4.2.2、Ubuntu、Linux+QT2.2及最新的Android4.4.4系统。

所以对于学习和产品研发非常适合。

而不论是在学习还是研发产品,都必须要对4412核心板开发板中常见的ARM名词有一个比较全面的了解才行。

下面是由荣品电子整理的一部分学习和使用开发板应该有的知识,希望能给用户朋友查漏补缺,温故而知新!1.ARM中一些常见英文缩写解释MSB:最高有效位;LSB:最低有效位;AHB:先进的高性能总线;VPB:连接片内外设功能的VLSI外设总线;EMC:外部存储器控制器;MAM:存储器加速模块;VIC:向量中断控制器;SPI:全双工串行接口;CAN:控制器局域网,一种串行通讯协议;PWM:脉宽调制器;ETM:嵌入式跟踪宏;CPSR:当前程序状态寄存器;SPSR:程序保护状态寄存器;2.MAM 使用注意事项:答:当改变 MAM 定时值时,必须先通过向 MAMCR 写入 0 来关闭 MAM,然后将新值写入 MAMTIM。

最后,将需要的操作模式的对应值写入MAMCR,再次打开MAM。

对于低于 20MHz 的系统时钟,MAMTIM 设定为 001。

对于 20MHz 到 40MHz 之间的系统时钟,建议将Flash访问时间设定为2cclk,而在高于40MHz的系统时钟下,建议使用3cclk。

基于tiny4412开发板的嵌入式linux开发环境.ppt

Linux内核的配置编译及下载启动

General setup ---> (-xxxx) Local version - append to kernel release 版本中加入自己的姓名拼音

Device Drivers ---> [*] Network device support ---> ▶<*> USB Network Adapters ---> ➢<*> Davicom DM96xx based USB 10/100 ethernet devices [*] USB support ---> ▶<*> USB4640 HSIC to USB20 Driver

sudo umount /media/FRIENDLYARM (不一定是FREIENDLYARM)

Bootloader的配置编译烧写及使用

Bootloader的配置编译烧写及使用

在tiny4412目录下执行如下命令烧写:

sudo ./sd_fusing.sh /dev/sdb

烧写脚本sd_fusing.sh的简单分析(课堂演示)

嵌入式Linux系统的组成

Bootloader的配置编译烧写及使用

解压友善之臂提供的bootloader程序源码

tar jxvf uboot_tiny4412-org.tar.bz2

切换到解压的目录uboot_tiny4412,打补丁修改

cd uboot_tiny4412 patch –p1 < ../uboot.patch

./mkbl2 u-boot.bin bl2.bin 14336 把插有SD卡的读卡器插入电脑USB口,可用命令sudo fdisk -l

嵌入式硬件基础知识

嵌入式硬件基础知识嵌入式系统是一种特殊的计算机系统,它通常用于嵌入到其他设备中,以完成特定的功能。

嵌入式硬件是构成嵌入式系统的硬件部分,它负责处理数据和控制设备的操作。

了解嵌入式硬件的基础知识对于理解嵌入式系统的工作原理和开发过程至关重要。

一、嵌入式硬件的特点嵌入式硬件与传统计算机硬件相比有一些明显的特点。

首先,嵌入式硬件通常设计为定制化的,针对特定的应用场景和功能需求。

其次,嵌入式硬件通常需要具备较小的尺寸和低功耗的特点,以适应嵌入到各种设备中的要求。

此外,嵌入式硬件还需要具备稳定可靠的性能,以保证系统的正常运行。

二、嵌入式硬件的组成嵌入式硬件通常由处理器、内存、输入输出接口和外设组成。

处理器是嵌入式系统的核心,负责执行指令和进行数据处理。

常见的处理器包括ARM、MIPS和x86等。

内存用于存储程序和数据,通常包括闪存和RAM。

输入输出接口用于与外部设备进行数据交互,例如串口、USB接口和以太网接口等。

外设包括各种传感器和执行器,用于获取环境信息和控制设备。

三、嵌入式硬件的设计流程嵌入式硬件的设计流程包括需求分析、系统设计、电路设计、PCB设计、硬件调试和验证等步骤。

首先,需求分析阶段需要明确系统的功能需求和性能指标。

然后,在系统设计阶段,根据需求分析的结果,确定处理器、内存、接口和外设等硬件组成。

接下来,进行电路设计,包括原理图设计和电路板布局设计。

然后,进行PCB设计,将电路设计结果转化为实际的电路板。

最后,在硬件调试和验证阶段,对设计的硬件进行测试和验证,确保其能够正常运行。

四、嵌入式硬件的开发工具嵌入式硬件的开发通常需要使用一些专用的工具。

常见的工具包括开发板、仿真器、调试器和编程器等。

开发板是用于软硬件开发和调试的平台,通常包括处理器、内存和接口等基本组件。

仿真器和调试器用于在开发过程中对硬件进行调试和测试,以确保其正确性和稳定性。

编程器则用于将程序和数据下载到嵌入式硬件中,使其运行起来。

ARM嵌入式开发板

ARM嵌入式开发板

iTOP-4412 ARM嵌入式开发板----主要特点

iTOP-4412开发平台是北京迅为电子研发设计的嵌入式开发板平台,核心板配备64位双通道2GB DDR3,16GBEMMC存储,三星原厂S5M8767电源管理芯片,低功耗。

底板板载高精度GPS模块,WIFI蓝牙模块,CAN,RS485等工业接口。

资料,源码全开源。

iTOP-4412 ARM嵌入式开发板

iTOP-4412 ARM嵌入式开发板

iTOP-4412 ARM嵌入式开发板----硬件参数屏幕

核心板参数

底板参数

iTOP-4412 ARM嵌入式开发板----软件介绍

稳定的Android 4.0.3 /Android 4.4 Bootloader

内核及设备驱动程序

交叉编译器

上层应用程序

PC端烧写工具

VmWare 7.0+Ubuntu12.04

稳定、通用的Linux + Qt操作系统Bootloader

内核及设备驱动程序

交叉编译器

PC端烧写工具

VmWare 7.0+Ubuntu12.04。

学习嵌入式Linux-选择iTOP-4412开发板

学习嵌⼊式Linux-选择iTOP-4412开发板部分视频观看地址:【视频教程】iTOP-4412开发板之学习⽅法--致初学者【视频教程】三星Exynos 4412处理器开发要点【视频教程】iTOP-4412核⼼板专题【视频教程】iTOP-4412开发板系统烧写篇(⼀)【视频教程】iTOP-4412开发板系统烧写篇(⼆)【视频教程】iTOP-4412开发板的底板设计【视频教程】iTOP-4412开发板编译环境的搭建以及编译指引【视频教程】iTOP4412开发板---⽤户产品定制剖析及设计指导(原理图及LAYOUT)【视频教程】iTOP-4412开发板Linux-QT编译环境的搭建以及编译指引【视频教程】 iTOP-4412开发板GPIO驱动设计--LED(⼀)【视频教程】 iTOP-4412开发板GPIO驱动设计--LED(⼆)【视频教程】基于iTOP-4412的嵌⼊式技术学习步骤部分视频⽬录:产品特点:处理器:Exynos 4412 处理器,Cortex-A9四核,功耗性能俱佳!性能:1GB(可选2GB)双通道 64bit数据总线 DDR3;4GB(可选16GB)固态硬盘EMMC存储;独家提供三星S5M8767电源管理。

丰富扩展:核⼼板320PIN管脚引出,远超同类产品HDMI MIPI ⽹⼝串⼝通⽤总线 GPIO等接⼝⼀应俱全t设计:核⼼板独家采⽤⼋层PCB沉⾦盲埋设计更能保证电磁兼容与系统稳定POP封装与SCP封装核⼼板同时兼容⼀块底板技术:专业平板电脑⽅案商迅为公司原⼚核⼼技术嵌⼊式学习、嵌⼊式开发必备开发板- ⼋层⾼速PCB设计,全机器焊接,杜绝⼿⼯,批量⽆忧!。

- 独家完美实现DVFS(动态电压频率调整)- 核⼼板引出脚最全,扩展能⼒最强- ⼯业级进⼝板对板连接器,插拔⽅便稳定可靠- 稳定运⾏Android 4.0.3操作系统及最新版Android4.2/4.4系统;最通⽤的Linux-3.0.15 + Qt操作系统(QT版本⽀持4.7.1、2.2.0 )。

【嵌入式学习笔记二】烧录制作好的镜像到4412开发板中

【嵌入式学习笔记二】烧录制作好的镜像到4412开发板中说明:本来打算第二份笔记作开发环境搭建的,但是整个开发环境的搭建比较复杂,所以学到后面的时候再回过来系统的讲述一下如何搭建开发环境,这一节内容就讲如何烧录制作好的镜像到开发板中。

一、Android4.0.3的烧写(OTG烧写)1.准备工作(1)硬件准备:iTOP-4412开发板、电源、串口线、OTG线(2)软件及驱动准备:ADB驱动、串口驱动、超级终端(3)安装镜像(压缩包):u-boot-iTOP-4412.bin(uboot,通用引导程序)zImage(kernel,内核)ramdisk-uboot.img和system.img(rootfs,根文件系统)2.烧写过程(1)连接电源、串口线和OTG线(2)打开超级终端,连接开发板(3)打开开发板电源,超级终端下立刻按下回车,进入uboot引导程序(4)分区和格式化操作:(5)第四步:格式化eMMC并创建分区,注:此步骤可以跳过!不必每次都格式化分区;2、格式化命令不会删除uboot文件和Linux 内核文件fdisk -c 0按照默认方式给EMMC分区Linux内核镜像文件为5MAndroid镜像文件为300MData和Cache文件为1G临时文件为300M剩下的为用户区,例如使用手机的时候下载的电影小说都是放在这个区域。

如果想更改Linux 内核镜像文件区域的大小,只能更改u-boot文件a)fatformat mmc 0:1格式化Fat文件系统,也就是默认最大的用户存储空间b)ext3format mmc 0:2格式化Android镜像文件c)ext3format mmc 0:3格式化Data和Cache分区d)ext3format mmc 0:4格式化临时文件保存区(5)输入fastboot 连接主机,这时候超级终端应该不能动了,切到cmd注:如果正常连接的话,输入fastboot应该会有音效,设备管理器也可以看到相应的驱动。

fs4412芯片手册详细解读流程(一)

fs4412芯片手册详细解读流程(一)FS4412芯片手册详细解读介绍•FS4412是一款强大的嵌入式处理器,广泛应用于智能手机、平板电脑和物联网设备等领域。

•本文将详细解读FS4412芯片手册,帮助读者更好地理解和应用该芯片。

架构概述•FS4412采用ARM架构,具有高性能和低功耗的特点。

•芯片集成了多个子系统,包括处理器核心、嵌入式存储器和各种外设接口。

芯片规格处理器性能•FS4412搭载Cortex-A9四核处理器,主频可达,支持NEON技术加速。

•处理器具有多级缓存和乱序执行功能,提高了指令级并行和性能。

存储器•芯片内置32KB指令缓存和32KB数据缓存,提供高速的存取能力。

•支持DDR3和LPDDR2双通道内存接口,最大可扩展到4GB。

外设接口•FS4412支持多种外设接口,包括USB、UART、SPI、I2C和GPIO 等。

•提供丰富的硬件接口和扩展能力,满足各种应用需求。

芯片手册解读引脚定义与功能•芯片手册详细列出了FS4412的引脚定义和功能,方便开发者进行硬件设计和接口连接。

•各个引脚的用途和电器特性都有详细的说明和推荐连接电路。

寄存器和寄存器编程•手册提供了芯片内部各个模块的寄存器定义和编程方法。

•开发者可以通过对寄存器的读写操作,控制芯片的各种功能和操作。

系统初始化•手册中给出了FS4412的系统初始化流程,包括时钟初始化、内存配置和外设初始化等步骤。

•详细的初始化流程图和代码示例,方便开发者快速上手和开发。

软件开发指南•手册中提供了基于FS4412芯片的软件开发指南。

•包括操作系统移植、驱动程序编写和应用程序开发等内容。

总结•通过对FS4412芯片手册的详细解读,我们对该芯片的架构、规格和功能有了深入的了解。

•开发者可以参考手册中的信息,进行硬件设计、系统初始化和软件开发。

以上是对FS4412芯片手册的详细解读,希望能对读者更好地理解和应用该芯片提供帮助。

4412嵌入式Linux课程设计

4412嵌入式Linux课程设计一、课程目标知识目标:1. 掌握4412嵌入式Linux的开发环境搭建和基本操作;2. 理解嵌入式Linux的内核架构,了解其启动流程;3. 学会使用Makefile进行嵌入式Linux项目的编译和管理;4. 掌握常见的嵌入式Linux设备驱动编程方法;5. 了解嵌入式Linux系统的调试与优化方法。

技能目标:1. 能够独立搭建4412嵌入式Linux开发环境;2. 能够编写简单的嵌入式Linux内核模块;3. 能够编写和修改Makefile,进行项目编译和管理;4. 能够编写常见的嵌入式设备驱动,如串口、I2C、SPI等;5. 能够运用调试工具对嵌入式Linux系统进行调试和优化。

情感态度价值观目标:1. 培养学生对嵌入式Linux系统的学习兴趣,提高自主学习能力;2. 培养学生具备良好的团队合作精神,提高沟通与协作能力;3. 培养学生严谨的编程习惯,注重代码质量;4. 培养学生具备创新意识,敢于挑战自我,克服困难。

课程性质:本课程为实践性较强的课程,旨在帮助学生掌握嵌入式Linux开发的基本知识和技能,提高学生的实际操作能力。

学生特点:学生具备一定的C语言基础,了解计算机组成原理,对嵌入式系统有一定兴趣。

教学要求:结合课程性质和学生特点,注重理论与实践相结合,强调动手实践,鼓励学生积极参与讨论和分享,提高学生的嵌入式Linux开发能力。

在教学过程中,将目标分解为具体的学习成果,以便进行教学设计和评估。

二、教学内容1. 嵌入式Linux开发环境搭建:包括Linux操作系统安装、交叉编译工具链配置、开发板连接与调试;教材章节:第1章 嵌入式Linux基础2. 嵌入式Linux内核架构与启动流程:分析内核源码结构,探讨启动流程中各个阶段的任务;教材章节:第2章 嵌入式Linux内核架构3. Makefile编写与管理:学习Makefile的基本语法,编写适用于嵌入式Linux项目的Makefile;教材章节:第3章 嵌入式Linux程序设计4. 嵌入式设备驱动编程:学习串口、I2C、SPI等常见设备的驱动编写方法;教材章节:第4章 嵌入式Linux设备驱动5. 嵌入式Linux系统调试与优化:介绍系统调试工具,如GDB、Kdump等,探讨系统优化方法;教材章节:第5章 嵌入式Linux调试与优化教学安排与进度:1. 第1周:嵌入式Linux开发环境搭建;2. 第2-3周:嵌入式Linux内核架构与启动流程;3. 第4周:Makefile编写与管理;4. 第5-7周:嵌入式设备驱动编程;5. 第8周:嵌入式Linux系统调试与优化。

嵌入式开发板的学习步骤-基于iTOP-4412开发板

嵌入式开发板的学习步骤-基于iTOP-4412开发板本文主要介绍嵌入式开发板技术的学习步骤。

嵌入式技术的知识面非常广,学起来往往不知道如何下手,那么嵌入式技术应该从哪里开始学起,以及按照什么样的步骤学习,顺利入门,成为一个合格的嵌入式工程师。

最初最基本的东西呢就是要搞清楚几个概念,要搞清楚什么是bootloadre引导程序,什么是Linux操作系统内核Kernel,什么是文件系统。

如果搞不明白,直接去学其他的内容,学起来就比较迷糊,实际上是在走弯路。

接下来大多数工作都是围绕这几个文件展开的,比如编译环境的搭建,源代码的编译和烧写,应用程序和驱动程序的编程等等,就是说这几个文件是贯穿我们整个嵌入式学习的始终的。

把这几个文件搞明白了,后面的学习也就有了目标,所以说搞明白这几个文件的含义非常重要。

接下来需要我们做的是搭建编译环境,迅为公司为了让大家少走弯路,已经把安装步骤做了很大程度的简化,比如已经做好了虚拟机的ubuntu镜像,直接拷贝进去就可以使用了。

开发环境搭建起来以后,这个时候可以学习一下对源码进行编译,同时也可以学习一下烧写,一步步按照教程去做就可以了。

系统的编译和烧写都是依赖于这个开发环境的,也就是必须在虚拟机上安装好ubuntu,并且把源代码从光盘中拷贝到ubuntu的环境下面,只要按照教程的提示往下做就可以了。

在熟练掌握系统的编译和烧写以后,就可以进一步开始嵌入式开发了,那么这个时候建议先学习一下Linux应用程序的设计,也就是按照教程开始逐步深入。

这个时候要按照网盘里的‘iTOP-4412开发板视频教程及其相关’里的‘嵌入式linux 视频’。

大家在初学的时候,还是要按照这个实验的顺序来走一遍,这里强调两个方面,来帮助大家理解:一、第一个实验也就是第0个,是制作linux的最小系统,那么什么是最小系统呢,就是Linux运行的时候能跑的起来的最小系统,也就是说我们在文件系统当中把图形系统的内容从这个文件系统里面砍掉了;在很多设备里面,比如说路由器,或者一些通讯类或者控制类的产品中是不需要图形界面的,这样我们就可以做一个简化的Linux文件系统,这时候最小系统的设计就排上用场了。

Linux平台下UT4412BV03裸机开发指南(五)

Linux平台下UT4412BV03裸机开发指南(五)第一章初始化时钟注:本章的内容来自韦东山老师的《嵌入式Linux系统开发完全手册_基于4412_上册》在芯片手册里,“时钟管理单元(Clock Management Unit)”的简称为CMU。

CMU_XXX表示“XXX模块内的CMU”,比如CMU_CPU等。

第一节Exynos 4412的时钟体系对于PC来说,CPU、内存、主板、声卡、显卡等等,这些功能部件由不同的芯片组成,在实体上是相互独立的。

在嵌入式系统里,一块芯片往往集成了多种功能,比如Exynos 4412上面既有CPU,还有音频/视频接口、LCD接口、GPS等模块。

这类芯片被称为SoC,即System on Chip,译为芯片级系统或片上系统。

不同的模块往往工作在不同的频率下,在一个芯片上采用单时钟设计基本上是不可能实现的,在SoC设计中采取多时钟域设计。

4412的时钟域有5个,如图6.1所示。

图6.1 Exynos 4412时钟域这5个时钟域名如下(下文中的BLK表示block,模块):① CPU_BLK:内含Cortex-A9 MPCore处理器、L2 cache控制器、CoreSight(调试用)。

CMU_CPU用于给这些部件产生时钟。

② DMC_BLK:内含DRAM内存控制器(DMC)、安装子系统(Security sub system)、通用中断控制器(Generic Interrupt Controller,GIC)。

CMU_DMC用于给这些部件产生时钟。

③ LEFTBUS_BLK和RIGHTBUS_BLK:它们是全局的数据总线,用于在DRAM和其他子模块之间传输数据。

④其他BLK:在图6.1中,用画笔圈起来的模块。

CMU_TOP用于给这些模块产生时钟。

从原理图上可知,4412开发板外接24MHz的晶振;但是4412的CPU频率可达1.4GHz。

可以想象,一定有硬件部件,把24MHZ的频率提升为1.4GHZ,这个部件被称为PLL。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

本文转自4412开发板实战书籍:硬件介绍嵌入式系统的硬件除了核心部件——嵌入式处理器外,还包括存储器系统、外围接口部件以及连接各种设备的总线系统。

其中,存储器是嵌入式系统存放数据和程序的功能部件,而外围设备决定了应用于不同领域的嵌入式系统的独特功能。

嵌入式处理器是嵌入式系统中硬件的核心组成部分,但是若没有存储器和I/O设备,它就无法具有各种实用的功能。

嵌入式处理器通常集成了大量的I/O模块单元(如中断控制器和通信控制器等)和存储器(Flash和RAM等)。

当嵌入式处理器上集成的存储器单元和I/O 单元不够时,可以通过扩充组成强大的嵌入式硬件系统。

嵌入式系统的硬件是以嵌入式处理器为中心,由存储器、I/O单元电路、通信模块、外部设备等必要的辅助接口组成的,如下图所示。

在实际应用中,嵌入式系统硬件配置可能非常精简,除了微处理器和基本的外围电路以外,其余的电路可以根据需要和成本进行裁剪、定制。

在嵌入式系统中使用的存储器可以是内部存储器,也可以是外部存储器。

通常处理器的内部存储器是非常有限的。

对于小型应用,如果这些存储器够用,就不必使用外部存储器;否则,就必须进行扩展,使用外部存储设备。

与通用计算机把应用软件和操作系统放在外存的工作方式不同,嵌入式系统的软件通常直接存放在内存(如Flash)中,上电之后可以立刻运行;当然,也有的嵌入式系统的软件从外存启动、装载并运行。

无论如何,需要考虑嵌入式系统的软件的固化问题,而这一问题在通用计算机(如PC机)上开发软件是不需要考虑的。

此外,考虑存储器系统时,还需要考虑嵌入式系统软件的引导问题。

嵌入式处理器工作时必须有附属电路支持,如时钟电路、复位电路、调试电路、监视定时器、中断控制电路等,这些电路并不完成数据的输入/输出功能,而是为嵌入式处理器的工作提供必要的条件。

在设计嵌入式系统的硬件电路时,常常将它们与嵌入式处理器设计成一个模块,形成处理器最小系统。

嵌入式处理器在功能上有别于通用处理器,其区别在于嵌入式处理器上集成了大量的I/O电路。

因此,用户在开发嵌入式系统时,可以根据系统需求选择合适的嵌入式处理器,而无需再另外配合I/O电路。

随着半导体技术的发展,嵌入式处理器的集成度不断提高,许多嵌入式处理器上集成的I/O功能完全满足应用的需求,基本无需扩展。

嵌入式系统的I/O 接口电路主要完成嵌入式处理器与外部设备之间的交互和数据通信。

这些电路包括网络接口、串行接口、模/数转换和数/模转换接口、人机交互接口等。

应用于不同行业的嵌入式系统,其接口功能和数量有很大的差异。

在设计I/O接口电路时,一般把这部分作为I/O子系统进行统一的设计,这样既可以综合考虑优化电路,又便于设计成果的重复使用。

处理器和ARM处理器中央微处理器,简称CPU,它是计算机中最重要的一个部分,它决定嵌入式系统的主要功能特性。

CPU又由运算器和控制器两大部分组成。

所谓寄存器(register),是CPU内部用来存放数据的一些小型存储区域,用于暂时存放参与运算的数据和运算结果。

外部设备也有寄存器,是一种存储单元,其物理结构跟内存单元不一样,但作用跟内存单元一样,都能保存信息。

在设计时,给外部设备的每个寄存器都分配一个地址,CPU可以根据地址访问某个寄存器,则该寄存器发生相应的动作:或接收数据总线上的数据(对应于写操作),或把自己的数据送到数据总线上(对应于读操作)。

当CPU访问某个寄存器时,同一个外设的其他寄存器和其他外设的寄存器由于没有CPU的指令不会发生动作。

嵌入式处理器通常包括几个部分:处理器内核、地址总线、数据总线、控制总线、片上I/O接口电路及辅助电路(如时钟、复位电路等)。

下面简单介绍一下ARM处理器的历史和发展。

1991年ARM公司(Advanced RISC Machine Limited)成立于英国剑桥,最早由Arcon、Apple和VLSI合资成立,主要出售芯片设计技术的授权,在1985年4月26 日,第一个ARM 原型在英国剑桥的Acorn 计算机有限公司诞生(在美国VLSI 公司制造)。

目前,ARM 架构处理器已在高性能、低功耗、低成本的嵌入式应用领域中占据了领先地位。

ARM 公司最初只有12 人,经过十多年的发展,ARM 公司已拥有近千名员工,在许多国家都设立了分公司,包括ARM 公司在中国上海的分公司。

目前,采用ARM 技术知识产权(IP)核的微处理器,即我们通常所说的ARM 微处理器,已遍及工业控制、消费类电子产品、通信系统、网络系统、无线系统等各类产品市场,基于ARM 技术的微处理器应用约占据了32 位RISC 微处理器80%以上的市场份额,其中,在手机市场,ARM 占有绝对的垄断地位。

可以说,ARM技术正在逐步渗入到人们生活中的各个方面,而且随着32 位CPU价格的不断下降和开发环境的不断成熟,ARM技术会应用得越来越广泛。

ARM公司是专门从事基于RISC技术芯片设计开发的公司,作为嵌入式RISC处理器的知识产权IP供应商,公司本身并不直接从事芯片生产,而是靠转让设计许可由合作公司生产各具特色的芯片,世界各大半导体生产商从ARM 公司购买其设计的ARM 微处理器核,根据各自不同的应用领域,加入适当的外围电路,从而形成自己的ARM 微处理器芯片进入市场,利用这种合伙关系,ARM很快成为许多全球性RISC标准的缔造者。

目前,全世界有几十家大的半导体公司都使用ARM公司的授权,其中包括Intel、IBM、Samsung、LG 半导体、NEC、SONY、PHILIP 等公司,这也使得ARM 技术获得更多的第三方工具、制造、软件的支持,又使整个系统成本降低,使产品更容易进入市场并被消费者所接受,更具有竞争力。

存储设备嵌入式系统的存储器子系统与通用计算机的存储器子系统的功能并无明显的区别,这决定了嵌入式系统的存储器子系统的设计指标和方法也可以采用通用计算机的方法,尤其是嵌入通用计算机的大型嵌入式系统更是如此。

存储器子系统设计的首要目标是使存储器在工作速度上很好地与处理器匹配,并满足各种存取需要。

因此,体系结构的特性能够提高存储系统的速度和容量。

随着微电子技术的发展,微处理器的工作速度有了很大的提高。

而微处理器时钟频率提高比内存速度提高要快,以至于内存速度远远落后于CPU速度。

如果大量使用高速存储器,使它们在速度上与处理器相吻合,就能够简便地解决问题。

但是,这种方法受到经济上的限制。

因为随着存储器芯片速度的提高,其价格急剧上升,使系统成本十分昂贵。

在实际的计算机系统中,总是采用分级的方法来设计整个存储器系统。

如下图所示为这种分级存储系统的组织结构示意图,它把全部存储系统分为四级,即寄存器组、高速缓存、内存和外存。

它们在存取速度上依次递减,而在存储容量上逐级递增。

寄存器组是最高一级的存储器。

在计算机设备中,寄存器组一般是微处理器内含的,如上一章介绍的ARM处理器中有37个寄存器。

有些待使用的数据或者运算的中间结果可以暂存在这些寄存器中。

微处理器在对本芯片内的寄存器读/写时,速度很快,一般在一个时钟周期内完成。

从总体上说,设置一系列寄存器是为了尽可能减少微处理器直接从外部取数的次数。

但是,由于寄存器组是制作在微处理器内部的,受芯片面积和集成度的限制,因此寄存器的数量不可能做得很多。

第二级存储器是高速缓冲存储器(Cache)。

高速缓存是一种小型、快速的存储器,其存取速度足以与微处理器相匹配。

高速缓存能够保存部分内存的内容的拷贝,如果正确使用,它能够减少内存平均访问时间。

第三级是内存。

运行的程序和数据都放在内存中。

由于微处理器的寻址大部分在高速缓存上,因此内存可以采用速度稍慢的存储器芯片,对系统性能的影响不会太大,同时又降低了成本。

内存除主要使用RAM外,还要使用一定量的ROM。

这些ROM主要用来解决系统初始化的一系列操作,如设备检测、接口电路初始化、启动操作系统等。

一般情况下,ROM的存取时间比较长,对ROM的每次读/写要增添3~4个等待周期。

但这种少量慢速存储器只在开机时运行,对系统性能影响不大。

最低一级存储器是大容量的外存。

这种外存容量大,但是在存取速度上比内存要慢得多。

目前嵌入式系统中常用闪存作为大容量硬盘存储各种程序和数据。

上述四级存储器系统并不是每个嵌入式系统所必须具备的,应当根据系统的性能要求和处理器的功能来确定。

例如,在8位处理器上,主要考虑内存的时间,而高速缓存极少被采用。

对于16位和32位微处理器组成的系统,随着性能的提高,存储系统变得更为复杂,一般都包含了全部四级存储器。

总线一个处理器系统可能使用多条总线来连接设备。

高速设备可以连到高速总线上,而低速设备连到低速总线上,通过一个被称为桥的逻辑电路使得总线可以互连。

使用这样的总线配置主要考虑到以下几个原因:(1) 高速总线通常提供较宽的数据连接。

(2) 高速总线通常要更昂贵的电路和连接器,可以通过使用较慢的、比较便宜的总线来降低低速设备成本。

(3) 桥允许总线独立操作,因此可以在I/O操作中提供并行性。

在高速总线和低速总线之间的总线桥是高速总线的受控器,是低速总线的主控器。

桥从高速总线上获取指令并将其传到低速总线,将结果从低速总线传到高速总线上。

嵌入式最常用的有四大总线有I2C总线、SPI总线、CAN总线、USB总线。

I2C总线IIC总线,是INTER-IC串行总线的缩写。

INTER-IC原文大意是用于相互作用的集成电路,这种集成电路主要由双向串行时钟线SCL和双向串行数据线SDA两条线路组成,由荷兰菲利浦公司于80年代研制开发成功。

IIC总线在传送数据时其速率可达100kbps,最高速率时可达400kbps,总线上允许连接的设备数主要决定于总线上的电容量,一般设定为400pF以下。

I2C总线主要在微处理器的控制之下,因此通常称微处理器是I2C总线的主机。

习惯上总称受控设备及功能电路为I2C总线的从机。

这种主机与从机之间的连接通常是在总线的输出端,而输出端的电路结构为IIC总线的从机。

这种主机与从机之间的连接通常是在总线的输出端,而输出端的电路结构又总是开漏输出或集电极开路输出。

通常数据传送要由主机发出启动信号和时钟信号,向所控从机发出一个地址、一个读写位和一个应答位,其中地址位为7位数据,在实际控制中,一般一次只能传送一个8位数据,并以一个停止位结束。

在实际应用中,往往被传送的数据位数会超过8位,也就是说总会有多字节传送,这时必须在传送数据地址结束后再传送一个副地址。

因此,被传送的字节没有限制,但每一个字节后面必须有一位应答位。

应答位通常被设定在低电平,当应答位处于高电平时,指示被传送的数据已结束。

在I2C总线的控制系统中,有时从机也可以是多台微处理器,在多台微机同时工作时,它们对总线的控制也由相似于时钟的同步方式进行仲裁,也就是说时钟的同步与仲裁过程是同时进行的,不存在因是主机而有优先权次序。