EDA课程设计彩灯控制器 -

EDA课程设计:八路彩灯控制器

EDA课程设计:八路彩灯控制器第一篇:EDA课程设计:八路彩灯控制器EDA课程设计设计题目:基于VHDL的8路彩灯控制器设计一、课程设计的目的1.熟悉QuartusⅡ软件的使用方法,使用VHDL 文本输入设计法进行任务设计。

2.增强自己实际动手能力,独立解决问题的能力。

3.通过课程设计对所学的知识进行更新及巩固.二、课程设计的基本要求本次课程设计是设计一个8路彩灯控制器,能够控制8路彩灯按照两种节拍,三种花型循环变化。

设计完成后,通过仿真验证与设计要求进行对比,检验设计是否正确。

三、课程设计的内容编写硬件描述语言VHDL程序,设计一个两种节拍、三种花型循环变化的8路彩灯控制器,两种节拍分别为0.25s和0.5s。

三种花型分别是:(1)8路彩灯分成两半,从左至右顺次渐渐点亮,全亮后则全灭。

(2)从中间到两边对称地渐渐点亮,全亮后仍由中间向两边逐次熄灭。

(3)8路彩灯从左至右按次序依次点亮,全亮后逆次序依次熄灭。

四、实验环境PC机一台;软件Quartu sⅡ6.0五、课程设计具体步骤及仿真结果1、系统总体设计框架结构分频模块:把时钟脉冲二分频,得到另一个时钟脉冲,让这两种时钟脉冲来交替控制花型的速度。

二选一模块:选择两种频率中的一个控制彩灯的花型。

8路彩灯的三种花型控制模块:整个系统的枢纽,显示彩灯亮的情况。

2、系统硬件单元电路设计1.分频模块设计实验程序:library ieee;use ieee.std_logic_1164.all;entity fenpin2 isport(clk:in std_logic;clkk:out std_logic);end fenpin2;architecture behav of fenpin2 is beginprocess(clk)variable clkk1:std_logic:='0';beginif clk'event and clk='1' thenclkk1:= not clkk1;end if;clkk<=clkk1;end process;end behav;RTL电路图:波形图:2.二选一模块设计实验程序:library ieee;use ieee.std_logic_1164.all;entity mux21 is port(a,b,s:in std_logic;y:out std_logic);end mux21;architecture behave of mux21 is begin process(a,b,s)begin if s='0' then y<=a;else y<=b;end if;end process;end behave;RTL电路图:波形图:3.8路彩灯的三种花型控制模块设计程序: library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity color8 is port(clk,rst :in std_logic;q:out std_logic_vector(7 downto 0));end;architecture a of color8 is signal s:std_logic_vector(4 downto 0);begin process(s,clk)begin if rst='1' then s<=“00000”;elsif clk'event and clk= '1' then if s=“11111” thens<=“00000”;else s<=s+1;end if;case s is when “00000”=>q<=“00000000”;when“00001”=>q<=“10001000”;when“00010”=>q<=“11001100”;when“00011”=>q<=“11101110”;when “00100”=>q<=“11111111”;when “00101”=>q<=“00000000”;when“00110”=>q<=“00011000”;when“00111”=>q<=“00111100”;when“01000”=>q<=“01111110”;when“01001”=>q<=“11111111”;when“01010”=>q<=“11100111”;when“01011”=>q<=“11000011”;when“01100”=>q<=“10000001”;when“01101”=>q<=“00000000”;when“01110”=>q<=“10000000”;when“01111”=>q<=“11000000”;when“10000”=>q<=“11100000”;when“10001”=>q<=“11110000”;when“10010”=>q<=“11111000”;when“10011”=>q<=“11111100”;when“10100”=>q<=“11111110”;when“10101”=>q<=“11111111”;when“10110”=>q<=“11111110”;when“10111”=>q<=“11111100”;w hen“11000”=>q<=“11111000”;when“11001”=>q<=“11110000”;when“11010”=>q<=“11100000”;when“11011”=>q<=“11000000”;when“11100”=>q<=“10000000”;when“11101”=>q<=“00000000”;when others=>null;end case;end if;end process;end;RTL电路图:波形图:4.综合程序library ieee;use ieee.std_logic_1164.all;entity fenpin2 isport(clk:in std_logic;clkk:out std_logic);end fenpin2;architecture behav of fenpin2 is beginprocess(clk)variable clkk1:std_logic:='0';beginif clk'event and clk='1' thenend if;clkk<=clkk1;end process;end behav;library ieee;use ieee.std_logic_1164.all;entity mux21 is port(a,b,s:in std_logic;y:out std_logic);end mux21;architecture behave of mux21 is begin process(a,b,s)begin if s='0' then y<=a;else y<=b;end if;end process;end behave;library ieee;clkk1:= not clkk1;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity color8 is port(clk,rst :in std_logic;q:out std_logic_vector(7 downto 0));end;architecture a of color8 is signal s:std_logic_vector(4 downto 0);begin process(s,clk)begin if rst='1' then s<=“00000”;elsif clk'event and clk= '1' then if s=“11111” thens<=“00000”;else s<=s+1;end if;case s is when “00000”=>q<=“00000000”;when“00001”=>q<=“10001000”;when“00010”=>q<=“11001100”;when“00011”=>q<=“11101110”;when“00100”=>q<=“11111111”;when“00101”=>q<=“00000000”;when“00110”=>q<=“00011000”;when“00111”=>q<=“00111100”;when“01000”=>q<=“01111110”;when“01001”=>q<=“11111111”;when“01010”=>q<=“11100111”;when“01011”=>q<=“11000011”;when “01100”=>q<=“10000001”;when “01101”=>q<=“00000000”;when“01110”=>q<=“10000000”;when“01111”=>q<=“11000000”;when“10000”=>q<=“11100000”;when“10001”=>q<=“11110000”;when“10010”=>q<=“11111000”;when“10011”=>q<=“11111100”;when“10100”=>q<=“11111110”;when“10101”=>q<=“11111111”;when“10110”=>q<=“11111110”;when“10111”=>q<=“11111100”;when“11000”=>q<=“11111000”;when“11001”=>q<=“11110000”;when“11010”=>q<=“11100000”;when“11011”=>q<=“11000000”;when“11100”=>q<=“10000000”;when“11101”=>q<=“00000000”;when others=>null;end case;end if;end process;end;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity balucaideng is port(clk,s,rst:in std_logic;q:out std_logic_vector(7 downto 0));end;architecture one of balucaideng issignal h0,h1:std_logic;component fenpin2port(clk:in std_logic;clkk:out std_logic);end component;component mux21 port(a,b,s:in std_logic;y:out std_logic);end component;component color8 port(clk,rst :in std_logic;q:out std_logic_vector(7 downto 0));end component;begin u1: fenpin2 port map(clk=>clk,clkk=>h0);u2: mux21 port map(a=>h0,b=>clk,s=>s;y=>h1);u3: color8 port map(clk=>h1,rst=>rst,q=>q);end;波形图:六、实验总结第二篇:eda课程设计-彩灯控制器1.设计目的学习EDA开发软件和MAX+plus Ⅱ的使用方法,熟悉可编程逻辑器件的使用,通过制作来了解彩灯控制系统。

EDA彩灯控制器设计报告

设计报告课程名称EDA技术指导教师王春玲设计题目彩灯灯控系统设计班级2010级专业电子信息科学与技术院系物理与电子工程学院姓名罗小涛学号2010080088合作者孙洋洋·陈方胜摘要:该设计是以现场可编程逻辑器件(FPGA)为设计载体,以硬件描述语言(VHDL)为主要,以原理图输入设计为辅的表达方式,以QuartusⅡ开发软件和EDA 试验箱为设计工具,阐述了彩灯控制器的工作原理和软硬件的实现方法。

它以按键控制彩灯工作模式。

并对所设计的控制器进行了时序仿真和编程下载进行硬件验证,顺利实现设计目标。

关键词:彩灯分频电路VHDL语言FPGA芯片有限状态机Abstract:this design based on field programmable logic devices (FPGA)to design the carrier, with hardware description language (VHDL) as the main, in principle diagram input design, supplemented by express way to Quartus development software and EDA test chamber for design tools, this paper expounds the working principle of lights controller hardware and software and the realization method of it buttons to control lights work mode and the design of controller on the timing simulation and programming download for hardware validation, smooth realization design goalKeywords:lights crossover circuit VHDL language FPGA chipfinite state machine1设计任务及要求1.1要有多重花型变化1.2多种花型可以自动变换,循环往复1.3彩灯变化的快慢节拍可以选择2 系统设计方案2.1 EDA技术简介EDA是电子设计自动化(Electronic Design Automation)缩写,是90年代初从CAD、CAM、CAT和CAE的概念发展而来的。

EDA彩灯控制器课程设计

目录第一章绪论 (1)1.1系统背景 (2)1.2课程设计的主要内容和任务以及要达到的目标 (2)第二章系统电路设计 (3)2.1 系统总体设计框架结构 (3)2.1 系统硬件 (3)第三章系统软件设计 (4)3.1 方案原理 (4)3.2 模块设计 (4)3.3 总体模块设计 (7)第四章实验结果和分析 (7)4.1 实验仿真结果 (7)结束语 (9)附录 (10)第一章绪论1.1系统背景20世纪90年代,国际上电子和计算机技术较先进的国家,一直在积极探索新的电子电路设计方法,并在设计方法、工具等方面进行了彻底的变革,取得了巨大成功。

在电子技术设计领域,可编程逻辑器件(如CPLD、FPGA)的应用,已得到广泛的普及,这些器件为数字系统的设计带来了极大的灵活性。

这些器件可以通过软件编程而对其硬件结构和工作方式进行重构,从而使得硬件的设计可以如同软件设计那样方便快捷。

这一切极大地改变了传统的数字系统设计方法、设计过程和设计观念,促进了EDA技术的迅速发展。

EDA技术就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言VHDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

EDA技术的出现,极大地提高了电路设计的效率和可操作性,减轻了设计者的劳动强度。

利用EDA工具,电子设计师可以从概念、算法、协议等开始设计电子系统,大量工作可以通过计算机完成,并可以将电子产品从电路设计、性能分析到设计出IC版图或PCB版图的整个过程的计算机上自动处理完成。

现在对EDA的概念或范畴用得很宽。

包括在机械、电子、通信、航空航天、化工、矿产、生物、医学、军事等各个领域,都有EDA的应用。

目前EDA技术已在各大公司、企事业单位和科研教学部门广泛使用。

例如在飞机制造过程中,从设计、性能测试及特性分析直到飞行模拟,都可能涉及到EDA技术。

EDA课程设计多路彩灯控制电路设计

EDA课程设计报告——多路彩灯控制电路设计多路彩灯控制电路设计报告题目:多路彩灯控制电路设计要求:⑴要有6种花型变化。

⑵多种花型可以自动变化,循环往复。

⑶彩灯变化的快慢节拍可以选择。

⑷具有清零开关。

设计方案:根据系统设计要求,设计一个具有6种花型循环变化的彩灯控制器。

整个系统共有三个输入信号:控制彩灯节奏快慢的基准时钟信号CLK_IN,系统清零信号CLR,彩灯节奏快慢选择开关CHOSE_KEY;共有16个输出信号LED[15..0],分别用于控制十六路彩灯。

据此,系统设计采用自顶向下的设计方法,我们可将整个彩灯控制器CDKZQ分为两大部分:时序控制电路SXKZ和显示控制电路XSKZ。

模块划分:时序控制电路(SXKZ)显示控制电路(XSKZ)端口介绍:CLK_IN—控制彩灯节奏快慢的基准时钟信号CLR—系统清零信号CHOSE_KEY—彩灯节奏快慢选择开关LED[15..0]—16个输出信号设计过程:⒈时序控制模块(SXKZ)①新建一个VHD格式的文本编辑文件,保存—默认—命名②编写源程序,如下:时序控制模块源程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY SXKZ ISPORT(CHOSE_KEY : IN STD_LOGIC;CLK_ZN : IN S TD_LOGIC;CLR : IN STD_LOGIC;CLK : OUT STD_LOGIC);END SXKZ;ARCHITECTURE ART OF SXKZ ISSIGNAL CK : STD_LOGIC;BEGINPROCESS (CLK_ZN, CLR,CHOSE_KEY)V ARIABLE TEMP : STD_LOGIC_VECTOR(2 DOWNTO 0);BEGINIF CLR='1' THENCK<='0';TEMP:="000";ELSIF (CLK_ZN'EVENT AND CLK_ZN='1') THENIF (CHOSE_KEY='1')THENIF TEMP="011" THENTEMP:="000";CK<=NOT CK;ELSETEMP:=TEMP+1;END IF;ELSEIF TEMP="111" THENTEMP:="000";CK<=NOT CK;ELSETEMP:=TEMP+'1';END IF;END IF;END IF;END PROCESS;CLK<=CK;END ART;③检查错误,如图:④器件配置。

EDA课程设计 彩灯控制器.

电子设计自动化大作业题目彩灯控制器的设计学院**学院班级电气**学号**********姓名********二O一二年十月三十一日彩灯控制器的设计一、彩灯控制器的设计要求设计能让一排彩灯(8只)自动改变显示花样的控制系统,发光二极管可作为彩灯用。

控制器应有两种控制方式:(1)规则变化。

变化节拍有0.5秒和0.x秒两种,交替出现,每种节拍可有4种花样,各执行一或二个周期后轮换。

(2)随机变化。

无规律任意变化。

二、彩灯控制器的设计原理本次彩灯控制器的设计包含几个主要模块,一是彩灯显示和扬声器的时序控制部分,二是发光二极管的动态显示和数码管的动态显示,本次设计中,二者的显示同步变化;三是扬声器的控制部分。

流程图如下所示:图 1 彩灯控制器的设计流程图彩灯控制器的设计核心主要是分频器的使用,显示部分的设计较简易。

分频的方法有很多种,本次设计之采用了其中较简易的一种,通过计数器的分频,将控制器外接的频率分为几个我们预先设定的值。

当计数器达到预先设定的值,即产生一个上升沿,从而实现分频。

扬声器通过不同的频率控制发出不同的声音。

同样发光二极管和数码管的显示速度也由其中分出来的一种频率控制(控制显示频率在1~4 之间为宜)。

通过使能端的控制可以控制不同的数码管显示预先设定的图案,数码管依次显示的图案为 AA、BB、CC,并随着发光二极管同步动态显示。

AA 为自左向右显示,BB 为自右向左显示,CC 从二边向中间再由中间向二边发散显示。

与此同时,显示不同的花型时扬声器发出不同的声音,代表不同的花型。

本次设计还带有复位功能,通过复位可以使彩灯控制器恢复到最初的状态。

三、程序设计和分析library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;建立设计库和标准程序包实体部分: entity pan isport(clk:in std_logic;clr:in std_logic;speak:out std_logic;led7s1:out std_logic_vector(6 downto 0);led7s2:out std_logic_vector(7 downto 0);led_selout:out std_logic_vector(7 downto 0);end entity;实体名为 pan,定义端口,输入端口为 clk 和 clr ,其中 clk 接脉冲信号,clr 接复位端;输出端口 speak 接扬声器,led7s1 接数码管的七段显示部分,led7s 接八个发光二极管,led_selout 接八个数码管的使能端,控制数码管的循环显示。

彩灯控制器课程设计eda

彩灯控制器课程设计eda一、课程目标知识目标:1. 让学生理解彩灯控制器的基本原理和EDA(电子设计自动化)软件的使用;2. 掌握彩灯控制器的电路设计、PCB布线及元件布局;3. 了解彩灯控制器的程序编写及调试方法。

技能目标:1. 培养学生运用EDA软件进行电路设计和PCB布线的能力;2. 培养学生编写彩灯控制程序,进行调试和优化的技能;3. 提高学生团队协作和解决问题的能力。

情感态度价值观目标:1. 培养学生对电子技术的兴趣和热情,激发创新意识;2. 培养学生严谨、细心的学习态度,养成良好的操作习惯;3. 增强学生的环保意识,关注电子产品对环境的影响。

课程性质:本课程属于电子技术实践课程,结合理论教学,注重培养学生的动手能力和实际操作技能。

学生特点:学生具备一定的电子技术基础知识,对实践操作有较高的兴趣,喜欢探索和挑战。

教学要求:教师需结合学生特点,采用循序渐进的教学方法,注重理论与实践相结合,提高学生的综合能力。

在教学过程中,关注学生的学习进度和需求,及时调整教学策略。

1. 彩灯控制器原理讲解:包括彩灯控制器的功能、工作原理及主要元件介绍,对应教材第3章;2. EDA软件操作:学习EDA软件的基本操作,如原理图绘制、PCB布线等,对应教材第4章;3. 彩灯控制器电路设计:根据原理图绘制PCB图,并进行元件布局,对应教材第5章;4. 彩灯控制程序编写:学习编写控制程序,实现彩灯的亮灭、闪烁等功能,对应教材第6章;5. 程序调试与优化:对编写好的程序进行调试,找出问题并进行优化,对应教材第7章;6. 实践操作:分组进行彩灯控制器的设计与制作,巩固所学知识,提高实际操作能力。

教学进度安排:第1周:彩灯控制器原理讲解;第2周:EDA软件操作学习;第3-4周:彩灯控制器电路设计;第5周:彩灯控制程序编写;第6周:程序调试与优化;第7周:实践操作。

教学内容确保科学性和系统性,结合教材章节进行有序安排,使学生能够逐步掌握彩灯控制器的设计与制作。

EDA课程设计报告彩灯控制器

1设计目的熟练掌握EDA技术利用计算机方面的课程解决专业课程方面点具体问题,达到解决问题,完成课程设计任务,培养实践的目的。

2设计要求和任务利用所学的EDA设计方法设计彩灯控制器,熟练使用使用QUARTUSII应用软件,进一步学习使用VHDL语言、原理图等EDA设计方法进行综合题目的方法。

功能要求:1.要有多种花型变化(至少4种).2.多种花型可以自动变换,循环往复.3.彩灯变换的快慢节拍可以选择.4.具有清零开关.3 总体设计思路及原理描述3.1功能描述在电路中以1 代表灯亮,以0 代表灯灭,由0,1按不同的规律组合代表不同的灯光图案,同时使其选择不同的频率,从而实现多种图案多种频率的花样功能显示。

在该电路中只需简单的修改程序就可以灵活地调整彩灯图案和变化方式。

下面就以一个十六路彩灯控制系统的实现为例进行简单说明。

此十六路彩灯控制系统设定有六种花样变化,这六种花样可以进行自动切换,并且每种花样可以选择不同的频率。

3.2设计原理用VHDL进行设计,首先应该了解,VHDL语言一种全方位硬件描述语言,包括系统行为级,寄存传输级和逻辑门级多个设计层次。

应充分利用DL “自顶向下”的设计优点以及层次化的设计概层次概念对于设计复杂的数字系统是非常有用它使得人们可以从简单的单元入手,逐渐构成庞大而复杂的系统。

首先应进行系统模块的划分,规定每一模块的功能以及各个模块之间的接口。

最终设计方案为:以一个十六路彩灯花样控制器、一个四频率输出分频器,一个四选一控制器和一个时间选择器总共四部分来完成设计。

四选一控制器从分频器选择不同频率的时钟信号输送到彩灯花样控制器,从而达到控制彩灯闪烁速度的快慢,时间选择器控制每种速度维持的时间长短。

整个十六路彩灯控制系统设计的模块图如图1所示图一4分层次方案设计及代码描述4.1子模块及其功能本次设计分为四个子模块,即十六路彩灯花样控制器、四频率输出分频器,四选一控制器和时间选择器,其子模块及其功能如下:4.1.1四频率输出分频器在本次设计中,设计了六种花样,要求这六种花样以不同的频率显示,而只有一个输入的时钟信号,所以对所输入的时钟信号进行2 分频,4 分频,8分频,16分频,得到四种频率信号,CLKDIV模块用来完成此功能。

彩灯控制器eda课程设计

彩灯控制器eda课程设计1000字此篇文章的主题为“彩灯控制器EDA课程设计”,下面将会从以下几个方面展开:1. 课程设计背景和目的2. 设计原理和方法3. 系统需求和规格4. 系统模块设计5. 系统实现和调试6. 课程设计总结和展望一、课程设计背景和目的彩灯控制器是一种用来控制色彩变换、亮度调节等的电子设备。

这种设备在日常生活中应用非常广泛,例如照明、广告牌等方面。

本次课程设计的目的是通过设计彩灯控制器,让学生深入了解EDA工具之间的协同效应并学习如何利用EDA工具实现完整的电子产品设计流程。

二、设计原理和方法彩灯控制器设计的原理比较简单,基本原理为利用单片机作为控制中心来控制不同灯泡的闪烁和色彩变换。

由于本次课程设计主要采用EDA工具进行设计开发,因此我们将采用如下方法实现:1. 采用verilog HLD (硬件描述语言)对彩灯控制器进行建模;2. 通过EDA软件(例如Vivado、ISE、Quartus等)进行模拟、综合和实现;3. 最后通过FPGA板搭建完整的系统并进行测试。

三、系统需求和规格1. 总体需求彩灯控制器主要功能为控制颜色变换、亮度等,并支持手持控制和远程控制两种方式。

系统需要满足以下要求:a) 彩灯控制器能够控制不同灯泡的颜色变换、亮度等;b) 支持手持遥控器和网络控制;c) 能够实现灯光的渐变和闪烁,且过渡效果自然;d) 有良好的灵活性和可扩展性。

2. 系统规格在确定系统规格时,除了要满足客户需求,还应考虑实际电子产品的性能要求,下面是我们对彩灯控制器的一些基本规格:a) 支持8组不同灯泡的控制;b) 支持颜色变换、亮度调节,且支持渐变和闪烁模式;c) 支持手持遥控器和网络控制,且手持遥控器能够进行10米内的控制;d) 有RBG三种控制灯泡的颜色变换,且变化频率在1-10Hz之间;e) 支持亮度调节,且亮度范围在0-100可调;f) 具有良好的电磁兼容性和稳定性。

四、系统模块设计根据我们的设计原理和系统需求和规格,我们可以将整个彩灯控制器的系统分为如下几个模块:1. 控制模块:主要是由单片机实现,能够接收遥控器和网络信号,并控制其他模块的工作;2. 灯光控制模块:包括RGB灯泡控制器、PWM调节器、芯片等,实现对灯泡的控制和亮度调节等功能;3. 消息传输模块:包括RS232、Wi-Fi、蓝牙等,实现遥控器和网络控制的功能。

EDA课程设计一个彩灯控制器

测试结果分析与改进

测试结果:系统集成与功能测试的结果 问题分析:分析测试结果中存在的问题和原因 改进方案:提出针对问题的改进方案 验证与优化:验证改进方案的有效性,并进行优化

06 总结与展望

课程设计总结

课程设计目标:掌握EDA技术,设计彩灯控制器 课程设计内容:包括电路设计、程序编写、仿真测试等 课程设计成果:成功设计并实现彩灯控制器 课程设计收获:提高了EDA技术应用能力,增强了团队合作精神

软件集成:将各个软件模块集成在一 起,形成完整的系统

功能测试:对系统的各个功能进行测 试,确保其正常工作

性能测试:对系统的性能进行测试, 确保其满足设计要求

稳定性测试:对系统的稳定性进行测 试,确保其长时间稳定工作

兼容性测试:对系统的兼容性进行测 试,确保其与其他设备或系统兼容

功能测试方案与实施

测试目标:验证系统功能是否符合设计要求 测试方法:黑盒测试、白盒测试、灰盒测试 测试内容:输入输出、数据处理、界面显示、系统稳定性等 测试工具:自动化测试工具、性能测试工具、安全测试工具等 测试结果分析:对测试结果进行分析,找出问题并提出改进措施 测试报告:编写测试报告,记录测试过程、结果和改进措施

布线原则:遵循信号流向,避免交叉干扰,保证信号完整性

布线技巧:使用自动布线工具,提高布线效率和质量

布线注意事项:注意电源线和地线的布局,保证电源和地线之间的隔离距离,避免电 磁干扰。

电源与接口电路设计

电源电路:提供 稳定的电源电压, 保证系统正常工 作

接口电路:连接 外部设备,实现 数据传输和控制

彩灯控制器应用前景与展望

彩灯控制器在节日装饰中的应用 彩灯控制器在商业广告中的应用 彩灯控制器在公共设施中的应用 彩灯控制器在智能家居中的应用

eda课程设计彩灯控制器

eda课程设计彩灯控制器eda课程设计彩灯控制器沈阳理工大学EDA技术课程设计报告1设计目的熟练掌握EDA技术利用计算机方面的课程解决专业课程方面点具体问题,达到解决问题,完成课程设计任务,培养实践的目的。

2设计要求和任务利用所学的EDA设计方法设计彩灯控制器,熟练使用使用QUARTUSII应用软件,进一步学习使用VHDL语言、原理图等EDA设计方法进行综合题目的方法。

功能要求: 1.要有多种花型变化(至少4种). 2.多种花型可以自动变换,循环往复. 3.彩灯变换的快慢节拍可以选择. 4.具有清零开关. 3 总体设计思路及原理描述 3.1功能描述在电路中以 1 代表灯亮,以0 代表灯灭,由0,1按不同的规律组合代表不同的灯光图案,同时使其选择不同的频率,从而实现多种图案多种频率的花样功能显示。

在该电路中只需简单的修改程序就可以灵活地调整彩灯图案和变化方式。

下面就以一个十六路彩灯控制系统的实现为例进行简单说明。

此十六路彩灯控制系统设定有六种花样变化,这六种花样可以进行自动切换,并且每种花样可以选择不同的频率。

3.2设计原理用VHDL进行设计,首先应该了解,VHDL语言一种全方位硬件描述语言,包括系统行为级,寄存传输级和逻辑门级多个设计层次。

应充分利用DL “自顶向下” 的设计优点以及层次化的设计概层次概念对于设计复杂的数字系统是非常有用它使得人们可以从简单的单元入手,逐渐构成庞大而复杂的系统。

首先应进行系统模块的划分,规定每一模块的功能以及各个模块之间的接口。

最终设计方案为:以一个十六路彩灯花样控制器、一个四频率输出分频器,一个四选一控制器和一个时间选择器总共四部分来完成设计。

四选一控制器从分频器选择不同频率的时钟信号输送到彩灯花样控制器,从而达到控制彩灯闪烁速度的快慢,时间选择器控制每种速度维持的时间长短。

整个十六路彩灯控制系统设计的模块图如图1所示图一4分层次方案设计及代码描述4.1子模块及其功能本次设计分为四个子模块,即十六路彩灯花样控制器、四频率输出分频器,四选一控制器和时间选择器,其子模块及其功能如下: 4.1.1四频率输出分频器在本次设计中,设计了六种花样,要求这六种花样以不同的频率显示,而只有一个输入的时钟信号,所以对所输入的时钟信号进行 2 分频,4 分频,8分频,16分频,得到四种频率信号,CLKDIV模块用来完成此功能。

EDA课程设计—彩灯控制器

燕山大学EDA课程设计报告书题目:彩灯控制器姓名:班级:成绩:一.设计要求具备两种彩灯花样显示,通过功能切换按钮选择花样。

花样一要求:1.有十只LED,L0……L92.显示方式(初态为全亮):①先奇数灯依次灭(灭的灯当下一个灯动作时,本灯回复原状态)②再偶数灯依次灭(同上)③再由L0到L9依次灭(同上)3.显示间隔0.5S,1S可调。

花样二要求:1.有八只LED,L0……L72.显示顺序如下表3.显示间隔为0.5S,1S可调。

二、设计过程及内容总体设计思路:彩灯控制器的总电路图主要由三大模块组成,分别是分频和选频模块、花样一模块和花样二模块。

1、分频和选频模块(1)、分频模块利用三个74160做成183进制的计数器,将732HZ的频率分成4HZ的频率,再在4HZ的基础上,利用T触发器,调节信号的占空比,得到2Hz 的Y信号。

电路图如下:仿真图:(2)、选频模块利用JK触发器上升沿触发将Y信号改变成1Hz的信号,再用M信号控制1Hz和2Hz信号的选择,即题目要求中实现时间间隔0.5s和1s可调。

控制端M为低电平时,输出2HZ的脉冲;控制端M为高电平时,输出1HZ 的脉冲。

电路图如下:仿真图:M为低电平时:M为高电平时:分频和选频模块合并后的电路图为:2、花样一模块花样一中有两大模块:计数模块和控制模块。

(1)、计数模块用一片76161制成11进制计数器,其中进位信号经过JK触发器得到占空比为1:2的C信号,作为控制模块的片选端输入,输出的QA、QB、QC、QD作为控制模块的输入。

电路图为:仿真图:(2)、控制模块用计数模块输出的C信号控制两片74154译码器轮流工作。

当C为低电平时,第一片译码器工作,实现十个彩灯的初态全亮、奇数灯依次灭和偶数灯依次灭;当C为高电平时,第二片译码器工作,实现十个彩灯的依次灭。

两片译码器的输出端用逻辑门与彩灯相连。

电路图如下:花样一模块的电路图为:仿真图为:3、花样二模块(1)、花样二中用两片74161制成一个33进制计数器,用来实现题目中33种状态的循环。

EDA循环彩灯控制课程设计

EDA循环彩灯控制课程设计一、课程目标知识目标:1. 学生能理解EDA技术的基本概念,掌握循环彩灯控制原理;2. 学生能掌握数字逻辑设计的基本方法,运用硬件描述语言进行简单程序设计;3. 学生了解循环彩灯在现实生活中的应用,理解其工作原理和设计方法。

技能目标:1. 学生能运用所学知识,独立完成循环彩灯控制电路的设计与仿真;2. 学生能通过实验操作,熟练使用相关仪器和设备,进行硬件电路搭建;3. 学生能够进行团队协作,共同解决在设计与实现过程中遇到的问题。

情感态度价值观目标:1. 学生对EDA技术产生兴趣,提高对电子工程领域的认识和热情;2. 学生培养良好的实验习惯,注重安全、环保,遵循实验操作规范;3. 学生在团队合作中,学会尊重他人,培养沟通能力和团队精神。

课程性质:本课程为电子设计自动化(EDA)相关课程,结合循环彩灯控制实例,使学生掌握数字逻辑设计的基本方法和技能。

学生特点:学生具备一定的电子基础知识,对硬件描述语言和数字电路有一定了解,但实际操作能力有待提高。

教学要求:结合理论教学与实验操作,注重培养学生的实际动手能力,提高学生的创新意识和团队合作能力。

通过本课程的学习,使学生能够将所学知识应用于实际项目中,达到学以致用的目的。

二、教学内容1. 理论知识:- EDA技术概述:介绍EDA技术的基本概念、发展历程和应用领域;- 数字逻辑设计基础:回顾逻辑门、组合逻辑和时序逻辑基础知识;- 硬件描述语言:讲解Verilog HDL或VHDL的基本语法和使用方法;- 循环彩灯控制原理:分析循环彩灯的控制方法、电路设计和程序实现。

2. 实践操作:- 循环彩灯控制电路设计与仿真:指导学生使用EDA软件(如Multisim、Proteus等)进行电路设计与仿真;- 硬件电路搭建与调试:教授学生如何搭建循环彩灯控制电路,并进行调试;- 程序编写与下载:教授学生如何编写循环彩灯控制程序,并将程序下载至FPGA或CPLD器件。

EDA技术:实验10-彩灯控制器设计与实现

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY counter_32 IS

PORT

(

clk,rst

: IN

std_logic;

count_out

: OUT integer range 0 to 31 );

END counter_32;

ARCHITECTURE cd OF fenpinqi IS

begin

p1:process(clk,rst)

variable a:integer range 0 to 20;

begin

if rst='1' then

clk_4<='0';

----- 复位信号控制部分

else

when 24=>output<="00000001";sm<="0100110";

when 25=>output<="00000010";sm<="0100110";

when 26=>output<="00000100";sm<="0100110";

when 27=>output<="00001000";sm<="0100110";

when 28=>output<="00010000";sm<="0100110";

eda课程设计-彩灯控制器

1.设计目的学习EDA开发软件和MAX+plus Ⅱ的使用方法,熟悉可编程逻辑器件的使用,通过制作来了解彩灯控制系统。

2.设计题目描述和要求1)设计一个彩灯控制器,使彩灯(LED管)能连续发出四种以上不同的显示形式;2)随着彩灯显示图案的变化,发出不同的音响声。

3)扩充其它功能。

3.设计原理3.1 方案论证这次的彩灯设计采用的是分模块来完成的,包括分频器、计数器、选择器、彩灯控制器。

其中彩灯控制器是用来输出不同的花样,彩灯控制器的输出则是用一个32进制的计数器来控制,扬声器的输出时用不同的频率来控制,所以用了一个集成分频器来使输入的频率被分为几种不同的频率,不同频率的选择性的输出则是用一个4选一的选择器来控制。

基于上述的介绍本次的彩灯控制采用的模式6来进行显示。

图3-1-1 模式6结构图3.2 模块设计1)集成分频器模块设计要求显示不同的彩灯的时候要伴随不同的音乐,所以设计分频器来用不同的频率控制不同的音乐输出。

模块说明:Rst:输入信号复位信号用来复位集成分频器的输出使输出为“0”,及没有音乐输出。

Clk:输入信号模块的功能即为分频输入的频率信号。

Clk_4、clk_6、clk_8、clk_10:输出信号即为分频模块对输入信号clk的分频,分别为1/4分频输出、1/6分频输出、1/8分频输出、1/10分频输出。

图3-2-1 集成分频器2)32进制计数器模块32进制模块用来控制彩灯输出模块,即确定彩灯控制器的不同的输出。

Rst:输入信号复位信号用来复位32进制使其输出为“00000”。

Clk:输入信号用来给模块提供工作频率。

Count_out[4..0]:输出信号即为32进制计数器的输出。

图3-2-2 32进制计数器3)彩灯控制模块彩灯控制模块用来直接控制彩灯的输出,使彩灯表现出不同的花样。

Rst:输入信号使彩灯控制模块的输出为“00000000”,即让彩灯无输出。

Input[4..0]:输入信号不同的输入使彩灯控制模块有不同的输出即彩灯显示出不同的花样。

EDA课程设计多路彩灯控制器

课程设计语言题目:多路彩灯控制器班级:姓名:学号:指导教师:成绩:电子与信息工程学院信息与通信工程系目录目录 (I)摘要 (II)关键字 (II)1 引言 (1)1.1 课程设计的目的和意义 (1)1.2 课程设计内容及要求 (1)2 设计方案 (1)3 模块设计 (2)3.1 时序控制模块 (2)3.2 显示控制电路 (3)3.3 总体模块框图 (3)4 模块程序 (4)4.1 时序控制电路模块程序 (4)4.2 显示模块电路程序 (5)4.3 顶层模块设计程序 (6)5 仿真波形 (6)5.1 时序控制模块仿真波形 (6)5.2 显示模块仿真波形 (7)6 试验总结 (7)7 心得体会 (8)8 参考文献 (8)III多路彩灯控制器摘要随着EDA技术发展和应用领域的扩大与深入,EDA技术在电子信息、通讯、自动控制及就算几应用等领域的重要性突出,随着技术市场与人才市场对EDA的需求不断提高,产品的市场需求和市场的要求也必然会反映到教学领域和科研领域中来,因此学好EDA技术对我们有很大的一处,EDA是指以计算机为工具,在EDA软件平台上,根据设计描述的源文件,自动完成系统的设计,包括编译、仿真、优化、综合、适配以及下载。

多路彩灯控制器通过对应的开关按钮,能够控制多个彩灯的输出状态,组合多种变幻的灯光闪烁,它被广泛应用到节目庆典、剧场灯光,橱窗装饰中。

关键字:EDA;多路彩灯;VHDLII1 引言1.1 课程设计的目的和意义巩固所学的专业技术知识,培养学生综合运用所学知识与生产实践经验,分析和解决工程技术问题的能力,培养初步的独立设计能力;通过课程设计实践,了解并掌握一般的综合设计过程,训练并提高学生在理论计算、结构设计、工程绘图、查阅设计资料、运用标准与规范和应用计算机等方面的能力,更好地将理论与实践相结合,提高综合运用所学理论知识独立分析和解决问题的能力。

再设计完成后,还要将设计的电路进行安装、调试,加强我们的动手能力。

EDA多路彩灯控制器设计报告

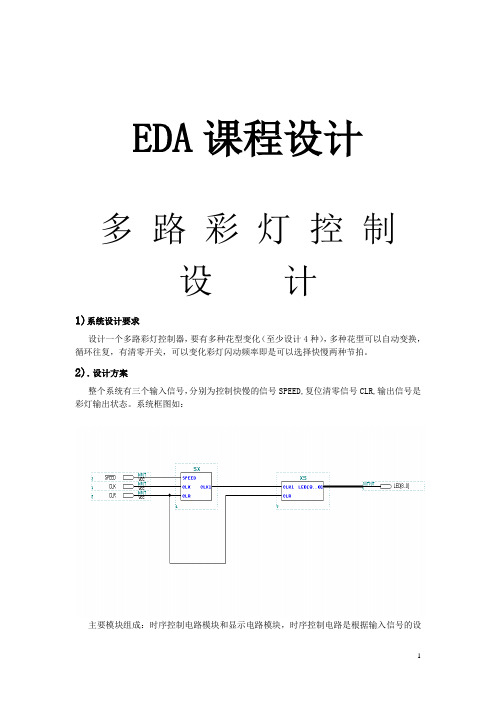

EDA课程设计多路彩灯控制设计1)系统设计要求设计一个多路彩灯控制器,要有多种花型变化(至少设计4种),多种花型可以自动变换,循环往复,有清零开关,可以变化彩灯闪动频率即是可以选择快慢两种节拍。

2).设计方案整个系统有三个输入信号,分别为控制快慢的信号SPEED,复位清零信号CLR,输出信号是彩灯输出状态。

系统框图如:主要模块组成:时序控制电路模块和显示电路模块,时序控制电路是根据输入信号的设置得到相应的输出信号,并将此信号作为显示电路的时钟信号;显示电路输入时钟信号的周期,有规律的输出设定的六种彩灯变化类型。

3).模块设计时序控制模块:CLK为输入时钟信号,电路在时钟上升沿变化;CLR为复位清零信号,高电平有效,一旦有效时,电路无条件的回到初始状态;SPEED为频率快慢选择信号,低电平节奏快,高电平节奏慢;CLK1为输出信号,CLR有效时输出为零,否则,随SPEED信号的变化而改变。

显示控制电路的模块框图如图所示,输入信号clk和clr的定义与时序控制电路一样,输入信号led[8...0]能够循环输出9路彩灯6种不同状态的花型。

对状态的所对应的彩灯输出花型定义如下:S0:000000000 S1:001001001 S2:010010010 S3:011011011 S4:100100100S5:101101101S 6:110110110多路彩灯在多种花型之间的转换可以通过状态机实现,当复位信号clr有效时,彩灯恢复初始状态s0,否则,每个时钟周期,状态都将向下一个状态发生改变,并对应输出的花型,这里的时钟周期即时时序控制电路模块产生的输出信号,它根据SPEED信号的不同取值得到两种快慢不同的时钟频率。

4).时序控制电路模块程序如下:LIBRARY IEEE;USE IEEE.std_logic_1164.ALL;USE IEEE.std_logic_unsigned.ALL;ENTITY SX ISPORT(SPEED:IN STD_LOGIC;CLK:IN STD_LOGIC;CLR:IN STD_LOGIC;CLK1:OUT STD_LOGIC);END SX;ARCHITECTURE ART OF SX ISSIGNAL CK:STD_LOGIC;BEGINPROCESS(CLK,CLR,SPEED)ISV ARIABLE TEMP:STD_LOGIC_VECTOR(2 DOWNTO 0);BEGINIF CLR='1' THENCK<='0';TEMP:="000";ELSIF(CLK'EVENT AND CLK='1')THENIF(SPEED='1')THENIF TEMP="001" THENTEMP:="000";CK<=NOT CK;ELSE TEMP:=TEMP+'1';END IF;ELSEIF TEMP="111" THENTEMP:="000";CK<=NOT CK;ELSETEMP:=TEMP+'1';END IF;END IF;END IF;END PROCESS;CLK1<=CK;END ART;5).显示模块电路程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY XS ISPORT(CLK1:IN STD_LOGIC;CLR:IN STD_LOGIC;LED:OUT STD_LOGIC_VECTOR(8 DOWNTO 0));END ENTITY XS;ARCHITECTURE ART OF XS ISTYPE STA TE IS(S0,S1,S2,S3,S4,S5,S6);SIGNAL CURRENT_STATE:STATE;SIGNAL LIGHT:STD_LOGIC_VECTOR(8 DOWNTO 0);BEGINPROCESS(CLR,CLK1)ISCONSTANT L0:STD_LOGIC_VECTOR(8 DOWNTO 0):="000000000";CONSTANT L1:STD_LOGIC_VECTOR(8 DOWNTO 0):="001001001";CONSTANT L2:STD_LOGIC_VECTOR(8 DOWNTO 0):="010010010";CONSTANT L3:STD_LOGIC_VECTOR(8 DOWNTO 0):="011011011";CONSTANT L4:STD_LOGIC_VECTOR(8 DOWNTO 0):="100100100"; CONSTANT L5:STD_LOGIC_VECTOR(8 DOWNTO 0):="101101101"; CONSTANT L6:STD_LOGIC_VECTOR(8 DOWNTO 0):="110110110";BEGINIF CLR='1' THENCURRENT_STATE<=S0;LIGHT<=L0;ELSIF(CLK1'EVENT AND CLK1='1')THENCASE CURRENT_STATE ISWHEN S0=> LIGHT<="ZZZZZZZZZ"; CURRENT_STA TE<=S1;WHEN S1=> LIGHT<=L1; CURRENT_STATE<=S2;WHEN S2=> LIGHT<=L2; CURRENT_STATE<=S3;WHEN S3=> LIGHT<=L3; CURRENT_STATE<=S4;WHEN S4=> LIGHT<=L4; CURRENT_STATE<=S5;WHEN S5=> LIGHT<=L5; CURRENT_STATE<=S6;WHEN S6=> LIGHT<=L6; CURRENT_STATE<=S1;END CASE;END IF;END PROCESS;LED<=LIGHT;END ART;6).时序控制模块仿真波形:从图中可以看出,当复位信号为高电平时,电路时钟输出清零,当快慢信号SPEED为低电平时,时序控制电路四分频起作用,当快慢信号SPEED为高电平时,时序控制电路八分频起作用,仿真结果符合电路要求。

彩灯控制器eda课程设计

目录1.引言 (3)2. EDA技术 (5)2.1 EDA技术介绍 (5)2.2硬件描述语言 (5)3 Quartus II介绍 (8)3.1 Quartus II软件介绍 (8)3.2 Quartus II软件界面介绍 (9)3.2.1 代码输入界面 (9)3.2.2 编译界面 (9)3.2.3 波形仿真界面 (10)4 系统设计 (12)4.1 设计过程 (12)4.1.1 设计内容及要求 (12)4.1.2 输入与输出说明 (12)4.1.3 设计过程思路分析 (12)4.2 程序分析及仿真 (13)4.2.1花型控制电路模块 (13)4.2.2 显示电路模块 (14)4.2.3 发声电路模块 (17)4.3 程序仿真图 (17)5 下载 (19)5.1 芯片选定 (19)5.2引脚设定 (19)5.3 程序下载 (20)5.4 结果显示 (20)6 设计总结 (22)参考文献 (23)附录:源代码程序 (24)1.引言伴随着计算机、集成电路和电子设计技术的发展,当今社会是数字化的社会,也是数字集成电路广泛应用的社会,数字本身在不断的进行更新换代。

它由早起的电子管、晶体管、小中规模集成电路发展到超大规模集成电路以及许多具有特定功能的专用集成电路。

EDA技术在过去的几十年里取得了巨大的进步。

EDA技术使得设计者的工作仅限于利用软件的方式,即利用硬件描述语言和EDA软件便可完成对系统硬件功能的实现。

如今,EDA软件工具已经成为电子信息类产品的支柱产业。

从高性能的微处理器、数字信号处理器一直到彩电、音响和电子玩具电路等,EDA技术不单是应用于前期的计算机模拟仿真、产品调试,而且也在P 哪的制作、电子设备的研制与生产、电路板的焊接、朋比的制作过程等有重要作用。

可以说电子EDA技术已经成为电子工业领域不可缺少的技术支持。

相比传统的电路系统的设计方法,VHDL具有多层次描述系统硬件功能的能力,支持自顶向下(Top to Down)和基于库(LibraryBased)的设计的特点。

eda八路彩灯控制器课程设计

课程名称:EDA八路彩灯控制器设计课程目的:1. 了解EDA软件的基本操作和应用;2. 掌握数字电路设计的基本理论和方法;3. 熟悉FPGA设计流程;4. 学习彩灯控制器的设计原理和实现方法;5. 培养学生的团队合作能力和实际动手能力。

课程大纲:1. EDA软件的基本操作和应用1.1 EDA概念及发展历史1.2 常见的EDA软件及其特点1.3 EDA软件的安装和基本操作2. 数字电路设计基础2.1 逻辑门及其运算2.2 组合逻辑电路设计2.3 时序逻辑电路设计2.4 FPGA概念及应用3. 彩灯控制器设计原理与方法3.1 LED灯控制器的基本原理3.2 PWM调光原理及实现3.3 彩灯控制器的电路设计与原理图绘制3.4 彩灯控制器的FPGA设计与仿真4. 课程实践4.1 彩灯控制器实验板的制作4.2 EDA软件仿真实验4.3 彩灯控制器的硬件调试与验证4.4 彩灯控制器的功能实现与效果展示课程评价:本课程通过结合理论学习和实践操作相结合的教学方式,让学生全面掌握EDA软件的使用方法,深入理解数字电路的设计原理,以及彩灯控制器的具体实现方法。

通过实践环节,培养学生的动手能力和团队合作精神,使学生在课程中获得知识的能够运用所学知识解决实际问题。

通过该课程的学习,学生将掌握FPGA设计流程,了解数字电路设计的基础知识,并具备彩灯控制器设计和制作的能力。

结语:EDA八路彩灯控制器设计课程旨在培养学生的实际操作技能,通过设计和制作彩灯控制器,让学生在实践中巩固所学的EDA软件操作和数字电路设计知识,同时培养学生的团队合作和解决问题的能力。

希望学生能够在课程中认真学习,勇于实践,在实验中不断探索和创新,不断提高自己的实际动手能力和工程实践能力。

在接下来的1500字内容中,我们将进一步细化课程设计的细节,包括每个主题下的具体教学内容、示例和案例分析等部分。

3. 彩灯控制器设计原理与方法3.1 LED灯控制器的基本原理LED(Light Emitting Diode)是一种半导体器件,是一种能将电能转化为光能的二极管。

EDA多路彩灯控制器设计

EDA多路彩灯控制设计一.系统设计要求设计一个多路彩灯控制器,彩灯能循环变化,可清零,可以变化彩灯闪动频率。

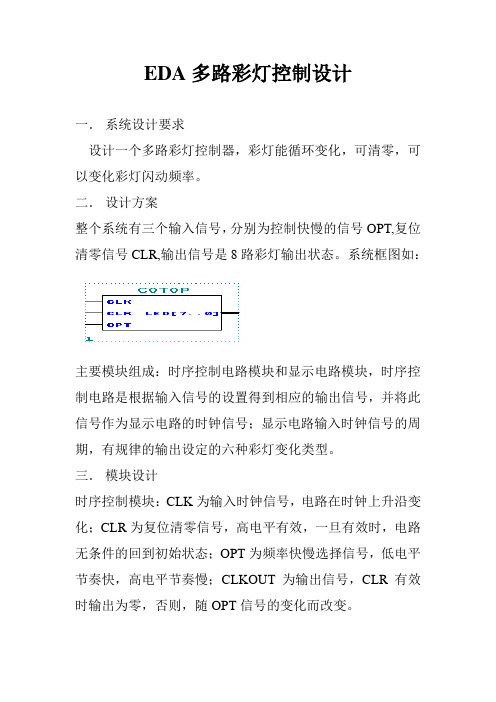

二.设计方案整个系统有三个输入信号,分别为控制快慢的信号OPT,复位清零信号CLR,输出信号是8路彩灯输出状态。

系统框图如:主要模块组成:时序控制电路模块和显示电路模块,时序控制电路是根据输入信号的设置得到相应的输出信号,并将此信号作为显示电路的时钟信号;显示电路输入时钟信号的周期,有规律的输出设定的六种彩灯变化类型。

三.模块设计时序控制模块:CLK为输入时钟信号,电路在时钟上升沿变化;CLR为复位清零信号,高电平有效,一旦有效时,电路无条件的回到初始状态;OPT为频率快慢选择信号,低电平节奏快,高电平节奏慢;CLKOUT为输出信号,CLR有效时输出为零,否则,随OPT信号的变化而改变。

时序控制电路模块程序如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity kz is --定义实体port(clk: in std_logic; --时钟信号clr: in std_logic; --复位信号opt: in std_logic; --快慢控制信号clkout: out std_logic --输出时钟信号);end kz;architecture rtl of kz issignal clk_tmp: std_logic;signal counter: std_logic_vector(1 downto 0); --定义计数器beginprocess(clk,clr,opt)beginif clr='1' then --清零clk_tmp<='0';counter<="00";elsif clk'event and clk='1' thenif opt='0' then --四分频,快节奏if counter="01" thencounter<="00";clk_tmp<=not clk_tmp;elsecounter<=counter+'1';end if;else --八分频,慢节奏if counter="11" thencounter<="00";clk_tmp<=not clk_tmp;elsecounter<=counter+'1';end if;end if;end if;end process;clkout<=clk_tmp; --输出分频后的信号end rtl;显示模块电路程序如下:library ieee;use ieee.std_logic_1164.all;entity xs isport(clk: in std_logic ;--输入时钟信号clr: in std_logic; --复位信号led: out std_logic_vector(7 downto 0)); --彩灯输出end xs;architecture rtl of xs istype states is --状态机状态列举(s0,s1,s2,s3,s4,s5,s6);signal state: states;beginprocess(clk,clr)beginif clr='1' thenstate<=s0;led<="00000000";elsif clk'event and clk='1' then --状态机状态之间的转换case state iswhen s0=>state<=s1;when s1=>state<=s2;led<="01010101";when s2=>state<=s3;led<="10101010";when s3=>state<=s4;led<="10001000";when s4=>state<=s5;led<="11001100";when s5=>state<=s6;led<="00110011";when s6=>state<=s1;led<="00010001";end case;end if;end process;end rtl;顶出模块设计程序:library ieee;use ieee.std_logic_1164.all;entity cotop isport (clk: in std_logic;clr: in std_logic;opt:in std_logic;led: out std_logic_vector(7 downto 0)); --八路彩灯输出end cotop;architecture rtl of cotop iscomponent kz is --定义元件:时序控制电路port(clk: in std_logic;clr: in std_logic;opt:in std_logic;clkout: out std_logic);end component kz;component xs is --定义元件:显示电路port(clk: in std_logic;clr: in std_logic;led: out std_logic_vector(7 downto 0));end component xs;signal clk_tmp: std_logic;beginu1:kz port map(clk,clr,opt,clk_tmp); --例化时序控制模块u2:xs port map(clk_tmp,clr,led); --例化显示电路模块end rtl;时序控制模块仿真波形:从图中可以看出,当复位信号为高电平时,电路时钟输出清零,当快慢信号OPT为低电平时,时序控制电路四分频起作用,当快慢信号OPT为高电平时,时序控制电路八分频起作用,仿真结果符合电路要求。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

EDA课程设计总结报告题目彩灯控制器学院 XXXXXXXXXXXXX学院专业 XXXXXXXXXX年级 XXXX级学号 XXXXXXXXXXXXXXXXXXXX姓名 XXX XXX指导教师 XXX成绩XXXX年 X月 XX日目录摘要 (2)Abstract (4)第一章绪论 (5)1.1 课题背景 (5)1.2 项目的实际研究意义 (7)第二章彩灯控制的要求及程序设计 (8)2.1 课程设计要求 (8)2.2设计思路 (8)2.3彩灯控制的软件程序设计 (8)第三章硬件焊接及彩灯调试 (12)3.1 焊接成品 (12)3.2 彩灯调试效果查看 (12)第四章波形仿真调试 (13)第五章感谢信 (14)参考文献 (15)摘要本课程设计提出基于FPGA的彩灯控制器的设计与分析。

本设计运用运用Verilog HDL语言在QuartusⅡ软件上进行了实验程序的编译和波形的仿真,具有代码简单易懂,功能易实现的特点,通过不断地调试和代码的多次完善,最终实现完整的多种花样彩灯控制器,达到了自主设计逻辑电路的水平。

关键词:彩灯控制;Verilog HDL语言;QuartusⅡ软件AbstractThe design and analysis of color lamp controller based on FPGA are presented in this course. This design using using Verilog HDL language in Quartus Ⅱsoftware has carried on the experimental program compilation and waveform simulation, has the code simple, function characteristics of easy implementation, through debugging and code many times the consummation unceasingly, finally realizes the complete variety lights controller, reached the independent design of logic circuit level.Keywords: The lantern controller;Verilog HDL language; Quartus Ⅱsoftware第一章绪论1.1课题背景1. FPGAFPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个新概念,内部包括可配置逻辑模块CLB(Configurable Logic Block)、输出输入模块IOB(Input Output Block)和内部连线(Interconnect)三个部分。

FPGA的基本特点主要有:1)采用FPGA设计ASIC电路,用户不需要投片生产,就能得到合用的芯片。

2)FPGA可做其它全定制或半定制ASIC电路的中试样片。

3)FPGA内部有丰富的触发器和I/O引脚。

4)FPGA是ASIC电路中设计周期最短、开发费用最低、风险最小的器件之一。

5)FPGA采用高速CHMOS工艺,功耗低,可以与CMOS、TTL电平兼容。

可以说,FPGA芯片是小批量系统提高系统集成度、可靠性的最佳选择之一。

2. EDA当今社会是数字化的社会,也是数字集成电路广泛应用的社会,数字本身在不断的进行更新换代。

它由早起的电子管、晶体管、小中规模集成电路发展到超大规模集成电路以及许多具有特定功能的专用集成电路。

而EDA技术就是以微电子技术为物理层面,现代电子设计为灵魂,计算机软件技术为手段,最终形成集成电子系统或专用集成电路ASIC为目的的一门新兴技术。

EDA是电子设计自动化(Electronic Design Automation)的缩写,在20世纪60年代中期从计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CAT)和计算机辅助工程(CAE)的概念发展而来的。

它以计算机为工具,设计者在EDA软件平台上,用硬件描述语言VHDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

EDA技术的出现,极大地提高了电路设计的效率和可操作性,减轻了设计者的劳动强度。

EDA技术(即Electronic Design Automation技术)就是依赖强大的计算机,在EDA工具软件平台上,对以硬件描述语言HDL(Hardware Description Language)为系统逻辑描述手段完成的设计文件,自动的完成逻辑编译、化简、分割、综合、布局布线以及逻辑优化和仿真测试,直至实现既定的电子线路系统功能。

他在硬件实现方面融合了大规模集成电路制造技术、IC版图设计、ASIC测试和封装、FPGA(Field Programme Gate Array)CPLD(Complex Programme Logic Device)编程下载和自动测试等技术:在计算机辅助工程方面融合了计算机辅助设计(CAD),计算机辅助制造(CAM),计算机辅助测试(CAT),计算机辅助工程(CAE)技术以及多种计算机语言的设计概念;而在现代电子学方面则容纳了更多的内容,如电子线路设计理论、数字信号处理技术、数字系统建模和优化技术及长线技术理论等。

硬件描述语言HDL是EDA技术的重要组成部分,常见的HDL主要有VHDL、Verilog HDL、ABEL、AHDL、System Verilog和System C。

其中VHDL、Verilog HDL和现在的EDA设计中使用最多,并且我们学习的是Verilog的编程方法及实用技术。

3.Verilog HDLVerilog HDL是一种硬件描述语言(HDL:Hardware Discription Language),是一种以文本形式来描述数字系统硬件的结构和行为的语言。

Verilog HDL就是在用途最广泛的C 语言的基础上发展起来的一种件描述语言,它是由GDA(Gateway Design Automation)公司的PhilMoorby在1983年末首创的,最初只设计了一个仿真与验证工具,之后又陆续开发了相关的故障模拟与时序分析工具。

1985年Moorby推出它的第三个商用仿真器Verilog-XL,获得了巨大的成功,从而使得Verilog HDL迅速得到推广应用。

1989年CADENCE公司收购了GDA公司,使得VerilogHDL成为了该公司的独家专利。

1990年CADENCE公司公开发表了Verilog HDL,并成立LVI组织以促进Verilog HDL成为IEEE标准,即IEEE Standard 1364-1995。

用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。

Verilog HDL的最大特点就是易学易用,如果有C语言的编程经验,可以在一个较短的时间内很快的学习和掌握,因而可以把Verilog HDL内容安排在与ASIC设计等相关课程内部进行讲授,由于HDL语言本身是专门面向硬件与系统设计的,这样的安排可以使学习者同时获得设计实际电路的经验。

与之相比,VHDL的学习要困难一些。

但Verilog HDL 较自由的语法,也容易造成初学者犯一些错误,这一点要注意。

下面列出的是Verilog 硬件描述语言的主要能力:(1)基本逻辑门,例如and 、or 和nand 等都内置在语言中。

(2)用户定义原语(UDP )创建的灵活性。

用户定义的原语既可以是组合逻辑原语,也可以是时序逻辑原语。

(3)开关级基本结构模型,例如pmos 和nmos 等也被内置在语言中。

(4)提供显式语言结构指定设计中的端口到端口的时延及路径时延和设计的时序检查。

(5)可采用三种不同方式或混合方式对设计建模。

这些方式包括:行为描述方式—使用过程化结构建模;数据流方式—使用连续赋值语句方式建模;结构化方式—使用门和模块实例语句描述建模。

Verilog HDL 中有两类数据类型:线网数据类型和寄存器数据类型。

线网类型表示构件间的物理连线,而寄存器类型表示抽象的数据存储元件。

能够描述层次设计,可使用模块实例结构描述任何层次。

设计的规模可以是任意的;语言不对设计的规模(大小)施加任何限制。

Verilog HDL 不再是某些公司的专有语言而是IEEE 标准。

人和机器都可阅读Verilog 语言,因此它可作为EDA 的工具和设计者之间的交互语言。

Verilog HDL 语言的描述能力能够通过使用编程语言接口(PLI )机制进一步扩展。

PLI 是允许外部函数访问Verilog 模块内信息、允许设计者与模拟器交互的例程集合。

设计能够在多个层次上加以描述,从开关级、门级、寄存器传送级(RTL )到算法级,包括进程和队列级。

能够使用内置开关级原语在开关级对设计完整建模。

同一语言可用于生成模拟激励和指定测试的验证约束条件,例如输入值的指定。

Verilog HDL 能够监控模拟验证的执行,即模拟验证执行过程中设计的值能够被监控和显示。

这些值也能够用于与期望值比较,在不匹配的情况下,打印报告消息。

在行为级描述中,Verilog HDL 不仅能够在RTL 级上进行设计描述,而且能够在体系结构级描述及其算法级行为上进行设计描述。

能够使用门和模块实例化语句在结构级进行结构描述。

Verilog HDL 的混合方式建模能力,即在一个设计中每个模块均可以在不同设计层次上建模。

Verilog HDL 还具有内置逻辑函数,例如& (按位与)和| (按位或)。

对高级编程语言结构,例如条件语句、情况语句和循环语句,语言中都可以使用。

可以显式地对并发和定时进行建模。

提供强有力的文件读写能力。

语言在特定情况下是非确定性的,即在不同的模拟器上模型可以产生不同的结果;例如,事件队列上的事件顺序在标准中没有定义。

1.2 项目的实际研究意义在经济和商业高度发达的今天,彩灯已经成为人民日常生活不可或缺的一部分,已经逐渐为越来越多的人们所关注,在家庭中的普及率不断提高,大大的丰富和点缀了人民的生活。

彩灯由不同的颜色的LED灯组成,通过控制不同颜色的灯的亮与灭,呈现给人们不同的花塑和图案,极大的点缀了单调的都市夜景,让城市成为了多姿多彩的不夜城。

因此八路彩灯控制器的设计具有现实意义。

Verilog HDL是一种应用较为广泛的HDL语言,能对范围广泛的各种复杂的网络在不同的抽象级加以描述,而且在整个设计过程中可使用同一种语言。