芯片设计后端工程师面试试题

华为芯片后端面试

竭诚为您提供优质文档/双击可除华为芯片后端面试篇一:华为技术面试流程及常问问题面试后要友好,表明自己的真实一面。

华为技术面试流程一共5轮:首先资格考试和面试(相应职位的资深工程师主持);其次应聘职位的部门副经理面试再次应聘职位的部门副经理面试再次人事面最后是副总级的面试。

q1:请你分别划划osi的七层网络结构图,和tcp/ip 的五层结构图?q2:请你详细的解释一下ip协议的定义,在哪个层上面,主要有什么作用?tcp与udp呢?q3:请问交换机和路由器分别的实现原理是什么?分别在哪个层次上面实现的?q4:请问c++的类和c里面的struct有什么区别?q5:请讲一讲析构函数和虚函数的用法和作用?q6:全局变量和局部变量有什么区别实怎么实现的操作系统和编译器是怎么知道的?q7:一些寄存器的题目,主要是寻址和内存管理等一些知识。

q8:8086是多少位的系统在数据总线上是怎么实现的?资料来源:中国教育在线http:///篇二:我在华为面试的经历我在华为面试的经历本文是一个份20xx届华为软件研发工程师面经,也包括面试题,感兴趣的同学可以参考下。

在8月17日的上机以及性格测试之后,在22号进行了双选交流会,选择了下部门,我选的是电信软件,其实对其也不了解,看起范围比较广,就比较随意地选择了。

通知我26号下午3点面试,现在我已经面完坐在实验室吹空调了,就分享下我的面试经验吧。

由于中午12点抢了个小米4,就在那积极兜售,结果午睡就没时间了。

跟别人交易完之后,早早的就坐公交去了,2点多一点就到了华为南研所,在那等待着,目测大约有100多人在那等待,扫荡了一遍没发现认识的人,就在那傻傻地等着。

终于到了3点半,hR叫到我了,不一会就来了个面试官把我带走了。

一面(技术面):面试官是个30左右的男性,感觉比较和蔼。

在从等待教室到面试教室的路上,他问我哪个学校哪个专业的,我告诉他是东南计算机研究生+南邮信息与计算科学本科的情况后,他说那还是蛮对口的。

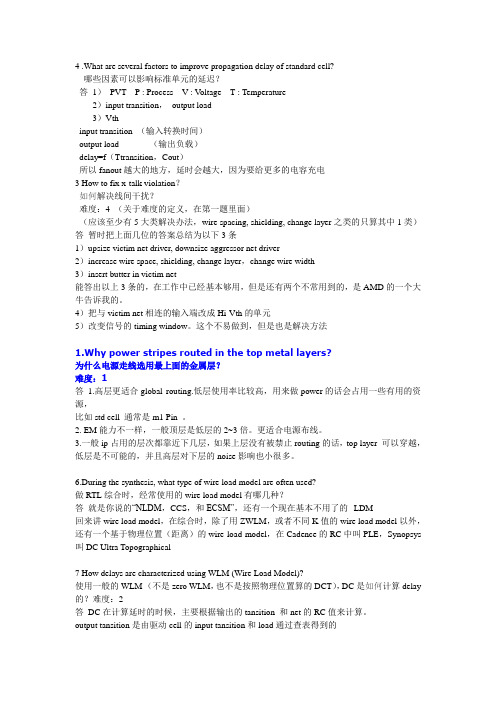

(完整版)ic后端面试题

4 .What are several factors to improve propagation delay of standard cell?哪些因素可以影响标准单元的延迟?答1)PVT P : Process V : V oltage T : Temperature2)input transition,output load3)Vthinput transition (输入转换时间)output load (输出负载)delay=f(Ttransition,Cout)所以fanout越大的地方,延时会越大,因为要给更多的电容充电3 How to fix x-talk violation?如何解决线间干扰?难度:4 (关于难度的定义,在第一题里面)(应该至少有5大类解决办法,wire spacing, shielding, change layer之类的只算其中1类)答暂时把上面几位的答案总结为以下3条1)upsize victim net driver, downsize aggressor net driver2)increase wire space, shielding, change layer,change wire width3)insert butter in victim net能答出以上3条的,在工作中已经基本够用,但是还有两个不常用到的,是AMD的一个大牛告诉我的。

4)把与victim net相连的输入端改成Hi-Vth的单元5)改变信号的timing window。

这个不易做到,但是也是解决方法1.Why power stripes routed in the top metal layers?为什么电源走线选用最上面的金属层?难度:1答1.高层更适合global routing.低层使用率比较高,用来做power的话会占用一些有用的资源,比如std cell 通常是m1 Pin 。

IC类面试题

IC类面试题IC类面试题一、基础知识部分1. 什么是集成电路(Integrated Circuit),它的优点和应用范围是什么?2. 请解释什么是半导体(Semiconductor),以及半导体材料的特点。

3. 请简要介绍一下半导体器件(如二极管、三极管)的结构、工作原理和应用。

4. 请解释什么是超大规模集成电路(VLSI),以及它的特点和应用范围。

5. 什么是数字集成电路(Digital Integrated Circuit)和模拟集成电路(Analog Integrated Circuit)?请列举它们各自的应用领域。

6. 请简要介绍一下有源器件(如场效应管、双极型晶体管)和无源器件(如电阻、电容、电感)的基本原理和应用。

二、设计能力部分1. 请设计一个简单的二极管整流电路,并解释它的工作原理和应用。

2. 如何设计一个简单的数字电路,将一个四位二进制数转换为十进制数?3. 请设计一个模拟滤波电路,用于去除输入信号中的高频噪声。

4. 如何设计一个集成电路,实现一个温度控制系统?请简要描述设计思路。

5. 请设计一个数字信号处理电路,能够实现输入数据的快速傅里叶变换。

6. 如何设计一个功率放大器电路,实现对输入信号的放大和输出?三、实践能力部分1. 请解释什么是电子设计自动化工具(Electronic Design Automation,简称EDA),并介绍一种常用的EDA工具。

2. 请介绍一种常用的半导体器件制造工艺,并谈谈其优缺点。

3. 请介绍一种常用的可编程逻辑器件(Programmable Logic Device,简称PLD),并解释它的工作原理和应用。

4. 请列举一些常见的集成电路封装形式,并解释它们的特点和应用场景。

5. 请介绍一种常用的模拟集成电路设计方法,以及一种常用的数字集成电路设计方法。

四、综合能力部分1. 在集成电路设计中,如何确定适当的工艺尺寸和电路结构,以实现设计要求?2. 在集成电路设计和制造中,如何解决功耗、发热和可靠性等问题?3. 在开发一个集成电路产品时,您认为最重要的是什么,为什么?4. 请谈谈您对未来集成电路技术发展的看法,以及您认为可能面临的挑战和机遇。

后端开发工程师常见面试题

后端开发工程师常见面试题在当今科技飞速发展的时代,后端开发工程师成为了众多企业争相抢夺的热门人才。

当你准备应聘后端开发工程师这一职位时,了解常见的面试题无疑是成功的关键之一。

以下是一些后端开发工程师常见的面试题,希望能对你有所帮助。

一、数据库相关1、请简要介绍一下数据库的事务以及其特性(ACID)。

事务是一组逻辑操作单元,被视为一个不可分割的工作序列。

ACID 分别代表原子性(Atomicity)、一致性(Consistency)、隔离性(Isolation)和持久性(Durability)。

原子性确保事务中的所有操作要么全部成功,要么全部失败;一致性保证事务执行前后数据库的完整性约束没有被破坏;隔离性使得多个并发事务之间相互隔离,互不干扰;持久性则保证事务一旦提交,其对数据库的更改就会永久保存。

2、解释一下数据库的索引以及它的作用和缺点。

索引是一种用于加速数据库查询的数据结构。

它的作用在于能够快速定位和检索数据,大大提高查询的效率。

然而,索引也有缺点,比如会增加数据插入、更新和删除的开销,因为这些操作不仅要修改数据,还要维护索引;此外,过多的索引会占用大量的存储空间。

3、讲述一下数据库的连接方式(内连接、外连接等)以及它们之间的区别。

内连接(INNER JOIN)返回两个表中满足连接条件的行。

左外连接(LEFT JOIN)返回左表中的所有行以及右表中与连接条件匹配的行,如果右表中没有匹配的行,则相应的列值为 NULL。

右外连接(RIGHT JOIN)与左外连接相反,返回右表中的所有行以及左表中与连接条件匹配的行。

全外连接(FULL JOIN)返回两个表中的所有行,如果某一行在另一个表中没有匹配的行,则相应的列值为 NULL。

二、编程语言相关1、以您熟悉的编程语言(如 Java、Python 等)为例,谈谈面向对象编程的三大特性(封装、继承、多态)。

封装是将数据和操作数据的方法封装在一个类中,隐藏内部实现细节,只提供公共的访问接口。

后台开发工程师岗位面试题及答案(经典版)

后台开发工程师岗位面试题及答案1.请介绍一下您的背景和在后台开发方面的经验。

答:我拥有计算机科学学士学位,并在过去五年里一直从事后台开发工作。

我曾在ABC公司开发过大型的数据管理系统,负责数据库设计、API开发以及性能优化等工作。

2.请描述一下RESTfulAPI的概念以及您在设计和实现中的经验。

答:RESTfulAPI是一种基于HTTP协议的架构风格,用于构建分布式系统。

我在以往的项目中,设计和实现了多个RESTfulAPI,确保了资源的正确映射、合适的HTTP方法使用,并采用版本控制来保持向后兼容性。

3.在数据库设计方面,您是如何考虑性能和扩展性的?答:在数据库设计中,我通常会选择合适的索引策略、范式化和反范式化的平衡。

此外,我会进行查询性能优化,如使用适当的JOIN、索引覆盖等,以减少查询时间。

为了实现扩展性,我会考虑分库分表、缓存策略以及使用分布式数据库。

4.请解释一下负载均衡的概念,以及您在项目中如何应用负载均衡技术。

答:负载均衡是一种分发网络流量以平衡服务器负载的技术。

我在以往的项目中,使用了负载均衡器如Nginx或AWSELB,将流量分发到多台服务器上,以确保高可用性和提高系统的性能。

5.请描述一下容器化技术(如Docker)的工作原理,以及您如何在项目中应用它。

答:容器化技术将应用及其依赖打包成一个独立的容器,具有一致性和可移植性。

我在以往的项目中,使用Docker创建容器,确保开发、测试和生产环境的一致性,同时利用DockerCompose 管理多个容器的协作。

6.您在保障数据安全方面有哪些经验?请举例说明。

答:我在数据安全方面,经常采取加密技术保护敏感数据,如使用TLS/SSL保护数据传输,使用加密算法存储敏感数据。

例如,在一个金融项目中,我使用了双因素认证、JWT令牌、IP白名单等方式来确保只有授权用户可以访问数据。

7.当系统遇到性能问题时,您会采取哪些措施来进行诊断和解决?答:首先,我会使用性能监测工具(如Prometheus)来定位瓶颈。

数字芯片面试题目(3篇)

第1篇一、基础概念题1. 请解释数字电路中的TTL和CMOS两种逻辑门的特点。

解析:TTL(Transistor-Transistor Logic)是一种双极型晶体管逻辑电路,具有速度快、功耗低、抗干扰能力强等优点。

CMOS(Complementary Metal-Oxide-Semiconductor)是一种金属氧化物半导体场效应晶体管逻辑电路,具有低功耗、高抗干扰能力、易于集成等优点。

2. 请解释数字电路中的时序、时序违例和建立时间、保持时间的关系。

解析:时序是指数字电路中信号传播、处理和响应的时间关系。

时序违例是指信号传播过程中出现的时间关系错误,如建立时间违例和保持时间违例。

建立时间是指输入信号稳定后,输出信号能够达到有效电平的时间;保持时间是指输出信号稳定后,输入信号保持有效电平的时间。

3. 请解释数字电路中的扫描链(Scan Chain)的作用。

解析:扫描链是一种用于测试数字电路内部逻辑的方法,可以将内部逻辑划分为多个模块,通过扫描链将这些模块连接起来,实现测试和调试。

二、电路设计题1. 请设计一个4位加法器,并给出其逻辑表达式。

解析:4位加法器可以采用串行进位或并行进位的方式设计。

以下是一个并行进位4位加法器的逻辑表达式:F = (A0 + B0)’ + (A0 + B0) (A1 + B1)’ + (A0 + B0) (A1 + B1) (A2 + B2)’ + (A0 + B0) (A1 + B1) (A2 + B2) (A3 + B3)2. 请设计一个3-8译码器,并给出其逻辑表达式。

解析:3-8译码器可以将3位二进制编码转换为8位输出。

以下是一个3-8译码器的逻辑表达式:F = A B C + A B C’ + A B C’ + A B C’ + A B C’ + A B C’ + A B C’ + A B C’三、时序设计题1. 请设计一个同步复位电路,并给出其逻辑表达式。

后端开发岗位招聘面试题与参考回答(某大型国企)2025年

2025年招聘后端开发岗位面试题与参考回答(某大型国企)面试问答题(总共10个问题)第一题假设你正在一家大型国企的后端开发团队中工作,你的团队最近接到了一个需求,需要在现有的系统中增加一个新的功能模块,用于处理用户的订单数据。

这个模块需要支持以下功能:1.用户可以查看自己的订单列表。

2.用户可以查看订单的详细信息。

3.用户可以更新订单的状态(例如,从“待处理”变为“已发货”)。

4.用户可以删除不再需要的订单。

请描述一下你会如何设计和实现这个功能模块,并说明你考虑的关键点。

参考答案及解析:设计思路:1.数据库设计:•创建一个新的订单表(orders),包含字段:订单ID、用户ID、订单状态、创建时间、更新时间等。

•确保订单表与现有的用户表(users)通过用户ID进行关联。

2.API设计:•设计RESTful API来支持上述功能。

•GET /orders:获取用户的订单列表。

•GET /orders/{orderId}:获取特定订单的详细信息。

•PUT /orders/{orderId}:更新订单状态。

•DELETE /orders/{orderId}:删除特定订单。

3.业务逻辑实现:•在订单服务(OrderService)中实现业务逻辑。

•创建订单时,将订单信息存入数据库,并关联用户信息。

•提供查询订单列表和详细信息的接口。

•实现更新订单状态的接口,确保订单状态的一致性。

•实现删除订单的接口,确保订单数据的完整性。

4.安全性考虑:•使用身份验证和授权机制(如JWT)来保护API端点。

•对用户的输入进行验证和过滤,防止SQL注入和XSS攻击。

5.性能优化:•使用缓存机制(如Redis)来提高查询性能。

•对数据库进行索引优化,确保高效的查询性能。

关键点:•数据库设计:确保数据的一致性和完整性。

•API设计:提供清晰、一致的接口,便于前端调用和维护。

•业务逻辑实现:确保业务逻辑的正确性和高效性。

•安全性:保护用户数据和系统安全。

集成电路设计岗位招聘面试题及回答建议(某大型集团公司)2025年

2025年招聘集成电路设计岗位面试题及回答建议(某大型集团公司)面试问答题(总共10个问题)第一题:请简述你对集成电路设计的理解以及你对该领域的兴趣所在。

你曾经遇到过哪些集成电路设计的挑战并是如何解决的?答案:我对集成电路设计有深入的理解,这是一个将多个电子元件集成在一块衬底上的技术过程,以实现特定的功能。

集成电路设计涉及到复杂的电路设计、模拟验证、布局布线以及后端制程等环节。

我对这个领域的兴趣源于其技术的前沿性和广泛的应用领域,如通信、计算机、消费电子等。

在我过去的项目中,我曾经遇到过集成电路设计的多种挑战。

例如,在设计低功耗的集成电路时,需要平衡功耗和性能的矛盾,这需要我深入研究电路的工作原理和功耗模型,通过优化算法和设计结构来实现低功耗设计。

另外,我还遇到过集成复杂功能的挑战,这需要我具备丰富的专业知识和团队协作经验,通过不断学习和实践,最终成功完成了设计任务。

解析:此题主要考察应聘者对集成电路设计的认知程度、兴趣点以及实际项目经验。

答案中需要体现出应聘者对集成电路设计的基本理解,包括其主要环节和技术要点。

同时,还需要展示应聘者在面对挑战时的应对策略和项目经验,以证明其具备解决实际问题的能力。

第二题假设你加入我们公司担任集成电路设计工程师,您认为在这个岗位上,最重要的技能和素质是什么?请结合你的经验或专业知识谈谈。

答案及解析:在集成电路设计岗位上,我认为最重要的技能和素质是深厚的电子工程、微电子学或相关领域的理论基础,同时需具备良好的问题解决能力、创新思维以及团队合作精神。

首先,扎实的理论基础是从事集成电路设计的前提。

这包括对半导体物理、电路原理、数字逻辑、模拟电路等核心知识的深入理解。

只有具备了这些基础知识,才能更好地理解和应对设计过程中遇到的各种问题。

其次,问题解决能力至关重要。

集成电路设计往往涉及到复杂的算法和优化问题,需要设计者能够迅速定位问题并提出有效的解决方案。

这要求设计者具备敏锐的洞察力和分析能力,能够从复杂的信息中提炼出关键点,并运用逻辑思维和创新方法找到最佳的设计方案。

数字后端工程师招聘面试题与参考回答(某大型国企)2025年

2025年招聘数字后端工程师面试题与参考回答(某大型国企)(答案在后面)面试问答题(总共10个问题)第一题题目:请详细解释一下你对RESTful API架构的理解,并描述一下如何在实际项目中应用RESTful API来提高系统的可维护性和扩展性。

第二题题目:请描述您在上一个项目中是如何优化系统的数据库性能的?请详细说明采取的具体措施及其效果。

第三题题目:请描述一次您在处理大型分布式系统时遇到的性能瓶颈问题,以及您如何进行分析和解决的。

第四题题目:请描述一下分布式系统中的CAP定理,并解释一下在实际工作中如何平衡C (一致性)、A(可用性)、P(分区容错性)三者之间的关系。

第五题题目:在设计一个高性能的数据库系统时,如何确保数据的一致性和高可用性?请结合CAP理论简要阐述您的设计方案。

第六题题目:请描述一下你对于微服务架构的理解,并举例说明你在过去的项目中是如何运用微服务架构来解决实际问题的。

第七题题目:请解释一下什么是数据库事务,并描述ACID特性。

第八题题目:假设你在工作中遇到了一个紧急的业务需求,需要在短时间内完成一个复杂的后端功能。

然而,你发现现有的技术栈难以在短期内满足需求。

此时,你将如何处理?第九题题目:某大型国企的数字化部门正在开发一个数据处理平台,该平台需要实现大量数据的实时处理与存储,同时保证系统的稳定性和高可用性。

以下是该平台的一些技术要求和功能模块,请根据这些要求,选择合适的技术方案,并说明理由。

1.数据存储:•若要存储千亿级的数据,需要保证读写速度,同时支持事务性。

2.实时数据处理:•数据需要实时存入系统,并对重要数据进行实时分析。

3.系统稳定性与高可用性:•该平台服务于多个部门,需要保证7*24小时运行不间断,并且能够快速恢复故障。

请根据以上要求,选择以下技术方案中的合适选项,并阐述理由:A. 采用Redis实现数据缓存,并结合MySQL进行数据存储;B. 使用MongoDB进行数据存储,并利用Elasticsearch进行全文检索;C. 采用Apache Kafka进行消息队列处理,以Kubernetes作为容器化解决方案,搭配HBase进行数据存储;D. 使用RabbitMQ作为消息队列,结合Cassandra进行数据存储,并使用Apache Zookeeper实现分布式协调。

后端开发工程师面试题及答案

后端开发工程师面试题及答案在当今数字化时代,后端开发工程师在构建高效、稳定和可扩展的Web 应用程序中发挥着至关重要的作用。

为了筛选出优秀的后端开发工程师,面试环节中的问题设计至关重要。

以下是一些常见的后端开发工程师面试题及答案:一、数据库相关1、什么是数据库索引?为什么要使用索引?答案:数据库索引是一种数据库结构,用于加快数据的检索和排序操作。

它类似于书籍的目录,可以帮助数据库快速定位到所需的数据,而不必扫描整个数据表。

使用索引的主要原因是提高查询性能,减少数据检索的时间。

2、解释一下数据库的事务及其特性(ACID)。

答案:事务是一个不可分割的工作单元,要么全部成功执行,要么全部回滚。

ACID 特性分别是:原子性(Atomicity),事务中的所有操作要么全部完成,要么全部不完成;一致性(Consistency),事务执行前后,数据库的完整性约束没有被破坏;隔离性(Isolation),多个事务并发执行时,它们之间相互隔离,互不干扰;持久性(Durability),一旦事务成功提交,其对数据库的更改是永久性的。

3、如何优化数据库查询性能?答案:可以通过创建合适的索引、避免全表扫描、优化 SQL 语句的结构、分表分库、合理使用存储过程等方式来优化数据库查询性能。

例如,在查询中尽量避免使用`LIKE '%value%'`这样的通配符在字符串开头,因为这通常无法使用索引。

二、编程语言相关(以 Python 为例)1、解释 Python 中的装饰器,并给出一个简单的示例。

答案:装饰器是 Python 中的一种高级特性,它可以在不修改被装饰函数源代码的情况下,为函数添加额外的功能。

例如:```pythondef my_decorator(func):def wrapper(args, kwargs):print("Before function execution")result = func(args, kwargs)print("After function execution")return resultreturn wrapper@my_decoratordef my_function():print("Inside the function")my_function()```2、谈谈 Python 的内存管理机制。

数字后端工程师招聘面试题与参考回答(某大型国企)

招聘数字后端工程师面试题与参考回答(某大型国企)面试问答题(总共10个问题)第一题答案:微服务架构是一种设计后端系统的架构风格,它将单一的后端应用程序开发为一组小型服务,每个服务都在自己的进程中运行,并与轻量级机制(通常是HTTP资源API)进行通信。

这些服务围绕业务功能构建,并且保持最低限度的集中式管理。

优势:1.业务模块独立:每个服务都是独立的,可以独立部署、扩展和升级,提高了系统的灵活性。

2.技术栈多样化:微服务允许使用不同的编程语言和技术栈来开发不同的服务,从而更好地匹配业务需求。

3.快速迭代:由于服务之间解耦,可以独立地对每个服务进行迭代和改进,加快了开发速度。

4.易于扩展:当某个服务负载过高时,可以单独对该服务进行水平扩展,而不影响其他服务。

5.故障隔离:服务之间的独立运行减少了系统整体故障的风险,一旦某个服务出现故障,只会影响该服务本身。

6.环境隔离:每个服务可以在不同的环境中运行(开发、测试、生产),避免了环境不一致导致的问题。

解析:微服务架构的后端开发优势体现在其模块化、独立性和灵活性上。

通过将应用程序拆分为多个小型、独立的服务,可以提高系统的可维护性和可扩展性。

在实际应用中,微服务架构有助于快速响应市场变化,降低技术债务,并提高开发效率。

当然,微服务架构也有其挑战,如服务间的通信复杂度增加、分布式事务管理等,但在适当的情况下,其优势是非常明显的。

第二题题目:请描述一下你在以往项目中遇到的一个技术难题,以及你是如何解决这个问题的。

答案:在我之前参与的一个云计算平台项目中,我们遇到了一个技术难题。

项目要求我们的平台能够支持大规模的并发访问,而在测试阶段,我们发现系统在高并发情况下响应速度明显下降,甚至出现了崩溃的情况。

解析:1.题目目的:此题旨在考察应聘者对实际问题的分析和解决能力,以及其在压力下的应对策略。

2.答案要点:•遇到的技术难题:描述一个具体的技术挑战,如系统性能瓶颈、技术选型不当等。

芯片工艺面试题目(3篇)

第1篇一、芯片工艺基础知识1. 简述半导体材料的基本性质,以及硅作为半导体材料的原因。

2. 解释晶体管的基本工作原理,并说明MOSFET和BJT的区别。

3. 简述集成电路制造过程中的光刻、蚀刻、离子注入等主要工艺。

4. 描述MOS晶体管的制造工艺流程,包括掺杂、光刻、蚀刻等步骤。

5. 解释芯片制造中的晶圆切割和晶圆加工技术。

二、芯片制造工艺6. 什么是CMOS工艺?简述其基本原理。

7. 什么是高介电常数(High-k)材料?它在芯片制造中的应用是什么?8. 解释栅极长度和栅极宽度的概念,并说明它们对晶体管性能的影响。

9. 什么是FinFET?与传统的MOSFET相比,它有哪些优势?10. 简述双极型晶体管(BJT)和MOSFET在制造过程中的差异。

三、芯片制造设备与材料11. 简述光刻机的工作原理,以及它对芯片制造的重要性。

12. 解释离子注入设备的原理,并说明其在芯片制造中的应用。

13. 描述刻蚀设备的基本类型和原理,以及它们在芯片制造中的作用。

14. 什么是化学气相沉积(CVD)?它在芯片制造中的应用有哪些?15. 解释溅射工艺的原理,并说明其在芯片制造中的应用。

四、芯片制造过程中的质量控制16. 简述芯片制造过程中的关键质量指标(KPI)。

17. 解释良率、成品率和缺陷率的概念,并说明它们之间的关系。

18. 描述芯片制造过程中的质量控制方法,如缺陷检测、缺陷分类和缺陷分析。

19. 解释芯片制造过程中的可靠性测试,如高温老化测试和高压测试。

20. 简述芯片制造过程中的安全规范,如ESD防护和化学品管理。

五、芯片制造工艺改进与创新21. 解释摩尔定律,并说明其对芯片制造工艺的影响。

22. 简述纳米技术对芯片制造工艺的挑战和机遇。

23. 描述芯片制造过程中的绿色工艺,如低功耗设计、低排放材料和可回收材料。

24. 解释芯片制造过程中的自动化和智能化趋势,如机器人、人工智能和机器学习。

25. 简述芯片制造过程中的新材料、新工艺和新设备的研究与开发。

数字IC后端笔试面试题库(附知识星球活动)

1. 简述数字IC设计流程2. 阐述下数字后端如何选择工艺节点(process node),如何选择metal stack(比如是选用1P7M还是1P8M)?3. 如何做好floorplan?大概阐述下做floorplan的步骤?如何qualify floorplan?4. 当design中memory特别多,多到已经无法全部摆放在boundary的周围,请问是否可以把memory摆放在core区域,为什么?这样做的利弊分别是什么?5. 如何规划powerplan?衡量powerplan好坏的指标有哪些?6. 影响标准单元延迟的因素有哪些?net delay是否可以为负值?为什么?如果可以为负值,请解释原因。

7. 请阐述placement这个步骤的作用,干什么的?placement这步包含哪些子步骤?8. 在placement阶段,针对时钟clock和reset等信号,是否需要额外特殊处理?为什么?9. placement后,如果发现timing violation比较大,应该如何debug?应该从哪些方面着手分析?10. placement阶段优化timing的方法,策略有哪些?11. 如何qualify一个placement结果?12. placement阶段是否需要设置clock uncertainty?如果需要,应该设多少值?13. 何为congestion?如果design中有比较严重的congestion,应该如何处理?14. 阐述下时钟树综合(clock tree synthesis)的作用?为何要做时钟树综合?15. 时钟树上clock inverter或者buffer的类型应该如何确定?是否可以用clock buffer来长tree?16. 要想让工具长好某段tree,应该告诉工具哪些要素?如何qualify一段clock tree?17. Clock tree latency 和clock skew哪个更重要?18. Clock tree太长有何坏处?clock skew较大有何利弊?19. cts之后clock skew是有哪些部分组成?cto后的clock skew值和cts 后的clock skew值有何不一样?20. 对于一个时钟结构比较复杂的设计,给你一个placement的constraint,你能否编写出时钟树约束文件(并非是指定clock inverter类型,max transition值等)?详述下你是如何分析设计的时钟结构的?21. cts后如何分析时钟树是否合理?22. 给定一个timing report,要求判断这条path是setup还是hold的timing report? 要求判断当前的report是什么阶段的report?分析该条path 是否有异常(比如某个delay值比较大等等)?23. 阐述下clock inter-balance是干什么用的?分析其存在的合理性。

IC设计模拟的经典的面试题及其答案

Latch up 最易产生在易受外部干扰的I/O电路处, 也偶尔发生在内部电路Latc h up是指cmo s晶片中,在电源p owerVDD和地线GND(VSS)之间由于寄生的PNP和NPN双极性BJT相互影响而产生的一低阻抗通路,它的存在会使VDD和GND之间产生大电流随着IC制造工艺的发展, 封装密度和集成度越来越高,产生L atchup的可能性会越来越大La tch u p 产生的过度电流量可能会使芯片产生永久性的破坏, Latc h up的防范是I C Lay out 的最重要措施之一Q1为一垂直式PNPBJT,基极(ba se)是n well,基极到集电极(co llect or)的增益可达数百倍;Q2是一侧面式的NPN B JT,基极为P su bstra te,到集电极的增益可达数十倍;Rwel l是nwe ll的寄生电阻;Rs ub是su bstra te电阻。

以上四元件构成可控硅(SC R)电路,当无外界干扰未引起触发时,两个BJT 处于截止状态,集电极电流是C-B的反向漏电流构成,电流增益非常小,此时La tch u p不会产生。

当其中一个BJT的集电极电流受外部干扰突然增加到一定值时,会反馈至另一个BJ T,从而使两个BJT因触发而导通,VDD至GND(VSS)间形成低抗通路,La tch u p由此而产生。

产生Latc h up的具体原因芯片一开始工作时VDD变化导致n well和P sub strat e间寄生电容中产生足够的电流,当VDD变化率大到一定地步,将会引起La tch u p。

当I/O的信号变化超出VDD-GND(V SS)的范围时,有大电流在芯片中产生,也会导致SC R的触发。

常见数字IC设计、FPGA工程师面试题

常见数字IC设计、FPGA⼯程师⾯试题1:什么是同步逻辑和异步逻辑?(汉王)同步逻辑是时钟之间有固定的因果关系。

异步逻辑是各时钟之间没有固定的因果关系。

答案应该与上⾯问题⼀致〔补充〕:同步时序逻辑电路的特点:各触发器的时钟端全部连接在⼀起,并接在系统时钟端,只有当时钟脉冲到来时,电路的状态才能改变。

改变后的状态将⼀直保持到下⼀个时钟脉冲的到来,此时⽆论外部输⼊ x 有⽆变化,状态表中的每个状态都是稳定的。

异步时序逻辑电路的特点:电路中除可以使⽤带时钟的触发器外,还可以使⽤不带时钟的触发器和延迟元件作为存储元件,电路中没有统⼀的时钟,电路状态的改变由外部输⼊的变化直接引起。

2:同步电路和异步电路的区别:同步电路:存储电路中所有触发器的时钟输⼊端都接同⼀个时钟脉冲源,因⽽所有触发器的状态的变化都与所加的时钟脉冲信号同步。

异步电路:电路没有统⼀的时钟,有些触发器的时钟输⼊端与时钟脉冲源相连,这有这些触发器的状态变化与时钟脉冲同步,⽽其他的触发器的状态变化不与时钟脉冲同步。

3:时序设计的实质:电路设计的难点在时序设计,时序设计的实质就是满⾜每⼀个触发器的建⽴/保持时间的⽽要求。

4:建⽴时间与保持时间的概念?建⽴时间:触发器在时钟上升沿到来之前,其数据输⼊端的数据必须保持不变的时间。

保持时间:触发器在时钟上升沿到来之后,其数据输⼊端的数据必须保持不变的时间。

不考虑时钟的skew,D2的建⽴时间不能⼤于(时钟周期T - D1数据最迟到达时间T1max+T2max);保持时间不能⼤于(D1数据最快到达时间T1min+T2min);否则D2的数据将进⼊亚稳态并向后级电路传播5:为什么触发器要满⾜建⽴时间和保持时间?因为触发器内部数据的形成是需要⼀定的时间的,如果不满⾜建⽴和保持时间,触发器将进⼊亚稳态,进⼊亚稳态后触发器的输出将不稳定,在0和1之间变化,这时需要经过⼀个恢复时间,其输出才能稳定,但稳定后的值并不⼀定是你的输⼊值。

后端面试_每日一题_总结_hazzm02

找工作准备set_dont_touch_network可以穿过logic,可以用于clocks, pins, 或ports。

当你对设计不十分熟悉时,这个属性可能会传到你不希望的地方去。

set_ideal_net = set_ideal_network -no_propagateclk在创建的时候,会默认为ideal net的,但当clk接入到data path的时候,D端就会考虑我clk上的负载,但并不会影响clk的ideal net的属性。

假如我的clk需要门电路做gating,gating后的时钟也有很大的扇出,那我为了忽略掉延迟,是不是需要在gating后重新给clk定义ideal net?因为ideal net不能穿过逻辑。

如果你的CG集成好的标准单元,它会自动继承ideal的属性上面这几句话中涉及到:set_dont_touch_network和set_ideal_network,而实际上我们在综合时用的是set_dont_touch_network虞希清是怎么讲的呢?P60虞希清书中给的时钟建模语句既不包含ideal network语句,也不包含dont touch network语句衍生时钟什么时候用?应该是分频的时候用?061的启示:CTS之后时序变好还是变差061的实验基于:smic65工艺下的源和后处理。

使用icc,所在目录icc_MACROsetupCTS之后,in2reg的时序如何变换?变好还是变差?CTS后,input port的capture clock由于时钟树的存在,会有延时;而input port的launch clock仍然保持不变,故input port的setup时序会变好。

左上图为Place后的时序报告,右上图的CTS后的时序报告。

虽然已经CTS过,但是其input port到达时间中的clock network delay仍然是ideal,仍然为0.input port的到达时间中的clock network delay即使一直到PnR步骤完成,仍然是ideal的,即为0.这并不符合实际情况,因为input port上的信号不可能比时钟提前到,该信号和时钟是同一时间到达的。

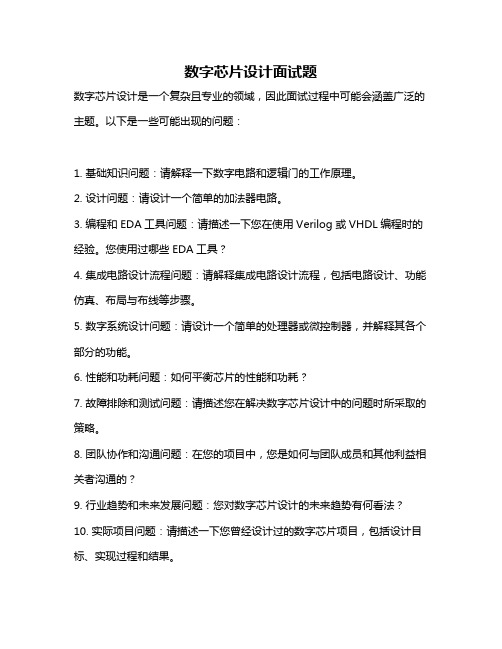

数字芯片设计面试题

数字芯片设计面试题

数字芯片设计是一个复杂且专业的领域,因此面试过程中可能会涵盖广泛的主题。

以下是一些可能出现的问题:

1. 基础知识问题:请解释一下数字电路和逻辑门的工作原理。

2. 设计问题:请设计一个简单的加法器电路。

3. 编程和EDA工具问题:请描述一下您在使用Verilog或VHDL编程时的经验。

您使用过哪些EDA工具?

4. 集成电路设计流程问题:请解释集成电路设计流程,包括电路设计、功能仿真、布局与布线等步骤。

5. 数字系统设计问题:请设计一个简单的处理器或微控制器,并解释其各个部分的功能。

6. 性能和功耗问题:如何平衡芯片的性能和功耗?

7. 故障排除和测试问题:请描述您在解决数字芯片设计中的问题时所采取的策略。

8. 团队协作和沟通问题:在您的项目中,您是如何与团队成员和其他利益相关者沟通的?

9. 行业趋势和未来发展问题:您对数字芯片设计的未来趋势有何看法?

10. 实际项目问题:请描述一下您曾经设计过的数字芯片项目,包括设计目标、实现过程和结果。

以上是一些可能的面试问题,但并不是全部。

具体的面试问题会根据面试官的要求和应聘者的经验、技能水平而有所不同。

半导体或芯片岗位招聘面试题与参考回答(某大型央企)

招聘半导体或芯片岗位面试题与参考回答(某大型央企)面试问答题(总共10个问题)第一题题目:请您描述一次您在半导体或芯片行业中遇到的技术难题,以及您是如何解决这个问题的。

答案:在我在某半导体公司担任工程师期间,我们团队负责的一款新型芯片在试产阶段出现了严重的性能波动问题。

这个问题直接影响了芯片的稳定性和可靠性,给项目进度带来了巨大的挑战。

解决过程如下:1.问题定位:首先,我与团队成员一起分析了芯片的性能数据,通过对比正常和异常情况下的数据,初步定位到问题可能出现在电路设计或材料选择上。

2.深入调查:为了更精确地找到问题根源,我对电路图进行了详细的审查,并重新进行了仿真模拟。

同时,我也对材料供应商进行了沟通,确认了材料的质量。

3.实验验证:为了验证初步的猜测,我设计了一系列实验,对电路进行逐步的修改和优化。

通过对比实验结果,最终确定了是某一级电路的设计存在问题。

4.解决方案:针对定位到的问题,我提出了两种解决方案:一是重新设计该级电路,二是优化电路参数。

经过团队讨论,我们决定实施第一种方案。

5.实施与优化:我与设计团队合作,重新设计了电路,并对新电路进行了详细的仿真和测试。

在经过多次迭代后,新电路的性能得到了显著提升。

6.总结与反馈:在问题解决后,我撰写了详细的报告,总结了问题发生的原因和解决过程,并向团队和上级进行了汇报。

同时,我将这一经验分享给了其他项目团队,以避免类似问题的再次发生。

解析:这道题目旨在考察应聘者对半导体或芯片行业的技术理解和解决问题的能力。

答案中,应聘者首先展示了能够迅速定位问题的能力,然后通过深入调查和实验验证,找到了问题的根源。

接着,提出了切实可行的解决方案,并展示了与团队协作解决问题的能力。

最后,通过总结经验并分享,体现了应聘者的专业素养和对团队贡献的认识。

这样的回答能够很好地展示应聘者的技术能力和团队合作精神。

第二题题目:请详细描述一下您在半导体或芯片行业的工作经验,包括您参与过的主要项目、承担的角色、遇到的挑战以及最终的成果。

数字IC后端设计工程师面试真题·1(含参考答案)

数字IC后端设计工程师面试真题·1(含参考答案)1.1.请说一下标准单元的延迟与哪些因素有关?此题经常容易被作为笔试题,考察学生的时序基础理解能力本质上,standard cell delay由cell的input transition和output load决定PVT作为外部条件,也会影响到cell的delay。

应该理解到PVT与delay的关系是怎么样?建议: 比较全面的回答是在同一种PVT条件下,cell delay由input transition和 output load决定。

2.2.请列举几个你知道的sdc命令,并说出它的用途?回顾常见的sdc命令:描述芯片的工作速度,即时钟的频率,包括create_clock, create_generated_clock等 2描述芯片的边界约束,包括set_input_delay, set_output_delay等,描述芯片的一些设计违反rule(DRV),包括set_max_fanout, set_max_capacitance, set_max_transition等描述设计中一些特殊的路径,包括set_false_path, set_multicycle_path等 5描述设计中一些需要禁止的timing arc,例如set_disable_timing3.3.请说一下drv的概念,主要包含哪些内容?Max transition, max capacitance, max fanout 为什么优先修复,课上提过多次,需要记牢可以特意和面试官指出:max fanout不需要修复4.4.请写一下setup, hold slack的计算公式5.5.列举你知道的几种修复setup timingviolation的方法,该优先使用哪一种?1.减小data path的delay Vt Swap, HVT>RVT, RVT>LVT 插入BUF (线太长,fanout过大) Size up cell(增强驱动) 走高层线2.增加capture clock path delay 需要注意:加buf在capture clock endpoint前面并且检查:下一级path是不是有setup slack margin 该级register的input pin上的有没有hold margin6.6.列举一下你知道的修复hold timing violation的方法? 经典必问题增加data path上的delay Endpoint上***uffer/delay cell讲师建议:面试官一般会引申出去,接着问你buffer插在什么位置优先采用delay cell还是buffer, 这两者的优缺点7.7.在修复hold violation时,delay cell和buffer该优先使用哪一种,各有什么优缺点?Violation较大时,优先使用delay cell;较小时,优先使用buffer。

后端开发工程师面试题及答案

后端开发工程师面试题及答案在当今数字化时代,后端开发工程师在构建强大而稳定的软件系统中发挥着至关重要的作用。

以下是一些常见的后端开发工程师面试题及答案,希望能对您有所帮助。

一、数据库相关1、请简述数据库索引的作用以及在什么情况下不适合使用索引?答案:数据库索引的主要作用是加快数据的查询速度。

它通过对特定列创建索引,使得数据库在查找数据时可以更快地定位到相关记录。

然而,在以下情况下不适合使用索引:数据量较小的表,因为建立索引可能增加额外的开销。

频繁更新的列,因为每次更新都会导致索引的更新,增加了系统的负担。

很少用于查询的列,创建索引没有实际意义。

2、解释一下数据库的事务以及 ACID 特性。

答案:事务是一个逻辑工作单元,要么全部成功执行,要么全部失败回滚。

ACID 特性包括:原子性(Atomicity):事务中的操作要么全部执行,要么全部不执行。

一致性(Consistency):事务执行前后,数据库必须保持一致性状态。

隔离性(Isolation):多个事务并发执行时,相互之间不能干扰。

持久性(Durability):一旦事务提交,其结果就会永久保存。

3、如何优化数据库的查询性能?答案:可以采取以下几种方式来优化数据库查询性能:合理创建索引,确保索引覆盖常用的查询条件。

避免在查询中使用不必要的函数和计算。

优化数据库结构,减少冗余数据。

分表和分区,将大表拆分成小表,提高查询效率。

对复杂查询进行适当的分解和缓存结果。

二、编程语言相关1、在 Java 中,解释一下面向对象的三大特性:封装、继承和多态。

答案:封装是将数据和操作数据的方法封装在一个类中,对外提供有限的访问接口,以保护数据的安全性和完整性。

继承允许一个类继承另一个类的属性和方法,实现代码的复用。

多态是指同一个方法在不同的对象上可以有不同的实现方式,通过父类引用指向子类对象来实现。

2、谈谈 Python 中的装饰器及其用途。

答案:装饰器是 Python 中的一种函数,可以在不修改被装饰函数源代码的情况下,为其添加额外的功能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

@@1、下面是第一个真正的问题:Why power stripes routed in the top metal layers? 为什么电源走线选用最上面的金属层?难度:11.高层更适合global routing.低层使用率比较高,用来做power的话会占用一些有用的资源,比如std cell 通常是m1 Pin 。

2. EM能力不一样,一般顶层是低层的2~3倍。

更适合电源布线。

顶层金属通常比较厚,可以通过较大的电流3.一般ip占用的层次都靠近下几层,如果上层没有被禁止routing的话,top layer 可以穿越,低层是不可能的,并且高层对下层的noise影响也小很多。

@@2、Why do you use alternate routing approach HVH/VHV (Horizontal-Vertical-Horizontal/ Vertical-Horizontal-Vertical)?为什么要使用横竖交替的走线方式?(感觉这个问题比较弱智,但是号称是intel的面试问题,晕!我憧憬和向往的圣地啊!!!)难度:1老是简单的问题比较无趣,问一个貌似简单,但是不容易回答完整的1.有效利用布线资源,更利于布线2.线间干扰最小@@3、How to fix x-talk violation?如何解决线间干扰?难度:4 (关于难度的定义,在第一题里面)(应该至少有5大类解决办法,wire spacing, shielding, change layer之类的只算其中1类)1.增加受害网络的驱动能力upsize victim driver减小侵害网络的驱动能力2.Double witch ,double spacing,wire shileding3.Insert buf in victim net4.Victim的输入端改成hi-vth cell ,hi-vth保证了再小纹波干扰下不发生翻转5.改变timing windows@@4、What are several factors to improve propagation delay of standard cell?哪些因素可以影响标准单元的延迟?难度:3答案应该包括1)PVT2)input transition,output load3)Vth@@5、What would you do in order to not use certain cells from the library?如何禁止使用库里面的某些单元?难度:1禁用就用set_dont_use禁止修改就用set_dont_touch@@6、During the synthesis, what type of wire load model are often used?做RTL综合时,经常使用的wire load model有哪几种?难度:2注意:问题是wire load model,不是wire load mode,也不是delay model答案:1)zero wire load model2)基于fanout的传统WLM3)基于物理位置(距离)的wire load model,在Cadence的RC中叫PLE,Synopsys叫DC Ultra Topographical附加问题:What types of delay model are used in digital design? (数字IC设计中有多少种类型的delay model)答案:NLDM CCS ECSM 还有一个现在基本不用了的—LDM@@7、How delays are characterized using WLM (Wire Load Model)?使用一般的WLM (不是zero WLM,也不是按照物理位置算的DCT),DC是如何计算delay的?难度:2 DC在计算延时的时候,net的rc就要根据所选取的wrie load model来计算,计算时和输出的fanout决定以smic13的smic13_wl10为例wire_load("smic13_wl10") {resistance : 8.5e-8;capacitance : 1.5e-4;area : 0.7;slope : 66.667;fanout_length (1,66.667);根据fanout值,由fanout(1,66.667)可以得出互连线长度为66.667,然后根据resistance和capacitance计算出互连线电容为 1.5e-4*66.667,互连线电阻为8.5e-8*66.667,当然如果扇出值表中没有,就会用到slope,例如扇出为3时,此时估算的互连线长度为1*66.667+(3-1)*slope,再计算出RC值,然后DC由此计算net 的延时。

@@8、There are source clock clka (create_clock), and generated clock clkb by clka.In pre-CTS netlist, there is network latency in clka, how this latency propagates to clkb?In post-CTS netlist, What you need to do for this network latency?假设有两个时钟,原始为clka,生成的时钟为clkb,在没有时钟树的网表中,clka的network latency会自动传递到clkb上吗?clkb的latency 如何描述?在生成时钟树的网表中,如何处理network latency? clkb的latency又如何描述?难度:3答案:在pre-CTS时,clka的network latency会自动传到clkb上在post-CTS时,可以把networklatency去掉,通过set_propagated_clock命令,让工具根据clock tree去计算实际的clocknetwork latency@@9、There are source clock clka (create_clock), and generated clock clkb by clka. how do youspecify them in CTS spec file? Assume there is real timing path between clka and clkb.clkb是clka的生成时钟,在CTS的spec文件中如何定义这两个时钟?假设clka和clkb 间的FF有时序收敛的要求。

难度:3答案:CTS的spec文件中定义clka 是root,clkb 为through pin,再加上那些应该有的skewtransition,insertion delay等就好了,其它的事CTS会给你做@@10、假设在pre-CTS的时序约束中,setup的clock uncertainty是由PLL jitter和clock treeskew两部分组成,那么1)pre-CTS的时序约束中,hold的clock uncertainty是什么?2)post-CTS的时序约束中,setup和hold的clock uncertainty要做什么样的修改?难度:2答案:1)pre-CTS,setup的clock uncertainty = PLL jitter + clock tree skewhold的clock uncertainty = clock tree skew2)post-CTS,setup的clock uncertainty = PLL jitterhold的clock uncertainty = 0@@11、What are various techniques to resolve routing congestion?请详细解释解决走线阻塞的问题难度:4提示:1)routing congestion发生在后端,前端一般不太考虑这个问题,需要后端自己去办法解决,但是解决的办法不只在后端,也有一些方法需要前端的配合2)阻塞有多种情形,要分别讨论,没有一个统一的解决办法。

能够把大部分的阻塞情况列举出来,就已经够4级的水平啦答案:1)阻塞在RAM(macro)之间:可能RAM之间的距离没有计算正确,可以加大RAM之间的间距;扭转RAM的方向,使得RAM的IO pin朝向更容易走线的那边;如果是多个RAM共用地址或者数据线,尽量把RAM的地址数据pin 对齐2)阻塞出现在RAM和帮助单元交界的地方:在RAM周围加一条halo(keepout);把RAM放在四周,尽量把中间留下的空间变成方形;在有阻塞的地方加一些由小的placement blockage组成的矩阵3)阻塞出现在标准单元的某一块:也可以加一些由小的placement blockage组成的矩阵;module/instance padding;利用placement guide减少那块地方的标准单元个数;scan chain reordering也会改善一些阻塞;定义density上限;使用congestion driven的placement,并且要求place之后做congestion优化;在综合是禁止使用那些pin太多太密集的标准单元(多半是那些复杂的组合逻辑单元);请前端使用RAM代替触发器矩阵;请前端修改算法4)应该尽量减少power route占有的资源,谨慎选择power mesh使用的金属层,VIA的大小等。

在detail route完成之后,你如果已经试了各种解决signal congestion的方法,还有少量DRC无法解决时,可以考虑切掉部分power mesh @@12、How do you get better skew/insertion delays in CTS (Clock Tree Synthesis)?如何得到更好的时钟树skew和insertion delay 难度:4如果是用普通的CTS的方法,可以从下面几个方面着手。

不太可能一次就把CTS 做得很好,要反复调试各种参数,达到最佳效果。

1)合理的clock root和through pin。

这个看似CTS会从SDC自动抓出来,但是并不一定是最好的,特别是多个clock相互有重叠的leaf pin时,要特别注意2)不要用太大或者太小的clock buf/inv3)选用RC最小的金属层。

如果上面RC最小的金属层已经被占用,比如RC最小的top,top-1已经不够clock net时,而top-2到layer2都是一样的RC时,可以选用layer3/4。