Cache一致性问题分析

zynq cache问题的解决方法 linux

zynq cache问题的解决方法linuxZynq是Xilinx公司推出的一款全可编程SoC,它集成了FPGA和处理器核心,广泛应用于嵌入式系统开发。

在使用Zynq平台时,开发者可能会遇到Cache相关问题,影响系统的性能。

本文将针对Zynq Cache问题的解决方法进行探讨,主要基于Linux操作系统。

一、Zynq Cache简介Zynq SoC包含ARM Cortex-A9处理器核心,这些核心具有独立的L1 Cache(指令和数据),以及共享的L2 Cache。

Cache的主要作用是临时存储处理器频繁访问的数据和指令,以提高访问速度。

二、Zynq Cache问题及解决方法1.Cache一致性问题问题描述:当多个处理器核心或者处理器与FPGA之间访问同一内存地址时,可能会出现Cache一致性问题。

解决方法:(1)关闭处理器核心的L2 Cache:在Linux内核启动参数中添加“l2cache_disable=1”,以关闭L2 Cache。

(2)使用Cache一致性协议:如MOESI协议,确保多个Cache之间的一致性。

2.Cache性能问题问题描述:Cache命中率和带宽较低,导致系统性能下降。

解决方法:(1)优化程序代码:避免频繁访问大块内存,增加数据局部性。

(2)调整Cache策略:根据应用场景,调整Cache的替换策略和写入策略。

(3)增加Cache容量:在硬件设计阶段,可以考虑增加Cache容量以提高性能。

3.Cache错误问题问题描述:Cache出现错误,可能导致数据丢失或系统崩溃。

解决方法:(1)使用ECC(Error Correction Code)技术:对Cache进行错误检测和纠正。

(2)定期刷新Cache:定期将Cache中的数据写入内存,防止数据丢失。

(3)监控Cache错误计数器:通过查看Cache错误计数器,定位错误原因。

三、总结Zynq Cache问题在嵌入式系统开发中较为常见,了解其解决方法有助于提高系统性能和稳定性。

cache组织方式

cache组织方式Cache组织方式一、什么是Cache?Cache(缓存)是计算机系统中的一种高速存储器,用于临时存放经常访问的数据,以便加快数据的访问速度。

在计算机系统中,Cache通常位于CPU与主存之间,作为CPU与主存之间的缓冲区域,用于暂时存储CPU频繁访问的数据。

二、Cache的作用Cache的主要作用是提高计算机系统的性能,通过减少对主存的访问次数,加快数据的读写速度。

Cache能够存储大量的数据,并通过高速的读写速度,提供快速的数据访问能力。

当CPU需要访问数据时,首先会在Cache中查找,如果找到了需要的数据,则直接返回给CPU,避免了对主存的访问。

如果Cache中没有需要的数据,则需要从主存中加载数据到Cache中,然后再返回给CPU。

三、Cache的组织方式1. 直接映射Cache直接映射Cache是最简单的一种组织方式。

它将主存的地址空间划分为多个Cache块,并将每个Cache块映射到一个特定的主存地址。

当CPU需要访问数据时,首先将数据的地址映射到Cache中对应的块,然后再在该块中查找对应的数据。

直接映射Cache的优点是结构简单,易于实现,但是容易出现冲突,即多个数据映射到同一个Cache块的情况。

2. 全相联Cache全相联Cache是一种较为复杂的组织方式。

它将主存的地址空间划分为多个Cache块,并且允许任意一个主存地址映射到任意一个Cache块。

当CPU需要访问数据时,需要遍历整个Cache,查找对应的数据。

全相联Cache的优点是解决了直接映射Cache中的冲突问题,但是需要进行全局的查找,速度较慢。

3. 组相联Cache组相联Cache是直接映射Cache和全相联Cache的折中方案。

它将Cache划分为多个组,每个组包含多个Cache块。

当CPU需要访问数据时,首先将数据的地址映射到对应的组,然后再在该组中查找对应的数据。

组相联Cache的优点是既减少了冲突,又加快了查找速度,是目前应用最广泛的Cache组织方式。

l2 cache在使用过程中可能遇到的问题

l2 cache在使用过程中可能遇到的问题在计算机科学和工程领域,L2缓存是指位于处理器和主内存之间的第二层缓存。

它的作用是存储处理器频繁访问的数据,以提高数据访问速度和系统性能。

然而,在实际使用过程中,L2缓存也可能会遇到一些问题,影响系统的稳定性和性能。

在本文中,我将从多个角度探讨L2缓存可能遇到的问题,并提供解决方案和个人观点。

1. L2缓存的故障在长时间使用过程中,L2缓存硬件可能会发生故障,导致数据丢失或错误。

这可能是由于电子元件老化、电压不稳定或温度过高等原因造成的。

当L2缓存发生故障时,处理器将无法正常读取和写入数据,从而影响系统的运行。

为了解决这一问题,对L2缓存进行定期检查和维护非常重要。

及时更换老化的硬件或者增加散热设备也能有效减少故障的发生。

2. L2缓存的性能瓶颈在一些高性能计算和数据处理场景下,L2缓存可能会成为系统性能的瓶颈。

由于数据量大、访问频繁,L2缓存的读取和写入速度可能无法满足处理器的需求,从而导致数据延迟和性能下降。

在这种情况下,可以考虑采用更大容量、更高速度的L2缓存,或者优化程序算法和数据访问方式,以减少对L2缓存的依赖,从而提高系统性能。

3. L2缓存的一致性问题在多核处理器或分布式系统中,L2缓存的一致性成为一个关键问题。

由于多个处理器核心共享L2缓存,当一个核心对缓存中的数据进行修改时,需要及时通知其他核心,以保证数据一致性。

否则会出现数据冲突和错误。

为了解决L2缓存一致性问题,可以采用缓存一致性协议、锁定机制或者消息传递等方式,确保数据在多个核心之间的一致性和可靠性。

在我看来,L2缓存在计算机系统中扮演着至关重要的角色,它不仅影响着处理器的性能和功耗,也直接关系到系统的稳定性和可靠性。

在设计和使用L2缓存时,需要综合考虑硬件、软件和应用场景,以充分发挥其性能优势和避免可能遇到的问题。

通过定期维护、优化算法和采用合理的一致性机制,可以有效解决L2缓存可能遇到的问题,提高系统的整体性能和可靠性。

cache工作原理

cache工作原理概述:Cache是计算机系统中的一种高速缓存技术,用于存储最常用的数据,以提高计算机系统的性能。

本文将详细介绍Cache的工作原理,包括Cache的层次结构、Cache的读取和写入操作、Cache的替换策略以及Cache的一致性问题。

一、Cache的层次结构:计算机系统中的Cache通常分为多级,如L1 Cache、L2 Cache、L3 Cache等。

这些Cache按照层次结构排列,速度逐级递减,容量逐级递增。

L1 Cache位于CPU内部,速度最快,容量较小;L2 Cache位于CPU和主内存之间,速度次于L1 Cache,容量较大;L3 Cache位于CPU和主内存之间,速度最慢,容量最大。

Cache的层次结构能够充分利用局部性原理,提高数据的访问效率。

二、Cache的读取和写入操作:1. 读取操作:当CPU需要读取数据时,首先会从L1 Cache开始查找,如果在L1 Cache中找到了需要的数据,则称为命中(Cache Hit),CPU可以直接使用该数据。

如果在L1 Cache中没有找到需要的数据,则会依次向下一级Cache查找,直到找到或者到达主内存。

如果在所有的Cache中都没有找到需要的数据,则称为未命中(Cache Miss),CPU需要从主内存中读取数据,并将数据存入Cache中,以供下一次访问使用。

2. 写入操作:当CPU需要写入数据时,同样会首先在L1 Cache中查找是否存在需要写入的数据。

如果存在,则直接在L1 Cache中进行写入操作。

如果不存在,则需要根据Cache的写策略进行处理。

常见的写策略有写回(Write Back)和写直达(WriteThrough)。

写回策略是将数据先写入Cache中,然后在某个时刻再将数据写入主内存;写直达策略是将数据同时写入Cache和主内存。

写回策略可以减少对主内存的访问次数,提高性能,但可能会引发一致性问题。

三、Cache的替换策略:当Cache已满时,需要替换一些数据以腾出空间存放新的数据。

数据的一致性问题

数据的⼀致性问题1.Cache引起的数据⼀致性问题 主要原因是位于数据IO路径上的各种Cache和Buffer(包括数据块Cache,⽂件系统的Cache,存储控制器的Cache,磁盘Cache等),由于不同系统模块操作处理数据IO的速度有差异,所以就需要添加Cache来缓存IO操作,适配不同模块的处理速度。

这些Cache在提⾼系统处理性能的同时,也可能会‘滞留’IO操作,带来⼀些负⾯影响。

如果在系统发⽣故障时,仍有部分IO‘滞留’在IO操作中,真正写到磁盘中的数据就会少于应⽤程序实际写出的数据,造成的数据不⼀致。

当系统恢复时,直接从硬盘中读出的数据可能存在逻辑错误,导致应⽤⽆法启动。

尽管⼀些数据库(Oracle,DB2)可以根据redo⽇志重新⽣成数据,修复逻辑错误,单着过程是⾮常耗时的,⽽且也不⼀定每次都能成功。

对于⼀些相对功能较弱的数据库(SQL Server),这个问题就更加严重了。

解决办法 关闭Cache或者创建快照。

尽管关闭Cache会导致系统系统性能下降,但在有些应⽤中,这却是必要的选择。

⽐如⼀些⾼等级的容灾⽅案中(RPO为0),都是利⽤同步镜像技术在⽣产中⼼和灾备中⼼之间实时同步复制数据。

由于数据是实时复制的,所以就必须要关闭Cache。

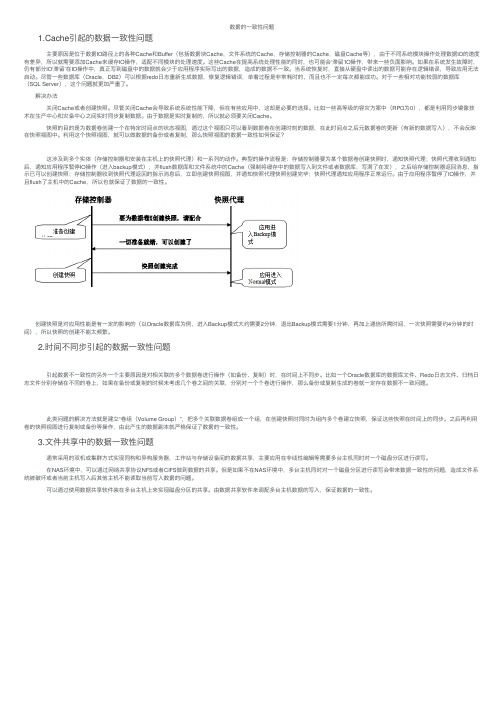

快照的⽬的是为数据卷创建⼀个在特定时间点的状态视图,通过这个视图只可以看到数据卷在创建时刻的数据,在此时间点之后元数据卷的更新(有新的数据写⼊),不会反映在快照视图中。

利⽤这个快照视图,就可以做数据的备份或者复制,那么快照视图的数据⼀致性如何保证? 这涉及到多个实体(存储控制器和安装在主机上的快照代理)和⼀系列的动作。

典型的操作流程是:存储控制器要为某个数据卷创建快照时,通知快照代理;快照代理收到通知后,通知应⽤程序暂停IO操作(进⼊backup模式),并flush数据库和⽂件系统中的Cache(强制将缓存中的数据写⼊到⽂件或者数据库,写满了在发),之后给存储控制器返回消息,指⽰已可以创建快照;存储控制器收到快照代理返回的指⽰消息后,⽴即创建快照视图,并通知快照代理快照创建完毕;快照代理通知应⽤程序正常运⾏。

多核对操作系统的影响1Cache一致性-PPT精选

下图表示数据块x在共享存储器和三个核的 Cache中的副本一致的情形。

x ……

共享存储器

总线

x

x

x

……

Cache

P1

P2

P3

核

10

下图表示core1进行写无效操作后的情形。 写通过:

x’ ……

共享存储器 总线

x’

I

I

Cache

……

core1

core2

core3

核

I表示无效

11

写回:

and updates memory. Both copies become valid). 27

Invalid

Valid

Dirty

Read-blk (3)

Reserved

(3)Read-blk(read from remote processors, the local copy become valid).

17

监听总线协议(Snoopy protocol)

通过总线监听机制实现Cache和共享存储器 之间的一致性。

适用性分析: 适用于具有广播能力的总线结构多Core系统,

允许每个Core监听其它Core的存储器访问情 况。 只适用于小规模的多Core系统。

18

写一次(write-once)协议

改本地和主存副本

并广播Write-inv

使所有副本失效

Write-hit

第二次写命中,用 写回法。但不修改

主存的副本

31

(续表)

command

current state

P-Write 重写

P-Write 无效

next state

cache一致性问题和解决方法

cache一致性问题和解决方法作者辽宁工程技术大学摘要高速缓冲存储器一致性问题是指高速缓冲存储器中的数据必须与内存中的数据保持同步(一致) 。

多核处理器将一个以上的计算内核集成在一个处理器中,通过多个核心的并行计算技术,增强处理器计算性能。

单片多处理器结构(CMP—ChipMultiprocessor)又是该领域中备受关注的问题。

本文简要论述了CMP的多级Cache存储结构,多级结构引起了Cache一致性问题,一致性协议的选取对CMP系统的性能有重要影响。

使用何种Cache一致性模型以及它的设计方案是本文重点研究的内容。

关键词:CMP;Cache一致性;存储器;协议;替换策略Cache consistency problem and solving methodAbstract Cache consistency refers to the data in the cache memory must be synchronized with the data in memory (the same).Multi·core processor was the integration of multiple computing cores on a single processoL which improved processor computing ability through the parallelcomputing Technology of multi-coreprocessors.Single chip multi-processorarchitecture(CMP-ChipMulfiprocessor)was hot spots in this area.The CMPmulti-level Cache storage structure was briefly discussed in this paper,which led to Cache coherence problem,the selection of consistency protocol had a major impact on the performance of the CMP system.The selection of model of theCache Coherence and methods of its design will have a significant impact ofoverall design and development of CMPKey words:CMP Cache; consistency; memory; protocol; replacement strategy1引言在过去的二十年中,计算机处理器设计工艺和处理器体系结构发展迅速,计算机也能够完成所赋予它的大部分任务。

Cache与主存一致性

Cache与主存间数据的一致性计算机存储系统中,高速缓冲存储器系统的引入虽然为计算机系统处理数据的速度带来了显著地提高,但是随之而来的Cache(高速缓存)与主存一致性问题也是日益凸显出来。

存储器中的一致性问题,是伴随着存储器结构的概念而提出的,又一直是困扰着计算机设计者的一个重要问题,也是很多从事计算机体系结构研究的人们所共同面对的一个热门研究课题。

特别是近年来出现的多处理系统,超并行机系统,超大规模计算机系统等采用DSM (Distributed Shared Memory)-分布式共享存储器技术的大型系统中,都采用了多级Cache 的存储器层次结构。

在Cache的数据一致性问题上,就更显突出了。

Cachc的操作与存储器一样具有读/写两种模式,其中读操作主要局限在不命中时更新Cache内容,只影响存储系统工作速度。

写操作不仅工作时间比读操作长,而且更新主存内容,直接影响机器性能。

写操作是直接导致数据一致性问题产生的原因。

在一个系统中,同一个数据的多个拷贝可以同时存在,如果一个拷贝改变了而其它的没变,那么两组不同的数据便与主存的同一地址有关。

Cache必须包含一个更新系统以防止老数据(陈旧数据)被使用,即解决一致性问题。

分析产生数据一致性问题的原因主要有三个:1> 同样一个数据可能既存于Cache中,也存于主存中,这样可能前者己更新,后者未更新,造成数据丢失。

2> 在有DMA系统或多处理器系统中,有多个部件可以访问主存,这时可能其中有些部件是直接访问主存,也可能每个DMA部件和每个处理器配一个Cache,这样主存的一块区域可能对应于多个Cache中的各1个块区,产生主存中的数据被某个总线主控部件更新过,而某个Cache中的内容未更新,造成Cache中数据过时。

3> 当主存中同时有多道程序运行时,Cache中均有相应的数据副本与每道程序相对应;对于共享数据,每道程序都有各自的Cache数据与主存数据相一致。

有关Cache的总结

有关Cache的总结[摘要]随着社会的不断进步和发展,人们对计算机速度和规模的需求不断提高。

在多体并行存储系统中,由于I/O设备向主存请求的级别高于CPU访存,为了避免CPU “空等”现象及CPU和主存的速度差异,在计算机系统的CPU与主存之间引入了cache。

本文介绍了Cache的作用,Cache一致性问题的原因及解决这个问题的两种协议。

[关键字]Cache、Cache一致性、监听协议、基于目录的协议一、C ache简介和工作原理由于I/O设备的向主存请求的级别高于CPU访存,这就出现了CPU等待I/O设备访存的现象,致使CPU空等一段时间,从而降低了CPU的工作效率。

为了避免CPU与I/O设备争抢访存,在CPU与主存之间加一级缓存,这样可将CPU要取的信息提前送至缓存,一旦主存在与I/O设备交换时,CPU可直接从内存中读取所需信息,不必空等而影响效率。

从另一角度来看,主存速度的提高始终跟不上CPU的发展。

据统计,CPU的速度平均每年改进60%,而组成主存的动态RAM速度平均每年只改进7%,结果是CPU和动态的RAM之间的速度间隙平均每年增大50%。

因此由高速缓存cache来解决CPU“空等”现象和主存与CPU速度不匹配的问题。

Cache的工作原理是基于程序访问的局部性,该局部性分为时间局限性和空间局限性。

对大量典型程序运行情况的分析结果表明,在一定时间内,由程序产生的地址只是对集中在存储器逻辑地址空间的很小范围内的访问。

指令地址的分布是连续的,再加上循环程序段和子程序段要重复执行多次。

因此,对这些地址的访问就自然地具有时间上集中分布的倾向。

数据分布的这种集中倾向不如指令明显,但对数组的存储和访问以及工作单元的选择都可以使存储器地址相对集中。

这种对局部范围的存储器地址频繁访问,而对此范围以外的地址则访问甚少的现象,就称为程序访问的局部性。

程序访问的局部性原理分为时间局部性和空间局部性。

根据程序的局部性原理,可以在主存和CPU通用寄存器之间设置一个高速的容量相对较小的存储器,把正在执行的指令地址附近的一部分指令或数据从主存调入这个存储器,供CPU在一段时间内使用。

嵌入式系统中典型Cache一致性问题的解决

② 回写

( RI w TE BACK 或 者 CoRY ACK) B

所 有 修 改 , 只 在 Ca h c e中 进 行 并 设 置 相 关 的 修

改位 ,当且 仅 当要替 换一 个被 修 改过 的行 时 ,才将

块 传送

个 字 传 送 给 CP 。 由 于 U

访 问 的 局 部 性 , 当一 块 数 据 存 入 Ca h 以 满 足 ce

l1

主存储器

Ca h c e无 法 得 知 的 , 所 以 单 纯 使 用 以 上 两 种 写 策 略 ,是 无 法 保 证 主 存 数 据 的 有 效 性 的 。 因 此 以 上 两

r- _

S l i n t y c lc c o e e c n mb d e y tm o uto o t pia a he c h r n e i e e d d s s e

7 U Ke Du Xi h a . 0 nu

( h n h i i tn ie s y S a g a , 0 0 0 S g a a o gUnv r i , h n h i 2 0 3 ) Jo t

摘

要 :随着嵌入式 系统 C U主频越来 越快 ,与 内存速度 差距越 来越大 ,C ce的使用 对解决 系统 的瓶颈 起到 P ah

越来越 重要 的作用 。如果不注 意 C ce ah 一致 性 问题 的处 理 ,将会 对 系统软 件运行 造成 难 以预 料 的结 果 ,甚 至会

导致 系统的崩溃 。 关 键词 :中央处理器 ;高速缓 存 ;P w r C o eP

维普资讯

电

ELECTR0NI C

浅谈并行系统中cache一致性问题和解决方法

浅谈并行系统中cache一致性问题和解决方法班级:0920 姓名:储俊学号:09419022摘要:高速缓冲存储器一致性问题是指高速缓冲存储器中的数据必须与内存中的数据保持同步(一致) 这个问题常发生在CPU内核与另一个设备异步访问内存时。

关键词:cache一致性,监听CACHE协议,基于CACHE目录的协议1.Cache一致性问题的发现本项目的目标板为:处理器采用ARM芯片S3C44B0X,存储器采用2片Flash 和1片SDRAM,在调试的时候输入采用键盘,输出采用显示器,用RS232串口实现通信。

在项目的开发过程中,经软件仿真调试成功的程序,烧入目标板后,程序却发生异常中止。

通过读存储器的内容发现,程序不能正常运行在目标板上,是因为存储器中写入的数据与程序编译生成的数据不一致,总是出现一些错误字节。

经过一段时间的调试发现,只要在程序中禁止Cache的使用,存储器中写入的数据将不再发生错误,程序可以正常运行,但速度明显减慢。

经过分析,认为问题是由于Cache数据与主存数据的不一致性造成的。

Cache数据与主存数据不一致是指:在采用Cache的系统中,同样一个数据可能既存在于Cache中,也存在于主存中,两者数据相同则具有一致性,数据不相同就叫做不一致性。

如果不能保证数据的一致性,那么,后续程序的运行就要出现问题2.分析Cache的一致性问题要解释Cache的一致性问题,首先要了解Cache的工作模式。

Cache的工作模式有两种:写直达模式(write-through)和写回模式(copyback)。

写直达模式是,每当CPU把数据写到Cache中时,Cache控制器会立即把数据写入主存对应位置。

所以,主存随时跟踪Cache的最新版本,从而也就不会有主存将新数据丢失这样的问题。

此方法的优点是简单,缺点是每次Cache内容有更新,就要对主存进行写入操作,这样会造成总线活动频繁。

S3C44B0X 中的Cache就是采用的写直达模式(write-through)。

多核处理器cache一致性技术综述

多核处理器cache一致性技术综述摘要:本文介绍了实现多核处理器cache一致性的基本实现技术,并分析了其存在的问题。

根据存在的问题,介绍了几种最新的解决方案。

关键词:cache 一致性监听协议目录协议性能能耗1 基本实现技术:实现cache一致性的关键在于跟踪所有共享数据块的状态。

目前广泛采用的有以下2种协议,它们分别使用不同的技术跟踪共享数据:1.监听协议( Snooping)处理器在私有的缓存中保存共享数据的复本。

同时处理器对总线进行监听,如果总线上的请求与自己相关,则进行处理,否则忽略总线请求信号。

2.目录式(Directory based)使用目录来存放各节点cache中共享数据的信息,把cache一致性请求只发给存放有相应数据块的节点,从而支持cache的一致性。

下面分别就监听协议和目录协议做简单的介绍:1.1 监听协议监听协议通过总线监听机制实现cache和共享内存之间的数据一致性。

因为其可以通过内存的总线来查询cache的状态。

所以监听协议是目前多核处理器主要采用的一致性技术。

监听协议有两种。

一种称为写无效协议(write invalidate protocol) ,它在处理器写数据块之前通过总线广播使其它该数据的共享复本(主要存储在其它处理器的私有缓存中)变为无效,以保证该处理器能独占访问数据块,实现一致性。

另一种称为写更新(write update) ,它在处理器写入数据块时更新该数据块所有的副本。

因为在基于总线的多核处理器中总线和内存带宽是最紧张的资源,而写无效协议不会给总线和内存带来太大的压力,所以目前处理器实现主要都是应用写无效协议。

读请求:如果处理器在私有缓存中找到数据块,则读取数据块。

如果没有找到数据块,它向总线广播读缺失请求。

其它处理器监听到读缺失请求,则检查对应地址数据块状态:无效状态下,向总线发读缺失,总线向内存请求数据块;共享状态下,直接把数据发送给请求处理器;独占状态下,远端处理器节点把数据回写,状态改为共享,并将数据块发送给请求处理器。

缓存一致性问题(CacheCoherency)

缓存⼀致性问题(CacheCoherency)引⾔ 现在越来越多的系统都会⽤到缓存,只要使⽤缓存就可能涉及到缓存数据与数据库数据之间双写双存储,只要双写就会遇到数据⼀致性的问题,除⾮只有⼀个数据库服务器,数据⼀致性问题也就不存在了。

缓存的作⽤ 1. 临时存储,⽤于提⾼数据查询速度。

⽐如CPU的L1⾼速缓存和L2⾼速缓存,缓存主要是为CPU和内存提供⼀个⾼速的数据缓存区域。

CPU读取数据的百顺序是:先在缓存中寻找,找到后就直接进⾏读取,如果未能找到,才从主内存中进⾏读取。

2. 降低系统反应时间,提⾼并发能⼒。

数据⼀致性的问题的原因 主要是由于两次操作时间不同步导致的数据⼀致性问题。

⽐如Mysql主从复制到时候,master数据在同步slave给数据到过程中会有数据不⼀致的时刻。

如何保证缓存与数据库双写⼀致性 ⼀. 缓存与数据库读写模式(Cache aside pattern) 分两种情况,读数据和写数据(更新) 1. 读数据:读数据时候先读取缓存,如果缓存没有(miss hit)就读取数据库,然后在从数据库中取出数据并添加到缓存中,最后在返回数据给客户端。

2. 更新数据: 先更新数据库数据在删除缓存(也有⼈认为先删除缓存在更新数据库)。

那么为什么在更新数据库同时在删除缓存呢? 这⾥主要考虑⼏个点: 1)缓存懒加载。

有些缓存出来的数据是应⽤在⽐较复杂的场景中,这些缓存存在的时候,不是简单的从数据库取出数据,⽐如更新了数据表中某个字段的值,有⼀条缓存数据值是这个字段的值与另外多个表中字段的值进⾏计算后的结果,当每次该字段被更新的时候都要与其他表多个字段去运算然后得到这个缓存数据,所以这样场景下更新缓存的代价很⾼。

所以要不要实时更新缓存视具体情况来定,⽐如这个字段⼀分钟内修改60次,那么跟该字段相关缓存也跟着要计算60次,但是该缓存⼀分钟内只被访问1次,当缓存真正被访问的时候在进⾏计算,这⼀分钟内缓存只计算了⼀次,开销就⼤幅减少。

计算机组成原理cache论文缓存一致性的解决方案大学论文

缓存一致性的解决方案摘要:随着计算机技术的飞速发展,CPU时计算机组成的核心部分,提高CPU的性能一直是一个很重要的课题,所以CPU从单核提高到多核,但是总会有一些技术上的难题需要解决,这其中,Cache的一致性问题的解决就推动计算机多核的发展,解决一致性人们提出了一些协议,这其中比较好的解决方案是MESI协议,MESI协议通过监视机制,实时监视总系的事务,当修改某一缓存时,通过通知其它同样持有同一内容的缓存来保持缓存的一致性。

这一协议是目前比较好的解决缓存一致性问题的解决方案,本篇文章就这一经典协议做了分析与总结。

关键词:缓存一致性窥探协议引言现代的CPU上,大部分都需要通过缓存来进行内存访问,由于物理架构的原因,CPU没有管脚直接连到内存,所以CPU的读/写(以及取指令)单元正常情况下不能进行直接内存访问。

相反,CPU和一级缓存通讯,而一级缓存才能和内存通讯。

而现在又大多有了二级缓存,甚至三级缓存。

缓存是分段(line)的,即下文要用的“缓存段”(cache line),当我们提到”缓存段”的时候,就是指一段和缓存大小对齐的内存,而不关心里面的内容是否真正被缓存进去。

当CPU看到一条读内存指令时,它会把内存地址传递给一级数据缓存,一级数据缓存会检查它是否有这个内存地址对应的缓存段,没有的话,它会把对应的缓存段加载进来。

如果进行的是读操作,这就很简单,所有级别的缓存都遵循以下规律:在任意时刻,任意级别缓存中的缓存段的内容,等同于它关联内存中的内容。

如果进行写操作,情况就会变得复杂些,一般分为两种基本的写模式:直写(write-through)和回写(write-back)。

直写简单一点:透过缓存,直接把数据写到下一级内存中,如果对应的段被缓存了,就更新缓存中的内容,同样遵循前面的定律:缓存中的段永远和它关联内存的内容匹配。

回写相对复杂一些,回写模式下不会立即把数据传递给下一级,而是仅仅修改本级缓存中的内容,并将其标记为“脏段”,“脏段”会在触发回写,就是将缓存段中的内容传递给下一级,然后脏段又变干净了,即当一个脏段被丢弃了,总是要进行一次回写,在回写模式中,去掉了“任意时刻”这个修饰词,而是以相对弱化的条件代替它:缓存段干净时,缓存段的内容和内存一致;缓存段是脏段时,缓存段中的内容最终要回写到内存中,也就是说可以允许关联内存不和缓存内容同步,但最终要同步。

cache工作原理

cache工作原理一、概述Cache是计算机系统中常用的一种高速缓存技术,用于提高数据访问速度和系统性能。

本文将详细介绍Cache的工作原理,包括Cache的结构、Cache的命中与未命中、Cache的替换策略以及Cache的一致性问题等。

二、Cache的结构Cache通常由多级结构组成,包括L1 Cache、L2 Cache、L3 Cache等。

每一级Cache都有自己的容量、速度和访问方式。

Cache的结构类似于一个存储器,由多个Cache行组成,每个Cache行包含一个标记(Tag)、一个有效位(Valid Bit)和一个数据块(Data Block)。

三、Cache的命中与未命中当CPU需要访问一个数据时,首先会查询Cache,如果数据在Cache中找到,即发生了Cache命中,CPU可以直接从Cache中读取数据,避免了访问主存的开销,提高了访问速度。

如果数据不在Cache中,即发生了Cache未命中,CPU需要从主存中读取数据,并将数据存入Cache中,以便下次访问时可以直接从Cache 中读取。

四、Cache的替换策略当Cache已满且发生了Cache未命中时,需要选择一个Cache行进行替换。

常用的替换策略有随机替换、先进先出替换(FIFO)、最近最少使用替换(LRU)等。

随机替换策略是简单且公平的,但可能会导致Cache的利用率不高;FIFO策略保证了Cache中的数据按照访问顺序排列,但无法适应程序的访问模式变化;LRU策略根据数据的使用频率进行替换,保证了较高的Cache命中率。

五、Cache的一致性问题由于Cache的存在,可能导致多个Cache之间的数据不一致。

当一个Cache修改了某个数据,其他Cache中对应的数据可能仍然是旧值。

为了解决Cache的一致性问题,通常采用缓存一致性协议,如MESI协议。

MESI协议定义了四种状态:修改(Modified)、独占(Exclusive)、共享(Shared)和无效(Invalid),通过协议规定了Cache之间的数据共享和更新机制,保证了Cache的一致性。

Cache一致性

Cache⼀致性

Cache 的⼀致性特性

即使内存区域满⾜了cache的使⽤条件,要正确的使⽤cache,仍然可能会碰到cache⼀致性的问题,由于cache会使得某⼀确定的时

刻,cpu看到的储存内容和内存中的实际内容不⼀致,如果仅仅只是CPU来操作这⽚区域,这不会产⽣任何问题,担当有其他外设也参与读写的时候,就会产⽣以下两种情况的cache⼀致性问题。

1、储存位置被其它外设修改

以⽹卡为例,⽹卡会将接收到的数据包写⼊到指定的内存中(A处地址),⽽如果此内存带cache,且cache中刚刚存A处地址内存的缓存,此时,CPU访问这段内存的时候cache并不知道这段内存已经被⽹卡更新,CPU获得的数据还是cache中缓存的内容,也就是说获取的不是最新数据包的内容。

2、外设需要看到CPU对某块区域储存的修改

以⽹卡发送为例,CPU将要发送的数据包写⼊指定的内存,然后通知⽹卡将此内存中的数据发送出去,如果此内存带cache,CPU写⼊到此内存的数据可能还停留在cache中,内存的数据还未更新,⽹卡就发送了错误的数据。

确保Cache⼀致性的操作

对应于产⽣cache⼀致性问题的两种情况,确保cache⼀致性的操作主要有:

1、cache ⽆效:cache⽆效是将cache中指定的区域的缓存标记为⽆效,当CPU再次访问这个区域时,将强制cache从这个区域重新缓存数据。

2、cache 刷新:cache刷新时指⽴即将cache中指定区域的内容写⼊到内存。

Cache的一致性问题

Cache的⼀致性问题Cache中的内容是主存中的副本。

访问数据是先访问Cache,Cache中没有再看主存中有没有。

当对cache中的内容更新时,就会存在cache和主存如何保持数据⼀致的问题。

此外,下列问题也会导致cache⼀致性问题。

多个设备都允许访问主存时,cache中的内容被cpu修改,⽽主存中的没有,同时该内容需要写⼊磁盘,此时从内存写⼊到磁盘的数据和cache(希望的数据)不⼀样。

当多个CPU都有各⾃的cache⽽共享主存时,若有⼀个cpu修改了⾃⾝cache中的内容,则对应的主存块和其他cpu中对应的cache⾏的内容都变为⽆效(共享数据,数据更改了,未及时更改的那些数据都没⽤了)Cache⼀致性问题的关键是处理好写操作。

全写法对写命中,写未命中的解释:cache的写命中和写未命中,就是磁盘或者内存上的存储区域之前有没有写过数据。

如果有,这次再写到相同的区域叫写命中;如果写到其他区域,叫写未命中。

写操作时,若写命中,则同时写cache和主存;若写不命中,则有以下两种⽅式。

写分配法:先更新主存中的数据,再将更新后的主存块装⼊到cache中。

可重复利⽤程序的局部性原理。

⾮写分配法:仅更新主存中数据不写⼊cache,可减少读⼊主存块的时间,但是没有很好地利⽤程序地局部性原理。

为减少写主存地开⼼,通常再cache和主存之间加⼀个写缓冲,写⼊cache时也写⼊缓冲中,然后由存储控制器将写缓冲中的数据写⼊主存。

(写缓冲的读取速度很快,远远⾼于对主存的读取速度)回写法CPU执⾏写操作时,若写命中,则信息只写⼊cache不写⼊主存;若写不命中,则在cache中分配⼀⾏,将主存块调⼊该cache⾏中并更新相应单元的内容。

该⽅式下,写不命中时通常采⽤写分配法进⾏写操作。

我个⼈理解,写命中就是这个数据在cahce和内存⾥,但是内容不对需要更新。

写未命中就是,这个数据不在内存,也不在cache,需要申请⼀块新的空间存放它。

5.3.5_Cache的一致性问题

5.3.5 Cache的一致性问题 Cache中的内容是主存的副本情况1:当Cache中的内容进行更新时,而没有改变主存中的相应内容时,Cache 和主存之间产生了不一致(inconsistent) 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 8 9 14 3Cache存储器 主存储器 写数据 Cache的一致性问题指什么? 5.3.5 Cache的一致性问题 Cache的一致性问题指什么? 情况2:当多个设备都允许访问主存时 例:I/O设备可通过DMA方式直接读写主存时,如果Cache中的内容被修改,则I/O设备读出的对应主存单元的内容无效;若I/O设备修改了主存单元的内容,则对应Cache行中的内容无效。

情况3:当多个CPU都有各自私有的Cache并且共享主存时 例:某个CPU修改了自身Cache中的内容,则对应的主存单元和其他CPU中对应的Cache行的内容都要变为无效。

5.3.5 Cache 的一致性问题 P3私有Cache 中的变量u 被更新后,各处理器读到的是不同的u 值处理器私有Cache 引入的问题• 同一变量拷贝可能出现在多个处理器私有Cache 中• 某处理器写操作可能对其它处理器是不可见的 程序不能容忍这样的错误, 但这种现象却很常见!I/O devicesMemoryP 1$ $$P2 P3 u :5u :512u :5 3u = 75u = ?4u = ?5.3.5 Cache 的一致性问题 需要研究Cache 写机制l● Write T hrough (写直达、写通过、直写) l● Write B ack (写回、一次性写、回写) 如何保持Cache 一致性呢? 当CPU 写存储地址命中Cache 时 如何保持。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

二、并行系统中的高速缓存一致性问题和解决 方法

2-1、并行系统的特点;

2-2、Cache一致性问题的发现 ;

2-3、分析Cache的一致性问题 ;

2-4、产生高速缓存( Cache )不一致的三个原因 ;

2-5、解决高速缓特点

与单机系统相比,并行系统具有自身的显著特点: (1)具有多个 CPU,同一时刻可以有多个进程同时 进行; (2)各个处理机具有共享内存或私有局部内存,或 两者兼备; (3)各个处理机具有本地高速缓存; (4)各个处理机之间通过共享总线或交换网络进行 通讯,交换数据; 所以除了主存与高速缓存之间可能产生不一致的情况 之外,高速缓存与高速缓存之间也可能存在不一致的情况。

分段 LRU算法基于次数的替换算法 LFU是选择缓存中被 访问次数最少的块为被替换块的替换算法。这种算法中,要为 每个缓存块维护一个计数器,记录该块的被访问次数。在替换 时,选择被访问次数最少的块进行替换。这种算法有两个缺点: 第一,维护和利用访问次数比访问时间困难的多;第二,当某 些短期内被访问多次,却在以后不再被访问的块会长期占据缓 存,降低缓存的利用率。为了解决这些问题,LFU算法在实际 应用中要进行适当的改进。 以上介绍的替换算法在替换时都只是利用缓存块被访问的 状态信息(如访问时间、访、问次数等),没有考虑这些访问 可能来自不同的程序,而且这些不同的应用程序可能具有不同 的数据访问特征,因此这些算法存在如下几个问题: 1、某些应用程序的访问局部性比较差,如果缓存这些访问 应用访问的块,会将其它应用的具有较高缓存价值的块替换掉, 降低缓存的有效性。例如,一些大型文件系统的顺序访问可能 会将缓存中所有的块都替换出缓存,而代以将来可能不会

1-4、高速缓存的组成结构

高速缓冲存储器是存在于主存与CPU之间的一级存 储器, 由静态存储芯片(SRAM)组成,容量比较小但速 度比主存高得多, 接近于CPU的速度。 主要由三大部分组成: Cache存储体:存放由主存调入的指令与数据块。 地址转换部件:建立目录表以实现主存地址到缓存 地址的转换。 替换部件:在缓存已满时按一定策略进行数据块替 换,并修改地址转换部件。

一、高速缓存的概念及其他相关概念的介绍 (单处理器环境下); 二、并行系统中的高速缓存一致性问题和解决 方法; 三、其他相关、相近概念和内容;

四、小结。

一、高速缓存的概念及其他相关概念的介绍 (单处理器环境下) • • • • • • 1-1、局部性现象和局部性定义 1-2、高速缓存定义 1-3、 高速缓存Cache的出现基于的因素 1-4、高速缓存的组成结构 1-5、高速缓存(Cache)的基本原理 1-6、替换算法

再被访问的这些大型文件系统的顺序访问块。这些块占用缓存 空间,会阻碍其他重要的数据进入缓存,因此降低了缓存的有 效性。 2、对于某种应用有效的替换算法可能对其他应用并不有效。 如果缓存系统允许应用程序定义哪种替换算法,就可以使应用 程序能够更有效地使用缓存。 3、某些应用程序可以提供将来的块访问信息,但以上讨论 的替换算法都没有考虑使用这些信息。如果能够在替换时使用 这些信息,可以实现更准确的替换,从而提高缓存的利用率。 4、以上的算法在选择被替换块时没有考虑到公平性。如果 某个程序快速地对大量数据块进行访问,会使缓存区中所有块 都属于该程序,从而会影响其他程序的运行。 工作集 LRU是一种较好解决以上问题的缓存管理算法。工 作集.. LRU为每个执行程序分配一个单独的内存区域,在每个区 域内部使用.. LRU算法,每个程序只替换自己的页面。分配给程 序的区域大小由系统来动态调整。这种方法具有以下优点:

1-3. 高速缓存Cache的出现基于的因素

Cache的出现是基于两种因素 的出现是基于两种因素:首先,是由于CPU的 的出现是基于两种因素 速度和性能提高很快而主存速度较低且价格高,第二就是程 序执行的局部性特点。因此,才将速度比较快而容量有限的 SRAM构成Cache,目的在于尽可能发挥CPU的高速度。很 显然,要尽可能发挥CPU的高速度就必须用硬件实现其全部 功能。 Cache Cache与主存之间可采取多种地址映射方式,直接映射 方式是其中的一种。在这种映射方式下,主存中的每一页只 能复制到某一固定的Cache页中。由于Cache块(页)的大小 为16B,而Cache容量为16KB。因此,此Cache可分为1024 页。可以看到,Cache的页内地址只需4位即可表示;而 Cache的页号需用10位二进制数来表示;在映射时,是将主 存地址直接复制,现主存地址为1234E8F8(十六进制),则最 低4位为Cache的页内地址,即1000,中间10位为Cache的 页号,即1010001111。Cache的容量为16KB决定用这14位 编码即可表示。题中所需求的Cache的地址为10100011111000。

1、可以将更多的内存分配给具有较高访问局部性的应用程 序,以适应这些应用程序的访问特征 ; 2、对某些区域可以使用有应用指定的替换策略而不使用 LRU,这样用户可以将应用指示结合到缓存管理中。 3、通过有系统为每个程序分配相应的系统内存来保证公平 性。 但是工作集 LRU也具有一些缺点,如果分给每个应用程序 的区域调整得太慢,许多应用程序可能无法利用动态多程序环 境中得可用内存:如果调整得太慢,会导致过多得系统调整开 销,超过工作集 LRU法所带来的性能改善。 随机替换法( RAND)不考虑使用情况,在组内随机选择 一块来代替。其性能比根据使用情况的替换算法要差一些。

下面我们先来看看以上内容中所出现的替换算法

1-6、替换算法

当新的主存字块需要调入高速缓存存储器而它的可用位置 又已经被占满时,就产生替换算法问题。常见的替换算法有先 进先出( FIFO)算法、近期最少使用( LRU)算法、分段 LRU算法( Segmented LRU),工作集 LRU(Worset LRU) 基于次数的替换算法( LFU)和随机替换法( RAND)。 FIFO算法总是把一组中最先使用的字块替换出去。它不需 要随时记录各个字块的使用情况,所以实现容易,开销小。 LRU算法是把一组中近期最少使用的字块替换出去。这种替 换算法需随时记录高速缓存存储器中各个字块的使用情况,以 便确定近期最少使用的字块。这种算法利用了访问的时间局部 性,即如果最近访问了某块数据,该块将会在短时间内很可能 被再次访问;如果近期没有访问某个数据块,该块很可能在短 期内不会被访问。LRU替换算法的平均命中率比 FIFO要高,并

1-1、局部性现象和局部性定义

高速缓存的提高系统性能是利用了局部性现象,这里 首先对局部性现象和局部性定义加以说明: 对于大量典型程序的运行情况分析结构表明,在一个 较短的时间间隔内,地址往往集中在存储器逻辑空间的很 小范围内。程序地址的分布本来就是连续的,在加上循环 程序段和子程序段要重复执行多次,因此,对程序地址的 访问就很自然地具有相对集中的倾向。数据分布的这种集 中的倾向不如指令明显,但对数组的存储和访问以及工作 单元的选择都可以使存储器地址相对集中。这种对局部范 围的存储器地址的频繁访问,而对此范围以外的地址则访 问甚少的现象就称为程序访问的局部性。

且当分组容量加大时,能提高 LRU替换算法的命中率。这种算 法简单有效,广泛应用于商业文件系统之中。 分段 LRU算法是建立在.. LRU算法基础上的替换算法。这 种算法基于以下思想,即被访问超过一次的块很可能被再次访 问,因此应该尽量避免替换被访问次数超过一次的块。在分段.. LRU算法中,缓存分成两个部分,探测段(.. Probe Segment) 和保护段(.. Protected Segment)。在这两个段中,数据按照 最近被访问的时间排序。当将一个新块存入缓存时,由于该块 还没有被访问超过一次,该块要被存放在探测段尾部;如果用 户访问的块是已在缓存中的块,由于该块被访问的次数已经超 过一次,该块将被移到保护段的尾部。当保护段满时,被从保 护段舍弃的块要被作为最近被访问的块放入探测段的尾部。利 用这个结构,在选择被替换块时,就能直接选择探测段的头部 的块作为被替换块。

1-2、高速缓存定义

那么什么是高速缓存、它具有什么特点,如何发挥作用呢? 高速缓存的定义如下: 根据局部性原理,可以在主存和 CPU之间设置一个高速 的、容量相对较小的存储器,如果当前正在执行的程序和数 据存放在这个存储器中,在程序运行时,不必从主存储器取 指令和取数据,只要访问这个高速存储器即可,所以提高了 程序运行速度,这个存储器称作高速缓冲存储器(Cache: 英文原意为“藏东西的地方”)。 高速缓存存储器介于 CPU和主存之间,它的工作速度数 倍于主存,全部功能由硬件实现,并且对程序员而言是透明 的。

1-5、高速缓存(Cache)的基本原理

CPU与cache之间的数据交换是以字为单位,而cache与主 存之间的数据交换是以块为单位。一个块由若干定长字组成的。 当CPU读取主存中一个字时,便发出此字的内存地址到cache和 主存。此时cache控制逻辑依据地址判断此字当前是否在 cache 中:若是,此字立即传送给CPU;若非,则用主存读周期把此字 从主存读出送到CPU,与此同时,把含有这个字的整个数据块从 主存读出送到cache中。由始终管理cache使用情况的硬件逻辑 电路来实现LRU替换算法 。

Cache一致性问题分析与解决

计科071

殷成芳 文德春 2010年10月20日

高速缓存(Cache)技术的发明和使用是计算机科学发展 史的重大发展,对于提高计算机系统性能起到了重要的作用。 “没有高速缓存的586计算机性能比不上有高缓存的486计算机” 这种说法可能只是一种理论分析后的简单比较,缺乏证据和说 服力。但是 Pentium II(奔腾二代)300CPU与 Celeron(赛 扬)处理器的根本差别就是Celeron CPU中没有高速缓存,其 性能的差别是显而易见的(当然从价格上,Celeron CPU的价 格也比同等 Pentium II CPU的价格低得多)。事实证明, Intel的 Celeron CPU是一个不成功低端策略。在此后的 Celeron 300A CPU中,就重新加入了高速缓存,实际测试的结 果,Celeron 300A的性能有了大幅度的提高。性能提高的基础 和前提是正确性,由于高速缓存本身的特点,存在产生错误的 因素,即一致性题,所以只有解决了高速缓存的一致性问题, 才能发挥高速缓存的作用,这将是本文关注的重点。为此,我 们通过以下三个方面了解Cache及Cache的一致性问题。