多处理机Cache一致性——监听协议

基于总线侦听Cache一致性协议算法与实现

个 处理 机共 享地 访 问 主存 {o mo moy , cm nme r} 同时 每 个处 理 机义 有 自己的高速缓 存 ( nci ahs 。其 O —hpC ce) 中 C ce 速度 比主存快 得 多的缓 冲存 储 器 , 是 其 ah 是 但

总 第 1 6期 4

基 于 总线 侦 听 C ce一 致性 协 议 算 法 与 实 现 ah

彭 军 杨 , 乐 , 婵 新 盛 立琨 稂 ,

(, 1 江西农业 大学,江西 南 昌 3 04 ; . 30 5 2 江西师范 大学计算机信息工程学院 ,江西 南昌 30 2 ) 30 2

摘要 : 以共 享 总 线 的 多处 理 机 系统 为例 , 文 介 绍 了在 共 享 总线 系统 中 ah 并 基 于 总 线侦 听 Cc e一 致性 协议 的优 点 和 协议 区分 状 态 的 原 因 , 出 了一 个评 价 协 议 好 坏 的 角 度 : 线 的 流 量 和 存 储 器 ah 给 总

Prt c 1 o oo.

Ke r s c c e c h rn e y wo d : a h o e e c ;Ca h ;s o p rtc l ce n y p oo o ;ME I S

计算机系统结构简答题

1.如果外设要求的通道实际流量十分接近货等于通道具有的最大流量解:1.增大通道最大流量2.动态改变设备优先级3.增加一定数量的缓存器,尤其是优先级比较低的设备2.RISC处理器的关键技术有哪几种?解:1.延时转移技术2.指令取消技术3.重叠寄存器窗口技术4.指令流调整技术3.向量的处理方式有哪三种?各有何特点?解:1.横向处理方式。

向量计算是按行的行从左至右横向地进行。

2.纵向处理方式。

向量计算是按列的方式自上而下地进行。

3.纵横处理方式。

横向处理和纵向处理相结合的方式。

4.列出互连网络中四种寻径方式?并指出他们各自优缺点?解:线路交换:传递信息时必须频繁建立从源节点到目的节点的物理通路,开销很大。

存储转发寻径:包缓冲区大,不利于VLSI的视线,时延大,与节点的距离成正比。

虚拟直通寻径:没有必要等到整个小心全部缓冲后在做路由选择,只要接受到用作寻址的消息头部即可判断,通信时延与节点数无关,同样不利于vlsi 的实现。

虫蚀寻径:每个节点的缓冲区小,易于VLSI的实现,较低的网络传输时延,通道共享性好,利用率高,易于实现选播和广播通信方式。

动态就是想把乘法做完,只要能做加法,就做加法!1.2.3.4.5是任务a1*b1--a5*b5.整个处理过程为17个时钟周期,进行了9次不同运算,TP=9/17t,这些运算串行处理所需要的时钟周期为31个时钟周期,S=31/17=1.82. Y=31/(17*5)=36.5.5.设计一台计算机应有哪五类基本指令?解:输入输出类指令数据传送类指令算数运算与逻辑运算类指令程序控制类指令控制管理机器类指令6.设计一个计算机系统时,确定数据表示的原则主要有哪几个?解:1.缩短程序的运行时间2.减少CPU与主存之间的通信量3.这种数据表示的通用性和利用率7.在多处理机系统中,Cache一致性问题由什么引起,主要采用哪两种方法解决?解:Cache一致性问题主要由共享可写的数据,进程迁移,I/O传输等原因产生。

cache 的mesi协议

cache 的mesi协议摘要:1.什么是Cache?2.Cache 的一致性问题和解决方案3.MESI 协议的提出4.MESI 协议的工作原理5.MESI 协议的优点和局限性6.总结正文:1.什么是Cache?Cache 是一种存储器,用于存储最近访问的数据。

在计算机系统中,Cache 位于处理器和主存储器之间,其作用是缓存主存储器中的数据,以便处理器能够更快地访问数据。

2.Cache 的一致性问题和解决方案当多个处理器同时访问Cache 时,可能会出现一致性问题。

为了解决这个问题,人们提出了多种一致性协议,其中最常用的是MESI 协议。

3.MESI 协议的提出MESI 协议是由加州大学伯克利分校的计算机科学家们提出的。

它是一种基于监听的总线协议,旨在解决Cache 一致性问题。

4.MESI 协议的工作原理MESI 协议根据数据的修改情况将Cache 分为四种状态:M(Modified)、E(Exclusive)、S(Shared)和I(Invalid)。

当处理器修改Cache 中的数据时,它将数据的状态设置为M。

当其他处理器请求访问该数据时,它将检查数据的状态,如果数据的状态为M,则处理器会拒绝访问;如果数据的状态为E,则处理器会允许访问;如果数据的状态为S,则处理器会共享数据;如果数据的状态为I,则处理器会重新加载数据。

5.MESI 协议的优点和局限性MESI 协议的优点是简单、高效,能够解决Cache 一致性问题。

然而,MESI 协议也有一些局限性,例如,它要求处理器能够区分不同状态的数据,这可能会增加处理器的复杂性。

6.总结MESI 协议是一种基于监听的总线协议,用于解决Cache 一致性问题。

它根据数据的修改情况将Cache 分为四种状态,并规定了不同状态下的处理器行为。

cache一致性协议实现的基本方法

面已经谈到,随着处理机数目N 的增大、存储器容量的增加,所 需要目录的容量以N2 的数量级增加。在目录本身就很庞大的情 况下,还需要增加一位C/D 位,以指示该复本是否允许写。所以 这种目录结构所需要的空间较为庞大。针对这个问题,提出了 有限目录的方法。 2)有限目录 有限目录的基本思想是要解决全映射目录空间过大的问题。 其采用的手段就是对任意一个数据块在高速缓存中同时存在的 复本的数目加以一定的限制,这是基于处理机使用的局部性, 即多机系统解决问题时,短时间内可能只集中使用其中几台机 器,所以某一个数据块的复本只有部分处理机需要,因此只需 要记录这几台机器,而不需要记录所有处理机,目录所需空间 大大减少:记录处理机号码的所需空间呈Log2N 增长,总的空间 需求为O(N XLog2N)。 3)链式目录 链式目录是采用目录指针链来跟踪共享可写数据的复本;链 表既可以采用单链表,又可以采用双链表。对于共享数据块的 复本数没有限制。所占用的空间和可扩展性与有限目录近似。

(3)Write- inv:远程高速缓存在写命中时在总线上广播一个无 效命令 (4)Read-inv:远程高速缓存在写缺失时在总线上广播一个无 效命令 (5)Read-blk:从另外一个高速缓存中读出一份有效复本。 这两条属于一致性命令 3)写操作可能遇到的几种情况 (1)如果C1 为VALID,写C1 时,则写命中(Write hit) a. 如果内存单元所在的块在高速缓存中,则可以写高速缓存 命中。 b. 如果内存单元所在的块不在高速缓存中,则写缺失,将内 存单元所在块读入高速缓存,再进行写操作发P-Write 修改C1 内 容,修改内存,发Write-Inv 给所有高速缓存,使它们的状态变 为无效。同时使本地的高速缓存中数据块的状态变Reserved。 (2)如果C1 为Reserved,对C1 进行写操作时,则写命中。发PWrite 命令修改C1内容,不修改内存中的复本,C1 状态变为 Dirty (3)如果C1 为Dirty,写C1 时则写命中。发出P-Write 命令修

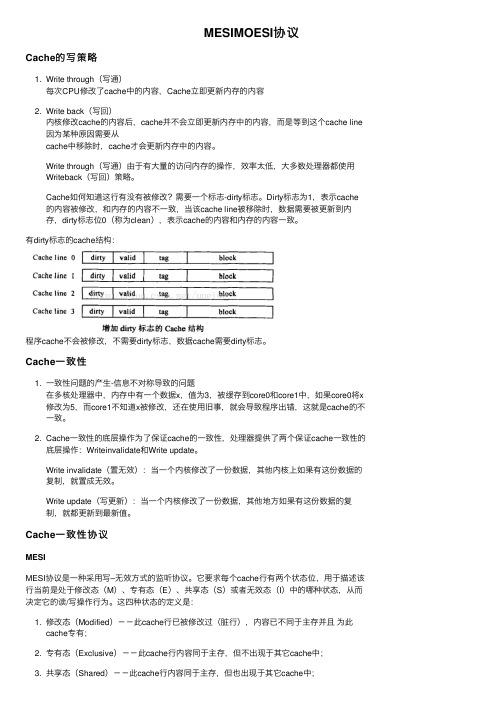

MESIMOESI协议

MESIMOESI协议Cache的写策略1. Write through(写通)每次CPU修改了cache中的内容,Cache⽴即更新内存的内容2. Write back(写回)内核修改cache的内容后,cache并不会⽴即更新内存中的内容,⽽是等到这个cache line 因为某种原因需要从cache中移除时,cache才会更新内存中的内容。

Write through(写通)由于有⼤量的访问内存的操作,效率太低,⼤多数处理器都使⽤Writeback(写回)策略。

Cache如何知道这⾏有没有被修改?需要⼀个标志-dirty标志。

Dirty标志为1,表⽰cache 的内容被修改,和内存的内容不⼀致,当该cache line被移除时,数据需要被更新到内存,dirty标志位0(称为clean),表⽰cache的内容和内存的内容⼀致。

有dirty标志的cache结构:程序cache不会被修改,不需要dirty标志,数据cache需要dirty标志。

Cache⼀致性1. ⼀致性问题的产⽣-信息不对称导致的问题在多核处理器中,内存中有⼀个数据x,值为3,被缓存到core0和core1中,如果core0将x 修改为5,⽽core1不知道x被修改,还在使⽤旧事,就会导致程序出错,这就是cache的不⼀致。

2. Cache⼀致性的底层操作为了保证cache的⼀致性,处理器提供了两个保证cache⼀致性的底层操作:Writeinvalidate和Write update。

Write invalidate(置⽆效):当⼀个内核修改了⼀份数据,其他内核上如果有这份数据的复制,就置成⽆效。

Write update(写更新):当⼀个内核修改了⼀份数据,其他地⽅如果有这份数据的复制,就都更新到最新值。

Cache⼀致性协议MESIMESI协议是⼀种采⽤写–⽆效⽅式的监听协议。

它要求每个cache⾏有两个状态位,⽤于描述该⾏当前是处于修改态(M)、专有态(E)、共享态(S)或者⽆效态(I)中的哪种状态,从⽽决定它的读/写操作⾏为。

并行机紧耦合松耦合系统原理构成以及存储体系结构

并行机紧耦合松耦合系统原理构成以及存储体系结构姓名:________________________班级:________________________学号:________________________并行机紧耦合松耦合系统原理构成以及存储体系结构摘要计算机发展的趋势是越来越先进,越来越高级。

从数据处理、信息处理到知识处理,最终到智能处理,每前进一步,都要求增强计算机系统的处理能力。

计算机发展的历史表明:为了达到高性能,除了必须提高元器件的速度外,系统结构的改进是另一种重要途径,特别是当元器件的速度达到极限时,改进系统结构就成为问题的焦点。

对此,了解紧耦合松耦合系统原理构成以及存储体系结构十分重要。

AbstractTrends in computer development is more advanced, more and more advanced. From the data processing, information processing to knowledge processing, eventually to the intelligent processing. Every step, require enhanced processing capabilities of the computer system .The history of computer development shows that in order to achieve high performance,in addition to the need to improve the speed of external components. Improved system architecture is another important way. In particular, when the speed limit is reached components.Improved system architecture has become the crux of the problem. Therefore,learn tightly coupled and loosely coupled systems theory constitutes storage architecture is very important.关键字:紧耦合;松耦合;存储体系;Cache一致性一.多处理机系统多处理机系统是由多台处理器组成的计算机系统。

适用于多核环境的混合Cache一致性协议

需要在高速缓冲 中为处理器 内核 中的 C c e ah 数据 副本创建较

多的 目录项 ,占用了大量 的存储空间 ,因此在 目录较大时 , 查询时延也较大 。

个处理器 内核 的私有 Cce a ,内核时刻监听总线 是否有请 求 h 送达 ,所有处理器 内核 发出的请求 以广播方式发送到其他 处 理器 内核节点 ,共享总线保证所有处理器 内核 的数据请求串 行执行 。典型 的监听协议有 ME I J S 协议和 M SF E I 协议 。

3 小容量 目录 D C ce - ah

本文协议为克服监听协议无差别发送广播的缺 点,在系 统结构 中引入 了一个 目录 cce a ——DC ce —ah 通过 h —ah ,DC ce 互联结构 和处理器 内核的私 有 L1 ah 互联。带有 D C c e ce C — ah

监听协议的优点是结构比较简单, 但因为总线是独占性 资源,当总线上互联的处理器内核节点较多时, 协议的效率 会急剧下降 。处理器内核的一致性数据请求事务都要无差 别地在总线上广播,并且所有监听到请求的 C ce ah 控制器都 要查找 C ce ah 中是否包含了请求数据 的副本 ,即使不包含远 程请求数据副本的 C ce ah 也需要执行 查找操作 ,无谓地消耗

如是 ,进行下一步处理 。

() 有请求 数据 的 目的 内核 将数据 副本 以点对 点方 式 2含 发送给源请求 内核 ,并进行数据副本状态维护 。

() 3 目的内核向 D C ce发送确认 ,D— ah 维护 目录。 — ah Cce

状态 ;C r—u e 为数据块 副本所在 内核编号 。 oen mb r

cache一致性问题和解决方法

cache一致性问题和解决方法作者辽宁工程技术大学摘要高速缓冲存储器一致性问题是指高速缓冲存储器中的数据必须与内存中的数据保持同步(一致) 。

多核处理器将一个以上的计算内核集成在一个处理器中,通过多个核心的并行计算技术,增强处理器计算性能。

单片多处理器结构(CMP—ChipMultiprocessor)又是该领域中备受关注的问题。

本文简要论述了CMP的多级Cache存储结构,多级结构引起了Cache一致性问题,一致性协议的选取对CMP系统的性能有重要影响。

使用何种Cache一致性模型以及它的设计方案是本文重点研究的内容。

关键词:CMP;Cache一致性;存储器;协议;替换策略Cache consistency problem and solving methodAbstract Cache consistency refers to the data in the cache memory must be synchronized with the data in memory (the same).Multi·core processor was the integration of multiple computing cores on a single processoL which improved processor computing ability through the parallelcomputing Technology of multi-coreprocessors.Single chip multi-processorarchitecture(CMP-ChipMulfiprocessor)was hot spots in this area.The CMPmulti-level Cache storage structure was briefly discussed in this paper,which led to Cache coherence problem,the selection of consistency protocol had a major impact on the performance of the CMP system.The selection of model of theCache Coherence and methods of its design will have a significant impact ofoverall design and development of CMPKey words:CMP Cache; consistency; memory; protocol; replacement strategy1引言在过去的二十年中,计算机处理器设计工艺和处理器体系结构发展迅速,计算机也能够完成所赋予它的大部分任务。

多处理机系统

量减少并行程序的执行时间。

2. 多处理机调度方式

确定性调度:在调度之前必须知道所有有关信息,例如每个任务的执行时间 和任务间的依赖关系,以便合理地把任务分派到处理机。 不确定性调度:根据任务运行的动态行为,将任务分配到特定的处理机上。

3. 调度性能评价

评价多处理机调度性能的参数有: 任务流时间 :完成任务所需要的时间

2.独立监督式

独立监督式中,每一个处理机均有各自的管理程序(核心)。

3.浮动监督式

每次只有一台处理机作为执行全面管理功能的“主处理机”,但根 据需要,“主处理机”是可浮动的,即从一台切换到另一台处理机。

多处理机系统控制

多处理机调度

1.什么是多处理机调度

将作业或任务分配给指定的处理机,并要求在指定的时间内完成。调度算 法的一般目标是:使用最少的处理机、在最短的时间内完成并行程序的执 行任务。在处理机器数目固定时,要改进处理机分配和进程调度算法,尽

I/O操作

Cache中的内容可能与由I/O子系统输入输出形成的存储 器对应部分的内容不同。

共享数据

不同处理器的Cache都保存有对应存储器单元的内容。

存储器的一致性

如果对某个数据项的任何读操作均可得到其最新写入的值,

则认为这个存储系统是一致的 需满足以下条件 ① 处理器P对X进行一次写之后又对X进行读,读和写之间没有

存储器

I/O 系统

多个处理器共享一个存储器 当处理器规模较小时,这种机器十分经济 支持对共享数据和私有数据的cache缓存 私有数据供一个单独的处理器使用,而共享数据供多个处 理器使用

共享数据进入cache ,产生一个新的问题

Cache一致性问题!

多处理机cache的一致性

多核Cache一致性

x’

core1

x’

core2

……

x’

core3

I表示无效

4.写无效的问题 主要开销在两个方面: (1)作废各Cache副本的开销; (2)由作废引起缺失造成的开销,即处理 机需要访问已经作废的数据时将引起Cache的 缺失。

后果: 如果一个Core经常对某个块连续写,且Core 间对共享块的竞争较小,这时写无效策略维护 一致性的开销是很小的。如发生严重竞争,即 Core之间对某个地址的共享数据竞争,将产生 较多的作废,引起更多的作废缺失。结果是共 享数据在各Cache间倒来倒去,产生颠簸现象, 当缓存块比较大时,这种颠簸现象更为严重。

5. Write-Once一致性协议状态转移表

current command state P-Read P-Write 有效 有效 next state status action

P-Write

保留

必是局部进行, 有效 Read-hit 不影响有效状态 第一次写命中,用 保留 Write-hit 写通过法。同时修 改本地和主存副本 并广播Write-inv 使所有副本失效 第二次写命中,用 重写 Write-hit 写回法。但不修改 主存的副本

5. 写更新的问题 由于更新时,所有的副本均需要更新,开 销很大。

1.1 Cache Coherence问题 1.2 监听总线协议

1.2.1 写一次协议

1.3 基于目录的Cache一致性协议 1.4 三种Cache一致性策略

1.2 监听总线协议(Snoopy protocol)

通过总线监听机制实现Cache和共享存储 器之间的一致性。 适用性分析: 适用于具有广播能力的总线结构多Core系 统,允许每个Core监听其它Core的存储器访 问情况。 只适用于小规模的多Core系统。

计算机体系结构习题答案

一、(5分)计算机系统设计中经常使用的4个定量原理是什么?请简要说明它们的含义。

答:(1)以经常性事件为重点。

在计算机系统的设计中,对经常发生的情况,赋予它优先的处理权和资源使用权,以得到更多的总体上的改进。

(2)Amdahl 定律。

加快某部件执行速度所获得的系统性能加速比,受限于该部件在系统中所占的重要性。

(3)CPU 性能公式。

执行一个程序所需的CPU 时间 = IC ×CPI ×T 。

(4)程序的局部性原理。

程序在执行时所访问地址的分布不是随机的,而是相对地簇聚。

二、(15分)假设某应用程序中有4类操作,通过改进各类操作的功能部件,可(2)各类操作单独改进后,程序获得的加速比分别是多少? (3)4类操作均改进后,整个程序的加速比是多少? 答:根据Amdahl 定律aff S n +-=)1(1,其中f 是可改进部分在总运行时间中所占比例,a 是可改进部分的加速比,可得4类操作均改进后,整个程序的加速比:11.77(1)n ii iS FF S =≈-+∑∑三、(5分)请简述指令之间数据冲突的类型。

答:指令之间的数据冲突有3种类型:真相关、反相关、输出相关。

真相关(数据依赖,有时候也称为数据相关):考虑两条指令i 和j ,i 在j 的前面,指令k 在指令i 和指令j 之间。

如果下述条件之一成立,则称指令j 与指令i 真相关:(1)指令j 使用指令i 产生的结果(写后读);(2)指令j 与指令k 真相关,而指令k 又与指令i 真相关。

(真相关的传递性) 反相关:考虑两条指令i 和j ,i 在j 的前面,如果指令j 所写的名与指令i 所读的寄存器名或存储地址相同,则称指令i 和j 发生了反相关。

(读后写)输出相关:考虑两条指令i 和j ,i 在j 的前面,如果指令j 和指令i 所写的寄存器名或存储地址相同,则称指令i 和j 发生了输出相关。

(写后写) 其中反相关和输出相关又合称名相关。

计算机体系结构综合习题

计算机体系结构习题一、名词解释第一章:计算机组成:指的是计算机系统结构的逻辑实现,包含物理机器中的数据流和控制流的组成以及逻辑设计等。

它着眼于物理机器级内各事物的排序方式与控制方式、各部件的功能以及各部件之间的联系。

计算机实现:指的是计算机组成的物理实现,包括处理机、主存等部件的物理结构,器件的集成度和速度,模块、插件、底板的划分与连接,信号传输,电源、冷却及整机装配技术等。

它着眼于器件技术和微组装技术,其中器件技术在实现技术中起主导作用。

程序的局部性原理:指程序执行时所访问的存储器地址不是随机分布的,而是相对簇聚。

常用的经验规则:程序执行时间的90%都是在执行程序中的10%的代码。

数据访问也具有局部性。

第二章:RISC:即精简指令集计算机,它是尽可能地把指令系统简化,不仅指令的条数少,而且指令的功能比较简单。

(P36页)CISC:即复杂指令集计算机,它是增强指令功能,把越来越多的功能交由硬件实现,指令的数量也越来越多。

(P36页)寻址方式:指指令系统中如何形成所要访问的数据的地址。

第三章:流水线技术:(P53页)把一个重复的过程分解为若干个子过程(相当于上面的工序),每个子过程由专门的功能部件来实现,把多个处理过程在时间上错开,依次通过各功能段,这样,每个子过程就可以与其他的子过程并行进行,这就是流水线技术。

线性流水线:(见P57页)线性流水线是指各段串行连接、没有反馈回路的流水线。

数据通过流水线中的各段时,每个段最多只流过一次。

非线性流水线:(见P57页)非线性流水线是指各段除了有串行的连接外,还有反馈回路的流水线。

数据相关:(见P73页)考虑两条指令i和j,i在j的前面,如果下述条件之一成立,则称指令j与指令i数据相关:(1)指令j使用指令i产生的结果;(2)指令j与指令k数据相关,而指令k又与指令i数据相关。

系统级流水线(P55)是把多个处理机串行连接起来,对同一数据流进行处理,,每个处理机完成整个任务中的一部分。

有关Cache的总结

有关Cache的总结[摘要]随着社会的不断进步和发展,人们对计算机速度和规模的需求不断提高。

在多体并行存储系统中,由于I/O设备向主存请求的级别高于CPU访存,为了避免CPU “空等”现象及CPU和主存的速度差异,在计算机系统的CPU与主存之间引入了cache。

本文介绍了Cache的作用,Cache一致性问题的原因及解决这个问题的两种协议。

[关键字]Cache、Cache一致性、监听协议、基于目录的协议一、C ache简介和工作原理由于I/O设备的向主存请求的级别高于CPU访存,这就出现了CPU等待I/O设备访存的现象,致使CPU空等一段时间,从而降低了CPU的工作效率。

为了避免CPU与I/O设备争抢访存,在CPU与主存之间加一级缓存,这样可将CPU要取的信息提前送至缓存,一旦主存在与I/O设备交换时,CPU可直接从内存中读取所需信息,不必空等而影响效率。

从另一角度来看,主存速度的提高始终跟不上CPU的发展。

据统计,CPU的速度平均每年改进60%,而组成主存的动态RAM速度平均每年只改进7%,结果是CPU和动态的RAM之间的速度间隙平均每年增大50%。

因此由高速缓存cache来解决CPU“空等”现象和主存与CPU速度不匹配的问题。

Cache的工作原理是基于程序访问的局部性,该局部性分为时间局限性和空间局限性。

对大量典型程序运行情况的分析结果表明,在一定时间内,由程序产生的地址只是对集中在存储器逻辑地址空间的很小范围内的访问。

指令地址的分布是连续的,再加上循环程序段和子程序段要重复执行多次。

因此,对这些地址的访问就自然地具有时间上集中分布的倾向。

数据分布的这种集中倾向不如指令明显,但对数组的存储和访问以及工作单元的选择都可以使存储器地址相对集中。

这种对局部范围的存储器地址频繁访问,而对此范围以外的地址则访问甚少的现象,就称为程序访问的局部性。

程序访问的局部性原理分为时间局部性和空间局部性。

根据程序的局部性原理,可以在主存和CPU通用寄存器之间设置一个高速的容量相对较小的存储器,把正在执行的指令地址附近的一部分指令或数据从主存调入这个存储器,供CPU在一段时间内使用。

2022年广西交通职业技术学院计算机应用技术专业《计算机系统结构》科目期末试卷A(有答案)

2022年广西交通职业技术学院计算机应用技术专业《计算机系统结构》科目期末试卷A(有答案)一、选择题1、除了分布处理、MPP和机群系统外,并行处理计算机按其基本结构特征可分为流水线计算机,阵列处理机,多处理机和()四种不同的结构。

A.计算机网络B.控制流计算机C.机群系统D.数据流计算机2、在多用户机器上,应用程序员不能使用的指令是()A.“执行”指令B.“访管”指令C.“启动IO”指令D“测试与置定”指令3、对汇编语言程序员透明的是()A.I/O方式中的DMA访问B.浮点数据表示C.访问方式保护D.程序性中断4、对系统程序员不透明的应当是( )。

A.Cache存贮器XB.系列机各档不同的数据通路宽度C.指令缓冲寄存器D.虚拟存贮器5、外部设备打印机适合于连接到( )。

A.数组多路通道B.字节多路通道C.选择通道D.任意一种通道6、从计算机系统结构上讲,机器语言程序员所看到的机器属性是()A.计算机软件所要完成的功能B.计算机硬件的全部组成C.编程要用到的硬件组织D.计算机各部件的硬件实现。

7、开发并行的途径有(),资源重复和资源共享。

A.多计算机系统B.多道分时C.分布式处理系统D.时间重叠8、直接执行微指令的是( )A.汇编程序B.编译程序C.硬件D.微指令程序9、浮点数尾数下溢处理时,最大误差最大,但下溢处理不需要时间,平均误差又趋于0的方法是( )。

A.截断法B.舍入法C.ROM查表法D.恒置"1"法10、块冲突概率最高的Cache地址映象方式是( )A.段相联B.组相联C.直接D.全相联二、判断题11、页面失效请求可以在每条指令执行到末尾时检测,以便在此时看是否调页。

()12、对标量数据来说,并行主存系统的实际频宽采用多体单字方式的要比采用单体单字方式组成的高。

()13、对操作码进行优化编码时,在了解每种指令在程序中出现的概率后,使用Huffman 算法构造Huffman树,这样获得的Huffman编码是唯一的。

《计算机体系结构设计》第07章 并行处理与普适计算

多核CPU,每个处理器核内部有多级指令流水线。 资源共享(Resource Sharing):

是一种软件方式,利用软件让多个用户按一定时间顺序 轮流地使用同一套资源,以提高其利用率,这样相应地提高 整个系统的性能。例如多道程序分时系统。

7.3.2 多处理机系统中的存储器管理

(1)集中共享(共享存储)的并行处理机

每个PE没有局部存触器,存储模块以集中形式为所有

PE共享。

CU

SC

PE0 PE1

… PEN-1

ICN

MM0 MM1

… MMN-1

I/O-CH I/O … SM 图7.15 集中共享存储器结构

(2)分布共享(分布存储)的并行处理机

7.1 并行计算机系统结构 7.2 单处理机系统中的并行机制 7.3 多处理机系统的组织结构 7.4 多处理机操作系统和算法 7.5 从计算机到网络 7.6 普适计算和移动计算 习题7

7.1.1 指令级并行和机器并行

1 并行性(Parallelism)

并行计算机系统最主要的特性就是并行性 (Parallelism),并行性是指计算机系统具有的同时运算或 同时操作的特性,它包括同时性与并发性两种含义。 同时性(Simultaneity):指两个或多个事件在同一时刻

发线程级并行和指令级并行的技术,使用的是线程级并行 性(Thread Level Parallelism,简称TLP)。

实现多线程有两种主要的方法: 细粒度(Fine-Grained)多线程 粗粒度(Coarse-Grained)多线程

7.2.2 单片多核处理器CMP

单芯片多处理器(Chip Multiprocessors,CMP)与同时 多线程处理器(Simultaneous Multithreading,SMT),这

多Cache一致性目录协议监听协议

多Cache一致性目录协议监听协议协议名称:多Cache一致性目录协议监听协议1. 引言本协议旨在定义多Cache一致性目录协议(Multi-Cache Coherence Directory Protocol)的监听机制,以确保多个Cache之间的数据一致性。

2. 监听协议概述2.1 监听目的本监听协议的目的是实现多Cache一致性目录协议中的监听机制,以确保Cache之间的数据一致性和正确性。

2.2 监听参与方本监听协议涉及的参与方包括:- Cache节点:存储数据的缓存节点。

- 目录节点:维护数据的一致性目录的节点。

2.3 监听原则本监听协议遵循以下原则:- Cache节点必须监听目录节点的变化,以获取最新的数据状态。

- 目录节点必须监听Cache节点的操作,以维护一致性目录的正确性。

3. 监听协议详述3.1 Cache节点的监听Cache节点必须监听目录节点的变化,以确保数据的一致性和正确性。

具体监听过程如下:- 当目录节点接收到来自其他Cache节点的写请求时,目录节点将更新一致性目录,并向所有Cache节点发送更新通知。

- Cache节点接收到目录节点的更新通知后,将更新本地存储的数据状态,并执行相应的操作,以保持数据一致性。

3.2 目录节点的监听目录节点必须监听Cache节点的操作,以维护一致性目录的正确性。

具体监听过程如下:- 当Cache节点执行写操作时,Cache节点将向目录节点发送写请求。

- 目录节点接收到Cache节点的写请求后,将更新一致性目录,并向所有Cache节点发送更新通知。

4. 监听协议的通信机制4.1 目录节点与Cache节点的通信目录节点与Cache节点之间的通信可以采用以下机制之一:- 基于消息队列:目录节点和Cache节点之间通过消息队列进行通信,目录节点将更新通知和写请求发布到消息队列,Cache节点订阅消息队列以接收更新通知和写请求。

- 基于事件驱动:目录节点和Cache节点之间通过事件驱动机制进行通信,目录节点将更新通知和写请求作为事件触发,Cache节点注册相应的事件处理程序以接收更新通知和写请求。

计算机系统结构习题

一、简答题(2题)相关概念、原理、方法说明及比较分析例题1:解释下列术语层次机构:按照计算机语言从低级到高级的次序,把计算机系统按功能划分成多级层次结构,每一层以一种不同的语言为特征。

虚拟机:用软件实现的机器。

翻译:先用转换程序把高一级机器上的程序转换为低一级机器上等效的程序,然后再在这低一级机器上运行,实现程序的功能。

解释:对于高一级机器上的程序中的每一条语句或指令,都是转去执行低一级机器上的一段等效程序。

执行完后,再去高一级机器取下一条语句或指令,再进行解释执行,如此反复,直到解释执行完整个程序。

计算机系统结构:传统机器程序员所看到的计算机属性,即概念性结构与功能特性。

透明性:在计算机技术中,把这种本来存在的事物或属性,但从某种角度看又好像不存在的概念称为透明性。

计算机组成:计算机系统结构的逻辑实现,包含物理机器级中的数据流和控制流的组成以及逻辑设计等。

计算机实现:计算机组成的物理实现,包括处理机、主存等部件的物理结构,器件的集成度和速度,模块、插件、底板的划分与连接,信号传输,电源、冷却及整机装配技术等。

软件兼容:一个软件可以不经修改或者只需少量修改就可以由一台计算机移植到另一台计算机上运行。

差别只是执行时间的不同。

兼容机:由不同公司厂家生产的具有相同系统结构的计算机。

模拟:用软件的方法在一台现有的计算机(称为宿主机)上实现另一台计算机(称为虚拟机)的指令系统。

仿真:用一台现有计算机(称为宿主机)上的微程序去解释实现另一台计算机(称为目标机)的指令系统。

并行性:计算机系统在同一时刻或者同一时间间隔内进行多种运算或操作。

只要在时间上相互重叠,就存在并行性。

它包括同时性与并发性两种含义。

时间重叠:在并行性概念中引入时间因素,让多个处理过程在时间上相互错开,轮流重叠地使用同一套硬件设备的各个部分,以加快硬件周转而赢得速度。

资源重复:在并行性概念中引入空间因素,以数量取胜。

通过重复设置硬件资源,大幅度地提高计算机系统的性能。

Cache的一致性问题

Cache的⼀致性问题Cache中的内容是主存中的副本。

访问数据是先访问Cache,Cache中没有再看主存中有没有。

当对cache中的内容更新时,就会存在cache和主存如何保持数据⼀致的问题。

此外,下列问题也会导致cache⼀致性问题。

多个设备都允许访问主存时,cache中的内容被cpu修改,⽽主存中的没有,同时该内容需要写⼊磁盘,此时从内存写⼊到磁盘的数据和cache(希望的数据)不⼀样。

当多个CPU都有各⾃的cache⽽共享主存时,若有⼀个cpu修改了⾃⾝cache中的内容,则对应的主存块和其他cpu中对应的cache⾏的内容都变为⽆效(共享数据,数据更改了,未及时更改的那些数据都没⽤了)Cache⼀致性问题的关键是处理好写操作。

全写法对写命中,写未命中的解释:cache的写命中和写未命中,就是磁盘或者内存上的存储区域之前有没有写过数据。

如果有,这次再写到相同的区域叫写命中;如果写到其他区域,叫写未命中。

写操作时,若写命中,则同时写cache和主存;若写不命中,则有以下两种⽅式。

写分配法:先更新主存中的数据,再将更新后的主存块装⼊到cache中。

可重复利⽤程序的局部性原理。

⾮写分配法:仅更新主存中数据不写⼊cache,可减少读⼊主存块的时间,但是没有很好地利⽤程序地局部性原理。

为减少写主存地开⼼,通常再cache和主存之间加⼀个写缓冲,写⼊cache时也写⼊缓冲中,然后由存储控制器将写缓冲中的数据写⼊主存。

(写缓冲的读取速度很快,远远⾼于对主存的读取速度)回写法CPU执⾏写操作时,若写命中,则信息只写⼊cache不写⼊主存;若写不命中,则在cache中分配⼀⾏,将主存块调⼊该cache⾏中并更新相应单元的内容。

该⽅式下,写不命中时通常采⽤写分配法进⾏写操作。

我个⼈理解,写命中就是这个数据在cahce和内存⾥,但是内容不对需要更新。

写未命中就是,这个数据不在内存,也不在cache,需要申请⼀块新的空间存放它。

计算机系统结构复习试题及答案(非计算)

一.名词解释计算机系统结构:传统机器程序员所看到的计算机属性,即概念性结构与功能特性。

在计算机技术中,把这种本来存在的事物或属性,但从某种角度看又好像不存在的概念称为透明性。

系列机:由同一厂家生产的具有相同系统结构、但具有不同组成和实现的一系列不同型号的计算机。

同构型多处理机系统:由多个同类型或至少担负同等功能的处理机组成,它们同时处理同一作业中能并行执行的多个任务。

堆栈型机器:CPU 中存储操作数的单元是堆栈的机器。

累加器型机器:CPU 中存储操作数的单元是累加器的机器。

通用寄存器型机器:CPU 中存储操作数的单元是通用寄存器的机器。

数据相关:考虑两条指令i 和j,i 在j 的前面,如果下述条件之一成立,则称指令j 与指令 i 数据相关:(1)指令j 使用指令i 产生的结果;(2)指令j 与指令k 数据相关,而指令k 又与指令i 数据相关。

定向:用来解决写后读冲突的。

在发生写后读相关的情况下,在计算结果尚未出来之前,后面等待使用该结果的指令并不见得是马上就要用该结果。

如果能够将该计算结果从其产生的地方直接送到其它指令需要它的地方,那么就可以避免停顿。

向量处理机:指令级并行:简称ILP。

是指指令之间存在的一种并行性,利用它,计算机可以并行执行两条或两条以上的指令。

指令的动态调度:是指在保持数据流和异常行为的情况下,通过硬件对指令执行顺序进行重新安排,以提高流水线的利用率且减少停顿现象。

是由硬件在程序实际运行时实施的。

指令的静态调度:是指依靠编译器对代码进行静态调度,以减少相关和冲突。

它不是在程序执行的过程中、而是在编译期间进行代码调度和优化的。

失效率:CPU 访存时,在一级存储器中找不到所需信息的概率。

失效开销:CPU 向二级存储器发出访问请求到把这个数据调入一级存储器所需的时间。

强制性失效:当第一次访问一个块时,该块不在Cache 中,需要从下一级存储器中调入Cache,这就是强制性失效。

容量失效:如果程序在执行时,所需要的块不能全部调入Cache 中,则当某些块被替换后又重新被访问,就会产生失效,这种失效就称作容量失效。

2022年大连医科大学中山学院计算机科学与技术专业《计算机系统结构》科目期末试卷A(有答案)

2022年大连医科大学中山学院计算机科学与技术专业《计算机系统结构》科目期末试卷A(有答案)一、选择题1、在系统结构设计中,提高软件功能实现的比例会( )。

A.提高解题速度B.减少需要的存贮容量C.提高系统的灵活性D.提高系统的性能价格比2、IBM360/91属于()A.向量流水机B.标量流水机C.阵列流水机D.并行流水机3、浮点数尾数下溢处理时,最大误差最大,但下溢处理不需要时间,平均误差又趋于0的方法是( )。

A.截断法B.舍入法C.ROM查表法D.恒置"1"法4、下列说法中不正确的是()A.软件设计费用比软件重复生产费用高B.硬件功能只需实现一次,而软件功能可能要多次重复实现C.硬件的生产费用比软件的生产费用高D.硬件的设计费用比软件的设计费用低5、程序员编写程序时使用的地址是( )。

A.有效地址B.逻辑地址C.辅存实地址D.主存地址6、对系统程序员不透明的应当是()A.CACHE 存储器B.系列机各档不同的数据通路宽度C.指令缓冲寄存器D.虚拟存储器7、对系统程序员不透明的应当是( )。

A.Cache存贮器XB.系列机各档不同的数据通路宽度C.指令缓冲寄存器D.虚拟存贮器8、()属于MIMD系统结构。

A.各处理单元同时受同一个控制单元的管理B.各处理单元同时接受同一个控制单元送来的指令C.松耦合多处理机和多计算机D.阵列处理机9、属计算机系统结构考虑的是()A.主存采用MOS还是TTLB.主存采用多体交叉还是单体C.主存容量和编址方式D.主存频宽的确定10、流水机器对全局性相关的处理不包括( )A.猜测法B.提前形成条件码C.加快短循环程序的执行D.设置相关专用通路11、计算机系统的层次结构按照由高到低的顺序分别为()。

A.高级语言机器级,汇编语言机器级,传统机器语言机器级,微程序机器级B.高级语言机器级,应用语言机器级,汇编语言机器级,微程序机器级C.应用语言机器级,传统机器语言机器级,汇编语言机器级,操作系统机器级D.应用语言机器级,操作系统机器级,微程序机器级,传统机器语言机器级12、浮点数尾数基值rm=8,尾数数值部分长6位,可表示的规格化最小正尾数为( )A.0.5B.0.25C.0.125D.1/6413、下列说法中不正确的是( )A.软件设计费用比软件重复生产费用高B.硬件功能只需实现一次,而软件功能可能要多次重复实现C.硬件的生产费用比软件的生产费用高D.硬件的设计费用比软件的设计费用低14、计算机中优化使用的操作码编码方法是( )。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

是

否

将要写入到存储器13的内容先写到存储器中,再送回cpuB的1替换掉原来的内容,同时其他cpu中的13的内容作废

5 多处理机Cache一致性——监听协议

5.1实验目的

加深对多Cache一致性的理解;

掌握解决多Cache一致性的监听协议的基本思想;

掌握在各种情况下监听协议是如何工作的。

5.2实验平台

实验平台采用多Cache一致性监听协议模拟器。

5.3实验内容

1)对于以下访问序列,写出监听协议所进行的操作。

所进行的访问

是否发生替换

是否发生写回

监听协议所进行的操作

CPU A读第5块

否

否

将存储器号为5的块送到cacheA的1中,再送到cpuA中

CPU B读第5块

否

否

将存储器号为5的块送到cacheB的1中,再送到cpuA中

CPU 第5块

否

否

将存储器号为5的块送到cacheC的1中,再送到cpuA中

CPU B读第5块

CPU C读第13块

否

否

将存储器号为13的块送到cacheC的1中,再送到cpuA中

CPU B读第13块

否

否

将cacheB中的13中的内容送到cpuB中

CPU D读第13块

否

否

将存储器号为13的块送到cacheD的1中,再送到cpuA中

CPU B写第29块

是

否

将存储器号为29的块送到cacheB的1中,替换掉原来存的13,再送29到cpuB中

否

否

将cacheB中的1中的内容送到cpuB中

CPU D读第5块

否

否

将存储器号为5的块送到cacheD的1中,再送到cpuA中

CPU B写第21块

是

否

将存储器号为21的块送到cacheB的1中,替换掉原来存的5,再送21到cpuB中

CPU A写第23块

否

否

将存储器号为23的块送到cacheA的3中,再送到cpuA中

CPU C写第23块

否

是

将cacheA中的23块内容写回存储器,再将此块内容送到cacheC的3中,再送到cpuC中

CPU B读第29块

是

是

将cacheB中1的21块内容写回存储器21块,之后在将29块内容送到cacheB中的1替换掉原来21块的内容。

CPU B写第5块

是

否

将要写入到存储器5的内容先写到存储器中,再送回cpuB的1替换掉原来的内容,同时其他cpu中的5的内容作废

CPU A写第15块

否

否

将存储器号为15的块送到cacheA的3中,再送到cpuA中

CPU C写第15块

否

是

将cacheA的3中15的内容写回到存储器然后将此块送到cacheC的3中,再送到cpuC中

CPU B读第21块

是

是

将cacheB中1的29块内容写回存储器29块,之后在将21块内容送到cacheB中的1替换掉原来29块的内容。

2)自己编写一个访问序列(尽量涵盖多种状态的转换),写出监听协议所进行的操作。

所进行的访问

是否发生替换

是否发生写回

监听协议所进行的操作

CPU A读第13块

否

否

将存储器号为13的块送到cacheA的1中,再送到cpuA中

CPU B读第13块

否

否

将存储器号为13的块送到cacheB的1中,再送到cpuA中