软件无线电调研

5G室分及重点项目建设方案

5G室分及重点项目建设方案5G室分是指将5G通信技术应用于室内覆盖场景,以提供高速、稳定和高质量的无线通信服务。

室分可以有效解决室内信号弱、覆盖不均匀等问题,提升用户的通信体验。

为了实施5G室分项目,我们需要制定详细的建设方案。

以下是一个可能的建设方案,其中包括室分系统选择、测试和调试、部署和优化等关键步骤。

1.项目准备阶段:在项目准备阶段,需要进行需求调研和分析,与运营商、建筑物所有者和相关部门进行沟通,确定项目的目标和要求。

同时,还需要对室内的结构和布线进行评估,以确定需要部署的设备和技术。

2.室分系统选择:在选择室分系统时,应综合考虑业务容量、频谱效率、网络性能和成本等因素。

可以选择基于小区内分频与共存技术(CID)的室分系统,以支持更多的用户和更高的速率。

此外,还可以考虑引入天线阵列(AAU)和基于网络的软件无线电(SDR)等技术,以提高系统的灵活性和可扩展性。

3.网络规划:在网络规划阶段,需要根据室内的结构和信号传播特点,确定天线位置、信道分配和功率设置等参数。

可以借助专业的仿真工具进行仿真和优化,以确保网络的覆盖率和信号质量。

4.设备采购和部署:在设备采购和部署阶段,需要选购合适的设备,并进行安装和调试。

可以考虑采购具有低延迟和高带宽的基站设备和天线,以满足5G的要求。

同时,还可以选择适合室内环境的天线布局和装置方式,例如天花板安装、墙壁安装或地板安装。

5.测试和调试:在设备部署完成后,需要进行测试和调试,以验证网络的性能和覆盖范围。

可以进行信号强度测试、速率测试和呼叫质量测试等,以评估网络的可用性和稳定性。

同时,还需进行连续优化,包括调整设备参数、改进天线布局和增加设备密度等,以提升系统性能。

6.网络优化和维护:在网络优化和维护阶段,需要定期监测和分析网络的性能指标,以识别和解决潜在问题。

可以使用监测系统和数据分析工具进行实时监控和故障诊断,以确保网络的稳定运行。

同时,还需要定期进行优化工作,如调整天线方向、加强隔离和优化无线资源等,以提升网络的容量和覆盖范围。

电信院导师研究方向

需要参与实验测试

《光通信原理与技术》

32

胡海峰

副教授

(1)于遨波,15349127 (2)邢宋隆,15350061 (3)张穗安,15349137 《概率论》、《计算机视觉》《数字图像处理》、《模式识别 (4)陈志鸿,15305009 》; (5)麦思杰,15350048 (6)徐凯昕,15343087 (7)孙健哲,14304141

《数字电路与逻辑设计》《数字集成电路设计》

9

夏明华

教授

确保在实验室有足够的工 作时间;认真负责,积极 主动;保研或者考研的同 学优先。

《数值计算方法》,《概率论与数理统计》

10

孙伟

教授

1、安全数据空间构建技术及其应用; 2、信息伪装处理编码及FPGA设计与实现; 3、基于Linux+ARM的安全通信系统设计与开发; 4、安全传输协议在网络通信中的应用研究; 5、基于面向对象聚类的协同过滤推荐算法及其 系统实现; 6、基于TensorFlow的仿人脑安全软件代码智能 生成技术研究及其应用。

对学生有何要求

主讲课程

1

戴宪华

教授

《数字通信系统》

2

刘星成

教授

《通信原理》;《无线通信原理》;《现代数字信号处理》

3

龙云亮

教授

1、基于PE的电波传播数值仿真及应用; 2、基于FDTD的电波传播数值仿真及应用; 3、移动通信终端天线设计。

《微波技术与天线》

4

马争鸣

教授

1,HSIC正则的流形学习 2,Grassmann流形上的字典学习 3,基于核学习的域自适应学习 4,流形学习的多项式逼近

《微电子学导论》、《半导体物理》

13

陈军

WLAN信令测试方法调研

2.2优点

WLAN信令测试方法的优点如下: (1 )测试之外的WLAN设备的核准 测试; (3 )测试简单(测试时设备在正常工作状态); (4 )可应用场景多。

2.3测试结果

表1为某型号手机的信令测试WLAN功率与无线射 频参数检测测得结果的对比,图4为测试过程中对该设备 2.4GHz信道、802.11g协议、54Mbps速率进行抓取的 结果截图:

1.3存在的问题

移动互联网行业的飞速发展,促使无线网络功能深入 其他跨行业领域中,涉及各式各类的电子设备,各式各样的 无线局域网设备在市场上到处可见,包括:机顶盒、智能家 居、生物医疗设备及各类民用消费类电子设备等。

WLAN终端设备的多样化也给无线射频参数检测测 试带来了一定的困难:

(1 )非信令的测试方法不能很好地表征WLAN设 备工作时候的状态及性能;

无线电设备管理分为事前准入检测和事中事后监测, 其中无线射频参数检测属于事前准入检测,市场抽检属 于事中事后监测。WLAN设备的市场抽检是检测正常使 用情况下的WLAN设备的射频性能,目前还没有有效 的技术手段用于开展WLAN设备的市场抽检工作,而 WLAN的信令测试能更好地体现无线局域网设备的正常 工作状态,且能够用于WLAN设备的市场抽检工作,但 是影响测试准确性的因素较多,需要进一步仔细研究。

b-11Mbps-2412 3.09 15.59 14.50 1.09

b-1Mbps-2472 2.44 14.24 13.30 0.94

b-11Mbps-2472 2.64 14.44 13.50 0.94

g-6Mbps-2412 0.45 12.95 10.20 2.75

g-54Mbps-2412 1.00 13.50 10.90 2.60

电路与系统专业(080902)硕士研究生培养方案

七、考核方式

1、类、类、类课程考核以笔试为主,由有关任课教师负责考核工作。

2、类课程可采取笔试与写专题综述报告相结合的方法,以了解学生对专业知识的掌握情况和综合分析问题的能力。

科学研究是研究生培养的重要组成部分,是培养学生独立工作能力和创新能力的主要途径,是提高研究生培养质量的关键环节。

研究生在导师指导下通过阅读文献资料和调研,选定研究课题。选题要体现电路与系统学科的前沿性和先进性,应和导师的科研任务结合,与国家经济建设紧密结合。选定研究课题后,作开题报告,由有关专家审议批准后送校研究生院备案。

⑦计算方法

易大义浙江大学出版社

⑧软件工程

(美).

梅宏译机械工业出版社

3、实验性课程必须完成实验,写出完整的实验报告。

4、中期考核:在入学后第三学期初进行中期考核,由导师组成的考核小组对研究生已修课程、论文进展情况及掌握国内外最新研究动态等方面进行考核。考核小组本着公正、负责、实事求是的态度对研究生做出评价,提出继续攻读硕士学位、提前攻读博士学位或停止攻读建议。

八、学位论文

申请硕士学位的学位论文应对所研究的课题有新的见解。

九、答辩和学位授予

学位论文完成后,须按照《南京大学授予博士学位、硕士学位细则》规定的程序和要求进行论文答辩并申请学位。

十、参考书目

、杂志

①电子学报中国电子学会主办

②电子与信息学报中科院电子所

国家自然科学基金信息科学部主办

③计算机应用研究《计算机应用研究》杂志社

④信息与控制中国自动化学会会刊

⑤模式识别与人工智能《模式识别与人工智能》编辑部

自适应跳频(AFH)技术在无线电抗干扰中的应用研究

自适应跳频(AFH)技术在无线电抗干扰中的应用研究研究方案:一、研究背景与目的:无线电通信系统中,干扰一直是一个令人头疼的问题。

干扰来源于多方面的因素,而解决方案的设计应该以有效减少干扰对通信系统的影响并提高通信质量为目的。

自适应跳频技术(AFH)是一种可以应对干扰的关键技术。

本研究旨在研究AFH技术在无线电抗干扰中的应用,探索其对干扰抑制与通信质量的影响,并通过数据采集和分析,提出新的观点和方法为解决实际问题提供有价值的参考。

二、研究内容:1. 分析和调研:对AFH技术的原理、特点和应用现状进行详细的分析和调研,探索其在抗干扰中的潜力以及存在的问题。

2. 实验设计:基于已有研究成果,设计一系列的实验来验证AFH技术在不同干扰场景下的效果。

实验重点包括:不同干扰类型下AFH技术的干扰抑制能力、AFH技术在不同信道条件下的性能等。

3. 数据采集:搭建相应的实验系统,使用专业测试设备收集与AFH技术相关的关键参数,如干扰功率、信号质量、通信成功率等。

4. 数据分析:对采集到的数据进行有效整理与分析,评估AFH技术在不同干扰场景下的有效性,并探索其影响因素。

结合实验结果和已有研究成果,提出新的观点和方法来改进AFH技术应用。

三、方案实施:1. 实验平台搭建:- 在实验室内搭建具有一定规模和场景可控性的无线通信系统,包括干扰源、干扰受干扰无线设备和AFH设备。

- 配置专业的通信设备和测试设备,用于数据采集和干扰场景模拟。

2. 实验参数设定:- 设定实验中要研究的干扰类型,如窄带干扰、宽带干扰等。

- 设定不同通信频率的无线设备,以模拟实际应用中的多频段干扰。

- 设定不同信道条件,包括室内、室外、多径衰落等。

3. 实验过程:- 通过控制干扰源产生不同的干扰信号,模拟不同的干扰场景。

- 分别记录在开启和关闭AFH技术的情况下,目标通信设备的信号质量、通信成功率等关键参数。

- 采集数据并存档备份,确保数据的真实性和完整性。

电厂无线局域网解决方案_技术

电厂无线局域网解决方案_技术目录一、内容概述 (2)1.1 背景介绍 (2)1.2 需求分析 (3)1.3 解决方案概述 (4)二、技术原理 (5)2.1 无线局域网技术原理 (5)2.2 无线传感器网络技术原理 (7)2.3 无线宽带接入技术原理 (8)三、解决方案设计 (10)3.1 网络架构设计 (11)3.2 设备选型与配置 (13)3.3 安全策略设计 (14)3.4 运维管理设计 (15)四、实施步骤 (17)4.1 项目启动与需求调研 (18)4.2 方案设计与评审 (19)4.3 设备安装与调试 (20)4.4 系统测试与优化 (21)4.5 运维培训与移交 (23)五、方案优势 (24)5.1 高效性与可靠性 (25)5.2 易用性与可扩展性 (27)5.3 安全性与保密性 (28)六、案例分析 (29)6.1 电厂无线局域网应用案例一 (32)6.2 电厂无线局域网应用案例二 (33)七、总结与展望 (34)7.1 实施效果评估 (35)7.2 发展趋势与创新方向 (36)一、内容概述随着电厂无线通信技术的不断发展,电厂无线局域网(WLAN)已经成为电厂信息化建设的重要组成部分。

本文档将详细介绍电厂无线局域网解决方案的技术要点,包括需求分析、系统架构设计、设备选型、网络规划与优化、安全策略以及后期维护等方面的内容。

通过对电厂无线局域网的全面研究,为企业提供一套高效、稳定、安全的无线网络解决方案,以满足电厂生产和管理的各种需求。

1.1 背景介绍随着信息技术的飞速发展,电厂对于数据的采集、传输和监控需求日益增强。

传统的有线网络在某些特定环境下,如电厂的锅炉房、涡轮机房等区域,由于环境复杂、设备布局密集,布线难度大且成本高昂,灵活性不足。

无线局域网技术在电厂的应用逐渐受到重视,无线局域网技术以其灵活部署、易于扩展和维护成本低的优势,成为现代电厂信息化建设的重要组成部分。

在此背景下,针对电厂特殊环境的无线局域网解决方案逐渐崭露头角,以满足电厂在生产过程中的实时监控和数据传输需求,进而提升电厂运行的安全性和效率。

中波发射台自动化播控系统研究

692023年12月下 第24期 总第420期信息技术与应用China Science & Technology Overview0 引言中波发射台自动化播控系统涉及较为复杂的软硬件设施,根据其控制结构以及功能划分,可具体归类于集中控制管理、分散控制管理以及分散集中管理模式,主要是将机房设备、遥控平台以及各个播报平台的功率、开关、功能进行整合和组合管控,结合发射机的主设备、备用设备,以及频率发射机主设备、备用设备,做好集中控制、精细化管理。

1 中波发射台自动化播控模式1.1 集中控制管理集中控制管理模式较为常见,其整体结构较为简单,在对整体架构打造过程中投入的资金相对较少,主要由播控平台采取集中管理控制,实现对发射设备的体系化、精细化把控。

现阶段,在生产管理过程中,中波发射机还未实现自动化运作,中波发射台自动化改造大多采取集中管理控制的方式,高度依赖机房监控管理系统,一旦监控平台出现相应的故障隐患,如服务器崩塌等,则会导致机房所有播控设备的运作受到影响,以至于整个播控系统无法发挥出实际的价值和作用,出现停播、停机的情况。

集中控制管理模式具备独特的优势和劣势,须对症下药,完成对整个控制系统的精细化管控[1]。

1.2 分散控制管理分散控制管理结构相对复杂,但是其安全性、可靠性、稳定性相对较高,主要是将各频率发射机在同一播控平台上协同、互动使用,不同频率发射机在运行过程中不会相互关联。

因此,在发射机设备出现故障问题后不会相互影响,可保证整个系统结构的稳定性、牢固性,前期会投入大量的资源完成对不同频率发射机设备的采购、布控。

整个监控平台较为宽广,后续的维护工作量也相对较大,很难在分散控制管理模式下开展标准化的设备管控工作。

因此,针对部分实力相对较为强劲的中波发射台,可以采取分散控制的策略,保证整个系统的运行水平得到有效提升,但是也需要在该环节制定更加科学合理的运维管理计划和方案,发挥整个系统的自动化价值。

4G网络发展趋势

4G技术发展趋势分析(一)中国通信网时间:2008-04-22信息来源:业界关于下一代移动通信网络技术的叫法很多,4G只是一个通用的名称,除此之外,还有B3G、BeyondIMT-2000、IMT-Advanced技术等名称。

不同组织在对4G技术的设想上存在着很大的差异。

ITU统一4G概念此前,世界很多组织给4G下了不同的定义,而ITU代表了传统移动蜂窝运营商对4G的看法,认为4G是基于IP协议的高速蜂窝移动网,现有的各种无线通信技术从现有3G演进,并在3GLTE阶段完成标准统一。

ITU4G要求传输速率比现有网络高1000倍,达到100Mbit/s。

在2005年10月的ITU-RWP8F第17次会议上,ITU给了4G技术一个正式的名称IMT-Advanced。

按照ITU的定义,当前的WCDMA、HSDPA等技术统称为IMT-2000技术;未来的新的空中接口技术,叫做IMT-Advanced技术。

IMT-Advanced标准继续依赖3G标准组织已发展的多项新定标准加以延伸,如IP核心网、开放业务架构及IPv6。

同时,其规划又必须满足整体系统架构能够由3G系统演进到未来4G架构的需求。

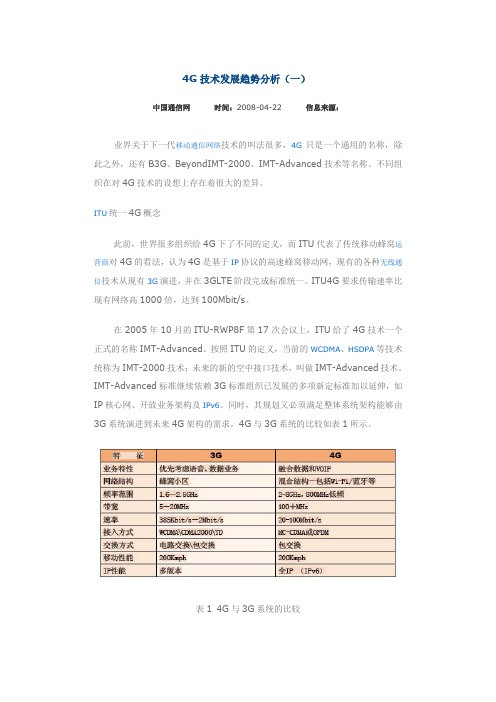

4G与3G系统的比较如表1所示。

表1 4G与3G系统的比较总之,4G是3G技术的进一步演化,是在传统通信网络和技术的基础上不断提高无线通信的网络效率和功能。

同时,它包含的不仅仅是一项技术,而是多种技术的融合。

不仅仅包括传统移动通信领域的技术,还包括宽带无线接入领域的新技术及广播电视领域的技术。

4G核心技术4G通信系统的这些特点,决定了它将采用一些不同于3G的技术。

对于4G 中将使用的核心技术,业界并没有太大的分歧。

总结起来,有以下几种。

1.正交频分复用(OFDM)技术OFDM是一种无线环境下的高速传输技术,其主要思想就是在频域内将给定信道分成许多正交子信道,在每个子信道上使用一个子载波进行调制,各子载波并行传输。

尽管总的信道是非平坦的,即具有频率选择性,但是每个子信道是相对平坦的,在每个子信道上进行的是窄带传输,信号带宽小于信道的相应带宽。

无线电测向的经济效益与投资回报率

无线电测向的经济效益与投资回报率无线电测向,这个听起来有些专业和神秘的词汇,其实在我们的日常生活和众多领域中都发挥着重要的作用,并且带来了显著的经济效益和可观的投资回报率。

首先,让我们来了解一下什么是无线电测向。

简单来说,它是通过测量无线电信号的方向和强度,来确定发射源位置的一种技术。

这项技术在军事、通信、导航、救援等领域都有着广泛的应用。

在军事领域,无线电测向是一项至关重要的技术。

它可以帮助军队准确地定位敌方的通信设备、雷达站等,从而获取情报、干扰敌方通信或者进行精确打击。

这对于提高军队的作战能力、保障国家安全具有不可估量的价值。

从经济效益的角度来看,成功的军事行动可以避免战争的长期拖延,减少人员伤亡和财产损失。

同时,强大的军事能力也为国家在国际事务中赢得更多的话语权和战略利益。

在通信领域,无线电测向有助于优化通信网络的覆盖和性能。

通过对信号源的定位,可以发现信号盲区和干扰源,从而有针对性地调整基站的布局和参数设置,提高通信质量和用户体验。

这不仅能够增加通信运营商的用户满意度和忠诚度,还能吸引更多的用户,进而带来更多的收入。

而且,高效的通信网络对于推动数字化经济的发展、促进信息流通和商业活动也具有重要意义。

在导航领域,无线电测向技术可以与卫星导航系统相结合,提供更精确和可靠的定位服务。

在城市峡谷、隧道等卫星信号较弱的环境中,无线电测向能够弥补卫星导航的不足,确保导航的连续性和准确性。

这对于交通运输、物流配送等行业来说,可以提高运输效率、降低成本、减少交通事故。

例如,物流企业能够更准确地规划路线,及时送达货物,提高客户满意度,从而在市场竞争中占据优势。

在救援行动中,无线电测向更是发挥着关键作用。

当遇到自然灾害、人员走失等紧急情况时,救援人员可以通过无线电测向设备快速定位被困人员的手机、对讲机等设备的信号,大大提高救援的效率和成功率。

每一次成功的救援都意味着拯救生命、减少损失,这是无法用金钱来衡量的巨大社会效益。

机房调研报告(五篇)

机房调研报告(五篇)第一篇:机房调研报告关于中国电信广东机房的调查报告一、广东电信机房概况广东电信自2000年开始经营idc业务,共有44个idc机房,遍布全省21个地市,形成了以广州、深圳为第一梯队,东莞、佛山、汕头、湛江为第二梯队,其余地市为边缘节点的总体机房布局。

其中包括五星级机房4个、四星级机房10个。

目前全省共有标准机架16000多个。

目前全省idc总出口带宽为1800g,保证每月的网络连通性在99.5%以上。

二、机房具体分布其中东莞电信和佛山电信机房被推荐为2012年全国六大最佳高防服务器机房。

三、顺德机房概况四、客户群分析1、以佛山、广州、东莞、深圳为例,按行业统计分析。

2、广东电信机房在广东各地区的托管、租赁情况。

3、广东电信机房在全国各省的托管、租赁情况。

五、电信机房优势与风险分析1、广东电信处于竞争主导地位广东电信idc机房覆盖全省,拥有三大旗舰级数据中心及九大电信级数据中心(佛山机房是其一)。

广东市场上活跃着一些灵活的专业idc服务提供商,如润迅、网宿等,但广东电信idc市场份额在本地占绝对优势。

目前,广东电信在广东地区的市场份额约为70%。

2、与其他服务商关系广东运营商和其他服务商之间处于互补又竞争的状态。

从细分业务上来看,专业服务商侧重于发展增值业务,而把主机托管等业务作为增值业务的基础来发展。

从客户群来看,电信运营商侧重于大客户,专业idc服务商主要面向中小客户。

3、国外潜在竞争者国际idc公司看准了中国市场的前景,纷纷加入竞争,但受限于政策因素,它们需要设计出别样的策略,向某些客户的独特需求投其所好,才能进入国内idc市场。

4、增长值服务不完善在idc业务构成上,广东电信仍然停留在idc的基础业务上,主机托管、租用占绝大部分比例,约90%,而增值业务比例很低,其中代维服务、负载均衡、数据存储备份、网络安全服务各占1%左右。

随着网游、电子商务平台、物流等行业的诞生,电信在增值服务等细分市场上并不太具有影响力。

MIMO系统信号检测算法研究的开题报告

MIMO系统信号检测算法研究的开题报告一、研究背景和目的:随着移动通信和无线电通信的不断发展,MIMO技术逐渐成为核心技术。

MIMO(Multiple-Input Multiple-Output)系统是一种利用多个天线发射和接收信号的技术,具有较高的频谱效率和抗干扰能力。

因此,在许多现代通信系统中,MIMO技术已经被广泛应用。

然而,由于信号传播路径上存在多径衰落、噪声干扰等问题,信号检测算法的复杂度较高。

如何提高MIMO系统的性能和减少信号检测算法的复杂度是本次研究的主要目的。

二、研究内容:1. MIMO系统基础知识:介绍MIMO技术原理和传输过程中存在的问题。

2. 信号检测算法综述:对目前主流的信号检测算法,如线性检测、扩展卡尔曼滤波、贪心迭代、逐步检测等进行综述。

3. 分类最大似然估计(ML)算法研究:基于前期的信号检测算法综述,详细分析分类ML算法的原理和步骤。

并利用Matlab软件进行仿真实验,对分类ML算法的性能进行实验验证。

4. 基于贪心迭代算法的改进:提出一种基于贪心迭代算法的改进方法,以减少算法的复杂度,并对改进后的算法进行仿真实验。

5. MIMO系统性能实验研究:对比分析不同信号检测算法的性能,利用FPGA实现硬件加速,进一步探究信号检测算法的硬件优化措施。

三、研究意义:本次研究将探究MIMO 系统信号检测算法的性能和复杂度问题,提高MIMO系统的通信质量和信号检测速度,从而推进MIMO技术的发展,为未来5G移动通信系统的提供技术保障。

四、研究方法:本次研究将主要采用文献调研和实验模拟两种方法,对MIMO系统信号检测算法进行研究。

在实验模拟中,采用Matlab软件对算法进行仿真实验,并利用FPGA进行硬件优化加速。

五、预期成果:通过本次研究,预期达到以下2个方面的成果:(1)提出一种基于贪心迭代算法的改进方法,以减少算法的复杂度,并通过仿真实验验证性能;(2)对比分析不同信号检测算法的性能,探究MIMO技术的硬件优化措施。

2024年江苏省软科学研究计划拟立项目清单

一、市场调研

1.溯源型供应链管理系统,研究软件落地与前瞻性开发;

2.基于智能技术的智能物流网络;

3.移动智能技术在公共安全管理应用研究;

4.彩票中心管理系统的优化技术研究;

5.银行流程自动化平台研究;

6.基于RFID技术的车辆定位监控系统研究;

7.消费者行为分析与营销管理的软件系统研究;

8.车联网的软件系统研究;

9.安全容量优化与容灾管理技术研究;

10.企业资源规划ERP的软件系统研究;

11.信息安全策略研究与实施;

12.智能武器系统软件研究。

二、技术研究

13.软件定义射频网络系统研究;

14.可视化技术在智能移动端应用研究;

15.无线自组网技术研究;

16.无线电规则研究;

17.物联网技术应用研究;

18.多路复用技术研究;

19.虚拟仿真技术在软件开发中的应用研究;

20.基于智能算法的计算能力技术研究;

21.嵌入式智能软件技术研究;

22.移动智能技术在电子商务应用研究;

23.高维数据挖掘技术研究;

24.云计算及大数据应用研究;

25.基。

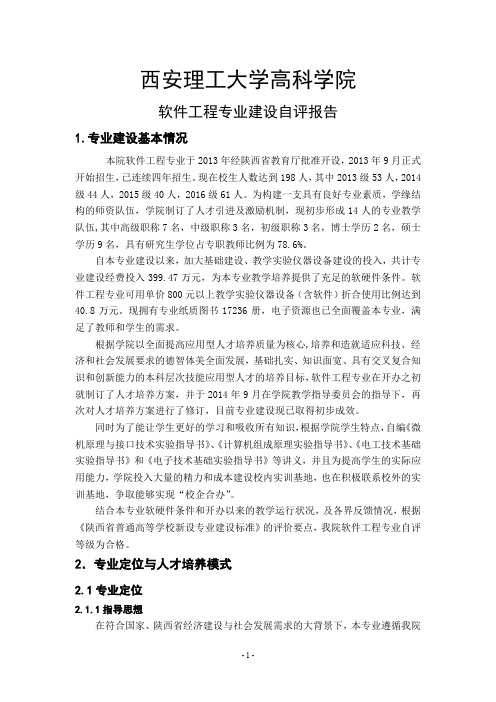

西安理工大学高科学院

西安理工大学高科学院软件工程专业建设自评报告1.专业建设基本情况本院软件工程专业于2013年经陕西省教育厅批准开设,2013年9月正式开始招生,已连续四年招生。

现在校生人数达到198人,其中2013级53人,2014级44人,2015级40人,2016级61人。

为构建一支具有良好专业素质,学缘结构的师资队伍,学院制订了人才引进及激励机制,现初步形成14人的专业教学队伍,其中高级职称7名,中级职称3名,初级职称3名,博士学历2名,硕士学历9名,具有研究生学位占专职教师比例为78.6%。

自本专业建设以来,加大基础建设、教学实验仪器设备建设的投入,共计专业建设经费投入399.47万元,为本专业教学培养提供了充足的软硬件条件。

软件工程专业可用单价800元以上教学实验仪器设备(含软件)折合使用比例达到40.8万元。

现拥有专业纸质图书17236册,电子资源也已全面覆盖本专业,满足了教师和学生的需求。

根据学院以全面提高应用型人才培养质量为核心,培养和造就适应科技、经济和社会发展要求的德智体美全面发展,基础扎实、知识面宽、具有交叉复合知识和创新能力的本科层次技能应用型人才的培养目标,软件工程专业在开办之初就制订了人才培养方案,并于2014年9月在学院教学指导委员会的指导下,再次对人才培养方案进行了修订,目前专业建设现已取得初步成效。

同时为了能让学生更好的学习和吸收所有知识,根据学院学生特点,自编《微机原理与接口技术实验指导书》、《计算机组成原理实验指导书》、《电工技术基础实验指导书》和《电子技术基础实验指导书》等讲义,并且为提高学生的实际应用能力,学院投入大量的精力和成本建设校内实训基地,也在积极联系校外的实训基地,争取能够实现“校企合办”。

结合本专业软硬件条件和开办以来的教学运行状况,及各界反馈情况,根据《陕西省普通高等学校新设专业建设标准》的评价要点,我院软件工程专业自评等级为合格。

2.专业定位与人才培养模式2.1专业定位2.1.1指导思想在符合国家、陕西省经济建设与社会发展需求的大背景下,本专业遵循我院“十三五”发展规划、中期专业建设与发展规划中的教学理念和教学管理模式进行教育教学,面向西北地区区域性的软件服务业,坚持以社会需求为导向,从应用型本科人才定位入手,建设有特色的人才培养模式,着力培养学生的工程实践能力和就业创业能力,努力不断提升专业实力和水平,不断提高服务经济社会的能力。

通信调研报告

通信调研报告

《通信调研报告》

在当今时代,通信技术日新月异,成为了人们生活中必不可少的一部分。

为了更好地了解当前通信技术的发展现状和未来趋势,我们进行了一项通信调研报告。

首先,我们调研了目前主流的通信技术,包括移动通信、互联网通信、卫星通信等。

通过对这些技术的发展历程和应用场景进行了解,我们发现移动通信技术的快速发展带来了人们生活的便利,互联网通信的普及促进了信息的传播与交流,卫星通信的广泛应用改变了人们对通信的认识。

其次,我们还对通信技术的未来发展趋势进行了分析。

在人工智能、大数据等领域的快速发展推动下,通信技术也将迎来新的突破和创新。

未来,5G技术将成为通信领域的主导技术,5G时代的到来将给人们带来更快的网络速度、更稳定的连接以及更多元化的应用。

最后,我们对通信技术的应用场景进行了探讨。

通信技术的快速发展不仅改变了人们的生活方式,也为各个行业带来了新的机遇和挑战。

在医疗、教育、金融等行业中,通信技术的应用已经成为了不可或缺的一部分。

未来,随着物联网、智能设备等概念的发展,通信技术的应用场景将继续扩大并深入到人们的生活中的方方面面。

通过这次通信调研报告,我们对通信技术的发展现状和未来发

展趋势有了更清晰的认识。

我们相信,在不久的将来,通信技术将继续推动人类社会的进步和发展。

基于软件无线电的通信系统平台研究和实现

信息职业技术学院教科研课题任务书课题名称:基于软件无线电的通信系统平台研究与实现课题负责人:智群联系电话:电子邮箱:ccgjzzq126.课题起止时间:2005年09月至2008年08月信息职业技术学院二○○五年一、为顺利完成本课题的研究开发任务,信息职业技术学院(以下简称甲方)与课题承担者(以下简称乙方)经协商一致,订立本合同。

三、本课题的成果提供形式以及达到的技术、经济指标四、本课题研究实施计划(工作具体安排、阶段实施计划、课题进度分工方案)五、参加本课题研究开发的单位和人员承担部门:电子工程系合作单位:主要研究开发人员六、本课题研究启动经费。

课题立项后,甲方拨给乙方元作为课题启动经费。

七、本课题的设备、软件投入经费预算(说明:开发设备应尽量使用学院现有的设备或04年度已计划购进的设备进行开发。

如确需购置新的设备及软件,请填写下表,并根据开发进八、课题的鉴定验收乙方在本课题任务合同完成期限时,应提交供鉴定验收的成果、完整技术资料和总结,甲方根据本合同约定容组织鉴定验收。

并参考课题立项时的等级和结题后的课题成果进行重新评比,评出学院年度教科研成果A、B、C、D类四个等级,确定并划拨相应课题经费(含启动经费)。

(科研类:A类6000元、B类4000元、C类3000元;教研教改类:A类3000元、B类2000元、C类1000元;课件类:A类4000~6000元、B类2000~3000元、C类500~1000元。

被评为D类的不给予课题经费。

)九、成果的权属和本课题研究取得的技术成果,其知识产权归属及成果转化,按国家和本省的有关规定执行。

上述技术成果涉及国家利益的,乙方有偿转让之前,应经过甲方的审查批准;涉及国家的,按国家《法》有关规定执行。

十、风险的承担研究开发过程中,因发生不可抗力、因本课题研究的技术已由他人公开或确因现有水平和条件难以克服的技术困难,致使研究开发工作成为不必要或不可能,乙方应提出书面报告(若属于难以克服的技术困难,应附上有关专家的书面认定意见),甲方经核实后提出处理意见。

《智能产品开发》专业调研报告

智能产品开发专业调研报告一、开设专业的必要性(一)是电子信息产业快速发展的必然需要在全球电子信息产业飞速发展的大背景下,我国电子信息产业将继续保持快速发展趋势,以大数据、云计算、物联网为核心派生出新兴领域的快速发展亦为我国电子信息产业创造新需求,预计“十三五”期间将保持25%以上的增长率,到2020年中国电子信息产业市场规模将达到20.39万亿元。

产业的发展必然带来对人才需求的增长,电子信息类人才成为高新技术企业争夺的要点,尤其是智能产品开发、微电子、通信工程、无线电技术、电气工程及自动化、电子信息工程等大部分理工科专业的人才需求,且呈持续上升势态。

根据调研,目前我省智能产品开发类相关企业,都存在着安装、调试、维护人员严重不足,因此,智能产品开发专业的设置与发展是电子信息产业快速发展的必然需要。

(二)是企业实现全面发展的必然需要不管是大型跨国公司还是小而专的智能产品开发商,电子信息制造业智能产品开发类企业都在轮番进行全国性的大规模人才招聘工作。

在企业中不仅急需行业领军人物,缺乏既懂技术又擅长管理的复合型人才,还存在高技能人才普遍短缺,人才流失严重现象。

提升从事智能电子产品辅助开发、生产管理、调试和服务等第一线工作的高素质劳动者和技术技能人才是企业实现全面发展的必然需要。

二、人才供求分析(一)人才供应分析辽宁省高职高专院校只有大连装备职业技术学院开设了本专业,这与辽宁省各企业所产生的对本专业的人才需求很不相称。

纵观全国高职高专院校,智能产品开发专业开设数量也不多。

因此,该专业学生的就业前景非常广阔,开设此专业将有利于推动辽宁乃至全国电子信息制造行业的发展。

(二)人才需求分析当整个I T行业的发展已经进入第三个十年的时候,物联网、云计算、智能产品开发俨然已成为信息产业的主旋律,不管从政府大力扶持的力度来看,还是从产业变革的主流方向来说,这股潮流早已势不可挡,而嵌入式智能产品开发正是这些产业应用计算机技术中最核心、最关键的部分,正因为如此,随着嵌入式智能产品开发技术在整个信息产业的广泛应用和高速发展,I T行业的发展也势不可挡地进入了嵌入式智能产品开发时代。

关于4G移动通信技术的调研报告

关于4G移动通信技术的调研报告前言:移动通信已成为当代通信领域内的发展潜力最大、市场前景最广的热点技术。

尽管第三代移动通信(3G)标准比现有无线技术更强大,但也将面临竞争和标准不兼容等问题。

人们开始呼吁移动通信标准的统一,以期通过第四代移动通信标准的制定来解决兼容问题。

第四代移动通信与第三代移动通信相比,将在技术和应用上有质的飞跃。

4G将适合所有的移动通信用户,最终实现商业无线网络、局域网、蓝牙、广播、电视卫星通信的无缝衔接并相互兼容。

一、4G简述4G是指集3G与WLAN于一体,并能够传输高质量视频图像,它的图像传输质量与高清晰度电视不相上下。

4G系统能够以100Mbps的速度下载,比目前的ADSL快200倍,比通常意义上的3G快50倍,上传的速度也能达到20Mbps,并能够满足几乎所有用户对于无线服务的要求。

而在用户最为关注的价格方面,4G与固定宽带网络在价格方面不相上下,而且计费方式更加灵活机动,用户完全可以根据自身的需求确定所需的服务。

此外,4G可以在DSL和有线电视调制解调器没有覆盖的地方部署,然后再扩展到整个地区。

国际电信联盟(ITU)目前已开始研究制定4G系统标准,把移动通信系统同其他系统(如无限局域网,WLAN)结合起来,产生4G技术,2010年前使数据传输速率达到100Mbit/s。

提供更有效的多种业务,实现商业无线网络、局域网、蓝牙、广播、电视卫星通信等的无缝衔接并相互兼容。

4G具有更高的数据率和频谱利用率,更高的安全性、智能性和灵活性,更高的传输质量和服务质量(QoS)。

4G系统应体现移动与无线接入网及IP网络不断融合的发展趋势。

因此4G系统应当是一个全IP的网络。

二、4G的技术特点4G是多功能集成宽带移动通信系统,比3G更接近于个人通信。

其特点主要有:1.高速率4G的信息传输速率要比3G高一个等级,从2Mbit/s提高到10Mbit/s。

2.灵活性强4G拟采用智能技术,可自适应地进行资源分配。

基于软件无线电的调频广播接收机设计的开题报告

基于软件无线电的调频广播接收机设计的开题报告一、选题背景随着科技的发展,软件无线电技术已经越来越被广泛应用。

调频广播接收机是现代通信中广泛应用的一种接收机,它可以接收0.1 MHz到1.8 GHz范围内的广播信号。

目前许多传统的调频广播接收机存在着一些局限,例如:价格较高、占用空间大、功能单一等等。

为了满足现代人对于调频广播接收机更高的要求,软件无线电技术应运而生。

通过利用软件无线电技术,可以大大降低调频广播接收机的成本,同时还可以使其体积更小、功能更强大。

因此,本课题选取了基于软件无线电的调频广播接收机设计,实现低成本、小体积、多功能的调频广播接收,并探究其实现方法和技术路线,为现代调频广播接收机技术的发展做出一定的贡献。

二、设计目标本课题旨在设计一款基于软件无线电技术的调频广播接收机,实现以下目标:1. 实现调频广播信号的接收和解码,并将信号转换为可播放的格式。

2. 实现对接收到的调频广播信号的解码和分析,从而实现对信号的多种操作,例如调频广播的解码和录音等。

3. 实现对接收信号的分析和显示,例如对主要信号的频谱显示,以及探测和分析调频广播信号。

4. 确保系统低功耗、低成本、小体积,以便于移动。

三、设计内容本课题主要研究内容包括以下方面:1. 调频广播接收机原理研究:调频广播接收机的原理及其适用范围,幅度调制和频率调制的区别,锁相环(PLL)的应用。

2. 软件无线电技术研究:SDR技术的基本原理,数字信号处理技术的应用,软件无线电的实现方法和技术路线。

3. 调频广播信号解调技术研究:调频广播信号的解码和录音技术、信号的分析和显示等技术。

4.硬件设计:根据软件无线电技术和调频广播接收机的原理以及目标需求,选取合适的芯片、模块和外设等,进行硬件设计与开发。

总之,本课题将会着重解决如何通过软件无线电技术实现调频广播接收机原理、相应技术及应用等方面的问题,同时还会对相应的硬件平台设计、软件平台架构等方面进行研究与探究。

高校通信实验室建设总体方案

源。仪器名称

型号

数

量

建议供应商

单

价

备注

现代通信原

理

综合实验系

统

ZH7001

40

南京哲华科技

有限公司

方案一

现代通信原

理

综合实验箱

ZH7001

(II)

40

南京哲华科技

有限公司

方案二

双踪示波器

40

20MHz

具有X-Y功

能

函数信号发

40

具有频率计

生器

数功能

误码测试仪

20

南京哲华科技

有限公司

ZH9001(可

正规,学校通过与这些设备供应商联系,一般可以得到较好

的售前和售后服务。

为了保障学校的利益,学校应多进行调研,以便获取更好

的教学设备。因为也有不少厂家的产品技术含量较低,但为

了改善其对外形象,一方面通过不正当的手段仿冒其它公司

产品,另一方面将其它公司产品纳入自己名下生产(通常所

说的贴牌),以提高自身的规模与身价。同时还不断对外许

选)

频谱分析仪

1

可选

(3)综合设计实验室(40人)

错误!未找

到引用源。

设备、错误!

未找到引用

源。仪器名称

型号

数

量

建议供应商

单价

备注

综合设计实

验箱

ZH700

6

20

南京哲华科技

有限公司

方案一

综合设计实

验箱

ZH700

6

20

南京哲华科技

有限公司

方案二

双踪示波器

20

20MHz

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

软件定义的无线电(Software Defined Radio,SDR)是一种无线电广播通信技术,它基于软件定义的无线通信协议而非通过硬连线实现。

频带、空中接口协议和功能可通过软件下载和更新来升级,而不用完全更换硬件。

主要应用:通信类,如5G通信原型机的搭建及现场试验,基站通信试部署,毫米波回传网络,大规模MIMO数字和模拟信号处理系统等高性能无线通信科研领域。

军用航空航天及对抗防卫类,如高带宽军用通信原型系统、先进的雷达信号处理、电子对抗和详细的频谱情报分析。

科研类,如嵌入式高性能计算和蜂窝通信的研究。

国外平台:WARPWARP v3 is the latest generation of WARP hardware, integrating a high performance FPGA, two flexible RF interfaces and multiple peripherals to facilitate rapid prototyping of custom wireless designs.Hardware FeaturesThe hardware features of WARP v3 are listed below. For full details please see the WARP v3 UserUSRP架构采用AD9364+FPGA主要特点高度集成,射频范围从70 MHz–6 GHz支持最大实时带宽56MHz,61.44MS/s的基准采样率支持高速的USB 3.0连接10 MHz参考或PPS同步触发5.0cm x 8.4cm尺寸开源的UHD支持多种框架用户可编写的Spartan 6 XC6SLX75 FPGAGPIO通用接口和JTAG调试能力需要UHD3.9.0或者更新的驱动版本支持支持GNU Radio开源软件框架BEECUBEBEE3源自于最初的伯克利仿真引擎(BEE),是基于计算机系统的第三代商用FPGA。

该系统由微软研究所、UC伯克利以及BEEcube公司联合开发,其设计基于前几代的系统,以及著名计算机设计师和图灵奖获得者Chuck Thacker(BEE3的主要设计者)40多年的设计经验。

利用先进的Xilinx 65nm FPGA系列,每个2U机架安装BEE3模块包括四个大的Virtex 5 LXT/SXT/FXT FPGA芯片,以及高达64GB 的DDR2 ECC DRAM和八个用于模块间通信的10GigE接口。

另外,多达4个PCI Express x8的连接允许每个BEE3模块和计算机主服务器之间进行每秒高达16GB、全双工的数据通信。

每个BEE3模块消耗小于400瓦的功率,就可以提供每秒四百万兆的整数操作,或者在64个RISC处理器核进行速率为100MHz的同时仿真。

BEE3系统已在世界众多领先大学和领先的商业公司得以应用。

大学如伯克利加利福尼亚大学、斯坦福大学、麻省理工学院、伦敦帝国理工学院、巴塞罗那超级计算机中心、东京大学、加拿大女王大学。

公司包括有微软公司和Sun微系统公司。

先进的Xilinx Virtex-5 FPGA:四个LX155T/SX95T FPGA高于400MHz的时钟速率5M门容量2560 DSP slice可扩展集群解决方案可从单个模块扩展到1024个模块每个机架有16~20个模块每个机架消耗的功率小于5千瓦每个机架超过1TB的DRAM灵活的系统综合利用USB、以太网和PCI Express的多个主计算机接口利用USB或以太网的远端系统管理支持Windows和Linux计算机系统对于客户的业务,与MATLAB和本土C API直接合成每个FPGA提供:双通道DDR2-400/533/667 RDIMMs,每个通道两个DIMM每个DIMM的最大容量为4GB,每个FPGA的最大总容量为16GB两个10GBase-CX4以太网接口单个PCI-Express x8端点时隙40对直接LVDS高速连接到外部的GHz模拟转换器设备,如ADC和DAC三态10/100/1000以太网(RJ45)IIC总线上的RTC/EEPROM利用USB的RS232串口连接到外部安全数字(SD)卡的SPI接口OctasicVocallo BTS 数字信号处理器(DSP)集成了完整的第一层(L1)基带,支持最多12 个GSM 载波,或者6 个EDGE 载波,或是其它组合。

所有这些都被安装在15mm x 15mm 的球珊阵列(BGA)组件上,功耗不到1W(即每个载波80mW)。

而这令人震撼的功率密度指数直接得益于Octasic 公司的异步DSP 核--Opus。

由于不存在时钟树,缩小了芯片尺寸。

这样就使VocalloBTS 可以为每个载波提供非常有竞争力的价格。

OCT2224W ,包括 24 个可编程的高性能 Opus2 DSP 核心。

这种相同的构架有助于简化应用分区,并且支持粗粒度并行化,同时它还具备高度可编程硬件加速器,不仅支持当前的蜂窝标准,而且还具备出色的灵活性以支持未来的修订标准。

OCT2224W 芯片采用了一套丰富的I/O接口和一个可选的 ARM 内核。

该芯片为各种规模的基站和所有空中接口提供了一个理想平台,包括面向农村地区的低功耗基站、宏基站、户外小蜂窝基站以及室内高流量的企业femtocell飞蜂窝。

Octasic 公司使用的 PHY 软件库可提供符合标准的 GSM、EDGE、WCDMA、HSPA+ 和LTE功能。

例如,一个 OCT2224W 芯片可执行一个完整的多标准picocell微微蜂窝,其可在一个硬件平台上提供 LTE、WiMAX、HSPA、EDGE 或其它商用无线标准。

面向无线的 OCT2224W 特性包括:24 个 Opus2 DSP内核, 能够在一个芯片上支持多达 64 个 HSPA+ 或 LTE 用户。

可为 MIMO 与同步空中接口提供最多 3 个本地无线接口串行快速 IO (Serial Rapid IO)、千兆以太网、USB接口、PCIe、 NAND 和 TDM 集成安全特性多个射频时钟同步选项可选的 ARM 处理器,可用于小型蜂窝基站灵活的框架支持定制的专有算法可编程平台为 Evolved EDGE、WiMAX 802.16m 和 LTE Advanced的未来演进提供方便的移植途径。

SFF SDR产品亮点:·属于业内体积最小的SDR平台,体积小,功能完备且独立,方便易携带;·无缝的软硬件集成开发流程,具备从射频(RF)到基带的完整的处理功能;·每一个处理器都配备有嵌入的、独立的功率监测系统;·支持基于模型的开发工具(MATLAB/Simulink,System Generator),加速原型验证过程;·具有集成的故障检修、硬件在回路、以及协同验证功能;·平台上集成了GPP、DSP和FPGA,方便实现一个完整的、无线电系统的所有协议层;重要特征:·TI TMS320DM6446 DSP片上系统/C64x+ DSP核,594MHz/ARM926核,297MHz/丰富的外围设备,包括串口,USB,EMAC,DDR2 EMIF,以及视频端口;·Xilinx Virtex-4 SX35 FPGA芯片·TI ADS5500, 125-MSPS, 14-bit双通道模数转换器·TI DAC5687, 500-MSPS, 16-bit双通道模数转换器·带宽选择(5MHz或者20MHz)·模块化组件:可以组装其它板卡·RF模块的工作频带:360MHz和960MHz·支持增加第二个RF模块,用于全双工模式操作,或者覆盖附加的频带·以太网远程接入功能应用领域:·军事军事通信手持和背负式系统车载系统·公共安全公共安全无线电设备军事通信手持和背负式系统车载系统发射机应答器多标准、多频带终端车载系统·商用宽带数据系统蜂窝手持移动电话无线电频率识别(RFID)Pico, femto基站认知无线电技术(Cognitive Radio)WiMAX, Wi-Fi接入点SFF SDR 开发平台提供从天线到基带处理的完整信号链。

可以用这套系统为军事、公安和商业应用创建单协议或多协议无线电手持设备。

这套系统还可用作快速原型设计和测试平台。

另外,该平台为了与 The MathWorks 的 Simulink 基于模型的设计 (MBD) 工具一起使用而进行了集成,所以可以选择使用 C/HDL 或 MATLAB Simulink 快速测试概念验证设计以及对架构进行成本和功耗优化。

与市场上其他 SDR 开发产品不同,SDR 开发平台是软硬件共同开发环境,可为多协议 SDR 设备提供全套构件,包括 RF 前端模块、模数及数模数据转换模块和数字处理模块。

通过将基带、IF 和 RF 分割成分立模块而非采用单一混合架构。

基带模块具有一个 Xilinx Virtex-4 SX35 FPGA 和一个 TI TMS320DM6446 芯片。

TI 芯片包含一个 TMS320CC64x+ DSP 内核和一个 ARM9 通用处理器内核。

SDR 开发平台具有一个独特的功耗测量 API。

此 API 可测量 FPGA、DSP 和 ARM 的加载并报告实时功耗数据。

其他还有Pluto sdr limesdr picozed sdr国内平台威瑞视YunSDR系列:基于SoC的嵌入式SDR平台。

YunSDR是一系列专为无线通信系统科研和教学实验而开发的一款高性价比的便携式软件无线电平台。

实现了频谱范围70MHz~6GHz,模拟带宽200KHz~56MHz的宽频段软件无线电系统,可以支持PC 模式的软件无线电架构,也可以脱离PC,实现嵌入式的软件无线电架构。

板卡技术指标:无线通信协议栈太速科技基于FMC接口的Kintex-7 XC7K325T PCIeX8 3U PXIe接口卡FMC上接高速AD DA子卡支持windows linux驱动64bit DDR3 容量2Gbyte支持1路PCIE X8 支持PCI Express V1.1 V2.0标准前锋科技采集子卡(FMC)+数据处理模块的架构QF67660 FMC 1Gsps采集子卡,符合VITA57.1 HPC标准。

4通道ADC支持内、外时钟参考,支持内、外触发模式。

量化位数16bit采样率1Gsps模拟输入阻抗单端50Ω耦合方式交流耦合SNR ≥68dBFS@170MHz, 1Gsps和-1dBFSSFDR ≥85dBFS@170MHz, 1Gsps和-1dBFS最大输入信号功率5dBm通道间延时≤65ps同步误差≤20nsQF67630 PCIe四通道数据处理模块基于Kintex 7FPGA平台下16bit量化位采集处理产品,支持内、外时钟、板载锁相环,可产生(30~250)Msps任意采样率。