7 创龙TMS320C665x基于广州创龙编写的RTSC组件的例程使用手册

1-2-TI TMS320C6655创龙开发板硬件说明书2

TMS320C6655(TL665x-EasyEVM)创龙开发板硬件说明书2 TMS320C6655(TL665x-EasyEVM)是创龙基于SOM-TL665x核心板研发的一款TI C66 x多核定点/浮点高性能DSP创龙开发板,采用核心板+底板方式,底板尺寸为200mm*1 06.65mm,采用4*50pin和1*80pin B2B工业级连接器,稳定、可靠、便捷,可以帮助客户快速评估核心板性能。

TMS320C6655(TL665x-EasyEVM)创龙开发板底板采用4层无铅沉金电路板设计,为了方便用户学习开发参考使用,上面引出了各种常见的接口。

共有2个系统复位按键(SW7:FULL RESET,SW5:WARM RESET),2个用户测试用按键(SW3:NMI,SW4:USER0),硬件及引脚定义如下创龙开发板图:9 TMS320C6655按键创龙开发板图19 FULL RESET创龙开发板图20 SW7创龙开发板图21 WARM RESET创龙开发板图22 SW5创龙开发板图23 USER创龙开发板图2410 TMS320C6655启动拨码开关SW2设有5位启动拨码开关,ON为1,硬件及引脚定义如下创龙开发板图:创龙开发板图25创龙开发板图2611 TMS320C6655 JTAG仿真器接口创龙开发板引出1个TI Rev B JTAG接口(CON4),间距为2.54mm,DC3-14P简易牛角座,硬件及引脚定义如下创龙开发板图:创龙开发板图27创龙开发板图2812 TMS320C6655 串口创龙开发板上共引出了2个串口,分别是CON1(UART1)、CON3(UART0)。

UART1通过MAX3232EUE串口电平转换芯片转换为RS232串口,使用DB9公座接口。

UART0则是使用CH340转成Micro USB接口,创龙开发板默认使用UART0进行调试。

硬件及引脚定义如下创龙开发板图:创龙开发板图29 UART1创龙开发板图30 创龙开发板CON1创龙开发板图31 创龙开发板UART0创龙开发板图32 创龙开发板CON3 13 TMS320C6655 千兆以太网口创龙开发板引出1个千兆意外网口(CON5),采用了Marvell Alaska 88E1112网络芯片,可自适应10/100/1000M网络,RJ45连接头内部已经包含了耦合线圈,因此不必另接网络变压器,使用普通的直连网线即可连接本创龙开发板至路由器或者交换机,若是PC和创龙开发板直接相连需要使用交叉网线。

AM5728创龙TL5728-EasyEVM开发板简介

Revision History

Draft Date 2018/09/07 2018/04/09 2017/12/25 2017/03/24 2016/08/16

Revision No. V1.5 V1.4 V1.3 V1.2 V1.0

Description

1. 修改电气特性参数。

1. 开发板版本更新为 A3。 1. 规格书文档内容勘误。 2. 修改电气特性参数。 1. 添加产品认证和开发例程。

Ethernet

2x RGMII,RJ45 接口,10/100/1000M 自适应

1x Micro USB 2.0 接口 USB

1x USB 3.0 接口

CAN

1x 3pin 3.81mm 绿色端子

1x UART3,Micro USB 接口,全双工模式

UART

1x RS232 串口(UART1),全双工模式

软件参数

ARM 端软件支持

表2 Linux-4.4.19,Linux-RT 4.9.65,TI-RTOS

DSP 端软件支持 TI-RTOS

CCS 版本号

CCS6.1.3

图形界面开发工具 Qt

双核通信组件支持 IPC

软件开发套件提供 Processor-SDK Linux、Processor-SDK Linux-RT、Processor-SDK TI-RTOS

1-1-TMS320C6655创龙开发板硬件说明书1

TMS320C6655(TL665x-EasyEVM)创龙开发板硬件说明书1TMS320C6655(TL665x-EasyEVM)是创龙基于SOM-TL665x核心板研发的一款TI C66 x多核定点/浮点高性能DSP创龙开发板,采用核心板+底板方式,底板尺寸为200mm*1 06.65mm,采用4*50pin和1*80pin B2B工业级连接器,稳定、可靠、便捷,可以帮助客户快速评估核心板性能。

SOM-TL665x核心板采用高密度沉金无铅工艺8层板设计,尺寸为80mm*58mm,采用TI KeyStone C66x多核定点/浮点DSP TMS320C665x高性能工业DSP处理器。

采用耐高温、体积小、精度高的B2B连接器,引出了核心板的全部接口资源,帮助开发者快速进行二次开发。

TMS320C6655(TL665x-EasyEVM)创龙开发板底板采用4层无铅沉金电路板设计,为了方便用户学习开发参考使用,上面引出了各种常见的接口。

1 TMS320C6655处理器TI TMS320C665x是一款高性能定点/浮点DSP处理器,主频高达1.0/1.25GHz,处理能力强,单核TMS320C6655和双核TMS320C6657管脚pin to pin兼容,拥有多种工业接口资源,以下是TMS320C665x CPU功能框创龙开发板图:创龙开发板图1创龙开发板图22 TMS320C6655 FLASH核心板上采用工业级NAND FLASH(128/256MByte),硬件如下创龙开发板图:创龙开发板图3核心板上采用工业级SPI NOR FLASH(64Mbit),硬件如下创龙开发板图:创龙开发板图43 TMS320C6655 RAMRAM采用工业级低功耗DDR3L,512M/1GByte可选,硬件如下创龙开发板图:创龙开发板图54 TMS320C6655温度传感器核心板上采用I2C接口的TMP102温度传感器,实现了系统温度的实时监测,测量误差≤2℃,测试温度为-40℃至125℃,硬件如下创龙开发板图:创龙开发板图65 TMS320C6655 EEPROM核心板上采用I2C接口1Mbit大小的工业级EEPROM,硬件如下创龙开发板图:创龙开发板图76 TMS320C6655 底板B2B连接器创龙开发板使用底板+核心板设计模式,底板共有5个B2B连接器。

TMS320C6678的EMIF16多核程序烧写的软件使用说明

TMS320C6678的EMIF16多核程序烧写的软件使用说明TMS320C6678的EMIF16多核程序烧写软件使用说明I目录1 概述 ........................................................................... .............................................................................. .. 5 1.1 范围............................................................................ ..............................................................................5 1.2 目的............................................................................ ..............................................................................5 1.3 设计依据 ........................................................................... ....................................................................... 5 1.4 背景............................................................................ ..............................................................................5 1.5 开发环境和运行环境 ........................................................................... ................................................... 5 2 任务概述 ........................................................................... ........................................................................ 5 3多核的待烧写工程说明 ........................................................................... ................................................ 6 3.1 core0待烧写工程说明 ........................................................................... ................................................. 6 3.1.1 工程文件说明 ........................................................................... ........................................................... 6 3.1.2 程序流程图 ........................................................................... ............................................................... 7 3.1.3 操作步骤 ........................................................................... ................................................................... 7 3.2 core1~core7待烧写工程说明 ........................................................................... ...................................... 8 4 EMIF16加载转换工具说明............................................................................ ......................................... 9 4.1 使用说明 ........................................................................... ....................................................................... 9 4.2 生成文件格式说明 ........................................................................... ....................................................... 9 4.2.1 core0的.dat文件的格式............................................................................ .......................................... 9 4.2.2 core1~core7的.dat文件的格式............................................................................ ............................. 10 5 烧写工程说明 ........................................................................... .............................................................. 10 5.1 工程文件说明 ........................................................................... ............................................................. 10 5.2 程序流程图 ........................................................................... ..................................................................11 6 Boot Mode设定 ........................................................................... ........................................................... 12 7 加载成功检验 ........................................................................... .. (13)II图表目录图1 TMS320C6678的EMIF16多核加载总体框图 ........................................................................... ................. 5 图2 core0待烧写程序的执行过程 ........................................................................... ............................................ 7 图3 core0的.dat文件格式 ........................................................................... ......................................................... 9 图4 core1~core7的.dat文件格式 ........................................................................... ............................................ 10 图5 core0代码烧写流程图 ........................................................................... (12)表1 八个核的代码在Flash中的空间分配 ........................................................................... ............................... 8 表2 烧写工程文件的函数说明 ........................................................................... ............................................... 11 表3 Boot Mode pins 定义 ........................................................................... .. (12)3符号和缩略词说明DSP:数字信号处理器(Digital Signal Processor) SPI:串行设备接口(Serial Peripheral Interface)EMIF16:外部存储器接口(External Memory Interface) DDR3:外部存储器 PLL:锁相环L2 SRAM:二级静态存储器IPC:核间通信(Interprocessor Communications)4TMS320C6678的EMIF16多核程序烧写软件使用说明1 概述1.1 范围本文档包括:TMS320C6678的EMIF16多核程序烧写软件使用说明。

TL665x-EasyEVM开发板规格书

1开发板简介基于TI KeyStone C66x多核定点/浮点DSP TMS320C665x,单核TMS320C6655和双核TMS320C6657管脚pin to pin兼容,同等频率下具有四倍于C64x+器件的乘累加能力; 主频1.0/1.25GHz,单核可高达40GMACS和20GFLOPS,包含2个Viterbi协处理器和1个Turbo协处理解码器,每核心32KByte L1P、32KByte L1D、1MByte L2,1MByte多核共享内存,8192个多用途硬件队列,支持DMA传输;可免装风扇,以最低的功率级别和成本提供最高的性能;支持PCIe、SRIO、HyperLink、uPP、EMIF16、千兆网口等多种高速接口,同时支持I2C、SPI、UART、McBSP等常见接口;连接稳定可靠,80mm*58mm,体积极小的C66x核心板,采用工业级高速B2B连接器,关键大数据接口使用高速连接器,保证信号完整性;提供丰富的开发例程,入门简单,支持裸机和SYS/BIOS操作系统。

图 1 开发板正面图图 2 开发板侧面图1图 3 开发板侧面图2图 4 开发板侧面图3图 5 开发板侧面图4TL665x-EasyEVM是一款基于广州创龙TI KeyStone C66x多核定点/浮点TMS320C665x 核心板SOM-TL665x设计的高端DSP开发板,底板采用沉金无铅工艺的4层板设计,它为用户提供了SOM-TL665x核心板的测试平台,用于快速评估SOM-TL665x核心板的整体性能。

SOM-TL665x引出CPU全部资源信号引脚,二次开发极其容易,客户只需要专注上层运用,降低了开发难度和时间成本,让产品快速上市,及时抢占市场先机。

不仅提供丰富的Demo程序,还提供DSP核间通信开发教程,全面的技术支持,协助客户进行底板设计和调试以及多核软件开发。

2典型运用领域✓数据采集处理显示系统Telecom Tower:远端射频单元(RRU)✓X 射线:行李扫描仪✓专业音频混合器✓军用和航空电子成像✓军用:军需品和目标应用✓军用:雷达/声纳✓军用:雷达/电子战✓打印机✓无线通信测试仪✓机器视觉:帧捕捉器✓机器视觉:摄像机✓条码扫描仪✓点钞机✓电信基带单元✓视频分析服务器✓软件无线电(SDR)✓高速数据采集和生成3软硬件参数硬件框图图 6 开发板硬件框图图7 开发板硬件资源图解1图8 开发板硬件资源图解24、硬件参数CPU单核TMS320C6655/双核TMS320C6657,主频1.0/1.25GHz ROM128/256MByte NAND FLASHRAM512M/1GByte DDR3EEPROM1MbitSENSOR 1x TMP102AIDRLT,核心板温度传感器,I2C接口B2B Connector 2x 50pin公座B2B,2x 50pin母座B2B,间距0.8mm,合高5.0mm;1x 80pin高速B2B连接器,间距0.5mm,合高5.0mm,共280pin,信号速率最高可达10GBaudLED2x供电指示灯(核心板1个,底板1个)5x用户指示灯(核心板2个,底板3个)KEY 2x复位按键,包含1个系统复位和1个软复位1x NMI按键1x用户按键SRIO1x SRIO,四端口四通道,每通道最高通信速率5GBaudPCIe1x PCIe Gen2,单端口双通道,每通道最高通信速率5GBaudHyperLink1x HyperLink,最高通信速率40GBaud,KeyStone处理器间互连的理想接口IO2x 25pin IDC3简易牛角座,间距2.54mm,含uPP、EMIF16拓展信号2x 25pin IDC3简易牛角座,间距2.54mm,含McBSP、SPI、TIMER、GPIO等拓展信号UART1x UART0,Micro USB接口,提供4针TTL电平测试端口1x UART1,DB9接口,提供6针TTL电平测试端口Ethernet 1x SGMII,RJ45接口,10/100/1000M自适应JTAG 1x 14pin TI Rev B JTAG接口,间距2.54mmFAN 1x FAN,12V供电,间距2.54mmBOOT SET 1x 5bit拨码开关SWITCH 1x电源开关POWER 1x 12V 2A直流输入DC417电源接口,外径4.4mm,内径1.65mm 备注:广州创龙SOM-TL6655、SOM-TL6657核心板在硬件上pin to pin兼容。

TI KeyStone C66x多核定点浮点DSP TMS320C665x工业核心板,单核TMS320C6655和双核TMS320C6657

Revision HistoryDraft Date Revision No. Description 2016/02/04 V1.1 1. 排版修改。

2014/07/30 V1.0 1. 初始版本。

目录1 核心板简介 (4)2 典型运用领域 (5)3 软硬件参数 (6)4 开发资料 (8)5 电气特性 (9)6 机械尺寸图 (9)7 产品订购型号 (10)8 技术支持 (11)9 增值服务 (11)更多帮助 (12)附录A 开发例程 (13)1核心板简介处理器架构先进:基于TI KeyStone C66x多核定点/浮点DSP TMS320C665x,单核TMS320C6655和双核TMS320C6657管脚pin to pin兼容,同等频率下具有四倍于C64x+器件的乘累加能力;运算能力强:主频1.0G/1.25GHz,单核可高达40GMACS和20GFLOPS,包含2个Viterbi 协处理器和1个Turbo协处理解码器,每核心32KB L1P、32KB L1D、1MB L2,1MB 多核共享内存,8192个多用途硬件队列,支持DMA传输;性价比高:可免装风扇,以最低的功率级别和成本提供最高的性能;拓展资源丰富:支持PCIe、SRIO、HyperLink、uPP、EMIF、千兆网口等多种高速接口,同时支持I2C、SPI、UART、McBSP等常见接口;连接稳定可靠:80mm*58mm,体积极小的C66x核心板,采用工业级高速B2B连接器;开发资料齐全:提供丰富的开发例程,入门简单,支持裸机和SYS/BIOS操作系统。

图 1 SOM-TL665x正面图 2 SOM-TL665x背面由广州创龙自主研发的SOM-TL665x是一款基于TI KeyStone系列多核架构的定点/浮点TMS320C665x 高端DSP核心板,采用沉金无铅工艺的八层板设计,专业的PCB Layout 保证信号完整性的同时,经过严格的质量控制,满足多种环境应用。

TI C66x TL665x-EasyEVM开发板开发例程学习_部分11

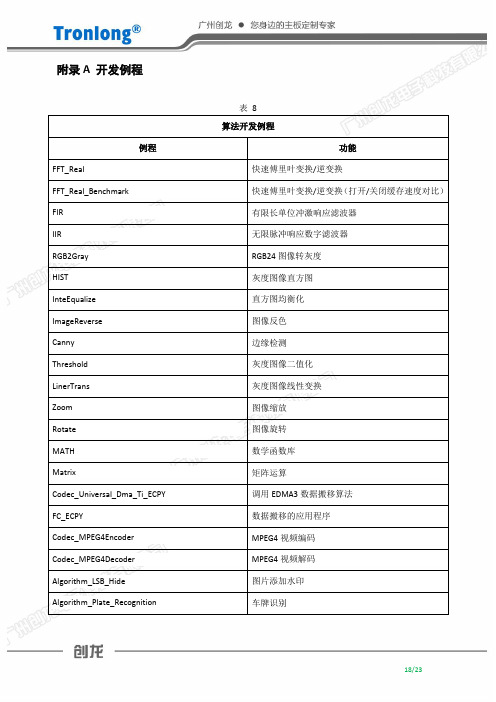

附录A 开发例程表8算法开发例程例程功能FFT_Real 快速傅里叶变换/逆变换FFT_Real_Benchmark 快速傅里叶变换/逆变换(打开/关闭缓存速度对比)FIR 有限长单位冲激响应滤波器IIR 无限脉冲响应数字滤波器RGB2Gray RGB24图像转灰度HIST 灰度图像直方图InteEqualize 直方图均衡化ImageReverse 图像反色Canny 边缘检测Threshold 灰度图像二值化LinerTrans 灰度图像线性变换Zoom 图像缩放Rotate 图像旋转MATH 数学函数库Matrix 矩阵运算Codec_Universal_Dma_Ti_ECPY 调用EDMA3数据搬移算法FC_ECPY 数据搬移的应用程序Codec_MPEG4Encoder MPEG4视频编码Codec_MPEG4Decoder MPEG4视频解码Algorithm_LSB_Hide 图片添加水印Algorithm_Plate_Recognition 车牌识别表9SYS/BIOS开发例程例程功能Task 任务CLOCK 时钟Task_MUTEX 抢占式多任务Task_STATIC 静态创建任务Timer 定时器(通用)Timer_C665x 定时器(专用)Timer_C665x_Runtime 定时器(动态创建)MEMORY 内存分配HWI_C66x 硬件中断(HWI设备专用组件)HWI_C66x_Hook 硬件中断(HWI挂钩函数)HWI_C66x_Nest 硬件中断(HWI中断嵌套)HWI_Runtime 硬件中断(HWI)HWI_Runtime_Post_SWI 硬件中断(HWI发布软件中断)HWI_Runtime_Post_Task 硬件中断(HWI触发任务)SWI 软件中断(静态配置)SWI_Runtime 软件中断(SWI)SWI_Runtime_Post_Conditionally_andn 软件中断(有条件触发ANDN)SWI_Runtime_Post_Conditionally_dec 软件中断(有条件触发DEC)SWI_Runtime_Post_Unconditionally_or 软件中断(无条件触发OR)Timestamp 时间戳(通用)Timestamp_C665x 时间戳(专用)EDMA3 EDMA3一维数据传输UART1_INT UART1串口中断收发McBSP0_LoopBack_Test McBSP0外部回环测试uPP_8Bit_B_TO_A uPP双通道8位外部线路回路读写uPP_16Bit_B_TO_A uPP双通道16位外部线路回路读写PCIe PCIe板间通信SRIO SRIO板间通信NDK_TCP TCP服务器NDK_UDP UDP通信NDK_TCP_Benchmark TCP发送/接收速度测试NDK_Telnet Telnet协议NDK_Runtime 网络Web服务器(支持串口输入IP)NDK_WebServer 网络Web服务器NDK_TCP_Client TCP客户端NDK_RawSocket 以太网数据链路层通信NDK_UIA 于网络传输的系统分析DSP_FPGA_CL_SRIO CameraLink工业相机高性能实时采集处理系统Board_C665x 开发板全基本功能测试表10裸机开发例程例程功能GPIO_LED GPIO输出(LED灯)GPIO_KEY GPIO输入(按键中断)UART0_POLL UART1串口查询收发NMI NMI不可屏蔽中断Timer 定时器2WatchDog 看门狗(定时器)SPI_FLASH SPI FLASH读写IIC_EEPROM IICEEPROM读写EDMA3 EDMA3一维数据传输UART1_INT UART1串口中断收发I2C_TempSensor IIC总线温度传感器测试I2C_TempSensor_POLL IIC总线温度传感器测试NANDFLASH NANDFLASH读写测试GPIO_LED_Assembly GPIO输出(标准汇编)GPIO_LED_LinearAssembly GPIO输出(线性汇编)NonOS_MPAX 访问相同的逻辑地址表11基于Platform平台库(均可不使用操作系统,但是库函数支持在SYS/BIOS下使用)例程功能EMIF_NandFlash EMIFA总线NAND FLASH测试Fan 风扇控制GPIO_KEY 按键状态查询GPIO_LED LED灯控制LED灯控制IIC总线EEPROM读写IIC_TemperatureSensor IIC总线温度传感器测试Memory_DDR3 DDR3内存读写测试SPI_Nor_Flash API总线NOR FLASH测试UART 串口查询收发Timer 定时器基于STK的Demo例程(裸机)例程功能STK_EMIF NAND FLASH测试STK_GE 网络测试STK_KEY 按键测试STK_LED GPIO输出测试STK_I2C 内部回环/EEPROM/TMP102温度传感器测试STK_Memory_Test 系统所有内存测试STK_Memory_Performance 内存性能测试STK_SPI SPI内部回环/EDMA回环/NOR FLASH测试STK_UART 串口0回环/EDMA/PC机通信测试STK_Timer 定时器测试STK_Robust 核心稳健性测试STK_SRIO SRIO外部线路回环测试STK_SRIO_FPGA SRIO通过DMA方式收发测试STK_Multicore_Navigator 多核导航器测试STK_HyperLink HyperLink内部回环测试STK_PCIe PCIe PHY回环测试表13其它Demo例程演示例程功能GPIO_LED_Assembly GPIO输出(标准汇编)GPIO_LED_LinearAssembly GPIO输出(线性汇编)表14多核开发例程例程功能MultiCore_SingleImage 多核单镜像通信测试MultiCore_DualImage 多核多镜像通信测试MultiCore_SingleImage_SYSBIOS 多核单镜像SYSBIOS通信测试MultiCore_DualImage_ SYSBIOS 多核多镜像SYSBIOS通信测试OpenMP_Hello OpenMP的测试OpenMP_Hello_SYSBIOS 基于SYBIOS的OpenMP测试OpenMP_Matrix-Vector_Multiplication 基于OpenMP的矩阵-向量乘法OpenMP_RGB2Gray 基于OpenMP的RGB24图像转灰度MultiCore_IPC_MessageQ MessageQ模块通讯测试MultiCore_IPC_Notify Notifyn模块通信测试MultiCore_IPC_SharedRegion SharedRegion模块通信测试MultiCore_IPC_Image_Canny 边缘检测表15基于广州创龙编写的RTSC组件的例程例程功能RTSC_Fan 对散热风扇转速进行控制RTSC_FFT_Real 快速傅里叶变换/逆变换RTSC_UART0_POLL UART0串口查询收发RTSC_UART1_POLL UART1串口查询收发RTSC_I2C_TempSensor IIC总线温度传感器测试RTSC_SysMin SysMin组件的输出调试演示RTSC_SysStd SysStd组件的输出调试演示RTSC_LoggerBuf 日志输出到缓冲区的演示例程RTSC_LoggerStd 实时输出日志信息的演示例程RTSC_Benchmark 测量代码性能方法RTSC_UART0_INTRRUPT UART0串口中断收发RTSC_LED LED测试RTSC_KEY 按键测试。

2 创龙基于TMS320C665x CCS工程新建、编译和导入开发例程使用手册

在"EmptyProjects"下方选择"EmptyProject(withmain.c)"。

点击"Advancedsettings",在弹出的界面中的"Linkercommandfile:"选项后面选择cmd文件。cmd文件C665x.cmd可在光盘目录"Images"路径下找到,选择前请先将cmd文件拷到非中文路径。

2.2.2

(1)点击"File->New->Project",在弹出的界面中点开"Code Composer Studio",双击"CCS Project",如下图所示:

图75

图76

(2)在弹出的界面中输入工程名字,选择CPU平台和型号、仿真器型号、SYS/BIOS工程模板,如下图所示:

图77

(3)点击Next,弹出如下界面:

2.2.1

(1)点击"File->New->Project",在弹出的对话框中选择"RTSC->NewRTSCPlatform",如下图所示:

图66

图67

(2)点击Next,在弹出的对话框中设置平台包名字、路径,如下图所示:

图68

备注:平台包文件存放路径PlatformPackageRepository不能含有非ASCII字符,请记住此路径,在下面SYS/BIOS工程新建步骤将用到。

图91

打开CCS,点击CCS菜单栏下"Window->Preferences",如下图所示:

图49

创龙TMS320C665x基于裸机开发的Demo例程演示

1创龙TMS320C665x基于裸机开发的Demo例程演示所有工程均位于光盘"Demo\NonOS\Application"文件夹内。

例程通过配置寄存器驱动GPIO。

本章节讲述在不使用操作系统的情况下,基于创龙TMS320C665x开发板的例程演示。

5.1GPIO_LED——GPIO输出(LED灯)此程序的作用是实现GPIO输出功能。

按照工程导入步骤加载GPIO_LED.out文件,然后点击程序运行按钮。

演示现象核心板用户指示灯循环点亮。

5.2GPIO_LED_C++——GPIO输出(LED灯)此程序是用C++语言编写,实现GPIO输出功能。

按照工程导入步骤加载NonOS_GPIO_LED_C++_C665x.out文件,然后点击程序运行按钮。

演示现象底板用户指示灯循环点亮。

5.3GPIO_KEY——GPIO输入(按键中断)此程序的作用是实现GPIO输入功能。

按照工程导入步骤加载GPIO_KEY.out文件,然后点击程序运行按钮。

演示现象●TL665x-EasyEVM:当按下USER0按键1次后,将标志Flag置1,底板LED D3、D5、D7开始循环点亮;当再次按下USER0按键1次后,将标志Flag置0,底板LED停止循环点亮。

●TL665xF-EasyEVM:当按下DSP USER1按键1次后,将标志Flag置1,底板DSP LED1~LED3开始循环点亮;当再次按下DSP USER1按键1次后,将标志Flag置0,底板DS P LED1~LED3停止循环点亮。

5.4UART0_POLL——UART0串口查询收发此程序的作用是实现UART0查询方式数据收发功能。

将开发板的UART0和PC机连接,打开串口调试终端,按照工程导入步骤加载UART 0_POLL.out文件,然后点击程序运行按钮。

演示现象(1)串口调试终端会打印提示信息,如下图所示:图 1(2)使用键盘输入任意字符,CPU会将接收到的字符回显到串口调试终端,如下图所示:图 25.5NMI——NMI不可屏蔽中断此程序的作用是实现不可屏蔽中断功能。

OpenCNC_PLC开发工具操作手冊说明书

OpenCNC_PLC發展工具操作手冊匯出日期:2023-05-10修改日期:2020-08-30英文文件 English Document: PLC Editor Operation Manual.Ladder-Editor 軟體操作介紹Ladder編寫開發PLC元件介紹操作手冊下載文件履歷1.2.•••• a.i.1 PLC 編輯器介紹1.1 軟體下載進入新代網站 ,完成線上注冊手續并確定權限開通。

至『下載中心』 => 『04.應用工具』 => 『Ladder Editor 』下載PLC 編輯器。

1.2 軟體安裝2.26.3(含)以前為安裝版執行LadEdit_vx.xx.x.msi 并依畫面指示,即可完成安裝程序。

安裝完成後,依序點選『開始』 => 『程式集』 => 『OpenCNC 』 => 『MLCEdit.exe 』,即可開啟PLC 編輯器。

2.29.0(含)以後為免安裝版第一次執行時:下載完LadEditor_x.xx.x.zip ,解壓縮後右鍵點擊『Install.bat 』,選擇『以系統管理員身分執行』,將.lad 檔的預設開啟程式設定為PLC 編輯器ii.b.c.i.ii.•••••••執行『MLCEdit.exe』開啟PLC編輯器第二次之後執行:執行『MLCEdit.exe』,或直接雙擊.lad檔,皆可開啟PLC編輯器注意事項:搬移免安裝包位置時,請再次執行免安裝包內的『Install.bat』,否則會無法正常開啟.lad檔。

下載新版本PLC編輯器時,請執行新版本免安裝包內的『Install.bat』,否則仍會以舊版PLC編輯器開檔。

1.3 介面操作PLC編輯器介面共有七個區域,如下圖所示:下拉式功能區指令按鈕功能區指令區程式管理區指令編輯區元件注解區元件索引區下拉式功能區指令按鈕功能區指令區指令區提供各種元件讓使用者選取、應用,詳細說明請參閱後續章節。

TMS320C645xDSPEMIFAUserGuide(用户手册)(精)

TMS320C645x DSP External Memory Interface (EMIFUser's GuideLiterature Number:SPRU971December 20052SPRU971–December20056 1Overview 8 2EMIF Interface Signals 9 3Memory Width and Byte Alignment 12 4Asynchronous Interface 13 4.1Asynchronous Interface Addressing 15 4.2Programmable ASRAM Parameters 15 4.3Asynchronous Reads 15 4.4Asynchronous Writes 164.5Ready Input 17 4.6Asynchronous Memory Access in Select Strobe Mode 194.7Asynchronous Memory Access in WE Strobe Mode 214.8Asynchronous Time-Out 235Programmable Synchronous Interface 24 5.1Programmable Synchronous Interface Addressing 24 5.2SBSRAM Interface 24 5.3Zero Bus Turnaround (ZBTSRAM Interface 285.4Synchronous FIFO 306Turnaround Time 33 7Command FIFO and Scheduling 34 7.1Command Ordering and 34 7.2Command Starvation 357.3Possible Race Condition 358Resetting the EMIF 36 9Hold Interface 37 10Emulation Halt Operation 37 11EMIF Registers 38 11.1Module ID and Revision Register (MIDR39 11.2Status Register 4011.3Burst Priority Register (BPRIO41 11.4CE n Configuration Registers (CEn CFG if SSEL =42 11.5CE n Configuration Registers (CEn CFG Field Descriptions if SSEL =144 11.6Asynchronous Wait Cycle Configuration Register 46 11.7Interrupt RAW Register (INTRAW47 11.8Interrupt Masked Register (INTMSK48 11.9Interrupt Mask Set Register (INTMSKSET49 11.10Interrupt Mask Clear Register 50SPRU971–December2005Table of Contents 3List of Figures1TMS320C645x DSP Block Diagram 9 2EMIF Interface 10 3Byte Alignment by Bus Size 12 4EMIF to 32-bit SRAM Interface Block Diagram 13 5EMIF to 8-Bit ROM Interface Block Diagram 14 6EMIF to 16-Bit ROM Interface Block Diagram 14 7EMIF to 32-Bit ROM Interface Block Diagram 14 8Asynchronous Read Timing Diagram 169Asynchronous Write Timing Diagram 17 10Asynchronous Write Timing Diagram Using Ready 18 11Asynchronous Read Timing Diagram Using Ready 1912Asynchronous Write in Select Strobe Mode 20 13Asynchronous Read in Select Strobe Mode 20 14Asynchronous Write in WE Strobe Mode 21 15Asynchronous Read in WE Strobe Mode 22 16EMIF to SBSRAM Interface Block Diagram 25 17SBSRAM Six-Element Read Timing Diagram 26 18SBSRAM Six-Element Write Timing Diagram 27 19EMIF to Zero Bus Turnaround (ZBTSRAM Interface Block Diagram 28 20Zero Bus Turnaround (ZBTSRAM Six-Element Write Timing Diagram 29 21Read and Write Synchronous FIFO Interface With Glue Block Diagram 30 22Standard Synchronous FIFO Read Timing 31 23Standard Synchronous FIFO Write Timing Diagram 32 24EMIF FIFO Block 34 25Hold 37 26Module ID and Revision Register (MIDR39 27Status Register (STAT40 28Burst Priority Register (BPRIO41 29CE n Configuration Registers (CEn CFG if SSEL =42 30CE n Configuration Registers (CEn CFG Field Descriptions if SSEL =144 31Asynchronous Wait Cycle Configuration Register 46 32Interrupt RAW Register (INTRAW47 33Interrupt Masked Register (INTMSK48 34Interrupt Mask Set Register (INTMSKSET49 35Interrupt Mask Clear Register 50List of Figures4SPRU971–December2005List of Tables1EMIF Pins Used to Access All Device 10 2EMIF Pins Specific to Asynchronous Devices 10 3EMIF Pins Specific to Synchronous Devices 11 4EMIF Pins Used for Hold 11 5Addressable Memory Ranges and Internal to External Address Bus Translation 12 6Asynchronous Interface Signal Descriptions 13 7Interrupt Monitor and Control Bit 23 8Programmable Synchronous Interface 24 9Turnaround Time 33 10EMIF FIFO Description 34 11Device and EMIF Reset Relationship 36 12EMIF 38 13Module ID and Revision Register (MIDRField Descriptions 39 14Status Register (STATField Descriptions 40 15Burst Priority Register (BPRIOField Descriptions 41 16CE n Configuration Registers (CEn CFG if SSEL =0Field Descriptions 42 17CE n Configuration Registers (CEn CFG Field Descriptions if SSEL =144 18Asynchronous Wait Cycle Configuration Register (AWCCField Descriptions 46 19Interrupt RAW Register (INTRAWField Descriptions 47 20Interrupt Masked Register (INTMSKField Descriptions 48 21Interrupt Mask Set Register (INTMSKSETField Descriptions 4922Interrupt Mask Clear Register (INTMSKCLRField Descriptions 50SPRU971–December2005List of Tables 5PrefaceSPRU971–December2005About This ManualThis document describes the operation of the external memory interface (EMIFin the digital signal processors (DSPsof the TMS320C645x™DSP family.Notational ConventionsThis document uses the following conventions.•Hexadecimal numbers are shown with the suffix h. For example, the following number is 40hexadecimal (decimal64:40h.•Registers in this document are shown in figures and described in tables.–Each register figure shows a rectangle divided into fields that represent the fields of the register. Each field is labeled with its bit name, its beginning and ending bit numbers above, and its read/writeproperties below. A legend explains the notation used for the properties.–Reserved bits in a register figure designate a bit that is used for future device expansion.Related Documentation From Texas InstrumentsThe following documents describe the C6000™devices and related support tools. Copies of thesedocuments are available on the Internet at . Tip:Enter the literature number in the search box provided at .The current documentation that describes the C6000devices, related peripherals, and other technical collateral, is available in the C6000DSP product folder at:.TMS320C6000CPU and Instruction Set Reference Guide (literaturenumbergivesanintroductiontothe TMS320C62x™and TMS320C67x™DSPs, development support.TMS320C6455Technical Reference (literaturenumber gives an introduction to theTMS320C6455™DSP and discusses the application enhanc ed.TMS320C6000Programmer's Guide (literaturenumber describes ways to optimize C and assembly code for the TMS320C6000™DSPs and program examples.TMS320C6000Code Composer Studio Tutorial (literaturenumber introduces the Code Composer Studio™integrat ed development environment and Studio Application Programming Interface Reference Guide (literaturenumberdescribes the Code Composer Studio™application programming interface (API,which allows custom plug-ins for Code Composer.TMS320C64x+Megamodule Reference Guide (literaturenumber describes theTMS320C64x+digital signal processor (DSPmegamodule. on the internal direct memory access (IDMAcontroller, the interrupt controller, the power-down controller, memory protection, bandwidth management, and the memory and cache.TMS320C6000DSP Peripherals Overview Reference Guide (literaturenumber provides a brief description of the peripherals available on the TMS320C6000digital signal TMS320C6455Chip Support Libraries (CSL(literaturenumber is a download with the latest chip support libraries.6Preface SPRU971–December2005Related Documentation From Texas Instruments TrademarksTMS320C645x, C6000, TMS320C62x, TMS320C67x, TMS320C6455,TMS320C6000, Code Composer Studio are trademarks of Texas Instruments.SPRU971–December2005Read This First 71OverviewUser's GuideSPRU971–December2005This document describes the operation and registers of the External Memory Interface (EMIFin the TMS320C645x™DSP.The C645x DSP External Memory Interface (EMIFcan interface to a variety of external devices, including:•Pipelined and flow-through synchronous-burst SRAM (SBSRAM•ZBT (zerobus turnaround SRAM and Late Write SRAM •Synchronous FIFOs•Asynchronous memory, including SRAM, ROM, and FlashA block diagram of the C645x DSP is shown in Figure 1In this document, the term EMIF refers to the EMIFA of C645x devices.The EMIF services requests of the external bus from on-chip masters such as the enhanceddirect-memory access (EDMAcontroller and the C64x+Megamodule, as well as external shared-memory device controllers (throughthe hold interface, Section 9On-chip masters place requests to the EMIF through the switched control resource(rmation on the SCR, see the device data manual.TMS320C645x DSP External Memory Interface (EMIF8SPRU971–December20052EMIF Interface SignalsEMIF Interface SignalsFigure 1. TMS320C645x DSP Block DiagramThe EMIF signals of the DSP are shown in the figure below and described in the following tables. The EMIF has the following features:•A 64-bit data bus which can also be configured to be 32-, 16-, and 8-bits wide.•An output clock, ECLKOUT, generated internally based on the EMIF input clock. You can select one of the following two clocks as the EMIF input clock source at device reset:internal SYSCLK3or external ECLKIN. All of the memories interfacing with the EMIF should operate using ECLKOUT (EMIFclock cycle. The ECLKOUT frequency equals the EMIF input clock frequency.•A programmable synchronous interface allowing glue less interfaces to synchronous devices such as ZBT SRAM, Late Write SRAM, and Pipelined and Flow-Through SBSRAM devices. Interfaces to synchronous FIFOs are also supported with the addition of external logic.•A configurable asynchronous interface allowing interfaces to asynchronous devices such as SRAM, EPROM, and Flash, as well as FPGA and ASIC designs.•Four EMIF spaces (CE2-5reserved for either asynchronous or synchronous memory accesses.SPRU971–December2005TMS320C645x DSP External Memory Interface (EMIF9 ED[63:0] BA[1:0]EA[19:0]configuration busShared by allinterfacesHold interfaceECLKINEDMA busARDYECLKOUTAsynchronous ready inputAsynchronous/synchronousinterfaceMUXed asynchronous/synchronous memorywrite enableEMIF Interface SignalsFigure 2. EMIF Interface SignalsTable 1. EMIF Pins Used to Access All Device Types Pin I/O/ZDescriptionECLKIN I EMIF external input clockED[63:0]I/O/ZEMIF 64-bit data bus I/OEA[19:0]O/ZExternal address output for EMIFBA[1:0]O/ZAddress outputs for async/syncinterface when the data bus is configured as 8-or 16-bits wide.O/ZActive-low byte enables. Byte enables go active for only the appropriate bytelane for both writes and reads.Table 2. EMIF Pins Specific to Asynchronous DevicesPin I/O/ZDescriptionO/ZActive-low chip select for memory space CE2O/ZActive-low chip select for memory space CE3O/ZActive-low chip select for memory space CE4O/ZActive-low chip select for memory space CE5ARDY I Active-high asynchronous ready input used to insert wait states for slowmemories and peripheralsO/ZRead/writeenable for asynchronous memory interfaceO/ZActive-low output enable for asynchronous memory interfaceO/ZActive-low write strobe for asynchronous memory interfaceTMS320C645x DSP External Memory Interface (EMIF10SPRU971–December2005EMIF Interface SignalsTable 3. EMIF Pins Specific to Synchronous DevicesPin I/O/ZDescriptionECLKOUT O/ZEMIF output clock at EMIF input clock (ECLKINor SYSCLK3 frequency O/ZActive-low chip select for memory space CE2O/ZActive-low chip select for memory space CE3O/ZActive-low chip select for memory space CE4O/ZActive-low chip select for memory space CE5O/ZRead/writeenable for asynchronous memory interface O/ZProgrammable synchronous interface output enableO/ZSynchronous memory address strobe or read enable.The R_ENABLEfield in the CE n Configuration Register (CEn CFG selects between and If R_ENABLE=0, then the signal functions as the signal. If R_ENABLE=1, then the signal functions as the signal. O/ZSynchronous memory write enableTable 4. EMIF Pins Used for Hold InterfacePin I/O/ZDescriptionI Active-low external bus hold (3-staterequest from host O Active-low hold-request-acknowledge to the hostBUSREQOActive-high bus request signal. Indicates pending refresh or memory access.SPRU971–December2005TMS320C645x DSP External Memory Interface (EMIF113Memory Width and Byte AlignmentAED[63:56]AED[55:48]AED[39:32]AED[47:40]AED[23:16]AED[31:24]AED[15:8]AED[7:0]EMIF64−bit device32−bit device16−bit device8−bit deviceMemory Width and Byte AlignmentThe EMIF supports memory widths of 8, 16, 32, and 64bits. The EMIF automatically performs packing and unpacking for accesses to external memories of less than the requested transfer length. Both big and little-endian formats are supported.Figure 3shows the byte lane used by the EMIF for each of the bus size configurations. The externalis always right aligned to the ED[7:0]side of the bus. The endianness mode determines whether byte lane 0(ED[7:0]is accessed as byte address 0(littleendian or as byte address N (bigendian, where 2N is memory width in bytes. Similarly, byte lane N is addressed as either byte address 0(bigendian or as byte address N (littleendian.Table 5summarizes the addressable memory ranges, as well as the internal address bus to external bus translation for each of the supported memory types.Figure 3. Byte Alignment by Bus Size ConfigurationTable 5. Addressable Memory Ranges and Internal to External Address Bus TranslationMaximumInternal address bus addressable bytes to external address Memory type Memory width per CE space bus translation Represents Async memory×84M EA[19:0]=A[21:2]Byte address ABA[1:0]=A[1:0]×164MEA[19:0]=A[21:2]Halfword address ABA1=A1×324M EA[19:0]=A[21:2]Word address ×648M EA[19:0]=A[22:3]Doubleword address Programmable ×84MEA[19:0]=A[21:2]Byte address sync memoryABA[1:0]=A[1:0]×164M EA[19:0]=A[21:2]Halfword address ABA1=A1×324M EA[19:0]=A[21:2]Word address ×648MEA[19:0]=A[22:3]Doubleword address12TMS320C645x DSP External Memory Interface (EMIFSPRU971–December20054Asynchronous InterfaceAsynchronous InterfaceThe asynchronous interface offers configurable memory cycle types to interface to a variety of memory and peripheral types, including SRAM, EPROM, and flash memory, as well as FPGA and ASIC designs. The EMIF allows widths of 64, 32, 16, and 8bits on any of the CE spaces, as shown in the ASIZEdescription of the CE n Configuration Register (CEn CFG register. The asynchronous interface signals on the EMIF are combined with the SBSRAM memory interface. To avoid bus contention, a programmable turnaround time also allows you to control the minimum number of cycles between a read followed by a write (sameor different CE spaces, or between reads from different CE spaces (seeSection 6Table 6lists the asynchronous interface pins. Figure 4shows an EMIF interface to standard SRAM. Figure 5Figure 6and Figure 7show EMIF to 8-, 16-, and 32-bit ROMs, respectively.Table 6. Asynchronous Interface Signal DescriptionsEMIF Signal FunctionActive-low chip select ED[63:0]64-bit data bus I/OEA[19:0]External address outputBA[1:0]Bank select outputs or address outputsActive-low output enable for asynchronous memory interface Active-low write strobe for asynchronous memory interface Read/writecontrol for asynchronous memory interfaceARDYAsynchronous ready. Input used to insert wait states into the memory cycle.Figure 4. EMIF to 32-bit SRAM Interface Block DiagramA See Section 4.1for information on memory addressing.BFor interface to a 64-bit data bus:and ED[63:0]are used. For interface to a 32-bit data bus:and ED[31:0]are used. For interface to a 16-bit data bus:and ED[15:0]are used. For interface to an 8-bit data bus:and ED[7:0]are used.CThe disabled state of the read input (ARDYcan be configured using the AP bit of the Asynchronous Wait Cycle Configuration register.SPRU971–December2005TMS320C645x DSP External Memory Interface (EMIF13Asynchronous InterfaceFigure 5. EMIF to 8-Bit ROM Interface Block DiagramAThe disabled state of the read input (ARDYcan be configured using the AP bit of the Asynchronous Wait Cycle Configuration register.Figure 6. EMIF to 16-Bit ROM Interface Block DiagramAThe disabled state of the read input (ARDYcan be configured using the AP bit of the Asynchronous Wait Cycle Configuration register.Figure 7. EMIF to 32-Bit ROM Interface Block DiagramAThe disabled state of the read input (ARDYcan be configured using the AP bit of the Asynchronous Wait Cycle Configuration register.TMS320C645x DSP External Memory Interface (EMIF14SPRU971–December20054.1Asynchronous Interface Addressing4.2Programmable ASRAM Parameters4.3Asynchronous ReadsAsynchronous InterfaceThe EMIF uses the EA[19:0]and BA[1:0]pins to define the address bus that connects to memory devices. For 8-, 16-, and 32-bit devices, ED[19:0]always carries the least significant bits of a 32-bit address. For 64-bit devices, ED[19:0]always carries the least significant bits of a 64-bit address.The functionality of BA[1:0]depends on the width of the addressed device, as follows:•For 64-bit and 32-bit devices, BA[1:0]are not used and should be left unconnected.•For 16-bit devices, BA1defines bit 0of the device’saddress; BA0is not used and should be left unconnected.•For 8-bit devices, BA[1:0]define bits 1and 0of the device’saddress.The EMIF allows a high degree of programmability for shaping asynchronous accesses. The programmable parameters are:•time the beginning of a memory cycle low, address valid and the activation of (writesor (reads.•Strobe:The time between the activation and deactivation of (writesor (reads.The read and write strobe period must not be programmed to be less than two ECLKOUT cycles when AE =1(ARDYextends the strobe cycle.•Hold:The time between the deactivation of (writesor (readsand the end of the cycle, which can be either an address change or the deactivation of the signal. These parameters are programmed in terms of ECLKOUT cycles. Separate setup, strobe, and hold timing parameters are available for read and write accesses. Minimum values for ASRAM are:•SETUP ≥1•STROBE ≥1(mustbe greater than or equal to 2when ARDY is used •HOLD ≥1Figure 8shows an asynchronous read with the ARDY signal always disabled. The disabled state of ARDY on the setting of AP. The R_SETUP,R_STROBE,andR_HOLDparameters are programmed with the values 1, 2, and 0, respectively. An asynchronous read proceeds as follows:•At the beginning of the setup period:–becomes active, if not already active from a previous access. –BE[7:0]become active.–EA[19:0]and BA[1:0]become valid.•At the beginning of a strobe period, becomes active. •At the beginning of a hold period:–becomes inactive (high.–Data is sampled on the ECLKOUT rising edge concurrent with the beginning of the hold period (theend of the strobe period. •At the end of the hold period:–becomes inactive only if another read or write access to the same space is not pending. –BE[7:0]become inactive.–EA[19:0]and BA[1:0]become invalid. The ARDY pin can be activated by the external device to extend the strobe period, giving it more time to provide the data. See Section 4.5for details on using the ARDY pin.To avoid bus contention, a programmable turnaround time also allows you to control the minimum number of cycles between a read followed by a write (sameor different CEspaces, or between reads from different CE spaces (seeSection 6SPRU971–December2005TMS320C645x DSP External Memory Interface (EMIF154.4Asynchronous WritesAsynchronous InterfaceFigure 8. Asynchronous Read Timing DiagramAThe disabled state of the ARDY pin depends on the setting of the AP bit in the Asynchronous Wait Cycle Configuration Register.Figure 9shows an asynchronous write cycle with the ARDY signal always disabled. The disabled state of on the setting of AP. The R_SETUP,R_STROBE,andR_HOLDparameters are programmed to 1, 2, and 0, respectively. An asynchronous write proceeds as:•At the beginning of the setup period:–becomes active, if not already active from a previous access. –become valid.–EA[19:0]and BA[1:0]become valid. –ED is driven.–becomes active (low.•At the beginning of a strobe period, becomes active. •At the beginning of a hold period, becomes inactive. •At the end of the hold period:–EA[19:0]and BA[1:0]become invalid. –ED[63:0]becomes invalid.–becomes inactive (ifno additional read or write accesses to the same CE n space are pending. To avoid bus contention, a programmable turnaround time also allows you to control the minimum number of cycles between a read followed by a write (sameor different CE spaces, or between reads from different CE spaces (seeSection6TMS320C645x DSP External Memory Interface (EMIF16SPRU971–December2005ECLKOUTEA[19:0]/BA[1:0] ED[63:0]ARDY (AByte enablesAddressWrite dataDisabled stateSetupStrobeHold 2314.5Ready InputAsynchronous Interface Figure 9. Asynchronous Write Timing DiagramA The disabled state of the ARDY pin depends on the setting of the AP bit in the Asynchronous Wait CycleConfiguration Register.The EMIF external asynchronous devices may assert control over the length of the strobe period through the use of the ready input (ARDYpin. pin can be activated by the AE bit in CE n Configuration Register (CEn CFG. When this bit is set, the EMIF monitors the ARDY pin to determine if the attached device wishes to extend the strobe period of the current access cycle beyond theprogrammed number of clock cycles.The ARDY pin must be asserted by the second rising edge of the ECLKOUT pin before the end of the programmed strobe period to be registered by the EMIF. When the EMIF detects that the ARDY pin has been asserted, it will begin inserting extra strobe cycles into the operation until the ARDY pin isdeactivated by the external device. The ARDY pin must be held in the asserted and deasserted states for a minimum of two ECLKOUT cycles to be synchronized inside ofthe EMIF. In addition to the two cycles of internal synchronization to deassert ARDY, the EMIF will insert two more wait cycles before returning to the last cycle of the programmed strobe period. The operation will proceed as usual at this point.The ARDY pin cannot be used to extend the strobe period indefinitely. The programmableMAX_EXT_WAITfield in the Asynchronous Wait Cycle Configuration register (AWCCdetermines the maximum number of ECLKOUT cycles the strobe period may be extended beyond the programmed length. When the counter expires, the EMIF proceeds to the hold period of the operation, regardless of the state of the ARDY pin. The EMIF can also generate an interrupt upon expiration of this counter. See Section 4.8for details on enabling this interrupt.For the ARDY pin to function properly, the AP bit of AWCC must be programmed to match the polarity used by the external device. In its reset state of 1, the EMIF will insert wait cycles when the ARDY pin is sampled high. When set to 0, the EMIF will insert wait cycles only when ARDY is sampled low. This programmability allows for a glueless connection to a larger variety of synchronous devices.Finally, a restriction is placed on the strobe period timing parameters when using the ARDY pin.Specifically, the W_STROBEand R_STROBEfields must not be set to 0for proper operation.Figure 10shows an example of extending a write operation using the ARDY pin, and Figure 11shows a for a read operation.SPRU971–December2005TMS320C645x DSP External Memory Interface (EMIF17ECLKOUTEA[19:0]/BA[1:0]ED[63:0]ARDYSetup Asynchronous InterfaceFigure 10. Asynchronous Write Timing Diagram Using Ready InputA In this figure:•SSEL =0, SS =0, BWEM =0, and AE =1in CE n Configuration register •AP =1in Asynchronous Wait Cycle Configuration register•W_SETUP=0, W_STROBE=1, and W_HOLD=0in CE n Configuration registerTMS320C645x DSP External Memory Interface (EMIF18SPRU971–December2005ECLKOUTEA[19:0]/BA[1:0]ED[63:0]ARDYSetup 4.6Asynchronous Memory Access in Select Strobe ModeAsynchronous InterfaceFigure 11. Asynchronous Read Timing Diagram Using Ready InputA In this fi gure:•SSEL =0, SS =0, BWEM =0, and AE =1in CE n Configuration register •AP =1in Asynchronous Wait Cycle Configuration register•W_SETUP=0, W_STROBE=1, and W_HOLD=0in CE n Configuration registerIf the SS bit in the Asynchronous Wait Cycle Configuration register for a particular chip select is set, that chip select acts as a strobe. In other words, the timing of is the same as and The value of the BWEM field in the Asynchronous Wait Cycle Configuration register is ignored in this mode; i.e., the pins act as byte enables. See Figure 12and Figure 13SPRU971–December2005TMS320C645x DSP External Memory Interface (EMIF19ECLKOUTEA[19:0]/BA[1:0]ED[63:0]ARDY (AStrobeStrobe ECLKOUTEA[19:0]/BA[1:0]ED[63:0]ARDY (AAsynchronous InterfaceFigure 12. Asynchronous Write in Select Strobe ModeA The disabled state of the ARDY pin depends on the setting of the AP bit in the Asynchronous Wait Cycle Configuration Register. BIn this figure:•SSEL =0, SS =1, BWEM =0, and AE =0in CE n Configuration register•W_SETUP=1, W_STROBE=3, and W_HOLD=2in CE n Configuration register •ARDY is set to its inactive stateFigure 13. Asynchronous Read in Select Strobe ModeA The disabled state of the ARDY pin depends on the setting of the AP bit in the Asynchronous Wait Cycle Configuration Register. BIn this figure:•SSEL =0, SS =1, BWEM =0, and AE =0in CE n Configuration register•R_SETUP=1, R_STROBE=3, and R_HOLD=2in CE n Configuration register •ARDY is set to its inactive state20TMS320C645x DSP External Memory Interface (EMIFSPRU971–December20054.7Asynchronous Memory Access in WE Strobe ModeECLKOUTEA[19:0]/BA[1:0]ED[63:0]ARDYSetup Asynchronous InterfaceThe pins act as write strobes when the WE Strobe Mode is enabled (theBWEM bit inAsynchronous Wait Cycle Configuration register is set. See Figure 14and Figure 15The WE Strobe Mode is useful when combining multiple 8-bit devices to bus. This mode allows the EMIF to perform byte writes to a group of 8-bit devices which do not have byte enable inputs. In this configuration, the byte enable pins are connected to the write strobes of the eight 8-bit devices. This mode cannot be used when in the Select Strobe mode, as the Select Strobe mode overrides this mode.Figure 14. Asynchronous Write in WE Strobe ModeA In this figure:•SSEL =0, SS =0, BWEM =1, and AE =1in CE n Configuration register •AP =1in Asynchronous Wait Cycle Configuration register•W_SETUP=0, W_STROBE=1, and W_HOLD=0in CE n Configuration registerSPRU971–December2005TMS320C645x DSP External Memory Interface (EMIF21ECLKOUTEA[19:0]/BA[1:0]ED[63:0]ARDYSetup Asynchronous InterfaceFigure 15. Asynchronous Read in WE Strobe ModeA In this figure:•SSEL =0, SS =0, BWEM =1, and AE =1in CE n Configuration register •AP =1in Asynchronous Wai t Cycle Configuration register•R_SETUP=0, R_STROBE=1, and R_HOLD=0in CE n Configuration register22TMS320C645x DSP External Memory Interface (EMIFSPRU971–December20054.8Asynchronous Time-Out InterruptAsynchronous InterfaceThe EMIF can generate an asynchronous time-out interrupt to the CPU when the attached device fails to deassert the ARDY pin within the number of cycles defined in the MAX_EXT_WAITfield of theAsynchronous Wait Cycle Configuration register (AWCC.This interrupt is enabled by writing a 1to the AT_MASK_SETbit of the Interrupt Mask Set register (INTMSKSETand is disabled by writing a 2to the AT_MASK_CLRfield of the Interrupt Mask Clear register (INTMSKCLR.Both AT_MASK_SETandAT_MASK_CLRbits read 1if the interrupt is enabled and read 0if the interrupt is disabled.Two other bits monitor the status of each interrupt. The AT bit of the Interrupt Raw register (INTRAWis set when an asynchronous time-out occurs, regardless of whether or not the interrupt has been enabled. The AT_MASKEDbit of the Interrupt Masked register (INTMSKis set when an asynchronous time-out occurs and the interrupt has been enabled. The AT_MASKEDbit will not be set if the interrupt is disabled. Writing a 1to either the AT bit or the AT_MASKEDbit will clear both bits.Table 7contains a summary of the interrupt monitor and control bit fields. See Section 11for complete the register fields.Table 7. Interrupt Monitor and Control Bit FieldsBit name Register name DescriptionAT Interrupt Raw register (INTRAWThis bit is always set when an asynchronous time-out occurs. AT_MASKEDInterrupt Masked register (INTMSKThis bit is only set when an asynchronous time-out occurs and the interrupt has been enabled by writing a1to AT_MASK_SET. AT_MASK_SETInterrupt Mask Set register Writing a 1to this bit enables the asynchronous time-out(INTMSKSETinterrupt.AT_MASK_CLRInterrupt Mask Clear register Writing a 1to this bit disables the asynchronous time-out(INTMSKCLRinterrupt.SPRU971–December2005TMS320C645x DSP External Memory Interface(EMIF235Programmable Synchronous Interface。

基于创龙TMS320C6678 DSP+ Xilinx Kintex-7 FPGA工业核心板简介

FPGA RAM ROM SENSOR Logic Cells DSP Slice GTX

IO

LED

表 2 FPGA 端硬件参数 Xilinx Kintex-7 XC7K325T-2FFG676I,兼容 XC7K160T/410T-2FFG676I 512M/1GByte DDR3 256Mbit SPI NOR FLASH 1x TMP102AIDRLT,核心板温度传感器,I2C 接口 326080 840 8 251 1x CPLD 状态灯 3x 用户指示灯

核心板在内部通过 I2C、EMIF16、SRIO 通信接口将 DSP 与 FPGA 结合在一起,组成 D SP+FPGA 架构,实现了需求独特、灵活、功能强大的 DSP+FPGA 高速数据采集处理系统。

SOM-TL6678F 引出 DSP 及 FPGA 全部资源信号引脚,二次开发极其容易,客户只需要 专注上层运用,降低了开发难度和时间成本,让产品快速上市,及时抢占市场先机。

表5 典型值电流

800mA

典型值功耗 7.47W

6 机械尺寸图

PCB 尺寸 安装孔数量 散热器安装孔数量

表6 112mm*75mm 4个 4个

7 产品订购型号

型号

SOM-TL6678F-1000/325T1GN-8/4GD-I

SOM-TL6678F-1000/325T1GN-8/8GD-I

SOM-TL6678F-1000/325T1GN-16/4GD-I

1 核心板简介

基于 TI KeyStone C66x 多核定点/浮点 DSP TMS320C6678 + Xilinx Kintex-7 FPGA 的高 性能信号处理器;

TI TMS320C6678 集成 8 核 C66x,每核主频 1.0/1.25GHz,每核运算能力高达 40GMACS 和 20GFLOPS,每核心 32KByte L1P、32KByte L1D、512KByte L2,4MByte 多核共享内 存,8192 个多用途硬件队列,支持 DMA 传输;

TMS320C6670数据手册说明书