数字逻辑答疑6.11

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

4.14更新

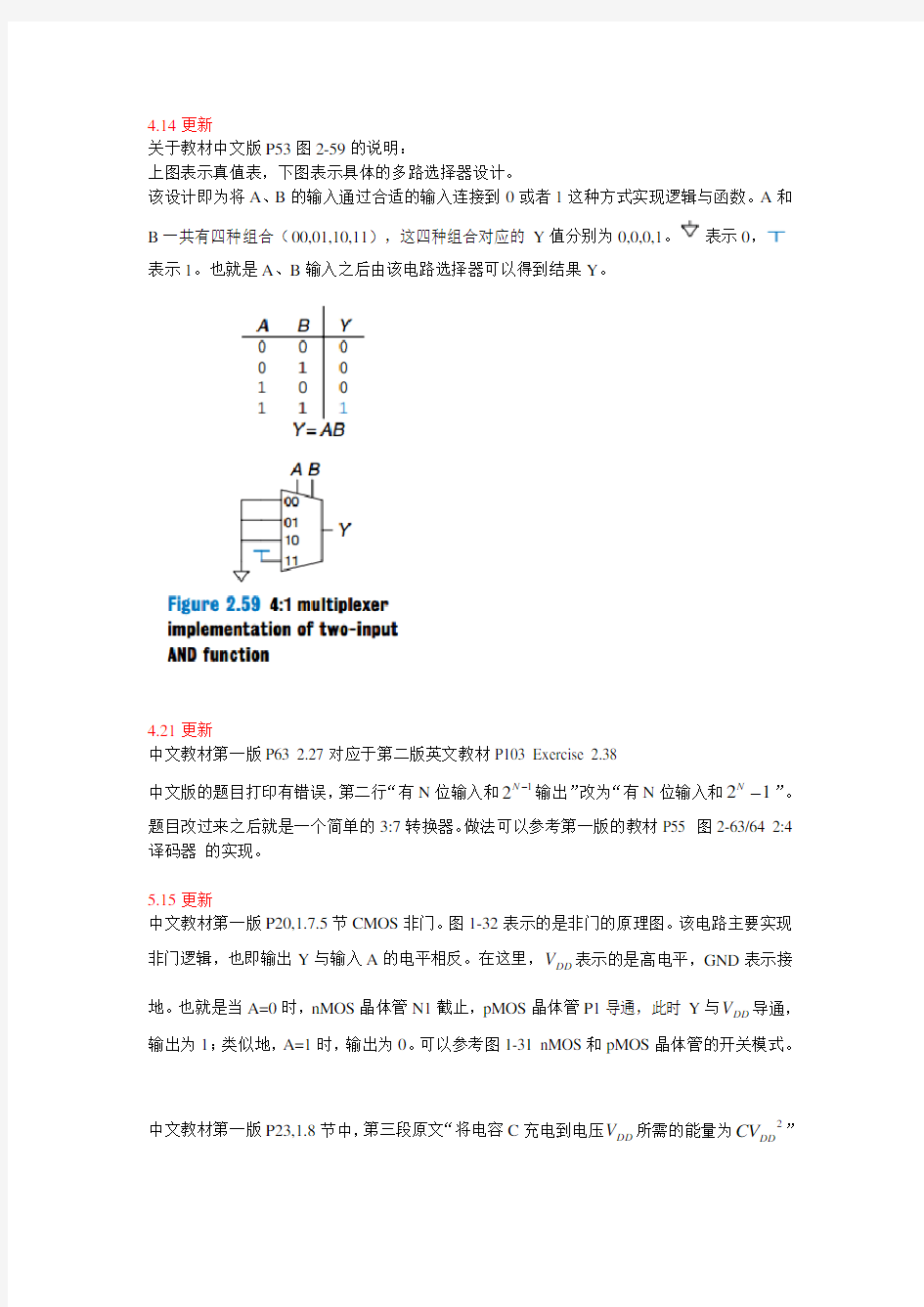

关于教材中文版P53图2-59的说明:

上图表示真值表,下图表示具体的多路选择器设计。

该设计即为将A 、B 的输入通过合适的输入连接到0或者1这种方式实现逻辑与函数。A 和B 一共有四种组合(00,01,10,11),这四种组合对应的Y 值分别为0,0,0,1。表示0,

表示1。也就是A 、B 输入之后由该电路选择器可以得到结果Y 。

4.21更新

中文教材第一版P63 2.27对应于第二版英文教材P103 Exercise 2.38 中文版的题目打印有错误,第二行“有N 位输入和1

2

-N 输出”改为“有N 位输入和12-N

”。

题目改过来之后就是一个简单的3:7转换器。做法可以参考第一版的教材P55 图2-63/64 2:4译码器 的实现。

5.15更新

中文教材第一版P20,1.7.5节CMOS 非门。图1-32表示的是非门的原理图。该电路主要实现非门逻辑,也即输出Y 与输入A 的电平相反。在这里,DD V 表示的是高电平,GND 表示接地。也就是当A=0时,nMOS 晶体管N1截止,pMOS 晶体管P1导通,此时Y 与DD V 导通,输出为1;类似地,A=1时,输出为0。可以参考图1-31 nMOS 和pMOS 晶体管的开关模式。

中文教材第一版P23,1.8节中,第三段原文“将电容C 充电到电压DD V 所需的能量为2

DD CV ”

改为“将电容C 充电到电压DD V 所需的能量为

2

12

DD CV ”。 说明:设定最终的电荷量为Q ,也即DD V C *,完成充电的时间为t ,则电流为t

Q I =。 能量E=U*I*t 。其中U 为平均电压,这里为DD V 21。所以最终结果为

2

12

DD CV 。

中文第一版P91,例3.9 时序分析。如下图所示,关键路径应该为如下红色箭头所标示的路径。如公式3-16所示,一个可靠触发器的保持时间要比它的最小延迟短。在这一题中,X ’的最小延迟为55ps ,而它的保持时间为60ps 。所以该触发器不能保持稳定的状态来捕获X=0状态。

解答的“第二段中B=0,C=0,D=0,A 从0上升为1”表示的是在这种状态下获得下图所示的关键路径。也就是题目解答的意思是在上面这种设定下,电路的改变就是如下图所示的路径。但是,只有当B=1,C=0,D=0时才会出现这种状态。所以该题应该将B=0改为B=1。虽然并不影响整个时序分析过程,但是严谨的来说应该改为B=1.

5.27更新

1. (2010)D =( )B = ( )H = ( )8421BCD 答案:(111 1101 1010)B = (7DA )H = (0010 0000 0001 0000)8421BCD

2. 仓库门上装了两把暗锁,A 、B 两位保管员各管一把锁的钥匙,必须二人同时开锁才能进库。这种逻辑关系为 。 答案:与逻辑

3. 逻辑函数式F=AB+AC 的对偶式为 ,最小项表达式为∑=m F ( )。 答案:))((C A B A F D ++= ∑=m F (5,6,7)

2.逻辑函数D AC CD A C AB D C ABD ABC F ''''''+++++=的最简与或式是 。

答案:'D

A+

4. 从结构上看,时序逻辑电路的基本单元是。

答案:触发器

5. JK触发器特征方程为。

答案:Q

K

'+

JQ'

6.A/D转换的一般步骤为:取样,保持,,编码。

答案:量化

中文教材P61

2.7(c)题目出现错误,按照英文教材,应为

C

B

D

A

C

A

Y+

+

+

+

+

+

=

B

B

D

C

D

A

C

B

C

B

D

ABD

A

A

中文教材中的等式右边第五项为C而不是C。

5.29更新

老师,想问:45页图2.36为什么没有图2.38好?图2.36还多了一个门。

答:图2.36是题目给出的题设条件,要求将该图变成与非、或非、非门构成的电路,说图2.38是相对于2.37来说的,是图2.37的简化。

老师,想问:40页完全使用布尔代数定理来简化表达式可能带来很多错误。我认为除了毛刺之类的错误没别的了,对吗?

答:布尔定理是没有错的,这句话在英文原版书上的表述是:”You may haove noticed that completely simplifying a Boolean equation with the threorems of Boolean Algebra can take some trial and error”这句话理解为用布尔定理更加复杂,容易出错。

中文教材第一版P56关于最小延迟的说明:最小延迟是在最短路径上每个元件的最小延迟之和。这里的最小延迟理解为要求最小延迟,是要求每个元件都取最小的时候得到的最小值。这只是一个极值问题。

P53 图2-59

该图中

表示输出为0,

表示输出为1。

P49图2.53

其中的0:1D 分别表示输入01,D D 。这种写法是为了方便列出真值表。

P74“组合逻辑没有环路和竞争”这句怎样理解,有竞争的就不能是组合逻辑吗? 这句的意思是有竞争的组合逻辑会出现问题,所以设计时要避免这种情况发生。

6.8更新

【题目1】:如何理解国产集成电路型号的命名法和主要技术指标? 【相关知识】:常用数字集成电路结构、外部特性和主要参数。

【解题方法】:数字集成电路除了TTL 和CMOS 两大类外,还有DTL ,HTL ,ECL ,I2L ,PMOS ,NMOS 等类型,这些类型的集成电路都可以看成是TTL 和CMOS 电路的改进型,