DFT(可测性设计、制造测试)

DFT测试类别描述正确

DFT测试类别描述正确DFT(数字技术模拟)测试是一种常见的电子设备测试方法,包括测试电路的功能,以及电子电路的功能和可靠性。

它是一个综合性的测试流程,不仅可以用于验证和测量单个元器件,还能够用于校验整个电子系统。

关于DFT(数字技术模拟)测试,首先我们需要了解它的主要目的:实现系统节省成本、品质提升的减少缺陷的目的。

在实际的DTF 测试中,以及DFT测试工具的使用,可以实现在设计到芯片实施前的检查,以减少缺陷数量。

在这样的检查中,可以及早检测出芯片在系统中出现的问题,有效提高芯片的可靠性,并减少系统出现故障的可能性。

DFT测试分为几个主要类别。

第一类是设计验证测试(DVT),它是测试电子设备的功能性,它不仅能够测量电子设备是否能够正常工作,还能测量它们的可靠性。

第二类是激励测试(Stimulus),它是一种面向芯片的测试,通过将模拟和数字信号驱动到芯片上,来测试芯片在不同激励下的功能和可靠性。

第三类是互联测试(Interconnect),它是一种硬件系统级测试,它检查和验证系统中硬件部件之间的互联关系,以确保其正确性。

DFT测试在工程中的应用更多的是体现在数字仿真的过程中。

数字仿真是指以数字信号的方式来仿真模拟信号,它可以在一定程度上准确地反映模特的行为和特性。

数字仿真的过程可以借助DTF测试的功能,帮助开发人员识别系统中的设计缺陷,并将其纠正。

另外,DFT测试还可以用于系统性能的分析,可以预测系统会在不同条件下运行的状态,从而发现系统中可能存在的潜在问题。

这些潜在问题可能包括系统中新组件引入的功能漏洞、设计失误导致的系统崩溃或性能瓶颈等等。

DFT测试可以在发现问题之前就帮助开发团队分析出系统性能可能出现的问题,从而有效的避免了这些问题的发生。

从以上内容我们可以看出,DFT测试不仅能够帮助开发人员识别并解决系统设计中的问题,而且还可以用于系统性能的分析。

DFT测试的技术特性可以满足多种系统设计的需求,因此在电子设备测试中得到了普遍的应用。

DFT基础

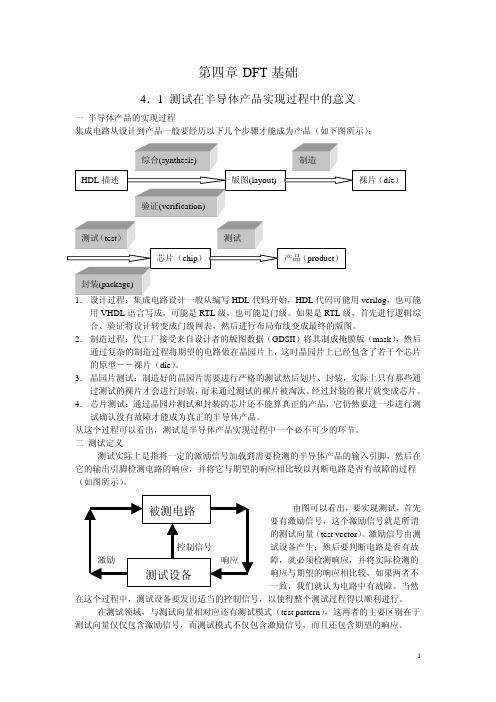

第四章 DFT 基础4.1 测试在半导体产品实现过程中的意义一 半导体产品的实现过程集成电路从设计到产品一般要经历以下几个步骤才能成为产品(如下图所示):verilog ,也可能用VHDL 语言写成,可能是RTL 级,也可能是门级。

如果是RTL 级,首先进行逻辑综合、验证将设计转变成门级网表,然后进行布局布线变成最终的版图。

2. 制造过程:代工厂接受来自设计者的版图数据(GDSII )将其制成掩膜版(mask ),然后通过复杂的制造过程将期望的电路做在晶园片上,这时晶园片上已经包含了若干个芯片的原型--裸片(die )。

3. 晶园片测试:制造好的晶园片需要进行严格的测试然后划片、封装,实际上只有那些通过测试的裸片才会进行封装,而未通过测试的裸片被淘汰。

经过封装的裸片就变成芯片。

4. 芯片测试:通过晶园片测试和封装的芯片还不能算真正的产品,它仍然要进一步进行测试确认没有故障才能成为真正的半导体产品。

从这个过程可以看出,测试是半导体产品实现过程中一个必不可少的环节。

二 测试定义测试实际上是指将一定的激励信号加载到需要检测的半导体产品的输入引脚,然后在它的输出引脚检测电路的响应,并将它与期望的响应相比较以判断电路是否有故障的过程(如图所示)。

在这个过程中,测试设备要发出适当的控制信号,式(test pattern ),这两者的主要区别在于测试向量仅仅包含激励信号,而测试模式不仅包含激励信号,而且还包含期望的响应。

由图可以看出,要实现测试,首先要有激励信号,这个激励信号就是所谓的测试向量(test vector )。

激励信号由测试设备产生;然后要判断电路是否有故障,就必须检测响应,并将实际检测的响应与期望的响应相比较,如果两者不一致,我们就认为电路中有故障。

当然以使得整个测试过程得以顺利进行。

在测试领域,与测试向量相对应还有测试模由上面的分析可以看出,测试问题在测试前就是测试模式生成和测试模式验证(时序验证)问题;而在测试时就是测试向量施加和测试响应检测及结果判断问题。

DFM简介PPT精选文档

24+/-1mil

改善后

无短路

DFM简介

51

DFM案例

案例四: 将插件物料改为SMT物料,改进生产效率

背景:X144 PCBA C2&C3&L3&L4为插件物料且采 用手工焊接,生产效率低

DFM简介

52

DFM案例

X144 PCBA C2&C3&L3&L4更改为SMT物料并采 用机器生产方式,提升生产效率

13

怎样做DFM

7. Small SMT 到Sub 0.050" Pitch的距离

DFM简介

14

怎样做DFM

8. BGA, CCGA到其他零件的距离

DFM简介

15

怎样做DFM

9. Small SMT 到其他SMT的距离

DFM简介

16

怎样做DFM

10. Small SMT 到插件元的距离

DFM简介

导入DFM,势在必行!

DFM简介

7

第一章&第二章内容回顾

DFM简介

8

怎样做DFM

第三讲、怎样做DFM

一、 DFM六要素

业界标准 (IPC等)

相关工具 (DFM工具Valor等)

材料特性(零 件,材料)

客户要求

DFM

设备能力(SMT,波 峰焊,自动化等) 制程能力 (Know-How)

DFM简介

9

怎样做DFM

二、PCBA及组装生产中常用的关于DFM的知识

1.各类元件距离PCB板边的距离

元件類型及描述 SMT零件到回焊爐的軌道板邊 SMT零件到過錫爐的軌道板邊 SMT零件距离非軌道邊 插件距离錫爐的軌道板邊 插件的PIN腳距离板邊 SMT元件高度大于9mm的元件距离板邊

可测性设计

5

.

可测性设计的重要概念

❖ 可测性 Testability = Controllable + Observable ➢ Controllable 可控性

➢ 有支持边界扫描测试功能的软件系统(用于建立边界扫描 测试所需要的各种文件和执行边界扫描测试,比如ASSET InterTech公司的ScanWorks 和法国Temento公司的 DiaTem )

14

.

边界扫描技术

❖ 选择集成电路 ➢ 在设计数字电路板时,应尽可能选择支持IEEE1149.1标

指能够对电路中每个内部节点进行复位和置位的能力 ➢ Observable 可观性

指不论用直接还是间接的方式都能观察到电路中任一个 内部节点状态的能力

6

.

可测性设计的重要概念

❖ 测试矢量与测试码自动生成(ATPG) (Automatic Test Pattern Generation)

➢ 测试矢量是每个时钟周期应用于管脚的用于测试或者操作 的逻辑1和逻辑0的数据

有三类方法:a、Ad hoc 测试

b、基于扫描的方法

c、BIST(Built in Self Test)

➢ Ad hoc 测试:即专项测试,按功能基本要求设计电路, 采取一些比较简单易行的措施,使他们的可测性得到提高

➢ SCAN扫描测试:Full Scan、 Boundary Scan 和 Partial Scan

.

边界扫描技术

❖ 数字电路板使用边界扫描测试方法有三个前提条件:

➢ 电路板上使用的集成电路(IC)支持边界扫描标准 IEEE1149.1(目前ALTERA、XILINX和 LATTICE的主要系 列的大规模可编程逻辑集成电路都支持IEEE1149.1 )

asic dft方法

asic dft方法ASIC DFT方法引言:ASIC(Application Specific Integrated Circuit)是一种专门为特定应用设计的集成电路。

在ASIC设计中,设计验证和测试是非常重要的环节。

DFT(Design for Testability)方法是一种用于增加集成电路可测试性的设计方法。

本文将介绍ASIC DFT方法的基本概念、常用技术和优势。

一、ASIC DFT方法的基本概念ASIC DFT方法是为了增加芯片测试的效率和可靠性而设计的一种方法。

它通过在设计阶段引入特定的测试结构和设计规约,提高了芯片测试的覆盖率和可测性。

二、ASIC DFT方法的常用技术1.扫描技术:扫描技术是ASIC DFT方法中最常用的技术之一。

它通过在设计中插入扫描链,将内部寄存器连接成一个线性的、可扫描的序列,从而实现了对芯片内部状态的全面测试。

2.边界扫描技术:边界扫描技术是扫描技术的一种变种。

它通过在芯片的输入输出边界插入扫描链,实现了对芯片输入输出端口之间的内部状态的测试。

3.内置自检技术:内置自检技术是一种在芯片中嵌入自检电路的技术。

它通过在芯片内部加入一些特殊的电路,实现了对芯片自身功能的测试。

4.故障模拟技术:故障模拟技术是一种通过模拟故障来测试芯片的技术。

它通过在芯片中插入故障模拟电路,对芯片进行故障注入,从而测试芯片在不同故障情况下的反应。

三、ASIC DFT方法的优势1.提高测试效率:ASIC DFT方法通过引入测试结构和设计规约,提高了芯片测试的覆盖率和可测性,从而提高了测试效率。

2.降低测试成本:ASIC DFT方法可以在设计阶段发现和修复可能存在的测试问题,避免了后期测试的重复工作,降低了测试成本。

3.增强芯片可靠性:ASIC DFT方法可以提前发现和修复芯片中的设计缺陷和故障,增强了芯片的可靠性。

4.减少测试时间:ASIC DFT方法通过扫描技术等手段,可以大大减少测试时间,提高测试效率。

可测性DFT

1 Active

1 0 0 Neighborhood

1

Pattern Sensitive

Various Faults With Address Decoder AdrE AdrE AdrE AdrE AdrE

Memory Fault – cont.

• Increase the defect coverage

How many function test patterns can cover all the devices?

Outlines

• Overview of IC Testing • Fault Modeling • Automatic Test Pattern Generation

• Fault models are typically defined

on a structure basis

Different fault models for digital logic, memories and analog circuit

• Typical fault models

Single stuck-at faults Transistor open/short faults Bridging faults Delay faults Memory faults Analog faults

to manufacturing.

• Responsible for

quality of design.

Test

• Verifies correctness of

manufactured hardware.

• Two-part process:

数字集成电路可测性设计(DFT)讲义第1讲

Good chip appears to be faulty (fails test)

EE141 VLSI Test Principles and Architectures

11

Introduction

Electronic System Manufacturing

A

system consists of

Moore’s Law: scale of ICs doubles every 18 months

Growing size and complexity poses many and new testing challenges

VLSI M LSI

1960s 1970s 1980s 1990s 2000s

EE141 VLSI Test Principles and Architectures

5

Introduction

Importance of Testing

Moore’s Law results from decreasing feature size (dimensions)

from 10s of µm to 10s of nm for transistors and interconnecting wires

8

Introduction

Testing During VLSI Development

Design verification targets design errors

Corrections made prior to fabrication

Design Specification Design Fabrication Packaging Quality Assurance Design Verification Wafer Test Package Test Final Testing

dft流程概述

dft流程概述DFT流程主要包括以下几个关键步骤:设计规范、逻辑设计、扫描链设计、测试生成、测试集成和测试应用。

下面将对每个步骤进行详细介绍。

首先是设计规范阶段。

在这个阶段,设计人员需要与客户和系统架构师进行沟通,了解设计需求和目标。

在明确需求后,设计人员会制定设计规范,定义芯片的功能和性能要求。

接下来是逻辑设计阶段。

在这个阶段,设计人员会使用硬件描述语言(HDL)来描述芯片的逻辑功能。

逻辑设计是整个DFT流程的基础,因为它决定了如何将测试电路集成到芯片中。

然后是扫描链设计阶段。

扫描链是一种用于测试的电路结构,可以在芯片制造之后对其进行测试。

在扫描链设计阶段,设计人员需要在逻辑设计的基础上添加扫描链电路,以便在测试时能够对芯片进行全面的覆盖。

接下来是测试生成阶段。

在这个阶段,设计人员会使用自动测试生成工具来生成测试模式,以确保测试能够覆盖到芯片的所有功能和电路。

测试生成是DFT流程中的一个关键步骤,因为它直接影响到测试的质量和效率。

然后是测试集成阶段。

在这个阶段,设计人员会将生成的测试模式集成到芯片中。

测试集成包括将测试模式加载到芯片的存储器中,并确保测试电路能够正确地与芯片的逻辑电路进行连接。

最后是测试应用阶段。

在这个阶段,设计人员会使用测试设备将测试模式应用到芯片上,并检测芯片的响应。

测试应用阶段是DFT流程中最后一个关键步骤,设计人员需要根据测试结果来评估芯片的性能和可靠性,并提供修复方案。

总结一下,DFT流程是一种用于验证和测试集成电路的方法。

它包括设计规范、逻辑设计、扫描链设计、测试生成、测试集成和测试应用等关键步骤。

通过DFT流程,设计人员可以在芯片制造之前发现潜在的问题,并提供修复方案以确保芯片的可靠性和性能。

这个流程对于芯片制造和验证起着至关重要的作用,可以提高芯片的质量和可靠性,同时减少制造成本和时间。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DFT Introduce 2016/7/29

DFT Summary

Scan Chain

BIST

Boundary Scan/Ntree

DFT: design for test(可测性设计)

测试分功能测试和制造测试

功能测试主要寻找设计上可能存在的错误,用来验证电路中的逻辑行为 制造测试用于寻找在制造过程中可能存在的制造缺陷(开路、短路等)

DFT是为了使制造测试尽可能简单,覆盖率尽可能高,而在电路中加入一些特殊逻辑的设计方法

DFT分类:

Scan: 扫描电路主要测试寄存器和组合逻辑。

工具生成

BIST: 内建自测试,电路自己生成测试向量对自己进行测试,主要用在IP测试,我们常用的就是测试RAM用的MBIST电路。

工具生成或者RTL设计

Boundary Scan: 测试IO,已及芯片与芯片之间互连测试。

工具生成

Ntree: 测试IO,功能比Boundary Scan少,但是面积也比Boundary Scan小。

RTL设计

DFT Summary

Scan Chain

BIST

Boundary Scan/Ntree

将电路中的普通触发器(flip-flops)替换为具有扫描能力的扫描触发器,如下图:当S=0时,触发器为正常的功能输入,而当S=1时,触发器为扫描输入。

将扫描触发器连在一起

Scan PIN可以和function pin共享,也可以是专用PIN,视实际应用而定

Scan PIN define example:

Stuck-At Fault

Fault类型有很多,这里主要讨论Stuck-At Fault(固定故障),某个信号的值被固定为某一电平值(0 或1)

Uncontrollable Clock Fix Example

Note: Uncontrollable Asynchronous Sets and Resets也需要FIX

下图为SCAN的几个主要过程,可以看出shfit占用了大部分时间,这个时间取决于scan chian的长度

一般说来,要定一个故障覆盖率指标,比如95% ,

DFT Summary

Scan Chain

BIST

Boundary Scan/Ntree

电路结构

MBIST

MBIST有多种算法

MBIST可用工具产生,也可设计RTL实现,我们是通过设计RTL 实现的,采用的是MARCH C+ 算法

DFT Summary

Scan Chain

BIST

Boundary Scan/Ntree

Boundary Scan

边缘扫描是欧美一些大公司联合成立的一个组织——联合测试行动小组(JTAG)为了解决PCB板上芯片与芯片之间互连测试而提出的一种解决方案。

由于该方案的合理性,它于1990年被IEEE采纳而成为一个标准,即IEEE1149.1

JTAG PIN:

TDI : test data in

TDO : test data out

TCK:test clock

TMS :test mode select

TRST: TAP复位信号(可选)

Boundary Scan一般是用工具做,在芯片的每一个IO上增加一个Boundary Scan Cell,然后再将这些Boundary Scan Cell连成一起,从而构成一条扫描链。

Boundary Scan Cell有多种,如下是输入/输出的Boundary Scan Cell例子

以输出Boundary Scan Cell来说明,Boundary Scan Cell的通路有四条Pi->PO: 正常功能

SI->SO: 移位操作

SI->PO: 移位到功能IO

PI->SO: 抓取功能IO的data进行移位

NTREE(nand tree)

对Input进行Nand操作,将测试结果通过Output送出观察,通过设计RTL实现。

优点:面积小

缺点:只能测本芯片IO的某个方向

对输入(a,b,c)来说,每一个输入都实现了0<->1的互相翻转。

而在输出(d)测,我们可以观察到1<->0翻转的输出波形

a b c d

0001。