CortexM1-Processor_Tutorial_UG

HCS08系列微控制器参考手册(中文)

HCS08系列微控制器参考手册第一册苏州大学飞思卡尔嵌入式系统研发中心翻译 2009年11月目录第一章通用信息与结构框图 (1)1.1HCS08系列微控制器介绍 (1)1.2HCS08CPU编程模型 (2)1.3外设模块 (2)1.4MC9S08GB60的特点 (3)1.4.1 HCS08系列的共性 (3)1.4.2 MC9S08GB60的特点 (3)1.5MC9S08GB60的结构框图 (4)第二章引脚及其连接 (5)2.1简介 (5)2.2推荐的系统连接 (5)2.2.1 电源 (7)2.2.2 MC9S08GB60振荡器 (7)2.2.3 复位 (8)2.2.4 背景/模式选择(BKGD/MS) (8)2.2.5 通用I/O及外设端口 (8)第三章工作模式 (10)3.1简介 (10)3.2特征 (10)3.3运行模式 (10)3.4背景调试模式 (11)3.5等待模式 (12)3.6停止模式 (12)3.6.1 Stop1模式 (13)3.6.2 Stop2模式 (13)3.6.3 Stop3模式 (14)3.6.4 停止模式下激活BDM使能 (14)3.6.5 设置OSCSTEN位 (15)3.6.6 停止模式下LVD使能 (15)3.6.7 停止模式下的片上外设模块 (15)3.6.8 系统选择寄存器(SOPT) (17)3.6.9 系统电源管理状态和控制寄存器1(SPMSC1) (18)3.6.10 系统电源管理状态和控制寄存器2(SPMSC2) (19)第四章片上存储器 (21)4.1简介 (21)4.2HCS08核定义的存储器组织 (21)4.2.1 HCS08存储器组织 (21)4.2.2 MC9S08GB60存储映像 (22)4.2.3 复位和中断向量表 (23)4.3寄存器地址和位分配 (24)4.4RAM (29)4.560K字节的FLASH (29)4.5.1 特征 (30)4.5.2 写入、擦除和空白检测命令 (30)4.5.3 命令时间和突发模式写入 (32)4.5.3.1 行和FLASH的组织结构 (32)4.5.3.2 程序命令时序 (33)4.5.4 访问错误 (34)4.5.5 向量重定向 (34)4.5.6 FLASH块保护(MC9S08GB60) (34)4.6MC9S08GB60的安全性 (35)4.7MC9S08GB60的FLASH寄存器和控制位 (36)4.7.1 FLASH时钟分频寄存器(FCDIV) (36)4.7.2 FLASH选项寄存器(FOPT和NVOPT) (37)4.7.3 FLASH配置寄存器(FCNFG) (38)4.7.4 FLASH保护寄存器(FPROT和NVPROT) (38)4.7.5 FLASH状态寄存器(FSTAT) (39)4.7.6 FLASH命令寄存器(FCMD) (40)4.8FLASH存储器应用实例 (41)4.8.1 FLASH模块时钟的初始化 (41)4.8.2 擦除FLASH的一页(512字节) (42)4.8.3 DoOnStack子程序 (43)4.8.4 SpSub子程序 (45)4.8.5 FLASH的字节编程 (46)第五章复位和中断 (47)5.1简介 (47)5.2MC9S08GB60复位和中断的特征 (47)5.4计算机正常操作监控模块(COP)看门狗 (48)5.5中断 (48)5.5.1 中断堆栈结构 (49)5.5.2 外部中断请求(IRQ)引脚 (50)5.5.2.1 引脚配置选项 (50)5.5.2.2 边沿/电平触发 (50)5.5.3 中断向量、中断源和局部屏蔽 (51)5.6低电压检测系统(LVD) (52)5.6.1 上电复位操作 (52)5.6.2 LVD复位操作 (52)5.6.3 LVD中断操作 (53)5.6.4 低电压警告(LVW) (53)5.7实时中断(RTI) (53)5.8复位、中断以及系统控制寄存器和控制位 (53)5.8.1 中断请求状态和控制寄存器(IRQSC) (54)5.8.2 系统复位状态寄存器(SRS) (55)5.8.3 系统背景调试强制复位寄存器(SBDFR) (56)5.8.4 系统选项寄存器(SOPT) (56)5.8.5 系统设备识别寄存器(SDIDH、SDIDL) (57)5.8.6 系统实时中断状态和控制寄存器(SRTISC) (57)5.8.7 系统电源管理状态控制寄存器1(SPMSC1) (58)5.8.8 系统电源管理状态和控制寄存器2(SPMSC2) (59)第六章中央处理单元 (61)6.1简介 (61)6.2编程结构和CPU寄存器 (61)6.2.1 累加器(A) (62)6.2.2 变址寄存器(H:X) (63)6.2.3 堆栈指针(SP) (64)6.2.4 程序计数器(PC) (66)6.2.5 条件码寄存器(CCR) (66)6.3寻址方式 (70)6.3.1 隐含寻址方式(INH) (71)6.3.2 相对寻址方式(REL) (71)6.3.3 立即寻址方式(IMM) (72)6.3.4 直接寻址方式(DIR) (72)6.3.5 扩展寻址方式(EXT) (72)6.3.6.1 无偏移量变址方式(IX) (73)6.3.6.2 无偏移量变址、变址加1寻址方式(IX+) (73)6.3.6.3 8位偏移量变址方式(IX1) (73)6.3.6.4 8位偏移量变址、变址加1寻址方式(IX1+) (73)6.3.6.5 16位偏移量变址方式(IX2) (73)6.3.6.6 8位偏移量堆栈寻址方式(SP1) (74)6.3.6.7 16位偏移量堆栈寻址方式(SP2) (74)6.4特殊操作 (75)6.4.1 复位序列 (75)6.4.2 中断 (76)6.4.3 等待模式 (76)6.4.4 停止模式 (76)6.4.5 背景模式 (77)6.4.6 总线周期的用户观点 (77)6.5通过指令类别进行指令集描述 (78)6.5.1 数据传送指令 (78)6.5.1.1 加载与存储 (78)6.5.1.2 位的置位与清零 (81)6.5.1.3 存储器到存储器的传送 (82)6.5.1.4 寄存器传输和半字节交换 (82)6.5.2 算术运算指令 (83)6.5.2.1 加、减、乘和除指令 (83)6.5.2.2 加一、减一、清零和求补 (88)6.5.2.3 比较和测试 (88)6.5.2.4 BCD的计算 (88)6.5.3 逻辑操作指令 (89)6.5.3.1 与、或、异或与求补 (90)6.5.3.2 位测试指令 (91)6.5.4 移位类指令 (91)6.5.5 跳转、转移和循环控制指令 (93)6.5.5.1 无条件跳转和转移指令 (94)6.5.5.2 简单转移 (95)6.5.5.3 有符号转移 (95)6.5.5.4 无符号转移 (95)6.5.5.5 位条件转移 (96)6.5.5.6 循环控制 (96)6.5.6 相关堆栈指令 (97)6.6指令简表 (102)6.7汇编语言指南 (114)6.7.1 列表行 (115)6.7.2 汇编指令 (116)6.7.2.1 BASE——设定编译器的缺省数进制 (116)6.7.2.2 INCLUDE——指定附加源文件 (116)6.7.2.3 NOLIST/LIST——关闭或打开程序列表 (116)6.7.2.4 ORG——设置程序的起始位置 (117)6.7.2.5 EQU——把一个标号和一个数值相关联 (118)6.7.2.6 dc.b——定义存储器中字节化常量 (119)6.7.2.7 dc.w——在存储器中定义16位(字)常量 (119)6.7.2.8 ds.b——定义存储(保留)内存变量字节 (120)6.7.3 标号 (121)6.7.4 表达式 (122)6.7.5 通用文件协议 (123)6.7.6 目标代码(S19)文件 (125)第七章开发支持 (129)7.1介绍 (129)7.2特点 (130)7.3背景调试控制器(BDC) (130)7.3.1 BKGD引脚描述 (131)7.3.2 通信细节 (132)7.3.2.1 BDC通信速率考虑事项 (132)7.3.2.2 位时序细节 (133)7.3.3 BDC寄存器和控制位 (135)7.3.3.1 BDC状态和控制寄存器 (135)7.3.3.2 BDC断点匹配寄存器 (137)7.3.4 BDC命令 (137)7.3.4.1 SYNC——要求时序参考脉冲 (138)7.3.4.2 ACK_ENABLE (139)7.3.4.3 ACK_DISABLE (139)7.3.4.4 BACKGROUND (139)7.3.4.5 READ_STATUS (140)7.3.4.6 WRITE_CONTROL (140)7.3.4.7 READ_BYTE (141)7.3.4.8 READ_BYTE_WS (142)7.3.4.10 WRITE_BYTE (143)7.3.4.11 WRITE_BYTE_WS (143)7.3.4.12 READ_BKPT (144)7.3.4.13 WRITE_BKPT (144)7.3.4.14 GO (144)7.3.4.15 TRACE1 (145)7.3.4.16 TAGGO (145)7.3.4.17 READ_A (145)7.3.4.18 READ_CCR (145)7.3.4.19 READ_PC (146)7.3.4.20 READ_HX (146)7.3.4.21 READ_SP (147)7.3.4.22 READ_NEXT (147)7.3.4.23 READ_NEXT_WS (148)7.3.4.24 WRITE_A (148)7.3.4.25 WRITE_CCR (148)7.3.4.26 WRITE_PC (149)7.3.4.27 WRITE_HX (149)7.3.4.28 WRITE_SP (149)7.3.4.29 WRITE_NEXT (149)7.3.4.30 WRITE_ NEXT_WS (150)7.3.5 串行接口硬件握手协议 (150)7.3.6 取消握手协议 (152)7.3.7 BDC硬件断点 (155)7.3.8 与M68HC12BDM的不同之处 (155)7.3.8.1 8位体系结构 (156)7.3.8.2 命令格式 (156)7.3.8.3 状态位的读写 (156)7.3.8.4 BDM与停止和等待模式 (157)7.3.8.5 SYNC指令 (157)7.3.8.6 硬件断点 (157)7.4标识部分和BDC强制复位 (158)7.4.1 系统设备识别寄存器(SDIDH:SDIDL) (158)7.4.2 系统背景调试强制复位寄存器 (158)7.5片上调试系统(DBG) (159)7.5.1 比较器A和B (159)7.5.2总线信息捕捉和FIFO操作 (160)7.5.4 标记与强制断点和触发器 (161)7.5.5 CPU断点请求 (162)7.5.6 触发模式 (162)7.5.6.1 单独A触发模式 (163)7.5.6.2 A或B触发模式 (163)7.5.6.3 A然后B触发模式 (163)7.5.6.4 事件B触发模式(存储数据) (163)7.5.6.5 A然后事件B触发模式(存储数据) (163)7.5.6.6 A和B数据触发(全模式) (164)7.5.6.7 A与非B数据触发(全模式) (164)7.5.6.8 触发范围内:A≤地址≤B (164)7.5.6.9 触发范围外:地址<A 或者地址>B (164)7.5.7 DBG寄存器和控制位 (165)7.5.7.1 调试比较器A的高地址页寄存器(DBGCAH) (165)7.5.7.2 调试比较器A的低位寄存器(DBGCAL) (165)7.5.7.3 调试比较器B的高地址页寄存器(DBGCAH) (165)7.5.7.4 调试比较器B的低位寄存器(DBGCAL) (165)7.5.7.5 调试FIFO高地址页寄存器(DBGFH) (165)7.5.7.6 调试FIFO低位寄存器(DBGFL) (165)7.5.7.7 调试控制寄存器(DBGC) (166)7.5.7.8 调试触发寄存器(DBGT) (167)7.5.7.9 调试状态寄存器(DBGS) (168)7.5.8 应用信息与举例 (169)7.5.8.1 定向的调试器例子 (171)7.5.8.2 例1:终止对地址A的处理 (171)7.5.8.3 例2:终止对地址A指令的处理 (172)7.5.8.4 例3:终止在地址A或B上的指令处理 (172)7.5.8.5 例4:开始跟踪在地址A的指令 (173)7.5.8.6 例5:A到B顺序后停止的尾部跟踪 (173)7.5.8.7 例6:起始跟踪数据B写入地址A (174)7.5.8.8 例7:从地址B中读取被捕获的首八位数据 (174)7.5.8.9 例8:捕获在读地址A后写入到地址B的值 (175)7.5.8.10 例9:在一个例程中触发所有的执行命令 (175)7.5.8.11 例10:通过触发来试图处理外部FLASH (176)7.5.9 硬件断点和ROM修补 (176)附录A 指令集详述 (177)A.2命名规则 (177)A.3规范定义 (180)A.4指令集 (180)ADC Add with Carry(带进位位加) (180)ADD Add without Carry(无进位位加) (181)AIS Add Immediate Value to Stack Pointer(立即数加到SP) (182)AIX Add Immediate Value to Index Register(立即数加到HX) (182)AND Logical AND(逻辑与) (183)ASL Arithmetic Shift Left(算术左移) (184)ASR Arithmetic Shift Right(算术右移) (184)BCC Branch if Carry Bit Clear(C为0则转移) (185)BCLR n Clear Bit n in Memory(内存单元n位清零) (185)BCS Branch if Carry Bit Set(C为1则转移) (186)BEQ Branch if Equal(等于则转移) (187)BGE Branch if Greater Than or Equal To(大于或等于则转移) (187)BGND Background(进入背景调试模式) (188)BGT Branch if Greater Than(大于则转移) (188)BHCC Branch if Half Carry Bit Clear(H为0则转移) (189)BHCS Branch if Half Carry Bit Set(H为1则转移) (189)BHI Branch if Higher(大于则转移) (190)BHS Branch if Higher or Same(大于或等于则转移) (191)BIH Branch if IRQ Pin High(引脚IRQ为1则转移) (191)BIL Branch if IRQ Pin Low(引脚IRQ为0则转移) (192)BIT Bit Test(位测试) (192)BLE Branch if Less Than or Equal To(小于或等于则转移) (193)BLO Branch if Lower(小于则转移) (193)BLS Branch if Lower or Same(小于或等于则转移) (194)BLT Branch if Less Than(小于则转移) (195)BMC Branch if Interrupt Mask Clear(I为0则转移) (195)BMI Branch if Minus(结果为负则转移) (196)BMS Branch if Interrupt Mask Set(I为1则转移) (196)BNE Branch if Not Equal(不等于则转移) (197)BPL Branch if Plus(结果为正则转移) (197)BRA Branch Always(无条件短转移) (198)BRCLR n Branch if Bit n in Memory Clear(M位n为0则转移) (199)BRN Branch Never(三个总线周期的空操作) (200)BRSET n Branch if Bit n in Memory Set(M位n为1则转移) (200)BSET n Set Bit n in Memory(M位n置1) (201)BSR Branch to Subroutine(转移到子程序) (201)CBEQ Compare and Branch if Equal(比较,等于则转移) (202)CLC Clear Carry Bit(进位位C清零) (203)CLI Clear Interrupt Mask Bit(中断屏蔽位I清零) (203)CLR Clear(清零) (204)CMP Compare Accumulator with Memory(A与M比较) (204)COM Complement(按位取反) (205)CPHX Compare Index Register with Memory(HX与M比较) (206)CPX Compare X with Memory(X与M比较) (207)DAA Decimal Adjust Accumulator(A十进制调整) (208)DBNZ Decrement and Branch if Not Zero(减1不为0则转移) (209)DEC Decrement(自减1) (209)DIV Divide(无符号除法) (210)EOR Exclusive-OR Memory with Accumulator(M与A异或) (211)INC Increment(自加1) (211)JMP Jump(无条件跳转) (212)JSR Jump to Subroutine(跳转到子程序) (213)LDA Load Accumulator form Memory(取M内容到A) (213)LDHX Load Index Register form Memory(取M内容到HX) (214)LDX Load X from Memory(取M内容到X) (215)LSL Logical Shift Left(逻辑左移) (215)LSR Logical Shift Right(逻辑右移) (216)MOV Move(M单元间数据传送) (217)MUL Unsigned Multiply(无符号数乘法) (218)NEG Negate(Two’s Complement) (求补) (218)NOP No Operation(空操作) (219)NSA Nibble Swap Accumulator(A的高低4位对调) (219)ORA Inclusive-OR Accumulator and Memory(逻辑或) (220)PSHA Push Accumulator onto Stack(A进栈) (220)PSHH Push H onto Stack(H进栈) (221)PSHX Push X onto Stack(X进栈) (221)PULA Pull Accumulator from Stack(A出栈) (222)PULH Pull H from Stack(H出栈) (222)PULX Pull X from Stack(X出栈) (223)ROL Rotate Left through Carry(带进位位的循环左移) (223)ROR Rotate Right through Carry(带进位位的循环右移) (224)RSP Reset Stack Pointer(堆栈指针置$FF) (224)RTI Return from interrupt(中断返回) (225)RTS Return from Subroutine(子程序返回) (226)SBC Subtract with Carry(带借位减法) (226)SEC Set Carry Bit(进位位置位) (227)SEI Set Interrupt Mask Bit(中断屏蔽位置位) (227)STA Store Accumulator in Memory(A存入M) (228)STHX Store Index Register(HX存入M) (229)STOP Enable IRQ Pin, Stop Processing(停机) (229)STX Store X in Memory(X存入M) (230)SUB Subtract(无借位减法) (231)SWI Software Interrupt(软件中断) (231)TAP Transfer Accumulator to Processor Status Byte(写CCR) (232)TAX Transfer Accumulator to X(A复制到X) (233)TPA Transfer Processor Status Byte to Accumulator(读CCR) (233)TST Test for Negative or Zero(小于或等于0测试) (234)TSX Transfer Stack Pointer to index Register(复制SP到HX) (235)TXA Transfer X to Accumulator(复制X到A) (235)TXS Transfer Index Register Low to Stack Pointer(HX-1写入SP) (235)WAIT Enable Interrupts; Stop Processor(待机) (236)附录B 通用文件规范 (237)B.1引言 (237)B.2存储映射区域划分 (238)B.3中断向量定义 (238)B.4位定义的两种方式 (239)B.5MC9S08GB60完整的通用文件 (240)第一章通用信息与结构框图1.1 HCS08系列微控制器介绍新型的FreescaleHCS08系列微控制器,尽管包含新指令,可以执行快速调试和开发功能,但仍然和旧的M68HC08系列完全兼容。

NUC130中文手册

3

编号信息列表及管脚名称定义 ................................................................................................... 12

3.1 NuMicro™ NUC130产品选型指南 ................................................................................. 12

3.2.1 NuMicro™ NUC130管脚图 ..............................................................................................13

3.3 管脚功能描述 ................................................................................................................ 16

5.5 I2C 串行接口控制器 (Master/Slave) (I2C)...................................................................... 44

5.5.1 概述.................................................................................................................................44 5.5.2 特征.................................................................................................................................45

NuMicro N9H30系列开发板用户手册说明书

NuMicro®FamilyArm® ARM926EJ-S BasedNuMaker-HMI-N9H30User ManualEvaluation Board for NuMicro® N9H30 SeriesNUMAKER-HMI-N9H30 USER MANUALThe information described in this document is the exclusive intellectual property ofNuvoton Technology Corporation and shall not be reproduced without permission from Nuvoton.Nuvoton is providing this document only for reference purposes of NuMicro microcontroller andmicroprocessor based system design. Nuvoton assumes no responsibility for errors or omissions.All data and specifications are subject to change without notice.For additional information or questions, please contact: Nuvoton Technology Corporation.Table of Contents1OVERVIEW (5)1.1Features (7)1.1.1NuMaker-N9H30 Main Board Features (7)1.1.2NuDesign-TFT-LCD7 Extension Board Features (7)1.2Supporting Resources (8)2NUMAKER-HMI-N9H30 HARDWARE CONFIGURATION (9)2.1NuMaker-N9H30 Board - Front View (9)2.2NuMaker-N9H30 Board - Rear View (14)2.3NuDesign-TFT-LCD7 - Front View (20)2.4NuDesign-TFT-LCD7 - Rear View (21)2.5NuMaker-N9H30 and NuDesign-TFT-LCD7 PCB Placement (22)3NUMAKER-N9H30 AND NUDESIGN-TFT-LCD7 SCHEMATICS (24)3.1NuMaker-N9H30 - GPIO List Circuit (24)3.2NuMaker-N9H30 - System Block Circuit (25)3.3NuMaker-N9H30 - Power Circuit (26)3.4NuMaker-N9H30 - N9H30F61IEC Circuit (27)3.5NuMaker-N9H30 - Setting, ICE, RS-232_0, Key Circuit (28)NUMAKER-HMI-N9H30 USER MANUAL3.6NuMaker-N9H30 - Memory Circuit (29)3.7NuMaker-N9H30 - I2S, I2C_0, RS-485_6 Circuit (30)3.8NuMaker-N9H30 - RS-232_2 Circuit (31)3.9NuMaker-N9H30 - LCD Circuit (32)3.10NuMaker-N9H30 - CMOS Sensor, I2C_1, CAN_0 Circuit (33)3.11NuMaker-N9H30 - RMII_0_PF Circuit (34)3.12NuMaker-N9H30 - RMII_1_PE Circuit (35)3.13NuMaker-N9H30 - USB Circuit (36)3.14NuDesign-TFT-LCD7 - TFT-LCD7 Circuit (37)4REVISION HISTORY (38)List of FiguresFigure 1-1 Front View of NuMaker-HMI-N9H30 Evaluation Board (5)Figure 1-2 Rear View of NuMaker-HMI-N9H30 Evaluation Board (6)Figure 2-1 Front View of NuMaker-N9H30 Board (9)Figure 2-2 Rear View of NuMaker-N9H30 Board (14)Figure 2-3 Front View of NuDesign-TFT-LCD7 Board (20)Figure 2-4 Rear View of NuDesign-TFT-LCD7 Board (21)Figure 2-5 Front View of NuMaker-N9H30 PCB Placement (22)Figure 2-6 Rear View of NuMaker-N9H30 PCB Placement (22)Figure 2-7 Front View of NuDesign-TFT-LCD7 PCB Placement (23)Figure 2-8 Rear View of NuDesign-TFT-LCD7 PCB Placement (23)Figure 3-1 GPIO List Circuit (24)Figure 3-2 System Block Circuit (25)Figure 3-3 Power Circuit (26)Figure 3-4 N9H30F61IEC Circuit (27)Figure 3-5 Setting, ICE, RS-232_0, Key Circuit (28)Figure 3-6 Memory Circuit (29)Figure 3-7 I2S, I2C_0, RS-486_6 Circuit (30)Figure 3-8 RS-232_2 Circuit (31)Figure 3-9 LCD Circuit (32)NUMAKER-HMI-N9H30 USER MANUAL Figure 3-10 CMOS Sensor, I2C_1, CAN_0 Circuit (33)Figure 3-11 RMII_0_PF Circuit (34)Figure 3-12 RMII_1_PE Circuit (35)Figure 3-13 USB Circuit (36)Figure 3-14 TFT-LCD7 Circuit (37)List of TablesTable 2-1 LCD Panel Combination Connector (CON8) Pin Function (11)Table 2-2 Three Sets of Indication LED Functions (12)Table 2-3 Six Sets of User SW, Key Matrix Functions (12)Table 2-4 CMOS Sensor Connector (CON10) Function (13)Table 2-5 JTAG ICE Interface (J2) Function (14)Table 2-6 Expand Port (CON7) Function (16)Table 2-7 UART0 (J3) Function (16)Table 2-8 UART2 (J6) Function (16)Table 2-9 RS-485_6 (SW6~8) Function (17)Table 2-10 Power on Setting (SW4) Function (17)Table 2-11 Power on Setting (S2) Function (17)Table 2-12 Power on Setting (S3) Function (17)Table 2-13 Power on Setting (S4) Function (17)Table 2-14 Power on Setting (S5) Function (17)Table 2-15 Power on Setting (S7/S6) Function (18)Table 2-16 Power on Setting (S9/S8) Function (18)Table 2-17 CMOS Sensor Connector (CON9) Function (19)Table 2-18 CAN_0 (SW9~10) Function (19)NUMAKER-HMI-N9H30 USER MANUAL1 OVERVIEWThe NuMaker-HMI-N9H30 is an evaluation board for GUI application development. The NuMaker-HMI-N9H30 consists of two parts: a NuMaker-N9H30 main board and a NuDesign-TFT-LCD7 extensionboard. The NuMaker-HMI-N9H30 is designed for project evaluation, prototype development andvalidation with HMI (Human Machine Interface) function.The NuMaker-HMI-N9H30 integrates touchscreen display, voice input/output, rich serial port serviceand I/O interface, providing multiple external storage methods.The NuDesign-TFT-LCD7 can be plugged into the main board via the DIN_32x2 extension connector.The NuDesign-TFT-LCD7 includes one 7” LCD which the resolution is 800x480 with RGB-24bits andembedded the 4-wires resistive type touch panel.Figure 1-1 Front View of NuMaker-HMI-N9H30 Evaluation BoardNUMAKER-HMI-N9H30 USER MANUAL Figure 1-2 Rear View of NuMaker-HMI-N9H30 Evaluation Board1.1 Features1.1.1 NuMaker-N9H30 Main Board Features●N9H30F61IEC chip: LQFP216 pin MCP package with DDR (64 MB)●SPI Flash using W25Q256JVEQ (32 MB) booting with quad mode or storage memory●NAND Flash using W29N01HVSINA (128 MB) booting or storage memory●One Micro-SD/TF card slot served either as a SD memory card for data storage or SDIO(Wi-Fi) device●Two sets of COM ports:–One DB9 RS-232 port with UART_0 used 75C3232E transceiver chip can be servedfor function debug and system development.–One DB9 RS-232 port with UART_2 used 75C3232E transceiver chip for userapplication●22 GPIO expansion ports, including seven sets of UART functions●JTAG interface provided for software development●Microphone input and Earphone/Speaker output with 24-bit stereo audio codec(NAU88C22) for I2S interfaces●Six sets of user-configurable push button keys●Three sets of LEDs for status indication●Provides SN65HVD230 transceiver chip for CAN bus communication●Provides MAX3485 transceiver chip for RS-485 device connection●One buzzer device for program applicationNUMAKER-HMI-N9H30 USER MANUAL●Two sets of RJ45 ports with Ethernet 10/100 Mbps MAC used IP101GR PHY chip●USB_0 that can be used as Device/HOST and USB_1 that can be used as HOSTsupports pen drives, keyboards, mouse and printers●Provides over-voltage and over current protection used APL3211A chip●Retain RTC battery socket for CR2032 type and ADC0 detect battery voltage●System power could be supplied by DC-5V adaptor or USB VBUS1.1.2 NuDesign-TFT-LCD7 Extension Board Features●7” resolution 800x480 4-wire resistive touch panel for 24-bits RGB888 interface●DIN_32x2 extension connector1.2 Supporting ResourcesFor sample codes and introduction about NuMaker-N9H30, please refer to N9H30 BSP:https:///products/gui-solution/gui-platform/numaker-hmi-n9h30/?group=Software&tab=2Visit NuForum for further discussion about the NuMaker-HMI-N9H30:/viewforum.php?f=31 NUMAKER-HMI-N9H30 USER MANUALNUMAKER-HMI-N9H30 USER MANUAL2 NUMAKER-HMI-N9H30 HARDWARE CONFIGURATION2.1 NuMaker-N9H30 Board - Front View Combination Connector (CON8)6 set User SWs (K1~6)3set Indication LEDs (LED1~3)Power Supply Switch (SW_POWER1)Audio Codec(U10)Microphone(M1)NAND Flash(U9)RS-232 Transceiver(U6, U12)RS-485 Transceiver(U11)CAN Transceiver (U13)Figure 2-1 Front View of NuMaker-N9H30 BoardFigure 2-1 shows the main components and connectors from the front side of NuMaker-N9H30 board. The following lists components and connectors from the front view:NuMaker-N9H30 board and NuDesign-TFT-LCD7 board combination connector (CON8). This panel connector supports 4-/5-wire resistive touch or capacitance touch panel for 24-bits RGB888 interface.Connector GPIO pin of N9H30 FunctionCON8.1 - Power 3.3VCON8.2 - Power 3.3VCON8.3 GPD7 LCD_CSCON8.4 GPH3 LCD_BLENCON8.5 GPG9 LCD_DENCON8.7 GPG7 LCD_HSYNCCON8.8 GPG6 LCD_CLKCON8.9 GPD15 LCD_D23(R7)CON8.10 GPD14 LCD_D22(R6)CON8.11 GPD13 LCD_D21(R5)CON8.12 GPD12 LCD_D20(R4)CON8.13 GPD11 LCD_D19(R3)CON8.14 GPD10 LCD_D18(R2)CON8.15 GPD9 LCD_D17(R1)CON8.16 GPD8 LCD_D16(R0)CON8.17 GPA15 LCD_D15(G7)CON8.18 GPA14 LCD_D14(G6)CON8.19 GPA13 LCD_D13(G5)CON8.20 GPA12 LCD_D12(G4)CON8.21 GPA11 LCD_D11(G3)CON8.22 GPA10 LCD_D10(G2)CON8.23 GPA9 LCD_D9(G1) NUMAKER-HMI-N9H30 USER MANUALCON8.24 GPA8 LCD_D8(G0)CON8.25 GPA7 LCD_D7(B7)CON8.26 GPA6 LCD_D6(B6)CON8.27 GPA5 LCD_D5(B5)CON8.28 GPA4 LCD_D4(B4)CON8.29 GPA3 LCD_D3(B3)CON8.30 GPA2 LCD_D2(B2)CON8.31 GPA1 LCD_D1(B1)CON8.32 GPA0 LCD_D0(B0)CON8.33 - -CON8.34 - -CON8.35 - -CON8.36 - -CON8.37 GPB2 LCD_PWMCON8.39 - VSSCON8.40 - VSSCON8.41 ADC7 XPCON8.42 ADC3 VsenCON8.43 ADC6 XMCON8.44 ADC4 YMCON8.45 - -CON8.46 ADC5 YPCON8.47 - VSSCON8.48 - VSSCON8.49 GPG0 I2C0_CCON8.50 GPG1 I2C0_DCON8.51 GPG5 TOUCH_INTCON8.52 - -CON8.53 - -CON8.54 - -CON8.55 - -NUMAKER-HMI-N9H30 USER MANUAL CON8.56 - -CON8.57 - -CON8.58 - -CON8.59 - VSSCON8.60 - VSSCON8.61 - -CON8.62 - -CON8.63 - Power 5VCON8.64 - Power 5VTable 2-1 LCD Panel Combination Connector (CON8) Pin Function●Power supply switch (SW_POWER1): System will be powered on if the SW_POWER1button is pressed●Three sets of indication LEDs:LED Color DescriptionsLED1 Red The system power will beterminated and LED1 lightingwhen the input voltage exceeds5.7V or the current exceeds 2A.LED2 Green Power normal state.LED3 Green Controlled by GPH2 pin Table 2-2 Three Sets of Indication LED Functions●Six sets of user SW, Key Matrix for user definitionKey GPIO pin of N9H30 FunctionK1 GPF10 Row0 GPB4 Col0K2 GPF10 Row0 GPB5 Col1K3 GPE15 Row1 GPB4 Col0K4 GPE15 Row1 GPB5 Col1K5 GPE14 Row2 GPB4 Col0K6GPE14 Row2GPB5 Col1 Table 2-3 Six Sets of User SW, Key Matrix Functions●NAND Flash (128 MB) with Winbond W29N01HVS1NA (U9)●Microphone (M1): Through Nuvoton NAU88C22 chip sound input●Audio CODEC chip (U10): Nuvoton NAU88C22 chip connected to N9H30 using I2Sinterface–SW6/SW7/SW8: 1-2 short for RS-485_6 function and connected to 2P terminal (CON5and J5)–SW6/SW7/SW8: 2-3 short for I2S function and connected to NAU88C22 (U10).●CMOS Sensor connector (CON10, SW9~10)–SW9~10: 1-2 short for CAN_0 function and connected to 2P terminal (CON11)–SW9~10: 2-3 short for CMOS sensor function and connected to CMOS sensorconnector (CON10)Connector GPIO pin of N9H30 FunctionCON10.1 - VSSCON10.2 - VSSNUMAKER-HMI-N9H30 USER MANUALCON10.3 - Power 3.3VCON10.4 - Power 3.3VCON10.5 - -CON10.6 - -CON10.7 GPI4 S_PCLKCON10.8 GPI3 S_CLKCON10.9 GPI8 S_D0CON10.10 GPI9 S_D1CON10.11 GPI10 S_D2CON10.12 GPI11 S_D3CON10.13 GPI12 S_D4CON10.14 GPI13 S_D5CON10.15 GPI14 S_D6CON10.16 GPI15 S_D7CON10.17 GPI6 S_VSYNCCON10.18 GPI5 S_HSYNCCON10.19 GPI0 S_PWDNNUMAKER-HMI-N9H30 USER MANUAL CON10.20 GPI7 S_nRSTCON10.21 GPG2 I2C1_CCON10.22 GPG3 I2C1_DCON10.23 - VSSCON10.24 - VSSTable 2-4 CMOS Sensor Connector (CON10) FunctionNUMAKER-HMI-N9H30 USER MANUAL2.2NuMaker-N9H30 Board - Rear View5V In (CON1)RS-232 DB9 (CON2,CON6)Expand Port (CON7)Speaker Output (J4)Earphone Output (CON4)Buzzer (BZ1)System ResetSW (SW5)SPI Flash (U7,U8)JTAG ICE (J2)Power ProtectionIC (U1)N9H30F61IEC (U5)Micro SD Slot (CON3)RJ45 (CON12, CON13)USB1 HOST (CON15)USB0 Device/Host (CON14)CAN_0 Terminal (CON11)CMOS Sensor Connector (CON9)Power On Setting(SW4, S2~S9)RS-485_6 Terminal (CON5)RTC Battery(BT1)RMII PHY (U14,U16)Figure 2-2 Rear View of NuMaker-N9H30 BoardFigure 2-2 shows the main components and connectors from the rear side of NuMaker-N9H30 board. The following lists components and connectors from the rear view:● +5V In (CON1): Power adaptor 5V input ●JTAG ICE interface (J2) ConnectorGPIO pin of N9H30Function J2.1 - Power 3.3V J2.2 GPJ4 nTRST J2.3 GPJ2 TDI J2.4 GPJ1 TMS J2.5 GPJ0 TCK J2.6 - VSS J2.7 GPJ3 TD0 J2.8-RESETTable 2-5 JTAG ICE Interface (J2) Function●SPI Flash (32 MB) with Winbond W25Q256JVEQ (U7); only one (U7 or U8) SPI Flashcan be used●System Reset (SW5): System will be reset if the SW5 button is pressed●Buzzer (BZ1): Control by GPB3 pin of N9H30●Speaker output (J4): Through the NAU88C22 chip sound output●Earphone output (CON4): Through the NAU88C22 chip sound output●Expand port for user use (CON7):Connector GPIO pin of N9H30 FunctionCON7.1 - Power 3.3VCON7.2 - Power 3.3VCON7.3 GPE12 UART3_TXDCON7.4 GPH4 UART1_TXDCON7.5 GPE13 UART3_RXDCON7.6 GPH5 UART1_RXDCON7.7 GPB0 UART5_TXDCON7.8 GPH6 UART1_RTSCON7.9 GPB1 UART5_RXDCON7.10 GPH7 UART1_CTSCON7.11 GPI1 UART7_TXDNUMAKER-HMI-N9H30 USER MANUAL CON7.12 GPH8 UART4_TXDCON7.13 GPI2 UART7_RXDCON7.14 GPH9 UART4_RXDCON7.15 - -CON7.16 GPH10 UART4_RTSCON7.17 - -CON7.18 GPH11 UART4_CTSCON7.19 - VSSCON7.20 - VSSCON7.21 GPB12 UART10_TXDCON7.22 GPH12 UART8_TXDCON7.23 GPB13 UART10_RXDCON7.24 GPH13 UART8_RXDCON7.25 GPB14 UART10_RTSCON7.26 GPH14 UART8_RTSCON7.27 GPB15 UART10_CTSCON7.28 GPH15 UART8_CTSCON7.29 - Power 5VCON7.30 - Power 5VTable 2-6 Expand Port (CON7) Function●UART0 selection (CON2, J3):–RS-232_0 function and connected to DB9 female (CON2) for debug message output.–GPE0/GPE1 connected to 2P terminal (J3).Connector GPIO pin of N9H30 Function J3.1 GPE1 UART0_RXDJ3.2 GPE0 UART0_TXDTable 2-7 UART0 (J3) Function●UART2 selection (CON6, J6):–RS-232_2 function and connected to DB9 female (CON6) for debug message output –GPF11~14 connected to 4P terminal (J6)Connector GPIO pin of N9H30 Function J6.1 GPF11 UART2_TXDJ6.2 GPF12 UART2_RXDJ6.3 GPF13 UART2_RTSJ6.4 GPF14 UART2_CTSTable 2-8 UART2 (J6) Function●RS-485_6 selection (CON5, J5, SW6~8):–SW6~8: 1-2 short for RS-485_6 function and connected to 2P terminal (CON5 and J5) –SW6~8: 2-3 short for I2S function and connected to NAU88C22 (U10)Connector GPIO pin of N9H30 FunctionSW6:1-2 shortGPG11 RS-485_6_DISW6:2-3 short I2S_DOSW7:1-2 shortGPG12 RS-485_6_ROSW7:2-3 short I2S_DISW8:1-2 shortGPG13 RS-485_6_ENBSW8:2-3 short I2S_BCLKNUMAKER-HMI-N9H30 USER MANUALTable 2-9 RS-485_6 (SW6~8) FunctionPower on setting (SW4, S2~9).SW State FunctionSW4.2/SW4.1 ON/ON Boot from USB SW4.2/SW4.1 ON/OFF Boot from eMMC SW4.2/SW4.1 OFF/ON Boot from NAND Flash SW4.2/SW4.1 OFF/OFF Boot from SPI Flash Table 2-10 Power on Setting (SW4) FunctionSW State FunctionS2 Short System clock from 12MHzcrystalS2 Open System clock from UPLL output Table 2-11 Power on Setting (S2) FunctionSW State FunctionS3 Short Watchdog Timer OFFS3 Open Watchdog Timer ON Table 2-12 Power on Setting (S3) FunctionSW State FunctionS4 Short GPJ[4:0] used as GPIO pinS4Open GPJ[4:0] used as JTAG ICEinterfaceTable 2-13 Power on Setting (S4) FunctionSW State FunctionS5 Short UART0 debug message ONS5 Open UART0 debug message OFFTable 2-14 Power on Setting (S5) FunctionSW State FunctionS7/S6 Short/Short NAND Flash page size 2KBS7/S6 Short/Open NAND Flash page size 4KBS7/S6 Open/Short NAND Flash page size 8KBNUMAKER-HMI-N9H30 USER MANUALS7/S6 Open/Open IgnoreTable 2-15 Power on Setting (S7/S6) FunctionSW State FunctionS9/S8 Short/Short NAND Flash ECC type BCH T12S9/S8 Short/Open NAND Flash ECC type BCH T15S9/S8 Open/Short NAND Flash ECC type BCH T24S9/S8 Open/Open IgnoreTable 2-16 Power on Setting (S9/S8) FunctionCMOS Sensor connector (CON9, SW9~10)–SW9~10: 1-2 short for CAN_0 function and connected to 2P terminal (CON11).–SW9~10: 2-3 short for CMOS sensor function and connected to CMOS sensorconnector (CON9).Connector GPIO pin of N9H30 FunctionCON9.1 - VSSCON9.2 - VSSCON9.3 - Power 3.3VCON9.4 - Power 3.3V NUMAKER-HMI-N9H30 USER MANUALCON9.5 - -CON9.6 - -CON9.7 GPI4 S_PCLKCON9.8 GPI3 S_CLKCON9.9 GPI8 S_D0CON9.10 GPI9 S_D1CON9.11 GPI10 S_D2CON9.12 GPI11 S_D3CON9.13 GPI12 S_D4CON9.14 GPI13 S_D5CON9.15 GPI14 S_D6CON9.16 GPI15 S_D7CON9.17 GPI6 S_VSYNCCON9.18 GPI5 S_HSYNCCON9.19 GPI0 S_PWDNCON9.20 GPI7 S_nRSTCON9.21 GPG2 I2C1_CCON9.22 GPG3 I2C1_DCON9.23 - VSSCON9.24 - VSSTable 2-17 CMOS Sensor Connector (CON9) Function●CAN_0 Selection (CON11, SW9~10):–SW9~10: 1-2 short for CAN_0 function and connected to 2P terminal (CON11) –SW9~10: 2-3 short for CMOS sensor function and connected to CMOS sensor connector (CON9, CON10)SW GPIO pin of N9H30 FunctionSW9:1-2 shortGPI3 CAN_0_RXDSW9:2-3 short S_CLKSW10:1-2 shortGPI4 CAN_0_TXDSW10:2-3 short S_PCLKTable 2-18 CAN_0 (SW9~10) Function●USB0 Device/HOST Micro-AB connector (CON14), where CON14 pin4 ID=1 is Device,ID=0 is HOST●USB1 for USB HOST with Type-A connector (CON15)●RJ45_0 connector with LED indicator (CON12), RMII PHY with IP101GR (U14)●RJ45_1 connector with LED indicator (CON13), RMII PHY with IP101GR (U16)●Micro-SD/TF card slot (CON3)●SOC CPU: Nuvoton N9H30F61IEC (U5)●Battery power for RTC 3.3V powered (BT1, J1), can detect voltage by ADC0●RTC power has 3 sources:–Share with 3.3V I/O power–Battery socket for CR2032 (BT1)–External connector (J1)●Board version 2.1NUMAKER-HMI-N9H30 USER MANUAL2.3 NuDesign-TFT-LCD7 -Front ViewFigure 2-3 Front View of NuDesign-TFT-LCD7 BoardFigure 2-3 shows the main components and connectors from the Front side of NuDesign-TFT-LCD7board.7” resolution 800x480 4-W resistive touch panel for 24-bits RGB888 interface2.4 NuDesign-TFT-LCD7 -Rear ViewFigure 2-4 Rear View of NuDesign-TFT-LCD7 BoardFigure 2-4 shows the main components and connectors from the rear side of NuDesign-TFT-LCD7board.NuMaker-N9H30 and NuDesign-TFT-LCD7 combination connector (CON1).NUMAKER-HMI-N9H30 USER MANUAL 2.5 NuMaker-N9H30 and NuDesign-TFT-LCD7 PCB PlacementFigure 2-5 Front View of NuMaker-N9H30 PCB PlacementFigure 2-6 Rear View of NuMaker-N9H30 PCB PlacementNUMAKER-HMI-N9H30 USER MANUALFigure 2-7 Front View of NuDesign-TFT-LCD7 PCB PlacementFigure 2-8 Rear View of NuDesign-TFT-LCD7 PCB Placement3 NUMAKER-N9H30 AND NUDESIGN-TFT-LCD7 SCHEMATICS3.1 NuMaker-N9H30 - GPIO List CircuitFigure 3-1 shows the N9H30F61IEC GPIO list circuit.Figure 3-1 GPIO List Circuit NUMAKER-HMI-N9H30 USER MANUAL3.2 NuMaker-N9H30 - System Block CircuitFigure 3-2 shows the System Block Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-2 System Block Circuit3.3 NuMaker-N9H30 - Power CircuitFigure 3-3 shows the Power Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-3 Power Circuit3.4 NuMaker-N9H30 - N9H30F61IEC CircuitFigure 3-4 shows the N9H30F61IEC Circuit.Figure 3-4 N9H30F61IEC CircuitNUMAKER-HMI-N9H30 USER MANUAL3.5 NuMaker-N9H30 - Setting, ICE, RS-232_0, Key CircuitFigure 3-5 shows the Setting, ICE, RS-232_0, Key Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-5 Setting, ICE, RS-232_0, Key Circuit3.6 NuMaker-N9H30 - Memory CircuitFigure 3-6 shows the Memory Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-6 Memory Circuit3.7 NuMaker-N9H30 - I2S, I2C_0, RS-485_6 CircuitFigure 3-7 shows the I2S, I2C_0, RS-486_6 Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-7 I2S, I2C_0, RS-486_6 Circuit3.8 NuMaker-N9H30 - RS-232_2 CircuitFigure 3-8 shows the RS-232_2 Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-8 RS-232_2 Circuit3.9 NuMaker-N9H30 - LCD CircuitFigure 3-9 shows the LCD Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-9 LCD Circuit3.10 NuMaker-N9H30 - CMOS Sensor, I2C_1, CAN_0 CircuitFigure 3-10 shows the CMOS Sensor,I2C_1, CAN_0 Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-10 CMOS Sensor, I2C_1, CAN_0 Circuit3.11 NuMaker-N9H30 - RMII_0_PF CircuitFigure 3-11 shows the RMII_0_RF Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-11 RMII_0_PF Circuit3.12 NuMaker-N9H30 - RMII_1_PE CircuitFigure 3-12 shows the RMII_1_PE Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-12 RMII_1_PE Circuit3.13 NuMaker-N9H30 - USB CircuitFigure 3-13 shows the USB Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-13 USB Circuit3.14 NuDesign-TFT-LCD7 - TFT-LCD7 CircuitFigure 3-14 shows the TFT-LCD7 Circuit.Figure 3-14 TFT-LCD7 CircuitNUMAKER-HMI-N9H30 USER MANUAL4 REVISION HISTORYDate Revision Description2022.03.24 1.00 Initial version NUMAKER-HMI-N9H30 USER MANUALNUMAKER-HMI-N9H30 USER MANUALImportant NoticeNuvoton Products are neither intended nor warranted for usage in systems or equipment, anymalfunction or failure of which may cause loss of human life, bodily injury or severe propertydamage. Such applications are deemed, “Insecure Usage”.Insecure usage includes, but is not limited to: equipment for surgical implementation, atomicenergy control instruments, airplane or spaceship instruments, the control or operation ofdynamic, brake or safety systems designed for vehicular use, traffic signal instruments, all typesof safety devices, and other applications intended to support or sustain life.All Insecure Usage shall be made at customer’s risk, and in the event that third parties lay claimsto Nuvoton as a result of customer’s Insecure Usage, custome r shall indemnify the damagesand liabilities thus incurred by Nuvoton.。

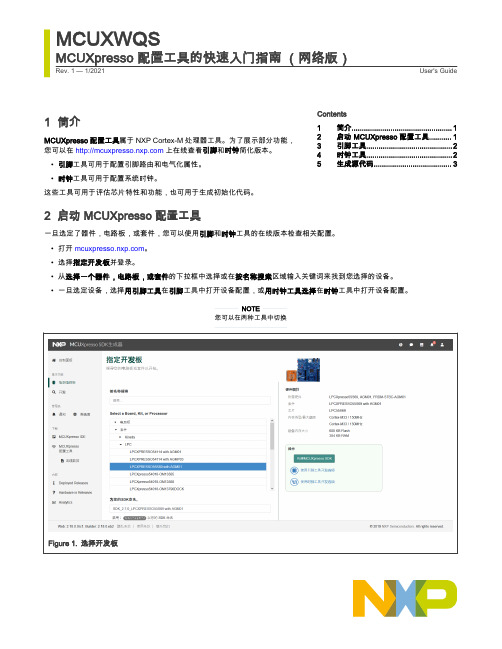

MCUXpresso 配置工具的快速入门指南(网络版)说明书

1简介MCUXpresso 配置工具属于 NXP Cortex-M 处理器工具。

为了展示部分功能,您可以在 上在线查看引脚和时钟简化版本。

•引脚工具可用于配置引脚路由和电气化属性。

•时钟工具可用于配置系统时钟。

这些工具可用于评估芯片特性和功能,也可用于生成初始化代码。

2启动 MCUXpresso 配置工具一旦选定了器件,电路板,或套件,您可以使用引脚和时钟工具的在线版本检查相关配置。

•打开 。

•选择指定开发板并登录。

•从选择一个器件,电路板,或套件的下拉框中选择或在按名称搜索区域输入关键词来找到您选择的设备。

•一旦选定设备,选择用引脚工具在引脚工具中打开设备配置,或用时钟工具选择在时钟工具中打开设备配置。

您可以在两种工具中切换Figure 1.选择开发板Contents 1简介.................................................12启动 MCUXpresso 配置工具...........13引脚工具..........................................24时钟工具..........................................25生成源代码.. (3)MCUXWQSMCUXpresso 配置工具的快速入门指南 (网络版)Rev. 1 — 1/2021User's Guide所有的工具设置会被保存于配置中。

3引脚工具引脚工具允许显示和配置处理器的引脚。

可在引脚、外设信号或封装视图中完成基本配置。

可在路由引脚视图中调整更高级的设置(引脚电气功能)。

Figure 2.引脚工具4时钟工具时钟工具允许在时钟表视图中显示和更改时钟源以及输出设置。

可通过时钟显示图和详情视图调整更高级的设置。

可在时钟表,时钟显示图,和详情视图中更改时钟环境全局设置,例如运行模式、MCG 模式和 SCG 模式。

Figure 3.时钟工具5生成源代码在主菜单中,选择视图 > 源代码来打开源代码界面以查看生成的源代码。

arm cortex m0+ io位操作

标题:深入理解ARM Cortex M0+ IO位操作一、概述ARM Cortex M0+是一款高性能、低功耗的嵌入式处理器,广泛应用于各种智能设备中。

在嵌入式系统开发中,IO位操作是一项基础而重要的操作。

本文将深入探讨ARM Cortex M0+的IO位操作,帮助读者更好地理解和应用这一技术。

二、ARM Cortex M0+概述1. ARM Cortex M0+架构简介ARM Cortex M0+是ARM公司推出的一款低功耗、高性能的嵌入式处理器。

它采用了ARMv6-M架构,具有高效的指令集和丰富的外设接口,适用于各种嵌入式应用场景。

2. 特点和优势ARM Cortex M0+具有低功耗、高性能、易于集成和灵活性等特点,可以满足各种嵌入式设备的需求。

它在物联网、智能家居、工业控制等领域得到了广泛应用。

三、IO位操作详解1. 概念介绍IO位操作是指对处理器的IO口进行读写操作,通过设置或清除特定的位来实现对IO口状态的控制。

在ARM Cortex M0+中,IO位操作通常涉及到寄存器的操作,读写寄存器的特定位来控制IO口。

2. 寄存器架构ARM Cortex M0+的寄存器包括通用寄存器(General Register)、特殊功能寄存器(Special Function Register)等。

在进行IO位操作时,需要了解相关寄存器的结构和功能。

3. IO位操作示例以下是一个简单的IO位操作示例,以LED控制为例:```c// 设置IO口为输出GPIO->DIR |= (1 << 5);// 打开LEDGPIO->DATA |= (1 << 5);// 关闭LEDGPIO->DATA = ~(1 << 5);```四、IO位操作的应用场景与意义1. 应用场景在嵌入式系统开发中,IO位操作广泛应用于外设控制、状态检测、通信协议等方面。

通过合理的IO位操作,可以实现对各种外设的控制和数据交换。

Keil AMetal平台快速入门手册说明书

快速入门手册 (keil) AMetal 平台 UM01010101 1.0.00 Data:2019/08/18©2019 Guangzhou ZHIYUAN Micro Electronics Co., Ltd修订历史目录1. 简介 (2)2. 搭建开发环境 (3)2.1环境简介 (3)2.1.1Keil µVision 集成开发环境 (3)2.1.2仿真器 (3)2.2MDK-ARM 软件安装 (3)2.2.1MDK-ARM 软件获取 (3)2.2.2MDK-ARM 软件安装 (2)2.3支持包(PACK)的安装 (6)2.3.1支持包(PACK)的获取 (6)2.3.2支持包(PACK)的安装 (8)2.4安装J-Link 软件及J-Link 仿真器驱动 (13)2.4.1J-Link 软件安装4 (13)2.4.2J-Link 仿真器驱动安装 (15)2.5安装TKScope 软件及CK100 仿真器驱动 (19)2.5.1TKScope 软件安装 (19)2.5.2安装VC8 实时运行库装 (24)2.5.3CK100 仿真器驱动安装 (25)3. 编写应用程序 (30)3.1从模板新建工程 (30)3.1.1打开工程 (33)3.2编写程序 (34)3.3编译程序 (35)4. 调试应用程序 (38)4.1连接仿真器 (38)4.2调试相关配置 (38)4.2.1CK100 调试配置 (38)4.2.2J-Link 调试配置 (45)4.3调试应用程序 (51)4.4停止调试 (57)5. 固化应用程序 (58)5.1使用µVision5 烧写程序 (58)5.2使用其他工具烧写程序 (58)5.2.1生成程序烧写文件 (58)5.2.2使用ISP 方式烧写程序 (60)6. 免责声明 (71)©2019 Guangzhou ZHIYUAN Micro Electronics Co., Ltd 1. 简介本文主要介绍如何使用 Keil 集成开发环境对开源项目进行工程的导入、新建工程、编译链接和调试等操作,帮助用户快速掌握 Keil 集成开发环境下的应用程序开发。

cortex-m0+使用条件编译

cortex-m0+使用条件编译英文回答:The Cortex-M0+ is a low-power microcontroller from Arm that is designed for embedded systems. It is based on the Armv6-M architecture and has a single-cycle multiply-accumulate (MAC) unit. The Cortex-M0+ also has a number of features that make it suitable for use in low-power applications, such as a sleep mode that consumes only 2.5uA.One of the features of the Cortex-M0+ is its supportfor conditional compilation. Conditional compilation allows you to compile different code depending on the value of a preprocessor macro. This can be useful for a variety of purposes, such as:Including or excluding code depending on the target platform.Enabling or disabling features depending on the user'sconfiguration.Debugging code by selectively including or excluding print statements.To use conditional compilation in the Cortex-M0+, you can use the `#ifdef`, `#ifndef`, `#else`, and `#endif` preprocessor directives. These directives allow you to specify a block of code that will only be compiled if a certain condition is met.For example, the following code will only be compiled if the `DEBUG` preprocessor macro is defined:c.#ifdef DEBUG.// Code that will only be compiled if DEBUG is defined.#endif.You can also use conditional compilation to define different code for different target platforms. For example, the following code will compile different code for the Cortex-M0+ and the Cortex-M3:c.#ifdef __CORTEX_M0。

M1A3P1000的多功能开发平台设计

Ke y wor s:FPGA ;cr ui d sgn;m u tf nc ina e l pm e t S d ic t e i liu to 1d veo n ; DR AM o r l r c ntole

1 平 台硬 件 设 计

11 主 板 电路设 计 .

M1 P 0 0内置 Co tx—M1内核 , 能 强 大 , 部 A3 1 0 re 功 内

G S扩 展 子 板 的 电路 设 计 及 P P CB设 计 、 用 S C 的 搭 建 , 后 设 计 了 基 于 C re 通 o 然 o tx—M 1内 核 的 S RAM 控 制 器 , 通 过 D 并 仿 真 实 现 了 平 台 的 协 同验 证 。 该 平 台 功 能 强 大 , 于 开 发 基 于 Ace F GA 的 P P、 车 电 子 或 工 业 控 制 等 。 适 t1 P M 汽 关 键 词 :F GA;电 路 设 计 ;多 功 能 开 发 ;S P DRAM 控 制 器 中 图 分 类 号 :TN9 1 5 1 . 文 献 标 识 码 :A

微小米 Cortex-M1 启用 ProASIC3L 开发套件中 Core8051s 微控制器系统的

Application Note AC427July 20141© 2014 Microsemi Corporation Loading and Debugging Core8051s Application From External Flash MemoryTable of ContentsPurposeThis application note describes how to load and debug application code from external flash memory available on the Microsemi ® Cortex-M1-enabled ProASIC3L Development Kit.IntroductionA Core8051s based microcontroller system is implemented on the Microsemi M1 enabled ProASIC3L field programmable gate array (FPGA). The external flash memory is interfaced to the Core8051s microcontroller system to load and debug the application code.ReferencesThe following references are used in this document:•Core8051s Based Hardware Tutorial •Core8051s Based Software User GuidePurpose . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1Design Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2Design Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2Design Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3Running the Design Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13Conclusion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22Appendix A – Design and Programming Files . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22List of Changes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23Loading and Debugging Core8051s Application From External Flash Memory2Design RequirementsDesign OverviewA Core8051s IP based microcontroller system is developed with peripheral IPs such as CoreGPIO,CoreUARTapb, CoreWatchdog, CoreTimer, and CoreAPB3 that are implemented on the Microsemi Cortex-M1-enabled ProASIC3L Development Kit . An external Micron JS28F640J3D-75 flash memory is interfaced to the Core8051s microcontroller system. A simple application is loaded into the external Micron JS28F640J3D-75 flash memory to blink the on-board LEDs. Figure 1 shows the Core8051s microcontroller system.Table 1 • Design RequirementsDesign RequirementsDescriptionHardware RequirementsCortex-M1-enabled ProASIC3L Development Kit-Host PC or LaptopAny 64-bit Windows Operating System Software RequirementsLibero ® System-on-Chip (SoC)v11.3SoftConsolev3.4One of the following serial terminal emulation programs:• HyperTerminal• TeraTerm• PuTTY -Figure 1 • Core8051s Microcontroller SystemDesign Description3Design DescriptionThis design example has the following IPs that are available in Libero SoC catalog:•Core8051s : an 8-bit microcontroller IP core •CoreGPIO : provides up to 32-bit inputs and 32-bit outputs for general purpose •CoreUARTapb : a serial communication interface •CoreWatchdog : provides a means of recovering from software crashes •CoreTimer : for interrupt-generation and programmable counter •CoreAPB3: a bus component that provides advanced microcontroller bus architecture (AMBA3)advanced peripheral bus (APB3) fabric supporting up to 16 APB slavesThe following sections provide a brief description of each IP and its configuration:•Core8051s Description•Difference Between Core8051s and Core8051•CoreAPB3 Description•External Flash Memory Description•CoreTimer Description•CoreWatchdog Description•CoreUARTapb Description•CoreGPIO Description•Description of Core8051s based Microcontroller System•Memory Map•Software Development Description Core8051s DescriptionThe Core8051s is a high-performance, 8-bit microcontroller IP core. It is an 8-bit embedded controller that executes all ASM51 instructions and has the same instruction set as 80C31. It provides software and hardware interrupts. It eliminates redundant bus states and implements parallel execution of fetch and execution phases. The Core8051s uses one clock per cycle, and most of the one byte instructions are performed in a single clock cycle. Figure 2 shows the Core8051s architecture.Difference Between Core8051s and Core8051The Core8051s is smaller and more flexible than the Core8051.The microcontroller-specific features such as SFR-mapped peripherals, power management circuitry, serial channel, I/O ports and timers of the original 8051 are not present in Core8051s. The Core8051s contains the main 8051 core logic, but it does not have peripheral logic. The Core8051s has an advanced peripheral bus interface that can be used like the SFR (special function register) bus to easily expand the functionality of the core by connecting it to the existing advanced peripheral bus IPs. The Core8051s allows to configure the coreFigure 2 • Core8051s ArchitectureLoading and Debugging Core8051s Application From External Flash Memory4with the peripheral functions (timers, UARTs, I/O ports, etc.) that are required for the application.Configure the Core8051s Configurator GUI as shown in Figure 3.Refer to the Core8051s Handbook for more details.CoreAPB3 DescriptionThe CoreAPB3 is a bus component that provides advanced microcontroller bus architecture (AMBA3)advanced peripheral bus (APB3) fabric supporting up to 16 APB slaves, and a single APB master. The CoreAPB3 can be used with an APB3 master that does not have a built-in APB address decoding, such as Core8051s. A single APB3 master is connected to CoreAPB3. The master’s PSEL and PADDR signals are used within the CoreAPB3 to decode the appropriate PSELS slave select signals, and only one signal can be active at a time. This address decoding depends on the RANGESIZE hardware parameter/generic. Refer to the CoreAPB3 Handbook for more information.Figure 3 • Core8051s Configurator GUIDesign Description5Configure the CoreAPB3 Configurator GUI as shown in Figure 4.External Flash Memory DescriptionPart Number:•Micron JS28F640J3D-75Architecture: •64 Mbit (64 blocks)Performance: •75 ns Initial Access Speed, 25 ns 8-word and 4-word Asynchronous page-mode reads •32-Byte Write buffer (4 μs per Byte Effective programming time)System voltage: •VCC = 2.7 V to 3.6 V and VCCQ = 2.7 V to 3.6 V Enhanced security options for code protection:•128-bit Protection Register (64-bits unique device identifier bits, 64-bits user-programmable OTP (one time programmable) bits)•Absolute protection with VPEN = GND •Individual block locking •Block erase/program lockout during power transitions Figure 4 • CoreAPB3 Configurator GUILoading and Debugging Core8051s Application From External Flash Memory6Software:•Program and erase suspend support•Flash data integrator (FDI)•Common flash interface (CFI) compatibleThe external flash memory device can be accessed as 8- or 16-bit words. A command user interface (CUI) serves as the interface between the system processor and the internal operation of the device. A valid command sequence written to the CUI that initiates the device automation. An internal write state machine (WSM) automatically executes the algorithms and timings necessary for block erase, program, and lock-bit configuration operations.Flash operations are command-based, where command codes are first issued to the flash memory, then the flash memory performs the required operation. Refer to the flash memory Micron JS28F640J3D-75 datasheet for a list of command codes and flowcharts. Flash memory has a read-only 8-bit status register that indicates the flash memory status and operational errors. Four types of data can be read from the flash memory: array data, device information, CFI data, and device status.The flash memory is set to Read Array mode by default after power-up or reset. Executing the Read Array command sets the flash memory to Read Array mode and reads the output array data. The flash memory remains in Read Array mode until a different read command is executed. To change the flash memory to Read Array mode while it is programming or erasing, first issue the suspend command. After suspending the operation, run the Read Array command to set to Read Array mode. When the program or erase operation is subsequently resumed, the flash memory automatically sets to Read Status mode. Issuing the Read Device Information command places the flash memory in Read Device Information mode and reads the output of the device information. The flash memory remains in Read Device Information mode until a different read command is issued. Also, performing a program, erase, or block-lock operation changes the flash memory to Read Status Register mode.Array programming is performed by first issuing the single-word/byte program command. This is followed by writing the desired data at the desired array address. The read mode of the device is automatically changed to Read Status Register mode, which remains in effect until another read-mode command is issued.Erasing a block changes zeros to ones. To change ones to zeros, a program operation must be performed. Erasing is performed on a block basis - an entire block is erased each time when an erase command sequence is issued. Once a block is fully erased, all addressable locations within that block read as logical ones (FFFFh). Only one block-erase operation can occur at a time, and it is not allowed during a program suspend. To perform a block-erase operation, issue the block erase command sequence at the required block address. An erase or programming operation can be suspended to perform other operations, and then subsequently resumed. To suspend an on-going erase or a program operation, issue the suspend command to any address.All blocks are unlocked at the factory. Blocks can be locked individually by issuing the set block lock bit command sequence to any address within a block. Once locked, blocks remain locked when power cable is unplugged or when the device is reset. All locked blocks are unlocked simultaneously by issuing the clear block lock bits command sequence to any device address. The locked blocks cannot be erased or programmed.The sequence of the commands that must be given to the flash memory are written in an XML file. The XML files are provided with the SoftConsole software for the JS28F640J3D-75 flash memory located at: C:\Program Files (x86)\Microsemi\SoftConsole v3.4\Sourcery-G++\share\sprite\flash.Design Description7CoreTimer DescriptionThe CoreTimer is an APB slave that provides a functionality for the interrupt generations, and a programmable decrementing counter. It is configurable and programmable, and can be used in either continuous or one-shot modes. It is an essential element in many designs because it supports accurate generation of timing for precise application control. Refer to the CoreTimer Handbook for more information. Configure the CoreTimer Configurator GUI as shown in Figure 5.CoreWatchdog DescriptionThe CoreWatchdog is an APB slave that provides a means of recovering from software crashes. When the CoreWatchdog is enabled, the core generates a soft reset if the microprocessor fails to refresh it on a regular basis. The CoreWatchdog can be configured based on a decrementing counter, which asserts a reset signal if it is allowed to time out. The width of the decrementing counter can be configured as either 16 or 32-bits. The processor-accessible registers in CoreWatchdog provide a means to control and monitor the operation of the core. Refer to the CoreWatchdog Handbook for more information.Configure the CoreWatchdog Configurator GUI as shown in Figure 6.Figure 5 • CoreTimer Configurator GUIFigure 6 • CoreWatchdog Configurator GUILoading and Debugging Core8051s Application From External Flash Memory8CoreUARTapb DescriptionThe CoreUARTapb is a serial communications interface that is primarily used in the embedded systems.The controller can operate in either an asynchronous (UART) or a synchronous mode. In asynchronous mode, the CoreUARTapb can be used to interface directly to industry standard UARTs. The CoreUARTapb has an APB-wrapper that adds an APB interface allowing the core to be connected to the APB bus and controlled by an APB bus master. Unlike a standard 8051 UART, the CoreUARTapb includes a baud rate generator and so does not need a separate timer for the baud rate. Refer to the CoreUARTapb Handbook for more information.Configure the CoreUARTapb Configurator GUI as shown in Figure 7.Figure 7 • CoreUARTapb Configurator GUIDesign Description9CoreGPIO DescriptionThe CoreGPIO is an APB bus peripheral that provides up to 32-bit inputs and 32-bit outputs for general purpose. Refer to the CoreGPIO Handbook for more information.Configure the CoreGPIO Configurator GUI as shown in Figure 8.Figure 8 • CoreGPIO Configurator GUILoading and Debugging Core8051s Application From External Flash Memory10Description of Core8051s based Microcontroller System All the peripherals are interfaced to the Core8051s as shown in Figure 9.Refer to the Core8051s Based Hardware Tutorial for more information.Figure 9 • SmartDesign Top-Level Block DiagramDesign Description Instantiate a two port RAM on the SmartDesign top-level and configure it as shown in Figure10.Figure 10 • SRAM ConfigurationExternal memory buffer and multiplexer are configured as shown in Figure11 and Figure12.Figure 11 • External Memory Buffer ConfigurationLoading and Debugging Core8051s Application From External Flash MemoryMemory MapRight-click the Modify Memory Map to see the memory map as shown in Figure 13.Software Development DescriptionThe drivers are generated from firmware catalog for CoreTimer, CoreGPIO, CoreWatchdog, CoreTimer,and hardware abstraction layer (HAL). The HAL is used by drivers to access the hardware and also allows the control of interrupts.Refer to the Core8051s Based Software User Guide for more information.The Core8051s hardware design provides access to the external flash memory and internal SRAM. The Core8051s flash programming flow for Core8051s program memory is similar to the existing programming flow for Cortex-M1 flash program memory. The principal difference is, instead of specifying the location, size and the type of the program memory in a linker script, the program memory details are given in a text file (a memory-region-file) which uses the same syntax as the memory command section of a GCC linker script. The SoftConsole project configuration must be modified to specify the memory-region-file as an argument to the actel-map.exe helper program. Application code is written in main.c of the SoftConsole project to blink the on-board LED's.Figure 12 • Multiplexer ConfigurationFigure 13 • Memory MapRunning the Design ExampleRunning the Design ExampleTo run the design example,1.Download the design example at,/download/rsc/?f=Core8051s_ExtFlashIntSRAM_DF2.Double-click the Program Device under Program Design to program the Cortex-M1-enabledProASIC3L Development Kit in the Design Flow window, as shown in Figure14.Figure 14 • Program DeviceLoading and Debugging Core8051s Application From External Flash Memory3.Open the SoftConsole project after successfully programming the device, as shown in Figure15.Figure 15 • SoftConsole Project WindowRunning the Design Example4.Right-click the Core8051s_ExtFlashIntSRAM on the left pane and click Properties, as shown inFigure16. The Properties window is displayed as shown in Figure16.Figure 16 • Project Properties5.Double-click Settings under C/C++ Build on the left pane of Properties window.Loading and Debugging Core8051s Application From External Flash Memory6.Click Tools Settings tab on the right pane and select the Memory map generator, as shown inFigure 17.7.Enter actel-map -M../intel-28f640-1x8-code-memory.txt text in the Command field.Note:The “intel-28f640-1x8” XML file, which is at C:\Program Files (x86)\Microsemi\SoftConsolev3.4\Sourcery-G++\share\sprite\flash is used for loading and debugging the JS28F640J3D-75 flash memory.Figure 17 • Memory Map GeneratorRunning the Design Example8.Right-click Core8051s_ExtFlashIntSRAM on the left pane and click Debug As > DebugConfigurations…, as shown in Figure18. The Debug Configurations window is displayed.Figure 18 • Debug ConfigurationsLoading and Debugging Core8051s Application From External Flash Memory9.Right-click Microsemi Core8051s Target and click New to create a new debug configuration, asshown in Figure19.Figure 19 • New Debug Configuration10.Click Debug.Figure 20 • Debug ConfigurationsRunning the Design Example After launching the debug session, the flash programming operation starts. The erase and writeoperations are shown in Figure21.Figure 21 • Flash ProgrammingLoading and Debugging Core8051s Application From External Flash Memory11.Start PuTTY (with settings 57600 baud rate, 8 data bits, and No parity), and choose Resumefrom the Run menu. The LEDs are scanned on the Cortex-M1-enabled ProASIC3L Development Kit in the forward and reverse direction. The messages are displayed as shown in Figure 22.12.Terminate and relaunch the debug session.13.Set break points at 60, 115 and 149 lines of main.c.14.Choose Resume from the Run menu.15.Choose Step Over from the Run menu until it reaches the 115 line of main.c. The “RunningCore8051s Application from External Flash Memory” message is displayed as shown in Figure 23.Figure 22 • Application Running From External Flash MemoryFigure 23 • Debug CodeRunning the Design Example2116.Choose Step Over from the Run menu. While stepping over the code, the LEDs blinks on theMicrosemi Cortex-M1-enabled ProASIC3L Development Kit . The message is displayed as shown in Figure 24.Figure 24 • Step OverLoading and Debugging Core8051s Application From External Flash Memory2217.Right-click Core8051s_ExtFlashIntSRAM Debug [Microsemi Core8051 Target] and clickTerminate and Remove the debug session as shown in Figure 25.18.Choose Exit from the File menu to close the SoftConsole project.19.Unplug the USB cables and power supply cable and plug-in the power supply cable. The sameLED scanning application runs from the non-volatile external flash memory.ConclusionThis application note describes how to load and debug the Core8051s application from the external flash memory using SoftConsole. The example design serves as a starting point to other Core8051s designs.It includes a Core8051s based system, firmware drivers, and a sample LED scanning application that runs from the external flash memory.Appendix A – Design and Programming FilesYou can download the design files from the Microsemi SoC Products Group website:/download/rsc/?f=Core8051s_ExtFlashIntSRAM_DFThe design file consists of Libero project and programming file. Refer to the Readme.txt file included in the design file for directory structure and description.Figure 25 • Terminate and Remove Debug SessionList of Changes 23List of ChangesThe following table lists the critical changes that were made in the current version of the application note.DateChanges Page Revision 1(July 2014)Initial Release.NA51900295-1/7.14© 2014 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.Microsemi Corporate HeadquartersOne Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100Sales: +1 (949) 380-6136Fax: +1 (949) 215-4996E-mail:***************************Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense and security, aerospace, and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs, and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif. and has approximately 3,400 employees globally. Learn more at .。

ARM Cortex系列

Cortex系列ARM核心及体系结构介绍作者:杨硕,华清远见嵌入式学院讲师。

众所周知,英国的ARM公司是嵌入式微处理器世界当中的佼佼者。

ARM一直以来都是自己研发微处理器内核架构,然后将这些架构的知识产权授权给各个芯片厂商,精简的CPU架构,高效的处理能力以及成功的商业模式让ARM公司获得了巨大的成功,使他迅速占据了32位嵌入式微处理器的大部分市场份额,甚至现在,ARM芯片在上网本市场的也大有与INTEL 的ATOM处理器一较高低的实力。

目前,随着对嵌入式系统的要求越来越高,作为其核心的嵌入式微处理器的综合性能也受到日益严峻的考验,最典型的例子就是伴随3G网络的推广,对手机的本地处理能力要求很高,现在一个高端的智能手机的处理能力几乎可以和几年前的笔记本电脑相当。

为了迎合市场的需求,ARM公司也在加紧研发他们最新的ARM架构,Cortex系列就是这样的产品。

在Cortex之前,ARM核都是以ARM为前缀命名的,从ARM1一直到ARM11,之后就是Cortex系列了。

Cortex在英语中有大脑皮层的意思,而大脑皮层正是人脑最核心的部分,估计ARM公司如此命名正有此含义吧。

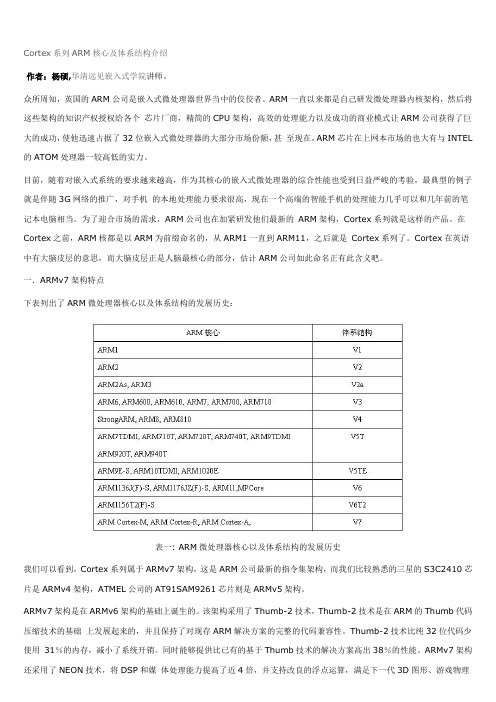

一.ARMv7架构特点下表列出了ARM微处理器核心以及体系结构的发展历史:表一: ARM微处理器核心以及体系结构的发展历史我们可以看到,Cortex系列属于ARMv7架构,这是ARM公司最新的指令集架构,而我们比较熟悉的三星的S3C2410芯片是ARMv4架构,ATMEL公司的AT91SAM9261芯片则是ARMv5架构。

ARMv7架构是在ARMv6架构的基础上诞生的。

该架构采用了Thumb-2技术,Thumb-2技术是在ARM的Thumb代码压缩技术的基础上发展起来的,并且保持了对现存ARM解决方案的完整的代码兼容性。

Thumb-2技术比纯32位代码少使用31%的内存,减小了系统开销。

同时能够提供比已有的基于Thumb技术的解决方案高出38%的性能。

《Cortex-M0权威指南》之Cortex-M0编程入门

《Cortex-M0权威指南》之Cortex-M0编程入门嵌入式系统编程入门微控制器是如何启动的为了保存编译号的二进制程序代码,大多数的现代微控制器都会包含片上flash存储器。

有些微控制器还可能有一个独立的启动ROM,里面装有Bootloader程序。

微控制器启动后,再执行flash的用户程序前,Bootloader会首先运行。

在复位流程中,处理器会取出MSP的初始化值和复位向量,然后开始执行复位处理,这些信息都放在一个叫做启动代码的程序文件中。

启动代码中的复位处理可能还会旅行初始化的职责,比如时钟控制电路和锁相环PLL的初始化。

有些情况下,系统初始化的工作是放在C程序的main()函数中进行的。

对于用C开发的应用程序,在进入主流程之前,启动代码已经开始执行,并且对应用程序用到的变量和内存等进行初始化。

启动代码无需编程者担心,C开发工具会将其自动插入程序映像中。

执行完C启动代码后,应用程序就开始执行了,应用程序通常包含下面几个部分:硬件初始化(如时钟,PLL和外设)应用程序的处理部分中断服务程序另外,应用程序可能会用到C语言库,此时,C编译器/链接器会将所需要的库函数加入编译好的程序映像中。

硬件初始化可能会涉及到一系列的外设、系统控制寄存器和中断控制器。

如果在复位处理时没有进行处理,系统时钟控制和PLL此时也需要进行初始化。

外设初始化完成后,程序就可以继续执行应用程序部分了。

嵌入式程序设计应用程序处理流程的实现方式如下:轮询,如中断驱动,如轮询和中断组合使用,如处理并发任务(操作系统),如对于复杂的应用程序,可以使用实时操作系统(RTOS)。

RTOS将处理器时间划分为多个时间片,在有多个应用进程运行时,只有一个进程会获得时间片。

使用RTOS,需要有定时器产生周期性的中断请求,当一个时间片的时间到时,RTOS的任务调度器会由定时器中断触发,调度器判断是否需要执行上下文切换。

如果需要进行上下文切换,调度器会暂停当前执行的任务,并切换到下一个准备就绪的任务。

专门针对FPGA而优化的ARM Cortex-M1处理器

的多处理 器结合硬 件加速 引擎 的S C o 体 条指 令 ,并支持 硬件双 线程技 术。视 频 况动 态地调 整编码 的码 率 。视频 显示 的 系架构设 计 , C U是 主频3 0 主 P 5 MHz 的 编解 码工作 由 3 个可 编程但 不 同架 构的 后处理 以及模拟输 出工作 由硬 件加速单 超级标量 RI C处 理器 ,运 行 2 6内核 子处 理器(5 位 的 向量处 理 器 , t n 元完成 ,它可以 支持 4 S . 26 Moi o 个硬件 OS D层 图

_

AR M

能需求进行标 准化 。

兼容 。 o tx C re —M1 理器 的运行速 度超 处

电 话 :0 1 6 3 —19 2 - 2 5 26

htp t // WWW . r .o a m c m

ARM otx C re —M1 处理 器是精 简的 过 1 0 MHz 7 ,体积 不到广泛 采用 的低 功

一

/ 包括 8 5 / 的 L S 器 接 口 ,还 支 持 DDR、S DRAM 7 Mb s VD DR S 低功耗工艺制造 , 含有 5 K~10 2 K逻辑单 业界 I O标 准 , 元( E , 8 个速率为 2 0 L ) 28 6 MHz 的DS P乘 通信接 口。 y ln I采用 交错 I O焊 和 QDRI S C co e II / I RAM,自校 准 P HY可迅速 提 法 器 ,存储 器容 量 达到 4M ,支持 盘进行 设计 , 供小外 形封装 以减小 管 实现时序 逼近 。 y ln I的每 个锁相 b C co e II L TT 、 VC S S T 、 v L L MO 、 S L 高速收 发器 芯和 电路板面 积 ,同时 支持低 成本的 串 环( LL 有 更多 的输 出 ,动 态配 置 PL P ) L

NuMicro Cortex-M0 Keil 调试器驱动用户手册

NuMicro Cortex-M0 Keil µVision 驱动之Nu-Link用户手册V1.17The information in this document is subject to change without notice.The Nuvoton Technology Corp. shall not be liable for technical or editorial errors or omissions contained herein; nor for incidental or consequential damages resulting from the furnishing, performance, or use of this material.This documentation may not, in whole or in part, be copied, photocopied, reproduced, translated, or reduced to any electronic medium or machine readable form without prior consent, in writing, from the Nuvoton Technology Corp.Nuvoton Technology Corp. All rights reserved.目录1. 简介 (4)2. 系统需求 (4)3. NU_LINK ICE 特性 (4)4. 提供文件 (4)5. 支持芯片 (5)6. 安装 (5)7. 调试工程 (10)8. 更新Config 位 (12)9. 外设 (14)10. Semihosting (16)11. 修订历史 (18)12. Nuvoton的Keil Add On-Component许可协议 (18)1.简介Keil的µVision开发工具主要是用来管理工程,编写、编译、调试程序以及下载程序到目标板上的,而调试或下载程序到目标板上则需要调试驱动程序的支持,如ULink ARM Debugger就是这样的调试驱动程序;Nuvoton也为µVision提供了这样的调试驱动程序:Nu-Link,它主要用来辅助µVision调试Cortex-M0系列芯片的,尤其是Nuvoton的NUC1XX系列的芯片。

德玛吉海德汉系统操作说明书-卓越教学手册

Gowin EMPU M1 下载参考手册说明书

Gowin_EMPU_M1下载参考手册IPUG532-1.9,2021-10-12版权所有© 2021广东高云半导体科技股份有限公司,,Gowin,GowinSynthesis,高云均为广东高云半导体科技股份有限公司注册商标, 本手册中提到的其他任何商标,其所有权利属其拥有者所有。

未经本公司书面许可,任何单位和个人都不得擅自摘抄、复制、翻译本文档内容的部分或全部,并不得以任何形式传播。

免责声明本文档并未授予任何知识产权的许可,并未以明示或暗示,或以禁止发言或其它方式授予任何知识产权许可。

除高云半导体在其产品的销售条款和条件中声明的责任之外,高云半导体概不承担任何法律或非法律责任。

高云半导体对高云半导体产品的销售和/或使用不作任何明示或暗示的担保,包括对产品的特定用途适用性、适销性或对任何专利权、版权或其它知识产权的侵权责任等,均不作担保。

高云半导体对文档中包含的文字、图片及其它内容的准确性和完整性不承担任何法律或非法律责任,高云半导体保留修改文档中任何内容的权利,恕不另行通知。

高云半导体不承诺对这些文档进行适时的更新。

版本信息目录目录 (i)图目录 (iii)表目录 (iv)1下载方法 (1)2软件编程输出作为硬件ITCM初始值 (3)2.1 软件工具 (3)2.2 命令参数 (3)2.3 软件配置 (3)2.4 硬件配置 (4)2.5 设计流程 (5)2.6 适用器件 (5)2.7 参考设计 (5)3合并软件编程设计和硬件设计 (6)3.1 软件工具 (6)3.2 命令参数 (6)3.3 硬件配置 (7)3.4 设计流程 (7)3.4.1 合并 (7)3.4.2 下载 (8)3.5 适用器件 (8)3.6 适用软件 (8)3.7 参考设计 (8)4片外SPI-Flash下载方法 (9)4.1 软件配置 (9)4.2 硬件配置 (10)4.2.1 ITCM Initialization配置 (10)4.2.2 Dual-Purpose Pin配置 (11)4.3 设计流程 (11)4.4 下载 (11)4.4.1 下载硬件设计码流文件 (12)4.4.2 下载软件设计二进制BIN文件 (13)4.5 适用器件 (14)4.6 参考设计 (14)5内嵌UserFlash下载方法 (15)5.1 软件配置 (15)5.2 硬件配置 (15)5.3 设计流程 (16)5.4 下载 (16)5.5 适用器件 (17)5.6 参考设计 (17)图目录图2-1配置外部工具 (4)图2-2配置ITCM Initialization (4)图3-1配置布局布线Post-Place File选项 (7)图3-2合并软件编程设计和硬件设计 (8)图4-1 ROM起始地址和容量配置 (9)图4-2配置ITCM Initialization Path选项 (10)图4-3配置Dual-Purpose Pin选项 (11)图4-4硬件下载Device configuration (12)图4-5软件下载Device configuration (13)图5-1 ROM起始地址和容量配置 (15)图5-2配置ITCM Select选项 (16)图5-3 GW1N(R)-9C Device Configuration (17)表目录表目录表3-1 merge_bit命令及参数 (6)表4-1不同ITCM Size对应的bootload (10)1下载方法Gowin_EMPU_M1支持四种硬件设计和软件编程设计下载方法:1. 软件编程设计产生映像文件,作为硬件设计中ITCM初始值。

MxGPU设置指南说明书

DISCLAIMERThe information contained herein is for informational purposes only, and is subject to change without notice. While every precaution has been taken in the preparation of this document, it may contain technical inaccuracies, omissions and typographical errors, and AMD is under no obligation to update or otherwise correct this information. Advanced Micro Devices, Inc. makes no representations or warranties with respect to the accuracy or completeness of the contents of this document, and assumes no liability of any kind, including the implied warranties of non-infringement, merchantability or fitness for particular purposes, with respect to the operation or use of AMD hardware, software or other products described herein. No license, including implied or arising by estoppel, to any intellectual property rights is granted by this document. Terms and limitations applicable to the purchase or use of AMD’s products are as set forth in a signed agreement between the parties or in AMD's Standard Terms and Conditions of Sale.©2016 Advanced Micro Devices, Inc. All rights reserved. AMD, the AMD arrow, FirePro, and combinations thereof are trademarks of Advanced Micro Devices, Inc. in the United States and/or other jurisdictions. OpenCL is a trademark of Apple, Inc. and used by permission of Khronos. PCIe and PCI Express are registered trademarks of the PCI-SIG Corporation. VMware is a registered trademark of VMware, Inc. in the United States and/or other jurisdictions. Other names are for informational purposes only and may be trademarks of their respective owners.Table of Contents1.Overview (4)2.Hardware and Software Requirements (4)2.1Hardware Requirements (4)2.1.1Host/Server (4)2.1.2Client (4)2.2Software Requirements (5)3.MxGPU Setup (6)3.1Programming SR-IOV Parameters for MxGPU (6)3.2VF Pass Through (8)3.3VF-to-VM Auto-Assignment (9)4.Appendix (11)4.1Host Server Configuration (11)4.2Manual Installation for GPUV Driver for VMware ESXi (13)4.2.1Upload GPUV Driver (13)4.2.2Install GPUV Driver (13)4.2.3Configure GPUV Driver (15)4.2.4Un-Install GPUV Driver (16)4.2.5Update GPUV Driver (17)1.OverviewThis setup guide details the advanced steps necessary to enable MxGPU on the AMD FirePro™ S7100X, S7150 and S7150x2 family of products. The guide uses VMware® products as an example setup. These products include VMware ESXi™ as a hypervisor, the VMware vSphere® client and VMware Horizon® View™. The basic setup steps for the VMware software is detailed in the companion document to this one.2.Hardware and Software RequirementsThe sections below lists the hardware and software that are required for setting up the VMware environment.2.1Hardware Requirements2.1.1Host/ServerGraphics Adapter: AMD FirePro™ S7100X, S7150, S7150x2 for MxGPU and/orpassthrough***note that the AMD FirePro™ S7000, S9000 and S9050 can be used for passthroughonlySupported Server Platforms:•Dell PowerEdge R730 Server•HPE ProLiant DL380 Gen9 Server•SuperMicro 1028GQ-TR ServerAdditional Hardware Requirements:•CPU: 2x4 and up•System memory: 32GB & up; more guest VMs require more system memory•Hard disk: 500G & up; more guest VMs require more HDD space•Network adapter: 1000M & up2.1.2ClientAny of the following client devices can be used to access the virtual machine once theseVMs are started on the host server:•Zero client (up to 4 connectors) with standard mouse/keyboard and monitor•Thin client with standard mouse/keyboard and monitor running Microsoft®Windows® Embedded OS•Laptop/Desktop with standard mouse/keyboard and monitor running withMicrosoft® Windows® 7 and up2.2 Software RequirementsProductType Install OnSectionVersion/Download LocationAMD FirePro™ VIB Driver Hypervisor Driver Host (Server) 3.1 /en-us/download/workstation?os=VMware%20vSphere%20ESXi%206.0#catalyst-pro AMD VIB Install Utility Script Host (Server) 3.1 /en-us/download/workstation?os=VMware%20vSphere%20ESXi%206.0#catalyst-pro PuTTYSSH client Host Admin. System / SSH Secure ShellSSH Client andDownload UtilityHost Admin. System3.1Table 1 : Required Software for Document(Links to non-AMD software provided as examples)3.MxGPU SetupThe following sections describe the steps necessary to enable MxGPU on the graphics adapter(s) in the host. Before proceeding, refer to the Appendix to ensure that the host system is enabled for virtualization and SR-IOV. Once virtualization capabilities are confirmed for the host system, follow the steps in the next two sections to program the graphics adapter(s) for SR-IOV functionality and to connect the virtual functions created to available virtual machines.3.1Programming SR-IOV Parameters for MxGPU1.Download and unzip the vib and MxGPU-Setup-Script-Installer.zip from Table 1.2.Copy script and vib file to the same directory (Example : /vmfs/volumes/datastore1)ing an SSH utility, log into the directory on the host and change the attribute of mxgpu-install.sh to be executable # chmod +x mxgpu-install.sh4.Run command: # sh mxgpu-install.sh to get a list of available commands5.Run command: # sh mxgpu-install.sh –i <amdgpuv…vib>•If a vib driver is specified, then that file will be used. If no vib driver is specified then the script assumes the latest amdgpuv driver in the current directory•The script will check for system compatibility before installing the driver•After confirming system compatibility, the script will display all available AMD adapters7.Next, the script will show three options: Auto/Hybrid/Manual.1)Auto: automatically creates a single config string for all available GPUs:•the script first prompts for the number of virtual machines desired (per GPU) and sets all settings accordingly (frame buffer, time slice, etc…)•next, the script prompts the user if they want to enable Predictable Performance, a feature that keeps performance fixed independent of active VMs•the settings are applied to all AMD GPU available on the bus•if a S7150X2 is detected, the script will add pciHole parameters to VMs• a reboot is required for the changes to take effect2)Hybrid: configure once and apply to all available GPUs:•the script first prompts for the number of virtual machines desired (per GPU) and sets all settings accordingly (frame buffer, time slice, etc…)•next, the script prompts the user if they want to enable Predictable Performance•the settings are applied to the selected AMD GPU; the process repeats for the next GPU•if a S7150X2 is detected, the script will add pciHole parameters to VMs• a reboot is required for the changes to take effect3)Manual: config GPU one by one:•the script prompts the user to enter VF number, FB size/VF, time slice•next, the script prompts the user if they want to enable Predictable Performance•the settings are applied to selected AMD GPU; the process repeats for the next GPU•if a S7150X2 is detected, the script will add pciHole parameters to VMs• a reboot is required for the changes to take effectFigure 1 : Screenshot of MxGPU Setup Script Installation FlowFor users who want to understand the individual steps required for vib installation and configuration,3.2VF Pass ThroughOnce the VFs (virtualfunctions) are set up, thenpassing through theses VFsfollows the same procedureas passing through a physicaldevice. To successfully passthrough the VFs, the physicaldevice CANNOT beconfigured as a passthroughdevice. If the physical deviceis being passed through tothe VM, then the GPUVdriver will not install properly.If that happens, the VFs willnot be enabled and no VFswill be shown.Once the VFs are enabled, they will be listed in the available device list for pass through, and the status of the PF will be changed to unavailable for pass through. No additional operation is needed to move VF into pass through device list.3.3VF-to-VM Auto-Assignment1.After rebooting the system and the VFs are populated on the device list, navigate to thedirectory containing the mxgpu-install.sh script2.Specify Eligible VMs for auto-assign in “vms.cfg” file•Note: If all registered VMs should be considered eligible, skip to step 43.Edit vms.cfg file to include VMs that should be considered for auto-assign•Use # vi vms.cfg to edit the configuration file•For help with using vi, an example can be found on the following VMware page: https:///selfservice/microsites/search.do?language=en_US&cmd=displayKC&externalId=1020302•Examples are provided in the vms.cfg configuration file on how to specify VMs should be considered eligible•Note: Make sure to delete the regular expression .* if you are specifying your own VMs4.Start the auto-assign option # sh mxgpu-install.sh –a5.Select the command to execute [assign|unassign|list|help]6.The assign command will continue if the number of eligible VMs does not exceed the number ofVFs7.Once the VM is powered on, a VF will appear in the Device Manager as a graphics device. Thegraphics driver can now be installedFigure 2 : Screenshot of the default contents of “vms.cfg” fileFigure 3 : Screenshot of Multi-Assign UsageFigure 4 : Screenshot of Multi-Assign “list” command after assigning VFs to VMs4.Appendix4.1Host Server ConfigurationTo enable the MxGPU feature, some basic virtualization capabilities need to be enabled in the SBIOS. These capabilities may be configured from the SBIOS configuration page during system bootup. Different system BIOS vendors will expose different capabilities differently. Some may have one control that enables a number of these capabilities. Some may expose controls for some capabilities while hardcoding others. The following settings, taken from an American Megatrends system BIOS, provides a list of the minimal set of capabilities that have to be enabled :Server CPU supports MMUServer chipset supports AMD IOMMU or Intel VT-dThe option “Intel VT for Directed I/O (VT-d)” should be enabledExample Path : IntelRCSetup → IIO Configuration → Intel(R) VT for Directed I/O (VT-d) → Intel VT for Directed I/O (VT-d)Server (SBIOS) support PCIe standard SR-IOVThe option “SR-IOV Support” should be enabled.Example Path : Advanced → PCI Subsystem Settings → SR-IOV SupportServer (SBIOS) support ARI (Alternative Routing ID)The option “ARI Forwarding” should be enabled.Example Path : Advanced → PCI Subsystem Settings → PCI Express GEN 2 Settings → ARI ForwardingServer (SBIOS and chipset (root port/bridge)) supports address space between 32bit and 40bitIf there is an “Above 4G Decoding” enable it.Example Path : Advanced → PCI Subsystem Settings → Above 4G DecodingServer (Chipset (root port / bridge)) supports more than 4G address spaceThere may be an option “MMIO High Size” for this function (default may be 256G).Example Path : IntelRCSetup → Common RefCode Configuration → MMIO High Size Examples on the next page demonstrate implementations from other system BIOS vendors.The following example showshow to enable SR-IOV on a Dell R730 platform.On some platforms, theSBIOS configuration page provides more options to control the virtualization behavior. One of these options is the ARI (alternative reroute interface) as shown below.In addition, some platformsalso provide controls to enable/disable SVM and/or IOMMU capability. These options must be enabled on the platform.4.2Manual Installation for GPUV Driver for VMware ESXi *note that the GPUV driver refers to the vib driver.4.2.1Upload GPUV Driver1.Download the GPUV driver to the administrator system from Table 1.2.Start SSH Secure File Transfer utility and connect to the host server.3.On the left (theadministratorsystem), navigate tothe directory wherethe GPUV driver issaved; on the right(the host system),navigate to/vmfs/volumes/datastore14.Right click on the GPUV driver file and select “Upload” to upload it to/vmfs/volumes/datastore1.4.2.2Install GPUV Driver1.In vSphere client, place system into maintenance mode2.Start SSH Secure Shell client, connect to host, run the following command:esxcli software vib install --no-sig-check -v /vmfs/volumes/datastore1/amdgpuv-<version>.vib ***note : the vib name is used as an example.You should seesomething this :3.In the vSphere client, exit maintenance mode4.In SSH Secure Shell client window, run the following command :esxcli system module set -m amdgpuv -e trueThis command makes theamdgpuv driver load on ESXiboot up.5.In vSphere client, reboot the server.4.2.3Configure GPUV Driver1.Find out the BDF (bus number, device number, and function number) of the SR-IOV adapter. InSSH Secure Shell client , type in command :lspciYou should see somethinglike in the picture. The BDFfor this adapter is 05.00.0 inthis example.2.In SSH Secure Shell client window run the following command to specify the setting for SR-IOVadapter:esxcfg-module –s “adapter1_conf=<bus>,<dev>,<func>,<num>,<fb>,<intv>” amdgpuvThe configuration is done through esxcfg-module command in the format of parameter as [bus, dev, func, num, fb, intv] to quickly set all VFs on one GPU to the same FB size and time slice.•bus – the bus number: in decimal value•dev – the device number: in decimal value•func – the function number•num – the number of enabled VFs•fb – the size of framebuffer for each VF•intv – the interval of VF switching.For example,•command: esxcfg-module -s "adapter1_conf=1,0,0,15,512,7000" amdgpuv Enables 15 virtual functions, each VF with 512M FB, and 7 millisecond time slice for*******************************.0•command: esxcfg-module -s "adapter1_conf=5,0,0,8,256,7000adapter2_conf=7,0,0,10,256,10000" amdgpuvEnable 8 VF, each VF has 256M FB and 7 millisecond time slice for adapter located @05:00.0Enable 10 VF, each VF has 256M FB and 10 millisecond time slice for adapter located @07:00.0•command: esxcfg-module -s "adapter1_conf=14,0,0,6,1024,7000adapter2_conf=130,0,0,4,1920,7000" amdgpuvEnable 6 VF, each VF has 1024M FB and 7 millisecond time slice for adapter located @0E:00.0Enable 4 VF, each VF has 1920M FB and 7 millisecond time slice for adapter located @82:00.0Note:1)Every time the command is executed, the previous configuration is overwritten. If the userwants to configure a newly added GPU, he needs to apply the previous parameterappending with new parameter in one command, otherwise the previous configuration for the existing GPU is lost.2)If you use lspci to find out the BDF of the GPU location, the value is in hex value instead ofdecimal value. In the last example, the first adapter is located at bus 14, but the lspci willshow as 0E:00.0; the second adapter is located at bus 130, the lspci will show as 82:00.0.3.In order to let the new configuration take effect, a server reboot is needed - in vSphere client,reboot the server.4.2.4Un-Install GPUV Driver1.Unload the GPUV driver by typing in command in SSH Secure Shell client :vmkload_mod -u amdgpuv2.In vSphere Client, set system to maintenance mode3.In SSH Secure Shell client type in command :esxcli software vib remove -n amdgpuv4.Start SSH Secure FileTransfer utility,connect to hostserver. On the right(the host system),navigate to/vmfs/volumes/datastore1, select theamdgpuv driver,right click, select“Delete”.5.In vSphere client, reboot the server.4.2.5Update GPUV Driver1.Follow the sequence in section 4.2.4 to remove the old driver.2.Follow the sequence in section 4.2.1 to download the new driver3.Follow the sequence in section4.2.2 to install the new driver4.Follow the sequence in section 4.2.3 to configure the new driver.。

CMSIS_RTOS_Tutorial