基于SRAM并部分可重配置的FPGA设计ECU

FPGA的种类与应用选型

FPGA的种类与应用选型FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,能够在用户设计中实现数字逻辑功能。

由于其可编程性,FPGA具有灵活性高、可重构性强的特点,被广泛应用于各种领域。

不同的应用需要使用不同类型的FPGA,下面将介绍FPGA的种类及其应用选型。

首先,FPGA可以根据其内部结构的不同分为SRAM-based FPGA和Antifuse-based FPGA两种。

1. SRAM-based FPGASRAM-based FPGA(基于静态随机存取存储器的FPGA)使用SRAM存储器来实现逻辑功能。

这种FPGA在设计过程中需要不断地读取配置位流(Configuration Bitstream),并在运行时对SRAM存储器进行配置。

它具有灵活性高、资源利用率高的特点,并且可以进行快速的设计迭代。

由于其可编程性,SRAM-based FPGA广泛应用于原型设计、系统验证、数字信号处理、计算机视觉等领域。

2. Antifuse-based FPGAAntifuse-based FPGA(基于直流反向电压击穿的FPGA)使用Antifuse技术实现逻辑功能。

Antifuse是一种非可逆电子器件,在设计过程中只需一次性地进行配置。

Antifuse-based FPGA具有配置安全性高、性能稳定的特点,可以应用于对安全性要求高的领域,如航空航天、国防等。

除了根据内部结构的不同,FPGA还可以根据其规模和功能的不同进行分类。

1.FPGA的规模分类根据FPGA的规模,可以将其分为大规模FPGA、中型FPGA和小规模FPGA。

大规模FPGA具有更多的逻辑资源和I/O引脚,适用于复杂的应用,如高性能计算、通信基础设施等。

中型FPGA具有适中的规模和资源,适用于多种应用场景,如消费电子、工业控制、医疗设备等。

小规模FPGA通常具有较低的功耗和成本,适用于低功耗应用,如传感器数据预处理、边缘计算等。

fpga期末复习题(答案)知识点题型

一、填空题:1、 FPGA结构一般分为三部分:可编程逻辑块(CLB)、可编程I/O模块和可编程内部连线。

2、 CPLD的内部连线为连续式布线互连结构,任意一对输入、输出端之间的延时是固定;FPGA的内部连线为分段式布线互连结构,各功能单元间的延时不定(不可预测)。

3、大规模可编程器件主要有CPLD和FPGA两类,其中CPLD通过可编程乘积项逻辑实现其逻辑功能。

基于SRAM的FPGA器件,每次上电后必须进行一次配置。

FPGA内部阵列的配置一般采用在电路可重构技术,编程数据保存在静态存储器(SRAM) ,掉电易失。

4、目前世界上有十几家生产CPLD/FPGA的公司,最大的两家是:Altera,Xilinx。

5、硬件描述语言(HDL)是EDA技术的重要组成部分,是电子系统硬件行为描述、结构描述、数据流描述的语言,它的种类很多,如VHDL、Verilog HDL、AHDL6、 WHEN_ELSE条件信号赋值语句和 IF_ELSE顺序语句的异同:* WHEN_ELSE条件信号赋值语句中无标点,只有最后有分号;必须成对出现;是并行语句,必须放在结构体中。

* IF_ELSE顺序语句中有分号;是顺序语句,必须放在进程中7、可编程逻辑器件设计输入有原理图输入、硬件描述语言输入和波形输入三种方式。

原理图输入方式是一种最直接的设计描述方式,波形设计输入适用于时序逻辑和有重复性的逻辑函数。

硬件描述语言的突出优点是:* 语言与工艺的无关性;语言的公开可利用性,便于实现大规模系统的设计;* 具有很强逻辑描述和仿真功能,而且输入效率高,在不同设计输入库之间的转换非常方便,用不着对底层的电路和PLD结构的熟悉。

8、用VHDL/Veilog HDL语言开发可编程逻辑电路的完整流程:文本编辑→功能仿真→逻辑综合→布局布线→时序仿真。

*所谓综合,就是根据设计功能和实现该设计的约束条件(如面积、速度、功耗和成本等),将设计输入转换成满足要求的电路设计方案,该方案必须同时满足与其的功能和约束条件。

基于FPGA的可重配置系统在新兴汽车标准中的应用

基于FPGA的可重配置系统在新兴汽车标准中的应用多种新兴汽车系统可在汽车各个节点间提供数据和控制信号,应用涉及从门锁到极其复杂的多媒体终端等方方面面。

对每个总线的需求各不相同,在低端应用需要低成本相对低速率的总线,在高端应用需要为视觉媒体提供高速率实时传输。

因为难以确定毕竟哪种标准会终于胜出,许多汽车OEM都支持多个标准。

对设计师而言,这些不确定性会延伸开发周期并可能终于导致失去商机。

本文介绍的基于的可重配置系统可以在设计后期甚至量产阶段通过重新编程以适应标准和协议的转变。

总线接口可以以配置IP内核的形式提前举行验证,这样可以节约时光和精力,因而可以缩短产品的面市时光。

图1:车载网络系统及其速率车载信息消遣系统和移动信息设备,特殊是车载导航系统,需要功能很强的操作系统及互连性。

目前,有数个组织和联盟引领着汽车总线的标准化方向,这包括MOST配合联盟、IDB论坛和SIG等等(图1)。

面对多媒体的系统传输(MOST)由MOST配合联盟主推的MOST网络,被用于衔接汽车中的多个设备,这些设备包括汽车导航系统、数字、、蜂窝电话及DVD。

MOST技术已被优化为可以用法塑料光纤,支持的数据传送率高达24.8Mbps,在设备层具有很高的牢靠性和可扩充性,同时还可彻低支持实时音频和压缩视频。

MOST总线已经被宝马、戴姆勒-克莱斯勒、Harman Becker、OASIS Silicon Systems等公司认可。

近期关于MOST项目的一个值得注重的例子是HarmanBecker汽车系统公司将其应用于最新型的BMW 7系列中。

智能传输系统数据总线(IDB)IDB论坛为那些从事开发售后市场和便携式设备的OEM公司推出IDB-C第1页共5页。

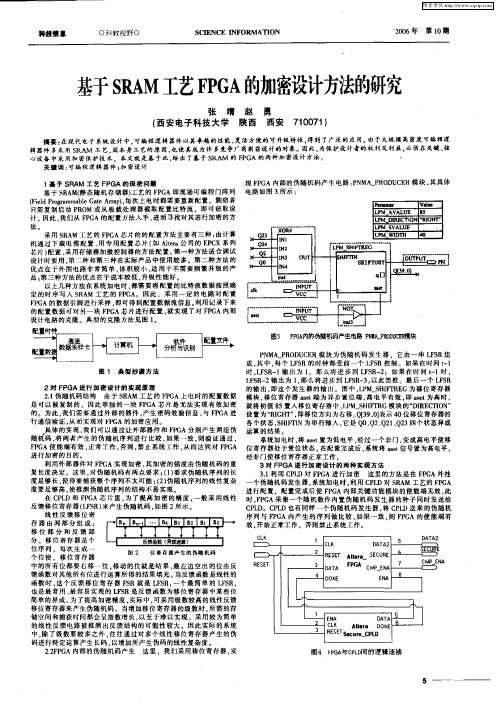

基于SRAM工艺FPGA的加密设计方法的研究

现 F G 内部 的 伪 随机 码 产 生 电 路 :N _ R U E 模 块 。 PA P MA P OD C R 其具 体

基于 S A 静态随机存储 器) R M( 工艺的 F G P A即现场可编 程门阵列 电路 如 图 3所 示 :

只需 复制 启动 P O 或从板载处理 器截取配置 比特 流 ,即可窃取设 RM

进 行 加 密的 目的 。

设 置为“IH ”即移位方向为右移。 [ .1 RG T , Q3 .表示 4 位移位寄存 器的 9O O 各个状 态,H F' S 1IN为串行输入 , I 它是 O 、 2 Q 1Q 3四个 状态异或 0 Q 、2 、 2

运算 的结 果 。 系统加 电时 , ae 置为低电平 , 将 st 经过 一个 非门, 变成 高电平使移

维普资讯

科技信息

O科毂视野 0

S IN E IF R TON CE C O MA I N

20 06年

第 l 期 O

基 RM 于SA FG 的 密 方 的 究 P A 加 设计 法 研

张 靖 赵 勇 ( 安 电子 科技 大学 陕 西 西安 西 707 ) 1 0 1

̄l : i - 在现代 电子系统设计 中, i 可编程逻辑 器件 以其卓越 的性能、 灵活 方便的 可升级_ 特性, 得到 了广泛的应 用。由于大规模 高密度可蝙程逻 辑器件 多采用 S. M 工 艺, PA 因奉 身工 艺的原 因, 也使其成为许 多竞争厂 商剥窃设计的对象。因此 。 为保 护设计 者的权利度利益 。 必须在关键 、 棱

LS一 F R 2输 出 为 1 那 么 将 进 步 到 L s 一 , , F R 3 以此 类 推 。最 后 一 个 L s FR

基于模块化设计方法实现FPGA动态部分重构汇总

基于模块化设计方法实现FPGA动态部分重构动态部分重构可以通过两种方法实现:基于模块化设计方法(Module-BasedParTIalReconfiguration)和基于差别的设计方法(Difference-BasedPartialReconfiguration),本文以基于模块化设计为例说明实现部分重构的方法。

1FPGA配置原理简介本文针对Xilinx公司的FPGA进行研究,支持模块化动态部分重构的器件族有Virtex/-II/-E和Virtex-IIPro。

Xilinx公司FPGA是基于SRAM工艺的,包括配置逻辑块(CLBs),输入输出块(IOBs),块RAMs,时钟资源和动态部分重构可以通过两种方法实现:基于模块化设计方法(Module-Based ParTIal Reconfiguration)和基于差别的设计方法(Difference-Based Partial Reconfiguration),本文以基于模块化设计为例说明实现部分重构的方法。

1 FPGA配置原理简介本文针对Xilinx公司的FPGA进行研究,支持模块化动态部分重构的器件族有Virtex/-II/-E和Virtex-II Pro。

Xilinx公司FPGA是基于SRAM工艺的,包括配置逻辑块(CLBs),输入输出块(IOBs),块RAMs,时钟资源和编程布线等资源[2]。

CLBs是构造用户所需逻辑的功能单元,IOBs提供封装引腿与内部信号引线的接口。

可编程互连资源提供布线通道连接可配置元件的输入和输出到相应的网络。

存储在内部配置存储器单元中的数值决定了FPGA实现的逻辑功能和互接方式。

Virtex FPGA的配置存储器是由配置列(Configuration Columns)组成的,这些配置列以垂直阵列的方式排列,如图1给出了Virtex-E XCV600E器件的配置列构成图。

配置存储器可分为五种配置列:Center 列包含四个全局时钟的配置信息;两个IOB 列存储位于器件左边和右边所有IOBs的配置信息;CLB列存储FPGA基本逻辑功能的配置信息;Block SelectRAM Content列存储内部块RAM的配置信息;Block SelectRAM Interconnect列存储内部块RAM间互联的配置信息[3]。

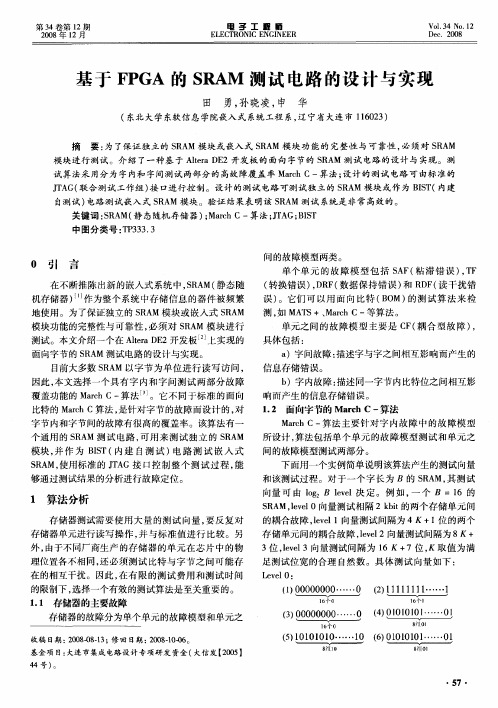

基于FPGA的SRAM测试电路的设计与实现

11 存储器的主要故障 . 存储器的故障分为单个单元的故障模型和单元之

收稿 日期 : 0 80 —3 修 回 日期 : 08 1- 。 20 -81 ; 2 0 —00 6

( o o 0 o …… 0 3 ooo o )

1个 0 6 8 圳O l

() 0 0 0 0 … l () 1 1 1 1 … 0 5l 1 1 1 … 0 6 00 00 … l

测试 。本文介 绍一 个在 Atr D 2开 发板 上实 现的 la E e 面 向字 节 的 S A 测试 电路 的设计 与实 现 。 R M

目前 大多数 S A 以 字节 为 单 位进 行 读 写 访 问 , R M 因此 , 文选 择一 个具 有 字 内 和字 问测 试 两 部分 故 障 本 覆盖功 能 的 Mac 算 法 。它 不 同于 标 准 的 面 向 rhC一 比特 的 Mac 法 , 针对 字节 的故 障而 设计 的 , rhC算 是 对 字节 内和字节 问 的故障有 很 高的覆 盖率 。该算 法有 一

试算法采用分为字内和字间测试两部分的高故 障覆盖率 M rh a 算法; c C一 设计的测试电路可由标准的 JA 联 合 测试 工作组 ) 口进行控 制 。设计 的测 试 电路 可测试 独立 的 S A 模块 或作 为 BS (内建 T G( 接 R M IT

自测试 ) 电路 测试嵌 入 式 S A R M模 块 。验证 结果 表 明该 S A 测 试 系统是 非常 高效 的。 RM 关键 词 :R M( 态随机存 储 器) Mac SA 静 ; rhC一算法 ; A BS J G;IT T

第3 第 l 4卷 2期 20 年 l 08 2月

电 子 工 蟹 师

EL T EC RON C E I NGI E NE R

基于SRAM和FPGA的DSO深存储功能设计9.2(产品设计12月)

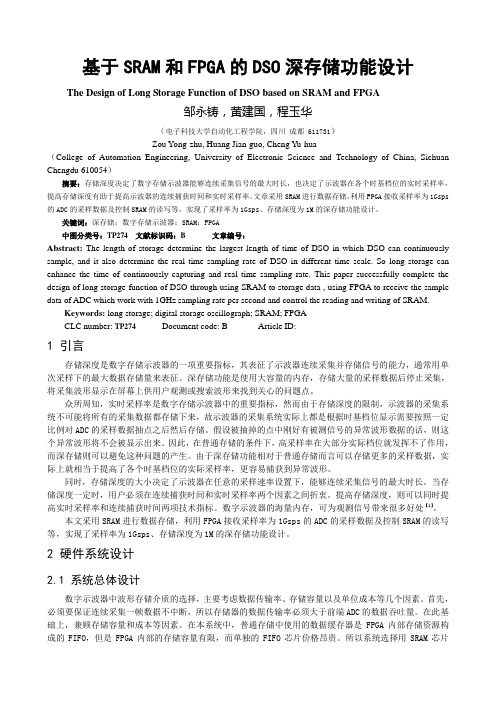

基于SRAM和FPGA的DSO深存储功能设计The Design of Long Storage Function of DSO based on SRAM and FPGA邹永铸,黄建国,程玉华(电子科技大学自动化工程学院,四川成都 611731)Zou Yong-zhu, Huang Jian-guo, Cheng Yu-hua(College of Automation Engineering, University of Electronic Science and Technology of China, Sichuan Chengdu 610054)摘要:存储深度决定了数字存储示波器能够连续采集信号的最大时长,也决定了示波器在各个时基档位的实时采样率,提高存储深度有助于提高示波器的连续捕获时间和实时采样率。

文章采用SRAM进行数据存储,利用FPGA接收采样率为1Gsps 的ADC的采样数据及控制SRAM的读写等,实现了采样率为1Gsps、存储深度为1M的深存储功能设计。

关键词:深存储;数字存储示波器;SRAM;FPGA中图分类号:TP274 文献标识码:B 文章编号:Abstract: The length of storage determine the largest length of time of DSO in which DSO can continuously sample, and it also determine the real time sampling rate of DSO in different time scale. So long storage can enhance the time of continuously capturing and real time sampling rate. This paper successfully complete the design of long storage function of DSO through using SRAM to storage data , using FPGA to receive the sample data of ADC which work with 1GHz sampling rate per second and control the reading and writing of SRAM.Keywords: long storage; digital storage oscillograph; SRAM; FPGACLC number: TP274Document code: B Article ID:1 引言存储深度是数字存储示波器的一项重要指标,其表征了示波器连续采集并存储信号的能力,通常用单次采样下的最大数据存储量来表征。

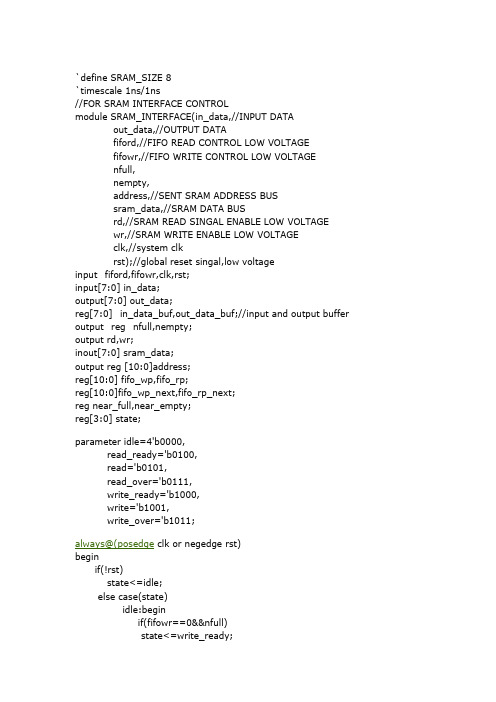

(完整word版)用FPGA实现SRAM读写控制的Verilog代码

`define SRAM_SIZE 8`timescale 1ns/1ns//FOR SRAM INTERFACE CONTROLmodule SRAM_INTERFACE(in_data,//INPUT DATAout_data,//OUTPUT DATAfiford,//FIFO READ CONTROL LOW VOLTAGEfifowr,//FIFO WRITE CONTROL LOW VOLTAGEnfull,nempty,address,//SENT SRAM ADDRESS BUSsram_data,//SRAM DATA BUSrd,//SRAM READ SINGAL ENABLE LOW VOLTAGEwr,//SRAM WRITE ENABLE LOW VOLTAGEclk,//system clkrst);//global reset singal,low voltageinput fiford,fifowr,clk,rst;input[7:0] in_data;output[7:0] out_data;reg[7:0] in_data_buf,out_data_buf;//input and output buffer output reg nfull,nempty;output rd,wr;inout[7:0] sram_data;output reg [10:0]address;reg[10:0] fifo_wp,fifo_rp;reg[10:0]fifo_wp_next,fifo_rp_next;reg near_full,near_empty;reg[3:0] state;parameter idle=4'b0000,read_ready='b0100,read='b0101,read_over='b0111,write_ready='b1000,write='b1001,write_over='b1011;always@(posedge clk or negedge rst)beginif(!rst)state<=idle;else case(state)idle:beginif(fifowr==0&&nfull)state<=write_ready;else if(fiford==0&&nempty)state<=read_ready;elsestate<=idle;endread_ready:state<=read;read:beginif(fiford==1)state<=read_over;elsestate<=read;endread_over:state<=idle;write_ready:state<=write;write:beginif(fifowr==1)state<=write_over;elsestate<=write;endwrite_over:state<=idle;default:state<=idle;endcaseendassign rd=~state[2];assign wr=(state==write)?fifowr:1'b1;always@(posedge clk)beginif(~fifowr)in_data_buf<=in_data;end//=============================================== ==============always@(state or fiford or fifowr or fifo_wp or fifo_rp)beginif(state[2]||~fiford)address=fifo_rp;else if(state[3]||~fifowr)elseaddress='bz;end//=============================================== ==================assign out_data=(state[2])?sram_data:8'bz;always@(posedge clk)beginif(state==read)out_data_buf<=sram_data;end//=============================================== ===always@(posedge clk or negedge rst)beginif(!rst)fifo_rp<=0;else if(state==read_over)fifo_rp<=fifo_rp_next;end//=============================================== ====always@(fifo_rp)beginif(fifo_rp==`SRAM_SIZE-1)fifo_rp_next=0;elsefifo_rp_next=fifo_rp+1;end//=============================================== ======always@(posedge clk or negedge rst)beginif(!rst)fifo_wp<=0;else if(state==write_over)fifo_wp<=fifo_wp_next;end//=============================================== ===always@(fifo_wp)beginif(fifo_wp==`SRAM_SIZE-1)elsefifo_wp_next=fifo_wp+1;end//=============================================== ====always@(posedge clk or negedge rst)beginif(!rst)near_empty<=1'b0;else if(fifo_wp==fifo_rp_next)near_empty<=1'b1;elsenear_empty<=1'b0;end//=============================================== ========always@(posedge clk or negedge rst)beginif(!rst)nempty<=1'b0;else if(near_empty&&state==read)nempty<=1'b0;else if(state==write)nempty<=1'b1;end//=============================================== =======always@(posedge clk or negedge rst)beginif(!rst)near_full<=1'b0;else if(fifo_rp==fifo_wp_next)near_full<=1'b1;elsenear_full<=1'b0;end//=============================================== =====always@(posedge clk or negedge rst)beginif(!rst)nfull<=1'b1;else if(near_full&&state==write)nfull<=1'b0;else if(state==read)nfull<=1'b1;end//=============================================== ============endmodule。

基于FPGA的动态可重构技术研究

64电子技术Electronic Technology电子技术与软件工程Electronic Technology & Software Engineering体功能实现方面,设计人员应立足于不同软件、网页的行业需求对导航栏、返回、信息提示框等方面进行悬浮型或是方框形的提示信息和窗口,并对多种软件图标以及展示界面进行上下级的任务链接,从而使用户能够在短时间内熟悉界面操作并完成交互指令和功能操作。

在对UI 视觉审美交互性进行设计时,主要是对文字、视频以及图标等视觉要素进行设计,并按照上下、垂直、左右以及居中等方式对其进行排班,便于用户检索需求。

另外,为使设备与用户能够更好的进行交互,对于窗口以及图标等方面的线条应尽量选择柔和的,同时,根据空间要素不同对功能区域之间的间隔进行设计,满足用户在软件产品操作过程中的心理需求[6]。

以中界面框架为例,在对其进行UI 界面交互式设计时,在保证交互功能的基础上需要保证各个设计和功能的协调性。

为此,可以采取上下结合的布局方式对UI 界面进行设计。

主要是将导航栏设计在界面最上方,并将关键信息放在导航栏上,从而使用户能够通过触摸、滑动或是点击导航栏进而快速进行信息检索或是浏览,并将网址放在上面,满足用户的功能使用。

在界面下方应设计图标按钮,通过点击和触摸能够直接打开软件,满足用户使用的多种需求。

除此之外,还可以使用导航栏在下放、展示页面在上方的界面布局。

在该布局方式中,主要是将重要信息设计在用户第一眼可以注意到的位置,从而更好的进行信息推送和交互,为此,应将导航栏设计在UI 界面下方。

在该布局下,用户只需要进行交互界面的滑动,或是对导航栏进行滑动、点击,就能够完成功能获取或是浏览等操作。

以微信UI 信息界面为例,最近使用的小程序图标为放置在最上方,而导航栏被设计在最下方,通过下滑,用户能够直接获得最近使用的小程序应用,满足其快速使用需求。

另外,为满足用户的使用需求,便于新用户使用,可以进登陆窗口设计在软件最上层,并使用箭头、文字等元素对用户进行引导,从而完成用户交互操作行为的同时,给予用户良好的使用体验。

在SRAM型FPGA中局部重构与配置刷新的兼容方案

第 32 卷第 2 期

杜新军等, 在 SRAM 型 FPGA 中局部重构与配置刷新的兼容方案

· 49·

[3 ] 制刷新的过程 。其系统结构示于图 1 。 图 1 中左侧的存储 器中存 储 着原 始 的 配置数据, 为了

防止其中的配置数据 受 到单 粒子 效 应 的 影响 发 生 翻 转, 通 常该存储器 采 用 抗 单 粒子 翻 转 的 存 储 器 件, 如 PROM 等。 在单独的配置刷 新 过 程 中, 不 会 涉及 对 存 储 器 的 写 操作, 因此图中的存储器与配置 控 制 器 的 数据 流 为 单 向, 由于本 文中的方案涉及对存 储 器中 的 配置数据进 行 更 新, 因此数 据流方向会调整为 双 向, 下 文 还 会 详 细 讨 论 该 问题。 配置 图1 配置刷新系统结构简图

3

兼容解决方案

针对前文所述的配置刷新与局部重构的兼容问题, 提出 一种 解 决 方案。配置刷 新 采 用 检 测 刷 新的 方 式, 其中的比较校验过程应用 CRC 编码校验方式。其系统结构如图 3 所示。 其中, 图 3 左侧为可读写的 存储 器, 用 于 配 置 数 据 的 读 写。 方案中的控制 器 可 以用 FPGA 来 实现, 在实际应用中, 为保 证 可 靠 性, 控 制 器 FPGA 应 选 用 反 熔丝 型。 3. 1 主控制器 主 控 制 器 由 主 状 态 机、 比较 器及 CRC 编码模 块 组 成, 控制局 部重构与配置刷新的具体 操作 过 程, 以及二者之间的切换。 3. 2 端口控制 图 3 兼容方案系统结构简图 端口控 制 包含三 个 模 块 ( 如 图 3 所示) : 外部通信模块接收外部 总线 传 来 的 局部重构配置数据, 并 且 与 外 部 总线 进 行指 令交 互; 存 储 器端口控制模块控制对存储器的读写操作; 配置端口控制模块控制对目标 FPGA 的回读及写入。

基于FPGA和SRAM的数控振荡器的设计与实现

Ke od: u r a cnrl doclt NC ) l k u be C V10 ;C 7 12 ;ds n yw rs nmei l ot l sia r( O; o - pt l;X 2 00 Y C 0 1 ei c oe l o o a g

文 献标识 码 : A 文章编 号 :0 6 6 7 (0 6 0 — 0 2 0 10 — 9 7 2 0 ) 1 0 2 — 3 中图分 类号 :N 1 、 T 9 43

De i n a d i p e n a i n o u e ia o t ol d o cl t r sg n m lme t t fn m rc lc n r l s i a o o e l

R M 作 为 查 找表 , 于 片内ቤተ መጻሕፍቲ ባይዱ资源 的 限制 , O 由 查找 表 的

深 度 和宽 度一 般 不会 很 大 ( 常 为 2 6 8bt) 大 通 5 x i , s

大 限 制 了 N O 性 能 的 提 高 。 用 独 立 的 大 容 量 C

SA R M作为 查 找 表 , 查 找表 从 片 内移 到 片外 . 以 把 可

1 引言

数控 振 荡 器 是 数 字 通信 中 调 制解 调 单 元 必 不

事 先 根据 各 个 N O正 弦波相 位 计算 好 相位 的正 弦 C 值 , 以相 位 角 度作 为地 址 把该 相位 的正 弦值 数 据 并 存 储在 表 中 . 然后 通 过 相位 累加产 生 地 址信 息 读取 当 前 时刻 的相 位 值在 表 中对 应 的 正 弦值 , 而 产生 从

维普资讯

一

2一 2

《 国外 电子元器 ̄)06年第 1 20 期 20 年 1 06 月

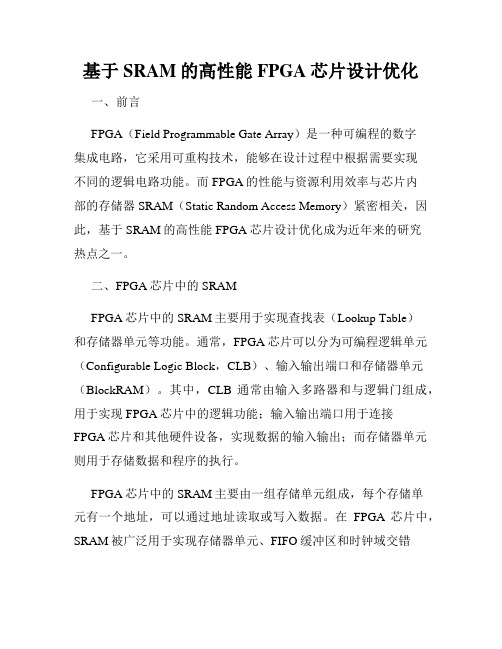

基于SRAM的高性能FPGA芯片设计优化

基于SRAM的高性能FPGA芯片设计优化一、前言FPGA(Field Programmable Gate Array)是一种可编程的数字集成电路,它采用可重构技术,能够在设计过程中根据需要实现不同的逻辑电路功能。

而FPGA的性能与资源利用效率与芯片内部的存储器SRAM(Static Random Access Memory)紧密相关,因此,基于SRAM的高性能FPGA芯片设计优化成为近年来的研究热点之一。

二、FPGA芯片中的SRAMFPGA芯片中的SRAM主要用于实现查找表(Lookup Table)和存储器单元等功能。

通常,FPGA芯片可以分为可编程逻辑单元(Configurable Logic Block,CLB)、输入输出端口和存储器单元(BlockRAM)。

其中,CLB通常由输入多路器和与逻辑门组成,用于实现FPGA芯片中的逻辑功能;输入输出端口用于连接FPGA芯片和其他硬件设备,实现数据的输入输出;而存储器单元则用于存储数据和程序的执行。

FPGA芯片中的SRAM主要由一组存储单元组成,每个存储单元有一个地址,可以通过地址读取或写入数据。

在FPGA芯片中,SRAM被广泛用于实现存储器单元、FIFO缓冲区和时钟域交错RAM等功能。

由于SRAM的存取速度较快,在FPGA芯片中往往被用作高速存储单元,用于存储大量的数据和状态信息。

三、基于SRAM的FPGA芯片设计的优化在FPGA芯片设计中,针对SRAM的优化技术包括SRAM的布局和对SRAM的访问方式等方面,旨在提高FPGA芯片的性能和资源利用率,具体包括以下几个方面:1.布局优化SRAM的布局是影响FPGA芯片性能的重要因素之一。

通常,在FPGA芯片中,SRAM单元的数量决定了FPGA芯片的总容量,而SRAM单元之间的布局则影响了FPGA芯片的存储器单元读写速度、电功率和时序等方面。

为了实现更高的性能和资源利用率,可以采用如下的布局优化技术:(1)优化SRAM单元的位置在FPGA芯片中,SRAM单元的位置与晶体管、传输线等零部件的位置密切相关。

动态局部可重构

• 总线宏是两个模块间的一个固定的布线桥。

总线宏的通讯

总线宏是两个模块间 的一个固定的布线桥

左边的A是一个模块,右边的B是另一个模块,A或者B是可重构模块,或者AB全是 可重构模块。A和B中间的总线宏,就是支持AB之间通信的特殊总线宏。它保证 AB间布线资源的不变性,也就是说当一个模块进行重构时模块内部信号用到的 布线资源不能改变。

基于差异动态重构设计流程

初始化设计

局部修改

布局布线结果 初始配置数据

修改后的布局 布线结果

比较

针对修改的部分动态 重构配置数据

基于差异的局部动态可重构局限性

• 基于差异重构系统的重构文件大小可以减少60%,极大的减少了重构 的配置时间。但是基于差异的重构方式所需要存储的副本太多,虽然 减少了系统重构时间,但是需要大量的存储空间。

• Xilinx ISE已经更新到第四代部分重配置功能,可以在FPGA运行的情况下, 加载部分bit文件,而改变其功能,这能大幅扩展 FPGA 的功能,因为包括 BRAM、DSP模块和 IO等在内的几乎 FPGA 所有资源都是可重配置的。除了减 小可编程系统的尺寸、重量、功耗和成本之外,部分重配置技术还能支持多 种不同的高级 FPGA 应用,如设计安全性和加速可配置计算等新技术。

• 下载这个配置文件必然比整个配置文件节约大量的时间,但是这种设 计流程只适合不太复杂的电路设计,因为电路复杂,人工的修改配置 信息很容易发生配置错误,甚至导致电路的损坏。

基于模块的局部可重构

• 可重构区域:局部可重构定义了一些特殊的区域,这些区 域可以在器件的其他部分还在运行的情况下进行重构,这 些特殊区域称作可重构区域。

用ARM对FPGA进行配置的原理与方法

用ARM对FPGA进行配置的原理与方法

0引言

基于SRAM工艺FPGA在每次上电后需要进行配置,通常情况下FPGA的

配置文件由片外专用的EPROM来加载。

这种传统配置方式是在FPGA的功能相对稳定的情况下采用的。

在系统设计要求配置速度高、容量大、以及远程升级时,这种方法就显得很不实际也不方便。

本文介绍了通过ARM对可编程器件进行配置的的设计和实现。

1 配置原理与方式

1.1配置原理

在FPGA正常工作时,配置数据存储在SRAM单元中,这个SRAM单元也被称为配置存储器(Configuration RAM)。

由于SRAM是易失性的存储器,因此FPGA在上电之后,外部电路需要将配置数据重新载入到片内的配置RAM中。

在芯片配置完成后,内部的寄存器以及I/O管脚必须进行初始化。

等初始化完成以后,芯片才会按照用户设计的功能正常工作。

1.2配置方式

根据FPGA在配置电路中的角色,其配置数据可以使用3种方式载入到目标器件中:

-FPGA主动(Active)方式;

-FPGA 被动(Passive)方式;

-JTAG 方式;

在FPGA 主动方式下,由目标FPGA来主动输出控制和同步信号(包括配置时钟)给专用的一种串行配置芯片,在配置芯片收到命令后,就把配置数据发到FPGA,完成配置过程。

在被动方式下,由系统中的其他设备发起并控制配置。

FPGA配置SRAM设计技术

A bstract:The paper f irst analyzes the role of SRAM in the FPGA SRA M ,introduces the structure of SRAM and the key points in the design,it desig n s a SRA M structure based on 65 nm process,and the corresponding simulation results are given for the reading and writing ability,pow er consumption and noise.This circuit structure which has been used in FPG A design and taped out successfullyhas the advantages of low power consum ption and st rong anti—noise ability. Keywords:FPGA;configuration SRAM ;static noise margin;read stability

1 引言

现场 可 编 程 门 阵 列 (FPGA,Field Programmable Gate Array)是 一种半定 制集成 电路 ,在其 内部集成 了 大量的 l'3+n触发器等基本逻辑 电路 ,用 户通 过编程来 改变其 内部 的逻辑关 系或连线 ,就可 以得到需要 的设 计 电 路 。FPGA 按 照 编 程 方 式 可 分 为 SRAM 型 、 ANTI—FLASH 型 、FLASH 型等 ,SRAM 型是迄 今为止 应 用范 围最广的 架构 ,具 有 密度高 、速 度快且 具有 可 重复编程能力 。配置 SRAM 作用是用户编程后存储配 置的代码 ,同时对于采用 SRAM 工艺 的可编程 逻辑 器 件而言 ,要求每次上电对可编程逻辑器件进行重配置『1】, 因此 SRAM 的设 计是 FPGA 芯片能 否正 常实现 配置

SRAM型FPGA的单粒子效应及TMR设计加固

SRAM型FPGA的单粒子效应及TMR设计加固SRAM型FPGA的单粒子效应及TMR设计加固随着科技的不断推进,先进的电子器件逐渐在各个领域中得到了广泛应用。

其中,SRAM型FPGA (静态随机存取存储器型场可编程门阵列) 作为一种重要的可编程电子器件类型,已经被广泛应用并且取得了显著的成果。

SRAM型FPGA 采用静态随机存储器(SRAM)作为存储单元,具有速度快、功耗低、容量大、可编程性强等特点,但是其单粒子效应使得其在高能环境下工作不稳定。

针对这一问题,通过引入TMR(三重模容纳)技术,可以有效地提高其抗干扰能力,从而使FPGA的性能更加出色。

SRAM型FPGA 的单粒子效应是指在FPGA的使用过程中,突然冲击的单个粒子会改变SRAM型FPGA的特性,从而使其工作状态发生变化。

这种现象不仅会引起电路不正常运行,还可能导致电路出现故障,从而影响FPGA 的使用效果。

单粒子效应可以通过三种方式引起:1、离子辐射;2、中子; 3、自然背景辐射。

其中,离子辐射是最常见的单粒子效应。

在SRAM型FPGA 中,单粒子效应的发生通常表现为临时错误和持久错误。

为了解决SRAM型FPGA 单粒子效应的问题,可以通过引入TMR 技术进行加固。

TMR 技术是通过多次问询同一个存储器元件,并发出相互独立的电路信号,从而提高存储器单元的可靠性。

在TMR技术中,每个存储器元件分为三个部分,每个部分都包含同一个值,通过比对这三个存储器元件值之间的异同,可以更好地判断正确记录的值。

当SRAM型FPGA 发生错误时,TMR 技术可以将 SRAM中不正确的数据与其他正确数据进行比对,最终确定正确的数据。

TMR 技术可以显著提高SRAM型FPGA的抗单粒子效应干扰能力,从而提高FPGA的可靠性和性能。

总的来说,SRAM型FPGA 在单粒子效应方面存在较大的问题,而TMR 技术作为一种有效的抗干扰技术,可以明显提高SRAM型FPGA的可靠性。

基于单片机的可编程逻辑器件配置及加密

中国校外教育理论 学科教育5基于单片机的可编程逻辑器件配置及加密◆何惠芳 唐小煜本文介绍了基于SRA M 的可编程逻辑器件的原理,以A lte ra 公司的FLEX 10K 系列芯片为例,从系统的复杂度、经济性、可扩展性和保密性等方面,对多种系统配置方式进行比较,提出了由单片机和E 2PROM 存储器组成的被动串行配置方式,并采用单片机产生长伪随机码序列的方法,实现对系统的加密。

现场可编程门阵列(FPG A ) 静态随机存储器(SRA M ) 被动串行配置(PS )引言基于S RA M 的可重配置FPG A 用来实现各种存储器及复杂的逻辑功能,系统内硬件功能完全由软件程序实现,允许系统设计者全面控制FP 2G A 内部的逻辑功能,非常方便快捷地反复修改设计。

另外,FPG A 重配置控制电路线路结构简洁、开发容易、体积小、成本低,因而深受设计者青睐。

1.基于SR AM 的可重配置FPG A 的结构基于S RA M LUT 结构的FPG A 器件,由于是易失性器件,配置数据必须保存在FPG A 器件以外的EPR OM 、E 2PR OM 或Flas h RO M 等非易失性存储器内,以便使系统在适当的时候将其下载到FPG A 中。

因此,它没有I SP (在系统可编程)的概念,代之以I CR (在线可重配置)。

2.可编程逻辑器件的配置原理概述(1)FPG A 的工作状态FPG A 的工作状态分为三种:一种称之为用户状态(U s er),指电路中FPG A 器件正常工作时的状态;另一种是配置状态(C onfi gurati on),指将编程数据装入FPG A 器件的过程,也可以称为构造;第三种是初始化状态(Ini ti alizati on ),FPG A 复位各类寄存器,让I/O 引脚为逻辑器件正常工作做准备。

(2)配置方式分类Altera 的FPGA 可以使用6种配置模式,由模式选择引脚MSEL1和M SE L2的电平来决定。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

适 用于汽 车产 业的 运行 时可重 配置 计算 技

耗 与 禁 用 区域 部 分 成 比 例 降 低 。在 使 用 汽 车 电 术 最 强 大 的 特 性 无 疑 是 共 享 的 硬 件 资 源 上 功 能

基 础 电子 l 01 1 2 2.0

I 技术前沿 I rnire h oo y o t c n lg F eT

含 有不必 在启动 时 ( 如在E CU唤醒或加 电 )配

在 采 用 运 行 时 可 重 配 置 逻 辑 的 系统 中 ,

E

置 的 部 分 可 重 配 置 区 域 ,可 以 缩 短 系 统 启 动 时 汽 车 设 计 人 员 还 可 使 用 一 种 从 航 空 航 天 应 用 间 。 不 支 持 动 态 部 分 可 重 配 置 的F GA在 加 电 时 中 借 鉴 来 的 重 配 置 技 术 。 重 配 置 (o f u ai n P c n i r to g

-

由于 当今 先 进 的 FP GA器 件 具 有 巨 大 的 容 配 置 硬 件 外 设 可 保 证 系 统 在 出 现 故 障 时 自我 修

量 ,故 在加 电时下 载 完整 的位 流会 引起 可观 的 复 。另外 ,这样也 可 以将故 障的最 大时 长限 制

配 置 时 间 开 销 。运 行 时 部 分 可 重 配 置 技 术 能 够 在 重 配 置 时 间 间 隔 内 。 这 种 技 术 也 通 常 运 用 在 显 著 地 缩 短 这 种 配 置 时 延 。 在 那 种 情 况 下 , 有 软 件 中 ,作 为 一 种 常 见 的 抗 干 扰 保 护 措 施 ,例 可 能 在 加 电 时 只配 置 一 个 最 起 码 的 子 系 统 ,让  ̄MC b 的 定 期 重 配 置 。 I Ug 设 I 系 统 其 余 部 分 保 持 待 机 状 态 ,直 到 有 必 要 初 始

供 更 多优 势 。

功 能 的F GA设 计 E U,能 够 为汽 车 设 计 人 员提 低 。 同 样 , 可 以 在 不 需 要 的 时 候 使 用 空 白 位 流 P C

禁 用F GA的部分区域 ,减少逻辑活动 ,从而 降 P

事实 上 ,其 中的 一大 优势 是 如果F PGA包 低动 态功 耗 。

另一 项运 行时 部分 重配置 技术 的灵 活性带

化 为 止 。 如 果 系统 在 加 电 或 唤 醒 时 需 要 快 速 响 来 的 有 前 景 的 功 能 是 在 F GA资 源 的某 个 特 定 二 P

应 ,可 将这种 启动 工作 划分 为两个 阶段 ,以加 维 位 置 出现 永 久 性 或 不 可 修 复 的 电 路 故 障 , 比

简 化制 造厂 的物流 要 求 ,将 存货 压 低到最 低水 平 。这 是 因为从硬 件 的角 度来 看 ,在 生产 线上

组 装的 模块对 所 有车辆 都是 一样 的 ,只有 可下 载 的位 流 会 让 E U的功 能 具 有 差异 。 C

高集 成度 E U C

对 汽 车 电 子 设 备 这 个 以 大 批 量 制 胜 的 产 业

C删

I 技术前沿 lr nir e h oo y o t ቤተ መጻሕፍቲ ባይዱ c n lg F eT

■

■ 基于S AM并部分可重配 R

尉戡 一

F . 1

l 西班牙塔拉戈纳R vr i i i大学 l r n o s o i rl aV gi l i oF n Ma a

G 在运行时可重配置硬件上进行 E C AU设计 ~

C U

需 要配 置 所 有 的 F GA资 源 ,但 运 行 时 可 重 配 置 srb ig可 以 将 系 统从 因单 粒 子 翻转 (E ) 电 P cubn ) S U和 FG P A只需 下 载 部 分 位 流 进 行 部 分 重 配 置 。

磁干扰造成 的S M故障中恢复过来。定期重新 RA

( 一般来说是主机C U) ,以及可重配 置引擎和 动 重 定 位 到 同 一 E P CU中 的 可 编 程 逻 辑 器 件 的 其 通 往位 流库 的数据 链路 。 由特定部 分位 流描述 他 部 分 。 虽 然 这 个 构 思 是 可 行 的 , 但 这 项 功 能

的其 他 域 可 按 应 用 需 求 ,随 后 下 载 。 另 外 ,如 果 禁 用P R域 ,则 可 以 让 器件 的功 R 还 没 有得 到 当今 的 自动 化 工 具 的完 全 支 持 。

图1在 由部分可重配置域和静态域构成 的运 行时 - IF |F G  ̄ - J . P A中 ' 实现 的汽 车E U应用的空间分区和临时分 区 C

汽 车 中 特 定 的 ECU功 能 进 行 定 制 。 这 种 构 想 在 技 术 上 借 助 可 重 配 置 硬 件 具 有 可 行 性 ,能 够

池 供 电 的ECU中 , 节 能 模 式 尤 为 重 要 。 为 此 ,

在 车辆 未使 用时 ( 即处 于休 眠模式 时 ) ,车载

采 用基 于 S RAM并 具 备 运 行 时 部分 可重 配 置 E CU可 使 用 低 功 耗 模 式 ,以 让 E Cu功 耗 保 持 最

计 一 设 。

的实时 时分 复用 。可 以对 由ECU中的相 同计算 而 言 ,控制 车载嵌 入 式系统 的 成本 对汽车 制造

快 初 始 化 过 程 。 为 此 , 可 将 系 统 架 构 分 解 为 如影响到特 定逻辑单 元或R AM模块 时 ,可通 过

一

个 静 态 域 和 一 个 或 者 多 个 部 分 可 重 配 置 域 功 能 重 定 位 实 现 故 障 修 复 。 一 旦 发 现 有 硬 件 或

( RR 。 静 态 域 涵 盖 负 责 执 行 启 动 过 程 的 系统 软 件 故 障 出 现 ,可 以 在 运 行 中 将 所 需 的 功 能 自 P )