Modelsim上机指导1

Modelsim仿真新手入门最详细教程

Modelsim仿真新⼿⼊门最详细教程2021年11⽉15⽇00 安装包/版本我是提前在⽹上下好的(但这⼀点也给我的实验造成了“⿇烦”),⽤的是Modelsim SE-64 2020.4版本的,学校实验室的似乎不同。

但最终没有太⼤影响。

01 配置环境步骤学校有⼀个⽂档,在机房电脑照做就⾏。

我因为是⾃⼰下载的,配置与机房软件有所不同,所以⼜平添了很多⿇烦。

01-0 verilog⽂件这个代码可以在很多地⽅编写:Visual Studio Code⾥有Verilog的插件;还可以有更强⼤的语⾔编辑器:Nodepad++。

这⾥我使⽤的是Nodepad++,因为看上去专业⼀点。

Nodepad++的页⾯效果如图:其实第⼀次上机,⽼师会给⼤家⽰例⽂件(包括设计代码与测试代码),跑出来⽰例波形就⾏。

01-1 具体步骤1. 新建⼀个⽤于安放project的⽂档,放在哪⾥都⾏。

把前⾯做出的.v⽂件添加到这个⽂档。

留意⼀下路径。

2. 打开modelsim,在jumpstart中create a new project。

3. 在弹出的提⽰框⾥browse,找到刚才的⽂件夹。

选中。

填写project 名,注意要与.v⽂件⾥的module名保持⼀致。

点击ok。

4. 进⼊页⾯后会是这样⼦:注意此处两个⽂件后⾯应当都有问号,代表没有编译。

先逐个右击⽂件add to this project确保加⼊。

5. 在上⽅提⽰栏中complie->compile all。

稍等些许会看到⽂件后问号全部变为对勾,表⽰代码编译通过,没有问题。

如果此步出错则代表代码有bug。

在下⾯的Transcript中上翻查找错误。

6. 点击上⽅Simulate->start simulation。

由于注意与实验室不同的,选中下⾯的Enable optimization,再在右侧Optimization Options中的Visibility中选中Apply full visibility....7. 接着在work⾥找到测试代码的⽂件,选中。

ModelSim轻松入门1

1.用KEY.exe生成的:2.加入到环境变量中:“我的电脑”——“属性”——“高级”——“环境变量”。

注意:我的系统为WINXP,一定要打开计算机的网络,如果不打开生产的LICENSE.dat不能使用。

“新建”——“用户变量”。

如图:4打开Modesim.建立项目和库文件,项目名:COUNTER;库名:WORK。

5.点“OK”,双击“Add Existing File”后点击”Browse…”,找到(Modelsim安装目录)\Modeltech_6.1f\examples\tutorials\verilog\automation\counter.v6.编译菜单栏“Compile”——“Compile All”。

7.仿真(1)切换到“Library”——“WORK”,双击里面的“counter”。

(2)进入的仿真界面把选中“counter”点右键选中“Add”的“Add to Wave”加入到“wave”中以观察波形(3)改变“Wave”中的CLK和RESET的值。

选中“Wave”中的CLK——右键——“Clock….”——“OK”选中“Wave”中的RESET——右键——“Force…”——“Value”为1——“OK”。

然后点“RUN”。

这时候“Wave”会有波形,但计数器是没有输出。

然后选中“Wave”中的RESET——右键——“Force…”——“Value”为0——“OK。

然后点击“RUN”计数器输出“count”会有波形输出。

最后的波形如下:以上仿真没有输入任何的Modelsim内部指令。

以上是个人对ModelSim的理解,如有错误请指正。

谢谢!Bynce2006 10.31。

modelsim使用教程

modelsim使用教程ModelSim是一款常用的硬件描述语言(HDL)仿真工具,本教程将向您介绍如何使用ModelSim进行仿真。

步骤1:安装ModelSim首先,您需要下载和安装ModelSim软件。

在您的电脑上找到安装程序并按照提示进行安装。

步骤2:创建工程打开ModelSim软件,点击"File"菜单中的"New",然后选择"Project"。

在弹出的对话框中,选择工程的存储位置,并为工程命名。

点击"OK"完成工程创建。

步骤3:添加设计文件在ModelSim的工程窗口中,右键点击"Design"文件夹,选择"Add Existing File"。

然后选择包含您的设计文件的目录,并将其添加到工程中。

步骤4:配置仿真设置在工程窗口中,右键点击"Design"文件夹,选择"Properties"。

在弹出的对话框中,选择"Simulation"选项卡。

在"Top level entity"字段中,选择您的设计的顶层模块。

点击"Apply"和"OK"保存设置。

步骤5:运行仿真在ModelSim的工具栏中,找到"Simulate"按钮,点击并选择"Start Simulation"。

这将打开仿真窗口。

在仿真窗口中,您可以使用不同的命令来控制和观察设计的行为。

步骤6:查看仿真结果您可以在仿真窗口中查看信号波形、调试设计并分析仿真结果。

在仿真窗口的菜单栏中,您可以找到一些常用的查看和分析工具,如波形浏览器、信号分析器等。

步骤7:结束仿真当您完成仿真时,可以选择在仿真窗口的菜单栏中找到"Simulate"按钮,并选择"End Simulation"以结束仿真。

ModelSim新手使用手册

ModelSim最基本的操作,初次使用ModelSim的同学,可以看看,相互学习。

无论学哪种语言,我都希望有个IDE来帮助我创建一个工程,管理工程里的文件,能够检查我编写代码的语法错误,能够编译运行出现结果,看看和预期的结果有没有出入,对于Verilog语言,我用过Altera的Quartus II,Xilinx的ISE,还有ModelSim(我用的是Altera 官网的ModelSim_Altera),甚至MAXPlus II,不过感觉这软件太老了,建议还是前三者吧。

学Verilog,找一本好书很重要,参考网友的建议,我也买了一本夏宇闻老师的《Verilog 数字系统设计教程》,用Quartus II来编写代码,个人觉得它的界面比ISE和ModelSim友好,我一般用它编写代码综合后自动生成testbench,然后可以直接调用ModelSim仿真,真的很方便,但学着学着,发现夏老师书里的例子很多都是不可综合的,比如那些系统命令,导致很多现象都发现不了,偶然间我直接打开了ModelSim,打开了软件自带的英文文档,步骤是:Help ->PDF Documentation->Tutorial如下所示:打开文档的一部分目录:往下读发现其实ModelSim可以直接创建工程,并仿真的。

下面以奇偶校验为例叙述其使用过程(当然前提是你在Altera官网下载了ModelSim并正确安装了)。

1.打开软件,新建一个工程,并保存到自定义的目录中(最好别含中文路径)2.点击Project,弹出窗口问是否关闭当前工程,点击Yes,接着又弹出如下窗口我个人的习惯是把Project Name和Default Library Name写成一样,自己定义Project Location。

又弹出如下窗口:3.点击Close(我的版本不能Create New File,其实新建好了工程一样可以新建.v文件),然后点击屏幕下方的Project标签:如果一开始不是如上图所示的界面,那么可以点击如下图所示红色标记的按键变成上图界面:4.在屏幕空白处右击鼠标,出现如下窗口:5.现在可以选New File或者Existing File(首先你已经编写好了)。

modelsim使用技巧

modelsim使用技巧ModelSim是一款常用的仿真工具,用于学习、开发和测试各种数字电路和系统设计。

它提供了大量的功能,可以帮助我们更好地进行仿真、调试和性能优化。

但是,对于初学者来说,熟练使用ModelSim可能需要一些时间和实践。

在本文中,我们将介绍一些ModelSim的使用技巧,以帮助读者更好地掌握这个工具。

一、基本操作1.创建工程在ModelSim中,创建工程是第一步。

可以通过File -> New -> Project来创建一个新的工程。

在工程创建过程中,需要指定工作目录、项目名称和工具链等信息。

在创建工程后,可以右键单击仿真文件夹,并选择添加到工程来添加设计文件。

2.添加仿真文件在ModelSim中,添加仿真文件非常简单。

可以将文件拖放到仿真文件夹、使用File -> Add to Project选项或使用命令行方式添加文件。

一旦添加了仿真文件,可以使用filelist命令查看所有添加的文件。

3.编译设计在ModelSim中,编译由两个阶段组成。

第一阶段称为分析阶段,在此阶段中,设计的各个模块被分析、组合并建立数据结构。

第二阶段称为综合阶段,在此阶段中,数据结构被综合成一个整体,并生成仿真网表。

可以通过compile option来指定编译选项,比如-v库等。

4.运行仿真在ModelSim中,可以通过三种方式来运行仿真。

第一种是在命令行中使用run命令,第二种是通过菜单和工具栏选项来启动仿真,第三种是使用脚本方式启动仿真。

在仿真过程中,可以使用wave、add wave、force、release等命令来控制信号的行为。

二、ModelSim高级技巧1.波形窗口波形窗口是ModelSim中最有用的窗口之一。

可以使用Add Wave按钮打开该窗口。

在波形窗口中,可以查看所有信号的变化情况。

可以使用full view、zoom in、zoom out等选项来放大或缩小波形窗口。

modelsim的详细使用方法

一、简介ModelSim是一款由美国Mentor Graphics公司推出的集成电路仿真软件,广泛应用于数字电路和系统设计领域。

它提供了强大的仿真和验证功能,能够帮助工程师快速高效地进行电路设计与验证工作。

本文将详细介绍ModelSim的使用方法,以帮助读者更好地掌握这一工具的操作技巧。

二、安装与配置1. 下载ModelSim安装包,并解压到指定目录2. 打开终端,进入ModelSim安装目录,执行安装命令3. 安装完成后,配置环境变量,以便在任何目录下都能够调用ModelSim程序4. 打开ModelSim,进行软件注册和授权,确保软件可以正常运行三、工程创建与管理1. 新建工程:在ModelSim主界面点击“File” -> “New” -> “Project”,输入工程名称和存储路径,选择工程类型和目标设备,点击“OK”完成工程创建2. 添加文件:在工程目录下右键点击“Add Existing”,选择要添加的源文件,点击“OK”完成文件添加3. 管理工程:在ModelSim中可以方便地对工程进行管理,包括文件的增删改查以及工程参数的设置等四、代码编写与编辑1. 在ModelSim中支持Verilog、VHDL等多种硬件描述语言的编写和编辑2. 在ModelSim主界面点击“File” -> “New” -> “File”,选择要新建的文件类型和存储位置,输入文件名称,点击“OK”完成文件创建3. 在编辑器中进行代码编写,支持代码高亮、自动缩进、语法检查等功能4. 保存代码并进行语法检查,确保代码符合规范,没有错误五、仿真与调试1. 编译工程:在ModelSim中进行代码编译,生成仿真所需的可执行文件2. 设置仿真参数:在“Simulation”菜单下选择“S tart Simulation”,设置仿真时钟周期、输入信号等参数3. 运行仿真:点击“Run”按钮,ModelSim将开始对设计进行仿真,同时显示波形图和仿真结果4. 调试设计:在仿真过程中,可以通过波形图和仿真控制面板对设计进行调试,查找并解决可能存在的逻辑错误六、波形查看与分析1. 查看波形:在仿真过程中,ModelSim会生成相应的波形文件,用户可以通过“Wave”菜单查看波形并进行波形分析2. 波形操作:支持波形的放大、缩小、平移、选中等操作,方便用户对波形进行分析和观察3. 波形保存:用户可以将波形结果保存为图片或文本文件,以便日后查阅和分析七、性能优化与验证1. 时序优化:在设计仿真过程中,可以通过观察波形和性能分析结果,对设计进行优化,提高设计的时序性能2. 逻辑验证:通过对仿真的结果进行逻辑验证,确保设计符合预期的逻辑功能3. 时序验证:对设计的时序性能进行验证,确保信号传输和时钟同步的正确性八、项目输出与文档整理1. 输出结果:在仿真和验证完成后,可以将仿真结果、波形图和性能分析结果输出为文本文件或图片,方便后续的文档整理和报告撰写2. 结果分析:对仿真结果和验证结果进行详细的分析,确定设计的性能和功能是否符合设计要求3. 文档整理:根据仿真和验证结果,进行文档整理和报告撰写,为后续的设计和优化工作提供参考九、总结与展望ModelSim作为一款专业的集成电路仿真软件,具有着强大的功能和丰富的特性,可以帮助工程师进行电路设计与验证工作。

modelsim使用方法

modelsim使用方法ModelSim 是一种功能强大的硬件描述语言 (HDL) 模拟工具,支持VHDL和Verilog,可用于设计和验证数字系统。

本文将介绍如何使用ModelSim。

**安装 ModelSim****创建项目**在启动 ModelSim 后,首先需要创建一个新的项目。

选择 "File" 菜单,然后选择 "New" -> "Project"。

在打开的对话框中,选择项目的文件夹和项目名称,然后点击 "OK"。

**添加设计文件和测试文件**在项目中,您需要添加设计文件和测试文件。

选择 "Project" 菜单,然后选择 "Add to Project" -> "Add Files". 在打开的对话框中,选择您的设计文件 (VHDL 或 Verilog) 和测试文件,然后点击 "OK"。

**设置仿真**在编译代码之后,下一步是设置仿真选项。

选择 "Simulate" 菜单,然后选择 "Start Simulation"。

在打开的对话框中,选择您的顶层模块。

您还可以选择以 GUI 模式还是批处理模式运行仿真。

在设置仿真之前,您可以添加信号波形文件以在仿真过程中显示波形。

选择 "Simulate" -> "Wave" -> "Add Waveform". 然后,选择信号波形文件 (.do 或 .vcd),并点击 "OK"。

**运行仿真**设置仿真选项后,您可以开始执行仿真。

通过选择 "Simulate" -> "Run",可以运行单步或连续仿真。

ModelSim简明操作指南

第一章 介 绍本指南是为ModelSim5.5f版本编写的,该版本运行于UNIX和Microsoft Windows 95/98/Me/NT/2000的操作系统环境中。

本指南覆盖了VHDL和Verilog 模拟仿真,但是你在学习过程中会发现对于单纯的HDL设计工作而言,它是一个很有用的参考。

ModelSim具备强大的模拟仿真功能,在设计、编译、仿真、测试、调试开发过程中,有一整套工具供你使用,而且操作起来极其灵活,可以通过菜单、快捷键和命令行的方式进行工作。

ModelSim的窗口管理界面让用户使用起来很方面,它能很好的与操作系统环境协调工作。

ModelSim的一个很显著的特点就是它具备命令行的操作方式,类似于一个shell有很多操作指令供你使用,给人的感觉就像是工作在Unix环境下,这种命令行操作方式是基于Tcl/Tk 的,其功能相当强大,这需要在以后的实际应用中慢慢体会。

ModelSim的功能侧重于编译、仿真,不能指定编译的器件,不具有编程下载能力。

不象Synplify和MAX+PLUS II可以在编译前选择器件。

而且ModelSim 在时序仿真时无法编辑输入波形,不象MAX+PLUS II可以自行设置输入波形,仿真后自动产生输出波形,而是需要在源文件中就确定输入,如编写测试台程序来完成初始化、模块输入的工作,或者通过外部宏文件提供激励。

这样才可以看到仿真模块的时序波形图。

另外对于Synplify来说,也只具有编译能力,但是比MAX+PLUS II可编译的verilog的内容要多,所以常常可以现在Synplify下编译,生成编译文件再送到MAX+PLUS II中使用。

ModelSim还具有分析代码的能力,可以看出不同的代码段消耗资源的情况,从而可以对代码进行改善,以提高其效率。

第二章 ModelSim的主要结构ModelSim的主窗口(Main window)包括菜单栏、工具栏、工作区和命令行操作区。

Modelsim初级使用教程(转)

Modelsim初级使用教程(转)一、 Modelsim简介Modelsim仿真工具是Model公司开发的。

它支持Verilog、VHDL以及他们的混合仿真,它可以将整个程序分步执行,使设计者直接看到他的程序下一步要执行的语句,而且在程序执行的任何步骤任何时刻都可以查看任意变量的当前值,可以在Dataflow窗口查看某一单元或模块的输入输出的连续变化等,比quartus自带的仿真器功能强大的多,是目前业界最通用的仿真器之一。

对于初学者,modelsim自带的教程是一个很好的选择,在Help->SE PDF Documentation->Tutorial里面.它从简单到复杂、从低级到高级详细地讲述了modelsim的各项功能的使用,简单易懂。

但是它也有缺点,就是它里面所有事例的初期准备工作都已经放在example文件夹里,直接将它们添加到modelsim就可以用,它假设使用者对当前操作的前期准备工作都已经很熟悉,所以初学者往往不知道如何做当前操作的前期准备。

二、安装同许多其他软件一样,Modelsim SE 同样需要合法的License,通常我们用Kengen产生license.dat。

1 解压安装工具包开始安装,安装时选择Full product安装。

当出现Install Hardware Security Key Driver时选择否。

当出现Add Modelsim T o Path选择是。

出现Modelsim License Wizard时选择Close。

2 在C盘根目录新建一个文件夹flexlm,用Keygen产生一个License.dat,然后复制到该文件夹下。

若License通过,但是打开ModelSim仍出错,则将系统时间调到2008年之前,重新生成License,再将时间调回来即可。

3 修改系统的环境变量。

右键点击桌面我的电脑图标,属性->高级->环境变量->(系统变量)新建。

Modelsim使用指南

Modelsim使用指南1 前言作为一种简单易用,功能强大的逻辑仿真工具,Modelsim具有广泛的应用。

这里对ModelSim作一个入门性的简单介绍。

首先介绍ModelSim的代码仿真,然后介绍门级仿真和时序验证。

2 代码仿真在完成一个设计的代码编写工作之后,可以直接对代码进行仿真,检测源代码是否符合功能要求。

这时,仿真的对象为HDL代码,比较直观,速度比较快,可以进行与软件相类似的多种手段的调试(如单步执行等)。

在设计的最初阶段发现问题,可以节省大量的精力。

2.1 代码仿真需要的文件1.设计HDL源代码:可以使VHDL语言或Verilog语言。

2.测试激励代码:根据设计要求输入/输出的激励程序,由于不需要进行综合,书写具有很大的灵活性。

3.仿真模型/库:根据设计内调用的器件供应商提供的模块而定,如:FIFO(Altera 常用的FIFO有:lpm_fifo /lpm_fifo_dc等)、DPRAM等。

2.2 代码仿真步骤1.建立工程:在ModelSim中建立Project。

如图2.1所示,点击FileÖNewÖProject,得到Creata Project的弹出窗口,如图2.2所示。

在Project Name栏中填写你的项目名字,建议和你的顶层文件名字一致。

Project Location是你的工作目录,你可通过Brose按钮来选择或改变。

Ddfault Library Name可以采用工具默认的work。

图2.1图2.22.给工程加入文件:ModelSim会自动弹出Add Items to the project窗口,如图2.3所示。

选择Add Exsiting File后,根据相应提示将文件加到该Project中。

图2.33.编译:编译(包括源代码和库文件的编译)。

编译可点击ComlileÖComlile All 来完成。

4.装载文件:如图2.4,点击SimulateÖSimulate…后,如图2.5所示,选定顶层文件(激励文件),ADD加入,然后点击LOAD,装载。

modelsim教程

ModelSim教程简介ModelSim是一种常用的硬件描述语言仿真器,它广泛应用于数字电路设计、验证和测试。

本教程将介绍ModelSim的基本知识和使用方法,帮助读者快速上手ModelSim,并顺利完成数字电路仿真和验证工作。

目录1.安装ModelSim2.创建工程3.设计代码编写4.编译和仿真5.波形查看和分析6.仿真高级特性7.总结安装 ModelSim首先,您需要下载和安装 ModelSim。

您可以从 Mentor Graphics(ModelSim的开发商)的官方网站上找到适用于您的操作系统版本的安装程序。

下载完成后,按照安装向导的提示进行安装,并确保将安装目录添加到系统的环境变量中。

创建工程在开始使用 ModelSim之前,您需要创建一个工程,用于组织和管理您的设计代码。

以下是创建ModelSim工程的基本步骤:1.打开 ModelSim,并选择“File -> New -> Project”。

2.在弹出的对话框中,选择要保存工程的目录和工程名称,并点击“Next”。

3.在下一步中,您可以选择是否添加已有文件到工程中,或者选择直接创建新的设计文件。

完成后,点击“Next”。

4.在下一步中,您可以选择激活某些特性,如代码覆盖率、时序分析等。

完成后,点击“Next”。

5.最后,点击“Finish”来完成工程的创建。

设计代码编写在 ModelSim中,您可以使用HDL(硬件描述语言)编写您的设计代码。

常用的HDL语言包括VHDL和Verilog。

以下是一个简单的VHDL代码示例:-- Counter.vhdentity Counter isport (clk :in std_logic;rst :in std_logic;count :out unsigned(7downto0));end entity Counter;architecture Behavioral of Counter issignal internal_count :unsigned(7downto0); beginprocess(clk, rst)beginif rst ='1'theninternal_count <= (others=>'0');elsif rising_edge(clk) thenif internal_count =8theninternal_count <= (others=>'0');elseinternal_count <= internal_count +1;end if;end if;end process;count <= internal_count;end architecture Behavioral;编译和仿真编译和仿真是在ModelSim中运行设计代码并生成波形的关键步骤。

modelsim详细图文使用教程(菜鸟基础教程)

版权所有,翻录必究!

天津大学

电子信息工程学院

戴鹏

总结:

建立工程编写主程序和测试程序编译仿真观察波形。 写了很多,但是应该讲得很详细了吧,希望对大家的学习有所帮 助。

版权所有,翻录必究!

写完代码后,不能马上就编译,要先保存,否则,编译无效。我们会看到“保存”的 图标是两色的,而且 half_clk.v 后的“?”还存在,这说明你没有保存文件,

这时,只需要点击保存,就会发现“保存”的图标变成了阴影,这样编译才有效,而 就是这么不起眼但至关重要的一步“保存” ,往往被很多初学者忽视,最终怀疑程序和

出现下框, 写入测试程序的名字 half_clk_tb, tb 是 testbench 的意思, 注意选 verilog, Ok。

这样就把 half_clk_tb.v 加载到了 project 中,双击 half_clk_tb.v 在右边的程序编辑区 中编写代码: `timescale 1ns/1ns

天津大学

电子信息工程学院

戴鹏

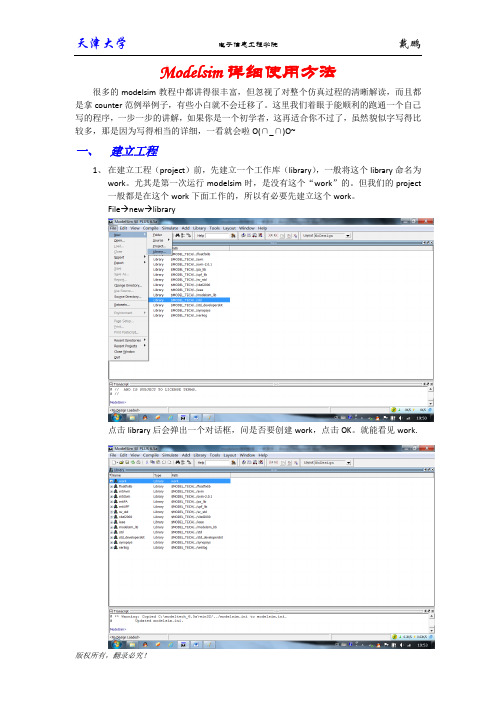

Modelsim 详细使用方法

很多的 modelsim 教程中都讲得很丰富,但忽视了对整个仿真过程的清晰解读,而且都 是拿 counter 范例举例子,有些小白就不会迁移了。这里我们着眼于能顺利的跑通一个自己 写的程序,一步一步的讲解,如果你是一个初学者,这再适合你不过了,虽然貌似字写得比 较多,那是因为写得相当的详细,一看就会啦 O(∩_∩)O~

版权所有,翻录必究!

天津大学

软件问题。其实只是没保存。

电子信息工程学院

戴鹏

2、写测试程序(testbench):每一个主程序(实现我们需要的某种功能的程序) ,都要 配套的编写一个测试程序,为什么?这里不打算细说,testbench 是给主程序提供时钟和 信号激励,使其正常工作,产生波形图,具体请参看 verilog 教课书。 在 half_clk.v 下方的空白区域内右键,选择 Add to Project New File

modelsim详细使用教程(一看就会)

Modelsim详细使用方法很多的modelsim教程中都讲得很丰富,但忽视了对整个仿真过程的清晰解读,而且都是拿counter范例举例子,有些小白就不会迁移了。

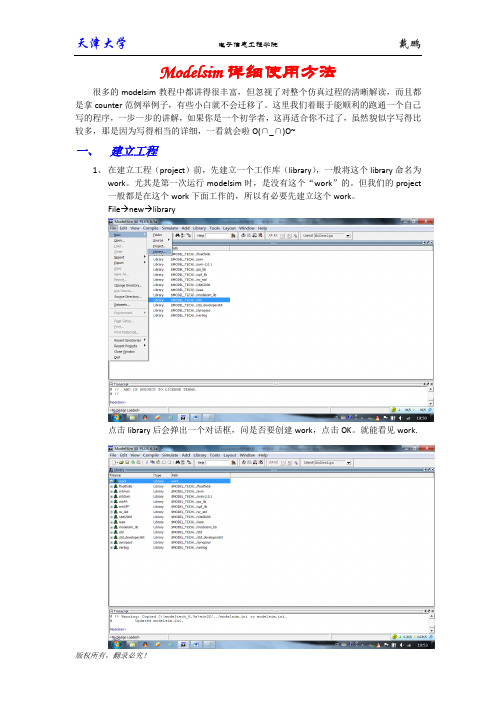

这里我们着眼于能顺利的跑通一个自己写的程序,一步一步的讲解,如果你是一个初学者,这再适合你不过了,虽然貌似字写得比较多,那是因为写得相当的详细,一看就会啦O(∩_∩)O~一、建立工程1、在建立工程(project)前,先建立一个工作库(library),一般将这个library命名为work。

尤其是第一次运行modelsim时,是没有这个“work”的。

但我们的project 一般都是在这个work下面工作的,所以有必要先建立这个work。

File→new→library点击library后会弹出一个对话框,问是否要创建work,点击OK。

就能看见work.2、如果在library中有work,就不必执行上一步骤了,直接新建工程。

File→new→project会弹出在Project Name中写入工程的名字,这里我们写一个二分频器,所以命名half_clk,然后点击OK。

会出现由于我们是要仿一个自己写的程序,所以这里我们选择Create New File。

在File Name中写入文件名(这里的file name和刚刚建立的project name可以一致也可以不一致)。

注意Add file as type 要选择成Verilog(默认的是VHDL),然后OK。

发现屏幕中间的那个对话框没有自己消失,我们需要手动关闭它,点close。

并且在project中出现了一个half_clk.V的文件,这个就是我们刚刚新建的那个file。

这样工程就建立完毕了。

二、写代码:1、写主程序:双击half_clk.v文件会出现程序编辑区,在这个区间里写好自己的程序,这里我们写一个简单的二分频的代码:module half_clk_dai(clk_in,rst,clk_out);input clk_in;input rst;output clk_out;reg clk_out;always @(posedge clk_in or negedge rst)beginif(!rst)clk_out<=0;elseclk_out<=~clk_out;endendmodule写完代码后,不能马上就编译,要先保存,否则,编译无效。

modelsim使用流程

modelsim使用流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor. I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!ModelSim 使用流程。

1. 项目设置。

启动 ModelSim 软件并新建一个项目。

modelsim使用入门(VHDL_

modelsim使用实例(VHDL)标签: modelsim仿真testbench FPGA看了几天的modelsim以及如何在quartusII中调用,浏览了N个网页,尝试了N次,......终于初步完成。

下面是入门部分介绍。

modelsim是专业的仿真软件,仿真运行速度比同类的其他仿真软件都要快很多。

Quartus 自己都不再做仿真器了,普遍使用modelsim,自有其缘由。

这里用的是modelsim-altera(6.6d)版本,与quartus II 11.0搭配。

据说Altera公司推出的Quartus软件不同版本对应不同的modelsim,相互之间不兼容。

某些功能齐全的modelsim版本可以进行两种语言的混合编程, modelsim-altera只能支持一种语言进行编程(VHDL或者Verilog选其一)。

1、新建工程打开modelsim-->file-->new-->project 新建工程,输入工程名,文件存放路径后(不可直接放在某盘下,必须放入文件夹中),进入下一步。

在主体窗口下方出现project标签。

见下图。

2、新建文件--create new file:输入名称div10,选择语言VHDL --关闭对话框新的工程文件将会在工程窗口出现。

3、写入源程序(VHDL)双击div10.vhd,打开文本编辑器。

实例代码如下(一个十分频的VHDL源代码):library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity div10 is --实体要与工程名相同 port(clk :in std_logic;div :out std_logic );end div10;architecture behav of div10 issignal temp :std_logic:='0';signal count :std_logic_vector(2 downto 0):="000";beginprocess(clk)beginif(clk'event and clk='1') thenif(count="100") thencount<=(others=>'0');temp<=not temp;elsecount<=count+1;end if;end if;end process;div<=temp;end behav;4、写testbenchmodelsim单独使用时需要自己写testbench,输入时钟,给测试电路加以激励源以驱动电路。

ModelSim高级使用进阶_1_do文件和批处理文件使用_Camp

------第六步

run –all

运行全部

------第七步

接下来就是仿真打印的消息,直到结束,打印运行到哪一行为止.如果运行到 finish 则关闭 modelsim,所以我们少

用 finish 系统函数。(中间打印太多,我用” (…………)”来做省略了)

看了这么多,我们该如何编写我们的.do 文件呢?或许有人已经想出点眉目了,

vlog -reportprogress 300 -work work D:/User/mywork/i2c/i2c_driver.v

# Model Technology ModelSim SE vlog 10.0d Compiler 2011.10 Oct 30 2011

# -- Compiling module i2c_driver

# Refreshing D:\User\mywork\i2c\work.Signal1

# Loading work.Signal1

# Refreshing D:\User\mywork\i2c\work.i2c_driver

# Loading work.i2c_driver

# Refreshing D:\User\mywork\i2c\work.at24cxx

的确如此但我这里所保存的波形文件它并不是保存波形的内容而是保存它显示方式比如下面图我们此次仿真出来的结果如下图图中我修改的地方有

ModelSim 高级使用进阶_1

致给奋斗与 FPGA 技术领域的朋友们 By Camp

_do 文件和批处理文件使用

如果你还没有学会使用 modelsim 进行仿真,请把该文档关闭。回去学习基本的使用 如果你已经学会使用 modelsim 进行仿真,而且自己非常的娴熟 modelsim,那恭喜你,你或许可以把该文档 关闭,继续你的学习;或者可以浏览一下这个文档,然后给出你的建议。 无论你是大虾还是小虾,我都会期待你的指正和批评. 都可以发送 E_MAIL 给我 先给个术语:GUI---- Graphical User Interface,简称 GUI. 图形用户界面.

ModelSim 指南说明书

ModelSim Guide CPR E 281: Digital LogicIntroductionModelSim is a software for simulating hardware related tasks such as those normally performed on the Altera FPGA Board. Due to the coronavirus pandemic we are not allowed to use these boards this semester, because they cannot be easily disinfected after each use. Therefore, we will use ModelSim to simulate our circuit designs.Starting ModelSimVDI provides a virtual Windows 10 or Linux desktop with the same software as our physical computer labs. VDI works both on-campus and off-campus and can be used from almost any computing device (https:///vdi/).How to Connect to VDIIf you are off campus you no longer need to connect to the VPN before using VDI (unless you want to; instructions for VPN are posted here: https:///).1.Download the client for Windows or Mac: https:///2.Install the client with all the defaults.unch the VMware Horizon Client4.Click the New Server icon on the Horizon Client Home window (the plus buttonon the top left), enter https:// for the name of the Connection Server, and click Connect.5.Enter your IASTATE NetID in the form of*****************and password6.Double click on the Windows Lab VDI icon.You should now be able to access Quartus Prime remotely, as well as your U: drive. When you are finished using the VDI session, make sure anything that you want to keep saved on your U: drive. Otherwise, it will be deleted after you logout. You can exit the VDI session via several methods:1.Start Menu > Log off2.Start Menu > Shut Down3.Quit the VMware View ClientAll sessions are automatically destroyed after 2 hours of inactivity or logoff/shutdown.To open ModelSim, simply search for ModelSim on the start menu as shown in Figure 1.Figure 1: Starting ModelSIM from the start menu.Creating a New ProjectAfter starting ModelSim, click on File > New > Project and select a directory for the project as shown in Figure 2 and Figure 3. This directory will contain all files for the new project.Figure 2: Selecting a directory for a new project.Figure 3: Selecting a directory for a new project.After completing these steps, ModelSim creates necessary project and preset files to later ease the process of opening projects and view previous simulation logs.Adding Files to ModelSimThe next step is to add files to the project. There are two options, either to createa new file within ModelSim’s built-in text editor or add an existing file from the directory. The choice is made with the pop-up window shown in Figure 4, which should show up automatically after creating a new project. The files that can beadded here are .v files, i.e., Verliog HDL files.Figure 4: Pop-up window to select file additions.What Are Verilog HDL (.v) Files?ModelSim can simulate circuits described using a Hardware Description Language (HDL). In this class we will use a language called Verilog, or sometimes Verilog HDL. There are two ways to create a Verilog (.v) file:1.Describe the functionality of the circuit directly in Verilog using a text editor.2.Create a block diagram file (.bdf) for the circuit using a software packagecalled Quartus. Then, convert the .bdf file to a .v file so that it can besimulated with ModelSim.Using Quartus to Convert a Block Diagram File to a Verilog HDL FileUsing the start menu, search for Quartus and start the application as shown in Figure 5.Figure 5: Starting Quartus from the start menu.Load the desired block diagram file (*.bdf) that you want to convert to a Verilog (*.v)file. Then, go to File > Create/Update > Create HDL Design from Current File as shown in Figure 6. A pop-up window will prompt you for the format of the output file. Make sure to select “Verolog HDL” as shown in Figure 7. Click OK and let Quartus dothe remaining work. The resulting *.v file is now in the same directory and is ready tobe opened by ModelSim.Note: After converting the file it should be added to a project in ModelSim so that it can be simulated (see the previous page).Figure 6: Converting a .bdf file to a .v file.Figure 7: Prompt for choosing the destination of the converted .v file.Compiling FilesTo compile a file, right click on the file name within the project directory and then Compile > Compile All (see Figure 8). If the compilation is successful, a green tickmark will appear in the status column for this file.Figure 8: Compiling files in ModelSim.Starting a SimulationBefore you proceed to this step, make sure that all files in your project are compiled successfully. This is necessary because there could be dependencies between the files.To run the simulation click Simulate > Start Simulation as shown in Figure 9. A pop-up window will prompt you to select the file that you want to simulate. In the “Design” tab, look for an item called “work” and then click the “+” button that is immediately to its left (see Figure 10). This will show more files. Click on the file that you want to test and then click OK.Figure 9: Starting a simulation in ModelSim.Figure 10: Selecting the file to be simulated from the work directory.Figure 11: Starting a simulation and invoking the wave form diagram.A simulation window should pop-up as shown in Figure 11. Double click the file name to add all input/signal/output variables to be analyzed. Then click on a variable name that pops up on the right and press “CTRL-W” to add waveforms. No actual wave forms should show up since the variables have no initial value yet. This is shown in Figure 12.Figure 12: Adding variables and incorporating them into the wave form.Edge-Case TestingNow, it’s time to finally test the circuit! For this example, we will hard code (or force) the values of the input variables for this circuit. This next step is important! Click on the desired input variable and not on an output variable. Then, right click and choose Force as shown in Figure 13. This allows you to force a value for that input indefinitely, orat least until it is forced to another value manually.Figure 13: Forcing values for an input.Another way to test is to create a testbench (if you’re interested look up some YouTubetutorials on this subject), but that is out of the scope of this class.After completing all of these steps, it is time to see some results. There is a command prompt at the bottom that allows for typing in commands in ModelSim syntax.Using these commands, we can quickly tell ModelSim to complete tasks, instead of looking for them in the dropdown menus. Please ensure that all input variables have a forced value before doing this step. On the command prompt type “run 100”, which lets the wave form simulate edge cases for 100 ns. The output variable now shows an expected output. In this case, the output of 0 AND 0 is 0! This is shown in Figure 14.Figure 14: Wave form showing 0 AND 0 for which the output is 0.QuestionsIf you have any questions or comments, please email your lab TA for further assistance.。

ModelSim入门指导

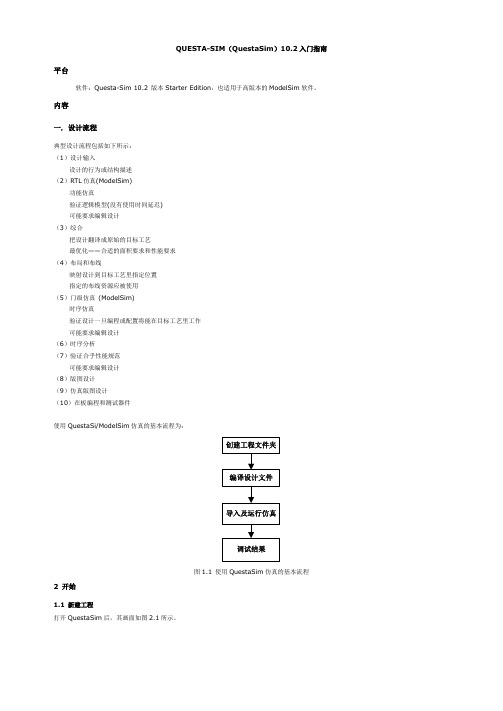

QUESTA-SIM(QuestaSim)10.2入门指南平台软件:Questa-Sim 10.2 版本Starter Edition,也适用于高版本的ModelSim软件。

内容一. 设计流程典型设计流程包括如下所示:(1)设计输入设计的行为或结构描述(2)RTL仿真(ModelSim)功能仿真验证逻辑模型(没有使用时间延迟)可能要求编辑设计(3)综合把设计翻译成原始的目标工艺最优化——合适的面积要求和性能要求(4)布局和布线映射设计到目标工艺里指定位置指定的布线资源应被使用(5)门级仿真(ModelSim)时序仿真验证设计一旦编程或配置将能在目标工艺里工作可能要求编辑设计(6)时序分析(7)验证合乎性能规范可能要求编辑设计(8)版图设计(9)仿真版图设计(10)在板编程和测试器件使用QuestaSi/ModelSim仿真的基本流程为:图1.1 使用QuestaSim仿真的基本流程2 开始1.1 新建工程打开QuestaSim后,其画面如图2.1所示。

图2.1 QuestaSim画面1. 创建工作目录E:/QuestaSim/, 在其路径下创建子文件夹/ip、/prj、/rtl、/tb, prj是QuestaSim工程主文件夹,ip是仿真模型目录,rtl 是代码目录,tb是testbench目录。

2. 选择File>New>Preject创建一个新工程。

打开的Create Project对话框窗口,可以指定工程的名称、路径和缺省库名称。

一般情况下,设定Default Library Name为work。

指定的名称用于创建一个位于工程文件夹内的工作库子文件夹。

该对话框如图2.2所示,此外还允许通过修改初始化文件QuestaSim.ini文件来映射库设置。

图2.2 创建工程的对话框2. 设置Project Name为BG0806,Project Location为E:/QuestaSim/prj, 勾选Copy Library Mappings ,点击OK。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Modelsim简易使用流程

1.进入Modelsim图形界面

PC机:点击Modelsim图标,运行程序。

工作站:在terminal窗口下,键入vsim &

编辑文件,键入dtpad [filename] &

2.创建一个新的工作库

点击library Create a New Library …

在Create控件框中,选中a new library and a logical mapping to it;

在library:后键入库名(student)并点击OK。

3.编译VHDL/Verilog语言文件

点击主窗口中工具栏中的compile…。

A.选择编译文件

在library后的选择控件中选择工作库(student),选中要编译的VHDL/Verilog文件。

B.选择VHDL-87/93标准

点击Default Options…按钮,在弹出的compiler options窗口中选中Use 1993 Language Syntax,即使用VHDL-93标准编译文件。

C.编译文件

在Compile HDL Source Files窗口中点击compile按钮。

编译的结果显示在主窗口中,warning、error信息分别以蓝色和红色字符显示。

D.修改VHDL/Verilog文件

在Compile HDL Source Files窗口中点击Edit Source按钮,在弹出的窗口中修改文件。

注:如果该文件在仿真条件下被打开,只读属性被设置,在菜单Edit中点击Read Only,去除只读属性后,进行修改。

4.仿真

A.载入设计

点击主窗口的Load Design按钮。

选择要仿真的实体名、结构体名或配置名,点击Load按钮。

在Modelsim5.5a中,可以直接双击主窗口library标签中对应的实体名、结构体名或配置名。

B.调试

点击主窗口的View→Structure;

在弹出的Structure窗口中选择要观察的实体名。

点击主窗口的View→Signals;

在弹出的Signals窗口中点击View→Wave→Signals in Region,观察该实体中所有信号。

在主窗口中的上下控件中设置缺省运行的时间间隔。

在wave窗口中点击Run按钮,观察波形。

在波形不正确的情况下,需要修改VHDL/Verilog文件。

修改后的文件必须重新编译,而后点击主窗口中的Restart按钮,在Modelsim5.5a中可以在wave窗口中点击该按钮。

点击continue Run按钮,则波形仿真至上次仿真时间。

5.补充

A.改变vector的显示进制

当Signal是一个矢量信号时,默认的显示进制是二进制,在wave窗口中选择要改变的信号(可以多选),点右键。

在弹出菜单中选择Radix,在下拉菜单中选择需要的显示进制。

B.设置断点

在Modelsim的文件编辑窗口中,绿色显示的行号数处可以设置断点,在行号处点击即可设置断点。

C.改变工作目录

选择主窗口中files→Change Direction…,指定新的工作目录。

在新的工作目录中需要重新创建工作库。