CY7C1061BV33-10ZC中文资料

中秀3000资料

CY7C1012AV33-10BGC中文资料

512K x 24 Static RAMCY7C1012AV33Features•High speed—t AA = 8, 10, 12 ns •Low active power —1080 mW (max.)•Operating voltages of 3.3 ± 0.3V •2.0V data retention•Automatic power-down when deselected •TTL-compatible inputs and outputs•Easy memory expansion with CE 0, CE 1 and CE 2 featuresFunctional DescriptionThe CY7C1012AV33 is a high-performance CMOS static RAM organized as 512K words by 24 bits. Each data byte is separately controlled by the individual chip selects (CE 0, CE 1,CE 2). CE 0 controls the data on the I/O 0–I/O 7, while CE 1controls the data on I/O 8–I/O 15, and CE 2 controls the data on the data pins I/O 16–I/O 23. This device has an automatic power-down feature that significantly reduces power consumption when deselected.Writing the data bytes into the SRAM is accomplished when the chip select controlling that byte is LOW and the write enable input (WE) input is LOW. Data on the respective input/output (I/O) pins is then written into the location specified on the address pins (A 0–A 18). Asserting all of the chip selects LOW and write enable LOW will write all 24 bits of data into the SRAM. Output enable (OE) is ignored while in WRITE mode.Data bytes can also be individually read from the device.Reading a byte is accomplished when the chip select controlling that byte is LOW and write enable (WE) HIGH while output enable (OE) remains LOW. Under these conditions, the contents of the memory location specified on the address pins will appear on the specified data input/output (I/O) pins.Asserting all the chip selects LOW will read all 24 bits of data from the SRAM.The 24 I/O pins (I/O 0–I/O 23) are placed in a high-impedance state when all the chip selects are HIGH or when the output enable (OE) is HIGH during a READ mode. For further details,refer to the truth table of this data sheet.The CY7C1012AV33 is available in a standard 119-ball BGA.Selection Guide–8–10–12Unit Maximum Access Time81012ns Maximum Operating Current Commercial 300275260mA Industrial300275260Maximum CMOS Standby CurrentCommercial/Industrial505050mAFunctional Block Diagram1516A 1A 2A 3A 4A 5A 6A 7A 8COLUMN DECODERR O W D E C O D E RS E N S E A M P SINPUT BUFFER512K x 24ARRAY A 0A 12A 14A 13A A A 17A 18A 10A 114096 x 4096I/O 0–I/O 7OEI/O 8–I/O 15CE 0, CE 1, CE 2WE A 9I/O 16–I/O 23CONTROL LOGICPin Configurations119 BGATop View1234567A NC A A A A A NCB NC A A CE0A A NCC I/O12NC CE1NC CE2NC I/O0D I/O13V DD V SS V SS V SS V DD I/O1E I/O14V SS V DD V SS V DD V SS I/O2F I/O15V DD V SS V SS V SS V DD I/O3G I/O16V SS V DD V SS V DD V SS I/O4H I/O17V DD V SS V SS V SS V DD I/O5J NC V SS V DD V SS V DD V SS DNUK I/O18V DD V SS V SS V SS V DD I/O6L I/O19V SS V DD V SS V DD V SS I/O7M I/O20V DD V SS V SS V SS V DD I/O8N I/O21V SS V DD V SS V DD V SS I/O9P I/O22V DD V SS V SS V SS V DD I/O10R I/O23A NC NC NC A I/O11T NC A A WE A A NCU NC A A OE A A NCMaximum Ratings(Above which the useful life may be impaired. For user guide-lines, not tested.)Storage Temperature .................................–65°C to +150°C Ambient Temperature withPower Applied.............................................–55°C to +125°C Supply Voltage on V CC to Relative GND[1]....–0.5V to +4.6V DC Voltage Applied to Outputsin High-Z State[1]....................................–0.5V to V CC + 0.5V DC Input Voltage[1]................................–0.5V to V CC + 0.5V Current into Outputs (LOW).........................................20 mAOperating RangeRangeAmbientTemperature V CC Commercial0°C to +70°C 3.3V ± 0.3V Industrial–40°C to +85°CDC Electrical Characteristics Over the Operating RangeParameter Description Test Conditions[2]–8–10–12Unit Min.Max.Min.Max.Min.Max.V OH Output HIGH Voltage V CC = Min.,I OH = –4.0 mA2.4 2.4 2.4VV OL Output LOW Voltage V CC = Min.,I OL = 8.0 mA0.40.40.4VV IH Input HIGH Voltage 2.0V CC+ 0.32.0V CC+ 0.32.0V CC+ 0.3VV IL[1]Input LOW Voltage–0.30.8–0.30.8–0.30.8V I IX Input Load Current GND < V I < V CC–1+1–1+1–1+1µA I OZ Output Leakage Current GND < V OUT < V CC, Output Disabled–1+1–1+1–1+1µAI CC V CC OperatingSupply Current V CC = Max.,f = f MAX = 1/t RCCommercial300275260mAIndustrial300275260mAI SB1Automatic CEPower-down Current—TTL Inputs Max. V CC, CE > V IHV IN > V IH orV IN < V IL, f = f MAX100100100mAI SB2Automatic CEPower-down Current—CMOS Inputs Max. V CC,CE > V CC– 0.3V,V IN > V CC– 0.3V,or V IN < 0.3V, f = 0Commercial/Industrial505050mACapacitance[3]Parameter Description Test Conditions Max.Unit C IN Input Capacitance T A = 25°C, f = 1 MHz, V CC = 3.3V8pF C OUT I/O Capacitance10pF Notes:1.V IL (min.) = –2.0V for pulse durations of less than 20 ns.2.0123.Tested initially and after any design or process changes that may affect these parameters.AC Test Loads and Waveforms [4]90%10%3.3V GND 90%10%ALL INPUT PULSES3.3V OUTPUT5 pFINCLUDING JIG AND SCOPE(a)(b)R1 317ΩR2351ΩRise time > 1 V/nsFall time:> 1 V/ns(c)OUTPUT50ΩZ 0= 50ΩV TH = 1.5V30 pF** Capacitive Load consists of all compo-nents of the test environment.AC Switching Characteristics Over the Operating Range [5]Parameter Description–8–10–12UnitMin.Max.Min.Max.Min.Max.Read Cycle t power [6]V CC (typical) to the first access 111ms t RC Read Cycle Time 81012ns t AA Address to Data Valid81012ns t OHA Data Hold from Address Change 333ns t ACE CE 1, CE 2, and CE 3 LOW to Data Valid 81012ns t DOE OE LOW to Data Valid 556ns t LZOE OE LOW to Low-Z [7]111ns t HZOE OE HIGH to High-Z [7]556ns t LZCE CE 1, CE 2, and CE 3 LOW to Low-Z [7]333ns t HZCE CE 1, CE 2, or CE 3 HIGH to High-Z [7]556ns t PU CE 1, CE 2, and CE 3 LOW to Power-up [8]0ns t PD CE 1, CE 2, or CE 3 HIGH to Power-down [8]81012ns t DBE Byte Enable to Data Valid 556ns t LZBE Byte Enable to Low-Z [7]111ns t HZBEByte Disable to High-Z [7]556nsWrite Cycle [9, 10]t WC Write Cycle Time81012ns t SCECE 1, CE 2, and CE 3 LOW to Write End678nsNotes:4.Valid SRAM operation does not occur until the power supplies have reached the minimum operating V DD (3.0V). As soon as 1 ms (T power ) after reachingthe minimum operating V DD , normal SRAM operation can begin including reduction in V DD to the data retention (V CCDR , 2.0V) voltage.5.Test conditions assume signal transition time of 3 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V, and output loading of the specifiedI OL /I OH and transmission line loads. Test conditions for the read cycle use output loading as shown in part a) of the AC test loads, unless specified otherwise.6.This part has a voltage regulator which steps down the voltage from 3V to 2V internally. t power time has to be provided initially before a read/write operationis started.7.t HZOE , t HZCE , t HZWE , t HZBE , and t LZOE , t LZCE , t LZWE , t LZBE are specified with a load capacitance of 5 pF as in part (b) of AC Test Loads. Transition is measured±200 mV from steady-state voltage.8.These parameters are guaranteed by design and are not tested.9.The internal write time of the memory is defined by the overlap of CE 1, CE 2, and CE 3 LOW and WE LOW. The chip enables must be active and WE mustbe LOW to initiate a write, and the transition of any of these signals can terminate the write. The input data set-up and hold timing should be referenced to the leading edge of the signal that terminates the write.10.The minimum write cycle time for Write Cycle No. 3 (WE controlled, OE LOW) is the sum of t HZWE and t SD .t AW Address Set-up to Write End 678ns t HA Address Hold from Write End 000ns t SA Address Set-up to Write Start 000ns t PWE WE PulseWidth 678ns t SD Data Set-up to Write End 5 5.56ns t HD Data Hold from Write End 000ns t LZWE WE HIGH to Low-Z [7]333ns t HZWE WE LOW to High-Z [7]556ns t BWByte Enable to End of Write678nsAC Switching Characteristics Over the Operating Range (continued)[5]Parameter Description–8–10–12Unit Min.Max.Min.Max.Min.Max.Switching WaveformsRead Cycle No. 1[11, 12]Read Cycle No. 2 (OE Controlled)[2, 12, 13]Notes:11.Device is continuously selected. OE, CE = V IL .12.WE is HIGH for read cycle.13.PREVIOUS DATA VALIDDATA VALIDt RCt AAt OHAADDRESSDATA OUT50%50%DATA VALIDt RCt ACEt DOEt LZOEt LZCE t PUHIGH IMPEDANCEt HZOEt HZCEt PDHIGH OECEI CC I SBIMPEDANCEADDRESSDATA OUT V CC SUPPLY CURRENTWrite Cycle No. 1 (CE Controlled)[2, 14, 15]Write Cycle No. 2 (WE Controlled, OE HIGH During Write)[14, 15]Write Cycle No. 3 (WE Controlled, OE LOW)[2, 15]Notes:14.Data I/O is high impedance if OE = V IH .15.16.During this period the I/Os are in the output state and input signals should not be applied.Switching Waveforms (continued)t WCDATA VALIDt AWt SAt PWEt HAt HDt SDt SCEt SCECEADDRESSWEDATA I/Ot HDt SDt PWEt SAt HAt AWt SCEt WCt HZOEDATA IN VALIDCEADDRESSWEDATA I/OOENOTE 16DATA VALIDt HDt SDt LZWEt PWEt SAt HAt AWt SCEt WCt HZWECEADDRESSWEDATA I/ONOTE 16Truth TableCE0CE1CE2OE WE I/O0–I/O23Mode PowerH H H X X High-Z Power-down Standby (I SB)L H H L H I/O0–I/O7 Data Out Read Active (I CC)H L H L H I/O8–I/O15 Data Out Read Active (I CC)H H L L H I/O16–I/O23 Data Out Read Active (I CC)L L L L H Full Data Out Read Active (I CC) L H H X L I/O0–I/O7 Data In Write Active (I CC)H L H X L I/O8–I/O15 Data In Write Active (I CC)H H L X L I/O16–I/O23 Data In Write Active (I CC)L L L X L Full Data In Write Active (I CC) L L L H H High-Z Selected, Outputs Disabled Active (I CC) Ordering InformationSpeed(ns)Ordering Code PackageName Package TypeOperatingRange8CY7C1012AV33-8BGC BG11914 × 22 mm 119-ball BGA Commercial CY7C1012AV33-8BGI Industrial 10CY7C1012AV33-10BGC Commercial CY7C1012AV33-10BGI Industrial 12CY7C1012AV33-12BGC Commercial CY7C1012AV33-12BGI IndustrialCY7C1012AV33 Package Diagram119-ball PBGA (14 x 22 x 2.4 mm) BG119CY7C1012AV33 Document History PageDocument Title: CY7C1012AV33 512K x 24 Static RAMDocument Number: 38-05254REV.ECN NO.IssueDateOrig. ofChange Description of Change**11371103/11/02NSL New Data Sheet*A11705707/31/02DFP Removed 15-ns bin.*B11798809/03/02DFP Added 8-ns bin.*C11899209/19/02DFP Change Cin - input capacitance -from 6 pF to 8 pF.Change Cout -output capacitance from 8 pF to 10 pF.*D1*******/15/02DFP Final data sheet. Added note 4 to “AC Test Loads and Waveforms.”。

CY7C1051DV33芯片手册

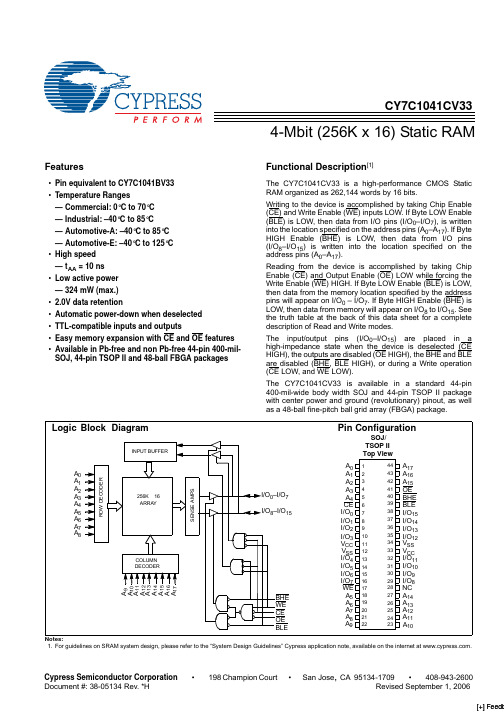

PRELIMINARY 8-Mbit (512K x 16) Static RAMCY7C1051DV33Features•High speed —t AA = 10 ns •Low active power—I CC = 110 mA @ 10 ns •Low CMOS standby power —I SB2 = 20 mA •2.0V data retention•Automatic power-down when deselected •TTL-compatible inputs and outputs•Easy memory expansion with CE and OE features•Available in lead-free 48-ball FBGA and 44-pin TSOP II packagesFunctional Description [1]The CY7C1051DV33 is a high-performance CMOS Static RAM organized as 512K words by 16 bits.Write to the device by taking Chip Enable (CE) and Write Enable (WE) inputs LOW. If Byte LOW Enable (BLE) is LOW,then data from IO pins (IO 0–IO 7), is written into the location specified on the address pins (A 0–A 18). If Byte HIGH Enable (BHE) is LOW, then data from IO pins (IO 8–IO 15) is written into the location specified on the address pins (A 0–A 18).Read from the device by taking Chip Enable (CE) and Output Enable (OE) LOW while forcing the Write Enable (WE) HIGH.If Byte LOW Enable (BLE) is LOW, then data from the memory location specified by the address pins will appear on IO 0–IO 7.If Byte HIGH Enable (BHE) is LOW, then data from memory will appear on IO 8 to IO 15. See the “Truth Table” on page 8 for a complete description of Read and Write modes.The input/output pins (IO 0–IO 15) are placed in a high-impedance state when the device is deselected (CE HIGH), the outputs are disabled (OE HIGH), the BHE and BLE are disabled (BHE, BLE HIGH), or a Write operation (CE LOW,and WE LOW) is in progress.The CY7C1051DV33 is available in a 44-pin TSOP II package with center power and ground (revolutionary) pinout, as well as a 48-ball fine-pitch ball grid array (FBGA) package.Note1.For guidelines on SRAM system design, please refer to the “System Design Guidelines” Cypress application note, available on the internet at .1415Logic Block DiagramA 1A 2A 3A 4A 5A 6A 7A 8COLUMN DECODERR O W D E C O D E RS E N S E A M P SINPUT BUFFER512K × 16ARRAYA 0A 11A 13A 12A A A 16A 17A 18A 9A 10IO 0–IO 7OE IO 8–IO 15CE WE BLEBHEPRELIMINARY CY7C1051DV33Selection Guide–10Unit Maximum Access Time 10ns Maximum Operating Current 110mA Maximum CMOS Standby Current20mAPin Configurations [2]48-ball Mini FBGAWE V CC A 11A 10NC A 6A 0A 3CE IO 10IO 8IO 9A 4A 5IO 11IO 13IO 12IO 14IO 15V SS A 9A 8OE V SS A 7IO 0BHE NC A 17A 2A 1BLE V CC IO 2IO 1IO 3IO 4IO 5IO 6IO 7A 15A 14A 13A 12NC A 18NC326541D E B A C F G HA 16(Top View)TSOP IIWE 1234567891011143132363534333740393812134144434216152930V CC A 5A 6A 7A 8A 0A 1OE V SS A 17IO 15A 2CE IO 2IO 0IO 1BHE A 3A 418172019IO 32728252622212324V SS IO 6IO 4IO 5IO 7A 16A 15BLE V CC IO 14IO 13IO 12IO 11IO 10IO 9IO 8A 14A 13A 12A 11A 9A 10A 18(Top View)Note2.NC pins are not connected on the diePRELIMINARY CY7C1051DV33Maximum Ratings(Exceeding the maximum ratings may impair the useful life of the device. These are for user guidelines, they are not tested.)Storage Temperature .................................–65°C to +150°C Ambient Temperature withPower Applied.............................................–55°C to +125°C Supply Voltage on V CC to Relative GND [3]....–0.5V to +4.6V DC Voltage Applied to Outputsin High-Z State [3]....................................–0.3V to V CC + 0.3V DC Input Voltage [3].................................–0.3V to V CC + 0.3VCurrent into Outputs (LOW).........................................20 mA Static Discharge Voltage............................................>2001V (per MIL-STD-883, Method 3015)Latch-up Current......................................................>200 mAOperating RangeRange Ambient Temperature V CC Industrial–40°C to +85°C3.3V ± 0.3VDC Electrical Characteristics Over the Operating RangeParameter DescriptionTest Conditions–10Unit Min MaxV OH Output HIGH Voltage V CC = Min, I OH = –4.0 mA 2.4V V OL Output LOW Voltage V CC = Min, I OL = 8.0 mA0.4V V IH Input HIGH Voltage 2.0V CC + 0.3V V IL [3]Input LOW Voltage –0.30.8V I IX Input Leakage Current GND < V I < V CC–1+1μA I OZ Output Leakage Current GND < V OUT < V CC , Output Disabled –1+1μA I CCV CC Operating Supply CurrentV CC = Max, f = f MAX = 1/t RC100 MHz 110mA83 MHz 100 66 MHz 9040 MHz80I SB1Automatic CE Power Down Current —TTL Inputs Max V CC , CE > V IH V IN > V IH or V IN < V IL , f = f MAX 40mA I SB2Automatic CE Power Down Current —CMOS Inputs Max V CC , CE > V CC – 0.3V,V IN > V CC – 0.3V or V IN < 0.3V, f = 020mACapacitance [4]Parameter DescriptionTest ConditionsMax.Unit C IN Input Capacitance T A = 25°C, f = 1 MHz, V CC = 3.3V12pF C OUTIO Capacitance12pFNotes3.V IL (min) = –2.0V and V IH (max) = V CC + 2.0V for pulse durations of less than 20 ns.4.Tested initially and after any design or process changes that may affect these parametersThermal Resistance [4]ParameterDescription Test ConditionsFBGA PackageTSOP II PackageUnit ΘJA Thermal Resistance (Junction to Ambient)Still Air, soldered on a 3 × 4.5 inch, four-layer printed circuit board28.3151.43°C/W ΘJCThermal Resistance (Junction to Case)11.415.8°C/WPRELIMINARYCY7C1051DV33AC Test Loads and Waveforms [5]AC Switching Characteristics [6] Over the Operating RangeParameterDescription–10UnitMinMaxRead Cycle t power [7]V CC (typical) to the first access 100μs t RC Read Cycle Time 10ns t AA Address to Data Valid10ns t OHA Data Hold from Address Change 3ns t ACE CE LOW to Data Valid 10ns t DOE OE LOW to Data Valid 5ns t LZOE OE LOW to Low-Z 0ns t HZOE OE HIGH to High-Z [8, 9]5ns t LZCE CE LOW to Low-Z [9]3ns t HZCE CE HIGH to High-Z [8, 9]5ns t PU CE LOW to Power Up 0ns t PD CE HIGH to Power Down 10ns t DBE Byte Enable to Data Valid 5ns t LZBE Byte Enable to Low-Z 0ns t HZBEByte Disable to High-Z6nsNotes5.AC characteristics (except High-Z) are tested using the load conditions shown in Figure (a). High-Z characteristics are tested for all speeds using the test loadshown in Figure (c).6.Test conditions assume signal transition time of 3 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V.7.t POWER gives the minimum amount of time that the power supply should be at typical V CC values until the first memory access can be performed.8.t HZOE , t HZCE , t HZBE and t HZWE are specified with a load capacitance of 5 pF as in part (d) of AC Test Loads.Transition is measured when the outputs enter ahigh impedance state.9.At any given temperature and voltage condition, t HZCE is less than t LZCE , t HZOE is less than t LZOE , t HZBE is less than t LZBE , and t HZWE is less than t LZWE for anygiven device.90%10%3.0VGND90%10%ALL INPUT PULSES * CAPACITIVE LOAD CONSISTS OF ALL COMPONENTS OF THE TEST ENVIRONMENTRise Time: 1 V/nsFall Time: 1 V/ns30 pF*OUTPUTZ = 50Ω50Ω1.5V (a)3.3V OUTPUT5 pF(c)R 317ΩR2351ΩHigh-Z Characteristics(b)PRELIMINARY CY7C1051DV33Data Retention WaveformWrite Cycle [10, 11]t WC Write Cycle Time 10ns t SCE CE LOW to Write End 7ns t AW Address Setup to Write End 7ns t HA Address Hold from Write End 0ns t SA Address Setup to Write Start 0ns t PWE WE Pulse Width 7ns t SD Data Setup to Write End 5ns t HD Data Hold from Write End 0ns t LZWE WE HIGH to Low-Z [9]3ns t HZWE WE LOW to High-Z [8, 9]5ns t BWByte Enable to End of Write7nsData Retention Characteristics Over the Operating RangeParameter DescriptionConditions [12]Min MaxUnit V DR V CC for Data Retention 2.0V I CCDR Data Retention CurrentV CC = V DR = 2.0V , CE > V CC – 0.3V , V IN > V CC – 0.3V or V IN < 0.3V20mA t CDR [4]Chip Deselect to Data Retention Time 0ns t R [13]Operation Recovery Timet RCnsAC Switching Characteristics [6] Over the Operating Range (continued)ParameterDescription–10UnitMinMax3.0V 3.0V t CDRV DR > 2VDATA RETENTION MODEt RCEV CC Notes10.The internal Write time of the memory is defined by the overlap of CE LOW, and WE LOW. CE and WE must be LOW to initiate a Write, and the transition ofeither of these signals can terminate the Write. The input data setup and hold timing should be referenced to the leading edge of the signal that terminates the Write.11.The minimum Write cycle time for Write Cycle No. 3 (WE controlled, OE LOW) is the sum of t HZWE and t SD .12.No inputs may exceed V CC + 0.3V13.Full device operation requires linear V CC ramp from V DR to V CC (min) > 50 μs or stable at V CC (min) > 50 μs.PRELIMINARY CY7C1051DV33Switching WaveformsRead Cycle No. 1[14, 15]Read Cycle No. 2 (OE Controlled)[15, 16]Notes14.Device is continuously selected. OE, CE, BHE or BHE or both= V IL .15.WE is HIGH for Read cycle.16.Address valid prior to or coincident with CE transition LOW.PREVIOUS DATA VALIDDATA VALIDt RCt AAt OHAADDRESSDATA OUT50%50%DATA VALIDt RCt ACEt DOE t LZOE t LZCE t PUHIGH IMPEDANCEt HZOEt HZBEt PDHIGHOE CEICC ISB IMPEDANCEADDRESSDATA OUT V CC SUPPLY t DBE t LZBEt HZCE BHE,BLECURRENTI CCI SBPRELIMINARY CY7C1051DV33Write Cycle No. 1 (CE Controlled)[17, 18]Write Cycle No. 2 (BLE or BHE Controlled)Notes17.Data I/O is high-impedance if OE or BHE or BLE or both = V IH .18.If CE goes HIGH simultaneously with WE going HIGH, the output remains in a high-impedance state.Switching Waveforms (continued)t HDt SDt SCEt SA t HAt AWt PWEt WCBWDATAI/OADDRESSCEWEBHE,BLEt t HDt SDt BWt SA t HAt AWt PWEt WCt SCEDATAI/OADDRESSBHE,BLEWECEPRELIMINARY CY7C1051DV33Write Cycle No. 3 (WE Controlled, OE LOW)Switching Waveforms (continued)t HDt SDt SCEt HAt AWt PWEt WCt BWDATA I/OADDRESSCEWEBHE,BLEt SAt LZWEt HZWETruth TableCE OE WE BLE BHE I/O 0–I/O 7I/O 8–I/O 15ModePower H X X X X High-Z High-Z Power-down Standby (I SB )L L H L L Data Out Data Out Read All Bits Active (I CC )L L H L H Data Out High-Z Read Lower Bits Only Active (I CC )L L H H L High-Z Data Out Read Upper Bits Only Active (I CC )L X L L L Data In Data In Write All Bits Active (I CC )L X L L H Data In High-Z Write Lower Bits Only Active (I CC )L X L H L High-Z Data In Write Upper Bits Only Active (I CC )LHHXXHigh-ZHigh-ZSelected, Outputs DisabledActive (I CC )Ordering InformationSpeed (ns)Ordering Code Package Diagram Package TypeOperating Range 10CY7C1051DV33-10BAXI 51-8510648-ball FBGA (Pb-Free)IndustrialCY7C1051DV33-10ZSXI51-8508744-pin TSOP II (Pb-Free)Please contact your local Cypress sales representative for availability of these parts.PRELIMINARY CY7C1051DV33 Package DiagramsPRELIMINARY CY7C1051DV33Document #: 001-00063 Rev. *C Page 10 of 11© Cypress Semiconductor Corporation, 2006-2007. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the All products and company names mentioned in this document may be the trademarks of their respective holders.Figure 2. 44-pin TSOP II (51-85087)Package Diagrams (continued)51-85087-*APRELIMINARY CY7C1051DV33Document #: 001-00063 Rev. *C Page 11 of 11Document History Page Document Title: CY7C1051DV33 8-Mbit (512K x 16) Static RAM Document Number: 001-00063REV.ECN NO.Issue Date Orig. of Change Description of Change **342195See ECN PCI New Data Sheet *A 380574See ECN SYT Redefined I CC values for Com’l and Ind’l temperature rangesI CC (Com’l): Changed from 110, 90 and 80 mA to 110, 100 and 95 mA for 8, 10and 12 ns speed bins respectivelyI CC (Ind’l): Changed from 110, 90 and 80 mA to 120, 110 and 105 mA for 8, 10and 12 ns speed bins respectivelyChanged the Capacitance values from 8 pF to 10 pF on Page # 3*B 485796See ECN NXR Changed address of Cypress Semiconductor Corporation on Page# 1 from“3901 North First Street” to “198 Champion Court”Removed -8 and -12 Speed bins from product offering,Removed Commercial Operating Range option,Modified Maximum Ratings for DC input voltage from -0.5V to -0.3V andV CC + 0.5V to V CC + 0.3VChanged the Description of I IX from Input Load Current toInput Leakage Current.Changed t HZBE from 5 ns to 6 nsUpdated footnote #7 on High-Z parameter measurementAdded footnote #11Updated the Ordering Information table and Replaced Package Name columnwith Package Diagram.*C 866000See ECN NXRChanged ball E3 from V SS to NC in FBGA pin configuration [+] FeedbThis datasheet has been downloaded from:Free DownloadDaily Updated Database100% Free Datasheet Search Site100% Free IC Replacement Search SiteConvenient Electronic DictionaryFast Search SystemAll Datasheets Cannot Be Modified Without PermissionCopyright © Each Manufacturing Company。

CY7C1470BV25资料

72-Mbit (2M x 36/4M x 18/1M x 72)Pipelined SRAM with NoBL™ ArchitectureCY7C1470BV25CY7C1472BV25, CY7C1474BV25Features■Pin-compatible and functionally equivalent to ZBT™ ■Supports 250 MHz bus operations with zero wait states ❐Available speed grades are 250, 200, and 167 MHz■Internally self-timed output buffer control to eliminate the need to use asynchronous OE■Fully registered (inputs and outputs) for pipelined operation■Byte Write capability ■Single 2.5V power supply ■2.5V IO supply (V DDQ )■Fast clock-to-output times ❐3.0 ns (for 250-MHz device)■Clock Enable (CEN) pin to suspend operation ■Synchronous self-timed writes■CY7C1470BV25, CY7C1472BV25 available inJEDEC-standard Pb-free 100-pin TQFP , Pb-free and non-Pb-free 165-ball FBGA package. CY7C1474BV25available in Pb-free and non-Pb-free 209-ball FBGA package ■IEEE 1149.1 JTAG Boundary Scan compatible ■Burst capability—linear or interleaved burst order ■“ZZ” Sleep Mode option and Stop Clock optionFunctional DescriptionThe CY7C1470BV25, CY7C1472BV25, and CY7C1474BV25are 2.5V, 2M x 36/4M x 18/1M x 72 synchronous pipelined burst SRAMs with No Bus Latency™ (NoBL ™) logic, respectively.They are designed to support unlimited true back-to-back read or write operations with no wait states. The CY7C1470BV25,CY7C1472BV25, and CY7C1474BV25 are equipped with the advanced (NoBL) logic required to enable consecutive read or write operations with data being transferred on every clock cycle.This feature dramatically improves the throughput of data in systems that require frequent read or write transitions. The CY7C1470BV25, CY7C1472BV25, and CY7C1474BV25 are pin-compatible and functionally equivalent to ZBT devices.All synchronous inputs pass through input registers controlled by the rising edge of the clock. All data outputs pass through output registers controlled by the rising edge of the clock. The clock input is qualified by the Clock Enable (CEN) signal, which when deasserted suspends operation and extends the previous clock cycle. Write operations are controlled by the Byte Write Selects (BW a –BW d for CY7C1470BV25, BW a –BW b for CY7C1472BV25, and BW a –BW h for CY7C1474BV25) and a Write Enable (WE) input. All writes are conducted with on-chip synchronous self-timed write circuitry.Three synchronous Chip Enables (CE 1, CE 2, CE 3) and an asynchronous Output Enable (OE) provide for easy bank selection and output tri-state control. To avoid bus contention,the output drivers are synchronously tri-stated during the data portion of a write sequence.Selection GuideDescription250 MHz 200 MHz 167 MHz Unit Maximum Access Time3.0 3.0 3.4ns Maximum Operating Current450450400mA Maximum CMOS Standby Current120120120mALogic Block Diagram – CY7C1470BV25 (2M x 36)Logic Block Diagram – CY7C1472BV25 (4M x 18)Logic Block Diagram – CY7C1474BV25 (1M x 72)Pin ConfigurationsA A A A A 1A 0V S SV D DA A A A A AV DDQ V SSDQb DQb DQb V SS V DDQDQb DQb V SSNCV DDDQaDQa V DDQ V SSDQa DQa V SS V DDQ V DDQV SS DQc DQc V SS V DDQ DQc V DD V SS DQd DQd V DDQ V SS DQd DQd DQd V SS V DDQ A A C E 1C E 2B W aC E 3V D DV S SC L K W E C E N O E A A123456789101112131415161718192021222324252627282930313233343536373839404142434445464748495080797877767574737271706968676665646362616059585756555453525110099989796959493929190898887868584838281A AA D V /L D ZZCY7C1470BV25A A A A A 1A 0V S SV D DA A A A A AA NC NC V DDQ V SS NC DQPa DQa DQa V SS V DDQ DQa DQa V SS NC V DD DQa DQa V DDQ V SS DQa DQa NC NC V SS V DDQ NC NC NCNC NC NC V DDQ V SS NC NC DQb DQb V SS V DDQDQb DQbV DD V SS DQb DQb V DDQV SS DQb DQb DQPbNC V SS V DDQNC NC NCA A C E 1C E 2N C N C B W b B W a C E 3V D DV S SC L K W E C E N O E A A123456789101112131415161718192021222324252627282930313233343536373839404142434445464748495080797877767574737271706968676665646362616059585756555453525110099989796959493929190898887868584838281A AA D V /L D ZZ M O D E CY7C1472BV25B W d M O D E B W c DQc DQc DQc DQc DQPc DQd DQd DQd DQPb DQb DQa DQaDQa DQaDQPa DQb DQb (2M × 36)(4M × 18)B W b NC NC NC DQc NC N C (288)N C (144)N C (288)N C (144)DQPdA A A A A A Figure 1. 100-Pin TQFP PinoutPin Configurations (continued)165-Ball FBGA (15 x 17 x 1.4 mm) PinoutCY7C1470BV25 (2M x 36)CY7C1472BV25 (4M x 18)2345671A B C D E F G H J K L M N P RTDO NC/576M NC/1G DQP c DQ c DQP d NC DQ d A CE 1BW b CE 3BW c CEN A CE2DQ c DQ d DQ d MODENC DQ c DQ c DQ d DQ d DQ d AV DDQ BW d BW a CLKWEV SS V SS V SS V SS V DDQ V SS V DD V SS V SS V SS NC V SS V SS V SS V SS V DDQ V DDQ NC V DDQ V DDQ V DDQ V DDQ A AV DD V SS V DD V SS V SS V DDQ V DD V SS V DD V SS V DD V SS V SS V SS V DD V DD V SS V DD V SS V SS NC TCKA0V SS TDIAA DQ c V SS DQ c V SS DQ c DQ c NC V SS V SS V SS V SS NC V SS A1DQ d DQ d NC/144M NCV DDQ V SS TMS891011NC/288MAA ADV/LDNC OE A A NC V SS V DDQ NC DQP b V DDQ V DD DQ b DQ b DQ b NC DQ b NC DQ a DQ a V DD V DDQ V DD V DDQ DQ b V DD NC V DD DQ a V DD V DDQ DQ a V DDQ V DD V DD V DDQ V DD V DDQ DQ a V DDQ AAV SS AAADQ b DQ b DQ b ZZ DQ a DQ a DQP aDQ a A V DDQ AA 2345671A B C D E F G H J K L M N P RTDO NC/576M NC/1G NC NC DQP b NC DQ b A CE 1CE 3BW b CEN A CE2NC DQ b DQ b MODENC DQ b DQ b NC NC NC AV DDQ BW a CLKWE V SS V SS V SS V SSV DDQ V SS V DD V SS V SS V SS NC V SS V SS V SS V SS V DDQ V DDQ NC V DDQ V DDQ V DDQ V DDQ A AV DD V SS V DD V SS V SS V DDQ V DD V SS V DD V SS V DD V SS V SS V SS V DD V DD V SS V DD V SS V SS NC TCKA0V SS TDIAA DQ b V SS NC V SS DQ b NC NC V SS V SS V SS V SS NC V SS A1DQ b NC NC/144M NCV DDQ V SS TMS891011NC/288MAA ADV/LDA OE A A NC V SSV DDQ NC DQPa V DDQ V DD NC DQ a DQ a NC NC NC DQ a NC V DD V DDQ V DD V DDQ DQ a V DD NC V DD NC V DD V DDQ DQ a V DDQ V DD V DD V DDQ V DD V DDQ NC V DDQ AAV SS AAADQ a NC NC ZZ DQ a NC NCDQ a A V DDQ AA NC NCPin Configurations (continued)CY7C1474BV25 (1M × 72)209-Ball FBGA (14 x 22 x 1.76 mm) PinoutA B C D E F G H J K L M N P R T U V W1234567891110DQgDQgDQgDQgDQgDQgDQgDQgDQcDQcDQcDQcNCDQPgDQhDQhDQhDQhDQdDQdDQdDQdDQPdDQPcDQcDQcDQcDQcNCDQhDQhDQhDQhDQPhDQdDQdDQdDQdDQbDQbDQbDQbDQbDQbDQbDQbDQfDQfDQfDQfNCDQPfDQaDQaDQaDQaDQeDQeDQeDQeDQPaDQPbDQfDQfDQfDQfNCDQaDQaDQaDQaDQPeDQeDQeDQeDQeA A A ANC NCNC/144M A A NC/288MA A AA A A A1A0A A AA AANC/576MNCNCNC NCNCBWS b BWS fBWS e BWS aBWS c BWS gBWS dBWS hTMS TDI TDO TCKNCNC MODE NCCEN V SSNCCLK NC V SSV DD V DD V DDV DDV DDV DDV DDV DDV DDV DDV DDV DDV DDV SS V SSV SSV SSV SSV SS V SSV SSNC/1GV DDNCOECE3CE1CE2ADV/LDWEV SSV SSV SSV SS V SS V SS VSSZZV SS V SS V SS V SSNCV DDQV SSV SS NC V SS V SSV SS V SS VSSV SSNCV SSV DDQ V DDQ V DDQ V DDQV DDQ NC V DDQ VDDQV DDQ V DDQ NC V DDQ V DDQV DDQ V DDQ NC V DDQ VDDQV DDQV DDQV DDQ V DDQV DDQ VDDQV DDQ V DDQTable 1. Pin DefinitionsPin Name IO Type Pin DescriptionA0 A1 AInput-SynchronousAddress Inputs Used to Select One of the Address Locations. Sampled at the rising edge of theCLK.BW a BW b BW c BW d BW e BW f BW g BW hInput-SynchronousByte Write Select Inputs, Active LOW. Qualified with WE to conduct writes to the SRAM. Sampledon the rising edge of CLK. BW a controls DQ a and DQP a, BW b controls DQ b and DQP b, BW c controlsDQ c and DQP c, BW d controls DQ d and DQP d, BW e controls DQ e and DQP e, BW f controls DQ f andDQP f, BW g controls DQ g and DQP g, BW h controls DQ h and DQP h.WE Input-Synchronous Write Enable Input, Active LOW. Sampled on the rising edge of CLK if CEN is active LOW. This signal must be asserted LOW to initiate a write sequence.ADV/LD Input-Synchronous Advance/Load Input Used to Advance the On-Chip Address Counter or Load a New Address. When HIGH (and CEN is asserted LOW) the internal burst counter is advanced. When LOW, a new address can be loaded into the device for an access. After being deselected, ADV/LD must be driven LOW to load a new address.CLK Input-Clock Clock Input. Used to capture all synchronous inputs to the device. CLK is qualified with CEN. CLK is only recognized if CEN is active LOW.CE1Input-Synchronous Chip Enable 1 Input, Active LOW. Sampled on the rising edge of CLK. Used in conjunction with CE2 and CE3 to select/deselect the device.CE2Input-Synchronous Chip Enable 2 Input, Active HIGH. Sampled on the rising edge of CLK. Used in conjunction with CE1 and CE3 to select/deselect the device.CE3Input-Synchronous Chip Enable 3 Input, Active LOW. Sampled on the rising edge of CLK. Used in conjunction with CE1 and CE2 to select/deselect the device.OE Input-Asynchronous Output Enable, Active LOW. Combined with the synchronous logic block inside the device to control the direction of the IO pins. When LOW, the IO pins can behave as outputs. When deasserted HIGH, IO pins are tri-stated, and act as input data pins. OE is masked during the data portion of a write sequence, during the first clock when emerging from a deselected state and when the device has been deselected.CEN Input-Synchronous Clock Enable Input, Active LOW. When asserted LOW the clock signal is recognized by the SRAM. When deasserted HIGH the clock signal is masked. Since deasserting CEN does not deselect the device, CEN can be used to extend the previous cycle when required.DQ s IO-Synchronous Bidirectional Data IO Lines. As inputs, they feed into an on-chip data register that is triggered by the rising edge of CLK. As outputs, they deliver the data contained in the memory location specified by A[18:0] during the previous clock rise of the read cycle. The direction of the pins is controlled by OE and the internal control logic. When OE is asserted LOW, the pins can behave as outputs. When HIGH, DQ a–DQ h are placed in a tri-state condition. The outputs are automatically tri-stated during the data portion of a write sequence, during the first clock when emerging from a deselected state, and when the device is deselected, regardless of the state of OE.DQP X IO-Synchronous Bidirectional Data Parity IO Lines. Functionally, these signals are identical to DQ[71:0]. During write sequences, DQP a is controlled by BW a, DQP b is controlled by BW b, DQP c is controlled by BW c, and DQP d is controlled by BW d, DQP e is controlled by BW e, DQP f is controlled by BW f, DQP g is controlled by BW g, DQP h is controlled by BW h.MODE Input Strap Pin Mode Input. Selects the burst order of the device. Tied HIGH selects the interleaved burst order.Pulled LOW selects the linear burst order. MODE must not change states during operation. Whenleft floating MODE defaults HIGH, to an interleaved burst order.TDO JTAG SerialOutputSynchronousSerial Data Out to the JTAG Circuit. Delivers data on the negative edge of TCK.TDI JTAG Serial InputSynchronousSerial Data In to the JTAG Circuit. Sampled on the rising edge of TCK.Functional OverviewThe CY7C1470BV25, CY7C1472BV25, and CY7C1474BV25 are synchronous-pipelined Burst NoBL SRAMs designed specif-ically to eliminate wait states during read or write transitions. All synchronous inputs pass through input registers controlled by the rising edge of the clock. The clock signal is qualified with the Clock Enable input signal (CEN). If CEN is HIGH, the clock signal is not recognized and all internal states are maintained. All synchronous operations are qualified with CEN. All data outputs pass through output registers controlled by the rising edge of the clock. Maximum access delay from the clock rise (t CO) is 3.0 ns (250-MHz device).Accesses can be initiated by asserting all three Chip Enables (CE1, CE2, CE3) active at the rising edge of the clock. If CEN is active LOW and ADV/LD is asserted LOW, the address presented to the device is latched. The access can either be a read or write operation, depending on the status of the Write Enable (WE). BW[x] can be used to conduct Byte Write opera-tions.Write operations are qualified by the Write Enable (WE). All writes are simplified with on-chip synchronous self-timed write circuitry.Three synchronous Chip Enables (CE1, CE2, CE3) and an asynchronous Output Enable (OE) simplify depth expansion. All operations (reads, writes, and deselects) are pipelined. ADV/LD must be driven LOW after the device is deselected to load a new address for the next operation.Single Read AccessesA read access is initiated when the following conditions are satisfied at clock rise: (1) CEN is asserted LOW, (2) CE1, CE2, and CE3 are ALL asserted active, (3) the input signal WE is deasserted HIGH, and (4) ADV/LD is asserted LOW. The address presented to the address inputs is latched into the Address Register and presented to the memory core and control logic. The control logic determines that a read access is in progress and allows the requested data to propagate to the input of the output register. At the rising edge of the next clock the requested data is allowed to propagate through the output register and onto the data bus within 2.6 ns (250-MHz device) provided OE is active LOW. After the first clock of the read access the output buffers are controlled by OE and the internal control logic. OE must be driven LOW to drive out the requested data. During the second clock, a subsequent operation (read, write, or deselect) can be initiated. Deselecting the device is also pipelined. Therefore, when the SRAM is deselected at clock rise by one of the chip enable signals, its output tri-states following the next clock rise.Burst Read AccessesThe CY7C1470BV25, CY7C1472BV25, and CY7C1474BV25 have an on-chip burst counter that enables the user to supply a single address and conduct up to four reads without reasserting the address inputs. ADV/LD must be driven LOW to load a new address into the SRAM, as described in the Single Read Accesses section. The sequence of the burst counter is deter-mined by the MODE input signal. A LOW input on MODE selects a linear burst mode, a HIGH selects an interleaved burst sequence. Both burst counters use A0 and A1 in the burst sequence, and wraps around when incremented sufficiently. A HIGH input on ADV/LD increments the internal burst counter regardless of the state of chip enables inputs or WE. WE is latched at the beginning of a burst cycle. Therefore, the type of access (read or write) is maintained throughout the burst sequence.Single Write AccessesWrite accesses are initiated when the following conditions are satisfied at clock rise: (1) CEN is asserted LOW, (2) CE1, CE2, and CE3 are ALL asserted active, and (3) the signal WE is asserted LOW. The address presented to the address inputs is loaded into the Address Register. The write signals are latched into the Control Logic block.On the subsequent clock rise the data lines are automatically tri-stated regardless of the state of the OE input signal. This allows the external logic to present the data on DQ and DQP (DQ a,b,c,d/DQP a,b,c,d for CY7C1470BV25, DQ a,b/DQP a,b for CY7C1472BV25, and DQ a,b,c,d,e,f,g,h/DQP a,b,c,d,e,f,g,h for CY7C1474BV25). In addition, the address for the subsequentTMS Test Mode SelectSynchronousTMS Pin Controls the Test Access Port State Machine. Sampled on the rising edge of TCK. TCK JTAG Clock Clock Input to the JTAG Circuitry.V DD Power Supply Power Supply Inputs to the Core of the Device.V DDQ IO Power Supply Power Supply for the IO Circuitry.V SS Ground Ground for the Device. Must be connected to ground of the system.NC–No Connects. This pin is not connected to the die.NC(144M, 288M, 576M, 1G)–These Pins are Not Connected. They are used for expansion to the 144M, 288M, 576M, and 1G densities.ZZ Input-Asynchronous ZZ “Sleep” Input. This active HIGH input places the device in a non-time critical “sleep” condition with data integrity preserved. For normal operation, this pin has must be LOW or left floating.ZZ pin has an internal pull down.Table 1. Pin Definitions (continued)Pin Name IO Type Pin Descriptionaccess (read, write, or deselect) is latched into the Address Register (provided the appropriate control signals are asserted). On the next clock rise the data presented to DQ and DQP (DQ a,b,c,d/DQP a,b,c,d for CY7C1470BV25, DQ a,b/DQP a,b for CY7C1472BV25, DQ a,b,c,d,e,f,g,h/DQP a,b,c,d,e,f,g,h for CY7C1474BV25) (or a subset for Byte Write operations, see “Partial Write Cycle Description” on page11 for details) inputs is latched into the device and the Write is complete.The data written during the Write operation is controlled by BW (BW a,b,c,d for CY7C1470BV25, BW a,b for CY7C1472BV25, and BW a,b,c,d,e,f,g,h for CY7C1474BV25) signals. The CY7C1470BV25, CY7C1472BV25, and CY7C1474BV25 provides Byte Write capability that is described in “Partial Write Cycle Description” on page11. Asserting the WE input with the selected BW input selectively writes to only the desired bytes. Bytes not selected during a Byte Write operation remain unaltered. A synchronous self-timed write mechanism has been provided to simplify the write operations. Byte Write capability has been included to greatly simplify read, modify, or write sequences, which can be reduced to simple Byte Write opera-tions.Because the CY7C1470BV25, CY7C1472BV25, and CY7C1474BV25 are common IO devices, data must not be driven into the device while the outputs are active. OE can be deasserted HIGH before presenting data to the DQ and DQP (DQ a,b,c,d/DQP a,b,c,d for CY7C1470BV25, DQ a,b/DQP a,b for CY7C1472BV25, and DQ a,b,c,d,e,f,g,h/DQP a,b,c,d,e,f,g,h for CY7C1474BV25) inputs. Doing so tri-states the output drivers. As a safety precaution, DQ and DQP (DQ a,b,c,d/DQP a,b,c,d for CY7C1470BV25, DQ a,b/DQP a,b for CY7C1472BV25, and DQ a,b,c,d,e,f,g,h/DQP a,b,c,d,e,f,g,h for CY7C1474BV25) are automatically tri-stated during the data portion of a write cycle, regardless of the state of OE.Burst Write AccessesThe CY7C1470BV25, CY7C1472BV25, and CY7C1474BV25 has an on-chip burst counter that enables the user to supply a single address and conduct up to four write operations without reasserting the address inputs. ADV/LD must be driven LOW to load the initial address, as described in “Single Write Accesses”on page8. When ADV/LD is driven HIGH on the subsequent clock rise, the Chip Enables (CE1, CE2, and CE3) and WE inputs are ignored and the burst counter is incremented. The correct BW (BW a,b,c,d for CY7C1470BV25, BW a,b for CY7C1472BV25, and BW a,b,c,d,e,f,g,h for CY7C1474BV25) inputs must be driven in each cycle of the burst write to write the correct bytes of data. Sleep ModeThe ZZ input pin is an asynchronous input. Asserting ZZ places the SRAM in a power conservation “sleep” mode. Two clock cycles are required to enter into or exit from this “sleep” mode. While in this mode, data integrity is guaranteed. Accesses pending when entering the “sleep” mode are not considered valid nor is the completion of the operation guaranteed. The device must be deselected before entering the “sleep” mode. CE1, CE2, and CE3, must remain inactive for the duration of t ZZREC after the ZZ input returns LOW.Table 2. Linear Burst Address Table (MODE = GND) FirstAddressSecondAddressThirdAddressFourthAddress A1,A0A1,A0A1,A0A1,A000011011011011001011000111000110Table 3. Interleaved Burst Address Table(MODE = Floating or V DD)FirstAddressSecondAddressThirdAddressFourthAddress A1,A0A1,A0A1,A0A1,A000011011010011101011000111100100ZZ Mode Electrical CharacteristicsParameter Description Test Conditions Min Max Unit I DDZZ Sleep mode standby current ZZ > V DD − 0.2V120mA t ZZS Device operation to ZZ ZZ > V DD− 0.2V2t CYC ns t ZZREC ZZ recovery time ZZ < 0.2V2t CYC ns t ZZI ZZ active to sleep current This parameter is sampled2t CYC ns t RZZI ZZ Inactive to exit sleep current This parameter is sampled0nsTable 4. Truth TableThe truth table for CY7C1470BV25, CY7C1472BV25, and CY7C1474BV25 follows.[1, 2, 3, 4, 5, 6, 7]Operation AddressUsed CE ZZ ADV/LD WE BW x OE CEN CLK DQ Deselect Cycle None H L L X X X L L-H Tri-State Continue Deselect Cycle None X L H X X X L L-H Tri-StateExternal L L L H X L L L-H Data Out (Q) Read Cycle(Begin Burst)Next X L H X X L L L-H Data Out (Q) Read Cycle(Continue Burst)External L L L H X H L L-H Tri-State NOP/Dummy Read(Begin Burst)Next X L H X X H L L-H Tri-State Dummy Read(Continue Burst)External L L L L L X L L-H Data In (D) Write Cycle(Begin Burst)Next X L H X L X L L-H Data In (D) Write Cycle(Continue Burst)None L L L L H X L L-H Tri-State NOP/Write Abort(Begin Burst)Next X L H X H X L L-H Tri-State Write Abort(Continue Burst)Ignore Clock Edge (Stall)Current X L X X X X H L-H–Sleep Mode None X H X X X X X X Tri-StateNotes1.X = “Don't Care”, H = Logic HIGH, L = Logic LOW, CE stands for ALL Chip Enables active. BW x = L signifies at least one Byte Write Select is active, BW x = Validsignifies that the desired Byte Write Selects are asserted, see “Partial Write Cycle Description” on page11 for details.2.[a:d]. See “Partial Write Cycle Description” on page11 for details.3.When a write cycle is detected, all IOs are tri-stated, even during Byte Writes.4.The DQ and DQP pins are controlled by the current cycle and the OE signal.5.6.Device powers up deselected with the IOs in a tri-state condition, regardless of OE.7.OE is asynchronous and is not sampled with the clock rise. It is masked internally during write cycles.During a Read cycle DQ s and DQP[a:d] = tri-state when OE isinactive or when the device is deselected, and DQ s = data when OE is active.Table 5. Partial Write Cycle DescriptionThe partial write cycle description for CY7C1470BV25, CY7C1472BV25, and CY7C1474BV25 follows.[1, 2, 3, 8]Function (CY7C1470BV25)WE BW d BW c BW b BW a Read H X X X X Write – No bytes written L H H H H Write Byte a – (DQ a and DQP a)L H H H L Write Byte b – (DQ b and DQP b)L H H L H Write Bytes b, a L H H L L Write Byte c – (DQ c and DQP c)L H L H H Write Bytes c, a L H L H L Write Bytes c, b L H LL L H Write Bytes c, b, a L H L L L Write Byte d – (DQ d and DQP d)L L H H H Write Bytes d, a L L H H L Write Bytes d, b L L H L H Write Bytes d, b, a L L H L L Write Bytes d, c L L L H H Write Bytes d, c, a L L L H L Write Bytes d, c, b L L L L H Write All Bytes L L L L LFunction (CY7C1472BV25)WE BW b BW aRead H x xWrite – No Bytes Written L H HWrite Byte a – (DQ a and DQP a)L H LWrite Byte b – (DQ b and DQP b)L L HWrite Both Bytes L L LFunction (CY7C1474BV25)WE BW xRead H xWrite – No Bytes Written L HWrite Byte X − (DQ x and DQP x)L LWrite All Bytes L All BW = LNote8.Table lists only a partial listing of the Byte Write combinations. Any combination of BW[a:d] is valid. Appropriate write is based on which Byte Write is active.IEEE 1149.1 Serial Boundary Scan (JTAG) The CY7C1470BV25, CY7C1472BV25, and CY7C1474BV25incorporates a serial boundary scan test access port (TAP). This port operates in accordance with IEEE Standard 1149.1-1990 but does not have the set of functions required for full 1149.1 compliance. These functions from the IEEE specification are excluded because their inclusion places an added delay in the critical speed path of the SRAM. Note that the TAP controller functions in a manner that does not conflict with the operation of other devices using 1149.1 fully compliant TAPs. The TAP operates using JEDEC-standard 2.5V IO logic levels.The CY7C1470BV25, CY7C1472BV25, and CY7C1474BV25 contains a TAP controller, instruction register, boundary scan register, bypass register, and ID register.Disabling the JTAG FeatureIt is possible to operate the SRAM without using the JTAG feature. To disable the TAP controller, TCK must be tied LOW (V SS) to prevent clocking of the device. TDI and TMS are inter-nally pulled up and may be unconnected. They may alternately be connected to V DD through a pull up resistor. TDO must be left unconnected. During power up, the device comes up in a reset state, which does not interfere with the operation of the device. The 0/1 next to each state represents the value of TMS at therising edge of TCK.Test Access Port (TAP)Test Clock (TCK)The test clock is used only with the TAP controller. All inputs are captured on the rising edge of TCK. All outputs are driven from the falling edge of TCK.Test MODE SELECT (TMS)The TMS input is used to give commands to the TAP controller and is sampled on the rising edge of TCK. It is allowable to leave this ball unconnected if the TAP is not used. The ball is pulled up internally, resulting in a logic HIGH level.Test Data-In (TDI)The TDI ball is used to serially input information into the registers and can be connected to the input of any of the registers. The register between TDI and TDO is chosen by the instruction that is loaded into the TAP instruction register. For information about loading the instruction register, see the TAP Controller State Diagram. TDI is internally pulled up and can be unconnected if the TAP is unused in an application. TDI is connected to the most significant bit (MSB) of any register. (See TAP Controller Block Diagram.)Test Data-Out (TDO)The TDO output ball is used to serially clock data-out from the registers. The output is active depending upon the current state of the TAP state machine. The output changes on the falling edge of TCK. TDO is connected to the least significant bit (LSB) of any register. (See TAP Controller State Diagram.)Performing a TAP ResetA RESET is performed by forcing TMS HIGH (V DD) for five rising edges of TCK. This RESET does not affect the operation of the SRAM and may be performed while the SRAM is operating. During power up, the TAP is reset internally to ensure that TDO comes up in a High-Z state.TAP RegistersRegisters are connected between the TDI and TDO balls to scan the data in and out of the SRAM test circuitry. Only one register can be selected at a time through the instruction register. Data is serially loaded into the TDI ball on the rising edge of TCK. Data is output on the TDO ball on the falling edge of TCK.Figure 2. TAP Controller State DiagramFigure 3. TAP Controller Block DiagramInstruction RegisterThree-bit instructions can be serially loaded into the instruction register. This register is loaded when it is placed between the TDI and TDO balls as shown in the “TAP Controller Block Diagram”on page12. During power up, the instruction register is loaded with the IDCODE instruction. It is also loaded with the IDCODE instruction if the controller is placed in a reset state as described in the previous section.When the TAP controller is in the Capture-IR state, the two least significant bits are loaded with a binary ‘01’ pattern to enable fault isolation of the board-level serial test data path.Bypass RegisterTo save time when serially shifting data through registers, it is sometimes advantageous to skip certain chips. The bypass register is a single-bit register that can be placed between the TDI and TDO balls. This shifts the data through the SRAM with minimal delay. The bypass register is set LOW (V SS) when the BYPASS instruction is executed.Boundary Scan RegisterThe boundary scan register is connected to all the input and bidirectional balls on the SRAM.The boundary scan register is loaded with the contents of the RAM IO ring when the TAP controller is in the Capture-DR state and is then placed between the TDI and TDO balls when the controller is moved to the Shift-DR state. The EXTEST, SAMPLE/PRELOAD and SAMPLE Z instructions can be used to capture the contents of the IO ring.The Boundary Scan Order tables on page 17 show the order in which the bits are connected. Each bit corresponds to one of the bumps on the SRAM package. The MSB of the register is connected to TDI and the LSB is connected to TDO. Identification (ID) RegisterThe ID register is loaded with a vendor-specific, 32-bit code during the Capture-DR state when the IDCODE command is loaded in the instruction register. The IDCODE is hardwired into the SRAM and can be shifted out when the TAP controller is in the Shift-DR state. The ID register has a vendor code and other information described in “Identification Register Definitions” on page16.TAP Instruction SetOverviewEight different instructions are possible with the three-bit instruction register. All combinations are listed in “Identification Codes” on page17. Three of these instructions are listed as RESERVED and must not be used. The other five instructions are described in this section in detail.The TAP controller used in this SRAM is not fully compliant to the 1149.1 convention because some of the mandatory 1149.1 instructions are not fully implemented.The TAP controller cannot be used to load address data or control signals into the SRAM and cannot preload the IO buffers. The SRAM does not implement the 1149.1 commands EXTEST or INTEST or the PRELOAD portion of SAMPLE/PRELOAD; rather, it performs a capture of the IO ring when these instruc-tions are executed.Instructions are loaded into the TAP controller during the Shift-IR state when the instruction register is placed between TDI and TDO. During this state, instructions are shifted through the instruction register through the TDI and TDO balls. To execute the instruction after it is shifted in, the TAP controller must be moved into the Update-IR state.EXTESTEXTEST is a mandatory 1149.1 instruction which is executed whenever the instruction register is loaded with all 0s. EXTEST is not implemented in this SRAM TAP controller, and therefore this device is not compliant to 1149.1. The TAP controller does recognize an all-0 instruction.When an EXTEST instruction is loaded into the instruction register, the SRAM responds as if a SAMPLE/PRELOAD instruction has been loaded. There is one difference between the two instructions. Unlike the SAMPLE/PRELOAD instruction, EXTEST places the SRAM outputs in a High-Z state.IDCODEThe IDCODE instruction loads a vendor-specific, 32-bit code into the instruction register. It also places the instruction register between the TDI and TDO balls and shifts the IDCODE out of the device when the TAP controller enters the Shift-DR state.The IDCODE instruction is loaded into the instruction register during power up or whenever the TAP controller is in a test logic reset state.SAMPLE ZThe SAMPLE Z instruction connects the boundary scan register between the TDI and TDO pins when the TAP controller is in a Shift-DR state. It also places all SRAM outputs into a High-Z state.SAMPLE/PRELOADSAMPLE/PRELOAD is a 1149.1 mandatory instruction. The PRELOAD portion of this instruction is not implemented, so the device TAP controller is not fully 1149.1 compliant.When the SAMPLE/PRELOAD instruction is loaded into the instruction register and the TAP controller is in the Capture-DR state, a snapshot of data on the inputs and bidirectional balls is captured in the boundary scan register.The user must be aware that the TAP controller clock can only operate at a frequency up to 20 MHz, while the SRAM clock operates more than an order of magnitude faster. Because there is a large difference in the clock frequencies, it is possible that during the Capture-DR state, an input or output may undergo a transition. The TAP may then try to capture a signal while in transition (metastable state). This does not harm the device, but there is no guarantee as to the value that is captured. Repeatable results may not be possible.To guarantee that the boundary scan register captures the correct value of a signal, the SRAM signal must be stabilized long enough to meet the TAP controller’s capture setup plus hold time (t CS plus t CH).The SRAM clock input might not be captured correctly if there is no way in a design to stop (or slow) the clock during a SAMPLE/PRELOAD instruction. If this is an issue, it is still。

ZC7310系列使用说明书

目录目录................................................................................................................................... - 1 -第一章概述 ......................................................................................................................... - 3 -1.1 使用条件 .............................................................................................................................................. - 4 -第二章操作规范和措施....................................................................................................... - 6 -2.1 操作规范 .............................................................................................................................................. - 6 -2.2 处理措施 .............................................................................................................................................. - 9 -第三章仪器面板概述......................................................................................................... - 11 -3.1 前面板说明 ........................................................................................................................................ - 11 -3.2 后面板说明 ........................................................................................................................................ - 13 -第四章操作说明 ................................................................................................................ - 14 -4.1 仪器界面结构描述 ............................................................................................................................ - 14 -4.2 测量显示界面(TEST界面)............................................................................................................ - 15 -4.2.1 测试结果界面--------------------------------------------------------------------------------------------------- - 16 -4.2.2 清零---------------------------------------------------------------------------------------------------------------- - 17 -4.3 测量设置界面 .................................................................................................................................... - 17 -4.3.1 交流耐压测试设置 -------------------------------------------------------------------------------------------- - 18 -4.3.2 直流耐压测试设置---------------------------------------------------------------------------------------------- - 21 -4.3.3 绝缘电阻测试设置 -------------------------------------------------------------------------------------------- - 24 -4.3.4 暂停模式测试设置 -------------------------------------------------------------------------------------------- - 27 -4.3.5 开路侦测测量设置 -------------------------------------------------------------------------------------------- - 28 -4.4 系统设置界面 .................................................................................................................................... - 29 -4.4.1 测试界面 --------------------------------------------------------------------------------------------------------- - 30 -4.4.2 环境界面 --------------------------------------------------------------------------------------------------------- - 34 -4.4.3 通讯设置界面--------------------------------------------------------------------------------------------------- - 35 -4.5 文件设置界面 .................................................................................................................................... - 36 -4.6 测试步骤 ............................................................................................................................................ - 37 -4.6.1 测试线/测试夹具清零---------------------------------------------------------------------------------------- - 37 -4.6.2 标准电容的采样 ----------------------------------------------------------------------------------------------- - 37 -4.6.3 连接被测件 ------------------------------------------------------------------------------------------------------ - 37 -4.6.4 测试程序 --------------------------------------------------------------------------------------------------------- - 38 -第五章接口与通讯 .......................................................................................................... - 40 -5.1 HANDLER接口 ................................................................................................................................... - 40 -5.1.1 外部控制线图例 ----------------------------------------------------------------------------------------------- - 41 -5.2 RS232C接口....................................................................................................................................... - 43 -5.2.1 与计算机通讯--------------------------------------------------------------------------------------------------- - 45 -5.2.2 软件协议 --------------------------------------------------------------------------------------------------------- - 45 -5.3 串口指令集说明 ................................................................................................................................ - 46 -5.3.1 SCPI指令集 ------------------------------------------------------------------------------------------------------ - 47 -5.3.2 DISPlay 子系统命令集-------------------------------------------------------------------------------------- - 47 -5.3.3 FUNCtion 子系统命令集 ------------------------------------------------------------------------------------ - 48 -5.3.4 SYSTem 子系统命令集 --------------------------------------------------------------------------------------- - 63 -5.3.5 MMEM 子系统命令集 --------------------------------------------------------------------------------------- - 71 -5.3.6 USB 子系统命令集-------------------------------------------------------------------------------------------- - 73 -5.3.7 FETCh 子系统命令集 ----------------------------------------------------------------------------------------- - 74 -5.3.8 其他控制命令集 ----------------------------------------------------------------------------------------------- - 75 -第六章技术指标 .............................................................................................................. - 76 -版本历史:本说明书将不断完善以利于使用。

BC107中文资料

Application information

Where application information is given, it is advisory and does not form part of the specification.

LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.

open emitter open base open collector

Tamb ≤ 25 °C

THERMAL CHARACTERISTICS

SYMBOL

PARAMETER

CONDITIONS

Rth j-a Rth j-c

thermal resistance from junction to ambient note 1 thermal resistance from junction to case

DESCRIPTION emitter base collector, connected to the case

CY7C1041CV33-10ZXI中文资料

Industrial

100

95

Automotive-A

100

Automotive-E

Commercial/

10

10

Industrial

Automotive-A

10

Automotive-E

48-ball FBGA

(Top View)

12

3

4

5

6

CY7C1041CV33

-15

-20

Unit

15

20

ns

80

28

A6, E3, G2, H1, No Connect No Connects. This pin is not connected to the die

H6

17

G5

Input/Control Write Enable Input, active LOW. When selected LOW, a

A5 18 A6 19 A7 20 A8 21 A9 22

44 A17 43 A16 42 A15 41 OE

40 BHE 39 BLE

38 I/O15 37 I/O14 36 I/O13 35 I/O12 34 VSS 33 VCC 32 I/O11 31 I/O10 30 I/O9 29 I/O8 28 NC

WRITE is conducted. When selected HIGH, a READ is

conducted.

6

ห้องสมุดไป่ตู้B5

Input/Control Chip Enable Input, active LOW. When LOW, selects the chip.

When HIGH, deselects the chip.

CY7C63723-PC中文资料