采用等精度测频原理的频率计的设计

《等精度频率计》课件

分析等精度频率计测量误差的主要来源,如信号源的频率稳定度、 计数器的计数误差等。

误差传递

研究误差在测量过程中的传递规律,为减小误差提供依据。

误差补偿

根据误差ห้องสมุดไป่ตู้析结果,采取相应的补偿措施,减小等精度频率计的测量 误差。

04

等精度频率计的性能测 试与评估

测试环境与设备

测试环境

实验室环境,确保电源稳定、温度适 宜、湿度适中。

应用领域拓展

通信领域

等精度频率计在通信领域的应用越来越广泛,如信号发生器、频 谱分析仪等。

测量测试

等精度频率计在测量测试领域的应用也越来越广泛,如时间频率测 量、电子元件测试等。

物联网领域

等精度频率计在物联网领域的应用也越来越广泛,如智能家居、智 能农业等。

未来发展方向

更高精度

随着科技的发展,对频率计的测量精度要求越来越高,未来等精 度频率计将向更高精度方向发展。

02

它采用等精度测量技术,消除了传统频率计由于时基不稳定而

引起的测量误差。

等精度频率计具有广泛的应用,如电子测量、通信、雷达、导

03

航等领域。

等精度频率计的原理

等精度频率计基于等精度测频 原理,采用高稳定的晶体振荡 器作为时基,对输入信号进行

计数和测量。

它通过计数输入信号在一定 时间内的周期数,再根据时 基的频率计算出输入信号的

宽测量范围

等精度频率计能够测量低频信 号和高频信号,测量范围较广 。

可扩展性

等精度频率计可以与其他测量 仪器进行集成,实现更复杂的 测量功能。

02

等精度频率计的应用

测量信号频率

测量信号频率是等精度频率计的基本 应用,它可以准确测量各种信号源的 频率,包括正弦波、方波、脉冲波等 。

实验二 数字频率计的设计

实验二数字频率计的设计一、实验目的1、了解等精度测频的方法和原理。

2、掌握数字频率计的设计方法。

3、掌握频率计误差分析方法。

二、实验原理所谓频率就是周期性信号在单位时间(1s)内变化的次数。

若在一定时间间隔T(也称闸门时间)内测得这个周期性信号的重复变化次数为N,则其频率可表示为f=N/T由上面的表示式可以看到,若时间间隔T取1s,则f=N。

由于闸门的起始和结束的时刻对于信号来说是随机的,将会有一个脉冲周期的量化误差。

进一步分析测量准确度:设待测信号脉冲周期为Tx,频率为Fx,当测量时间为T=1s时,测量准确度为δ=Tx/T=1/Fx。

由此可知这种直接测频法的测量准确度与被测信号的频率有关,当待测信号频率较高时,测量准确度也较高,反之测量准确度较低。

因此,这种直接测频法只适合测量频率较高的信号,不能满足在整个测量频段内的测量精度保持不变的要求。

若要得到在整个测量频段内的测量精度保持不变的要求,应该考虑等精度频率测量等其它方法。

等精度频率测频的实现方法,可以用图2-1所示的框图来实现。

图2-1 等精度测频实现框图所谓等精度是指该频率计在所测量的整个频段内部,均可实现相同精度的测量,即测量精度与频率无关。

图中预置门信号通常为1s。

其内部包括一个同步门电路,用来实现被测频标与被测频率的同步,提高测量精度,减少基本误差。

该部分与清零脉冲协调工作用来控制两个计数器的启动脉冲。

计数器1和计数器2分别用来给频标和被测数字脉冲计数,设在同步门控制结束时计数器1计数N1,计数器2计数N2,假设频标频率为F1,被测频率位Fx,则可写出公式:Fx/N2=F1/N1; (1)Fx=(F1/N1)* N2 (2)由公式可以看出,测量精度与预置门时间无关,主要由F1的频率稳定度来确定,所以为了提高测量精度,主要是提高频标的频率稳定度,换句话说,测量精度基本上近似于频标的稳定度。

在该电路中,为了确保频标计数与被测频率完全同步(即被测频率的上升沿开始计数,1s以后,被测频率的下跳沿停止计数),同步门必须由被测信号来控制,设计方法多种多样,可由学生独立完成。

等精度频率计的设计

测试原理图

图

等精度频率计主控结构图

Your company slogan

原理图2 原理图

图

等精度频率计主控结构图2 等精度频率计主控结构图

Your company slogan

主系统组成

图

频率计主系统电路组成

Your company slogan

VHDL 程序设计

Your company slogan

VHDL 程序

ELSIF TCLK'EVENT AND TCLK='1' THEN ENA<=CL; END IF; END PROCESS; MA<=(TCLK AND CL) OR NOT(TCLK OR CL); --测脉宽逻辑 测脉宽逻辑 CLK1<=NOT MA; CLK2<=MA AND Q1; CLK3<=NOT CLK2; SS<=Q2 & Q3; DD1 : PROCESS(CLK1, CLR) BEGIN IF CLR='1' THEN Q1<='0'; ELSIF CLK1'EVENT AND CLK1='1' THEN Q1<='1'; END IF; END PROCESS; DD2 : PROCESS(CLK2, CLR) BEGIN IF CLR='1' THEN Q2<='0'; ELSIF CLK2'EVENT AND CLK2='1' THEN Q2<='1'; END IF; END PROCESS; DD3 : PROCESS(CLK3, CLR) BEGIN IF CLR='1' THEN Q3<='0'; ELSIF CLK3'EVENT AND CLK3='1' THEN Q3<='1'; END IF; END PROCESS; PUL<=‘1’ WHEN SS=“10” ELSE --EEND为低电平时,表示正在记数,由低电平变为高电平 为低电平时, 为低电平时 表示正在记数, ‘0’; --时,表示记数结束,可以从标准计数器中读数据了 时 表示记数结束, EEND<='1' WHEN SS="11" ELSE '0'; BENA<=ENA WHEN SPUL=‘1’ ELSE --标准计数器时钟使能控制信号,当SPUL为1时,测频率 标准计数器时钟使能控制信号, 标准计数器时钟使能控制信号 为 时 PUL WHEN SPUL=‘0’ ELSE --当SPUL为0时,测脉宽和占空间比 当 为 时 PUL; Your company slogan END behav;

等精度频率计的研究与设计

高 新 技 术

C i aNe e h oo i s n rd cs hn w T c n l g d P o u t e a

等精 度频率计 的研究与设计 吴小 所 ’ Nhomakorabea冯 海

(、 1兰州交通 大学 , 肃 兰州 707 ; 、 甘 300 2 兰州 ̄-:学技 术工程学院 , Yk -. 甘肃 兰州 705) 300

摘 要 : 用等精 度频 率 测量 方 法具有 测量精 度保 持 恒定 , 随所测 信号 的 变化 而变化 的特 点。 文首先 综述 了E A技 术的发展 概 采 不 本 D 况 ,P A C L 开发 的涵 义 、 缺 点 , H FG / PD 优 V DL语 言 的历 史及 其优 点 , 述 了 E A软 件 平 台 QU KT 1; 概 D A US 1 然后介 绍 了频 率 测 量的 般 原 理 , 用 等精度 测 量原理 , 过 F G 利 通 P A运 用 V DL编程 , 用 F G ( 场 可编程 门阵列) 片设 计 了一 个 8 数 字式等 精度 频 H 利 P A现 芯 位 率 计 , 频 率计 的测 量 范围 为 0 IO 该 - OMHZ 利 用 QU KT I 。 A US I集成 开发 环境 进行 编辑 、 综合 、 形仿真 , 下栽到 C L 器件 中 , 波 并 PD 经 实际 电路 测 试 , 真和 实验 结 果表 明 , 频 率计有 较 高的 实用性 和 可靠性 。 仿 该 关键 词 : H V DL语 言 ; 等精 度 测量 ; 字频 率 计 数

一

中图分 类号 : 4 23 2 U 9 .+ 3

文 献标识 码 : A

1引言 。频 率 检测 是 电子测 量 领域 的最 会 由于 周期 性 的清 零信 号而 不 断 闪烁 。在每 基 本也 是最 重要 的测量 之一 。频 率 信号 抗 干 次测量开始时, 都必须重新对计数器清零。 扰能力强、 易于传输 , 可以获得较高的测量精 3 . 4锁存器模块。锁存器模块也是必不 度 , 以测频 方 法的研 究越 来越 受 到重 视 。 所 等 可 少 的 , 模块 测量 完成 后 , l d 号 的 测量 在 o 信 a 精度测量消除了对被测信号计数所产生的正 上升沿时刻将测量值锁存到寄存器中,然后 负1 误差 ,并 且 达 到 了在整 个测 试 频段 的等 输 出到 显示 模块 。 精度测量,测量信号的精度不随所测信号频 3 十进 制 计数 器 模 块 。计 数 器模 块 是 . 5 率 的变化 而 变化 。 由8 个带 有 异步 清 零端 ,进 位信 号输 出 的模 2等精度频率测量算法 。精度测频方法 为 l 的计 数模 块级 连 而成 。 十进 制计 数器 O 此 的 闸门 时间不 是 固定 的 值 ,而是 被测 信 号周 的 特殊之 处是 , 一时 钟使 能输入 端 E A, 有 N 用 期 的整 数 倍 , 即与 被 测 信 号 同步 , 因此 , 除 于锁 定计 数器 。 避 当高 电平计 数允 许 , 电平 时 低 了对被测信号计数所产生± 个字误差 , 1 并且 计数 禁止 。计 数器 模 块用 于对 输 入信 号 的脉 达到 了在 整个 测 试频 段 的等 精度 测 量 。在测 冲进 行计 数 , 模 块必 须 有计数 允 许 、 清 该 异步 量 过程 中 ,有 两个 计数 器 分别 对标 准 信号 和 零 等端 口, 于控 制模 块对 其进 行控 制 。 以便 被测信号同时计数 。首先给出闸门开启信号 3 . 示模 块 。 本设 计 中设 计 了一个 3 6显 在 ( 置 闸 门上 升 沿 ) 时计 数 器 并 不 开始 计 位 的循环 计数 器 , 数结 果 输入 到译 码 器 , 预 ,此 将计 数, 而是等到被测信号的上升沿到来时, 计数 译码结果输出即可依次使能每个 L D。 E 4 顶层 模 块设计 器才真正开始计数 。然后预置闸门关闭信号 ( 降 沿) 时 , 数器 并 不 立 即停 止 计 数 , 下 到 计 而 数字 频率 计 的顶层 文件 如 图 1 : 是等到被测 信号的上升沿到来 时才结 束计 在硬件电路上,用 F G P A取代传统的集 数 , 成一 次测 量过 程 。 完 成 电路 和单 片 机作 为 主要 载体 ,除 了输 入 和 3 设计 仿 真 与实 现 。本 设 计 实现 信号 源 输 出显 示 等少 数 电路外 , 它 大部 分 电路都 其 模 块 、 制 模 块 、 数 模块 、 控 计 锁存 器 模 块 和 显 可 以集 成 在一 片 F G P A芯片 中 ,大 大降 低 了 示 器模 块 5大模 块 , 面 分别 介 绍 三个 模块 电路 的复杂 程 度 、 小 了体 积 、 下 减 电路 工作 也更 的结构 和实 现 方法 。 加 可靠 和稳 定 , 也大 为提 高 。 速度 在开 发方式 31信号 源模块 。信号 源是 为 了产 生 上 ,用 自顶向下的的系统开发方法取代 了传 . 1 z的门控信号和待测的定频信号 ,而对 统 的 自下而 上 的硬 件堆 砌式 开 发模 式 。借助 MH 输 入 系统 时 钟 c (0 H ) 分 频 的模 块 , l 5 M z进行 k 设计源代码 PN1 ZV D 对输入系统时钟 I MH .H c (0 H ) 分 频产 生 1 z信 号 。 l 5 M z进行 k MH 3 分 频 器 模 块 。 此 程 序要 求将 1 H . 2 M Z 的 输入 频率 分 别进 行 2 分频 f 生 50 H 1 产 0K Z 的 输 出 频 f q 0k、3分 频 ( 生 15 K Z e5012 产 2 H 的 输 出 频 率 f q2 k、5 分 频 ( 生 r 15) e 2 产 320 Z的输 出频 f q 15)2 15 H r 320、7分频 ( e 产生 7 1H 82 Z的输 出频 率 fq 82、9分频 f r 7 1)2 e 产生 15H 93 Z的输 出频 率 fq 93、1 分频 ( 生 r 15)2 1 e 产 4 8 Z的输 出 频 率 f q8)23分 频 f 生 8H r 48、1 e 产

用51单片机完成等精度频率测量仪的设计毕业论文

(4)编写软件;

(5)系统调试,仿真。

2等精度频率计的原理与应用

2.1 等精度频率计的原理

频率计的核心为单片机对数据的运算处理,而此等精度测量方法是以同步门逻辑控制电路为核心的。同步门逻辑控制电路由D触发器构成。

基本频率测量要求:

幅度:0.5V~5V

频率:1Hz~500kHz

用51单片机完成等精度频率测量仪的设计毕业论文

1 绪 论

1.1 数字频率计简介

数字频率计是计算机、通讯设备、音频视频等科研生产领域不可缺少的测量仪器。它是一种用十进制数字,显示被测信号频率的数字测量仪器。它的基本功能是测量正弦信号,方波信号以及其他各种单位时间变化的物理量。在进行模拟、数字电路的设计、安装、调试过程中,由于其使用十进制数显示,测量迅速,精度高,显示直观,所以经常要用到数字频率计。

国际国通用数字频率计的主要技术参数:1.频率测量围:电子计数器的测频围,低端大部分从10Hz开始;高端则以不同型号的频率计而异。因此高端频率是确定低、中、高速计数器的依据。如果装配相应型号的变频器,各种类型的数字频率计的测量上限频率,可扩展十倍甚至几十倍。2.周期测量围:数字频率计最大的测量周期,一般为10s,可测周期的最小时间,依不同类型的频率计而定。对于低速通用计数器最小时间为1ys;对中速通用计数器可小到0.1ys。3.晶体振荡器的频率稳定度:是决定频率计测量误差的一个重要指标。可用频率准确度、日波动、时基稳定度、秒级频率稳定度等指标,来描述晶体振荡器的性能。4.输入灵敏度:输入灵敏度是指在侧频围能保证正常工作的最小输入电压。目前通用计数器一般都设计二个输入通道,即d通道和月通道。对于4通道来说,灵敏度大多为50mV。灵敏度高的数字频率计可达30mV、20mV。5.输入阻抗:输入阻抗由输入电阻和输入电容两部分组成。输入阻抗可分为高阻(1M//25PF、500k//30PF)和低阻(50)。一般说来,低速通用计数器应设计成高阻输入;中速通用计数器,测频围最高端低于100MHz,仍设计为高阻输入;对于高速通用计数器,测频>100MHz, 设计成低阻 (50Q) 输入,测频<100MHz,设计成高阻(500k//30PF)输入。

等精度法测频率计的原理

等精度法测频率计的原理引言:等精度法测频率计是一种常用的频率测量方法,它利用稳定的参考信号与待测信号进行比较,从而精确地测量待测信号的频率。

本文将介绍等精度法测频率计的原理及其工作流程。

一、原理概述:等精度法测频率计的原理基于频率比较技术,通过将待测信号与参考信号进行相位比较,从而得到待测信号的频率信息。

其核心思想是将待测信号与参考信号进行周期性的比较,通过计算比较结果的平均值来消除测量误差,从而提高测量精度。

二、工作流程:等精度法测频率计的工作流程主要包括以下几个步骤:1. 产生参考信号:首先需要产生一个稳定的参考信号,通常使用高稳定度的晶振或标准频率源作为参考信号源。

2. 将待测信号与参考信号进行比较:待测信号与参考信号经过相位比较,得到相位差信息。

3. 相位差计算:通过测量待测信号与参考信号的相位差,可以计算出待测信号的周期。

4. 周期计算:根据相位差计算出的周期信息,可以得到待测信号的频率。

5. 精度提高:为了提高测量精度,需要进行多次测量并取平均值,以消除测量误差。

三、关键技术说明:等精度法测频率计的实现需要借助一些关键技术,包括:1. 相位锁定技术:通过将待测信号与参考信号进行相位锁定,可以确保两者相位一致,从而实现准确的相位比较。

2. 周期计数器:周期计数器用于测量待测信号与参考信号的相位差,通过计数器的计数结果可以得到待测信号的周期信息。

3. 数字信号处理:为了提高测量精度,可以利用数字信号处理技术对测量结果进行滤波、平均等处理,以消除噪声和提高信号质量。

四、优缺点分析:等精度法测频率计具有以下优点:1. 高精度:通过多次测量并取平均值的方法,可以消除测量误差,提高测量精度。

2. 稳定性好:利用稳定的参考信号进行比较,可以保证测量结果的稳定性。

3. 适用范围广:等精度法测频率计适用于各种频率范围的信号测量,包括低频、中频和高频等。

然而,等精度法测频率计也存在一些缺点:1. 对参考信号要求高:由于等精度法测频率计依赖于参考信号的稳定性,因此对参考信号的要求比较高。

等精度频率计的实现

等精度频率计的实现频率测量在电子设计和测量领域中经常用到,因此对频率测量方法的研究在实际工程应用中具有重要意义。

常用的频率测量方法有两种:频率测量法和周期测量法。

频率测量法是在时间t 内对被测信号的脉冲数N 进行计数,然后求出单位时间内的脉冲数,即为被测信号的频率。

周期测量法是先测量出被测信号的周期T,然后根据频率f=1/T 求出被测信号的频率。

但是上述两种方法都会产生±1 个被测脉冲的误差,在实际应用中有一定的局限性。

根据测量原理,很容易发现频率测量法适合于高频信号测量,周期测量法适合于低频信号测量,但二者都不能兼顾高低频率同样精度的测量要求。

1 等精度测量原理等精度测量的一个最大特点是测量的实际门控时间不是一个固定值,而是一个与被测信号有关的值,刚好是被测信号的整数倍。

在计数允许时间内,同时对标准信号和被测信号进行计数,再通过数学公式推导得到被测信号的频率。

由于门控信号是被测信号的整数倍,就消除了对被测信号产生的±l 周期误差,但是会产生对标准信号±1 周期的误差。

等精度测量原理如图1 所示。

从以上叙述的等精度的测量原理可以很容易得出如下结论:首先,被测信号频率fx 的相对误差与被测信号的频率无关;其次,增大测量时间段软件闸门或提高标频f0,可以减小相对误差,提高测量精度;最后,由于一般提供标准频率f0 的石英晶振稳定性很高,所以标准信号的相对误差很小,可忽略。

假设标准信号的频率为100 MHz,只要实际闸门时间大于或等于1s,就可使测量的最大相对误差小于或等于10-8,即精度达到1/100 MHz。

2 等精度测频的实现等精度测量的核心思想在于如何保证在实际测量门闸内被测信号为整数个。

等精度频率计课程设计

等精度频率计课程设计一、课程目标知识目标:1. 学生能理解等精度频率计的基本原理,掌握频率、周期及其相互关系。

2. 学生能够运用已学过的电子元件知识,识别并说明等精度频率计中的关键电子元件及其作用。

3. 学生能够掌握等精度频率计的测量步骤和方法,并进行简单的数据处理。

技能目标:1. 学生能够通过小组合作,动手搭建简单的等精度频率计电路。

2. 学生能够运用等精度频率计进行实验测量,准确读取并记录数据。

3. 学生能够通过实验数据分析,解决实际问题,提升解决问题的能力。

情感态度价值观目标:1. 学生通过等精度频率计的学习,培养对物理科学的兴趣,提高探究精神和创新意识。

2. 学生在小组合作中,学会相互尊重、沟通协作,培养团队合作精神。

3. 学生通过实验认识到精确测量在实际应用中的重要性,培养严谨的科学态度和良好的实验习惯。

课程性质:本课程为电子技术及应用学科的教学内容,结合学生年级特点,注重理论知识与实践操作的相结合。

学生特点:学生处于高中阶段,具有一定的物理知识和电子元件基础,对实验操作感兴趣,但需进一步引导和培养实验技能。

教学要求:教师应注重理论与实践相结合,引导学生通过小组合作、实验探究等形式,提高学生的实践能力和创新能力。

在教学过程中,关注学生的个体差异,鼓励学生积极参与,使每位学生都能在课程中取得实际的学习成果。

通过课程目标的实现,为后续相关课程的学习打下坚实基础。

二、教学内容本课程教学内容主要围绕等精度频率计的原理、电路搭建、测量方法及数据处理等方面展开。

1. 理论知识:- 频率、周期概念及其关系- 等精度频率计的工作原理- 关键电子元件(如晶体振荡器、计数器、时钟等)的作用2. 实践操作:- 搭建等精度频率计电路- 实验操作步骤及注意事项- 数据的采集、处理与分析3. 教学大纲:- 第一章:等精度频率计基本原理1.1 频率与周期的关系1.2 等精度频率计的工作原理- 第二章:关键电子元件2.1 晶体振荡器的特性与应用2.2 计数器与时钟的作用- 第三章:实验操作与数据处理3.1 电路搭建与调试3.2 实验步骤与注意事项3.3 数据采集、处理与分析4. 教学进度安排:- 理论知识学习:2课时- 实践操作与实验:4课时- 数据处理与分析:2课时教学内容根据课程目标进行科学组织和系统安排,确保学生能够循序渐进地掌握等精度频率计的相关知识。

等精度频率计的研究与设计

等精度频率计的研究与设计作者:吴小所冯海来源:《中国新技术新产品》2011年第24期摘要:采用等精度频率测量方法具有测量精度保持恒定,不随所测信号的变化而变化的特点。

本文首先综述了EDA技术的发展概况,FPGA/CPLD开发的涵义、优缺点,VHDL语言的历史及其优点,概述了EDA软件平台QUARTUS Ⅱ;然后介绍了频率测量的一般原理,利用等精度测量原理,通过FPGA运用VHDL编程,利用FPGA(现场可编程门阵列)芯片设计了一个8位数字式等精度频率计,该频率计的测量范围为0-100MHZ。

利用QUARTUS Ⅱ集成开发环境进行编辑、综合、波形仿真,并下载到CPLD器件中,经实际电路测试,仿真和实验结果表明,该频率计有较高的实用性和可靠性。

关键词: VHDL语言;等精度测量;数字频率计中图分类号:U492.3+23 文献标识码:A1 引言。

频率检测是电子测量领域的最基本也是最重要的测量之一。

频率信号抗干扰能力强、易于传输,可以获得较高的测量精度,所以测频方法的研究越来越受到重视。

等精度测量消除了对被测信号计数所产生的正负1误差,并且达到了在整个测试频段的等精度测量,测量信号的精度不随所测信号频率的变化而变化。

2 等精度频率测量算法。

精度测频方法的闸门时间不是固定的值,而是被测信号周期的整数倍,即与被测信号同步,因此,避除了对被测信号计数所产生±1个字误差,并且达到了在整个测试频段的等精度测量。

在测量过程中,有两个计数器分别对标准信号和被测信号同时计数。

首先给出闸门开启信号(预置闸门上升沿),此时计数器并不开始计数,而是等到被测信号的上升沿到来时,计数器才真正开始计数。

然后预置闸门关闭信号(下降沿)到时,计数器并不立即停止计数,而是等到被测信号的上升沿到来时才结束计数,完成一次测量过程。

3 设计仿真与实现。

本设计实现信号源模块、控制模块、计数模块、锁存器模块和显示器模块5大模块,下面分别介绍三个模块的结构和实现方法。

基于FPGA的等精度频率计的设计

基于FPGA的等精度频率计的设计一、引言频率计是一种广泛应用于电子领域的仪器设备,用于测量信号的频率。

常见的频率计有软件频率计和硬件频率计两种。

软件频率计主要基于计算机软件,通过采集到的信号数据来计算频率。

硬件频率计则是基于专用的硬件电路,直接对信号进行采样和处理,具有实时性强、准确度高的优点。

本文将基于FPGA设计一种等精度频率计,旨在实现高精度、高稳定性的频率测量。

二、设计原理本设计采用基于FPGA的硬件频率计方案,其主要原理是通过对输入信号的时间计数,并结合固定参考值,计算出信号的频率。

具体流程如下:1.信号输入:将待测量的信号输入至FPGA芯片,输入信号的幅度应符合输入电平范围。

2.信号计数:利用FPGA芯片内部的计数器,对输入信号进行计数,并记录计数器的数值。

计数器的值与输入信号的频率成反比,即计数器值越大,信号频率越低。

3.定时器触发:通过定时器产生一个固定的参考信号,用于触发计数器的复位操作。

定时器的频率应足够高,以保证计数器能够实时精确计数。

4.数据处理:计数器值与定时器触发的时间周期共同决定了输入信号的频率。

通过计算参考值与计数器值的比例,可以得到准确的频率值。

5.结果输出:将计算得到的频率值输出至显示屏或其他外部设备,以便用户进行查看。

三、设计方案1.FPGA选型:选择一款适合频率计设计的FPGA芯片,要求其具有较高的计数能力、较大的存储空间和丰富的外设接口。

2.输入电路设计:设计一个合适的输入电路,将待测信号进行电平调整和滤波处理,以确保输入信号的稳定性和合适的幅度范围。

3.计数器设计:利用FPGA内部的计数器模块,进行计数操作。

根据需要选择适当的计数器位宽,以满足待测频率范围的要求。

4.定时器设计:通过FPGA内部的时钟源和计时器模块,设计一个精确的定时器,用于触发计数器的复位操作。

定时器的频率要足够高,以保证计数的准确性。

5.数据处理设计:利用FPGA内部的算数逻辑单元(ALU)对计数器值进行处理,计算得到准确的频率值。

等精度频率计的设计

等精度频率计的设计一、实验原理基于传统测频原理的频率计的测量精度将随被测信号频率的下降而降低,即测量精度随被测信号的频率的变化而变化,在实用中有较大局限性,而等精度频率计不但具有较高的测量精度,且在整个频率区域能保持恒定的测试精度。

设计项目可达到的指标如下:频率测试功能:测频范围0.1Hz~100Hz。

测频精度:测频全域相对误差恒为百万分之一。

脉宽测试功能:测试范围:0.1us~1s,测试精度1%~99%。

占空比测试功能:测试(显示)精度1%~99%。

相位测试功能:测试范围0~360度,测试精度0.2度。

主系统组成等精度频率计的主系统由六个部分组成:信号整形电路。

用于对待测信号进行放大和整形,以便作为PLD器件的输入信号。

测频电路。

是测频的核心模块,可以由FPGA器件担任。

100MHz的标准频率信号源(可通过PLL倍频所得)进入FPGA.。

单片机电路模块。

用于控制FPGA的测频操作和读取测频数据,并作出相应数据处理。

安排单片机的P0口读取测试数据,P2口向FPGA发控制命令。

键盘模块。

可以用5个键执行测试控制,一个是复位键,其余是命令键。

数码显示模块。

可以用7个数码管显示测试结果,最高可表示百万分之一的精度。

考虑到提高单片机IO口的利用率,降低编程复杂性,提高单片机的计算速度以及降低数码显示器对主系统的干扰,可以采用串行静态显示或液晶显示方式。

主系统组成测频原理等精度测频原理为:“预置门控信号”CL由单片机发出,可以证明,在1秒至0.1秒间的选择范围内,CL的时间宽度对测频精度几乎没有影响,在此设其T。

BZH和TF模块是两个可控的32位高速计数器,BENA和ENA分别是宽度为p它们的计算允许信号端,高电平有效。

标准频率信号从BZH 的时钟输入端BCLK 输入,设其频率为s F ;经整形后的被测信号从与BZH 相似的32位计数器TF 的时钟输入端TCLK 输入,设其真实频率值为xe F ,被测频率为x F 。

一种高性价比等精度数字频率计方案设计

一种高性价比等精度数字频率计方案设计引言频率的概念就是1 s 时间内被测信号的周期个数,最直接的测量方法就是单位时间内计数法,这种方法比较适合高频测量。

低频通常用测周期法。

这两种方法的测量精度不固定,与被测信号的范围相关。

等精度频率测量法融合以上两种方法的优点,可兼顾低频与高频信号;但较以上两种方法而言,等精度频率测量有较高的测量精度,且误差不会随着被测信号频率的改变而改变。

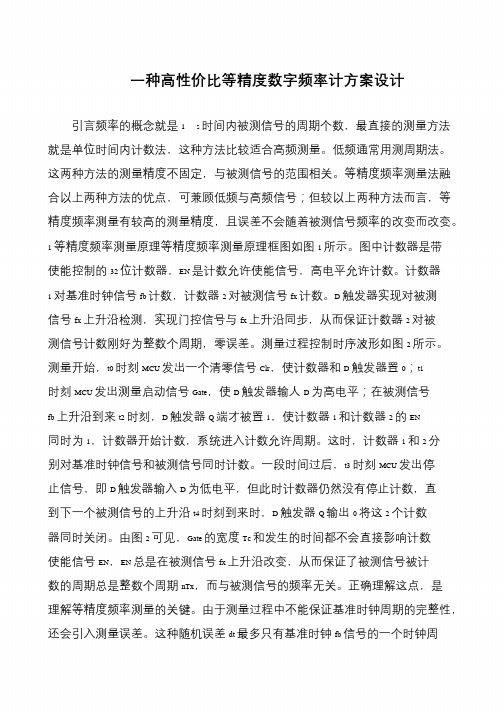

1 等精度频率测量原理等精度频率测量原理框图如图1 所示。

图中计数器是带使能控制的32 位计数器,EN 是计数允许使能信号,高电平允许计数。

计数器1 对基准时钟信号fb 计数,计数器2 对被测信号fx 计数。

D 触发器实现对被测信号fx 上升沿检测,实现门控信号与fx 上升沿同步,从而保证计数器2 对被测信号计数刚好为整数个周期,零误差。

测量过程控制时序波形如图2 所示。

测量开始,t0 时刻MCU 发出一个清零信号Clr,使计数器和D 触发器置0;t1 时刻MCU 发出测量启动信号Gate,使D 触发器输人D 为高电平;在被测信号fb 上升沿到来t2 时刻,D 触发器Q 端才被置1,使计数器1 和计数器2 的EN 同时为1,计数器开始计数,系统进入计数允许周期。

这时,计数器1 和2 分别对基准时钟信号和被测信号同时计数。

一段时间过后,t3 时刻MCU 发出停止信号,即D 触发器输入D 为低电平,但此时计数器仍然没有停止计数,直到下一个被测信号的上升沿t4 时刻到来时,D 触发器Q 输出0 将这2 个计数器同时关闭。

由图2 可见,Gate 的宽度Tc 和发生的时间都不会直接影响计数使能信号EN,EN 总是在被测信号fx 上升沿改变,从而保证了被测信号被计数的周期总是整数个周期nTx,而与被测信号的频率无关。

正确理解这点,是理解等精度频率测量的关键。

由于测量过程中不能保证基准时钟周期的完整性,还会引入测量误差。

这种随机误差dt 最多只有基准时钟fb 信号的一个时钟周。

等精度频率计设计

等精度频率计设计一、设计原理:测试频率的基本方法包括直接测频法和测周法。

其中直接测频法是产生一个标准宽度(例如1s)的时基信号,然后在这个信号时间范围内打开闸门对被测频率信号进行计数。

此方法的弱点之一是高精度的标准时基信号不容易获得;其二这种方法对于高频信号有保证,但对于低频信号由于计数周期有限测试精度较低。

测周法是用被测信号作为闸门信号、对标准脉冲信号进行计数,显然这种方法适合测量低频信号的频率。

等精度测频法的核心思想是用两个计数器分别对标准脉冲和被测脉冲在相同时间内进行计数,计数时间严格同步于被频脉冲。

这种方法的最大优点是测试的精度和被测信号的频率无关,因而可以做到等精度测量。

其测试原理所示:二、等精度测频误差分析:设在一次实际的闸门时间τ以内记得被测信号和标准信号的计数值分别为N x和N s,标准信号的频率为Fs,则被测信号的频率为:若被测信号的实际频率为Fxe ,则测量误差为:由于实际闸门完全同步于被测脉冲,因此t=N x T x(其中为被测信号的周期)。

而对T s的计数则最多相差1。

所以被测信号真实的频率可以表示为:由以上各式可以得到:误差与被测频率无关,因而称为等精度测频。

三、系统框图:四、系统组成:(1)FPGA测频电路:是测频的核心电路模块,由FPGA器件组成。

(2)单片机电路模块:用于控制FPGA的测频操作和读取测频数据,并做出相应处理。

(3)数码显示模块:用8个数码显示测试结果,并采用串行静态显示方法五、FPGA模块:顶层文件波形仿真六、单片机模块:七、心得:附录一:FPGA程序LIBRARY IEEE;--D_FF程序USE IEEE.STD_LOGIC_1164.ALL;ENTITY D_FF ISPORT ( CLK,D,CLR : IN STD_LOGIC;Q : OUT STD_LOGIC);END D_FF;ARCHITECTURE behav OF D_FF ISBEGINPROCESS (CLK,CLR)V ARIABLE Q1:STD_LOGIC;BEGINIF CLR='1' THEN Q1:='0';ELSIF CLK'EVENT AND CLK='1' THENQ1:=D;END IF;Q<=Q1;END PROCESS;END behav;LIBRARY IEEE;--BZH程序USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY BZH ISPORT ( BENA,BCLK,CLR : IN STD_LOGIC;BZQ : OUT STD_LOGIC_VECTOR(31 DOWNTO 0)); END BZH;ARCHITECTURE behav OF BZH ISBEGINPROCESS (BCLK,CLR,BENA)V ARIABLE BZQ1:STD_LOGIC_VECTOR(31 DOWNTO 0);BEGINIF CLR='1' THEN BZQ1:=(OTHERS =>'0');ELSIF BCLK'EVENT AND BCLK='1' THENIF BENA='1' THENBZQ1:=BZQ1+1;END IF;END IF;BZQ<=BZQ1;END PROCESS;END behav;LIBRARY IEEE;--TF 程序USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY TF ISPORT ( ENA,TCLK,CLR : IN STD_LOGIC;TSQ : OUT STD_LOGIC_VECTOR(31 DOWNTO 0)); END TF;ARCHITECTURE behav OF TF ISBEGINPROCESS (TCLK,CLR,ENA)V ARIABLE TSQ1:STD_LOGIC_VECTOR(31 DOWNTO 0);BEGINIF CLR='1' THEN TSQ1:=(OTHERS =>'0');ELSIF TCLK'EVENT AND TCLK='1' THENIF ENA='1' THENTSQ1:=TSQ1+1;END IF;END IF;TSQ<=TSQ1;END PROCESS;END behav;LIBRARY IEEE;--MUX64_8 程序USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY MUX64_8 ISPORT ( SEL : IN STD_LOGIC_VECTOR(2 DOWNTO 0);BZQ : IN STD_LOGIC_VECTOR(31 DOWNTO 0);TSQ : IN STD_LOGIC_VECTOR(31 DOWNTO 0);DATA : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); END MUX64_8;ARCHITECTURE behav OF MUX64_8 ISBEGINDATA <= BZQ(7 DOWNTO 0) WHEN SEL="000" ELSE BZQ(15 DOWNTO 8) WHEN SEL="001" ELSEBZQ(23 DOWNTO 16) WHEN SEL="010" ELSEBZQ(31 DOWNTO 24) WHEN SEL="011" ELSETSQ(7 DOWNTO 0) WHEN SEL="100" ELSETSQ(15 DOWNTO 8) WHEN SEL="101" ELSETSQ(23 DOWNTO 16) WHEN SEL="110" ELSETSQ(31 DOWNTO 24);END behav;附录二:单片机程序#include <reg51.h>sbit clr=P2^3;sbit cl=P2^4;sbit start=P2^5;unsigned long fx,fs=199981300,save;unsigned char code led_tab[]={0xfc,0x60,0xda,0xf2,0x66,0xb6,0xbe,0xe0,0xfe,0xf6,0x01,0x00};//LED数码管显示0123456789.共阴反向送数void delay(unsigned char z);void send(unsigned char m);void display(unsigned long n);struct p2_control{unsigned sel:3;}dat;void main(){unsigned long nx=0,ns=0,input=0;while(1){cl=0;clr=0; //初始化clr=1;delay(1);clr=0; //清零cl=1;delay(2000);cl=0; //产生闸门信号clif (start!=0){for(dat.sel=0;dat.sel<8;dat.sel++){P2=dat.sel;delay(1);input=P0;switch(dat.sel){case 0 : ns=ns+input;break;case 1 : ns=ns+(input<<8);break;case 2 : ns=ns+(input<<16);break;case 3 : ns=ns+(input<<24);break;case 4 : nx=nx+(input);break;case 5 : nx=nx+(input<<8);break;case 6 : nx=nx+(input<<16);break;case 7 : nx=nx+(input<<24);break;}}}fx=(nx/ns)*fs;// while(fx==save);// save=fx;display(fx);}}void delay(unsigned char z) //1ms延迟{unsigned int x,y;for(x=z;x>0;x--)for(y=124;y>0;y--);}void display(unsigned long n) //显示,单位为Hz {int c;for(c=0;c<8;c++) //去余辉{send(11);}send(n/10000000);n=n%10000000;send(n/1000000); n=n%1000000;send(n/100000); n=n%100000;send(n/10000); n=n%10000;send(n/1000); n=n%1000;send(n/100); n=n%100;send(n/10); n=n%10;send(n);}void send(unsigned char m) //发送位数{TI=0;SBUF=led_tab[m];while(TI==0);delay(1);}。

等精度测频课程设计

等精度测频课程设计一、课程目标知识目标:1. 学生能理解等精度测频的基本概念,掌握其计算公式及原理。

2. 学生能运用等精度测频方法,对给定的频率信号进行准确测量,并计算出相应的频率值。

3. 学生能了解等精度测频在实际应用中的优缺点,并掌握其改进方法。

技能目标:1. 学生能够熟练操作等精度测频实验设备,进行实验数据的采集和处理。

2. 学生能够运用数学知识和物理原理分析等精度测频的误差来源,并提出相应的解决方案。

3. 学生能够通过小组合作,共同完成等精度测频实验,提高团队协作能力。

情感态度价值观目标:1. 学生能够认识到测量技术在科学研究和国民经济发展中的重要性,增强社会责任感和使命感。

2. 学生在实验过程中,能够培养严谨、细心的科学态度,提高实验操作的规范性和安全性。

3. 学生通过等精度测频的学习,能够体会到团队合作的力量,培养团结协作、共同进步的精神。

课程性质:本课程为物理学科实验课程,旨在帮助学生掌握等精度测频的基本原理和实际应用,提高学生的实验操作能力和科学素养。

学生特点:本课程针对的是高中二年级学生,他们已经具备了一定的物理知识和实验技能,但需进一步培养实验操作规范性和数据分析能力。

教学要求:教师应注重理论与实践相结合,引导学生通过小组合作、自主探究等方式,掌握等精度测频的相关知识和技能。

在教学过程中,关注学生的情感态度价值观的培养,使他们在学习过程中形成良好的科学素养。

二、教学内容1. 理论知识:- 等精度测频的基本原理- 频率测量的误差分析- 等精度测频的改进方法2. 实践操作:- 等精度测频实验设备的认识与使用- 实验数据的采集、处理与分析- 小组合作完成实验任务,提高团队协作能力3. 教学大纲:- 第一课时:介绍等精度测频的基本原理,使学生理解并掌握其计算公式。

- 第二课时:学习频率测量的误差分析,引导学生分析误差来源并探讨改进方法。

- 第三课时:认识等精度测频实验设备,教授操作规范,确保实验安全。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

采用等精度测频原理的频率计的设计一.设计要求1.设计一个用等精度测频原理的频率计。

2.频率测量测量范围1~9999;3.用4位带小数点数码管显示其频率;二.测频原理及误差分析1.常用的直接测频方法主要有测频法和测周期法两种。

2.测频法就是在确定的闸门时间Tw内,记录被测信号的变化周期数(或脉冲个数)Nx,则被测信号的频率为:fx=Nx/Tw。

3.测周期法需要有标准信号的频率fs,在待测信号的一个周期Tx内,记录标准频率的周期数Ns,则被测信号的频率为:fx=fs/Ns。

4.这两种方法的计数值会产生±1个字误差,并且测试精度与计数器中记录的数值Nx或Ns有关。

为了保证测试精度,一般对于低频信号采用测周期法;对于高频信号采用测频法,因此测试时很不方便,所以人门提出等精度测频方法。

5.等精度测频方法是在直接测频方法的基础上发展起来的。

6.它的闸门时间不是固定的值,而是被测信号周期的整数倍,即与被测信号同步,因此,测除了对被测信号计数所产生±1个字误差,并且达到了在整个测试频段的等精度测量。

等精度测频原理波形图7.在测量过程中,有两个计数器分别对标准信号和被测信号同时计数。

8.首先给出闸门开启信号(预置闸门上升沿),此时计数器并不开始计数,而是等到被测信号的上升沿到来时,计数器才真正开始计数。

然后预置闸门关闭信号(下降沿)到时,计数器并不立即停止计数,而是等到被测信号的上升沿到来时才结束计数,完成一次测量过程。

可以看出,实际闸门时间τ与预置闸门时间τ1并不严格相等,但差值不超过被测信号的一个周期9.设在一次实际闸门时间τ中计数器对被测信号的计数值为Nx,对标准信号的计数值为Ns。

10.标准信号的频率为fs,则被测信号的频率为11.由式(1)可知,若忽略标频fs的误差,则等精度测频可能产生的相对误差为12.δ=(|fxc-fx|/fxe)×100% (2)13.其中fxe为被测信号频率的准确值。

14.δ=|ΔNs|/Ns≤1/Ns=1/(τ·fs)⏹由上式可以看出,测量频率的相对误差与被测信号频率的大小无关,仅与闸门时间和标准信号频率有关,即实现了整个测试频段的等精度测量。

⏹闸门时间越长,标准频率越高,测频的相对误差就越小。

⏹标准频率可由稳定度好、精度高的高频率晶体振荡器产生,在保证测量精度不变的前提下,提高标准信号频率,可使闸门时间缩短,即提高测试速度。

等精度测频的实现方法可简化为下图所示的框图三.设计步骤⏹CNT1和CNT2是两个可控计数器,标准频率(fs)信号从CNT1的时钟输入端CLK输入;经整形后的被测信号(fx)从CNT2的时钟输入端CLK输入。

⏹每个计数器中的CEN输入端为时钟使能端控制时钟输入。

⏹当预置门信号为高电平(预置时间开始)时,被测信号的上升沿通过D触发器的输出端,同时启动两个计数器计数;同样,当预置门信号为低电平(预置时间结束)时,被测信号的上升沿通过D触发器的输出端,同时关闭计数器的计数。

系统组成⏹系统由分频器、计数器1、计数器2、D触发器等组成。

⏹分频器出来的信号作为等精度测频原理的预置闸门信号。

⏹其中D触发器,计数器2和计数器1的作用与前2页图中所示相同。

⏹运算模块就是完成公式(1)的运算。

⏹复位主要对分频、计数器1和计数器2进行清零操作。

采用等精度测频原理的频率计的程序与仿真--文件名:PLJ.vhd。

--功能:4位显示的等精度频率计。

--最后修改日期:2004.4.14。

library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity PLJ isport(clk:in std_logic; --基准时钟(10KHz)tclk:in std_logic;--被测信号 start:in std_logic; --复位信号 alarm0,alarm1:out std_logic; --超量程,欠量程显示dian:out std_logic_vector(3 downto 0); --小数点data1:out integer range 0 to 9999);--频率数据end PLJ;architecture behav of PLJ issignal q:integer range 0 to 9999; --预置闸门分频系数signal q1:integerrange 0 to 10000;--被测信号计数器signal q2:integer range 0 to 20000; --基准信号计数器signal en,en1:std_logic; --预置闸门,实际闸门signal qq,qqq:integer range0 to 200000000; --运算器signal data0:integer range 0 to 9999; --频率数据中间信号beginprocess(clk)--此进程得到一个预置闸门信号beginif clk'event andclk='1' thenif start='1' then q<=0;en<='0';elsifq=9999 then q<=9999;en<='0';else q<=q+1;en<='1';endif;end if;end process;process(tclk) --此进程计被测信号脉冲数,和得到一个实际闸门信号beginif tclk'event and tclk='1' thenif start='1' thenq1<=0;en1<='0';elsif en='1' then q1<=q1+1;en1<='1';else en1<='0';end if;end if;end process;process(clk) --此进程完成在实际闸门时间内,计基准脉冲数beginif clk'event and clk='1' thenif start='1' then q2<=0;elsif en1='1' thenifq2=20000 then q2<=20000;else q2<=q2+1;end if;end if;endif;end process;process(clk) --此进程完成等精度频率计的运算beginif clk'eventand clk='1' thenif start='1' then data0<=0;dian<="0000";alarm0<='0';alarm1<='0';q qq<=0;qq<=00;elsif en1='0' thenif q1>=1000 then qq<=q1*10000; --根据q1的大小来判断小数点的位置if qqq<qq then qqq<=qqq+q2;data0<=data0+1;dian<="0000";完成数据运算elsifdata0>=10000then alarm0<='1';--超量程显示else data1<=data0;end if;elsif q1>=100 then qq<=q1*100000;if qqq<qq then qqq<=qqq+q2;data0<=data0+1;elsif data0>=10000 then data1<=1000;dian<="0000";else data1<=data0;dian<="0010";end if;elsif q1>=10 then qq<=q1*1000000;if qqq<qqthen qqq<=qqq+q2;data0<=data0+1;elsif data0>=10000 then data1<=1000;dian<="0010";else data1<=data0;dian<="0100";end if;elsif q1>=1 then qq<=q1*10000000;if qqq<qqthen qqq<=qqq+q2;data0<=data0+1;elsifdata0>=10000 then data1<=1000;dian<="0100";else data1<=data0;dian<="1000";end if;end if;elsif q2>19999 then alarm1<='1';--欠量程显示else alarm1<='0';end if;end if;end process;end behav;附录等精度频率计仿真图—欠量程等精度频率计仿真图—超量程等精度频率计仿真图—5tclk=clk等精度频率计仿真图—9tclk=clk等精度频率计仿真图—50tclk=clk等精度频率计仿真图—80tclk=clk等精度频率计仿真图—300tclk=clk等精度频率计仿真图—1000tclk=clk等精度频率计仿真图—5000tclk=clk等精度频率计仿真图—6000tclk=clk等精度频率计仿真图—10000tclk=clk。