FPGA多功能电子钟

【优秀WORD论文】基于FPGA的全功能万年历电子钟的设计

基于FPGA的全功能万年历电子钟的设计提要本文主要介绍了基于FPGA的万年历电子钟的设计方案,从而介绍了可编程逻辑器件的发展及应用。

基于FPGA的电子钟的设计与实现介绍了基于FPGA芯片的系统设计,并对系统的软硬件构成、FPGA内部逻辑设计工作原理等进行了详细说明。

论文第一部分对FPGA进行概述,讲述了可编程逻辑器件的发展与应用及论文题目的意义、目的和内容编排;第二部分:叙述了系统设计方案,介绍了FPGA应用的特点和电子钟的方案概述及实现语言和调试平台MAX+plusⅡ开发工具;第三部分:叙述了基于FPGA的电子钟系统的设计的硬件设计和软件设计;第四部分:对系统实现的外围电路进行概述。

第五部分:再次说明本设计的系统方案和得到的结论。

目录第一章序论 (1)1.1研究目的和意义: (1)1.2可编程逻辑器件的发展与应用: (1)1.2.1可编程逻辑单元CLB (3)1.2.2输入/输出模块IOB (3)1.2.3可编程内部连线PI (4)1.2.4 FPGA芯片的特点 (4)1.3FPGA国内外的发展状况及应用 (5)1.4本课题所能实现的功能: (8)第二章总体方案的设计 (9)2.1万年历电子钟的设计原理: (9)2.2FPGA的设计方法 (11)2.2.1 FPGA的器件设计流程 (11)2.2.2 MAX+plusⅡ开发工具 (13)2.2.3 VHDL语言 (17)2.3系统设计方案 (18)第三章系统的硬件设计与实现 (19)3.1功能模块设计 (19)3.2系统功能实现 (21)3.2.1底层元件设计 (22)3.2.2顶层元件设计 (32)3.3芯片的选择 (41)第四章设计应用电路 (45)4.1整体电路 (45)4.2电源电路 (46)4.3键盘部分 (49)4.4主动配置电路 (53)第五章总结 (61)5.1概述: (61)5.2设计方案: (62)参考文献 (64)致谢 (67)摘要 (I)ABSTRACT (II)第一章序论1.1研究目的和意义:通过对FPGA的了解,我们要应用FPGA来设计全功能万年历的设计,主要实现电子钟的所有功能,万年历是一种应用非常广泛的日常计时工具,具有时分秒计时功能,还有日历、年历功能,涉及计数、显示、参数输入技术,能够实时显示年、月、日和时间,并具有校准和闹铃等功能。

基于FPGA的电子钟设计报告

基于FPGA的电子钟设计报告一、FPGA的基本知识1、可编程逻辑器件的概况可编程逻辑器件主要分为FPGA和CPLD 两种,两者的功能基本相同。

FPGA--现场可编程门阵列的简称CPLD--复杂可编程逻辑器件的简称2、FPGA芯片及其最小系统(1)FPGA芯片它的外形与普通嵌入式处理器芯片相同采用PGA(Organic pin grid Array,有机管脚阵列)的封装形式,但可以通过烧写特殊程序改变其内部结构,实现专门的电路功能。

基于FPGA的数字时钟2019-11-23 21:36·电力源动一、FPGA的基本知识1、可编程逻辑器件的概况可编程逻辑器件主要分为FPGA和CPLD 两种,两者的功能基本相同。

FPGA--现场可编程门阵列的简称CPLD--复杂可编程逻辑器件的简称它的外形与普通嵌入式处理器芯片相同采用PGA(Organic pin grid Array,有机管脚阵列)的封装形式,但可以通过烧写特殊程序改变其内部结构,实现专门的电路功能。

二、FPGA的设计方法1、编程语言FPGA的主流程序设计语言主要有VHDL语言与Verilog语言两种。

本课题采用VHDL语言进行编写。

VHDL--用简洁明确的源代码来描述复杂的逻辑控制。

它具有多层次的设计描述功能,层层细化,最后可直接生成电路级描述。

Verilog--一种基本语法与C语言相近,相比较于C语言更容易理解,2、图形化程序设计(设计效率低)三、软件开发环境QuartusII是Altera提供的FPGA开发集成环境,它提供了一种与结构无关的设计环境,使设计者能方便地进行设计输入、快速处理和器件编程。

它完全支持VHDL设计流程,其内部嵌有VHDL逻辑综合器。

四、数字钟功能模块认识数字时钟的设计采用了自顶向下分模块的设计。

底层是实现各功能的模块,各模块由VHDL语言编程实现顶层采用原理图形式调用。

具体的设计框图:各模块原理剖析:(1)在七段数码管上具有时--分--秒的依次显示;(2)时、分、秒的个位记满十向高位进一,分、秒的十位记满五向高位进一,小时按24进制计数,分、秒按60进制计数;(3)整点报时,当计数到整点时扬声器发出响声;(4)时间设置:可以通过按键手动调节秒和分的数值。

基于FPGA数字系统设计实例

x(n)

z-1

z-1

z-1

h(0)

h(1)

h(2)

h(N-2)

h(N-1) y(n)

图12-9 直接型FIR滤波器结构示意图

x(n)

z-1

z-1

z-1

z-1

z-1

z-1

z-1

W

W h(0)

W h(1)

W h(2)

W h(3)

W h(3)

W h(2)

W h(1)

W h(0)

+

W y(n)

图12-10 直接型FIR滤波器实现方案 如图12-11所示的结构来实现滤波器,在这种结构中,滤波器 的输出可写成下面的形式:

在功能4模式时,用作时、分、秒的数字调整,按一下,将 会使当前按键2选择的位置的数字加1。

系统的设计方案如图:

按键3 按键2 按键1

FPGA

时间显示

分

选择位模块

频

模

块

显

数

示

码

模

管

块

组

秒表模块

时间及设置

闹钟模块

控制模块

图12-2 多功能数字钟的设计方案

2基于FPGA的信号发生器的设计

2.1系统设计要求

1 基于 FPGA 的多功能数字钟的设计

1.1系统设计要求

多功能数字钟的设计要求如下: (1)能够正常显示时间信息,包括小时、分钟、秒; (2)能够设置与调整时间; (3)具有闹钟显示与设置功能; (4)具有秒表功能; (5)利用数码管显示。

1.2系统设计方案

时间、状态等功能的显示

按键1 按键2 按键3

MATLAB软件仿真的滤波器的抽头系数为:0.0036,-0.0127 ,0.0417,-0.0878,0.1318,0.8500,0.1318,-0.0878,

学习笔记-fpga设计电子时钟(12864显示)

fpga设计电子时钟(12864显示)设计心得:1,进行分块设计,类似调用函数,脉冲使能2,充分了解fpga的并行特性(c程序的串行特性,不能并行处理,线性:只有完成了当前任务,才能进行下一个任务)设计问题:1,似乎读有问题,在char_LR=1时,写的数据为汉字(程序中时间没有更改,主要为了调试看波形)实际板子验证时,将LCD_clk模块中的分频调为50到100kHz左右整体架构功能模块液晶初始化时序parameter Idle =8'b0000_0001,Basic_com =8'b0000_0010, //basic instruction:0x30Disp_set =8'b0000_0100, //set show curse blingDDRAM_clear =8'b0000_1000, //colunm address XWait_clear =8'b0001_0000,Point_set =8'b0010_0000,Show_on =8'b0100_0000,Stop=8'b1000_0000;写字符的时序由于字符属于半宽字形,且DDRAM形式下,每行只有8个地址,而字符可以写16个,因此用下面三个来表示写的地址:i nput [1:0] Y, //row 0-3i nput [2:0] X, //clunm 0-7i nput LR, //0/1因此当LR=0时,直接写地址,然后写一个字符编码即可LR=1时,先写地址,读出高位数据,然后写入两个字节(读出的数据,要写的数据)parameter Idle =8'b0000_0001,DDRAM =8'b0000_0010, //drawing modeW_addr =8'b0000_0100, //row address YDummy =8'b0000_1000, // not really readingR_data =8'b0001_0000, //reading high byte dataW0_data =8'b0010_0000,W1_data =8'b0100_0000,Stop =8'b1000_0000;# t1: 0 t2: 2305, T: 10,n_init: 38 # t1: 2305 t2: 2665, T: 10,n_char: 6 # t1: 2665 t2: 3265, T: 10,n_char: 10完成了上述工作,就可以设计一个简单的电子时钟,其要求如下:在屏幕上显示时间00:00:00要动态走(主要就是控制脉冲信号的产生)设计思路:100:00:0023LCD更新数据显示00:00:0100:01:591代码/*sign.v//creat the control signclock h:m:s*/module sign(//module LED(input lcd_clk, //100kHzinput sys_rst,output reg lcd_char_en,output reg lcd_init_en,output reg [7:0]char_data,output reg [2:0]char_X,output reg [1:0]char_Y,output reg char_LR);parameter T_w_char = 5,T_lcd_init = 40;reg [47:0] time_out;/* 1s */reg [16:0] cnt_s;reg [5:0] cnt0_clk;reg [3:0] cnt1_clk;reg [2:0] cnt_char;reg [5:0] sec,min;reg [4:0] hour;reg flag_s,flag_init;always @ (posedge lcd_clk or negedge sys_rst) begin //100kHz if(!sys_rst)begincnt_s <=0;cnt0_clk<=0;cnt1_clk<=0;cnt_char<=0;sec <=0;min <=0;hour <=0;flag_s <=0;flag_init <=1'b1;char_Y <= 2'b10;endelsebeginif(cnt_s == (40-1))begincnt_s <=0;flag_s<=1'b1;data_deal; //taskendelsecnt_s <=cnt_s+1'b1;if(flag_init)begincnt0_clk <= cnt0_clk +1'b1;case(cnt0_clk)1 : begin lcd_init_en <=1'b0; end2 : begin lcd_init_en <=1'b1; end3 : begin lcd_init_en <=1'b1; end4 : begin lcd_init_en <=1'b0; endT_lcd_init: beginflag_init <=0;cnt0_clk <=0;enddefault: lcd_init_en <=0;endcaseendelseif(flag_s)begincnt1_clk <= cnt1_clk +1'b1;case(cnt1_clk)1 : begin lcd_char_en <=1'b0; e nd2 : begin lcd_char_en <=1'b1; e nd3 : begin lcd_char_en <=1'b1; e nd4 : begin lcd_char_en <=1'b0; e ndT_w_char: beginif(cnt_char == 3'b111)begin cnt_char<=0; flag_s <=0; endelsecnt_char <=cnt_char+1'b1;cnt1_clk <=0;enddefault: lcd_char_en <=0;endcasecase(cnt_char)//2 3 4 50 : begin char_X <=3'b000; char_LR <=0; char_data <=time_out[47:40]; end //x0:00:001 : begin char_X <=3'b001; char_LR <=0; char_data <=time_out[39:32]; end //0x:00:002 : begin char_X <=3'b010; char_LR <=0; char_data <=8'h3a; end //: ascii 0583 : begin char_X <=3'b011; char_LR <=0; char_data <=time_out[31:24]; end //00:x0:004 : begin char_X <=3'b100; char_LR <=0; char_data <=time_out[23:16]; end //00:0x:005 : begin char_X <=3'b101; char_LR <=0; char_data <=8'h3a; end //: ascii 0586 : begin char_X <=3'b110; char_LR <=0; char_data <=time_out[15: 8]; end//00:00:x07 : begin char_X <=3'b111; char_LR <=0; char_data <=time_out[7 : 0]; endendcaseendendendtask data_deal;beginif(sec == 59)if(min ==59)if(hour == 23)begin hour<=0;min <=0;sec <=0; endelsebegin hour<=hour + 1'b1; min <=0; sec<=0; endelsebegin min <= min+1'b1; sec <=0; endelsesec <= sec +1'b1;time_out[47:40] <= 8'h30+(hour/10);time_out[39:32] <= 8'h30+(hour%10);time_out[31:24] <= 8'h30+(min /10);time_out[23:16] <= 8'h30+(min %10);time_out[15: 8] <= 8'h30+(sec /10);time_out[ 7: 0] <= 8'h30+(sec %10);endendtaskendmodule2代码module LCD_init(//module LED(input lcd_clk,input sys_clk,input lcd_en, //1 is activedoutput reg LCD_RS,output reg LCD_RW,output reg LCD_EN,inout [7:0] LCD_DATA,output reg ACK);reg flag;reg [7:0] lcd_data;reg [7:0] State;reg link_rs;reg link_data;parameter Idle =8'b0000_0001,Basic_com =8'b0000_0010, //basic instruction:0x30Disp_set =8'b0000_0100, //set show curse blingDDRAM_clear =8'b0000_1000, //colunm address XWait_clear =8'b0001_0000,Point_set =8'b0010_0000,Show_on =8'b0100_0000,Stop =8'b1000_0000;reg [9:0] cnt; //16*2*32=2^10 byte(8bits)/* LCD_RW LCD_DATA*/assign LCD_DATA = link_data ? lcd_data: 8'hzz;/* LCD_RW LCD_EN */always @ (posedge sys_clk) beginif(flag)beginLCD_RW =0;LCD_EN = lcd_clk;endelsebeginLCD_RW =1'bz;LCD_EN =1'bz;endend/* LCD_RS */always @ (posedge lcd_clk) beginif(link_rs)LCD_RS <=1'b0;elseLCD_RS <=1'bz;end/*-Main state transter-*/always @ (posedge lcd_clk) begincase (State)Idle : beginif(lcd_en)begin link_rs=1; State <= Basic_com; endelseState <= Idle;ACK =0;flag <=1'b0;lcd_data <= 8'hzz;cnt <= 0;endBasic_com : beginflag <=1'b1;link_data =1'b1;cnt <= cnt +1'b1;if(cnt == 1)State <= Disp_set;elseState <= Basic_com;lcd_data <= 8'h30;endDisp_set : beginState <= DDRAM_clear;lcd_data <= 8'h0c; //show curse blink is offendDDRAM_clear : beginState <= Wait_clear;lcd_data <= 8'h01;endWait_clear : begincnt <=cnt +1'b1;link_data = 1'b0;flag <=0;lcd_data <= 8'hzz;if(cnt == 30)State <= Point_set;elseState <= Wait_clear;endPoint_set : beginflag <=1'b1;link_data =1'b1;State <= Show_on;lcd_data <= 8'h06; //point +1 automatically,screen move off endShow_on : beginState <= Stop;lcd_data <= 8'h0c;endStop : beginState <= Idle;flag <=1'b0;link_data =1'b0;ACK <=1'b1;lcd_data <= 8'hzz;cnt <= 0;link_rs =0;enddefault: begin ACK =0;State <= Idle;end endcaseendendmodule3代码//module LCD_top(module LED(input sys_clk,input sys_rst,output LCD_RS,output LCD_RW,output LCD_EN,inout [7:0] LCD_DATA,output BUSY);wire [7:0] char_data;wire [2:0] char_X;wire [1:0] char_Y;sign singb(.lcd_clk (lcd_clk), //100kHz.sys_rst (sys_rst),.lcd_char_en(lcd_char_en),.lcd_init_en(lcd_init_en),.char_data (char_data),.char_X (char_X),.char_Y (char_Y),.char_LR (char_LR));LCD_init lcd_init(.lcd_clk (lcd_clk),.sys_clk (sys_clk),.lcd_en (lcd_init_en), //1 is actived .LCD_RS (LCD_RS),.LCD_RW (LCD_RW),.LCD_EN (LCD_EN),.LCD_DATA (LCD_DATA),.ACK (init_ack));LCD_charac a(.lcd_clk (lcd_clk),.sys_clk (sys_clk),.lcd_en (lcd_char_en), //1 is actived .Y (char_Y), //row 0-3.X (char_X), //clunm 0-7.LR (char_LR), //0/1.data_disp (char_data),.LCD_RS (LCD_RS),.LCD_RW (LCD_RW),.LCD_EN (LCD_EN),.LCD_DATA (LCD_DATA),.ACK (init_ack));LCD_clk clk1(.sys_clk (sys_clk),.lcd_clk (lcd_clk));endmodule4代码module LCD_clk(//module LED(input sys_clk,output reg lcd_clk);/*-creat the 25kHz clock-*/reg [11:0] lcd_cnt;always @ (posedge sys_clk) beginif(lcd_cnt == 2) //100kHzbeginlcd_cnt =0;lcd_clk <= ~ lcd_clk;endelselcd_cnt = lcd_cnt +1'b1;endinitial begin lcd_clk =0; lcd_cnt =0; endendmodule5代码/* to display character */module LCD_charac(//module LED(input lcd_clk,input sys_clk,input lcd_en, //1 is activedinput [1:0] Y, //row 0-3input [2:0] X, //clunm 0-7input LR, //0/1input [7:0] data_disp,output reg LCD_RS,output reg LCD_RW,output reg LCD_EN,inout [7:0] LCD_DATA,output reg ACK);reg [7:0] lcd_data;reg [7:0] R_buff;reg [7:0] State;parameter Idle =8'b0000_0001,DDRAM =8'b0000_0010, //drawing modeW_addr =8'b0000_0100, //row address YDummy =8'b0000_1000, // not really readingR_data =8'b0001_0000, //reading high byte dataW0_data =8'b0010_0000,W1_data =8'b0100_0000,Stop =8'b1000_0000;reg flag,cnt;reg link_data;reg flag0;/* LCD_DATA */assign LCD_DATA = link_data ? lcd_data :8'hzz;/* LCD_EN */always @ (posedge sys_clk) beginif(flag == 1'b1)LCD_EN <= lcd_clk;elseLCD_EN <=1'bz;end/* LCD_RW */always @ (posedge lcd_clk) beginif(flag0)if(State == Dummy || State == R_data)LCD_RW <=1'b1;elseLCD_RW <=1'b0;elseLCD_RW <=1'bz;end/* LCD_RS */always @ (posedge lcd_clk) beginif(flag0)if(State == W0_data || State == W1_data || State == Dummy || State == R_data) LCD_RS <=1'b1;elseLCD_RS <=1'b0;elseLCD_RS <=1'bz;end/*-Main state transter-*/always @ (posedge lcd_clk) begincase (State)Idle : beginif(lcd_en)begin State <= DDRAM; link_data =1; flag0=1'b1; endelsebegin State <= Idle; flag0= 1'b0;endflag <= 1'b0;lcd_data <= 8'hzz;ACK <=0;endDDRAM : begin //here flag is changed,not Idle, cause sys_clk flag <= 1'b1;State <= W_addr;link_data =1;lcd_data <= 8'h30;endW_addr : beginif(!cnt)beginif(LR)State <= Dummy;elseState <= W0_data;cnt =1'b1;endelseState <= W0_data;case (Y)2'b00: lcd_data <= 8'h80 + X;2'b01: lcd_data <= 8'h90 + X;2'b10: lcd_data <= 8'h88 + X;2'b11: lcd_data <= 8'h98 + X;endcaselink_data =1'b1;endDummy : beginState <= R_data;R_buff <= LCD_DATA;link_data =0;endR_data : beginState <=W_addr;R_buff <= LCD_DATA;endW0_data : beginif( !LR)beginlcd_data <= data_disp;State <= Stop;endelsebeginlcd_data <= R_buff;State <= W1_data;endendW1_data : beginlcd_data <= data_disp;State <=Stop;flag0=0;endStop : beginState <= Idle;flag <= 1'b0;lcd_data <= 8'hzz;cnt <= 0;ACK <= 1;enddefault: begin ACK =0;State <= Idle; link_data=0 ;end endcaseendendmodule。

基于FPGA的多功能数字时钟设计

7.利用适配器将综合后的网络表文件针对某一具体的目标器件进行逻辑映射操作,包括底层器件配置、逻辑分割、逻辑优化和布局布线。

8.在适配完成后,产生多项设计结果:(a)适配报告,包括芯片内部资源利用情况,设计的布尔方程描述情况等;(b)适配后的仿真模型;(c)器件编程文件。根据适配后的仿真模型,可以进行适配后时序仿真,因为已经得到器件的实际硬件特性(如时延特性),所以仿真结果能比较精确的预期未来芯片的实际性能。如果仿真结果达不到设计要求,就修改VHDL源代码或选择不同速度和品质的器件,直至满足设计要求。

1.CLB是FPGA的主要组成部分。图2-1是CLB基本结构框图,它主要由逻辑函数发生器、触发器、数据选择器等电路组成。CLB中3个逻辑函数发生器分别是G、F和H,相应的输出是G’、F’和H’。G有4个输入变量G1、G2、G3和G4;F也有4个输入变量F1、F2、F3和F4。这两个函数发生器是完全独立的,均可以实现4输入变量的任意组合逻辑函数。逻辑函数发生器H有3个输入信号;前两个是函数发生器的输出G’和F’,而另一个输入信号是来自信号变换电路的输出H1。这个函数发生器能实现3输入变量的各种组合函数。这3个函数发生器结合起来,可实现多达9变量的逻辑函数。

基于FPGA的数字电子钟的设计与实现

基于FPGA的数字电⼦钟的设计与实现背景:本实验所有结果基于Quartus II 13.1 (64-bit)实现,实验过程采⽤⾃下⽽上⽬录⼀、基本功能设计与思路基本功能:能实现秒、分钟、⼩时的计数,计数结果清晰稳定的显⽰在 6 位数码管上。

1、动态显⽰模块该模块主要功能是通过数码管的动态扫描实现 6 位数码管显⽰计数结果,本模块由扫描模块scan_cnt6,位选控制模块 dig_select,数据选择控制模块 seg_select 以及译码模块 decoder 构成扫描模块 scan_cnt6模块功能:产⽣ 位选控制端dig_select 和数据选择端 code_select 模块所需要的地址信息,扫描时钟决定位选信号和数据切换的速度。

设计思路:利⽤74390芯⽚(P160 TTL 双⼗进制异步计数器)构建⼀个模六计数器,就是6进制计数器,利⽤计数到6(110)时,“q2”和“q1”为⾼电平,产⽣ ⼀个复位信号,加到74390的⾼电平有效的异步清0端“1CLR”上,使计数器回0,从⽽实现模六计数。

设计结果:cnt6模块设计图波形仿真:(默认为时序仿真)cnt6模块波形仿真图位选模块 dig_select模块功能:在地址端的控制下,产⽣位选信号。

设计思路:利⽤74138芯⽚(3线-8线译码器),当选通端输⼊端G1为⾼电平,选通端输⼊端G2AN和G2BN为低电平时,将扫描信号cnt6的输出作为输⼊信号,dig[5..0]是译码输出,输出低电平有效。

设计结果:dig_select模块设计图波形仿真:dig_select模块波形仿真图数据选择模块 seg_select模块功能:输⼊ 6 组数据,每组数据 4bit,本模块完成在地址端的控制下从6 组数据当中选择 1 组输出。

设计思路:利⽤74151芯⽚(P91 8选1数据选择器),在控制输⼊端GN为低电平时,将扫描信号的选择下,分别选中D[5..0]对应的输⼊信号输出为Y。

fpga数字钟实验总结

fpga数字钟实验总结

FPGA数字钟实验总结:

本次FPGA数字钟实验旨在设计并实现一个基于FPGA的数字时钟。

通过该实验,我掌握了以下几个方面的知识和技能。

首先,我学会了使用FPGA开发工具进行电路设计和编程。

我使用了一种特定的硬件描述语言(HDL),如Verilog或VHDL,来描述时钟电路的功能和行为。

通过学习和实践,我能够熟练地使用FPGA开发工具创建和编辑代码。

其次,我了解了数字时钟的基本原理和组成部分。

数字时钟通常由时钟芯片、计数器、显示器和控制电路组成。

我学会了如何使用FPGA来实现这些功能,并通过编程控制时钟的显示方式和计时功能。

在实验过程中,我还学会了时序设计和逻辑电路的基本概念。

由于时钟电路需要精确的时序控制,我学会了如何设计和优化时钟电路的时序路径,以确保电路的正常运行和准确计时。

此外,我还学会了如何使用开发板上的按钮和开关等外部输入

设备来控制时钟的设置和调整功能。

通过编程,我能够实现时钟的

时间调整、闹钟设置等功能,并通过显示器将相应的信息展示出来。

最后,在实验过程中,我也遇到了一些挑战和问题。

例如,时

钟的精确性和稳定性是一个重要的考虑因素,我需要注意时钟信号

的抖动和噪声问题。

此外,时钟的显示方式和格式也需要根据实际

需求进行设计和调整。

通过本次FPGA数字钟实验,我不仅巩固了对数字电路和FPGA

开发的理论知识,还提高了实际操作和问题解决能力。

这个实验为

我今后在数字电路设计和嵌入式系统开发方面的学习和工作奠定了

坚实的基础。

基于FPGA:电子钟的设计报告

电子钟的设计报告姓名:< >组别:< >专业班级:< >目录目录 (1)一、数字钟的设计要求 (2)二、顶层设计 (2)三、模块 (3)1.顶层模块 (3)2.分频器模块 (4)3.按键消抖模块 (4)4.计时模块 (5)5.显示模块 (6)6.报时和闹钟模块 (6)四、系统调试及运行结果分析 (7)1、硬件调试 (7)2、软件调试 (8)3、调试过程及结果 (8)(1)显示模块调试 (8)(2)时间系统模块调试 (9)五、总结 (9)一、数字钟的设计要求设计一个具有时、分、秒计时第二电子钟电路,按24小时制记时。

要求:1、准确计时,以数字形式显示时、分、秒的时间;2、具有分、时校正功能,校正输入脉冲频率为1Hz;3、具有仿广播电台整点报时的功能,即每逢59分51秒、53秒、55秒及57秒时,发出4声500Hz低音,在59分59秒时发出一声1kHz高音,它们的持续时间均为1秒。

最后一声高音结束的时刻恰好为正点时刻。

4、具有定时闹钟功能,且最长闹铃时间为一分钟。

要求可以任意设置闹钟的时、分;闹铃信号为500Hz和1kHz的方波信号,两种频率的信号交替输出,且均持续1S。

设置一个停止闹铃控制键,可以停止输出闹铃信号。

二、顶层设计采用自顶向下的设计方法,首先根据数字时钟的功能要求进行顶层设计和分析,用FPGA实现系统的计时、显示驱动、按键输入处理、仿广播电台整点报时的功能。

根据实训平台的硬件资源情况,输入信号包括时钟输入和按键输入,其中系统时钟由实训平台核心板50MHz晶振提供,拨码开关作为校时、闹钟时间设置和复位的信号输入,输出信号包括峰鸣器控制输出、8位动态数码管位选和段选控制输出。

数字电字时钟系统主要有分频器模块、按键消抖模块、计时模块、整点报时和闹铃模块和显示驱动模块构成。

三、模块1.顶层模块如下图所示。

2.分频器模块分频器模块的主要功能是为其他模块提供时钟信号。

fpga闹钟工作原理

FPGA(Field-Programmable Gate Array,现场可编程门阵列)闹钟是一种基于FPGA芯片设计和实现的数字时钟设备。

下面是FPGA闹钟的工作原理:

1.时钟信号输入:FPGA闹钟通常会接收一个外部的时钟信号作为参考,比如晶体振荡器

产生的脉冲信号。

2.时钟分频:利用FPGA内部的时钟分频电路,将外部时钟信号分频为更低频率的时钟信

号。

例如,将1秒的脉冲信号分频为每秒钟一个时钟周期。

3.时间计数器:FPGA闹钟内部有一个时间计数器,根据分频后的时钟信号递增来记录当

前的时间。

计数器可以具体设置为年、月、日、时、分、秒等各个时间单位的计数值。

4.按键输入检测:FPGA闹钟可能还包含按键输入检测电路,用于检测用户操作的按键输

入,比如调整时间、设置闹钟、关闭闹钟等。

5.显示与输出控制:FPGA闹钟通常配备显示模块,如数码管或液晶显示屏,用于显示当

前的时间。

根据时间计数器的值,将相应的数字或字符输出到显示模块上。

6.闹钟功能:FPGA闹钟还可以具备闹钟功能,通过用户设置的时间和闹钟触发条件,当

计数器达到设定的闹钟时间时,触发闹钟功能,如蜂鸣器发出提示音或显示闹钟图标。

7.其他功能:FPGA闹钟还可以具备其他附加功能,如温度显示、日历功能、定时器功能

等,这些功能可以根据具体需求进行设计和实现。

通过FPGA芯片的灵活性和可编程性,闹钟的功能和特性可以由设计者根据需要进行自定义和扩展。

因此,FPGA闹钟具有较高的定制性和可扩展性,适用于各种不同的应用场景。

基于FPGA的电子钟设计

基于FPGA的电子钟设计基于FPGA的电子钟设计随着物联网技术的发展,我们对于时间的要求也越来越精细。

电子钟作为一个基本的时间计量工具,其精度和稳定性至关重要。

而FPGA作为一种强大的可编程逻辑器件,具有高速、高效、灵活等优势,成为电子钟设计的重要基础。

一、电子钟的基本原理电子钟是指采用电路元器件、微处理器等电子器件构成的时钟。

其基本原理可以概括为:利用更精确的时间计量器件替代机械时钟中的发条和摆轮,同时采用数字处理器等电子元器件代替机械表盘展示时间。

电子钟的核心是时基电路,其作用是产生高精度的时间信号,为其它电路提供时间标准。

通常采用晶振、TCXO、OCXO等时基器件。

为了保证时间精度,还要从外部时钟或天线接收校正信号。

二、FPGA的优势FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,可以灵活地对电路进行编程和调整,从而实现不同的功能。

FPGA相对于ASIC(Application Specific Integrated Circuit),具有以下优点:1. 灵活性:FPGA可以通过重新编程来实现不同的逻辑功能,而ASIC则需要重新设计电路,成本和时间都比较高。

2. 高速:FPGA以可编程方式实现电路逻辑,减少了多级缓存的开销,因此运行速度更快。

3. 低功耗:FPGA可以在逻辑上进行优化,以达到低功耗效果,同时利用现代的制造技术,还可以采用低功耗工艺。

4. 可重用性:FPGA的电路设计可以在不同的项目中重复使用,从而提高了效率和经济性。

三、基于FPGA的电子钟设计基于FPGA的电子钟设计方案主要包括两部分,分别是时基电路和数码显示电路。

1. 时基电路设计时基电路是电子钟的核心部分,可以采用晶振、TCXO、OCXO等器件来产生高精度的时间信号。

在电子钟的设计中,一般还需要接收外部同步校时信号,用于校正时钟误差。

基于FPGA的时基电路设计主要包括以下几个部分:(1)时钟输入电路:接收来自外部同步信号的时钟脉冲,用于校准电子钟的误差。

基于FPGA的数字电子时钟

第1章绪论数字化是电子设计发展的必由之路已成为共识。

在数字化的道路上,我国电子设计技术的发展经历了,并将继续经历许多重大的变革与飞跃、从应用SSI通用数字电路芯片构成电路系统,到广泛地应用MCU(微控制器或单片机),它使得电子系统的智能化水平在广度和深度上产生了质的飞跃。

MCU的广便应用并没有抛弃SSI的应用,而是为它们在电于系统中找到了更合理的地位。

随着社会经济发展的延伸、各类新型电子产品的开发为我们提出了许多全新的课题和更高的要求。

FPGA在EDA基础上的广泛应用.从某种意义上说,新的电子系统运转的物理机制又将回到原来的纯数字电路结构,但这是—种更高层次的循环,应是一次否定之否定的运动,它在更高层次上容纳了过去数字技术的优秀部分,对MCU系统将是—种扬弃,但在电子设计的技术操作和系统构成的整体上却发生质的飞跃。

如果说MCU在逻辑的实现上是无限的话,那么高速发展的FPGA 不但包括了MCU这一特点,并兼有串、并工作方式和高速、高可靠性以及宽口径适用等诸多方面的特点、不仅如此,随着EDA技术的发展和FPGA在深亚微米领域的进军、它们与MCU、MPU、DSP、A/D、D/A、RAM和ROM等独立器件问的物理与功能界限正日趋模糊。

以大规模集成电路为物质基础的EDA技术终于打破了软硬件之间最后的屏障,使软硬件工程师们有了共同的语言[1]。

1.1 课题背景电子产品随着技术的进步,更新换代速度可谓日新月异。

不同行业层出不穷的技术需求,使得对配套电子系统或部件的功能、可靠性、集成度、成本、设计周期的要求日益提高。

随着时间的推移,科学研究与技术开发行为日益市场化,而远非纯粹的学术行为,这要求设计工作必须在较短的时间内出色完成,技术人员感到工作压力越来越大。

显然,采用传统的电子设计手段完成复杂电子系统设计显得越来越力不从心了,传统的电子设计与现实手段受到极大的挑战。

如果在激烈的技术产品竞争中仍沿用老办法,很可能在激烈的竞争中处于被动落后的境地,例如,当设计比较复杂的电子系统时,要等到做完全部硬件试验才开始设计印制电路板,这样,设计周期必然会相应拉长,即使设计出印制电路板来,也很难保证它的电气连接全部正确、各个元器件参数合理以及完善的电磁兼容性能,如果需要设计实现的数字电路部份规模较大,仍习惯地利用中、小规模数字集成芯片实现,电路的集成度和可靠性在许多应用场合会受到很大限制,甚至根本无法满足需求。

基于FPGA的电子钟设计

基于FPGA的电子钟设计摘要VHDL是Very High Speed Integrated Circuit Hardware Description Language 的缩写,意思是超高速集成电路硬件描述语言。

对于复杂的数字系统的设计,它有独特的作用。

它的硬件描述能力强,能轻易的描述出硬件的结构和功能。

这种语言的应用至少意味着两种重大的改变:电路的设计竟然可以通过文字描述的方式完成;电子电路可以当作文件一样来存储。

随着现代技术的发展,这种语言的效益与作用日益明显,每年均能够以超过30%的速度快速成长。

这次设计的内容是在简要介绍了VHDL语言的一些基本语法和概念后,进一步应用VHDL设计一个电子钟,最后通过仿真出时序图实现预定功能。

电子钟的时间显示用到了七段数码管的电路设计,内部的时间控制输出则用到了各种设计,包括:时钟分频模块、计时模块、按键模块和显示模块四个部分。

关键词VHDL 电子钟七段显示器FPGA目录摘要 (I)1 前言 (1)1.1 选题的目的和意义 (1)1.2 FPGA技术的介绍 (1)1.3 VHDL简介 (2)2 系统总体设计方案 (4)2.1 电子钟功能概述 (4)2.2电子钟外观 (4)3 系统程序设计 (5)3.1 共享组件与程序包的设计说明 (5)3.1.1 my_pkg组件包程序代码 (5)3.1.2 1Hz_generator组件 (8)3.1.3 count60组件 (9)3.1.4 count24组件 (11)3.1.5 alarm_set组件 (12)3.1.6 stop_watch组件 (15)3.1.7 i60bcd组件 (18)3.1.8 i24bcd组件 (20)3.2 系统模块设计 (24)3.2.1 七段显示器扫描输出电路模块(display) (24)3.2.2 entity模块 (28)3.2.3 architecture模块 (30)3.2.4 正常计数时间功能模块 (31)3.2.8 扫描多路输出功能模块 (36)4 总结 (39)致谢 (40)参考文献 (41)附录 (42)1 前言1.1 选题的目的和意义20世纪末,电子技术获得了飞速的发展,在其推动下,现代电子产品几乎渗透了社会的各个领域,有力地推动了社会生产力的发展和社会信息化程度的提高,同时也使现代电子产品性能进一步提高,产品更新换代的节奏也越来越快。

fpga课程设计基于fpga多功能电子钟设计

FPGA课程设计报告书题目:基于FPGA多功能电子钟设计学院:电气工程与自动化专业班级:摘要 (1)第一章FPGA简介 (2)1.2 FPGA基本结构 (2)1.3 FPGA系统设计流程 (3)第二章系统电路设计 (4)2.1电子钟的设计方案选择 (4)2.2总体设计方案 (4)2.3显示电路设计 (5)2.3.1分频器电路 (7)2.3.2扫描电路电路 (7)2.3.3 BCD码多路选择器 (7)2.3.4 BCD译码器 (7)2.3.5位选码电路 (8)2.4电子时钟计数器电路设计 (8)2.4.1秒和分计数器设计 (8)2.4.2小时计数器设计 (10)总结 (12)参考文献 (13)附录 (14)本文介绍了多功能电子钟的现状及发展动态,多功能电子钟的应用,多功能电子钟的基本原理和实现方法以及系统构建理论。

针对现行电子钟设计方案实现起来相对复杂、误差偏大等弊端,对以FPGA为核心器件的电子钟方案进行了实验研究,利用EDA技术自顶向下的设计方法,设计电子钟各模块及相应具体电路,通过编译、仿真并下载到FPGA实验平台进行测试,运行结果表明:系统能以较小的误差显示时、分、秒,并且当走时不准时,可以通过相应设置键实现校时。

关键词:多功能电子钟;EDA;FPGA第一章 FPGA简介1.1 FPGA概述FPGA是现场可编程门阵列(Field Programmable Gate Array)的简称,与之相应的CPLD 是复杂可编程逻辑器件(Complex Programmable Logic Device)的简称,两者的功能基本相同,只是实现原理略有不同,有时可以忽略这两者的区别,统称为可编程逻辑器件或CPLD/PGFA。

CPLD/PGFA几乎能完成任何数字器件的功能,上至高性能CPU,下至简单的74电路。

它如同一张白纸或是一堆积木,工程师可以通过传统的原理图输入或硬件描述语言自由的设计一个数字系统。

通过软件仿真可以事先验证设计的正确性,在PCB完成以后,利用CPLD/FPGA的在线修改功能,随时修改设计而不必改动硬件电路。

基于FPGA的多功能数字时钟_毕业论文

南京航空航天大学金城学院毕业设计题目基于FPGA的多功能数字时钟学生姓名学号系部自动化系专业电气工程与自动化班级指导教师二〇一三年六月南京航空航天大学金城学院本科毕业设计(论文)诚信承诺书本人郑重声明:所呈交的毕业设计(论文)(题目:基于FPGA的多功能数字时钟)是本人在导师的指导下独立进行研究所取得的成果。

尽本人所知,除了毕业设计(论文)中特别加以标注引用的内容外,本毕业设计(论文)不包含任何其他个人或集体已经发表或撰写的成果作品。

作者签名:郭建超2013年5 月31 日(学号):2009031236毕业设计(论文)报告纸基于FPGA的多功能数字时钟摘要数字钟由于其具有走时准,显示直观,款式新颖,附加功能多等特点而受到人们的广泛使用。

采用FPGA设计一个具有整点报时,可校时,可显示万年历的数字时钟是本课题的主要任务。

由于数字集成电路的发展和石英晶体震荡器的广泛应用,使得数字钟的精度,远远超过老式钟表,钟表的数字化给人们生产、生活带来了极大的方便,而且大大地扩展了钟表原先的报时功能。

诸如定时自动报警、定时启闭电路、定时开关烘箱、通断动力设备,甚至各种定时电气的自动启用等,所有这些都是以钟表数字化为基础的。

近些年,随着科技的发展和社会的进步,人们对数字钟的要求也越来越高,传统的时钟已不能满足人们的需求,因此研究数字钟以及扩大其应用有着非常现实的意义。

本文介绍的基于现场可编程门阵列FPGA实现数字多功能数字时钟,采用自上而下的方法对系统进行设计,以硬件描述语言VHDL为描述语言,利用QuartusII软件进行设计,并在智能可编程器件开发实验系统KH-310上实现数码管显示的时钟,及其计时、校时、整点提示和万年历功能。

其中时钟的秒钟、分钟为60进制计时方式,小时可通过24进制的计时方式,天可通过与月传过来的判断信号来判断大、小平、闰月,可分别用28、29、30、31进制计数实现,月通过12进制计数实现,年通过100进制计数实现。

基于FPGA的多功能数字钟设计实现

电子技术课程设计设计报告题目:基于FPGA的多功能数字钟设计实现班级:姓名:学号:指导教师:上交日期:2017.5.21摘要本设计为基于FPGA的多功能数字钟设计实现,具有计时、校对、闹钟、报整点等基础功能,以及日期、秒表、电子琴、延时闹钟、音乐闹钟等拓展功能。

本设计采用EDA技术,以硬件描述语言Verilog HDL为系统逻辑描述语言设计文件,在QUARTUSII工具软件环境下,采用自顶向下的设计方法,由各个基本模块共同构建了一个基于FPGA的数字钟。

系统采用Alera DE0开发板,并外接了蜂鸣器电路。

系统由分频模块、计时模块、闹钟模块、控制模块、显示模块、秒表模块、音乐模块、日期模块、电子琴模块组成。

经编译和仿真所设计的程序,在可编程逻辑器件上下载验证,本系统能够完成需求功能。

关键词:数字时钟,硬件描述语言,Verilog HDL,FPGA目录摘要 (2)目录 (3)1 绪论 (5)1.1背景 (5)1.2项目创意 (7)2需求分析 (8)2.1任务目标 (8)2.2元件清单 (8)2.3小组分工 (9)3系统设计 (9)3.1 系统主板电路分析 (9)3.2模块化设计方案 (16)4 模块电路设计 (17)4.1顶层模块 (17)4.2分频模块 (19)4.2.1 分频模块设计 (19)4.2.2 分频模块仿真 (21)4.3 计时模块 (21)4.3.1 计时模块设计 (21)4.3.2 计时模块仿真 (23)4.4 控制模块 (24)4.4.1 控制模块设计 (24)4.4.2 控制模块仿真 (24)4.5 秒表模块 (24)4.5.1 秒表模块设计 (24)4.6 日期模块 (26)4.6.1 日期模块设计 (26)4.7 电子琴模块 (28)4.7.1 电子琴模块设计 (28)5 系统调试及结果分析 (30)5.1 硬件检查 (30)5.2 软件编译 (30)5.3 调试过程及结果 (31)5.4 调试注意事项 (32)6 总结 (33)6.1课设中出现的问题与解决方案 (33)6.2心得体会 (33)1 绪论1.1 背景现代的社会是一个信息产品广泛使用,产品的性能越来越强大,做工越来越精细,工艺越来越高,更新换代越来越迅速的社会。

FPGA电子钟LED+LCD显示

1 目的和意义数字电子钟是数字电路中的一个经典学习内容。

我们选用电子钟作为最后结课项目的目的,是为了学习verilog语言、FPGA的基本知识、由顶层至底层的设计思路。

使我们对EDA知识有了个基本的了解,也掌握了基础的知识,同时锻炼了我们团队合作的精神,特别是在接口的确定上,我们学到了更多。

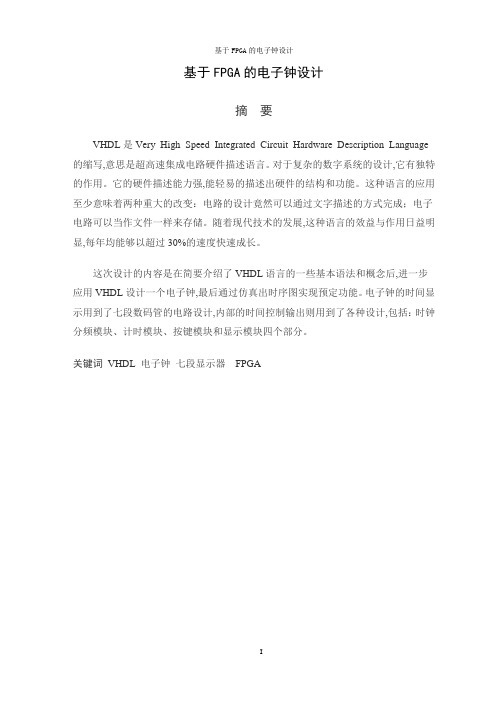

2 原理2.1 电子钟的计数和调节功能数字电子钟的核心内容是三个计数器,即秒钟计数器、分钟计数器和时钟计数器。

秒钟计数器的时钟为1秒的时钟,当秒钟计数器计满60,则输出一个计满信号。

秒钟的计满信号作为分钟计数器的时钟,同样,分钟计数器计满60后,则输出一个分钟计满信号,这个信号作为时钟计数器的时钟。

同时,三个计数器里面的计数值,会实时的经过译码等操作,显示在7段LED数码管和LCD上。

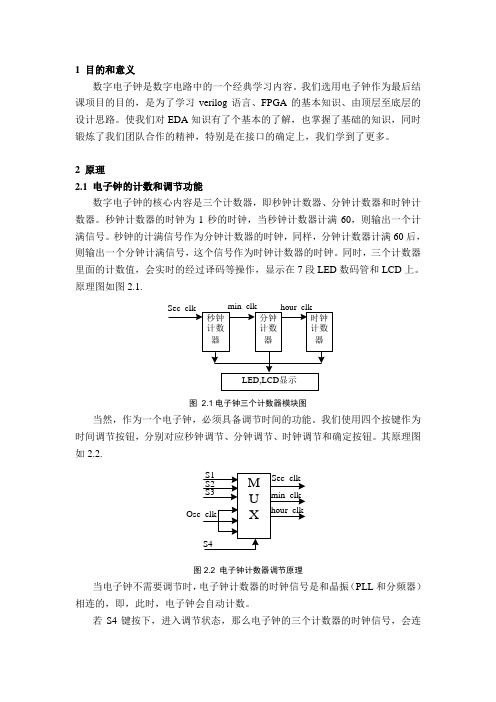

原理图如图2.1.图 2.1电子钟三个计数器模块图当然,作为一个电子钟,必须具备调节时间的功能。

我们使用四个按键作为时间调节按钮,分别对应秒钟调节、分钟调节、时钟调节和确定按钮。

其原理图如2.2.图2.2 电子钟计数器调节原理当电子钟不需要调节时,电子钟计数器的时钟信号是和晶振(PLL和分频器)相连的,即,此时,电子钟会自动计数。

若S4键按下,进入调节状态,那么电子钟的三个计数器的时钟信号,会连链接到按键S1、S2、S3上,这样,只要按一次S1(S2或者S3),计数器中的计数值就会增加一个。

即实现了按键调节时钟的功能。

若调节完毕,再按S4键,计数器的时钟信号又连接到晶振(PLL和分频器)上去,再次进入自动计时状态。

2.2 计数器的显示2.2.1 LED数码管的显示LED数码管的示意图如下图2.3(DE-2中的数码管多一个小数点):图2.3 七段数码管的示意图只要点亮相应的码段,即可显示相应的数字。

所以,LED数码管的显示要通过一个简单的译码器,译码表如下:表1 LED数码管的译码表2.2.2LCD显示DE-2板载的液晶为16x2液晶。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA的多功能电子钟集美大学信息工程学院电子科学与技术专业 2015届闭应明学号:2011850057[摘要] 本设计在基于以硬件描述语言VHDL为基础的EDA设计方法上,设计中根据系统的功能要求合理划分出层次,进行分级设计和仿真验证,将较为复杂的数字系统逻辑简化为基本的模型从而降低实现的难度。

通过层次化的设计方法,自顶向下设计,把不同的功能模块组合到一起,使用quartus II工具进行设计编译仿真,最终在在FPGA的DE2_70开发板上中实现具有基本的年月日、时分秒、农历显示、节气提醒、传统节假日提醒、闹铃闰年提醒等多功能的电子钟[关键字] 硬件描述语言VHDL EDA FPGA quartus II DE2_70开发板多功能电子钟The multi-function electronic clock of FPGABi YingmingNO:2011850057,Electronic science and technology major,2015Information Engineering College of Jimei UniversityAbstract: This design based on VHDL(hardware description language)and EDA design method, so that we can through the function of the system in the design to divide reasonably into layers, hierarchical design and simulation, and to simplify the complex number system logic as a basic model to reduce the difficulty of implementation. Through the design method of hierarchical, top-down design, the different function modules were moved together by using the quartus II tool design compiled simulation.Finally ,the multi-function electronic clock that can show the date and time,and can warn the Solar terms,Traditional festivals,the leap year and the alarm,was realized in DE2_70 development board of FPGAKey words:VHDL hardware description language EDA FPGA the quartus II DE2_70 development board multi-function electronic clock目录目录引言 (1)第一章 FPGA介绍 (3)1.1 FPGA简单工作原理 (3)1.2 FPGA应用 (3)1.2.1 FPGA的硬件描述语言VHDL简述 (3)1.2.2 FPGA的DE2_70开发板简述 (3)第二章电子时钟设计 (5)2.1 电子钟的功能设计指标 (5)2.2 电子钟的整体构造 (5)2.2.1 分频模块 (6)2.2.2 秒模块 (6)2.2.3 分模块 (7)2.2.4 小时模块 (7)2.2.5 天模块 (8)2.2.6 月份模块 (9)2.2.7年模块 (10)2.2.8 阳历转阴历模块 (11)2.2.9 闹铃模块 (13)2.2.10 译码转换模块 (13)2.2.11 七段数码管和LCD显示模块 (15)2.2.12、传统节假日提醒模块 (16)2.2.13 24节气提醒模块 (17)2.2.14 定时关机模块 (18)2.2.15 l602LCD显示驱动模块 (19)2.2.16、顶层模块 (20)第三章时钟验证 (24)3.1 管脚绑定 (24)3.2 时间参数一 (24)3.3 时间参数二 (26)3.4 时间参数三 (26)3.5 结果分析 (27)总结 (29)致谢 (30)参考文献 (31)附录 (32)引言引言FPGA是现场可编程门阵列(Field-Programmable Gate Array)的缩写,它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

FPGA器件具有标准化,小型化、多功能、低功耗、高密度、系列化、高速率、低成本,可无限反复编程,并可现场模拟调试验证,设计灵活方便等特点。

随着FPGA芯片的更新和发展,使数字系统的设计迈进了SOPC时代,而各种IP核的设计和应用是SOPC设计的重要特征。

除了各FPGA设计厂商,还有许多第三方的IC设计公司将各种IP核推向市场,用户可以方便地下载试用,将其集成到自己的系统中。

本设计是基于以硬件描述语言VHDL为基础的EDA设计方法,在FPGA芯片上实现多功能电子钟。

本设计涉及了EDA设计的完整流程,可以很方便地通过修改增删,应用于各种基于FPGA的系统中。

闭应明第一章FPGA介绍第一章 FPGA介绍1.1 FPGA基本工作原理FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个概念,内部包括输出输入模块IOB(Input Output Block),可配置逻辑模块CLB(Configurable Logic Block)和内部连线(Interconnect)三个部分。

FPGA是由存放在片内RAM 中的程序来设置其工作状态的,因此,工作时需要对片内的RAM进行编程。

用户可以根据不同的配置模式,采用不同的编程方式。

加电时,FPGA芯片将EPROM 中数据读入片内编程RAM中,配置完成后,FPGA进入工作状态。

掉电后,FPGA 恢复成白片,内部逻辑关系消失,因此,FPGA能够反复使用。

FPGA的编程无须专用的FPGA编程器,只须用通用的EPROM、PROM编程器即可。

当需要修改FPGA 功能时,只需换一片EPROM即可。

这样,同一片FPGA,不同的编程数据,可以产生不同的电路功能。

因此,FPGA的使用非常灵活。

1.2 FPGA应用1.2.1 FPGA的硬件描述语言VHDL简述VHDL(very High Speed Integrate Circuit Hardware Description Language)是一种标准的硬件描述语言,也可以理解为超高速集成电路硬件描述语言。

由于IEEE标准硬件描述语言,在电子产业中,利用VHDL进行系统行为级设计已经成为FPGA和ASIC的设计主流。

一个完整的VHDL程序,通常包括程序包(package)、库(library)、实体(entity)、结构体(architecture)和配置(configuration)5部分。

其中,程序包用于存放各种设计模块的能共赏的数据类型、常数和子程序等;实体用于描述设计实体的外部接口信号(I/O接口);结构体用于描述设计实体的内部电路;配置用于从库中选取所需的元件,并将其安装到设计单元的实体中;库用于存放已经编译的实体、结构体、包集合和配置。

1.2.2 FPGA的DE2_70开发板简述DE2_70开发板是基于FPGA应用的一种多功能运用的电子设备,它采用了Altera Cyclone II 2C70 FPGA芯片,给用户提供了方便,且所有的端口都是由FPGA来驱动,其可以利用硬件描述语言,通过软件编程、仿真、编译、最终下载到开发板上,从而实现具有特定功能的电路。

以下对DE2_70开发板的一些驱动管脚及芯片型号做简单是描述闭应明图1 DE2_70开发板DE2平台上提供的资源如下:1、Altera Cyclone II 系列的EP2C35F672C6 FPGA芯片(板上器件标号U11),该芯片内含35 000个逻辑单元(LE)。

2、主动串行配置器件EPCS16(板上器件标号U30)。

3、板上内置用于编程调试和用户API设计的USB Blaster,支持JTAG模式和AS模式;U25是实现USB Blaster的USB接口芯片FT245B;U26是用于控制和实现JTAG 模式和AS模式的CPLD器件EPM3128,可以通过SW19选择配置模式;USB接口为J9。

4、512K字节SRAM(U18)。

5、8M字节(1Mx4x16)SDRAM(U17)。

6、1M字节闪存(可升级至4M字节)(U20)。

7、SD卡接口(U19)。

8、4个按键KEY0 ~ KEY3。

9、18个拨动开关SW0 ~ SW17。

10、9个绿色LED灯LEDG0 ~ LEDG8。

11、18个红色LED灯LEDR0 ~ LEDR17。

12、两个板上时钟源(50MHz晶振Y1和27 MHz晶振Y3),也可通过J5使用外部时钟。

13、24位CD品质音频编/解码器WM8371(U1),带有麦克风输入插座J1、线路输入插座J2和线路输出插座J3。

14、VGA DAC ADV7123(U34,内含3个10位高速DAC)及VGA输出接口J12。

15、支持NTSC和PAL制式的TV解码器ADV7181B(U33)及TV接口J12。

第二章电子时钟设计第二章电子时钟设计2.1 电子钟的功能设计指标A、支持日历和当日事件提醒两种显示模式;B、具有电子钟的基本功能:年月日显示、是否闰年提示、阴阳历显示、中国传统重要节日提醒、中国24节气提示;C、支持定时自动关机功能;D、支持闹铃功能;E、FPGA基于DE2开发板。

2.2 电子钟的整体构造本电子时钟系统含有分频模块、计时模块、显示模块、节气提醒模块、闹铃提醒模块、传统节假日提醒模块、定时关机模块,阳历转阴历模块、译码转换模块等。

分频器通过晶振得到1HZ的频率时钟信号,加载到秒模块中,通过异步的计数方式,从而实现时钟计数的驱动。

通过译码转换模块,可以实现显示模块和提醒模块的功能,具体的框架图如下图所示:图2 电子钟结构闭应明2.2.1 分频模块详细代码描述见附录分频模块图3管脚说明如下Clk:50MHZ时钟输入COUT:1HZ时钟输出图3 50分频结构2.2.2 秒模块秒模块采用60进制,分频模块输出的时钟信号作为该模块的时钟信号clks,每当时钟的上升沿来时,就开始计数,即从0计数到59,之后返0,再开始计数到59,如此反复,每当计数到59后,都会产生一个进位信号clk1,这个进位信号作为分模块的时钟信号。