第五讲 verilog设计进阶

verilogHDL培训教程华为

verilogHDL培训教程华为近年来,随着人工智能、物联网和5G等新兴技术的快速发展,数字电路设计和FPGA开发方面的需求也越来越迫切。

而Verilog HDL已成为数字电路设计中最受欢迎和广泛使用的硬件描述语言之一。

因此,华为公司推出了一系列的Verilog HDL培训教程,帮助从业人员快速获得这个技能。

华为Verilog HDL培训教程的特点华为Verilog HDL培训教程主要针对初学者和中级学员,旨在让学生掌握Verilog HDL基础和应用。

教程内容科学、系统,结合了中国实际情况,给人耳目一新的感觉。

华为Verilog HDL培训教程遵从"理论与实践相结合"的原则,保证学生能够灵活应用所学知识。

在理论教学方面,华为Verilog HDL培训教程先后介绍和讲解了Verilog HDL的基础概念、语法、数据类型、运算符、模块等。

在实践操作方面,华为Verilog HDL培训教程采用基于FPGA芯片的开发板完成实验,让学生能够真正体验到数字电路设计的工程化过程。

此外,华为Verilog HDL培训教程融合了多元化的教学形式,通过讲解PPT、操作演示视频、实验文档等多种形式进行教学。

教材编制过程中对各章节的课程设计进行了充分的考虑,让学生可以从基础入手,系统性、完整性地掌握Verilog HDL语言。

总之,华为Verilog HDL培训教程尽力使学习过程严谨、声音,减少因知识不足而带来的错误和困惑。

华为Verilog HDL培训教程的课程设置华为Verilog HDL培训教程旨在让学员了解数字电路设计中最常用的硬件描述语言-- Verilog HDL,并在FPGA开发板上完成一些典型实验。

华为Verilog HDL培训教程包含以下章节:第一章:Verilog HDL基础概念在本章中,学生将学习Verilog HDL的起源、产生背景、基本概念、Verilog HDL的体系结构、Verilog HDL模块体系结构等知识。

verilog数字系统设计教程

verilog数字系统设计教程Verilog数字系统设计教程作者:XXX引言:数字系统设计是现代电子工程中非常重要的一部分。

Verilog作为一种硬件描述语言,提供了一种方便且专业的方法来设计和描述数字系统。

本教程旨在为初学者提供关于Verilog数字系统设计的详细介绍和指导。

1. Verilog简介Verilog作为一种硬件描述语言,用于描述数字系统的功能、结构和时序行为。

它类似于C语言,但更专注于硬件级别。

Verilog可以用于设计各种数字系统,例如处理器、嵌入式系统、通信设备等。

2. Verilog基本语法2.1 模块定义Verilog的基本单位是模块。

模块是数字系统的基本组成部分,可以看作是一个独立的功能单元。

模块可以包含输入、输出、内部信号以及其它子模块等。

2.2 信号声明在Verilog中,可以声明各种类型的信号,包括输入信号、输出信号和内部信号等。

信号声明定义了信号的类型、宽度和方向。

3. Verilog建模3.1 组合逻辑建模组合逻辑是数字系统中最基本的部分。

Verilog提供了各种组合逻辑建模的方法,包括逻辑运算、选择结构和多路复用器等。

3.2 时序逻辑建模时序逻辑是数字系统中需要考虑时序关系的部分。

Verilog提供了时序逻辑建模的方法,包括触发器、计数器和时序控制等。

4. Verilog仿真4.1 仿真器介绍仿真器是用于验证数字系统设计的工具。

Verilog可以与各种仿真器配合使用,用于验证设计的正确性和性能。

4.2 仿真流程仿真流程包括编写测试平台和测试用例、编译和仿真等步骤。

本节将介绍基本的仿真流程和相关技巧。

5. Verilog综合5.1 综合概述综合是将Verilog代码转换为逻辑门级描述的过程。

综合器通过将Verilog代码映射到实际的硬件库中,生成能够实现指定功能的逻辑电路。

5.2 综合流程综合流程包括综合前的优化和综合本身两个阶段。

本节将介绍综合的基本流程和主要考虑因素。

verilog教程

verilog教程当您开始学习Verilog时,以下是一些重要的基础知识和概念。

1. Verilog是一种硬件描述语言(HDL),用于描述和设计数字电路。

它可以用于模拟、合成和验证电路。

2. Verilog使用模块化的设计风格。

每个设计都由一个或多个模块组成,每个模块有自己的输入和输出。

3. 使用`module`关键字定义一个模块,并在其后给出模块的名称。

```verilogmodule my_module;// 模块主体endmodule```4. 模块内部包含用`input`和`output`声明的端口,用于与其他模块进行通信。

```verilogmodule my_module(input wire a,input wire b,output wire c);// 模块主体endmodule```5. `wire`关键字用于声明连接不同模块的导线。

可以将导线看作是用于传输数字信号的线。

6. 在模块主体中,可以使用`assign`关键字创建逻辑连接。

逻辑连接使用`=`运算符连接输入和输出。

```verilogmodule my_module(input wire a,input wire b,output wire c);assign c = a & b;endmodule```7. 除了逻辑连接外,可以在模块内部使用`always`块创建组合和时序逻辑。

```verilogmodule my_module(input wire a,input wire b,output wire c);reg d;always @(a or b)d = a | b;assign c = d;endmodule```8. Verilog还支持使用`if-else`语句,`case`语句和循环结构等常见的编程结构。

9. 为了模拟和验证设计,可以使用Verilog仿真工具,如ModelSim、VCS等。

Verilog入门

第五章 Verilog 语言

Verilog 语法与实例

• 数字表示:整数,实数 整数:+/- <位宽> ‘<基数符号> <数值>

<位宽>:指定整数的大小,以bit为单位。

<基数符号>:指定整数的基数,可以是b(binary)二进

制;o(octal)八进制;d(decimal)十进制;h(hex-

adecimal)十六进制。

第五章 Verilog 语言

Verilog 语法与实例

• Verilog的四种逻辑状态: 0:逻辑零、逻辑非、低电平 1:逻辑1、逻辑真、高电平 x或X:不定态 z或Z:高阻态

第五章 Verilog 语言

verilog语言及程序设计

verilog语言及程序设计Verilog语言及程序设计什么是Verilog语言?Verilog是一种硬件描述语言(HDL),用于描述数字系统的行为和结构。

它最初是由Gateway Design Automation公司(现在是Cadenza Design Automation公司的一部分)于1984年开发的,用于模拟和验证集成电路设计。

Verilog不仅可以用于模拟和验证电路设计,还可以用于编写可综合的硬件描述。

可综合的硬件描述可以通过合成工具转换成实际的硬件电路,在FPGA(现场可编程门阵列)和ASIC(应用特定集成电路)中实现。

Verilog的应用领域Verilog广泛应用于数字系统的设计、验证和实现。

它可以用于设计各种数字电路,包括处理器、存储器、通信接口、数字信号处理器等。

Verilog还被用于编写可综合的程序,用于验证电路设计的正确性。

Verilog的基本语法Verilog语言的基本语法与C语言类似,包括模块定义、端口声明、信号声明、组合逻辑、时序逻辑等。

下面是一个简单的Verilog模块的例子:verilogmodule MyModule (input wire clk,input wire rst,input wire in_data,output wire out_data);reg [7:0] reg1;always (posedge clk or posedge rst) beginif (rst)reg1 <= 8'b0;elsereg1 <= reg1 + in_data;endassign out_data = reg1;endmodule上面的例子定义了一个名为`MyModule`的Verilog模块,有4个端口:`clk`(时钟),`rst`(复位),`in_data`(输入数据),`out_data`(输出数据)。

其中的`reg1`是一个8位的寄存器,使用时序逻辑进行更新。

VerilogHDL语言基础教材教学课件

1990年代,Verilog HDL成为IEEE标准,并不断发展完善。

新版本

随着数字电路设计的发展,Verilog HDL不断推出新版本,支持更高级的硬件描述和验证功能。

Verilog HDL的历史和发展

01

02

03

04

ASIC设计

在ASIC设计中,Verilog HDL用于描述数字电路的结构和行为。

FPGA设计

在FPGA设计中,Verilog HDL用于描述逻辑块、路由和IO接口等。

仿真验证

Verilog HDL还用于数字电路的仿真验证,通过模拟电路的行为来检测设计中的错误和缺陷。

学术研究

在数字电路和系统设计领域,Verilog HDL广泛应用于学术研究、教学和实验中。

Verilog HDL的应用领域

测试平台编写是指编写用于测试Verilog设计的测试平台代码。测试平台代码可以使用Verilog语言编写,并使用仿真测试平台进行测试和验证。

仿真测试平台

测试平台编写

仿真和测试平台

Verilog HDL设计实例

04

组合逻辑设计

总结词:组合逻辑设计是Verilog HDL中最基础的设计之一,主要用于实现逻辑函数。

02

数字系统设计涉及逻辑门、触发器、寄存器、组合逻辑、时序逻辑等基本数字逻辑单元的设计和组合,Verilog HDL语言能够方便地描述这些结构和行为。

03

数字系统广泛应用于计算机、通信、控制等领域,通过Verilog HDL语言可以实现高效、可靠的数字系统设计。

01

Verilog HDL的未来发展

发展趋势和挑战

THANKS

ASIC设计涉及逻辑设计、电路设计、物理实现等环节,Verilog HDL语言能够描述硬件结构和行为,为ASIC设计提供强大的支持。

第五讲 verilog设计进阶

时序逻辑设计要点 --分频 时序逻辑设计要点---分频 设计要点简单二分频: 简单二分频: reg fout1 always @(posedge clk) begin if (!rst) fout1<=0; else fout1<=!fout; 任意分频: 任意分频: 如3.5分频,7个时钟 3.5分频, 分频 中取2 中取2个,本质是模可 控计数器或状态机。 控计数器或状态机。

Task例

module bus_ctrl_tb; reg [7:0] data; reg valid, rd; cpu ul(valid,data, rd); initial begin cpu_driver (8’b0000_0000); cpu_driver (8’b1010_1010); cpu_driver (8’b0101_0101); end

clk rst

½ f

q

不能综合的 Verilog 结构

1. 2. 3. 4. 5. 6. 7. 8. 9. 10. initial 循环语句: 循环语句: repeat forever while for 的非结构用法 一部分数据类型 event real time 11.UDPs 12. fork…join 块 13. wait 14. 过程连续赋值语句 15. assign 和 deassign 16. force 和 release 17. 部分操作符 18. = = = 19. != =

Verilog HDL 语法和设计 设计进阶 语法和设计进阶

武 斌

VerilogHDL的抽象级别 的抽象级别

•系统级 系统级(system) 系统级

•算法集 算法集(algorithmic) 算法集

•寄存器传输级 寄存器传输级(Register-Transfer-Lever) 寄存器传输级 •门级(结构级) (gate-lever) 门级(结构级) 门级 •开关级 开关级(switch-lever) 开关级

Verilog设计深入PPT学习教案

5.2 过程结构总结

always语句 ——无 限循 环语句 always语句在仿真过程中是不断重复执行的,但always语句后跟着的 过程块是否执行,则要看它的触发条件是否满足,如满足则运行块一 次,如不断满足,则循环执行 格式: always <时序控制> <语句> 注意: always语句由于其不断重复执行特性,只有和一定的时序控制 结合在一起才有用,如果一个always语句没有时序控制,则这个 always语句将回生成一个仿真死锁。如: always areg = ~areg;

output q,a;

reg q,a;

input clk;

always @(posedge clk)

reg q,a;

begin

always @(posedge clk)

q=~q; //阻塞赋值语 对前一时刻的q值取反

句

begin

对 前 一 时 刻 的q值取 反

a=~q;

a=~q;

q=~q;

end

对 当 前 时 刻 的q值取 反

reg b, c, d;

always @( b ) begin

d <= c; e = d; end

always @(posedge clk) b <= a;

endmodule

c

= b;

第4页/共78页

5.1 过程中的两类赋值 语句

5.1.3 深 入 认 识 阻 塞赋值 和非阻 塞式赋 值的特 点

第5页/共78页

简 单 延 时 (#delay): 延 迟 指 定时 间步后 执行

边 沿 敏 感 的 时序控 制:@(<signal>)

Verilog设计层次及风格

➢ 【例9.4】包含x态输入的1位全加器进位输出UDP元件

primitive carry_udpx(cout,cin,a,b); input cin,a,b; output cout; table //cin a b : cout //真值表

改用endprimitive关键词结束。

➢ 与一般的模块相比,UDP模块具有下面一些特点: 1. UDP的输出端口只能有一个,且必须位于端口列表的第一项。只有输出端口能被定义为reg类

型。

2. UDP的输入端口可有多个,一般时序电路UDP的输入端口可多至9个,组合电路UDP的输入端

口可多至10个。

➢ 上拉、下拉电阻

pullup(上拉电阻) pulldown(下拉电阻)

➢ 基本门的逻辑真值表

nand 有0则1,全1则0,其它x; nor 有1则0,全0则1,其它x; xor 01则1, 全1则0,全0则0,其它x; xnor 全0则1,全1则1,01则0, 其它x; buf 入出相同; not 01相反,其它x; bufif1 0控则z,1控则同; bufif0 1控则z,0控则同; notif1 0控则z,1控则反; notif0 1控则z,0控则反。

0 0 0 : 0; 0 1 0 : 0; 0 0 1 : 0; 0 1 1 : 1; 1 0 0 : 0; 1 0 1 : 1; 1 1 0 : 1; 1 1 1 : 1;

0 0 x : 0; 0 x 0 : 0; x 0 0 : 0; 1 1 x : 1; 1 x 1 : 1; x 1 1 : 1; endtable endprimitive

verilog教程

verilog教程Verilog是一种硬件描述语言(HDL),用于设计和描述数字电路。

它是一种事件驱动的语言,可以用来描述时序逻辑和组合逻辑。

Verilog可以用于设计和验证各种数字电路,从简单的门电路到复杂的处理器和系统。

Verilog的语法和结构与C语言相似,它由模块、端口、信号和行为描述组成。

Verilog中的模块是模块化设计的基本单元,可以将模块集成到更大的设计中。

模块可以具有输入端口、输出端口和内部信号。

输入和输出端口用于与其他模块进行通信,而内部信号用于在模块内部传递和保存数据。

Verilog的行为描述方式包括并行块和顺序块。

并行块表示同时执行的代码,而顺序块表示按顺序执行的代码。

Verilog中的并行块使用关键字"always @(posedge clock)"来表示,其中的代码只在时钟上升沿触发时执行。

顺序块使用关键字"always @(*)"来表示,其中的代码在输入信号变化时立即执行。

在Verilog中,可以使用各种逻辑运算符,如AND、OR、NOT和XOR,来实现组合逻辑。

此外,还可以使用各种触发器和寄存器类型,如D触发器和JK触发器,来实现时序逻辑。

通过将组合逻辑和时序逻辑结合起来,可以实现复杂的数字电路。

Verilog的仿真可以使用各种工具,如ModelSim和Vivado,来验证设计的正确性。

仿真可以通过将输入信号施加到设计中,然后观察输出信号的变化来进行。

如果输出信号与预期的结果一致,那么设计就是正确的。

在Verilog中,还可以使用分层设计的概念来实现模块的结构化和组织。

通过使用层次化模块,可以将设计划分为更小的模块,并将它们组合在一起以实现更大的系统。

尽管Verilog的学习曲线可能有点陡峭,但它是数字电路设计中最常用和最强大的工具之一。

通过掌握Verilog,您可以实现自己的数字电路设计,并进行验证和测试。

总之,Verilog是一种用于设计和描述数字电路的硬件描述语言。

verilog设计的层次与风格课件

01x z

01x z

输0 z 1 H H输0 1 z H H

入

入

1z0LL

10 z L L

xzxxx

xxzxx

z z xxx

zxzxx

verilog设计的层次与风格

10

2.门元件的调用

调用门元件的格式为:

门元件名字 <例化的门名字>(<端口列表>)

其中普通门的端口列表按下面的顺序列出:

(输出,输入1,输入2,输入3……);

verilog设计的层次与风格

16

2.4 数据流描述

格式:assign LHS_net=RHS_expression;

【例2.3】 数据流描述的4选1 MUX module mux4_1c(out,in1,in2,in3,in4,s0,s1); input in1,in2,in3,in4,s0,s1; output out; assign out=(in1 & ~s0 & ~s1)|(in2 & ~s0 & s1)| (in3& s0 & ~s1)|(in4 & s0 & s1); endmodule

27

【例2.15】 用模块例化方式设计的1位全加器顶层设计

module full_add(ain,bin,cin,sum,cout);

input ain,bin,cin; output sum,cout;

wire d,e,f;

//用于内部连接的节点信号

half_add u1(ain,bin,e,d);

{cout,sum}=a+b+cin; end endmodule

verilog设计的层次与风格

第-五讲--行为建模PPT课件

西安邮电学院通信工程系

格式: begin: 块名 … end 或 fork:块名 … join

第五讲 行为建模

过程的时序控制

西安邮电学院通信工程系

在过程块中可以说明过程时序。过程时序控制有三类: ❖ 延时执行:#delay, 延迟指定时间步后执行语句 ❖ 边沿敏感事件的时序控制:@(<signal>)

第五讲 行为建模

有名块

有名块的块名作用: ❖ 便于实现对块语句的有效控制 用disable语句终止或提前结束有名块的执行过

程 ❖ 允许在块内引入局部变量 只在块内起作用的变量 变量名可以和块外的其他变量名相同 一定是寄存器类 例: begin: SEQ_BLK

reg[3:0] sat sat = mask & data; ff = ^sat; end

❖ Verilog的行为建模是用一系列以高级编程语言编写的并行的、动态的过

程块来描述系统的工作。

D触发器行为

在每一个时钟上升沿,

若Clr不是低电平,

ห้องสมุดไป่ตู้

置Q为D值,

置Qb为D值的反

无论何时Clr变低 置Q为0, 置Qb为1

第五讲 行为建模

西安邮电学院通信工程系

过程块(procedural)

❖ 过程块是行为模型的基础。一个模块中可以有多个过程块,过程块有两种:

第五讲 行为建模

西安邮电学院通信工程系

行为建模(描述)

❖ 行为级描述是对系统的高抽象级描述。在这个抽象级,注重的是整个系 统的功能而不是实现。

❖ Verilog有高级编程语言结构用于行为描述,包括:initial, always,@, wait, for, while, if else, case 和 forever 等。

VerilogHDL设计进阶专题知识讲座

6.8 Verilog HDL旳RTL表述

6.8.2 数据流描述

6.8.3 构造描述

习题

6-1 在Verilog设计中,给时序电路清零(复位)有两种不同措施,它们是什么,怎 样实现? 6-2 哪一种复位措施必须将复位信号放在敏感信号表中?给出这两种电路旳Verilog 描述。 6-3 用不同循环语句分别设计一种逻辑电路模块,用以统计一8位二进制数中含1旳 数量。 6-4 用循环语句设计一种7人投票表决器。 6-5 设计一种4位4输入最大数值检测电路。 6-6 从不完整旳条件语句产生时序模块旳原理看,例6-9和例6-10从表面上看都包括 不完整条件语句,试阐明,为何例6-9旳综合成果含锁存器,二例6-10却没有。 6-7 设计一种求补码旳程序,输入数据是一种有符号旳8位二进制数。 6-8 设计一种比较电路,当输入旳8421BCD码不小于5时输出1,不然输出0。 6-9 用原理图或Verilog输入方式分别设计一种周期性产生二进制序列01001011001 旳序列发生器,用移位寄存器或用同步时序电路实现,并用时序仿真器验证其功能。 6-10 基于原理图输入方式,用74194、74273、D触发器等器件构成8位串入并出旳 转换电路,要求在转换过程中数据不变,只有当8位一组数据全部转换结束后,输 出才变化一次。

试验与设计

6-3 VGA彩条信号显示控制电路设计

(1)试验目旳: (2)试验原理:

试验与设计

6-3 VGA彩条信号显示控制电路设计

(1)试验目旳:GA彩条信号显示控制电路设计

(1)试验目旳: (2)试验原理:

试验与设计

6-3 VGA彩条信号显示控制电路设计

第6章 Verilog HDL设计进阶

6.1 过程构造中旳赋值语句

Verilog设计进阶

可综合的设计中应注意

➢ 不使用初始化语句;不使用带有延时的描述;不使用循环 次数不确定的循环语句,如forever,while等。 ➢ 应尽量采用同步方式设计电路。除非是关键路径的设计, 一般不采用调用门级元件来描述设计的方法,建议采用行为语 句来完成设计。 ➢ 用always过程块描述组合逻辑,应在敏感信号列表中列出块 中出现的所有输入信号。

2. ZigBee特性

9 9)数据传输可靠 ZigBee的媒质传入控制层(MAC层)采用talk-whenready的碰撞避免机制。在这种完全确认的数据传输机制 下,当有数据传送需求时则立刻发送,发送的每个数据 分组都必须等待接收方的确认消息,并进行确认信息回 复。若没有得到确认信息的回复就表示发生了冲突,将 重传一次。采用这种方法可以提高系统信息传送的可靠 性。ZigBee为需要固定带宽的通信业务预留了专用时隙,

为2美元。

3)低速率

3

ZigBee工作在20~250kbps的速率,分别提供250 kbps(2.4GHz)、

40kbps(915 MHz)和20kbps(868 MHz)的原始数据吞吐率,满足低速率传输数

据的应用需求。

第五章

5.1ZigBee介绍

5.1.1 什么是ZigBee

2. ZigBee特性

Zigbee是一种新兴的短距离、低速率无线网络技术,它

是一种介于无线标记技术和蓝牙之间的技术方案。它有自

己的无线电标准,在数千个微小的传感器之间相互协调实

第五章

5.1ZigBee介绍

5.1.1 什么是ZigBee

2. ZigBee特性

1)低功耗

1 在工作模式下,ZigBee技术的传输速率低,传输数据量很小, 因此信号的收发时间很短。其次,在非工作模式情况下,ZigBee的 节点处于休眠状态。设备搜索延迟一般为30ms,休眠激活时延为 15ms,活动设备接入信道时延为15 ms。由于工作时间较短,收发信 息功耗较低且采用了休眠模式,使得ZigBee节点非常省电。ZigBee 节点的电池工作时间可以长达6个月到2年左右,对于某些占空比 (工作时间/(工作时间+休眠时间))小于1%的应用,电池的寿命 甚至可以超过十年。相比较蓝牙仅能工作数周,WIFI仅可工作数小 时。

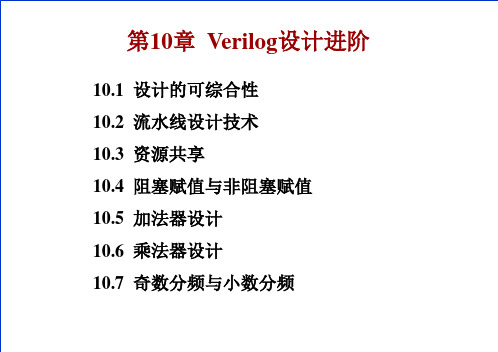

第10章-Verilog设计进阶

Latch

Latches cover less area as compared to flipflops.

Latches make DFT scan insertion difficult. Latches make static analysis complicated. Flip-flops are preferred. A latch is inferred when a conditional

always @(weather) case (weather) sunny : action <= motorcycling; snowy : action <= skiing; windy : action <= paragliding; endcase

18

Hints

Always cover all the case in order to avoid unintentional latch inference.

=== and !==

7

HDL Compiler Unsupport (2)

Division and modulus operators can’t be used as following example

Note: division can be done using design-ware instantiation

statement is incompletely specified. A latch may also get inferred from an

incompletely specified case statement.

15

Latch in if

always @(weekend) begin

Verilog设计进阶

//用case语句进行译码

6.5 循环语句

在Verilog中存在四种类型的循环语句,用来控制语句的执行次数。这四 种语句分别为: (1)forever:连续地执行语句;多用在“initial”块中,以生成时钟等周 期性波形。 (2)repeat:连续执行一条语句n次。 (3)while:执行一条语句直到某个条件不满足。 (4)for:有条件的循环语句。

宏替换`define

`define语句用于将一个简单的名字或标志符(或称为宏名)来 代替一个复杂的名字或字符串,其使用格式为: `define 宏名(标志符) 字符串 如:`define sum ina+inb+inc+ind 在上面的语句中,用简单的宏名sum来代替了一个复杂的表 达式ina+inb+inc+ind,采用了这样的定义形式后,在后面的 程序中,就可以直接用sum来代表表达式ina+inb+inc+ind了。

for loop

initial begin for(i=0;i<4;i=i+1) out = out +1; end

repeat loop

initial begin repeat(5) out = out +1; end

while loop

initial begin i=0; while(i<0) i=i+1; end

阻塞赋值与非阻塞赋值

非阻塞赋值仿真波形图

阻塞赋值仿真波形图

阻塞赋值与非阻塞赋值

非阻塞赋值综合结果

阻塞赋值综合结果

6.4 条件语句

( if-else语句) if-else语句使用方法有以下3种: (1)if(表达式) 语句1; (2)if(表达式) 语句1; else 语句2; (3)if(表达式1) 语句1; else if(表达式2) 语句2; else if(表达式3) 语句3; …… else if(表达式n) 语句n; else 语句n+1;

verilog语法进阶

verilog语法进阶模块的结构、数据类型、变量和基本运算符号3.1.模块的结构Verilog的基本设计单元是“模块”(block)。

一个模块是由两部分组成的,一部分描述接口,另一部分描述逻辑功能,即定义输入是如何影响输出的。

下面举例说明:图1 模块示例m请看上面的例子: 程序模块旁边有一个电路图的符号。

在许多方面,程序模块和电路图符号是一致的,这是因为电路图符号的引脚也就是程序模块的接口。

而程序模块描述了电路图符号所实现的逻辑功能。

以上就是设计一个简单的Verilog程序模块所需的全部内容。

从上面的例子可以看出,Verilog结构位于在module和endmodule声明语句之间,每个Verilog程序包括四个主要部分:端口定义、I/O说明、内部信号声明、功能定义。

3.1.1、模块的端口定义模块的端口声明了模块的输入输出口。

其格式如下:module 模块名(口1,口2,口3,口4, ………);…….endmodule模块的端口表示的是模块的输入和输出口名,也就是它与别的模块联系端口的标识。

在模块被引用时,在引用的模块中,有些信号要输入到被引用的模块中,有的信号需要从被引用的模块中取出来。

在引用模块时其端口可以用两种方法连接:1)在引用时,严格按照模块定义的端口顺序来连接,不用标明原模块定义时规定的端口名,举例说明如下:模块名实例化名(连接端口1信号名, 连接端口2信号名,连接端口3信号名,….,,,);2)在引用时用“.”标明原模块定义时规定的端口名,举例说明如下:模块名实例化名(.端口1名( 连接信号1名),.端口2名( 连接信号2名),….,,,);这样表示的好处在于可以用端口名与被引用模块的端口对应,不必严格按端口顺序对应,提高了程序的可读性和可移植性。

3.1.2、模块内容模块的内容包括I/O说明、内部信号声明、功能定义。

3.1.2.1、I/O说明的格式如下:输入口: input [信号位宽-1 :0] 端口名1;input [信号位宽-1 :0] 端口名2;………;input [信号位宽-1 :0] 端口名i; //(共有i个输入口)输出口: output [信号位宽-1 :0] 端口名1;output [信号位宽-1 :0] 端口名2;………;output [信号位宽-1 :0] 端口名j; //(共有j个输出口)输入/输出口:inout [信号位宽-1 :0] 端口名1;inout [信号位宽-1 :0] 端口名2;………;inout [信号位宽-1 :0] 端口名k; //(共有k个双向总线端口)I/O说明也可以写在端口声明语句里。

第6章 Verilog HDL设计进阶

12

1.initial语句

1. initial块从仿真0时刻开始执行,在整个仿真过程中只执行一 次; 2. initial块内部的语句是顺序执行的; 3.如果一个模块里包含多个initial块,则这些initial块从仿真0时 刻开始并发执行,且每个块的执行是各自独立的 4.作用:一般用于初始化、信号监视、生成仿真波形等目的。 5. initial是一条主要面向模拟仿真的过程语句,通常不被综合 工具所接受。

例6-2中,对Q1的多次赋值是允许的,最终Q1获得表达式

C∧A的值。

4

第6章 Verilog HDL设计进阶

说明:

假设A与B在同一时刻从0变化到1。例6-3与例6-4都讲启动过程。 例6-3中最终Q的值是1

例6-4中,3条语句是同时赋值的,因此Q得到的值是M1与M2在A、 B变动以前的值0。

always

#10 clock=~clock; //产生周期为20的脉冲

initial #1000 $finish;

endmodule

第6章 Verilog HDL设计进阶

6.3

移位寄存器之Verilog HDL设计

1、移位指令分类

普通移位指令: 逻辑左移、逻辑右移

算术左移、算术右移

循环移位:不带进位位的循环

工作过程:当CLK的上升沿到来时,过程被启动,如果 LOAD是高电平,则把DIN端口的8位数据被同步并行置入寄存 器里面。如果LOAD是低电平则执行。

REG8[6:0] <= REG8[7:1] ;

原来的的最低位REG8[0]向QB输出.

29

第五讲verilog设计进阶

3 可预置数双向可控寄存器实例

in

rst

out

dir

时序逻辑设计 ----计数器

? 举例3-21 (P90) 改进 reg[3:0] q wire out; always@(posedge clk )q=q+1; assign out=(q==4‘h)f 1:0; // 其他写法

? 模计数器,2n (模可控)任意进制计数器

clk counter q

rst

regs

count<=count+1;

assign out=(count==2 n-1)?1:0;//?

2 带复位模计数器 always @(posedge clk) if(!rst) count<=0; else count<=count+1; assign out=(count== 2 n-1)?1:0; //毛刺?

input [7:0]a,b;

input [7:0]a;

input clk;

input clk;

output [8:0] sum;

output [8:0] sum;

reg[8:0] sum;

reg[8:0] sum;

always @(posedge clk)

always @(posedge clk)

sum<=a+b;

sum<=a+sum;

endmodule

endmodule

regs

regs

时序逻辑设计方法

移位寄存器实例:

1 按位描述

左移 reg [7:0] shift; always@(posedge clk)

begin shift[7:1]<=shift[6:0]; shift[0]<=din; end

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2 带复位模计数器 always @(posedge clk) if(!rst) count<=0; else count<=count+1; assign out=(count== 2n-1)?1:0; //毛刺?

具有寄存器输出计数器(两种风格)

合写为: always @(posedge clk) reg out; if(!rst) begin always @(posedge clk) count<=0; out<=0; if(!rst) count<=0; end else else if(count== 2n-1) count<=count+1; begin always @(posedge clk) count<=0; out<=1; if(!rst) out<=0; end n-1) else if(count== 2 else begin out<=1; count<=count+1; out<=0; else out<=0; end

设计示例(续)

START:if (A) begin state <= STOP; F<=0; end else state <=IDLE STOP: begin state <= IDLE; //状态合并 F<=A; //????? end default: begin state <=IDLE; F<=0; end endcase endmodule

endcase endmodule

状态机设计要点(Mealy型)

单过成结构: module state(…A…) always @(posedge clock) if (!rst) begin do_rst; state<=xx; end else case(state) state_1: if(A) begin do_1; state<=xx; end else….; state_2: if(A) begin do_2; state<xx; end else……; …… default: begin do_n state <=xx; end endcase endmodule 多过程略去

计数器组合逻辑与寄存器输出区别

rst clk

count

out

000

001

010

011

100

101

110

111

000

4 模可控计数器(任意进制:m<2n-1 )

同步复位法 always @(posedge clk) 同步置数法…... if (!rst) begin count<=0;out<=0; end …… else if (count==m-1) else if (counter==2n-1) begin counter<= 2n-m-1; count<=0; out<=1; out<=1; end else……. else begin count<= count+1; out<=0; end

a clk rst

counter regs

q

else if(a==1) begin count<=count+1; out<=0; end end else; endmodule

例:模可控计数器---7进计数器

module counter(rst,clk,out); input clk,rst; output out; reg out; reg[2:0] count; always @(posedge clk) if(rst==0) begin count<=0; out<=0; end else if(count==6) begin out<=1; count<=0; end else begin out<=0; count<=count+1; end endmodule

• 多过程结构 • 单过程结构

状态机设计要点(Moore型)

单过程: 一个时序块

module state(……) reg[2:0] state; parameter ST0=3’b000, ST1=3’b001, ……;//参数 always @(posedge Clock) if (!reset) state <=ST0; else case(state) ST0:begin state <= ST1; out0=?; end

Mealy型计数器

module counter(……..) input rst,clk, a; …… reg[n-1:0] count always @(posedge clock) begin if (!rst) begin count<=0; out<=0; end else if (count==m-1&&a==1) begin out<=1; count<=0; ete machine

什么是状态机:时序控制电路, 1、复杂逻辑设计的核心, 2、高效的顺序控制 3、极高稳定型,摆脱毛刺干扰 4、处理速度极快 5、规范的程序表达 :一个always块

状态机设计要点

状态的选择 • typedef enum{s0,s1,…..} type_user //枚举类型 type_user state,next_state; 用独热码来表示同一个有限状态, • parameter Idle= 4’b1000, Start = 4’b0100, • Stop= 4’b0010, Clear = 4’b0001; 使用参数和宏定义 • `define ?? ?? • parameter ??=??; 状态机设计结构(两种风格)

Moore型设计实例

脉冲分配器:

日历: 3个60进制计数器 1个24进制计数器 至少6个数码管 显示驱动: BCD调整, 16转10进制 数码管驱动逻辑

显示驱动:动态静态

60 计数

60 计数

24 计数

分频器设计案例

简单二分频: reg fout always @(posedge clk) begin if (!rst) fout<=0;// fout<=fout+1; else fout<=!fout; 任意分频: 计数器分频: count<=count+1; 如3.5分频,7个时钟中取2 assign f_2_1=count[0]; 个,本质是模可控计数器 assign f_4_1=count[1]; 中取出若干状态 assign f_8_1=count[2]; ………

时序逻辑设计方法

移位运算符 <<n:和 >>n: 无符号数左右移n位,空位补0 <<<n和 >>>n :有符号数左移右移, 左移补0,右移补符号位

reg [7:0] shift; always@(posedge clk) begin shift<=shift<<1; shift[0]<=din; end reg [7:0] shift; always@(posedge clk) begin shift<=shift>>1; shift[7]<=din; end

Moore型模计数器设计…..(案例)

1 自启动模计数器(2n) module counter(……..) ; wire out; clk reg[n-1:0] count; rst always @(posedge clk) count<=count+1; assign out=(count==2n-1)?1:0;//? counter regs

ST1: begin state <=ST2; out1<=?; end ……………….. STn: begin state <=ST0; outn<=?; end default: begin state <=0; out0,out1…<=?; end endcase

状态机设计要点

多过程结构 多个块:组合、时序分开 也可按变量分开 module state(……) …… parameter ST0=3’b000, ST1=3’b001, ……;//参数 reg[n-1:0] state,next_st; always @(posedge clock) if (!rst) state<=ST0; else state <= next_st; // state <= state+1; always @(state) case(state) ST0:begin out1=?; out2=?;… next_st =ST1; end ST1: … next_st =ST2; ST2: … default: next_st =ST0;

移位寄存器案例

2 循环(左循环右循环): 右循环描述 shift[7:1]<=shift[6:0]; shift[6:0]<=shift[7:1]; shift[0]<=shift[7] ; shift[7]<=shift[0];

3 可预置数双向可控寄存器实例

in rst dir out

时序逻辑设计----计数器

• 举例3-21 (P90) 改进 reg[3:0] q wire out; always@(posedge clk)q=q+1; assign out=(q==4‘hf)1:0; // 其他写法

• 模计数器,2n (模可控)任意进制计数器 置数法,复位法 Moore型,输出只与当前状态有关,一般只有clk Mealy型,输出不仅与当前状态有关,也与此时输入有关 parameter 和 define的使用