AVR指令

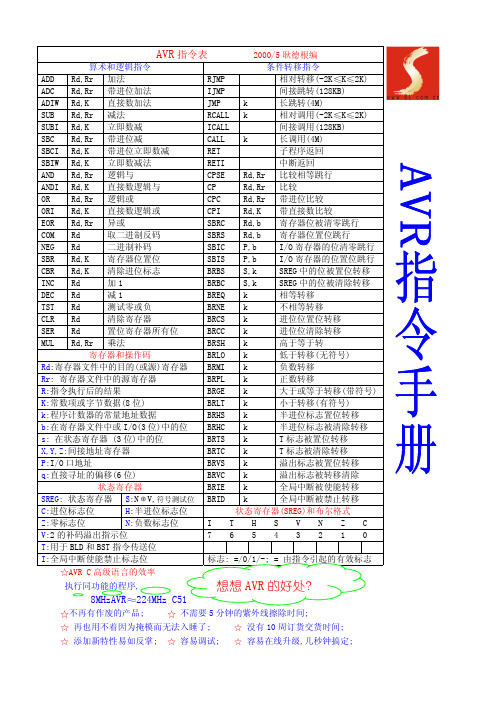

AVR指令表

(-2K 28KB)(-2K 28KB) 执行同功能的程序 8MHzAVR 224MHz C5不再有作废的产品; 不需要5分钟的紫外线擦除时间;再也用不着因为掩模而无法入睡了;没有10周订货交货时间; 添加新特性易如反掌;容易调试;容易在线升级,几秒钟搞定;AVR指令表2000/5耿德根编数据传送指令位指令和位测试指令MOV Rd,Rr寄存器拷贝LSL Rd逻辑左移LDI Rd,K装入立即数LSR Rd逻辑右移LDS Rd,K直接从SRAM装入ROL Rd通过进位左循环LD Rd,X X变址间接装入R ROR Rd通过进位右循环LD Rd,X+X变址ASR Rd算术右移LD Rd,-X X变址SWAP s半字节交换LD Rd,Y Y变址BSET s置状态寄存器的位LD Rd,Y+Y变址BCLR s SREG中的位清除LD Rd,-Y Y变址SBI P,b置I/O寄存器的位LDD Rd,Y+q Y变址间接装入R CBI P,b清I/O寄存器的位LD Rd,Z Z变址BST Rr,b R中位到SREG中T标志LD Rd,Z+Z变址BLD Rd,b SREG中T标志到R某位LD Rd,-Z Z变址SEC置位进位标志LDD Rd,Z+q Z变址CLC清除进位标志STS K,Rr R数据直接送SRAM SEN置位负数标志ST X,Rr X变址间接装入SRAM CLN清除负数标志ST X+,Rr X变址SEZ置位零标志ST-X,Rr X变址CLZ清零标志位ST Y,Rr Y变址SEI置位全局中断标志ST Y+,Rr Y变址CLI清除全局中断标志ST-Y,Rr Y变址SES置位符号标志STD Y+q,Rr变址间接装入SRAM CLS清除符号标志ST Z,Rr Z变址SEV置位溢出标志位ST Z+,Rr Z变址CLV清除溢出标志ST-Z,Rr Z变址SET置位T标志STD Z+q,Rr Z变址CLT清除T标志LPM装入程序存储器SEH置位半进位标志IN Rd,P I/O口数据装入到R CLH清除半进位标志OUT P,Rr寄存器数据送I/O口NOP空操作PUSH Rr压寄存器到堆栈SLEEP休眠POP Rd堆栈弹出到寄存器WDR看门狗复位汇编器伪指令(伪指令前必须加“ ..” ).BYTE-- 保存寄节到变量.CSEG-- 代码段.DB-- 字节常数.EXIT-- 退出文件.DEF-- 设置寄存器的符号名.INCLUDE--包括号外的文件.DEVICE--定义被汇编的器件.LIST-- 打开列表文件生成器.DSEG-- 数据段.LISTMAC--打开宏表达式.DW-- 字常数.MACR O-- 宏开始.ENDMACRO--宏结束.NOLIST-- 关闭列表文件生成器.EQU-- 设置符号相等于一个表达式.ORG-- 设置程序起始位置.ESEG-- EPROM段.SET-- 设置一个与表达式相等的符号A VR ICE200在线仿真器双龙电子为中国大陆总代理ICE200可仿真的器件为A T90S1200/2313/2333/4433/4414/8515/4434/8535及A Ttiny10/11/12由于仿真器的电源不对外所以ICE200也支持低电压器件A T90S I/O空间定义十六进制地址名称AT90SMEG103名称AT90S1200名称AT90S8515功能(对应8515名称,*为对应MEG103)$3F($5F)SREG SREG SREG状态寄存器$3E($5E)SPH SPH堆栈指针高$3D($5D)SPL SPL堆栈指针低$3C($5C)XDIV XTAL分频控制器 *$3B($5B)RAMPZ GIMSK GIMSK通用中断屏蔽寄存器$3A($5A)EICR GIFR通用中断标态寄存器$39($59)EIMSK TIMSK TIMSK定时器/计数器中断屏敝寄存器$38($58)EIFR TIFR TIFR定时器/计数器中断标志寄存器$37($57)TIMSK定时器/计数器中断屏敝寄存器 * $36($56)TIFR定时器/计数器中断标志寄存器 * $35($55)MCUCR MCUCR MCUCR MCU通用控制寄存器$34($54)MCUSR MCU通用控制寄存器 *$33($53)TCCR0TCCR0TCCR0定时器/计数器0控制寄存器$32($52)TCNT0TCNT0TCNT0定时器/计数器0(8位)$31($51)OCR0定时器/计数器0输出比较寄存器 * $30($50)ASSR异步方式状态寄存器 *$2F($4F)TCCR1A TCCR1A定时器/计数器1控制寄存器A$2E($4E)TCCR1B TCCR1B定时器/计数器1控制寄存器B$2D($4D)TCNT1H TCNT1H定时器/计数器1高字节$2C($4C)TCNT1L TCNT1L定时器/计数器1低字节$2B($4B)OCR1AH OCR1AH定时器/计数器1输出比较寄存器A高字节$2A($4A)OCR1AL OCR1AL定时器/计数器1输出比较寄存器A低字节$29($49)OCR1BH OCR1BH定时器/计数器1输出比较寄存器B高字节$28($48)OCR1BL OCR1BL定时器/计数器1输出比较寄存器B低字节$27($47)ICR1H定时器/计数器1输入捕获寄存器高字节 * $26($46)ICR1L定时器/计数器1输入捕获寄存器低字节 * $25($45)TCCR2ICR1H T/C1输入捕获寄存器高字节$24($44)TCNT2ICR1L T/C1输入捕获寄存器低字节$23($43)OCR2定时器/计数器2输出比较寄存器 * $22($42)$21($41)WDTCR WDTCR WDTCR看门狗定时控制寄存器$20($40)$1F($3F)EEARH EEARH EPROM地址寄存器高字节$1E($3E)EEARL EEAR EEARL EPROM地址寄存器低字节$1D($3D)EEDR EEDR EEDR EPROM数据寄存器$1C($3C)EECR EECR EECR EPROM控制寄存器$1B($3B)PORTA PORTA A口数据寄存器$1A($3A)DDRA DDRA A口数据方向寄存器$19($39)PINA PINA A口输入脚$18($38)PORTB PORTB PORTB B口数据寄存器$17($37)DDRB DDRB DDRB B口数据方向寄存器$16($36)PINB PINB PINB B口输入脚$15($35)PORTC PORTC C口数据寄存器$14($34)ODRC C口数据方向寄存器$13($33)PINC C口输入脚$12($32)P0RTD PORTD PORTD D口数据寄存器$11($31)DDRD DDRD DDRD D口数据方向寄存器$10($30)PIND PIND PIND D口输入脚$0F($2F)SPOR SPOR SPI I/O数据寄存器$0E($2E)SPSR SPSR SPI状态寄存器$0D($2D)SPCR SPCR SPI控制寄存器$0C($2C)UDR UDR UART I/O数据寄存器$0B($2B)USR USR UART状态寄存器$0A($2A)UCR UCR UART控制寄存器$09($29)UBRR UBRR UART波特率寄存器$08($28)ACSR ACSR ACSR模拟比较控制和状态寄存器$07($27)ADMUX ADC多路选择寄存器 *$06($26)ADCSR ADC状态和控制寄存器 *$05($25)ADCH ADC数据寄存器高 *$04($24)ADCL ADC数据寄存器低 *$03($23)PORIE E口数据寄存器 *$02($22)DDRE E口数据方向寄存器 *$01($21)PINE E口输入脚 *$00($20)PINF F口输入脚 *复位和中断向量向量号程序地址源源中断定义1$000/RESET/RESET硬件脚和看门狗复位2$001INT0INT0外部中断请求03$002INT1INT1外部中断请求14$003TIMER1 CAPT TIMER1 CAPT定时器/计数器1捕获事件5$004TIMER1 COMPA TIMER1 COMPA定时器/计数器1比较匹配A6$005TIMER1 COMPB TIMER1 COMPB定时器/计数器1比较匹配B7$006TIMER1 OVF TIMER1 OVF定时器/计数器1溢出8$007TIMER0 OVF TIMER0 OVF定时器/计数器0溢出9$008SPI,STC SPI,STC串行传送完成10$009UART,RX UART,RX UART,RX完成11$00A UART,UDRE UART,UDRE UART数据寄存器空12$00B UART,TX UART,TX UART,TX完成13$00C ANA_COMP ANA_COMP模拟比较器OK-AVR万用串行下载开发实验板OK-AVR万用串行下载开发实验板,采用双龙电子公司的专利技术(专利号:98226094.6),是为ATMEL公司的AVR单片机特别研制的廉价的万用串行下载开发实验工具该板适用于ATMEL公司所有具有串行下载功能的AVR单片机,同时还可做AVR单片机的I/O口A/D D/A音频输出等实验本公司随机提供了ATMEL的集成模拟仿真调试软件,对初学AVR 单片机的设计者,可暂时节省购买较昂贵的实时仿真器及万用编程器的费用; OK-AVR万用串行下载开发实验板有CZ1电源及通讯下载用插座,LED电源指示,下载通讯工作指示;附AVR单片机8根下载信号线; AVR单片机四种DIP封装器件下载锁紧插座;WR划线电位器可作为模拟信号输入用,有音响器,另有用户器件扩展区,焊接你实验需要的器件;AVR集成软件包包括: AVR Assembler 1.30编译器; AVR Studio 3.00; AVR Prog;送一片AT90S1200单片机及集成软件AVR单片机数据资料OK-AVR下载开发实验板使用说明等光盘AVR单片机可下载器件:90S120090S231390S2323/90LS232390S2343/90LS234390S2333/90LS233390S4433/90LS443390S441490LS851590S4434/90LS443490S8535/90LS853590S8555ATtiny10/11/12/15MEGA103/603/161/163(适用所有串行下载信号线的AVR单片机)。

嵌入式系统入门—03—AVR的指令与汇编系统

数据优化

合理使用寄存器和内存,减少数据传输开销。

并行处理

利用AVR的并行处理能力,实现多任务并发 执行。

性能评估与优化建议

性能评估

通过性能测试和基准测试,评估程序的执行效率和性能。

优化建议

根据性能评估结果,提出针对性的优化建议,如采用更高效的算法、优化数据结构等。

THANKS FOR WATCHING

来执行这组指令。

宏展开

02

在宏定义后,可以使用宏展开将宏符号替换为相应的指令序列。

宏参数

03

在宏定义中可以定义参数,并在宏展开时将参数替换为相应的

值。

汇编语言程序结构

程序入口

程序从入口点开始执行,通常在程序的开头定义入口点。

程序主体

程序主体包含程序的逻辑和算法,由一系列指令和数据组成。

程序结束

程序结束时需要返回操作系统或返回到调用程序中。

控制流类指令

用于控制程序的流程,如JMP、CALL、RET等。

02 AVR指令详解

数据传输指令

数据传输指令用于在寄存器和内存之 间、寄存器和寄存器之间传输数据。

例如:MOV, LDS, STS等指令可以实 现数据的传输。

算术指令

算术指令用于执行加、减、乘、除等 算术运算。

例如:ADD, SUB, MUL, 语言的基础,汇编语言是使用助记 符表示机器指令的符号化语言。

指令集与机器码

指令集最终被转换为机器码,由计算机硬件执行。

AVR指令集的特点

精简高效

AVR指令集设计简洁,功能强大,适用于嵌入式系统。

丰富的寻址模式

AVR指令集支持多种寻址模式,如直接寻址、间接寻 址、相对寻址等,方便编程。

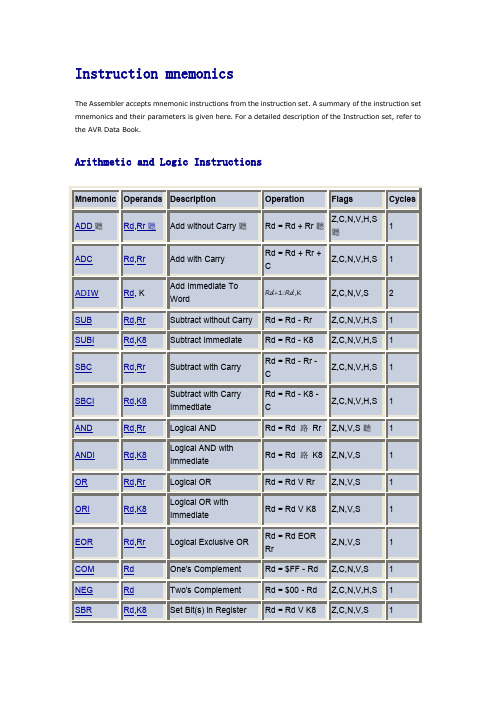

AVR单片机汇编指令合集-

Instruction mnemonicsThe Assembler accepts mnemonic instructions from the instruction set.A summary of the instruction set mnemonics and their parameters is given here.For a detailed description of the Instruction set,refer to the AVR Data Book.Arithmetic and Logic InstructionsMnemonic Operands Description Operation Flags CyclesADD聽Rd,Rr聽Add without Carry聽Rd=Rd+Rr聽Z,C,N,V,H,S聽1ADC Rd,Rr Add with Carry Rd=Rd+Rr+CZ,C,N,V,H,S1ADIW Rd,K Add Immediate ToWordRd+1:Rd,K Z,C,N,V,S2SUB Rd,Rr Subtract without Carry Rd=Rd-Rr Z,C,N,V,H,S1 SUBI Rd,K8Subtract Immediate Rd=Rd-K8Z,C,N,V,H,S1SBC Rd,Rr Subtract with Carry Rd=Rd-Rr-CZ,C,N,V,H,S1SBCI Rd,K8Subtract with CarryImmedtiateRd=Rd-K8-CZ,C,N,V,H,S1AND Rd,Rr Logical AND Rd=Rd路Rr Z,N,V,S聽1ANDI Rd,K8Logical AND withImmediateRd=Rd路K8Z,N,V,S1OR Rd,Rr Logical OR Rd=Rd V Rr Z,N,V,S1ORI Rd,K8Logical OR withImmediateRd=Rd V K8Z,N,V,S1EOR Rd,Rr Logical Exclusive OR Rd=Rd EORRrZ,N,V,S1COM Rd One's Complement Rd=$FF-Rd Z,C,N,V,S1 NEG Rd Two's Complement Rd=$00-Rd Z,C,N,V,H,S1 SBR Rd,K8Set Bit(s)in Register Rd=Rd V K8Z,C,N,V,S1CBR Rd,K8Clear Bit(s)in Register Rd=Rd路($FF-K8)Z,C,N,V,S1INC Rd Increment Register Rd=Rd+1Z,N,V,S1 DEC Rd Decrement Register Rd=Rd-1Z,N,V,S1TST Rd Test for Zero orNegativeRd=Rd路Rd Z,C,N,V,S1CLR Rd Clear Register Rd=0Z,N,V,S1 SER Rd Set Register Rd=$FF None1SBIW Rdl,K6Subtract Immediatefrom WordRdh:Rdl=Rdh:Rdl-K6Z,C,N,V,S2MUL Rd,Rr Multiply Unsigned R1:R0=Rd*RrZ,C2MULS Rd,Rr Multiply Signed R1:R0=Rd*RrZ,C2MULSU Rd,Rr Multiply Signed withUnsignedR1:R0=Rd*RrZ,C2FMUL Rd,Rr Fractional MultiplyUnsignedR1:R0=(Rd*Rr)<<1Z,C2FMULS Rd,Rr Fractional MultiplySignedR1:R0=(Rd*Rr)<<1Z,C2FMULSU Rd,Rr Fractional MultiplySigned with UnsignedR1:R0=(Rd*Rr)<<1Z,C2聽Branch InstructionsMnemonic Operands Description Operation Flags Cycles RJMP k Relative Jump PC=PC+k+1None2IJMP None Indirect Jump to(Z)PC=Z None2EIJMP None Extended IndirectJump(Z)STACK=PC+1,PC(15:0)=Z,PC(21:16)=EINDNone2JMP k Jump聽PC=k None3RCALL k Relative CallSubroutineSTACK=PC+1,PC=PC+k+1None3/4*ICALL None Indirect Call to(Z)STACK=PC+1,PC=Z聽None3/4*EICALL None Extended IndirectCall to(Z)STACK=PC+1,PC(15:0)=Z,PC(21:16)=EINDNone4*CALL k Call Subroutine STACK=PC+2,PC=kNone4/5*RET None SubroutineReturnPC=STACK None4/5*RETI None Interrupt Return PC=STACK I4/5*CPSE Rd,Rr Compare,Skip ifequal聽if(Rd==Rr)PC=PC2or3None1/2/3CP Rd,Rr Compare Rd-Rr Z,C,N,V,H,S1CPC Rd,Rr Compare withCarryRd-Rr-C Z,C,N,V,H,S1CPI Rd,K8Compare withImmediateRd-K Z,C,N,V,H,S1SBRC Rr,b Skip if bit inregister clearedif(Rr(b)==0)PC=PC+2or3None1/2/3SBRS Rr,b Skip if bit inregister setif(Rr(b)==1)PC=PC+2or3None1/2/3SBIC P,b Skip if bit in I/Oregister clearedif(I/O(P,b)==0)PC=PC+2or3None1/2/3SBIS P,b Skip if bit in I/Oregister setif(I/O(P,b)==1)PC=PC+2or3None1/2/3BRBC s,k Branch if Statusflag clearedif(SREG(s)==0)PC=PC+k+1None1/2BRBS s,k Branch if Statusflag setif(SREG(s)==1)PC=PC+k+1None1/2BREQ k Branch if equal if(Z==1)PC=PC+k+1None1/2BRNE k Branch if notequalif(Z==0)PC=PC+k+1None1/2BRCS k Branch if carry set if(C==1)PC=PC+k+1None1/2BRCC k Branch if carryclearedif(C==0)PC=PC+k+1None1/2BRSH k Branch if same orhigherif(C==0)PC=PC+k+1None1/2BRLO k Branch if lower if(C==1)PC=PC+k+1None1/2BRMI k Branch if minus if(N==1)PC=PC+k+1None1/2BRPL k Branch if plus if(N==0)PC=PC+k+1None1/2BRGE k Branch if greaterthan or equal(signed)if(S==0)PC=PC+k+1None1/2BRLT k Branch if lessthan(signed)if(S==1)PC=PC+k+1None1/2BRHS k Branch if halfcarry flag setif(H==1)PC=PC+k+1None1/2BRHC k Branch if halfcarry flag clearedif(H==0)PC=PC+k+1None1/2BRTS k Branch if T flagsetif(T==1)PC=PC+k+1None1/2BRTC k Branch if T flagclearedif(T==0)PC=PC+k+1None1/2BRVS k Branch if overflowflag setif(V==1)PC=PC+k+1None1/2BRVC k Branch if overflowflag clearedif(V==0)PC=PC+k+1None1/2BRIE k Branch if interrupt if(I==1)PC=PC+k+None1/2enabled1BRID k Branch if interruptdisabledif(I==0)PC=PC+k+1None1/2*Cycle times for data memory accesses assume internal memory accesses,and are not valid for accesses through the external RAM interface.For the instructions CALL,ICALL,EICALL,RCALL,RET and RETI,add three cycles plus two cycles for each wait state in devices with up to16bit PC(128KB program memory).For devices with more than128KB program memory,add five cycles plus three cycles for each wait state.Data Transfer InstructionsMnemonic Operands Description Operation Flags Cycles MOV Rd,Rr Copy register Rd=Rr None1MOVW Rd,Rr Copy register pair Rd+1:Rd=Rr+1:Rr,r,d evenNone1LDI Rd,K8Load Immediate Rd=K None1 LDS Rd,k Load Direct Rd=(k)None2* LD Rd,X Load Indirect Rd=(X)None2*LD Rd,X+Load Indirect andPost-IncrementRd=(X),X=X+1None2*LD Rd,-X Load Indirect andPre-DecrementX=X-1,Rd=(X)None2*LD Rd,Y Load Indirect Rd=(Y)None2*LD Rd,Y+Load Indirect andPost-IncrementRd=(Y),Y=Y+1None2*LD Rd,-Y Load Indirect andPre-DecrementY=Y-1,Rd=(Y)None2*LDD Rd,Y+q Load Indirect withdisplacementRd=(Y+q)None2*LD Rd,Z Load Indirect聽Rd=(Z)None2*LD Rd,Z+Load Indirect andPost-IncrementRd=(Z),Z=Z+1None2*LD Rd,-Z Load Indirect and Z=Z-1,Rd=(Z)None2*Pre-DecrementLDD Rd,Z+q Load Indirect withdisplacementRd=(Z+q)None2*STS k,Rr Store Direct(k)=Rr None2* ST X,Rr Store Indirect(X)=Rr None2*ST X+,Rr Store Indirect andPost-Increment(X)=Rr,X=X+1None2*ST-X,Rr Store Indirect andPre-DecrementX=X-1,(X)=Rr None2*ST Y,Rr Store Indirect(Y)=Rr None2*ST Y+,Rr Store Indirect andPost-Increment(Y)=Rr,Y=Y+1None2ST-Y,Rr Store Indirect andPre-DecrementY=Y-1,(Y)=Rr None2ST Y+q,Rr Store Indirect withdisplacement(Y+q)=Rr None2ST Z,Rr Store Indirect(Z)=Rr None2ST Z+,Rr Store Indirect andPost-Increment(Z)=Rr,Z=Z+1None2ST-Z,Rr Store Indirect andPre-DecrementZ=Z-1,(Z)=Rr None2ST Z+q,Rr Store Indirect withdisplacement(Z+q)=Rr None2LPM None Load Program Memory R0=(Z)None3 LPM Rd,Z Load Program Memory Rd=(Z)None3LPM Rd,Z+Load Program Memory andPost-IncrementRd=(Z),Z=Z+1None3ELPM None Extended Load ProgramMemoryR0=(RAMPZ:Z)None3ELPM Rd,Z Extended Load ProgramMemoryRd=(RAMPZ:Z)None3ELPM Rd,Z+Extended Load ProgramMemory and Post IncrementRd=(RAMPZ:Z),Z=Z+1None3SPM None Store Program Memory(Z)=R1:R0None-ESPM None Extended Store ProgramMemory(RAMPZ:Z)=R1:R0None-IN Rd,P In Port Rd=P None1OUT P,Rr Out Port P=Rr None1 PUSH Rr Push register on Stack STACK=Rr None2POP Rd Pop register from Stack Rd=STACK None2*Cycle times for data memory accesses assume internal memory accesses and are not valid for accesses through the external RAM interface.For the LD,ST,LDD,STD,LDS,STS,PUSH and聽POP instructions, add one cycle plus one cycle for each wait state.Bit and Bit-test InstructionsMnemonic Operands Description Operation Flags CyclesLSL Rd Logical shift left Rd(n+1)=Rd(n),Rd(0)=0,C=Rd(7)Z,C,N,V,H,S1LSR Rd Logical shift right Rd(n)=Rd(n+1),Rd(7)=0,C=Rd(0)Z,C,N,V,S1ROL Rd Rotate leftthrough carryRd(0)=C,Rd(n+1)=Rd(n),C=Rd(7)Z,C,N,V,H,S1ROR Rd Rotate rightthrough carryRd(7)=C,Rd(n)=Rd(n+1),C=Rd(0)Z,C,N,V,S1ASR Rd Arithmetic shiftrightRd(n)=Rd(n+1),n=0,...,6Z,C,N,V,S1SWAP Rd Swap nibbles Rd(3..0)=Rd(7..4),Rd(7..4)=Rd(3..0)None1BSET聽s Set flag SREG(s)=1SREG(s)1 BCLR s Clear flag SREG(s)=0SREG(s)1SBI P,b Set bit in I/OregisterI/O(P,b)=1None2CBI P,b Clear bit in I/O I/O(P,b)=0None2registerBST Rr,b Bit store fromregister to TT=Rr(b)T1BLD Rd,b Bit load fromregister to TRd(b)=T None1SEC None Set carry flag C=1C1 CLC None Clear carry flag C=0C1 SEN None Set negative flag N=1N1CLN None Clear negativeflagN=0N1SEZ None Set zero flag Z=1Z1 CLZ None Clear zero flag Z=0Z1 SEI None Set interrupt flag I=1I1CLI None Clear interruptflagI=0I1SES None Set signed flag S=1S1 CLN None Clear signed flag S=0S1 SEV None Set overflow flag V=1V1CLV None Clear overflowflagV=0V1SET None Set T-flag T=1T1 CLT None Clear T-flag T=0T1SEH None Set half carryflagH=1H1CLH None Clear half carryflagH=0H1NOP None No operation None None1 SLEEP None Sleep See instruction manual None1 WDR None Watchdog Reset See instruction manual None1 BREAK None Execution Break See instruction manual None1The Assembler is not case sensitive.The operands have the following forms:Rd:Destination(and source)register in the register fileRr:Source register in the register fileb:Constant(0-7),can be a constant expressions:Constant(0-7),can be a constant expressionP:Constant(0-31/63),can be a constant expressionK6;Constant(0-63),can be a constant expressionK8:Constant(0-255),can be a constant expressionk:Constant,value range depending on instruction.Can be a constant expression q:Constant(0-63),can be a constant expressionRdl:聽R24,R26,R28,R30.For ADIW and SBIW instructions。

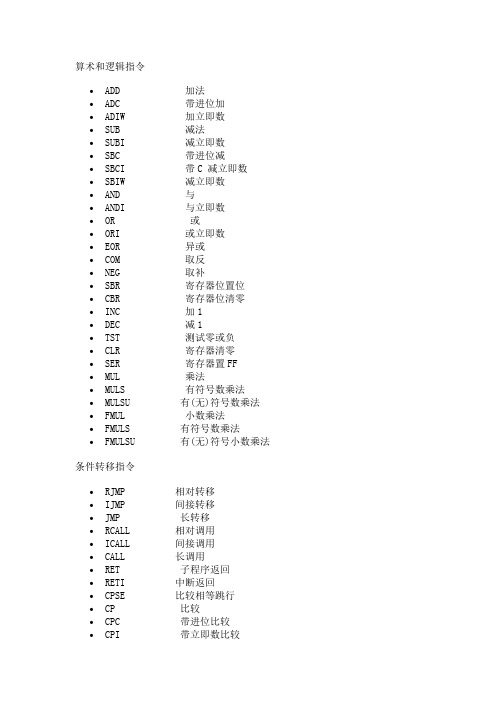

AVR汇编指令集

算术和逻辑指令•ADD 加法•ADC 带进位加•ADIW 加立即数•SUB 减法•SUBI 减立即数•SBC 带进位减•SBCI 带C 减立即数•SBIW 减立即数•AND 与•ANDI 与立即数•OR 或•ORI 或立即数•EOR 异或•COM 取反•NEG 取补•SBR 寄存器位置位•CBR 寄存器位清零•INC 加1•DEC 减1•TST 测试零或负•CLR 寄存器清零•SER 寄存器置FF•MUL 乘法•MULS 有符号数乘法•MULSU 有(无)符号数乘法•FMUL 小数乘法•FMULS 有符号数乘法•FMULSU 有(无)符号小数乘法条件转移指令•RJMP 相对转移•IJMP 间接转移•JMP 长转移•RCALL 相对调用•ICALL 间接调用•CALL 长调用•RET 子程序返回•RETI 中断返回•CPSE 比较相等跳行•CP 比较•CPC 带进位比较•CPI 带立即数比较•SBRC 位清零跳行•SBRS 位置位跳行•SBIC I/O 位清零跳行•SBIS I/O 位置位跳行•BRBS SREG 位置位转•BRBC SREG 位清零转•BREQ 相等转移•BRNE 不相等转移•BRCS C 置位转•ELPM 扩展装载程序存储器•EIJMP 扩展间接跳转•ESPM 扩展存储程序存储器•EICALL延长间接调用子程序•BRCC C 清零转•BRSH 转•BRLO 小于转(无符号)•BRMI 负数转移•BRPL 正数转移•BRGE 转(带符号)•BRLT 小于转(带符号)•BRHS H 置位转移•BRHC H 清零转移•BRTS T 置位转移•BRTC T 清零转移•BRVS V 置位转移•BRVC V 清零转移•BRIE 中断位置位转移•BRID 中断位清零转移数据传送指令•MOV 寄存器传送•MOVW 拷贝寄存器字•LDI 装入立即数•LD X X 间接取数•LD X+ X 间接取数后•LD -X X 间接取数先•LD Y Y 间接取数•LD Y+ Y 间接取数后+•LD –Y Y 间接取数先•LDD Yq Y 间接取数 q•LD Z Z 间接取数•LD Z+ Z 间接取数后•LD –Z Z 间接取数先•LDD Zq Z 间接取数 q•LDS 从SRAM 装入•ST X X 间接存数•ST X+ X 间接存数后•ST –X X 间接存数先•ST Y Y 间接存数•ST Y+ Y 间接存数后•ST –Y Y 间接存数先•STD Yq Y 间接存数 q•ST Z Z 间接存数•ST Z+ Z 间接存数后•ST –Z Z 间接存数先•STD Zq Z 间接存数 q•STS 数据送SRAM•LPM 装程序存储器•LPM Z Z•LPM Z+ Z+•SPM 存储程序存储器•IN I/O 口输入•OUT 送I/O 口•PUSH 压栈•POP 出栈位指令和位测试指令•SBI 置位I/O 位•CBI 清零I/O 位•LSL 左移•LSR 右移•ROL 带进位左循环•ROR 带进位右循环•ASR 算术右移•SWAP 半字节交换•BSET 置位SREG•BCLR 清零SREG•BST Rr 的b 位送T•BLD T 送Rr 的b 位•SEC 置位C•CLC 清零C•SEN 置位N•CLN 清零N•SEZ 置位Z•CLZ 清零Z•SEI 置位I•CLI 清零I•SES 置位S•CLS 清零S•SEV 置位V•CLV 清零V•SET 置位T•CLT 清零T•SEH 置位H•CLH 清零H•NOP 空操作•SLEEP 休眠•WDR 看门狗复位90 条指令器件:Attiny11/12/15/2289 条指令器件:AT90S1200118 条指令器件:AT90S2313/2323/2343/2333 AT90S4414/4433/4434/8515 AT90S8534/8535 121 条指令器件:ATmega603/103130 条指令器件:ATmega161。

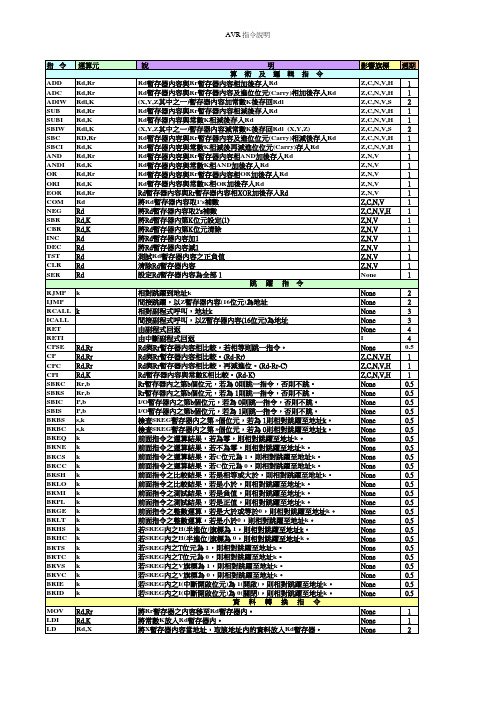

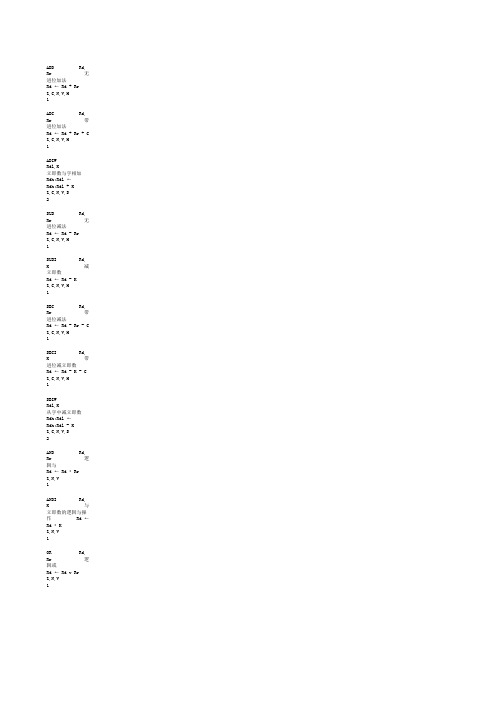

AVR 指令说明

說

影響旗標 Z,C,N,V,H Z,C,N,V,H Z,C,N,V,S Z,C,N,V,H Z,C,N,V,H Z,C,N,V,S Z,C,N,V,H Z,C,N,V,H Z,N,V Z,N,V Z,N,V Z,N,V Z,N,V Z,C,N,V Z,C,N,V,H Z,N,V Z,N,V Z,N,V Z,N,V Z,N,V Z,N,V None None None None None None I None Z,C,N,V,H Z,C,N,V,H Z,C,N,V,H None None None None None None None None None None None None None None None None None None None None None None None None None None None

X暫存器內容當地址,取該地址內的資料放入Rd暫存器後X加1。 X暫存器內容先減1當地址,取該地址內的資料放入Rd暫存器。 將Y暫存器內容當地址,取該地址內的資料放入Rd暫存器。 Y暫存器內容當地址,取該地址內的資料放入Rd暫存器後Y加1。 Y暫存器內容先減1當地址,取該地址內的資料放入Rd暫存器。 將Y暫存器內容加 q當地址,取該地址內的資料放入Rd暫存器。 將Z暫存器內容當地址,取該地址內的資料放入Rd暫存器。 Z暫存器內容當地址,取該地址內的資料放入Rd暫存器後Z加1。 Z暫存器內容先減1當地址,取該地址內的資料放入Rd暫存器。 將Z暫存器內容加 q當地址,取該地址內的資料放入Rd暫存器。 直接讀進地址為K的SRAM內容,放入Rd暫存器。 儲存Rr暫存器內容到X所指的RAM地址內。 儲存Rr暫存器內容到X所指的RAM地址內,後X加1。。 X先減1後,儲存Rr暫存器內容到X所指的RAM地址。。 儲存Rr暫存器內容到Y所指的RAM地址內。 儲存Rr暫存器內容到Y所指的RAM地址內,後Y加1。。 Y先減1後,儲存Rr暫存器內容到Y所指的RAM地址。。 儲存Rr暫存器內容到Y+q所指的RAM地址內。 儲存Rr暫存器內容到Z所指的RAM地址內。 儲存Rr暫存器內容到Z所指的RAM地址內,後Z加1。。 Z先減1後,儲存Rr暫存器內容到Z所指的RAM地址。。 儲存Rr暫存器內容到Z+q所指的RAM地址內。 將Rr內容存入地址為K的SRAM內。 由程式記憶體載入資料到R0,地址在Z暫存器內。 由I/O記憶體地址P載入資料到Rd暫存器。 將Rd暫存器內容送出到I/O記憶體地址P上。 將Rr暫存器內容壓到堆疊內,堆疊地址在SPL暫存器。 由堆疊中取出資料到Rr暫存器內,堆疊地址在SPL暫存器。 位 元 及 位 元 測 試 指 令 將I/O記憶體地址中的b位元設定1。 將I/O記憶體地址中的b位元清除。 將Rd暫存器內容左移一位元,並在右端輸入補 0。 將Rd暫存器內容右移一位元,並在左端輸入補 0。 將Rd暫存器內容與C旗標一起左旋一位元,C旗標由右端送入。 將Rd暫存器內容與C旗標一起右旋一位元,C旗標由左端送入。 將Rd暫存器內容作算術右移,MSB不動,其餘右移一位並補0。 將Rd暫存器內容之高4位元(4~7)與低4位元(0~3)互換。 將SREG暫存器內第s位元設定(1)。 將SREG暫存器內器第s位元清除。 將Rr暫存器內第b個位元存入SREG暫存器內之T位元內。 將SREG暫存器內之T位元放入Rr暫存器內第b個位元內。 設定進位位元C。 清除進位位元C。 設定負值位元N。 清除負值位元N。 設定零旗標Z。 清除零旗標Z。 設定總中斷旗標I。 清除總中斷旗標I。 設定正負值旗標S。 清除正負值旗標S。 設定溢位旗標V。 清除溢位旗標V。 設定SREG暫存器內之T位元。 清除SREG暫存器內之T位元。 設定半進位旗標H。 清除半進位旗標H。 無動作指令。 睡覺指令 重設看門狗指令。

汇编语言的类型

汇编语言的类型汇编语言是一种低级语言,它是由机器指令和汇编指令组成的。

汇编语言是一种直接操作计算机硬件的语言,它可以直接控制计算机的各种硬件资源,如CPU、内存、I/O等。

汇编语言的类型主要有以下几种:1. x86汇编语言x86汇编语言是一种基于Intel x86架构的汇编语言,它是目前最为流行的汇编语言之一。

x86汇编语言可以直接操作CPU的寄存器、内存和I/O端口等硬件资源,它可以实现高效的程序设计和优化。

x86汇编语言的语法比较复杂,需要掌握大量的指令和寄存器,但是它可以实现非常高效的程序设计和优化。

2. ARM汇编语言ARM汇编语言是一种基于ARM架构的汇编语言,它是嵌入式系统和移动设备上最为流行的汇编语言之一。

ARM汇编语言可以直接操作CPU的寄存器、内存和I/O端口等硬件资源,它可以实现高效的程序设计和优化。

ARM汇编语言的语法比较简单,但是需要掌握大量的指令和寄存器。

3. MIPS汇编语言MIPS汇编语言是一种基于MIPS架构的汇编语言,它是嵌入式系统和网络设备上常用的汇编语言之一。

MIPS汇编语言可以直接操作CPU的寄存器、内存和I/O端口等硬件资源,它可以实现高效的程序设计和优化。

MIPS汇编语言的语法比较简单,但是需要掌握大量的指令和寄存器。

4. AVR汇编语言AVR汇编语言是一种基于AVR架构的汇编语言,它是嵌入式系统和单片机上常用的汇编语言之一。

AVR汇编语言可以直接操作CPU 的寄存器、内存和I/O端口等硬件资源,它可以实现高效的程序设计和优化。

AVR汇编语言的语法比较简单,但是需要掌握大量的指令和寄存器。

5. PowerPC汇编语言PowerPC汇编语言是一种基于PowerPC架构的汇编语言,它是IBM和苹果电脑上常用的汇编语言之一。

PowerPC汇编语言可以直接操作CPU的寄存器、内存和I/O端口等硬件资源,它可以实现高效的程序设计和优化。

PowerPC汇编语言的语法比较复杂,需要掌握大量的指令和寄存器,但是它可以实现非常高效的程序设计和优化。

AVR ATmega16指令大全

状态寄存器与标志位SREG:8 位状态寄存器,其中每一位的定义为:C:进位标志位Z:结果为零标志位N:结果为负数标志位V: 2 的补码溢出标志位S:N⊕V,用于符号测试的标志位H:操作中产生半进位的标志位T:用于和BLD、BST 指令进行位数据交换的位I:全局中断触发/禁止标志位算术和逻辑指令加法指令1.不带进位位加法ADD Rd,Rr 0≤d≤31,0≤r≤31说明:两个寄存器不带进位 C 标志相加,结果送目的寄存器Rd。

2.带进位位加法ADC Rd,Rr 0≤d≤31,0≤r≤31说明:两个寄存器和C标志的内容相加,结果送目的寄存器Rd。

3.字加立即数ADIW Rdl,K dl 为:24、26、28、30,0≤K≤63说明:寄存器对(一个字)同立即数(0~63)相加,结果放到寄存器对。

4.增1 指令INC Rd 0≤d≤31说明:寄存器Rd 的内容加1,结果送目的寄存器Rd 中。

减法指令1.不带进位位减法SUB Rd,Rr 0≤d≤31,0≤r≤31说明:两个寄存器相减结果送目的寄存器Rd 中。

2.减立即数(字节)SUBI Rd,K 16≤d≤31,0≤K≤255说明:一个寄存器和常数相减,结果送目的寄存器Rd。

3.带进位位减法SBC Rd,Rr 0≤d≤31,0≤r≤31说明:两个寄存器带着C 标志相减,结果放到目的寄存器Rd 中。

4.带进位位减立即数(字节)SBCI Rd,K 16≤d≤31,0≤K≤255说明:寄存器和立即数带着 C 标志相减,结果放到目的寄存器Rd 中。

5.减立即数(字)SBIW Rdl,K dl为24、26、28、30,0≤K≤63说明:寄存器对(字)与立即数0~63 相减,结果放入寄存器对。

6.减1 指令DEC Rd 0≤d≤31说明:寄存器Rd 的内容减1,结果送目的寄存器Rd 中。

取反码指令COM Rd 0≤d≤31说明:该指令完成对寄存器Rd 的二进制反码操作。

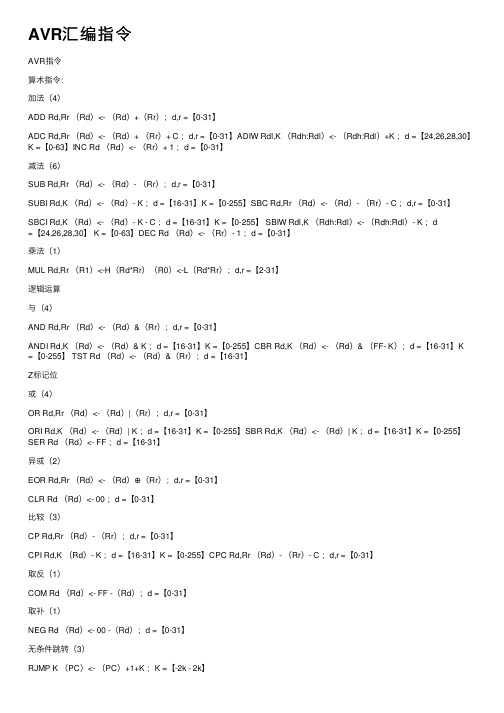

AVR汇编指令

AVR汇编指令AVR指令算术指令:加法(4)ADD Rd,Rr (Rd)<- (Rd)+(Rr);d,r =【0-31】ADC Rd,Rr (Rd)<- (Rd)+ (Rr)+ C ;d,r =【0-31】ADIW Rdl,K (Rdh:Rdl)<- (Rdh:Rdl)+K ;d =【24,26,28,30】K =【0-63】INC Rd (Rd)<- (Rr)+ 1 ;d =【0-31】减法(6)SUB Rd,Rr (Rd)<- (Rd)- (Rr);d,r =【0-31】SUBI Rd,K (Rd)<- (Rd)- K ;d =【16-31】K =【0-255】SBC Rd,Rr (Rd)<- (Rd)- (Rr)- C ;d,r =【0-31】SBCI Rd,K (Rd)<- (Rd)- K - C ;d =【16-31】K =【0-255】 SBIW Rdl,K (Rdh:Rdl)<- (Rdh:Rdl)- K ;d=【24,26,28,30】 K =【0-63】DEC Rd (Rd)<- (Rr)- 1 ;d =【0-31】乘法(1)MUL Rd,Rr (R1)<-H(Rd*Rr)(R0)<-L(Rd*Rr);d,r =【2-31】逻辑运算与(4)AND Rd,Rr (Rd)<- (Rd)&(Rr);d,r =【0-31】ANDI Rd,K (Rd)<- (Rd)& K ;d =【16-31】K =【0-255】CBR Rd,K (Rd)<- (Rd)& (FF- K);d =【16-31】K=【0-255】 TST Rd (Rd)<- (Rd)&(Rr);d =【16-31】Z标记位或(4)OR Rd,Rr (Rd)<- (Rd)|(Rr);d,r =【0-31】ORI Rd,K (Rd)<- (Rd)| K ;d =【16-31】K =【0-255】SBR Rd,K (Rd)<- (Rd)| K ;d =【16-31】K =【0-255】SER Rd (Rd)<- FF ;d =【16-31】异或(2)EOR Rd,Rr (Rd)<- (Rd)⊕(Rr);d,r =【0-31】CLR Rd (Rd)<- 00 ;d =【0-31】⽐较(3)CP Rd,Rr (Rd)- (Rr);d,r =【0-31】CPI Rd,K (Rd)- K ;d =【16-31】K =【0-255】CPC Rd,Rr (Rd)- (Rr)- C ;d,r =【0-31】取反(1)COM Rd (Rd)<- FF -(Rd);d =【0-31】取补(1)NEG Rd (Rd)<- 00 -(Rd);d =【0-31】⽆条件跳转(3)RJMP K (PC)<- (PC)+1+K ;K =【-2k - 2k】IJMP (PC)<- (Z);Z : 16BITJMP K (PC)<- K ;K =【0-4M】条件跳转(20)BRBS S , K BRBC S , K 状态寄存器判断位;S =【0-7】K =【-64,63】BREQ K BRNE K 为零标记不为零BRIE K BRID K 全局中断开关BRTS K BRTC K 标记位为零BRHS K BRHC K 半进位置位为零BRGM K BRLT K 带符号⼤于等于⼩于BRSH K BRLO K ⽆符号⼤于等于⼩于BRCS K BRCC K 进位置位为零BRVS K BRVC K 补码溢出置位为零BRMI K BRPL K 负数正数条件跳⾏(5)CPSE Rd,Rr 相等时跳⾏;d,r =【0-31】SBRS Rd,b 该为置位时跳⾏;d =【0-31】S =【0-7】 SBRC Rd,b 该为零时跳⾏;d =【0-31】S =【0-7】SBIC P,b 该为零时跳⾏;P =【0-31】S =【0-7】 SBIS P,b 该为置位时跳⾏;P =【0-31】 S =【0-7】调⽤(5)RCALL K (PC)<- (PC)+1+K ;K =【-2k - 2k】ICALL 跳转到Z指向地址;16 bitCALL K 0-4MRET ⼦程序返回RETI 中断返回栈(2)PUSH Rd 进⼊堆栈;d =【0-31】POP Rd 出栈;d =【0-31】直接数据传送(4)MOV Rd,Rr (Rd)<-(Rr);d,r =【0-31】LDS Rd,K (Rd)<-(K);d =【0-31】STS K,Rd (K)<-(Rd);d =【0-31】LDI Rd,K (Rd)<- K ;d =【16-31】K =【0-255】间接数据传送(22)X寄存器:LD Rd,X (Rd)<-((X));d =【0-31】LD Rd,X+ (Rd)<-((X)),(X)+=1 ;d =【0-31】LD Rd,-X (X)- =1,(Rd)<-((X));d =【0-31】ST X,Rd ((X))<-(Rd);d =【0-31】ST X+,Rd ((X))<-(Rd),(X)+=1 ;d =【0-31】ST -X,Rd (X)- =1,((X))<-(Rd);d =【0-31】Y寄存器:LD Rd,YLD Rd,Y+LD Rd,-YLDD Rd,Y+Q (Rd)<-((Y+Q));d =【0-31】Q =【0-63】 ST Y,RdST Y+,RdST -Y,RdSTD Y+Q,RdZ寄存器:LD Rd,ZLD Rd,Z+LD Rd,-ZLDD Rd,Z+QST Z,RdST Z+,RdST -Z,RdSTD Z+Q,Rd寻址(1)LMP 利⽤Z寄存的地址寻址(注意lsb位要为0读低8位数1读⾼8位数)I/O⼝(2)IN Rd,P (Rd)<- (P);d =【0-31】 P =【0-63】 OUT P,Rd (P)<- (Rd);d =【0-31】 P =【0-63】移位(6)LSL Rd (Rd)<<1, C<-MSB ,LSB<-0 ;d =【0-31】LSR Rd (Rd)>>1, C<-LSB ,MSB<-0 ;d =【0-31】ROL Rd (Rd)<<1 ,LSB<-C , C<-MSB ;d =【0-31】ROR Rd (Rd)>>1 ,MSB<-C , C<-LSB ;d =【0-31】SWAP Rd 半字节交换;d =【0-31】ASR Rd 7位不变,其余右移 , C<-LSB ;d =【0-31】T标记位(2)BLD Rd,b 将位读⼊T标记;d =【0-31】 b =【0-7】BST Rd,b 将T标记写⼊位;d =【0-31】 b =【0-7】状态位设置(20)BSET S BCLR S 设置状态寄存器指定位; S =【0-7】SEI CLI 状态标记设置或清除SEH CLHSET CLTSES CLSSEN CLNSEV CLVSEZ CLZSEC CLCSBI P,b CBI P,b 32IO⼝指定位设置清楚;P =【0-31】 b =【0-7】其他WDR 看门狗复位SLEEP 休眠NOP 空指令。

avr指令[详解]

![avr指令[详解]](https://img.taocdn.com/s3/m/93f1b45bf6ec4afe04a1b0717fd5360cba1a8d1d.png)

AVR指令算术和逻辑指令 ESPM 扩展存储程序存储器位指令和位测试指令ADD 加法 EICALL延长间接调用子程序 SBI 置位I/O 位ADC 带进位加 BRCC C 清零转CBI 清零I/O 位ADIW 加立即数 BRSH 转LSL 左移SUB 减法 BRLO 小于转(无符号) LSR 右移SUBI 减立即数 BRMI 负数转移ROL 带进位左循环SBC 带进位减 BRPL 正数转移ROR 带进位右循环SBCI 带C 减立即数 BRGE 转(带符号) ASR 算术右移SBIW 减立即数 BRLT 小于转(带符号) SWAP 半字节交换AND 与 BRHS H 置位转移BSET 置位SREGANDI 与立即数 BRHC H 清零转移BCLR 清零SREGOR 或 BRTS T 置位转移BST Rr 的b 位送TORI 或立即数 BRTC T 清零转移BLD T 送Rr 的b 位EOR 异或 BRVS V 置位转移SEC 置位CCOM 取反 BRVC V 清零转移CLC 清零CNEG 取补 BRIE 中断位置位转移 SEN 置位NSBR 寄存器位置位 BRID 中断位清零转移 CLN 清零NCBR 寄存器位清零数据传送指令SEZ 置位ZINC 加1 MOV 寄存器传送 CLZ 清零ZDEC 减1 MOVW 拷贝寄存器字 SEI 置位ITST 测试零或负 LDI 装入立即数 CLI 清零ICLR 寄存器清零 LD X X 间接取数 SES 置位SSER 寄存器置FF LD X+ X 间接取数后 CLS 清零SMUL 乘法 LD -X X 间接取数先 SEV 置位VMULS 有符号数乘法 LD Y Y 间接取数 CLV 清零VMULSU 有(无)符号数乘法 LD Y+ Y 间接取数后+ SET 置位TFMUL 小数乘法 LD –Y Y 间接取数先 CLT 清零TFMULS 有符号数乘法 LDD Yq Y 间接取数 q SEH 置位HFMULSU 有(无)符号小数乘法 LD Z Z 间接取数 CLH 清零H条件转移指令 LD Z+ Z 间接取数后 NOP 空操作RJMP 相对转移 LD –Z Z 间接取数先 SLEEP 休眠IJMP 间接转移 LDD Zq Z 间接取数 q WDR 看门狗复位JMP 长转移 LDS 从SRAM 装入RCALL 相对调用 ST X X 间接存数 90 条指令器件( )ICALL 间接调用 ST X+ X 间接存数后 Attiny11/12/15/22CALL 长调用 ST –X X 间接存数先RET 子程序返回 ST Y Y 间接存数 89 条指令器件RETI 中断返回 ST Y+ Y 间接存数后 AT90S1200CPSE 比较相等跳行 ST –Y Y 间接存数先 118 条指令器件( )CP 比较 STD Yq Y 间接存数 q AT90S2313/2323/2343/2333CPC 带进位比较 ST Z Z 间接存数 AT90S4414/4433/4434/8515CPI 带立即数比较 ST Z+ Z 间接存数后 AT90S8534/8535SBRC 位清零跳行 ST –Z Z 间接存数先 121 条指令器件( )SBRS 位置位跳行 STD Zq Z 间接存数 q ATmega603/103SBIC I/O 位清零跳行 STS 数据送SRAM 130 条指令器件( )SBIS I/O 位置位跳行 LPM 装程序存储器 ATmega161BRBS SREG 位置位转 LPM Z Z 90 条指令= +89 条BRBC SREG 位清零转 LPM Z+ Z+ 118 条指令= + 90 条BREQ 相等转移 SPM 存储程序存储器 121 条指令= + 118 条BRNE 不相等转移 IN I/O 口输入 130 条指令= +121 条BRCS C 置位转 OUT 送I/O 口更详细资料阅ELPM 扩展装载程序存储器 PUSH 压栈英文指令表EIJMP 扩展间接跳转 POP 出栈。

AVR第三章(AVR指令系统)11年上

机器码:10q0 qq0d dddd 1qqq。

13

九、从程序存储器取常数寻址

只有一条指令LPM,也称查表指令。

程序存储器中存放常数字节的地址由寄存器Z的内容确定。 Z寄存器的高15位用于选择字地址,而Z寄存器的最低位D0用 于存放字地址的高低字节。若最低位为0,则选择低字节;若 最低位为1,则选择高字节。

说明:

一个汇编文件包含若干个代码段,若干个数据段 ,若 干个E2PROM 段 ,在汇编时,它们按类型的不同被分别连接 成一个代码段,一个数据段,一个E2PROM段。

18

二、ORG——设置程序、数据在段中的起始位置

语法: .ORG 表达式 ; 表达式的值为定位计数器的值---绝对值(无符号数)。 如果ORG伪指令放在数据段,则设置SRAM定位计数器。 如果该伪指令放在代码段,则设置程序存储器计数器。 如果该伪指令放在E2PROM段,则设置E2PROM定位计数器。 缺省值:代码段:0;数据段:32; E2PROM 段 :0。 注意:程序存储器定位计数器--按字计数; 而E2PROM和SRAM 定位计数器--按字节计数。

19

三、数据定义伪指令

1.BYTE——在SRAM数据区定义字节 语法:LABEL:.BYTE 表达式(表)

2. DB——在程序存储器或E2区中定义字节常数 语法:LABEL: .DB 表达式(表)

tab:.db $3f,$06,$5b,$4f,$66,$6d,$7d,$07,$7f,$6f ;七段码表

例:LPM ; 操作: R0←(Z),既把以Z为指针的程序存储 器的内容送R0。若Z=$0100,即把地址为$0080的程序存储器 的低字节内容送R0,若Z=$0101,即把地址为$0080的程序存 储器的高字节内容送R0。 先了解一下,指令部分详细讲解。

第三章 AVR汇编指令

AVR 汇编语言系统

器件定义文件“m16def.inc” 函数

LOW(表达式) 返回一个表达式值的最低字节。 HIGH(表达式) 返回一个表达式值的第二个字节。 BYTE2(表达式) 与HIGH 函数相同。 BYTE3(表达式) 返回一个表达式值的第三个字节。 BYTE4(表达式) 返回一个表达式值的第四个字节。 LWRD(表达式) 返回一个表达式值的0~15 位。 HWRD(表达式) 返回一个表达式值的16~31 位。 PAGE(表达式) 返回一个表达式值的16~21 位。 EXP2(表达式) 返回(表达式值)2 次幂的值。 LOG2(表达式) 返回Log2(表达式值)的整数部分。

Rd,Rr Rd,Rr Rd,Rr Rd,Rr Rd,Rr

Rd,Rr

AVR指令系统-比较和跳转指令

无条件跳转指令

相对跳转 间接跳转 直接跳转 测试条件符合跳转指令

RJMP IJMP JMP

k k

条件跳转指令

状态寄存器中位为“1”跳转 状态寄存器中位为“0”跳转 相等跳转 不相等跳转 进位标志位C 为“1”跳转 进位标志位C 为“0”跳转

BRBS BRBC BREQ BRNE BRCS BRCC

s, s,

k k

k k

k k

AVR指令系统-比较和跳转指令

大于或等于跳转(对无符号数) 小于跳转(对无符号数) 结果为负跳转 结果为正跳转 大于或等于跳转(带符号数) 小于跳转(带符号数) 半进位标志为“1”跳转 半进位标志为“0”跳转 T 标志为“1”跳转 T 标志为“0”跳转 溢出标志为“1”跳转 溢出标志为“0”跳转 中断标志为“1”跳转 中断标志为“0”跳转

单片机除法指令

单片机是一种微型计算机,它集成了处理器核心、内存和可编程输入输出端口在一个芯片上。

在单片机编程中,除法指令是用于执行两个数相除的算术操作。

不同的单片机架构可能有不同的除法指令集,但大多数都提供了基本的整数除法功能。

以下是一些常见的单片机架构及其对应的除法指令:1.8051单片机: 8051单片机使用8位微控制器,其指令集中包含了除法指令。

例如,DIV AB指令用于将累加器A中的值除以寄存器B中的值,商存放回累加器A,余数存放在累加器B。

2.PIC单片机:在PIC单片机(如PIC16系列)中,除法操作通常通过库函数来实现,而不是直接的硬件指令。

例如,可以使用div函数来执行除法操作。

3.ARM单片机: ARM架构的单片机(如基于Cortex-M系列)提供了更为复杂的除法指令。

例如,SDiv指令用于有符号整数除法,而UDiv 用于无符号整数除法。

这些指令可以处理32位或64位的操作数。

4.AVR单片机: AVR单片机(如Atmega系列)使用ATmega指令集,其中包括DIV指令,用于无符号整数除法。

这个指令将寄存器r0和r1的内容除以r24和r25的内容,结果存放回r0和r1。

5.MSP430单片机: MSP430单片机使用的是MSP430指令集,其中包括16位和32位的除法指令。

例如,div.w #num指令用于将工作寄存器W的内容除以立即数num,结果存放回工作寄存器W。

在使用除法指令时,需要注意以下几点:•数据大小:确保操作数的大小与指令匹配。

例如,如果指令是为8位操作数设计的,那么确保你的数据不会溢出8位的范围。

•除数为零:在执行除法操作前,检查除数是否为零,以避免运行时错误。

•符号:如果你的单片机支持有符号除法,确保正确处理正负号。

•精度:根据需要选择合适的数据类型和精度。

在某些情况下,可能需要使用浮点除法。

单片机的除法指令是编程中的基本操作之一,它们使得单片机能够进行各种数学计算和数据处理任务。

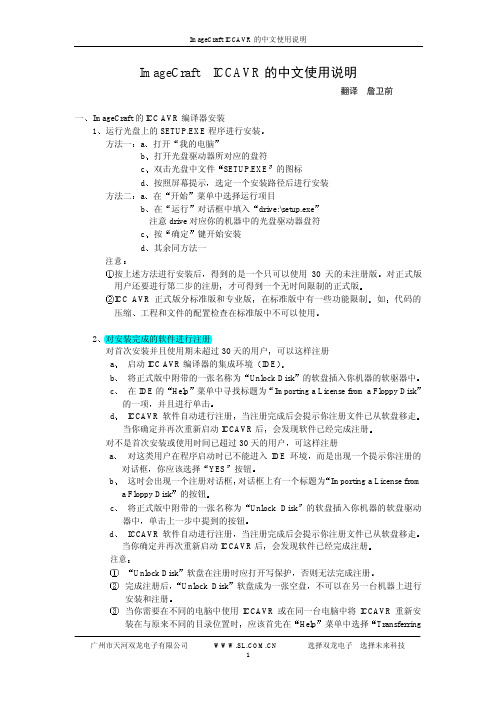

ImageCraft ICCAVR 的中文使用说明

广州市天河双龙电子有限公司

3

选择双龙电子 选择未来科技

ImageCraft ICCAVR 的中文使用说明

三 ICCAVR 向导 1 起步 自你启动 IDE 后 首先从 Project 菜单系统选择 Open 命令 进入\icc\examples.avr 目 录并且选择并打开 led 工程 工程管理器显示在这个工程中只有一个文件 led.c 然 后从 Project 菜单中选择 Options 命令打开工程编译选项 在"Target"标号下选择目标处理 器 然后从 Project 菜单中选择 Make Project 命令 IDE 将调用编译器编译这个工程文件 并且在状态窗口中显示所有的信息

中时必须被使 读者可参考访问 EEPROM 的例子

#pragma abs_address:<address> 函数与全局数据不使用浮动定位 重定位

在访问中断向量和其它硬件项目时特别有用

而是从<address>开始分配绝对地址 这

#pragma end_abs_address 结束绝对定位 使目标程序使用正常浮动定位 C++ 注释

如果你选择了编译扩充(Project->Options->Compiler) 你可以在你的源代码中使用 C ++ 的 // 类型的注释 二进制常数

如果你选择了编译扩充(Project->Options->Compiler) 你可以使用 0b<1|0>* 来指定二 进制常数 例如 0b10101 等于十进制数 21 在线汇编

ICCAVR 是一个 32 位的程序 支持长文件名 出于篇幅考虑 本说明书并不介绍通用的 C 语言语法知识 仅介绍使用 ICC AVR 所 必须具备的知识 因此要求读者在阅读本说明书之前 应对 C 语言有了一定程度的理解 2 ICCAVR 中的文件类型及其扩展名 文件类型是由它们的扩展名决定的 IDE 和编译器可以使用以下几种类型的文件 输入文件 .c 扩展名----表示是 C 语言源文件 .s 扩展名----表示是汇编语言源文件 .h 扩展名----表示是 C 语言的头文件 .prj 扩展名----表示是工程文件 这个文件保存由 IDE 所创建和修改的一个工程的有 关信息 .a 扩展名----库文件 它可以由几个库封装在一起 libcavr.a 是一个包含了标准 C 的 库和 AVR 特殊程序调用的基本库 如果库被引用 链接器会将其链接到您的模块或文件中 您也可以创建或修改一个符合你需要的库 输出文件 .s 对应每个 C 语言源文件 由编译器在编译时产生的汇编输出文件 .o 由汇编文件汇编产生的目标文件 多个目标文件可以链接成一个可执行文件 .hex INTEL HEX 格式文件 其中包含了程序的机器代码 .eep INTEL HEX 格式文件 包含了 EEPROM 的初始化数据 .cof COFF 格式输出文件 用于在 ATMEL 的 AvrStudio 环境下进行程序调试 .lst 列表文件 在这个文件中列举出了目标代码对应的最终地址 .mp 内存映象文件 它包含了您程序中有关符号及其所占内存大小的信息 .cmd NoICE 2.xx 调试命令文件 .noi NoICE 3.xx 调试命令文件 .dbg ImageCraft 调试命令文件 3 附注和扩充 #pragma 编译附注 这个编译器接受以下附注

AVC讲义.

安徽省电力科学研究院

发电侧电压无功自动调控系统

主站下发指令格式

电压遥调量编码规则: 统一下发母线电压优化设定值与量测之间的改变量的一次调节步

长值,,该调节值在遥调量中通过一定的编码方式加以体现。

主站下发的遥调量由三位数组成。 其中百位表示调节增减方向,2表示上调,1表示下调,其他数据认为是通讯

v

上式表明,无论X值是否精确,预测系统无功的变化方向与母线目标电压变化 的方向始终是相同的。在母线电压由一个稳态值向目标电压变化过程中,系 统无功先用系统阻抗估算值进行计算,母线电压随着无功调节开始变化,当 母线电压变化超过死区值时,将得到较准确的系统阻抗值(X),因此可得到

精确的系统无功预测值。

设备功能与联结

通讯数据处理平台(或监控中心)作为发电侧主控单元,兼有通讯、数据库、计算分配、 人机界面、参数编辑、运行状态监视等功能。联结部分:电力调度数据网、RTU、执行终 端 、MMI监视终端。 调控系统(或执行终端):各机组AVC控制的数据采集及控制信号输出。每台机组配置一 台。联结部分:AVR、DCS、监控中心(即上位机)。 MMI监视终端具有 人机界面、状态监视等功能,联结部分:上位机。 执行终端与励磁调节器间通过控制电缆联结,控制信号经电缆输入励磁调节器。 执行终端与DCS间通过控制电缆联结,AVC状态信号送至DCS供运行监视,DCS可对进 行AVC系统的投切操作。

上位机程序退出发电侧电压无功自动调控系统安徽省电力科学研究院执行终端指示灯逻辑说明执行终端硬件输入节点正常输出节点正常通讯数据正常cpu工作状态上位机程序退出发电侧电压无功自动调控系统安徽省电力科学研究院执行终端指示灯逻辑说明上位机程序退出发电侧电压无功自动调控系统安徽省电力科学研究院执行终端指示灯逻辑说明aavr自动信号消失brtu通信故障c省调通信中断未选择本地控制d无功越高闭锁e机端电压越高闭锁f机端电流越高闭锁g母线电压越高闭锁h有功越高闭锁i母线电压越有效值j有功越有效值k无功越有效值l机端电压越有效值m机端电流越有效值n数据波动过大o数据停止刷新p终端通信恢复且具备上述任一条件aavr自动信号出现brtu通信正常c省调通信恢复正常未选择本地控制d无功出力位于高低闭锁之间e机端电压位于高低闭锁之间f机端电流位于高低闭锁之间g有功出力位于高低闭锁之间h母线电压位于高低闭锁之间i闭锁指示灯亮时终端通讯异常j上位机程序退出五分钟后将自动熄灭发电侧电压无功自动调控系统安徽省电力科学研究院执行终端指示灯逻辑说明aavr自动信号消失brtu通信故障c省调通信中断未选择本地控制d无功越低闭锁e机端电压越低闭锁f机端电流越低闭锁g母线电压越低闭锁h有功越低闭锁i母线电压越有效值j有功越有效值k无功越有效值l机端电压越有效值m机端电流越有效值n数据波动过大o数据停止刷新p终端通信恢复且具备上述任一条件aavr自动信号出现brtu通信正常c省调通信恢复正常未选择本地控制d无功出力位于高低闭锁之间e机端电压位于高低闭锁之间f机端电流位于高低闭锁之间g有功出力位于高低闭锁之间h母线电压位于高低闭锁之间i闭锁指示灯亮时终端通讯异常j上位机程序退出五分钟后将自动熄灭发电侧电压无功自动调控系统安徽省电力科学研究院执行终端指示灯逻辑说明系统执行减磁指令解除条件

avr指令集4

MOVW - Copy Register Word

This instruction makes a copy of one register pair into another register pair. The source register pair Rr+1:Rr is left unchanged, while the destination register pair Rd+1:Rd is loaded with a copy of Rr + 1:Rr.This instruction is not available in all devices. Refer to the device specific instruction set summary.

AVR单片机指令集

ADD Rd, Rr 无进位加法 Rd ← Rd + Rr Z,C,N,V,H 1 ADC Rd, Rr 带进位加法 Rd ← Rd + Rr + C Z,C,N,V,H 1 ADIW Rdl,K 立即数与字相加 Rdh:Rdl ← Rdh:Rdl + K Z,C,N,V,S 2 SUB Rd, Rr 无进位减法 Rd ← Rd - Rr Z,C,N,V,H 1 SUBI Rd, K 减立即数 Rd ← Rd - K Z,C,N,V,H 1 SBC Rd, Rr 带进位减法 Rd ← Rd - Rr - C Z,C,N,V,H 1 SBCI Rd, K 带进位减立即数 Rd ← Rd - K - C Z,C,N,V,H 1 SBIW Rdl,K 从字中减立即数 Rdh:Rdl ← Rdh:Rdl - K Z,C,N,V,S 2 AND Rd, Rr 逻辑与 Rd ← Rd • Rr Z,N,V 1 ANDI Rd, K 与立即数的逻辑与操作 Rd ← Rd • K Z,N,V 1 OR Rd, Rr 逻辑或 Rd ← Rd v Rr Z,N,V 1 ORI Rd, K 与立即数的逻辑或操作 Rd ← Rd v K Z,N,V 1 EOR Rd, Rr 异或 Rd ← Rd ⊕ Rr Z,N,V 1 COM Rd 1 的补码 Rd ← 0xFF − Rd Z,C,N,V 1 NEG Rd 2 的补码 Rd ← 0x00 − Rd Z,C,N,V,H 1 SBR Rd,K 设置寄存器的位 Rd ← Rd v K Z,N,V 1 CBR Rd,K 寄存器位清零 Rd ← Rd • (0xFF - K) Z,N,V 1 INC Rd 加一操作 Rd ← Rd + 1 Z,N,V 1 DEC Rd 减一操作 Rd ← Rd − 1 Z,N,V 1 TST Rd 测试是否为零或负 Rd ← Rd • Rd Z,N,V 1 CLR Rd 寄存器清零 Rd ← Rd ⊕ Rd Z,N,V 1 SER Rd 寄存器置位 Rd ← 0xFF None 1 MUL Rd, Rr 无符号数乘法 R1:R0 ← Rd x Rr Z,C 2 MULS Rd, Rr 有符号数乘法 R1:R0 ← Rd x Rr Z,C 2 MULSU Rd, Rr 有符号数与无符号数乘法 R1:R0 ← Rd x Rr Z,C 2 FMUL Rd, Rr 无符号小数乘法 R1:R0 ← (Rd x Rr) << 1 Z,C 2 FMULS Rd, Rr 有符号小数乘法 R1:R0 ← (Rd x Rr) << 1 Z,C 2 FMULSU Rd, Rr 有符号小数与无符号小数乘法 R1:R0 ← (Rd x Rr) << 1 Z,C 2跳转指令RJMP k 相对跳转 PC ← PC + k + 1 无 2 IJMP 间接跳转到(Z) PC ← Z 无 2 RCALL k 相对子程序调用 PC ← PC + k + 1 无 3 ICALL 间接调用(Z) PC ← Z 无 3 RET 子程序返回 PC ← STACK 无 4 RETI 中断返回 PC ← STACK I 4 CPSE Rd,Rr 比较,相等则跳过下一条指令if (Rd = Rr) PC ← PC + 2 or 3 无 1 / 2 / 3 CP Rd,Rr 比较 Rd − Rr Z, N,V,C,H 1 CPC Rd,Rr 带进位比较 Rd − Rr − C Z, N,V,C,H 1 CPI Rd,K 与立即数比较 Rd − K Z, N,V,C,H 1 SBRC Rr, b 寄存器位为"0” 则跳过下一条指令if (Rr(b)=0) PC ← PC + 2 or 3 无 1 / 2 / 3 SBRS Rr, b 寄存器位为"1” 则跳过下一条指令if (Rr(b)=1) PC ← PC + 2 or 3 无 1 / 2 / 3 SBIC P, b I/O 寄存器位为"0” 则跳过下一条指令if (P(b)=0) PC ← PC + 2 or 3 无 1 / 2 / 3 SBIS P, b I/O 寄存器位为"1” 则跳过下一条指令if (P(b)=1) PC ← PC + 2 or 3 无 1 / 2 / 3 BRBS s, k 状态寄存器位为"1” 则跳过下一条指令if (SREG(s) = 1) then PC←PC+k + 1 无 1 / 2 BRBC s, k 状态寄存器位为"0” 则跳过下一条指令if (SREG(s) = 0) then PC←PC+k + 1 无 1 / 2 BREQ k 相等则跳转if (Z = 1) then PC ← PC + k + 1 无 1 / 2 BRNE k 不相等则跳转if (Z = 0) then PC ← PC + k + 1 无 1 / 2 BRCS k 进位位为"1” 则跳转if (C = 1) then PC ← PC + k + 1 无 1 / 2 BRCC k 进位位为"0” 则跳转if (C = 0) then PC ← PC + k + 1 无 1 / 2 BRSH k 大于或等于则跳转 if (C = 0) then PC ← PC + k + 1 无 1 / 2 BRLO k 小于则跳转if (C = 1) then PC ← PC + k + 1 无 1 / 2 BRMI k 负则跳转if (N = 1) then PC ← PC + k + 1 无 1 / 2 BRPL k 正则跳转if (N = 0) then PC ← PC + k + 1 无 1 / 2 BRGE k 有符号数大于或等于则跳转if (N ⊕ V= 0) then PC ← PC + k + 1 无 1 / 2 BRLT k 有符号数负则跳转if (N ⊕ V= 1) then PC ← PC + k + 1 无 1 / 2 BRHS k 半进位位为"1” 则跳转if (H = 1) then PC ← PC + k + 1 无 1 / 2 BRHC k 半进位位为"0” 则跳转if (H = 0) then PC ← PC + k + 1 无 1 / 2 BRTS k T 为"1” 则跳转if (T = 1) then PC ← PC + k + 1 无 1 / 2 BRTC k T 为"0” 则跳转if (T = 0) then PC ← PC + k + 1 无 1 / 2 BRVS k 溢出标志为"1” 则跳转if (V = 1) then PC ← PC + k + 1 无 1 / 2 BRVC k 溢出标志为"0” 则跳转if (V = 0) then PC ← PC + k + 1 无 1 / 2 274 ATmega8(L)2486N–AVR–07/04指令操作数说明操作标志# 时钟数BRIE k 中断使能再跳转if ( I = 1) then PC ← PC + k + 1 无 1 / 2 BRID k 中断禁用再跳转if ( I = 0) then PC ← PC + k + 1 无 1 / 2数据传送指令MOV Rd, Rr 寄存器间复制 Rd ← Rr 无 1 MOVW Rd, Rr 复制寄存器字 Rd+1:Rd ← Rr+1:Rr 无 1 LDI Rd, K 加载立即数 Rd ← K 无 1 LD Rd, X 加载间接寻址数据 Rd ← (X) 无 2 LD Rd, X+ 加载间接寻址数据,然后地址加一 Rd ← (X), X ← X + 1 无 2 LD Rd, - X 地址减一后加载间接寻址数据 X ← X - 1, Rd ← (X) 无 2 LD Rd, Y 加载间接寻址数据 Rd ← (Y) 无 2 LD Rd, Y+ 加载间接寻址数据,然后地址加一 Rd ← (Y), Y ← Y + 1 无 2 LD Rd, - Y 地址减一后加载间接寻址数据 Y ← Y - 1, Rd ← (Y) 无 2 LDD Rd,Y+q 加载带偏移量的间接寻址数据 Rd ← (Y + q) 无 2 LD Rd, Z 加载间接寻址数据 Rd ← (Z) 无 2 LD Rd, Z+ 加载间接寻址数据,然后地址加一 Rd ← (Z), Z ← Z+1 无 2 LD Rd, -Z 地址减一后加载间接寻址数据 Z ← Z - 1, Rd ← (Z) 无 2 LDD Rd, Z+q 加载带偏移量的间接寻址数据 Rd ← (Z + q) 无 2 LDS Rd, k 从SRAM 加载数据 Rd ← (k) 无 2 ST X, Rr 以间接寻址方式存储数据 (X) ← Rr 无 2 ST X+, Rr 以间接寻址方式存储数据,然后地址加一 (X) ← Rr, X ← X + 1 无 2 ST - X, Rr 地址减一后以间接寻址方式存储数据 X ← X - 1, (X) ← Rr 无 2 ST Y, Rr 加载间接寻址数据 (Y) ← Rr 无 2 ST Y+, Rr 加载间接寻址数据,然后地址加一 (Y) ← Rr, Y ← Y + 1 无 2 ST - Y, Rr 地址减一后加载间接寻址数据 Y ← Y - 1, (Y) ← Rr 无 2 STD Y+q,Rr 加载带偏移量的间接寻址数据 (Y + q) ← Rr 无 2 ST Z, Rr 加载间接寻址数据 (Z) ← Rr 无 2 ST Z+, Rr 加载间接寻址数据,然后地址加一 (Z) ← Rr, Z ← Z + 1 无 2 ST -Z, Rr 地址减一后加载间接寻址数据 Z ← Z - 1, (Z) ← Rr 无 2 STD Z+q,Rr 加载带偏移量的间接寻址数据 (Z + q) ← Rr 无 2 STS k, Rr 从SRAM 加载数据 (k) ← Rr 无 2 LPM 加载程序空间的数据 R0 ← (Z) 无 3 LPM Rd, Z 加载程序空间的数据 Rd ← (Z) 无 3 LPM Rd, Z+ 加载程序空间的数据,然后地址加一 Rd ← (Z), Z ← Z+1 无 3 SPM 保存程序空间的数据 (Z) ← R1:R0 无 -IN Rd, P 从I/O 端口读数据 Rd ← P 无 1 OUT P, Rr 输出端口 P ← Rr 无 1 PUSH Rr 将寄存器推入堆栈 STACK ← Rr 无 2 POP Rd 将寄存器从堆栈中弹出 Rd ← STACK 无 2位和位测试指令SBI P,b I/O 寄存器位置位 I/O(P,b) ← 1 无 2 CBI P,b I/O 寄存器位清零 I/O(P,b) ← 0 无 2 LSL Rd 逻辑左移 Rd(n+1) ← Rd(n), Rd(0) ← 0 Z,C,N,V 1 LSR Rd 逻辑右移 Rd(n) ← Rd(n+1), Rd(7) ← 0 Z,C,N,V 1 ROL Rd 带进位循环左移 Rd(0)←C,Rd(n+1)← Rd(n),C←Rd(7) Z,C,N,V 1 ROR Rd 带进位循环右移 Rd(7)←C,Rd(n)← Rd(n+1),C←Rd(0) Z,C,N,V 1 ASR Rd 算术右移 Rd(n) ← Rd(n+1), n=0..6 Z,C,N,V 1 SWAP Rd 高低半字节交换 Rd(3..0)←Rd(7..4),Rd(7..4)←Rd(3..0) 无 1 BSET s 标志置位 SREG(s) ← 1 SREG(s) 1 BCLR s 标志清零 SREG(s) ← 0 SREG(s) 1 BST Rr, b 从寄存器将位赋给T T ← Rr(b) T 1 BLD Rd, b 将T 赋给寄存器位 Rd(b) ← T 无 1 SEC 进位位置位 C ← 1 C 1 CLC 进位位清零 C ← 0 C 1 SEN 负标志位置位 N ← 1 N 1 CLN 负标志位清零 N ← 0 N 1 SEZ 零标志位置位 Z ← 1 Z 1 CLZ 零标志位清零 Z ← 0 Z 1 SEI 全局中断使能 I ← 1 I 1 CLI 全局中断禁用 I ← 0 I 1 SES 符号测试标志位置位 S ← 1 S 1 CLS 符号测试标志位清零 S ← 0 S 1 SEV 2 的补码溢出标志置位 V ← 1 V 1 CLV 2 的补码溢出标志清零 V ← 0 V 1 SET SREG 的T 置位 T ← 1 T 1指令集概述275ATmega8(L)2486N–AVR–07/04指令操作数说明操作标志# 时钟数CLT SREG 的T 清零 T ← 0 T 1 SEH SREG 的半进位标志置位 H ← 1 H 1 CLH SREG 的半进位标志清零 H ← 0 H 1 MCU 控制指令NOP 空操作 无 1 SLEEP 休眠( 见对睡眠功能的特殊说明) 无 1 WDR 复位看门狗( 见对WDR/timer 的特殊说明) 无 1。

第三讲 AVR位操作

4、按位进行操作

举例五:将PB2、PB3定义为输入,不带上拉 电阻 DDRB&=~(BIT(2)|BIT(3)); //定义 PB2、PB3 为输入 PORTB&=~(BIT(2)|BIT(3)); // 将 PORT 置0, 没有上拉电阻

4、按位进行操作

举例六:将PB2、PB3定义为输入,带上拉电阻。即 没有引用这些引脚时,缺省值为高电平 SFIOR&=~BIT(PUD); // SFIOR寄存器的上拉电阻控 制位PUD置0,在整个代码中,这句话可以不出现,或 仅出现一次即可。因为它是一个控制全部上拉电阻的 控制位。 DDRB&=~(BIT(2)|BIT(3)); //定义 PB2、PB3为输入 PORTB|=BIT(2)|BIT(3); // 将 PORT 置1,满足上拉电 阻的另一个条件

& 位逻辑与运算

& 运算的规则是当两个位都为1时,结果为1, 否则为0;(小提示:你可以在心中默念乘法来 代替它,真与真,就是1乘以1,真与假,就是1 乘以0,假与假,就是0乘以0) 在单片机中,常用于某一位清0,其他位不变 例:将PC4口清零,我们写出二进制数 11101111 0XEF

PC4

PORTC &=0xEF (等价于PORTC=PORTC&0xEF) 或PORTC&=0b11101111

读取PC2口的数据

假设 PC口接了若干设备,当前状态是 11110010,而我们现在要读取第3位即PC2, 则 1111 0110 PA2口的当前值 0000 0 100

求与后,最终变成 0000 0000

通过(1<<PA2)得出的值 那么if ((PINC&(1<<PC2))==0) 实际上就读出了 PC2的值

AVR指令

(31) Z 寄存器(4): ST Z,Rr;ST Z+,Rr;ST –Z,Rr;STD Z+q,Rr

读存储器(1): LPM

ADD Rd,Rr 加法 BRSH k C=1 无符号数 转 SBI P,b 置位I/O 位

ADC Rd,Rr 带进位加 BRLO k C=0无符号数小于转 CBI P,b 清零I/O 位

ADIW Rdl,K 加立即数 BRMI k N=1 负数转移 LSL Rd 左移

I/O指令(2): IN,OUT

栈指令(2): PUSH,POP

算术指令与 加(4): ADD,ADC,ADIW,INC;

(10) 减(6): SUB,SUBI,SBC,SBCI,SBIW,DEC

asr rd 算术右移

andi rd,k 与立即数

brne k 不相等转移

swap rd 半字节交换

or rd,rr 或brcs k c 置位转

bset s 置位sreg

ori rd,k 或立即数

brcc k c 清零转

bclr s 清零sreg

eor rd,rr 异或brsh k 转

Y寄存器(4): LD Rd,Y;LD Rd,Y+;LD Rd,-Y;LDD Rd,Y+q

Z寄存器(4): LD Rd,Z;LD Rd,Z+;LD Rd,-Z;LDD Rd,Z+q

X 寄存器(3): ST X,Rr;ST X+,Rr;ST –X,Rr

(31) BCLR -- CLI,CLT,CLH,CLS,CLV,CLN,CLZ,CLC (CL清0某位)

AVR单片机指令系统

第五章A V R单片机指令系统计算机的指令系统是一套控制计算机操作的代码,称之为机器语言。

计算机只能识别和执行机器语言的指令。

为了便于人们理解、记忆和使用,通常用汇编语言指令来描述计算机的指令系统。

汇编语言指令可通过汇编器翻译成计算机能识别的机器语言。

AVR单片机指令系统是RISC结构的精简指令集,是一种简明易掌握﹑效率高的指令系统。

SL-DIY02-3开发实验器使用AT90S8535单片机,有118条指令,而我们所做的11个实验程序仅用了34条指令,我们重点讲这34条指令,其余指令就可自学了。

AVR器件(指令速查表)118条指令器件1.不带进位加法ADD一不带进位加说明:两个寄存器不带进位C标志加,结果送目的寄存器Rd。

操作:Rd✍Rd+Rr语法:操作码:程序计数器:ADDRd,RrO≤d≤31,0≤r≤31PC✍PC+1例子:。

(实践操作程序4411.ASM)实践操作例子*.ASM,必须编译生成*.OBJ文件才可调试,如要修改*.ASM,必须修改文件属性,去掉*.ASM只读文件属性2.带进位加法ADC-一带进位加说明:两个寄存器和C标志的内容相加,结果送目的寄存器Rd。

操作:Rd←Rd+Rr+C语法:操作码:程序计数器:ADCRd,Rr0≤d≤31,0≤r≤31PC←PC+1例子:(实践操作程序4412.ASM)3.减1指令DEC一减1说明:寄存器Rd的内容减1,结果送目的寄存器Rd中。

操作:Rd✍Rd-l语法:操作码:程序计数器:DECRd0≤d≤31PC✍PC十1例子:(实践操作程序4426.ASM)4.立即数比较CPI——带立即数比较说明:该指令完成寄存器Rd和常数的比较操作。

寄存器的内容不改变。

该指令后能使用所有条件转移指令。

操作:Rd-K语法:操作码:程序计数器:CPIRd,K16≤d≤31,0≤K≤255PC✍PC+1例子:(实践操作程序4463.ASM)5.带立即数与ANDI——立即数逻辑与;全1为1,有0即0说明:寄存器Rd的内容与常数逻辑与,结果送目的寄存器Rd。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

算术和逻辑指令ESPM 扩展存储程序存储器位指令和位测试指令

ADD 加法EICALL延长间接调用子程序SBI 置位I/O 位ADC 带进位加BRCC C 清零转CBI 清零I/O 位

ADIW 加立即数BRSH 转LSL 左移

SUB 减法BRLO 小于转(无符号) LSR 右移

SUBI 减立即数BRMI 负数转移ROL 带进位左循环

SBC 带进位减BRPL 正数转移ROR 带进位右循环

SBCI 带C 减立即数 BRGE 转(带符号) ASR 算术右移

SBIW 减立即数BRLT 小于转(带符号) SWAP 半字节交换

AND 与BRHS H 置位转移BSET 置位SREG

ANDI 与立即数BRHC H 清零转移BCLR 清零SREG

OR 或BRTS T 置位转移BST Rr 的b 位送T

ORI 或立即数BRTC T 清零转移BLD T 送Rr 的b 位EOR 异或BRVS V 置位转移SEC 置位C

COM 取反BRVC V 清零转移CLC 清零C

NEG 取补BRIE 中断位置位转移SEN 置位N

SBR 寄存器位置位BRID 中断位清零转移CLN 清零N

CBR 寄存器位清零数据传送指令SEZ 置位Z

INC 加1 MOV 寄存器传送CLZ 清零Z

DEC 减1 MOVW 拷贝寄存器字SEI 置位I

TST 测试零或负LDI 装入立即数CLI 清零I

CLR 寄存器清零LD X X 间接取数SES 置位S

SER 寄存器置FF LD X+ X 间接取数后CLS 清零S

MUL 乘法LD -X X 间接取数先SEV 置位V

MULS 有符号数乘法LD Y Y 间接取数CLV 清零V

MULSU 有(无)符号数乘法LD Y+ Y 间接取数后+ SET 置位T FMUL 小数乘法LD –Y Y 间接取数先CLT 清零T

FMULS 有符号数乘法LDD Yq Y 间接取数q SEH 置位H FMULSU 有(无)符号小数乘法LD Z Z 间接取数CLH 清零H 条件转移指令LD Z+ Z 间接取数后NOP 空操作

RJMP 相对转移LD –Z Z 间接取数先SLEEP 休眠

IJMP 间接转移LDD Zq Z 间接取数q WDR 看门狗复位

JMP 长转移LDS 从SRAM 装入

RCALL 相对调用ST X X 间接存数90 条指令器件( )

ICALL 间接调用ST X+ X 间接存数后Attiny11/12/15/22

CALL 长调用ST –X X 间接存数先

RET 子程序返回ST Y Y 间接存数89 条指令器件

RETI 中断返回ST Y+ Y 间接存数后AT90S1200

CPSE 比较相等跳行ST –Y Y 间接存数先118 条指令器件( )

CP 比较STD Yq Y 间接存数q AT90S2313/2323/2343/2333 CPC 带进位比较ST Z Z 间接存数AT90S4414/4433/4434/8515 CPI 带立即数比较ST Z+ Z 间接存数后AT90S8534/8535

ST –Z Z 间接存数先121 条指令器件( )

SBRS 位置位跳行STD Zq Z 间接存数q ATmega603/103

SBIC I/O 位清零跳行STS 数据送SRAM 130 条指令器件( ) SBIS I/O 位置位跳行LPM 装程序存储器ATmega161

BRBS SREG 位置位转LPM Z Z 90 条指令= +89 条

BRBC SREG 位清零转LPM Z+ Z+ 118 条指令= + 90 条BREQ 相等转移SPM 存储程序存储器121 条指令= + 118 条BRNE 不相等转移IN I/O 口输入130 条指令= +121 条BRCS C 置位转OUT 送I/O 口更详细资料阅

ELPM 扩展装载程序存储器PUSH 压栈英文指令表

EIJMP 扩展间接跳转POP 出栈。