80C51微处理器嵌入式内核的设计研究

80C51嵌入式微处理器内核的低功耗设计

数值逻 程序地 数据地 寄存器 存储器 主控制 控制 辑运算 址产生 址产生 更新 模块 模块 模块 模块 模块 模块

% )(23 9:;<+, &寄存器更新模块 % 包括了 (23

( 特殊功能寄存器 $ 的配置 ’ 移 位 操 作 ’ 内 部 其 他 重 要寄存器的设置以及相应的更新电路 %

K".L &;.

C=F@I.5C#!" ( 电 源 电 压 IOIS $" 用 06F=,:5G,6 对 未

进行低 功 耗 设 计 的 嵌 入 式 微 处 理 器 内 核 进 行 功 耗 分析 "得到的结果如表 # 所示 &

表# 微处理器内核功耗分析结果 总功耗 (=V $ 动态功耗 (=V $ 峰值功耗 (=V $

制 " 时钟和复位信号的产生以及中断响应控制等 !

同时 " 对微处理器内部的每一模块也进行了细 致的功 耗 分 析 " 以 便 针 对 系 统 中 能 量 消 耗 大 的 部 分 " 有重点地进行优化 " 使低功耗的设计更为有效 % 表 " 给出了微处理器内核的功耗分布 " 即每一模块 的功耗占总功耗的百分比 %

=91>/6;>? +YQ XT] ^T]QW _QRNOI TU HI $%&’# QC‘Q__Q_ CNVWT^WTVQRRTW VTWQ NR ^WQRQISQ_ NI SYNR ^H^QWB 8T]QW VTC^TIQISR TU

SYQ VTWQ HWQ HIHXJaQ_ ‘HRQ_ TI QIQWOJ _NRRN^HSNTI SYQTWJ NI &()* VNWVGNSB ,VVTW_NIO ST SYQ H‘TZQ HIHXJaQ_ WQRGXS6 HI_ H^^XJ H RQWNQR TU WQ_GVNIO ^T]QW CQSYT_R NIZTXZNIO VXTVbEOHSNIO6 SYQ WQ_QRNOI HI_ T^SNCNaHSNTI TU SYQ CNVWT^WTVQRRTW NR ^WTVQRRQ_B +YQ OHSQEXQZQX RNCGXHSNTI TU SYQ VTWQ TI H %BA’ "C SQVYITXTOJ XN‘WHWJ _QCTIRSWHSQR SYQ RJRSQCNV ^T]QW WQ_GVSNTI VXTRQ ST ’%=B

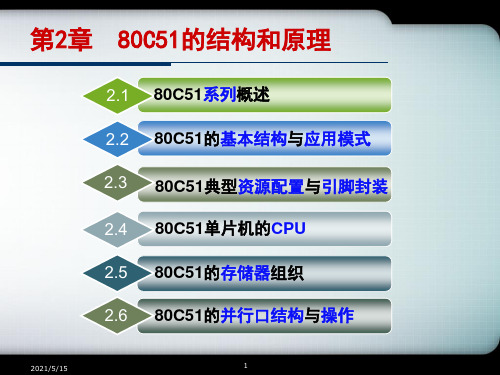

80C51的结构和原理

注:类似的还有Philips公司的 87LPC64,20引脚 8XC748/750/(751),24引脚 8X749(752),28引脚 8XC754,28引脚 等等

二、引脚分类: 1、主电源引脚 Vss、Vcc 2、外接晶振引脚 XTAL1、XTAL2

2021/5/15

14

3、控制或复位引脚

①、RST / VPD ——复位 /备用电源

2021/5/15

16

2.4 80C51的CPU

VCC

40

RAM 地址寄存器

RAM 128 /256字节

ROM 地址寄存器

程序计数器PC

DPH 缓冲器

DPL

P0.0 ~ P0.7

EA ALE PSEN P2.7 ~ P2.0

39

32

P0口驱动器

31

30 29 28

21

P2口驱动器

ROM 4K/8K字节

ALU

振荡器

P1口驱动器

1

8

P1.0 ~ P1.7

P3口驱动器

9

10

17

18

19

20

RST P3.0 ~ P3.7 XTAL2 XTAL1 VSS

2021/5/15

17

80C51的内部结构 一、总体结构

1、中央处理单元CPU(8位) 用于数据处理、位操作(位测试、置位、复位)

2、只读存储器ROM(4KB或8KB) 用于永久性存储应用程序,掩膜ROM、EPROM、EEPROM

GND 10

89S2051

20 VCC 19 P1.7 18 P1.6 17 P1.5 16 P1.4 15 P1.3 14 P1.2 13 P1.1/AIN1 12 P1.0/AIN0 11 P3.7

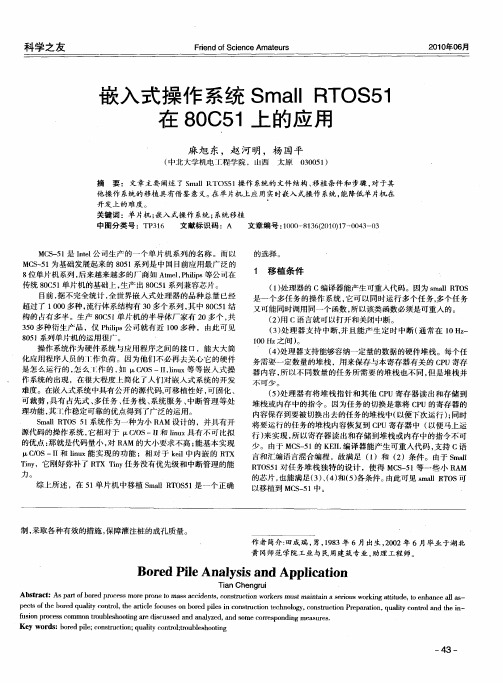

嵌入式操作系统Small RTOS51在80C51上的应用

综上所述 ,在 5 单 片机 中移植 S a T S 1 一个正确 1 m lR O 5 是 l

( ) 理器有将堆 栈指针 和其他 C U寄存器 读出和存储 到 5处 P 堆栈或 内存 中的指令 。因为任务的切换是靠将 C U的寄存器 的 P 内容保存到要被切换出去的任务的堆栈 中( 以便下次运行 ) 同时 ; 将要运行 的任 务的堆栈 内容恢 复到 C U寄存器 中 ( P 以便 马上运 行) 来实现 , 所以寄存器读 出和存储到堆栈或 内存 中的指令不可 少 。由于 M S 5 C 一 1的 K I EL编译器 能产 生可重人代码 , 支持 c语 言和汇编语言混合 编程 ,故满足 ( )和 ( )条件 。由于 S a 1 2 ml l R O 5 对 任务堆栈 独特的设计 ,使得 MC 一 l等一些 小 R M T S1 S5 A 的芯片 , 也能满足( )( ) ( ) 3 、4 和 5 各条件 。 由此可见 s a T S可 m lR O l 以移 植 到 M S 5 C 一 1中 。

的选择 。

1 移 植条件

( ) 理 器 的 C编 译 器 能 产生 可重 入 代 码 。 因为 s l R O 1处 ma T S l

是 一个多任务 的操 作系统 , 它可 以同时运行 多个任务 , 多个任 务 又可能 同时调用 同一个函数 , 以该类 函数必须是可重人 的。 所

T a e g u i n Ch n r i

Absr c :Aspa t f r dprc s r o s c i e s c n t cin w r e mu t i ti e iu o kn t td , oe h n ea s ta t r o e o e smo eprnet ma sa c d nt o s u t o k r s na na s r sw r ig aⅡ u e t n a c Ⅱa — bo o r o ma o

单片机第2章80C51的结构与原理课件

通信。

并行通信接口的构成和使用

1

并行传输

2

接口标准

3

应用举例

同时发送和接收多个数据

定义了数据传输的电气和

并行通信接口常用于图形

位,适用于高速数据传输

逻辑特性,如PIO、DDR、

显示、高速数据采集、并

和快速响应的应用。

USB等。

行计算等。

3

寄存器

用于存储临时数据和控制单元的状态信息。

80C51的存储系统:ROM与RAM的区别

ROM

RA M

只读存储器,用于存储程序和常量数据。

随机存储器,用于存储变量和临时数据。

片内I/O口的构成和使用

引脚接口

输入模式

通过引脚连接外部设备和单片机。

接收外部信号并将其转换为数字信号。

输出模式

通信接口

将数字信号转换为外部的模拟或数字信号。

80C51芯片在各个行业中

的特点,提供了出色的性

RAM,使得80C51非常灵

得到广泛应用,包括消费

能表现,适用于各种领域

活,能够适应不同的应用

电子、通信、汽车电子、

的嵌入式应用。

需求。

医疗设备等领域。

单片机中的CPU结构和工作原理

1

控制单元

负责指令解码和控制单片机的操作。

2

运算单元

执行算术和逻辑运算,以及位操作等基本操作。

单片机第2章80C51的结

构与原理课件

本课件将详细介绍单片机80C51的结构和原理。包括单片机的基本结构与分

类、80C51芯片的特点与应用、CPU结构和工作原理、ROM与RAM的区别等内

容。

80C51芯片:特点与应用

1

单片机毕业设计80c51

单片机毕业设计80c51本文的毕业设计主要涉及到80C51单片机的应用。

本篇文章将介绍单片机的基本原理、在数字电子钟的设计中的具体应用、硬件设计和软件编程,并给出程序设计流程与详细实现过程。

一、 80C51单片机的基本原理只要有些基础的理解,学习单片机并不难。

单片机是包含CPU、ROM、RAM和其他外设的一种集成电路(IC)芯片。

单片机因其体积小、功耗低、成本低而在实际应用中广泛使用。

具有代表性的是80C51单片机系列。

80C51单片机有多种不同的型号,每个型号内置指令集在某种程度上都有所不同。

最简单的80C51型号内置的指令集只有40多种指令。

可以想象,由于指令集非常简化、结构紧凑,这样设计出来的芯片具有性能非常稳定的特点。

二、数字电子钟的设计数字电子钟是指采用数字电路或数字电子技术设计的显示时间的钟。

数字电子钟广泛应用于生活中的种种需要,能够比较稳定地显示时间,其他功能还包括定时、闹钟、备忘等选项。

三、数字电子钟的硬件设计数字电子钟的硬件设计涵盖了三个方面:1. 显示电路的设计数字电子钟的显视屏幕通常是7片LED,其中6片是数字显示屏,第7片为冒号显示屏。

这个设计采用COS-8886电路,典型的应用范围是数码电子表、温度计等。

2. 时基方案的设计时基方案是指数字电子钟中的总体控制方案。

这里我们采用的是74HC4060的集成电路。

使用74HC4060,可以非常方便地进行时钟频率的分频设计。

3. 蓝牙通信模块的设计蓝牙通信模块的设计中,我们使用了常见的蓝牙串口传输模块,如HC-06,其工作电压在3.3V ~ 5V之间,具备良好的兼容性。

四、数字电子钟的软件编程数字电子钟的软件编程主要涉及以下两个方面:1. 定时计数器的设计采用80C51单片机设计定时计数器时,需要考虑到时钟频率、计时器精度、转换精度等问题。

借助于8051单片机提供的Timer/Counter模块,可以很方便地实现这个功能。

2. 蓝牙通信程序设计程序设计中需要考虑到串口通信协议,包括蓝牙模块的波特率,校验位和数据位等问题。

微处理器与嵌入式系统设计

微处理器与嵌入式系统设计电子与电气工程是现代科技领域中不可或缺的重要学科之一。

在当今数字化时代,微处理器与嵌入式系统设计成为电子与电气工程领域中的热门话题。

本文将深入探讨微处理器与嵌入式系统设计的相关概念、应用以及未来发展趋势。

1. 微处理器的基本概念微处理器是一种集成电路芯片,内部包含了中央处理器(CPU)、内存控制器、输入输出控制器等核心组件。

它是计算机系统的大脑,负责处理和执行各种指令,实现数据的运算和处理。

微处理器的性能和功能直接影响到计算机的运行速度和效率。

2. 嵌入式系统的定义与特点嵌入式系统是指将计算机技术和电子技术应用于各种电子设备中,使其具备智能化、自动化和网络化等特点的系统。

与通用计算机不同,嵌入式系统通常具有体积小、功耗低、功能专一等特点。

它广泛应用于汽车电子、智能家居、医疗设备、工业控制等领域。

3. 微处理器在嵌入式系统中的应用微处理器在嵌入式系统中起到了至关重要的作用。

它可以实现对各种外设的控制和管理,同时还能处理各种数据和信号。

例如,在智能手机中,微处理器负责控制屏幕显示、摄像头拍摄、无线通信等功能;在工业自动化系统中,微处理器可以实现对生产线的自动控制和监测。

4. 嵌入式系统设计的挑战与解决方案嵌入式系统设计面临着多种挑战,如资源受限、功耗管理、实时性要求等。

为了解决这些问题,设计工程师需要充分考虑硬件和软件的结合,采用优化的算法和技术。

例如,通过对系统进行功耗优化、任务调度优化和资源分配优化,可以提高系统的效率和性能。

5. 微处理器与嵌入式系统的未来发展趋势随着物联网和人工智能等领域的快速发展,微处理器与嵌入式系统的应用范围将进一步扩大。

未来的微处理器将更加强大和高效,能够处理更复杂的任务和数据。

嵌入式系统将更加智能化和自动化,能够与其他设备进行无缝连接和通信。

综上所述,微处理器与嵌入式系统设计是电子与电气工程领域中的重要研究方向。

通过深入研究微处理器的基本概念和嵌入式系统的特点,我们可以更好地理解它们在现代科技中的应用和意义。

AT80C51的工作原理

AT80C51的工作原理AT80C51是一款8位微控制器,其工作原理如下:1. 寄存器:AT80C51包含了多个内部寄存器,用于存储数据和控制微控制器的操作。

这些寄存器可以通过特定的地址访问,并且用于存储输入/输出端口、时钟控制、中断向量等信息。

2. CPU:AT80C51的中央处理器(CPU)负责执行指令和处理数据。

它包含一个累加器(ACC)和多个通用寄存器(R0-R7),用于进行算术和逻辑运算。

CPU通过从寄存器中读取数据、执行指令、写入结果来完成计算。

3. 存储器:AT80C51具有内部存储器和外部存储器接口。

内部存储器包括程序存储器(ROM)和数据存储器(RAM)。

ROM用于存储程序指令,RAM用于存储临时数据和变量。

外部存储器接口可以连接额外的存储器设备,以扩展存储容量。

4. 时钟:AT80C51使用时钟来驱动CPU和其他部件的操作。

时钟可以通过内部时钟源或外部时钟源提供。

时钟速度决定了AT80C51的工作频率和指令执行速度。

5. 输入/输出(I/O)端口:AT80C51具有多个可编程输入/输出端口。

这些端口可以连接外部设备,如传感器、显示器、键盘等。

通过读取和写入I/O端口的状态,AT80C51可以与外部设备进行通信。

6. 中断:AT80C51支持中断功能,可以响应外部信号的触发。

当发生中断信号时,CPU会立即暂停当前的任务,并跳转到对应的中断处理程序。

中断可以用于实时响应外部事件,提高系统的实时性能。

总结起来,AT80C51的工作原理是通过CPU执行指令,从寄存器和存储器中读取数据,进行计算和处理,并与外部设备进行通信。

时钟驱动整个系统的运行,而中断机制能够实现实时响应外部事件。

利用单片机80C51芯片作为核心元件的染整机控制系统技术设计研究与探讨

目录摘要 (I)Abstract (II)1 绪论 (1)1.1染整工艺的概述 (1)1.1.1当前染整业的背景 (1)1.1.2我国纺织染整行业现状 (1)1.2染整机控制系统的原理 (1)1.3国内外的研究现状 (2)1.4本文的主要研究内容 (2)2.硬件设计 (2)2.1硬件系统组成 (2)2.2硬件系统技术路线和具体要求 (3)2.3硬件器件的选择 (4)2.3.1染整机控制器 (4)2.3.1.1 80C51的引脚及功能 (5)2.3.1.2 80C51的定时计数器的原理 (8)2.3.1.3 定时器/计数器的工作方式 (9)2.3.2 A/D转换器芯片ADC0809 (9)2.3.2.1ADC0809的内部逻辑结构 (9)2.3.2.2 信号引脚图 (10)2.3.2.3 80C51单片机与ADC0809接口 (12)2.3.2.4 8路模拟通道选择 (12)2.3.2.5 转换数据的传送 (12)2.3.3 D/A转换器芯片DAC0832 (13)2.3.3.1芯片DAC0832的引脚及功能 (13)2.3.3.2 DAC0832的工作方式 (16)2.3.4单片机的输出端口芯片 (16)2.3.4.1 8155的引脚极其功能 (16)12.3.4.2 8155的工作方式 (17)2.3.5看门狗电路 (18)2.3.6光电耦合器 (19)2.3.7整波电路 (20)2.3.8显示部分设计 (20)2.3.9键盘输入部分设计 (21)3 三菱变频器 (21)3.1三菱变频器(FRA-540)的特性 (21)3.2回路端子说明 (22)3.3三菱变频器在本系统中的运用 (25)4 染整机控制系统的实现 (26)5 软件设计 (26)5.1程序流程图 (26)5.2程序编程 (33)结论 (38)参考文献 (40)摘要本文根据染整机控制系统的需求,利用单片机系统中80C51芯片作为控制部分的核心元件,通过霍尔检测元件检测电机转速,光电隔离电路的电气隔离,整波电路的整波,以及ADC0809、DAC0832、8155等外围芯片,同三菱变频器(FRA-540)、染整机电动机相配合,实现了步速、步长的调整,使其工作在所期望的范围之内。

基于80c51单片机仿真程序

基于80c51单片机仿真程序在现代科技的快速发展下,嵌入式系统已经成为人们生活中不可或缺的一部分。

而在嵌入式系统中,单片机是最常用的核心控制器之一。

80C51单片机作为一种经典的单片机,广泛应用于各个领域。

为了更好地了解和掌握80C51单片机的工作原理和应用,开发仿真程序成为了一种重要的学习手段。

一、80C51单片机简介80C51单片机是由英特尔公司设计的一款8位微控制器。

它采用了哈佛结构,具有较大的存储器容量和丰富的外设接口。

80C51单片机具备高性能、低功耗和易于编程的特点,被广泛应用于电子设备控制、通信、汽车电子等领域。

二、仿真程序的意义仿真程序是一种通过软件模拟硬件工作过程的方法。

对于学习80C51单片机的人来说,仿真程序是一种非常有效的学习工具。

通过仿真程序,我们可以实现对单片机的功能模拟和调试,不仅可以加深对单片机工作原理的理解,还可以提高我们的编程能力和故障排除能力。

三、基于80C51单片机的仿真程序开发1. 硬件仿真在开发基于80C51单片机的仿真程序之前,我们首先需要准备好相应的硬件仿真平台。

常见的硬件仿真平台有Proteus、Keil等。

这些平台提供了丰富的单片机模型和外设模块,可以模拟出真实的硬件环境。

通过硬件仿真,我们可以在不实际搭建电路的情况下,进行单片机程序的开发和测试。

2. 软件开发在硬件仿真平台准备好后,我们就可以开始进行软件开发了。

软件开发主要包括编写程序和调试程序两个步骤。

编写程序时,我们需要根据具体的应用需求,设计相应的算法和逻辑。

在编写过程中,我们可以利用80C51单片机的指令集和外设接口,实现各种功能。

调试程序时,我们可以通过仿真平台提供的调试工具,逐步调试程序,查找和解决问题。

3. 仿真测试在程序开发和调试完成后,我们需要进行仿真测试。

仿真测试是验证程序正确性和性能的重要环节。

通过仿真测试,我们可以模拟出各种工作场景,测试程序在不同情况下的运行情况。

如果测试结果符合预期,说明程序开发成功;如果测试结果不符合预期,我们需要重新调试程序,直到达到预期效果为止。

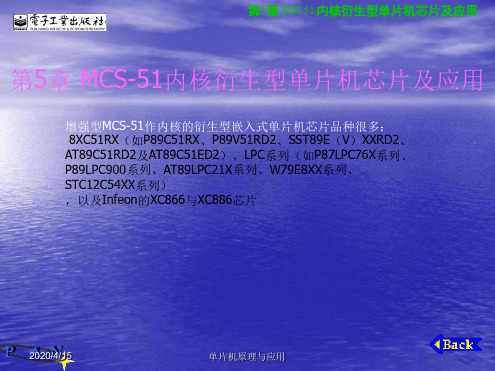

80C51内核衍生型单片机芯片及应用

通脉冲宽度为6时钟周期(与传统的MCS-51兼容),但在T89C51RX中,可以 选择30时钟周期,以便读写存取速度慢的外部RAM存储器。

P A N 2020/4/15

单片机原理与应用

第5章 80C51内核衍生型单片机芯片及应用

? ② 增加了时钟模式控制寄存器CKCON。即当FX2位处于擦除状态(未

编程,FX2位为1)时,可通过软件修改时钟控制寄存器CKCON的X2 位来选择系统时钟模式(但值得注意的是,位于Flash ROM保密字节 内的系统时钟配置位FX2比CKCON寄存器内的X2位优先,即当FX2位 被编程后,X2位无效)。

第5章 80C51内核衍生型单片机芯片及应用

1.Philips公司第一代P89C51RXXH系列芯片

① 采用增强型80C51内核,硬件资源、封装形式及引脚排列、指令系统与增强型MCS-51 芯片保持100%兼容,即P89C51RX系列完全可以替换具有相同封装形式的8XC5X、 8XC5XX2系列芯片。 ② 扩充了片内RAM存储器容量,在P89C51RX内部,除了256字节的内部RAM外,还集成 了256~768字节的内部扩展RAM(简称ERAM)。为此,在辅助功能寄存器AUXR中增加 了内部扩展RAM/外部RAM选择位EXTRAM。当EXTRAM位为0时,MOVX指令的读写对象为 内部扩展RAM;反之,当EXTRAM位为1时,MOVX指令的读写对象为外部RAM。 ③ 集成了与Intel P8XC51FX系列芯片完全兼容的可编程计数器阵列PCA模块。 ④ 可使用与 MCS-51相同的“12时钟/机器周期”模式(在标准时钟模式下,晶振频率为 0~33MHz),也可以采用“6时钟/机器周期”模式(晶振频率为0~20MHz,指令执行速 度快了一倍)。 ⑤ 内置了硬件看门狗计数器WDT。 ⑥ 具有7个中断源(4个中断优先级)。

CISC微处理器嵌入式内核的设计

’t imescal e 1ns/ 1ns module adder ( a, b, sum, carry) ; input a, b; out put sum , carry ;

buf gat e1( sum , sum—m id) , gat e2( carr y, car ry—mid) ; assig n sum—mid= a+ b; assig n carr y—m id= a&b; sp ecify ( a, b* > sum) = ( 10, 9, 8) ; ( a, b* > carry ) = ( 6, 5, 4) ; endspecif y

Key words : M icr opr ocesso r ; CISC; Embedded co r e; CPU ; M emo ry

EEACC: 1具 有可重用 性、可编 程的特点。比如, 用 M CU 内核、RF 内核和加密内核( 3DES, RSA) 可实 现无线加密 CP U 卡。本文设计了与 80C51 兼容的

微电 子学 Micr oelect roni cs

V ol. 33, № 4 Aug . 2003

低功耗异步80C51微处理器设计

低功耗异步80C51微处理器设计低电压是微处理器低功耗设计最有效的方法之一。

工艺参数波动对电路延时的影响随着电压的降低而增大,同步电路需要保留额外的时序余量来保证其功能正确,由此导致的性能下降成为低电压设计的瓶颈。

异步电路通过握手保证时序的正确性,虽然面积开销较大,但可以自适应工艺参数波动带来的影响,在低电压下具有高性能低功耗的特点,适合应用于低电压微处理器设计。

本文使用定制NCL(Null Convension Logic)单元与双轨数据编码设计了基于SMIC 40nm的低功耗异步80C51微处理器。

首先根据异步电路的结构,建立异步电路的延时和功耗模型,论证了异步电路低电压下相对同步电路性能和功耗上的优势。

通过不同类型的异步电路模型对比,确定了采用NCL逻辑异步电路的技术路线。

其次,异步80C51微处理器设计使用了全新的精简三级流水架构,简化了流水线结构,增加了组合逻辑的级数,降低了局部工艺参数波动对延时的影响,并降低了功耗。

在寄存器堆设计中,通过对寄存器堆中相同功能的寄存器进行合并,降低了寄存器堆的功耗。

采用分支电路优化的方法,对微处理器中电路中的冗余反馈逻辑进行了精简,降低了分支电路中寄存器的功耗。

运算单元采用了Wavefront steering技术优化了组合逻辑,提高了微处理器的能效。

最后使用静态逻辑设计了NCL单元库,优化了单元尺寸,并基于UNCLE工具完成异步80C51微处理器的综合。

搭建了异步电路仿真验证平台,以同步80C51为参照,对异步80C51的性能和功耗进行了对比。

在0.6V工作电压,异步80C51的能量延时积相对同步80C51有14.2%的提升。

最后验证了异步微处理器性能功耗随电压的变化,结果表明,在更低的电压下,异步80C51相对同步80C51在性能和功耗上都有着更加明显的优势。

80C51实验指导书

目录

第一章 初级软件实验部分…………………………………………………………………………1 实验一 二进制转换成十进制实验…………………………………………………………1 实验二 无符号数十进制加法实验…………………………………………………………3 实验三 数据传送实验………………………………………………………………………4 实验四 数据排序实验………………………………………………………………………5

MOV 31H,#DATA1 ;被加数送31H,30H

MOV 40H,#DATA2

MOV 41H,#DATA3 ;加数送41H,40H

MOV A,30H

ADD A,40H

;(30H)+(40H)→A

MOV 50H,A

;保存低位结果

MOV A,31H

ADDC A,41H

;(40H)+(50H)+CY→A

二、实验内容

编写并调试一个双字节无符号十进制数加法程序,其功能为将被加数写入30H、31H单元,

加数写入40H、41H单元,运行程序结果写入52H、51H、50H单元中,则加法程序功能为

(31H) (30H)+(41H) (40H)=(52H) (51H) (50H)(都是高位在前、低位在后)。

三、实验步骤

1

THGQC-1 型嵌入式·单片机实验开发系统――浙江天煌科技实业有限公司研制

第一章 初级软件实验部分

实验一 二进制转换成十进制实验

一、实验设备 1.THGQC-1型嵌入式单片机实验开发系统-套。 2.PC机一台。 注:其它实验与此相同,此项以后不再重述。

二、实验目的 掌握汇编语言设计和实验步骤,熟悉在KEIL环境下观察内部RAM 的方法。

2_80C51单片机的基本结构和工作原理

c. PSW.3、PSW.4(RS0、RS1,工作寄存器选择控制

位) 该两位通过软件置“0”或“1”来选择当前工作寄存器 组,具体定义见表2-1。

表2-1 工作寄存器组选择

RS1 0

0 1

RS0 0

1 0

所选中的寄存器组 寄存器0组(00H~07H)

寄存器1组(08H~0FH) 寄存器2组(10H~17H)

(1) 程序存储器

程序存储器内部结构参见图2-8,程序存储器就是 用来存放编好的程序和表格常数,它以程序计数器PC作 地址指针。由于80C51单片机采用16位的程序计数器和16 位的地址总线,因此,可寻址的地址空间为64 KB,且这 64K地址是片内外连续、统一的。

①片内程序存储器和片外程序存储器

2.2 80C51单片机内部结构 和引脚功能

2.2.1 80C51的内部结构

80C51单片机的内部结构如图2-2所示。它主要由以 下几个部分组成:1个8位的中央处理器;4KB的 EPROM/ROM;128B的RAM;32条I/O线;2个定时器/计 数器;1个具有5个中断源、2个优先级的中断嵌套结构; 用于多处理机通讯、I/O口扩展或全双工通用异步接收发 器(UART);特殊功能寄存器(SFR);1个片内振荡器 和时钟电路。这些部件通过内部总线连接起来,构成一个 完整的微型计算机。

①算术逻辑单元ALU

算术逻辑单元ALU的结构如图2-3所示。ALU功能 十分强大,不仅可以对8位变量进行逻辑“与”、“或”、 “异或”、循环求补、清零等基本操作,还可以进行加、 减、乘、除等基本运算,并具有数据传输、程序转移等功 能。为了乘除运算的需要,设置了B寄存器。

图2-3 ALU结构

②累加器ACC

外部振荡方式:把外部已有的时钟信号引入单片机 内。该方式适宜用来使单片机的时钟信号与外部信号保持 同步。外部振荡方式的外部电路如图2-6所示。

80C51原始IP核内部RAM的扩展方案

80C51原始IP核内部RAM的扩展方案引言80C51系列单片机是一类经典的8位微处理器,其设计方法和体系结构一直是其他各类单片机设计的参考典范,自从20世纪80年代面世以后,得到了极大的发展与应用。

直到今天,市场上还有一大部分单片机应用成品将其作为处理核心。

基于80C51系列单片机无知识产权保护、市场应用广泛等优点,对其进行功能拓展,既有利于经济上节约成本,也有利于成果的推广使用。

而随着单片机应用日趋复杂化,传统的51系列单片机在设计上的不足逐渐显现出来。

如在现有128字节内部RAM基础上,处理一些比较复杂的算法就显不足。

鉴于此,本文在Oregano公司设计的8051 IP核(即下述MC8051)基础上,进行了对其内部RAM高128字节扩展。

给出一种新的扩展设计方法,实现了对与一般RAM区地址空间相连的高128字节的间接寻址操作,并以此为基础,对内部RAM进行了可达64 KB的扩展实现,通过了相应的软硬件仿真测试。

1 对MC8051高位128字节的扩展设计对MC8051高位128字节的扩展设计主要分3个方面加以说明:一是传统80C51系列的内部基本结构;二是高128字节的寻址方式;三是对IP核内部的RAM地址选择控制。

1.1 传统80C51系列的内部基本结构80C51是经典的单片机系列,具有典型的单片机体系结构,由CPU系统、ROM、RAM、I/O口以及特殊功能寄存器SFR、2个16位定时/计数器、5个中断源和1个串口组成。

针对本文所要讨论的内容,这里介绍一下80C51存储结构和寻址方式:80C51系列单片机存储器结构采用哈佛型结构,物理上共分片内外程序存储器、片内外数据存储器4个存储空间。

对于数据存储器,片内外数据存储器地址彼此独立,指令寻址各自不同,这里主要关注片内数据存储单元的结构。

8051单片机共有7种寻址方式,这里只对其中3种作一下简要介绍:立即寻址,操作码后的一个字节就是实际操作数本身;寄存器寻址,操作码后为某一寄存器编号,寄存器的内容为操作数;寄存器间接寻址,其与寄存器寻址的区别在于前者寄存器中的内容就是操作数,而后者寄存器中的内容为操作数地址,此地址指向的寄存器中存入的数据才是实际操作数本身。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第30卷第1期2000年2月微电子学M icroelectron icsV o l 130,№1Feb 12000收稿日期:1999203215,定稿日期:1999205210文章编号:100423365(2000)012002820380C 51微处理器嵌入式内核的设计研究尚 笠,葛元庆,周润德,朱 宁,梁松海(清华大学 微电子学研究所,北京 100084)摘 要: 采用高层综合的方法设计出80C 51微处理器嵌入式内核,并在1.2Λm 工艺线上完成了投片实验,获得了满意的结果。

内核面积按照等效门计算为7600门规模。

关键词: 微处理器;嵌入式内核;专用集成电路;高层综合中图分类号: T P 312 文献标识码: A The D esign of a Genera l -Purpose Em bedded M icroprocessor CoreSHAN G L i ,GE Yuan 2qing ,ZHOU R un 2de ,ZHU N ing ,L I AN G Song 2hai(Institu te of M icroelectronics ,T sing hua U niversity ,B eij ing 100084)Abstract : A n em bedded m icrop rocesso r co re u sed fo r A S I C ′s is p resen ted ,w h ich is compatib le w ith 80C 51m i 2crop rocesso r .T he co re is designed by u sing h igh 2level syn thesis ,and fab ricated successfu lly in a 1.2Λm techno lo 2gy .T he area of the co re equals 7600gates.Key word : M icrop rocesso r ;A S I C ;Em bedded co re ;H igh 2level syn thesisEEACC : 1265F1 引 言随着A S I C 的发展,面向用户和设计周期短的特点体现得越来越突出。

用户的特定应用不但具有特殊性,同时又具有一定的共性。

设计实现功能通用的模块,针对特定A S I C 的应用,嵌入于不同的集成电路中,与特定的外围电路形成功能系统A S I C ,可以大大简化设计难度、缩短设计周期、降低设计成本。

从本质上讲,这是“设计复用”(D esign 2R eu se )的设计思想。

而今,通用的功能模块已发展为具有知识产权的IP 模块。

IP 模块一般采用V HDL 或V er 2ilog 语言描述、网表描述(N etlist )和版图描述(L ay 2ou t )三种形式。

其中,采用V HDL 或V erilog 描述相当于“软”内核(Soft Co re ),由于其与工艺无关,故应用最灵活。

而版图描述由于受限于特定的工艺与设计规则,其灵活性最小,但版图设计最优。

嵌入式内核从功能上划分包括微处理器内核、D SP 内核、R F 内核等,其本质特点是可重用性,通常具有可编程性,因此需要软硬件的协同设计。

例如,采用Con tro ller内核、R F 内核、加密内核(D ES ,R SA )或D SP 内核即可实现无线加密CPU 卡,如图1所示。

图1 无线加密CPU 卡结构 正是由于嵌入式内核的引入,使设计者可以着眼于更高的层次上,即用户系统的层次上,进行设计。

2 嵌入式内核的结构确定与划分嵌入式内核的特点在于设计复用,设计者一般提供“黑盒子”,同时,必须提供标准的使用接口。

友好的接口界面是嵌入式内核的关键。

而嵌入式微处理器则要求具有指令集的通用性、时序特性、电气特性以及接口的标准化。

为适应嵌入式内核本身的特性与采用的V HDL 语言工具的描述风格,在满足逻辑功能与时序要求的前提下,考虑面积与功耗的优化,对系统结构进行划分。

这样可以均衡各模块的面积规模,减少模块数量,降低面积代价,并优化延时特性与功耗特性。

一个数字系统从系统结构上可划分为控制器(Con tro ller )和算术逻辑单元(ALU ),其数据流向是从寄存器或输入端口通过系统资源再回到寄存器或输出端口。

针对80C 51的特点,考虑以上面积、时序等诸多因素,嵌入式微处理器内核系统结构可分为控制器、算术逻辑单元、外围模块3部分,通过控制器对其他模块数据流向实现控制,如图2所示。

电路方框图如图3所示。

图2 嵌入式内核的结构确定与划分图3 80C 51电路方框图 从图3可以看出,电路主要由以下几部分组成:1)Con tro ller 模块:控制器的输入为8位指令码与4位指令状态位组合,通过控制BU S I N 、BU 2SOU T 模块的译码选通,控制数据从寄存器及输入端口到ALU 、寄存器和输出端口,从而实现程序控制功能。

2)BU S I N 、BU SOU T 模块:为输入输出译码控制,接受Con tro ller 控制译码而控制ALU 输入输出数据流向。

3)ALU 模块:算述逻辑单元,可实现算术、逻辑操作以及位操作。

4)Po rt 1~4模块:双向端口,可作为地址数据双向端口及通用I O 端口。

5)T i m er 模块:包含2个定时器和计数器,有4种工作模式,与80C 51兼容。

)信接口,既可作为通用异步接收和发送器,也可作为同步移位寄存器,与80C 51兼容。

7)R egisters 模块:寄存器组,包括80C 51中所有寄存器。

由于这一内核采用自顶至下的模块化设计,基于结构特性和逻辑功能的模块划分,并考虑到模块间面积实现的均衡和模块间时钟电路的同步信息交换,因此所设计的内核具有优化的面积、时间特性与可测性。

3 内核设计考虑在内核的设计中,着重考虑了描述语言、模块同步化、系统复位、功耗和时钟策略等方面。

311 内核结构的V HDL 描述采用V HDL 语言描述有诸多优点,但使用时需注意与一般编程语言的区别。

描述需面向综合,这包括两方面:第一,采用模块化规则的语言结构,语言要面向硬件映射,不但需保证可综合性,同时还应考虑到代码映射到硬件的相应规模。

在模块描述中,要把握好时序电路与组合电路的区别,控制硬件规模;第二,从行为级到R TL 寄存器传输级,实质为从系统行为描述到硬件的逐渐具体的映射,应在R TL 级估算最终电路实现的大致规模,包括从系统划分开始到单元选择、时钟周期选择、算子调度、分配、联线网络及控制码生成,以便有效地保证最终电路规模。

312 功能模块的同步设计如前所述,一个系统或系统内部模块数据流向应保证从寄存器的输出端或系统输入端到资源再到寄存器的输入端或系统输出端,即保证从时序单元到组合单元再到时序单元。

这样不但保证面积综合有更好的优化结果,同时保证一个同步系统的实现。

同步系统的优点在于其可靠性。

与之相反,一个异步电路的两输入与门即可导致毛刺的出现,如图4所示。

图4 异步电路及其时序 图中,当A 输入端信号从‘1’变为‘0’、B 输入端信号从‘0’变为‘1’时,若B 信号的变化提前于A 信号,则输出端出现假信号;若A 、B 输入端‘1’与‘0’信号出现概率相同,而与A 、B 之间翻转次序无关,则必然导致假信号现象的随机发生。

这不但增大了功耗,同时,有可能导致后级电路的错误翻转。

所以在设计电路时必须保证:第一,系统输出数据端必须采用时钟同步输出,以防止假信号的产生;第二,系统内部各个模块之间数据输入输出采用时钟同步,以防止上级模块输出导致下级模块的误操作;第三,系统输入数据端用时钟对输入数据进行采样,以保证输入数据的正确性;第四,系统有限状态机编码采用4位循环码,以保证在状态转换时只有一位码字的翻转,防止由于多位码同时翻转造成的瞬时误码。

313 系统复位的实现为使系统加电正确复位,以及防止由于R ST 端输入信号抖动影响造成的误复位,采用时钟在特定内部状态下对外部复位信号进行采样。

在连续两个机器周期采样到有效复位信号时,内部电路进入复位状态。

而复位端由于外部电路干扰导致的抖动则由于其有效宽度达不到系统复位的要求,不会导致系统误复位。

314 低功耗设计C M O S 电路的系统功耗可表示为: P avg =P s w.cap.+P sho rt-circuit +P leakage +P static式中,P avg 为平均功耗,P s w.cap 为电路切换电容消耗的功耗,P sho rt-circuit 为短路电路功耗,P leakage 为漏电功耗,P static 为静态功耗。

P s w.cap 和P sho rt-circuit 是功耗的主要部分,它们都与电路切换率成正比。

为此,在设计电路中应采用功耗管理的方法降低功耗。

31411 门控时钟树采用多级门控时钟达到优化功耗的目的,如图5所示。

图5 门控多级时钟树结构31412 预处理如果对一个复杂的控制组合电路网络的任何输入都进行响应,将产生大量功耗。

为此,对特定输入可附加针对相应输入子集的译码电路,以防止整个控制组合电路网络的无效翻转,从而降低了整体功耗。

31413 模块隔离使不同模块在各自的Idle 状态时锁死输入时钟,即通过合理划分系统层次和模块控制依赖关系来防止无效翻转,达到降低功耗的目的。

31414 高层综合从时钟周期选择、资源选择、调度、资源复用和联线控制网络过程中考虑功耗优化。

315 时钟策略采用单时钟沿触发,以提高系统工作频率。

4 设计验证与结论对控制器采用功能验证包括单条指令验证、中断及其他外围电路验证和编写复杂测试程序附加随机中断验证,系统验证分为行为级(R TL 级)仿真验证、门级仿真验证和采用A ltera 的FPGA 进行硬件电路验证三个过程,结果表明达到了设计要求。

最后采用1.2Λm 工艺投片测试,证明了设计的正确性。

内核面积规模为7600等效门,工作时钟频率超过10M H z 。

本文介绍了面向A S I C 应用与80C 51兼容的嵌入式内核的设计。

该内核采用1.2Λm 标准单元库进行综合,面积规模为7600等效门,并进行了投片测试验证,时钟频率超过10M H z 。

在设计过程中采用高层综合等设计方法,在满足时间特性的前提下,有效地降低了面积与系统功耗。

它可以作为嵌入式内核应用于A S I C 中,特别是非接触式CPU 卡等对功耗要求苛刻的特定应用中。

[参考文献][1]Chandrakasan A P ,B rodersen R W .L ow pow er digital C M O S design [M ].K luw er A cadem ic Pub lishers ,1995.[2]P iguet C ,M asgon ty J M .L ow 2pow er design of 82b em bedded coo lrisc m icrocon tro ller co res [J ].IEEE JSo lid 2State C ircu its ,1997;(32)7:1067~1077.[3]M icheli G D .Compu ter 2aided hardw are 2softw are code 2sign [J ].IEEE M icro ,1994;14(4):10~16.[4]Ch i odo M ,Giu sto P .H ardw are 2softw are codesign ofem bedded system s [J ].IEEE M icro ,1994;14(4):26~36.作者简介: 尚 笠 (197411~ )男,1997年毕业于清华大学电子工程系,获学士学位;1999年7月在清华大学微电子学研究所毕业,获硕士学位。