EP1C6Q144I6中文资料

EPI561321G4036L中文资料

Part Number

EPI1L0342B20 EPI4L7122B20 EPI6L8951B20 EPI100801B20 EPI150701B20 EPI220601B20 EPI330441B20 EPI470371B20 EPI680321B20 EPI101261B20 EPI151211B20 EPI221181B20

WH

.330 .270 .440 .360 .430 .360 .500 .215 .215 .500 .560 .350 .615 .370 .610 .390 .650 .400 .715 .390 .700 .390 .940 .390 1.00 .390 1.00 .500 .640 .315 .195 .118 .195 .079 .224 .118 .264 .157 .264 .118 .287 .177 .287 .138 .394 .150 .472 .315 .472 .236 .472 .177 .157 .126 .354 .213 .354 .157 .460 .235 .460 .165 .560 .250

---

54

---

40

---

34

---

35

---

40

42

---

38

---

34

---

37

---

37

---

37

---

40

---

Package B20

.330 (8.83)

PCA EPIXXXXXXB20

D.C.

.330 (8.38)

.060 (1.52)

.300 (7.62)

Suggested Pad Latout

CDRH64NP-1OOMB中文资料

仕 様 書形 名CDRH641.外形1-1.寸法図(mm)1-2.捺印表示例 1-3.推奨ランド寸法 (mm)2.コイル仕様 2-1.端子接続図(裏面図)電極(端子)間の隙間はシルク処理をして御使用下さい。

頭部直捺印捺印位置不定compliance Cd:Max.0.01wt%others:Max.0.1wt%RoHS1仕 様 書 形 名CDRH642-2.電気的特性Ⅰ(リール の場合)NO. 品 名 表示 インダクタンス[以内]※1D.C.R.(Ω)[以下](at 20℃)※2定格電流(A)※3スミダコード0102 CDRH64NP-1ØØMCCDRH64NP-12ØMC10012010 μH ± 20%12 μH ± 20%0.11(84m)0.13(96m)1.681.514732-00134732-00150304 CDRH64NP-15ØMCCDRH64NP-18ØMC15018015 μH ± 20%18 μH ± 20%0.14(0.11)0.16(0.12)1.321.184732-00164732-00170506 CDRH64NP-22ØMCCDRH64NP-27ØMC22027022 μH ± 20%27 μH ± 20%0.21(0.16)0.29(0.23)1.060.954732-00184732-00190708 CDRH64NP-33ØMCCDRH64NP-39ØMC33039033 μH ± 20%39 μH ± 20%0.33(0.25)0.35(0.27)0.880.774732-00204732-00210910 CDRH64NP-47ØMCCDRH64NP-56ØMC47056047 μH ± 20%56 μH ± 20%0.39(0.30)0.43(0.34)0.760.674732-00224732-00231112 CDRH64NP-68ØMCCDRH64NP-82ØMC68082068 μH ± 20%82 μH ± 20%0.59(0.46)0.66(0.51)0.600.574732-00244732-00261314 CDRH64NP-1Ø1MCCDRH64NP-121MC101121100μH ± 20%120μH ± 20%0.76(0.58)0.83(0.64)0.500.474732-00274732-00281516 CDRH64NP-151MCCDRH64NP-181MC151181150μH ± 20%180μH ± 20%1.24(0.96)1.89(1.51)0.420.374732-00294732-00301718 CDRH64NP-221MCCDRH64NP-271MC221271220μH ± 20%270μH ± 20%2.10(1.68)2.37(1.90)0.340.314732-00314732-00321920 CDRH64NP-331MCCDRH64NP-391MC331391330μH ± 20%390μH ± 20%2.66(2.13)2.94(2.35)0.270.264732-00334732-00342122 CDRH64NP-471MCCDRH64NP-561MC471561470μH ± 20%560μH ± 20%3.89(3.11)5.25(4.20)0.240.214732-00354732-00372324 CDRH64NP-681MCCDRH64NP-821MC681821680μH ± 20%820μH ± 20%5.97(4.78)6.54(5.23)0.180.174732-00384732-003925 CDRH64NP-1Ø2MC 102 1.0 mH ± 20% 8.94(7.15) 0.16 4732-0040※1: 測定周波数 L at 1 kHz※2: ( )内は、標準値とする。

ep1c3t144

B1VREF0B1IO LVDS4p INIT_DONE1DM1L B1VREF0B1IO LVDS4n CRC_ERROR2DQ1L0 B1VREF0B1IO LVDS3p CLKUSR3DQ1L1 B1VREF0B1IO LVDS3n4B1VREF0B1IO VREF0B15B1VREF0B1IO LVDS2p6DQ1L2 B1VREF0B1IO LVDS2n7DQ1L3 B1VREF0B1VCCIO18B1VREF0B1GND9B1VREF0B1IO DPCLK110DQS0L B1VREF1B1IO VREF1B111B1VREF1B1IO nCSO12B1VREF1B1DATA0DATA013B1VREF1B1nCONFIG nCONFIG14VREF1B1VCCA_PLL115B1VREF1B1CLK0LVDSCLK1p16B1VREF1B1CLK1LVDSCLK1n17VREF1B1GNDA_PLL118VREF1B1GNDG_PLL119B1VREF1B1nCEO nCEO20B1VREF1B1nCE nCE21B1VREF1B1MSEL0MSEL022B1VREF1B1MSEL1MSEL123B1VREF1B1DCLK DCLK24B1VREF1B1IO ASDO25B1VREF1B1IO PLL1_OUTp26B1VREF1B1IO PLL1_OUTn27B1VREF2B1IO DPCLK028DQS1L B1VREF2B1VCCIO129B1VREF2B1GND30B1VREF2B1IO VREF2B131B1VREF2B1IO32DQ1L4 B1VREF2B1IO LVDS1p33DQ1L5 B1VREF2B1IO LVDS1n34DQ1L6 B1VREF2B1IO LVDS0p35DQ1L7 B1VREF2B1IO LVDS0n36B4VREF2B4IO LVDS33p37B4VREF2B4IO LVDS33n38B4VREF2B4IO LVDS32p39DQ1B7 B4VREF2B4IO LVDS32n40DQ1B6 B4VREF2B4IO LVDS31p41DQ1B5 B4VREF2B4IO LVDS31n42DQ1B4 B4VREF2B4GND43B4VREF2B4VCCIO444VREF2B4GND45VREF2B4VCCINT46B4VREF2B4IO DPCLK747DQS1B B4VREF2B4IO VREF2B448B4VREF2B4IO49B4VREF2B4IO LVDS30p50B4VREF2B4IO LVDS30n51B4VREF1B4IO LVDS29p52B4VREF1B4IO LVDS29n53B4VREF1B4IO LVDS28p54B4VREF1B4IO LVDS28n55B4VREF1B4IO VREF1B456B4VREF1B4IO LVDS27p57DM1B B4VREF1B4IO LVDS27n58B4VREF1B4IO LVDS26p59B4VREF0B4IO LVDS26n60B4VREF0B4IO VREF0B461B4VREF0B4IO DPCLK662DQS0B VREF0B4GND63VREF0B4VCCINT64B4VREF0B4GND65B4VREF0B4VCCIO466B4VREF0B4IO LVDS25p67DQ1B3 B4VREF0B4IO LVDS25n68DQ1B2 B4VREF0B4IO LVDS24p69DQ1B1 B4VREF0B4IO LVDS24n70DQ1B0 B4VREF0B4IO LVDS23p71B4VREF0B4IO LVDS23n72B3VREF2B3IO LVDS22n73B3VREF2B3IO LVDS22p74B3VREF2B3IO LVDS21n75B3VREF2B3IO LVDS21p76B3VREF2B3IO LVDS20n77DQ1R7 B3VREF2B3IO LVDS20p78DQ1R6 B3VREF2B3IO VREF2B379B3VREF2B3GND80B3VREF2B3VCCIO381B3VREF2B3IO DPCLK582DQS1R B3VREF2B3IO LVDS19n83DQ1R5 B3VREF2B3IO LVDS19p84DQ1R4 B3VREF2B3IO85DM1R B3VREF1B3CONF_DONE CONF_DONE86B3VREF1B3nSTATUS nSTATUS87B3VREF1B3TCK TCK88B3VREF1B3TMS TMS89B3VREF1B3TDO TDO90B3VREF1B3IO91B3VREF1B3CLK3LVDSCLK2n92B3VREF1B3CLK2LVDSCLK2p93B3VREF1B3IO94B3VREF1B3TDI TDI95B3VREF1B3IO VREF1B396B3VREF0B3IO97DQ1R3 B3VREF0B3IO LVDS18n98DQ1R2 B3VREF0B3IO LVDS18p99DQ1R1 B3VREF0B3IO DPCLK4100DQS0R B3VREF0B3GND101B3VREF0B3VCCIO3102B3VREF0B3IO103DQ1R0 B3VREF0B3IO VREF0B3104B3VREF0B3IO LVDS17n105B3VREF0B3IO LVDS17p106B3VREF0B3IO LVDS16n107B3VREF0B3IO LVDS16p108B2VREF0B2IO LVDS15n109B2VREF0B2IO LVDS15p110B2VREF0B2IO LVDS14n111DQ0T0 B2VREF0B2IO LVDS14p112DQ0T1B2VREF0B2IO LVDS13n113DQ0T2 B2VREF0B2IO LVDS13p114DQ0T3 B2VREF0B2VCCIO2115B2VREF0B2GND116VREF0B2VCCINT117VREF0B2GND118B2VREF0B2IO DPCLK3119DQS0T B2VREF0B2IO VREF0B2120B2VREF0B2IO LVDS12n121B2VREF1B2IO LVDS12p122B2VREF1B2IO LVDS11n123DM0T B2VREF1B2IO LVDS11p124B2VREF1B2IO VREF1B2125B2VREF1B2IO LVDS10n126B2VREF1B2IO LVDS10p127B2VREF1B2IO LVDS9n128B2VREF1B2IO LVDS9p129B2VREF2B2IO LVDS8n130B2VREF2B2IO LVDS8p131B2VREF2B2IO132B2VREF2B2IO VREF2B2133B2VREF2B2IO DPCLK2134DQS1T VREF2B2VCCINT135VREF2B2GND136B2VREF2B2VCCIO2137B2VREF2B2GND138B2VREF2B2IO LVDS7n139DQ0T4 B2VREF2B2IO LVDS7p140DQ0T5 B2VREF2B2IO LVDS6n141DQ0T6 B2VREF2B2IO LVDS6p142DQ0T7 B2VREF2B2IO LVDS5n DEV_OE143B2VREF2B2IO LVDS5p DEV_CLRn144VCCIO[1..4]Power These are I/O supply voltage pins for banks 1 through 4. Each bank can support a different voltage level. VCCIO supplies power to the output buffers for all I/O standards. VCCIO also supplies power to the input buffers used for the LVTTL, LVCMOS, 1.5-V, 1.8-V, 2.5-V, and 3.3-V PCI I/O standards.VCCINT Power These are internal logic array voltage supply pins. VCCINT also supplies power to the input buffers used for the LVDS, SSTL2, and SSTL3 I/O standards.GND Ground Device ground pins. All GND pins should be connected to the board GND plane.VREF[0..2]B[1..4]I/O, Input Input reference voltage for banks 1-4. If a bank uses a voltage-referenced I/O standard, then these pins are used as the voltage-reference pins for the bank. If voltage reference I/O standards are not used in the bank, the VREF pins are available as user I/O pins.VCCA_PLL[1..2]Power Analog power for PLLs[1..2]. The designer must connect this pin to 1.5 V, even if the PLL is not used. GNDA_PLL[1..2]Ground Analog ground for PLLs[1..2]. The designer can connect this pin to the GND plane on the board. GNDG_PLL[1..2]Ground Guard ring ground for PLLs[1..2]. The designer can connect this pin to the GND plane on the board. NC No Connect No connect pins should not be connected on the board. They should be left floating.CONF_DONE Bidirectional (open-drain)This is a dedicated configuration status pin; it is not available as a user I/O pin.nSTATUS Bidirectional (open-drain)This is a dedicated configuration status pin; it is not available as a user I/O pin.nCONFIG Input Dedicated configuration control input. A low transition resets the target device; a low-to-high transition begins configuration. All I/O pins tri-state when nCONFIG is driven low.DCLK Input (PS mode), Output(AS mode)In passive serial configuration mode, DCLK is a clock input used to clock configuration data from an externalsource into the Cyclone device. In active serial configuration mode, DCLK is a clock output from the Cyclonedevice (the Cyclone device acts as master in this mode). This is a dedicated pin used for configuration.DATA0Input Dedicated configuration data input pin.nCE Input Active-low chip enable. Dedicated chip enable input used to detect which device is active in a chain of devices. When nCE is low, the device is enabled. When nCE is high, the device is disabled.nCEO Output Output that drives low when device configuration is complete. During multi-device configuration, this pin feeds a subsequent device’s nCE pin.ASDO I/O, Output Active serial data output from the Cyclone device. This output pin is utilized during active serial configuration mode. The Cyclone device controls configuration and drives address and control information out on ASDO. In passive serial configuration, this pin is available as a user I/O pin.nCSO I/O, Output Chip select output that enables/disables a serial configuration device. This output is utilized during active serial configuration mode. The Cyclone device controls configuration and enables the serial configuration device by driving nCSO low. In passive serial configuration, this pin is available as a user I/O pin.CRC_ERROR I/O, Output Active high signal that indicates that the error detection circuit has detected errors in the configuration SRAM bits. This pin is optional and is used when the CRC error detection circuit is enabled.INIT_DONE I/O, Output (open-drain)This is a dual-purpose pin and can be used as an I/O pin when not enabled as INIT_DONE. When enabled, the pin indicates when the device has entered user mode. This pin can be used as a user I/O pin after configuration.CLKUSR I/O, Input Optional user-supplied clock input. Synchronizes the initialization of one or more devices. This pin can be used as a user I/O pin after configuration.DEV_CLRn I/O, Input Dual-purpose pin that can override all clears on all device registers. When this pin is driven low, all registers are cleared; when this pin is driven high, all registers behave as defined in the design.DEV_OE I/O, Input Dual-purpose pin that can override all tri-states on the device. When this pin is driven low, all I/O pins are tri-stated; when this pin is driven high, all I/O pins behave as defined in the design.MSEL[1..0]Input Dedicated mode select control pins that set the configuration mode for the device. TMS Input This is a dedicated JTAG input pin.TDI Input This is a dedicated JTAG input pin.TCK Input This is a dedicated JTAG input pin.TDO Output This is a dedicated JTAG output pin.CLK0Input, LVDS Input Dedicated global clock input. The dual-function of CLK0 is LVDSCLK1p, which is used for differential input to PLL1.CLK1Input, LVDS Input Dedicated global clock input. The dual-function of CLK1 is LVDSCLK1n, which is used for differential input to PLL1. The EP1C3T100 does not support this clock pin.CLK2Input, LVDS Input Dedicated global clock input. The dual-function of CLK2 is LVDSCLK2p, which is used for differential input to PLL2.Clock and PLL PinsSupply and Reference PinsConfiguration and JTAG PinsCLK3Input, LVDS Input Dedicated global clock input. The dual-function of CLK3 is LVDSCLK2n, which is used for differential input to PLL2. The EP1C3T100 does not support this clock pin.DPCLK[7..0]I/O Dual-purpose clock pins that can connect to the global clock network. These pins can be used for high fan-out control signals, such as clocks, clears, IRDY, TRDY, or DQS signals. These pins are also available as user I/O pins.PLL1_OUTp I/O, Output External clock output from PLL 1. This pin can be used with differential or single ended I/O standards. If clock output from PLL1 is not used, this pin is available as a user I/O pin. The EP1C3T100 does not support this output pin.PLL1_OUTn I/O, Output Negative terminal for external clock output from PLL1. If the clock output is single ended, this pin is available as a user I/O pin. The EP1C3T100 does not support this output pin.LVDS[0..33]p I/O, LVDS RX or TX Dual-purpose LVDS I/O channels 0 to 33. These channels can be used for receiving or transmitting LVDS compatible signals. Pins with a "p" suffix carry the positive signal for the differential channel. If not used for LVDS interfacing, these pins are available as user I/O pins. The EP1C3T100 does not support LVDS I/O interfacing.LVDS[0..33]n I/O, LVDS RX or TX Dual-purpose LVDS I/O channels 0 to 33. These channels can be used for receiving or transmitting LVDS compatible signals. Pins with an "n" suffix carry the negative signal for the differential channel. If not used for LVDS interfacing, these pins are available as user I/O pins. The EP1C3T100 does not support LVDS I/O interfacing.LVDSCLK1p Input, LVDS Input Dual-purpose LVDS clock input to PLL1. If differential input to PLL1 is not required, this pin is available as the CLK0 input pin.LVDSCLK1n Input, LVDS Input Dual-purpose LVDS clock input to PLL1. If differential input to PLL1 is not required, this pin is available as the CLK1 input pin. The EP1C3T100 does not support this clock pinLVDSCLK2p Input, LVDS Input Dual-purpose LVDS clock input to PLL2. If differential input to PLL2 is not required, this pin is available as the CLK2 input pin.LVDSCLK2n Input, LVDS Input Dual-purpose LVDS clock input to PLL2. If differential input to PLL2 is not required, this pin is available as the CLK3 input pin. The EP1C3T100 does not support this clock pin.DQS[0..1][L,R,T,B]I/O Optional data strobe signal for use in external memory interfacing. These pins also function as DPCLK pins; therefore, the DQS signals can connect to the global clock network. A programmable delay chain is used to shift the DQS signals by 90 or 72 degreesDQ[0..7][L,R,T,B]I/O Optional data signal for use in external memory interfacing.DM[0..1][L,R,T,B]I/O Optional data mask output signal for use in external memory interfacing.Dual-Purpose LVDS & External Memory Interface PinsPin Information for the Cyclone™ EP1C3T144 Device, ver 1.4VREF2B2VREF1B2VREF0B2B2V R E F 0B 1B 1B 3V R E F 0B 3V R E F 1B 1V R E F 1B 3PLL1V R E B 2B 1V R E B 2B 3B4VREF2B4VREF1B4VREF0B4Notes:1.This is a top view of the silicon die.2.This is a pictoral representation only to get an idea of placement on the device. Refer to the pin-list andthe Quartus II for exact locations.Version 1.4 Version Number Date Changes Made1.43/6/2006Added CRC_ERROR pin in Pin List and Pin Definitions。

EP1-3G2S中文资料

DESCRIPTIONThe NEC TOKIN EP2 / EP1 series are PC-board mount type automotive relays suitable for various motorcontrols and other applications that require a high level of quality and performance.EP2 series is a twin-relay and divided into two types for different usage.One is an H-bridge type designed for forward and reverse control of the motors, and the other, a separatetype containing two separated relays in one package.EP1 series is a 1 Form c relay equivalent to EP2 series in performance.FEATURESFor motor reversible control and solenoid controlApprox. 50% less relay space than conventional relayHigh performance and productivity by unique structureFlux tight housingAPPLICATIONSPower windowAntenna lifterAuto-seat positioningElectrical door lockPassive seat belt controlKeyless/Remote entry systemSliding roof controlThe information in this document is subject to change without notice.Date Published August 2002 MPrinted in Japan© NEC TOKIN Corporation 2002EP2 / EP1 SERIES2SCHEMATIC (BOTTOM VIEW)EP2 SERIESEP1 SERIESDIMENSIONS mm (inch)EP2 SERIESEP2/EP1 SERIES3EP1 SERIESPCB PAD LAYOUT mm (inch) (BOTTOM VIEW)EP2 SERIESEP1 SERIESEP2 / EP1 SERIES4SPECIFICATIONSat 25°C (77°F )Items EP2 EP1Contact Form1 Form c ×2 (H bridge type and separatetype)1 Form c Contact Material Silver oxide complex alloy(special type available) Contact Resistance 50 m Ω max. (measured at 7 A) initial Contact Switching Voltage 16 Vdc max. Contact Switching Current 25 A max. (at 16 Vdc) Contact Carrying Current 20 A max. (1 hour max.),25 A max. (2 minutes max.) at 12 Vdc25 A max. (1 hour max.),30 A max. (2 minutes max.) at 12 VdcOperate Time Approx. 5 ms (at 12 Vdc) initialRelease TimeApprox. 2 ms (at 12 Vdc) initial. without diode Normal Operate Power 0.48 W / 0.64 W (at 12 Vdc) Insulation Resistance 100 M Ω min. (at 500 Vdc) initial Breakdown Voltage 500 Vdc min. (for 1 minute) initialShock Resistance 98 m / s 2[10 G] min. (misoperating), 980 m / s 2[100 G] min. (destructive failure)Vibration Resistance10 to 300 Hz, 43 m/s 2[ 4.4 G] min. (misoperating)10 to 500 Hz, 43 m/s 2, [ 4.4 G] 200 hours (destructive failure) Ambient Temperature –40 °C to +85 °C (–40 °F to +185 °F)Coil Temperature50 °C / W (122 °F/W)(contact carrying current 0 A)Mechanical1 × 106operationsLife ExpectancyElectrical100 x 103operations (at 14 Vdc. Motor Load 20 A / 3 A) WeightApprox. 15 gn (0.53oz) Approx. 8 gr (0.28 oz)COIL RATINGEP2 SERIESat 25°C (77°F ) Part Number H Bridge Type Separate Type Nominal Voltage (Vdc) Coil Resistance (Ω±10%)Nominal Current (mA) Must Operate Voltage (Vdc max.)Must Release Voltage (Vdc min.)Nominal Operate Power (W) EP2-3L1 EP2-3L2 EP2-3L3 EP2-4L3 EP2-4L4 EP2-4L5EP2-3L1T EP2-3L2T EP2-3L3T EP2-4L3T EP2-4L4T EP2-4L5T12 12 12 12 12 12225 225 225 300 300 30053.5 53.5 53.5 40.0 40.0 40.06.57.0 7.5 7.58.0 8.50.9 0.9 0.9 0.9 0.9 0.90.64 0.64 0.64 0.48 0.48 0.48EP1 SERIESPart NumberRegularTypeHigh Carrying Current Type Nominal Voltage (Vdc) Coil Resistance (Ω±10%)Nominal Current (mA) Must Operate Voltage (Vdc max.)Must Release Voltage (Vdc min.)Nominal Operate Power (W) EP1-3L1EP1-3L2EP1-3L3EP1-4L3EP1-4L4EP1-4L5EP1-B3G1 EP1-B3G2 EP1-B3G3 EP1-B4G3 EP1-B4G4 EP1-B4G5 12 12 12 12 12 12225 225 225 300 300 30053.3 53.3 53.3 40.0 40.0 40.06.57.0 7.5 7.58.0 8.50.9 0.9 0.9 0.9 0.9 0.90.64 0.64 0.64 0.48 0.48 0.48EP2/EP1 SERIES5NUMBERING SYSTEMTYPICAL APPLICATION (H Bridge Type)MOTOR Tr1Tr2 STOP off off FORWARD on off REVERSE off onIt is necessary to take more than 100 ms intervals for on / off timing between driving Tr1 and Tr2. If the interval is less than 100 ms, an excessive current happen to flow to the relay contacts.EP2 / EP1 SERIES6TECHNICAL DATACoil Temperature Rise (EP2-3L1)Operate Time (EP2-3L1) Release time (EP2-3L1)EP2/EP1 SERIES7EP2 / EP1 SERIESPrinted on recycled paper。

FPGA可编程逻辑器件芯片EP1C6T144I7N中文规格书

SPI-Compatible Port Controllers3.The core writes to the SPIx_BAUD and SPIx_CTL registers, enablingthe device as a master and configuring the SPI system by specifyingthe appropriate word length, transfer format, baud rate, and othernecessary information.4.If CPHA = 1, the core activates the desired slaves by clearing one ormore of the SPI flag bits (FLGx) of SPIx_FLG.5.The TIMOD bits in SPIx_CTL determine the SPI transfer initiatemode. The transfer on the SPI link begins upon either a data writeby the core to the transmit data buffer(SPIx_TDBR) or a data readof the receive data buffer (SPIx_RDBR).6.The SPI then generates the programmed clock pulses on SPIxSCKand simultaneously shifts data out of SPIx MOSI and shifts data infrom SPIxMISO. Before a shift, the shift register is loaded with thecontents of the SPIx_TDBR register. At the end of the transfer, thecontents of the shift register are loaded into SPIx_RDBR.7.With each new transfer initiate command, the SPI continues tosend and receive words, according to the SPI transfer initiate mode.See Figure22-8 on page22-39 for additional information.If the transmit buffer remains empty or the receive buffer remains full, thedevice operates according to the states of the SZ and GM bits in SPIx_CTL. If SZ = 1 and the transmit buffer is empty, the device repeatedly transmits 0s on the SPIxMOSI pin. One word is transmitted for each new transfer initi-ate command. If SZ = 0 and the transmit buffer is empty, the devicerepeatedly transmits the last word it transmitted before the transmit buffer became empty. If GM = 1 and the receive buffer is full, the device continues to receive new data from the SPIxMISO pin, overwriting the older data in the SPIx_RDBR buffer. If GM = 0 and the receive buffer is full, the incoming data is discarded, and SPIx_RDBR is not updated.ADSP-BF54x Blackfin Processor Hardware ReferenceSPI-Compatible Port ControllersFigure 22-7. SPI Transfer Protocol for CPHA=1SPI General OperationEach SPI can be used in a single master as well as multimaster environ-ment. The SPIxMOSI, SPIxMISO, and the SPIxSCK signals are all tiedtogether in both configurations. SPI transmission and reception are always enabled simultaneously, unless the broadcast mode is selected. In broad-cast mode, several slaves can be enabled to receive, but only one of the slaves must be in transmit mode driving the SPIxMISO line. If the transmit or receive is not needed, it can simply be ignored. This section describes the clock signals, SPI operation as a master and as a slave, and errorgeneration.Precautions must be taken to avoid data corruption when changing the SPI module configuration. The configuration must not be changed duringa data transfer. The clock polarity should only be changed when no slavesare selected. An exception to this is when an SPI communication link con-sists of a single master and a single slave, CPHA = 1, and the slave select input of the slave is always tied low. In this case, the slave is alwaysselected and data corruption can be avoided by enabling the slave only after both the master and slave devices are configured.ADSP-BF54x Blackfin Processor Hardware Reference。

NFE61PTxxx资料

For High Speed Signal

For Standard (Low DC

Resistance Type)

For Standard

0603

For High Speed Signal (Sharp impedance characteristics)

* Please see P.58 "Derating of Rated Current".

60 (0.5A) 60 (3A)

50 (3A)

60 (6A)

33 (3A) 30 (1A)

30 (3A)

33 (6A)

22 22

10 10 10

10 10

555

mm 0603 1005 1608 2012 1005 1608 2012 1608 2012

EIA Code 0201 0402 0603 0805 0402 0603 0805 0603 0805

47 47

1800

1000 (1.5A) 1000

1000

1

600 (1.5A)

600

600

470 (2A)

470

390 (2A)

390

330 (1.5A)

330

220 (2A)

220

220

180 (1.5A)

180 (3A)

120 (2A)

120 (3A)

120

120

100

80 (1A)

75 (3A)

4516 1806

1005

1608

0402

0603

GHz Range Noise GHz Range Noise Suppression Type Suppression Type BLM15H/E BLM18H/E/G

EPX 系列电子开关说明书

COIL VOLTAGES

COIL POWER AT PICKUP VOLTAGE (typical)

5 thru 24 VDC

Standard coils: 220 mW

Sensitive coils: 100 mW

Light duty: 2 A at 28 VDC or 300 VAC Medium duty: 6 A at 28 VDC or 300 VAC Heavy duty: 10 A at 24 VDC or 250 VAC

Contact to coil: 1500 Vrms

Between open contacts:

1000 Vrms

Contact to coil: 1500 Vrms

Between open contacts: 1000 Vrms

TYPICAL LIFE

Electrical

At rated load unless otherwise specified

and 68.304

EPOXY SEALED Form

Yes 1 Form C

AZ8

• High sensitivity (110 mW) • Class B (130°C) insulation

standard • Class F (155°C) insulation

available • VDE versions available • Hermetic sealed versions

THT X X X

UL/CUR/TÜV

ห้องสมุดไป่ตู้

1 x 108 at 10 mA at 6 VDC 1.5 x 106 at 2 A at 28 VDC or

EP1C3T144FPGAdevelopboardmanual(开发板原理图)

EP1C3T144FPGAdevelopboardmanual(开发板原理图)FPGA develop board manual ALTERA Cyclone EP1C3T144ALTERA Cyclone 系列的fpga是altera 公司针对底端用户推出的一个系列的fpga。

具有成本低,使用的方便的优点,规模从3000到20000LE。

这一块实验板用的EP1C3T144的芯片,有3000LE逻辑资源,另外还有13条M4K RAM (共6.5Kbyte),另外还有还有一个数字锁相环。

这些资源能够足够应付电子设计竞赛和日常教学的需要,也可以作为初学者入门学习fpga的工具。

1. 开发板介绍1.1. 总体介绍开发板的电路图,如附录所示,电路图一共可分为9个部分:电源部分、按键和LED、下载配置部分、复位部分、外部时钟、滤波电容、用户扩展接口、5 1单片机接口、FPGA 芯片。

1.2. 具体介绍1.2.1. 电源部分板子由外部提供5V电源,使用的圆头插座的封装,可以直接用5V的电源适配器插上使用,不需要直流稳压电源,FPGA的IO的电源是3.3V,内核的电压是1.5V,所以用上两个LEO,一个将5V转到3.3V,另一个将3.3V转到1.5V,加上一些滤波电容,板上的其他外设的电源均是3.3V,另外有3.3V的电源指示灯,表示电源是否正常,还有防反插二极管,防止电源反插,对器件造成损坏。

1.2.2. 按键和LED板上提供4个拨码按键和4个led,分别接到fpga的8个IO引脚上,具体的引脚可以参看电路图或者丝印。

对于初学者,按键和led 可以用外当成最简单的外设,用和来控制这些外设。

对于用该板作开发的用户来说,可以把按键当成键盘控制,而把led当成提示来用。

1.2.3. 下载配置部分大家都知道fpga是sram型的可编程逻辑器件,不像rom型可编程器件cpld那样,通过jtag就可以直接把代码固化片子里面。

遥控资料

注:为了提高网速,图片可能被压缩!图片仅供参考!声光控开关必须同时具备两个条件,声光才起作用。

从声光控开关的结构上分析,开关面板表面装有光敏二级管,内部装有柱极体话简。

而光敏二极管的敏感效应,只有在黑暗时才起到作用(可用液晶万用表测得数值)。

也就是说当天色变暗到一定程度,光敏二级管感应后会在电子线路板上产生一个脉冲电流,使光敏二级管一路电路处在关闭状态,这时在楼梯口等处只要有响声出现,驻极体话筒就会同样产生分压,这时声光控制开关电路就连通起作用。

因为必须要二个条件同时存在,声光控开关才起作用,故叫与门电路。

(该电路涉及高压电,安全第一,请谨慎制作!)套件详细资料:印刷电路板,原理图,元件清单,元件,原理说明,制作说明、外壳等等。

电路原理图及工作原理:220V的市电经过灯泡和全桥整流后一路加在单向可控硅MCR 100-8上,另一路经R1限流后给本电路供电。

由于一开始可控硅无触发信号,呈关断状态,灯不亮。

C1为主滤波电容,VD为12V的稳压二极管给本电路提供稳定的工作电压。

Q1、R3、R4组成前级电压放大电路,微弱声音信号(话话声,脚步或掌声)由话筒MIC接收并转换成电信号,经C2耦合到Q9014的基极进行电压放大,R2为MIC的供电限流电阻,R3、R4是Q9014的偏置电阻,放大的信号送到与非门(F1)的2脚。

光敏电阻RG和R5组成串联分压电路,夜晚环境下无光时,光敏电阻的阻值很大,TC4011 一脚电压为高(反之则低),F1和F2将信号进行两级整形放大。

后经D5整流加在F3的输入端及同时给C3充电,很快C3上就充到了门电路的翻转电压, F3输出低电平,F4输出高电平,经R7加在单向可控硅的G极,可控硅导通,灯泡点亮。

在这个过程中,声音信号只需一个瞬时即可,这是因为,当声音信号来时,C3上的电压很快就充到了电源电压,而这时即使声音信号消失,C3只能通过W、R6进行放电,所以C3上将维持一段时间的高电平,这个高电平将维持单向可控硅导通,这就是延时的效果,灯亮后所能延时的长短取决于C3上维持高电平的时间长短,所以选择C3、W和R6的组合,可以控制延时的长短。

FPGA可编程逻辑器件芯片EP4CE6F17C6N中文规格书

Chapter 3:Memory Blocks in Arria II DevicesMemory Modes Arria II Device Handbook Volume 1: Device Interfaces and IntegrationSimple dual-port mode supports different read and write data widths (mixed widthsupport). Table 3–5 lists the mixed width configurations for the M9K blocks in simpledual-port mode. MLABs do not have native support for mixed width operations. TheQuartus II software can implement mixed width memories in MLABs with more thanone MLAB.Table 3–6 lists the mixed-width configurations for M144K blocks in simple dual-portmode.In simple dual-port mode, M9K and M144K blocks support separate write-enable andread-enable signals. Read-during-write operations to the same address can eitheroutput a “don’t care” or “old data” value.MLABs only support a write-enable signal. Read-during-write behavior for theMLABs can be either a “don’t care” or “old data” value. The available choices dependon the configuration of the MLAB.Table 3–5.M9K Block Mixed-Width Configurations (Simple Dual-Port Mode)Read PortWrite Port 8K ×14K ×22K ×41K ×8512×16256×321K ×9512×18256×368K ×1v v v v v v ———4K ×2v v v v v v ———2K ×4v v v v v v ———1K ×8v v v v v v ———512×16v v v v v v ———256×32v v v v v v ———1K ×9——————v v v 512×18——————v v v 256×36——————v v vTable 3–6.M144K Block Mixed-Width Configurations (Simple Dual-Port Mode)Read PortWrite Port 16K ×88K ×164K ×322K ×6416K ×98K ×184K ×362K ×7216K ×8v v v v ————8K ×16v v v v ————4K ×32v v v v ————2K ×64v v v v ————16K ×9————v v v v 8K ×18————v v v v 4K ×36————v v v v 2K ×72————v v v vChapter 1:Overview for the Arria II Device FamilyArria II Device Architecture Arria II Device Handbook Volume 1: Device Interfaces and Integration■Arria II GX devices have dedicated configuration banks at Bank 3C and 8C, whichsupport dedicated configuration pins and some of the dual-purpose pins with a configuration scheme at 1.8, 2.5, 3.0, and 3.3V . For Arria II GZ devices, thededicated configuration pins are located in Bank 1A and Bank 1C. However, these banks are not dedicated configuration banks; therefore, user I/O pins are available in Bank 1A and Bank 1C.■Dedicated VCCIO , VREF , and VCCPD pin per I/O bank to allow voltage-referenced I/O standards. Each I/O bank can operate at independent V CCIO , V REF , and V CCPD levels.High-Speed LVDS I/O and DPA■Dedicated circuitry for implementing LVDS interfaces at speeds from 150Mbps to1.25Gbps■R D OCT for high-speed LVDS interfacing■DPA circuitry and soft-CDR circuitry at the receiver automatically compensates for channel-to-channel and channel-to-clock skew in source-synchronous interfaces and allows for implementation of asynchronous serial interfaces with embedded clocks at up to 1.25Gbps data rate (SGMII and GbE)■Emulated LVDS output buffers use two single-ended output buffers with an external resistor network to support LVDS, mini-LVDS, BLVDS (only forArria II GZ devices), and RSDS standards.Clock Management■Provides dedicated global clock networks, regional clock networks, and peripheryclock networks that are organized into a hierarchical structure that provides up to 192 unique clock domains■Up to eight PLLs with 10 outputs per PLL to provide robust clock management and synthesis■Independently programmable PLL outputs, creating a unique andcustomizable clock frequency with no fixed relation to any other clock■Inherent jitter filtration and fine granularity control over multiply and divide ratios■Supports spread-spectrum input clocking and counter cascading with PLL input clock frequencies ranging from 5 to 500MHz to support both low-cost and high-end clock performance ■FPGA fabric can use the unused transceiver PLLs to provide more flexibilityTable 1–9.Location of OCT Calibration Block in Arria II Devices DevicePackage Option I/O Bank Arria II GXAll pin packages Bank 3A, Bank 7A, and Bank 8A Arria II GZ 780-pin flip chip FBGA Bank 3A, Bank 4A, Bank 7A, and Bank 8A 1152-pin flip chip FBGABank 1A, Bank 3A, Bank 4A, Bank 6A, Bank 7A, and Bank 8A 1517-pin flip chip FBGABank 1A, Bank 2A, Bank 3A, Bank 4A, Bank 5A, Bank 6A, Bank 7A, and Bank 8AChapter 3:Memory Blocks in Arria II DevicesMemory Features Arria II Device Handbook Volume 1: Device Interfaces and Integration Table 3–3 lists the truth table for the ECC status flags.1You cannot use the byte enable feature when ECC is engaged.1Read-during-write old data mode is not supported when ECC is engaged.Figure 3–8 shows a diagram of the ECC block of the M144K block.Table 3–3.Truth Table for ECC Status Flags in Arria II Devices Statuseccstatus[2]eccstatus[1]eccstatus[0]No error 000Single error and fixed011Double error and no fix101Illegal001Illegal010Illegal100Illegal 11X Figure 3–8.ECC Block Diagram of the M144K Block Data Input 646464872SECDED EncoderRAM Array 7264648888864643Status FlagsData Output SECDED Encoder Comparator ErrorCorrectionBlockErrorLocatorFlag Generator。

EP1C6Q240C8封装和部分引脚的功能分析

EP1C6Q240C8封装和部分引脚的功能分析图U21A图U21B图U21C图U21D第一部分:封装图U21A、U21B、U21C、U21D表示的是同一块芯片EP1C6Q240C8,有240个引脚,采用的是PQFP封装(即Plastic Quad Flat Package,塑料方块平面封装),PQFP封装的芯片的四周均有引脚,而且引脚之间距离很小,管脚也很细,一般大规模或超大规模集成电路采用这种封装形式.用这种形式封装的芯片必须采用SMT(Surface Mount Technology,表面组装技术)将芯片边上的引脚与主板焊接起来。

对于SMT技术,个人理解,即表面组装技术,一般用来焊接一些引脚在几百以上的芯片,比如说BGA,PGA一般都采用这种技术;例如笔记本主板上的intel北桥芯片,一般都采用球形封装,又如比较古老的Intel 965底部球形引脚大约有600多个,现在笔记本流行用的P43、P45、P55、X58,从P43一代引脚多达几千个甚至更多,这样做的好处是节约面积,坏处是测试的时候比较麻烦,像BGA这种封装的芯片一般焊上去之后,顶部要引出几个接点,以防止在使用过程中坏掉,方便用万用表或者示波器来测试各个通路便于修理.对于这几种类型的芯片,除了PQFP少数罕见的高手能手工焊接之外,一般都采用贴片机来进行专门的焊接工作。

这里简单介绍一下这两种封装:PQFP/PFP封装具有以下特点1.适用于SMD表面安装技术在PCB电路板上安装布线。

2.适合高频使用。

2.操作方便,可靠性高。

3.芯片面积与封装面积之间的比值较小。

4.Intel系列CPU中80286、80386和某些486主板采用这种封装形式。

这里的SMD表示的是贴片组装器件;BGA球栅阵列封装随着集成电路技术的发展,对集成电路的封装要求更加严格.产品的功能性,当IC的频率超过100MHz时,传统封装方式可能会产生所谓的“CrossTalk(串扰)”现象,而且当IC的管脚数大于208 Pin时,传统的封装方式有其困难度。

EP1C6Q240I7N中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

更改摘要

— — — — — —

1–3

初稿

使用该设备插脚引线对于一个给定包所有计划中密度引脚

输入识别哪些I / O引脚可以迁移.在Quartus

® II

软件可以自动交叉引用和地点所有引脚你

当给定一个设备迁移列表.如果一个设备有电源或地 销,但这些相同引脚是不同装置,其在对用户I / O 迁移路径,Quartus II软件防护证销不作为 用户I / O在Quartus II软件.确防护这些引脚连接

100-Pin TQFP

0.5 256 16×16

144-Pin TQFP

0.5 484 22×22

240-Pin PQFP

0.5 1,024 34.6×34.6

256-Pin FineLine

BGA

1.0

289

17×17

324-Pin FineLine

BGA

1.0

361

19×19

400-Pin FineLine

1–2

初稿

2008年 5月

芯片中文手册,看全文,戳

文档修订历史记录

到电路板上相应平面. Quartus II软件储备 I / O引脚所必需与在同一个包有多个电源引脚较大密度布局电源引 脚.

表 1-3.旋风 QFP和 BGAFineLine包装规格

尺度

间距(mm) 区(毫米 ) 长短 × width (mm × mm)

高达288千位RAM.有这样锁相环路(PLL),用于时钟和一个专用双倍数据

速率(DDR)接口,以满足DDR SDRAM和快速周期RAM(FCRAM)内存需求特

点,Cyclone器件可用于数据通道应用提供具有成本效益解决

方案. Cyclone器件支持多种I / O标准,包括LVDS数据速率高达每

XCS05XL-4PC144I中文资料

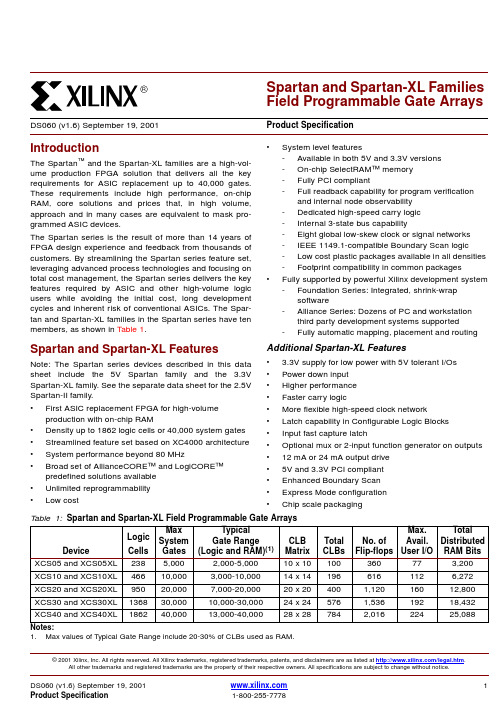

© 2001 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at /legal.htm .All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.IntroductionThe Spartan ™ and the Spartan-XL families are a high-vol-ume production FPGA solution that delivers all the key requirements for ASIC replacement up to 40,000 gates.These requirements include high performance, on-chip RAM, core solutions and prices that, in high volume,approach and in many cases are equivalent to mask pro-grammed ASIC devices.The Spartan series is the result of more than 14 years of FPGA design experience and feedback from thousands of customers. By streamlining the Spartan series feature set,leveraging advanced process technologies and focusing on total cost management, the Spartan series delivers the key features required by ASIC and other high-volume logic users while avoiding the initial cost, long development cycles and inherent risk of conventional ASICs. The Spar-tan and Spartan-XL families in the Spartan series have ten members, as shown in T able 1.Spartan and Spartan-XL FeaturesNote: The Spartan series devices described in this data sheet include the 5V Spartan family and the 3.3V Spartan-XL family. See the separate data sheet for the 2.5V Spartan-II family.•First ASIC replacement FPGA for high-volume production with on-chip RAM•Density up to 1862 logic cells or 40,000 system gates •Streamlined feature set based on XC4000 architecture •System performance beyond 80MHz•Broad set of AllianceCORE ™ and LogiCORE ™ predefined solutions available •Unlimited reprogrammability •Low cost•System level features-Available in both 5V and 3.3V versions -On-chip SelectRAM ™ memory -Fully PCI compliant-Full readback capability for program verificationand internal node observability -Dedicated high-speed carry logic -Internal 3-state bus capability-Eight global low-skew clock or signal networks -IEEE 1149.1-compatible Boundary Scan logic -Low cost plastic packages available in all densities -Footprint compatibility in common packages•Fully supported by powerful Xilinx development system -Foundation Series: Integrated, shrink-wrapsoftware-Alliance Series: Dozens of PC and workstationthird party development systems supported-Fully automatic mapping, placement and routing Additional Spartan-XL Features• 3.3V supply for low power with 5V tolerant I/Os •Power down input •Higher performance •Faster carry logic•More flexible high-speed clock network•Latch capability in Configurable Logic Blocks •Input fast capture latch•Optional mux or 2-input function generator on outputs •12 mA or 24 mA output drive •5V and 3.3V PCI compliant •Enhanced Boundary Scan •Express Mode configuration •Chip scale packagingSpartan and Spartan-XL Families Field Programmable Gate ArraysDS060 (v1.6) September 19, 2001Product Specification T able 1: Spartan and Spartan-XL Field Programmable Gate Arrays1.Max values of Typical Gate Range include 20-30% of CLBs used as RAM.2DS060 (v1.6) September 19, 2001General OverviewSpartan series FPGAs are implemented with a regular, flex-ible, programmable architecture of Configurable Logic Blocks (CLBs), interconnected by a powerful hierarchy of versatile routing resources (routing channels), and sur-rounded by a perimeter of programmable Input/Output Blocks (IOBs), as seen in Figure 1. They have generous routing resources to accommodate the most complex inter-connect patterns.The devices are customized by loading configuration data into internal static memory cells. Re-programming is possi-ble an unlimited number of times. The values stored in thesememory cells determine the logic functions and intercon-nections implemented in the FPGA. The FPGA can either actively read its configuration data from an external serial PROM (Master Serial mode), or the configuration data can be written into the FPGA from an external device (Slave Serial mode).Spartan series FPGAs can be used where hardware must be adapted to different user applications. FPGAs are ideal for shortening design and development cycles, and also offer a cost-effective solution for production rates well beyond 50,000 systems per month.Figure 1: Basic FPGA Block DiagramSpartan series devices achieve high-performance, low-cost operation through the use of an advanced architecture and semiconductor technology. Spartan and Spartan-XL devices provide system clock rates exceeding 80MHz and internal performance in excess of150MHz. In contrast to other FPGA devices, the Spartan series offers the most cost-effective solution while maintaining leading-edge per-formance. In addition to the conventional benefit of high vol-ume programmable logic solutions, Spartan series FPGAs also offer on-chip edge-triggered single-port and dual-port RAM, clock enables on all flip-flops, fast carry logic, and many other features.The Spartan/XL families leverage the highly successful XC4000 architecture with many of that family’s features and benefits. T echnology advancements have been derived from the XC4000XLA process developments.Logic Functional DescriptionThe Spartan series uses a standard FPGA structure as shown in Figure1, page2. The FPGA consists of an array of configurable logic blocks (CLBs) placed in a matrix of routing channels. The input and output of signals is achieved through a set of input/output blocks (IOBs) forming a ring around the CLBs and routing channels.•CLBs provide the functional elements for implementing the user’s logic.•IOBs provide the interface between the package pins and internal signal lines.•Routing channels provide paths to interconnect the inputs and outputs of the CLBs and IOBs.The functionality of each circuit block is customized during configuration by programming internal static memory cells. The values stored in these memory cells determine the logic functions and interconnections implemented in the FPGA.Configurable Logic Blocks (CLBs)The CLBs are used to implement most of the logic in an FPGA. The principal CLB elements are shown in the simpli-fied block diagram in Figure2. There are three look-up tables (LUT) which are used as logic function generators, two flip-flops and two groups of signal steering multiplexers. There are also some more advanced features provided by the CLB which will be covered in the Advanced Features Description, page13.Function GeneratorsTwo 16x1 memory look-up tables (F-LUT and G-LUT) are used to implement 4-input function generators, each offer-ing unrestricted logic implementation of any Boolean func-tion of up to four independent input signals (F1 to F4 or G1 to G4). Using memory look-up tables the propagation delay is independent of the function implemented.A third 3-input function generator (H-LUT) can implement any Boolean function of its three inputs. Two of these inputs are controlled by programmable multiplexers (see box "A" of Figure2). These inputs can come from the F-LUT or G-LUT outputs or from CLB inputs. The third input always comes from a CLB input. The CLB can, therefore, implement cer-tain functions of up to nine inputs, like parity checking. The three LUTs in the CLB can also be combined to do any arbi-trarily defined Boolean function of five inputs.4DS060 (v1.6) September 19, 2001A CLB can implement any of the following functions:•Any function of up to four variables, plus any second function of up to four unrelated variables, plus any third function of up to three unrelated variablesNote: When three separate functions are generated, one of the function outputs must be captured in a flip-flop internal to the CLB. Only two unregistered function generator outputs are available from the CLB.•Any single function of five variables•Any function of four variables together with some functions of six variables•Some functions of up to nine variables.Implementing wide functions in a single block reduces both the number of blocks required and the delay in the signal path, achieving both increased capacity and speed. The versatility of the CLB function generators significantly improves system speed. In addition, the design-software tools can deal with each function generator independently.This flexibility improves cell usage.Flip-FlopsEach CLB contains two flip-flops that can be used to regis-ter (store) the function generator outputs. The flip-flops and function generators can also be used independently (see Figure 2). The CLB input DIN can be used as a direct input to either of the two flip-flops. H1 can also drive either flip-flop via the H-LUT with a slight additional delay.The two flip-flops have common clock (CK), clock enable (EC) and set/reset (SR) inputs. Internally both flip-flops are also controlled by a global initialization signal (GSR) which is described in detail in Global Signals: GSR and GTS ,page 20.Latches (Spartan-XL only)The Spartan-XL CLB storage elements can also be config-ured as latches. The two latches have common clock (K)and clock enable (EC) inputs. Functionality of the storage element is described in Table 2.Figure 2: Spartan/XL Simplified CLB Logic Diagram (some features not shown)Clock InputEach flip-flop can be triggered on either the rising or falling clock edge. The CLB clock line is shared by both flip-flops.However, the clock is individually invertible for each flip-flop (see CK path in Figure 3). Any inverter placed on the clock line in the design is automatically absorbed into the CLB. Clock EnableThe clock enable line (EC) is active High. The EC line is shared by both flip-flops in a CLB. If either one is left discon-nected, the clock enable for that flip-flop defaults to the active state. EC is not invertible within the CLB. The clock enable is synchronous to the clock and must satisfy the setup and hold timing specified for the device.Set/ResetThe set/reset line (SR) is an asynchronous active High con-trol of the flip-flop. SR can be configured as either set or reset at each flip-flop. This configuration option determines the state in which each flip-flop becomes operational after configuration. It also determines the effect of a GSR pulse during normal operation, and the effect of a pulse on the SR line of the CLB. The SR line is shared by both flip-flops. If SR is not specified for a flip-flop the set/reset for that flip-flop defaults to the inactive state. SR is not invertible within the CLB.CLB Signal Flow ControlIn addition to the H-LUT input control multiplexers (shown in box "A" of Figure 2, page 4) there are signal flow control multiplexers (shown in box "B" of Figure 2) which select the signals which drive the flip-flop inputs and the combinatorial CLB outputs (X and Y).Each flip-flop input is driven from a 4:1 multiplexer which selects among the three LUT outputs and DIN as the data source.Each combinatorial output is driven from a 2:1 multiplexer which selects between two of the LUT outputs. The X output can be driven from the F-LUT or H-LUT, the Y output from G-LUT or H-LUT .Control SignalsThere are four signal control multiplexers on the input of the CLB. These multiplexers allow the internal CLB control sig-nals (H1, DIN, SR, and EC in Figure 2 and Figure 4) to be driven from any of the four general control inputs (C1-C4 in Figure 4) into the CLB. Any of these inputs can drive any of the four internal control signals.T able 2: CLB Storage Element FunctionalityLegend:XDon ’t careRising edge (clock not inverted).SR Set or Reset value. Reset is default.0*Input is Low or unconnected (default value)1*Input is High or unconnected (default value)Figure 3: CLB Flip-Flop Functional Block Diagram6DS060 (v1.6) September 19, 2001The four internal control signals are:•EC: Enable Clock•SR: Asynchronous Set/Reset or H function generator Input 0•DIN: Direct In or H function generator Input 2•H1: H function generator Input 1.Input/Output Blocks (IOBs)User-configurable input/output blocks (IOBs) provide the interface between external package pins and the internal logic. Each IOB controls one package pin and can be con-figured for input, output, or bidirectional signals. Figure 6shows a simplified functional block diagram of the Spar-tan/XL IOB.IOB Input Signal PathThe input signal to the IOB can be configured to either go directly to the routing channels (via I1 and I2 in Figure 6) or to the input register. The input register can be programmed as either an edge-triggered flip-flop or a level-sensitive latch. The functionality of this register is shown in Table 3,and a simplified block diagram of the register can be seen in Figure 5.Figure 4: CLB Control Signal InterfaceFigure 5: IOB Flip-Flop/Latch Functional BlockDiagramTable 3: Input Register FunctionalityX Don ’t care.Rising edge (clock not inverted).SR Set or Reset value. Reset is default.0*Input is Low or unconnected (default value)1*Input is High or unconnected (default value)The register choice is made by placing the appropriate library symbol. For example, IFD is the basic input flip-flop (rising edge triggered), and ILD is the basic input latch (transparent-High). Variations with inverted clocks are also available. The clock signal inverter is also shown in Figure5 on the CK line.The Spartan IOB data input path has a one-tap delay ele-ment: either the delay is inserted (default), or it is not. The Spartan-XL IOB data input path has a two-tap delay ele-ment, with choices of a full delay, a partial delay, or no delay. The added delay guarantees a zero hold time with respect to clocks routed through the global clock buffers. (See Glo-bal Nets and Buffers, page12 for a description of the glo-bal clock buffers in the Spartan/XL families.) For a shorter input register setup time, with positive hold-time, attach a NODELAY attribute or property to the flip-flop.The output of the input register goes to the routing channels (via I1 and I2 in Figure6). The I1 and I2 signals that exit the IOB can each carry either the direct or registered input signal.The 5V Spartan input buffers can be globally configured for either TTL (1.2V) or CMOS (VCC/2) thresholds, using an option in the bitstream generation software. The Spartan output levels are also configurable; the two global adjust-ments of input threshold and output level are independent. The inputs of Spartan devices can be driven by the outputs of any 3.3V device, if the Spartan inputs are in TTL mode. Input and output thresholds are TTL on all configuration pins until the configuration has been loaded into the device and specifies how they are to be used. Spartan-XL inputs are TTL compatible and 3.3V CMOS compatible. Supported sources for Spartan/XL device inputs are shown in Table4.Spartan-XL I/Os are fully 5V tolerant even though the V CC is 3.3V. This allows 5V signals to directly connect to the Spar-tan-XL inputs without damage, as shown in Table4. In addi-tion, the 3.3V V CC can be applied before or after 5V signals are applied to the I/Os. This makes the Spartan-XL devices immune to power supply sequencing problems.Figure 6: Simplified Spartan/XL IOB Block Diagram8DS060 (v1.6) September 19, 2001Spartan-XL V CC ClampingSpartan-XL FPGAs have an optional clamping diode con-nected from each I/O to V CC . When enabled they clamp ringing transients back to the 3.3V supply rail. This clamping action is required in 3.3V PCI applications. V CC clamping is a global option affecting all I/O pins.Spartan-XL devices are fully 5V TTL I/O compatible if V CC clamping is not enabled. With V CC clamping enabled, the Spartan-XL devices will begin to clamp input voltages to one diode voltage drop above V CC . If enabled, TTL I/O com-patibility is maintained but full 5V I/O tolerance is sacrificed.The user may select either 5V tolerance (default) or 3.3V PCI compatibility. In both cases negative voltage is clamped to one diode voltage drop below ground.Spartan-XL devices are compatible with TTL, LVTTL, PCI 3V, PCI 5V and LVCMOS signalling. The various standards are illustrated in Table 5.Additional Fast Capture Input Latch (Spartan-XL only)The Spartan-XL IOB has an additional optional latch on the input. This latch is clocked by the clock used for the output flip-flop rather than the input clock. Therefore, two different clocks can be used to clock the two input storage elements.This additional latch allows the fast capture of input data,which is then synchronized to the internal clock by the IOB flip-flop or latch.T o place the Fast Capture latch in a design, use one of the special library symbols, ILFFX or ILFLX. ILFFX is a trans-parent-Low Fast Capture latch followed by an active High input flip-flop. ILFLX is a transparent Low Fast Capture latch followed by a transparent High input latch. Any of the clock inputs can be inverted before driving the library element,and the inverter is absorbed into the IOB.IOB Output Signal PathOutput signals can be optionally inverted within the IOB,and can pass directly to the output buffer or be stored in an edge-triggered flip-flop and then to the output buffer. The functionality of this flip-flop is shown in T able 6.T able 4: Supported Sources for Spartan/XL InputsT able 5: I/O Standards Supported by Spartan-XL FPGAsTable 6: Output Flip-Flop Functionality X Don ’t careRising edge (clock not inverted). SR Set or Reset value. Reset is default.0*Input is Low or unconnected (default value)1*Input is High or unconnected (default value)Z3-stateOutput Multiplexer/2-Input Function Generator (Spartan-XL only)The output path in the Spartan-XL IOB contains an addi-tional multiplexer not available in the Spartan IOB. The mul-tiplexer can also be configured as a 2-input function generator, implementing a pass gate, AND gate, OR gate, or XOR gate, with 0, 1, or 2 inverted inputs.When configured as a multiplexer, this feature allows two output signals to time-share the same output pad, effec-tively doubling the number of device outputs without requir-ing a larger, more expensive package. The select input is the pin used for the output flip-flop clock, OK.When the multiplexer is configured as a 2-input function generator, logic can be implemented within the IOB itself. Combined with a Global buffer, this arrangement allows very high-speed gating of a single signal. For example, a wide decoder can be implemented in CLBs, and its output gated with a Read or Write Strobe driven by a global buffer. The user can specify that the IOB function generator be used by placing special library symbols beginning with the letter "O." For example, a 2-input AND gate in the IOB func-tion generator is called OAND2. Use the symbol input pin labeled "F" for the signal on the critical path. This signal is placed on the OK pin — the IOB input with the shortest delay to the function generator. Two examples are shown in Figure7.Output BufferAn active High 3-state signal can be used to place the out-put buffer in a high-impedance state, implementing 3-state outputs or bidirectional I/O. Under configuration control, the output (O) and output 3-state (T) signals can be inverted. The polarity of these signals is independently configured for each IOB (see Figure6, page7). An output can be config-ured as open-drain (open-collector) by tying the 3-state pin (T) to the output signal, and the input pin (I) to Ground.By default, a 5V Spartan device output buffer pull-up struc-ture is configured as a TTL-like totem-pole. The High driver is an n-channel pull-up transistor, pulling to a voltage one transistor threshold below V CC. Alternatively, the outputs can be globally configured as CMOS drivers, with additional p-channel pull-up transistors pulling to V CC. This option, applied using the bitstream generation software, applies to all outputs on the device. It is not individually programma-ble.All Spartan-XL device outputs are configured as CMOS drivers, therefore driving rail-to-rail. The Spartan-XL outputs are individually programmable for 12mA or 24mA output drive.Any 5V Spartan device with its outputs configured in TTL mode can drive the inputs of any typical 3.3V device. Sup-ported destinations for Spartan/XL device outputs are shown in Table7.Three-State Register (Spartan-XL Only)Spartan-XL devices incorporate an optional register control-ling the three-state enable in the IOBs. The use of the three-state control register can significantly improve output enable and disable time.Output Slew RateThe slew rate of each output buffer is, by default, reduced, to minimize power bus transients when switching non-criti-cal signals. For critical signals, attach a FAST attribute or property to the output buffer or flip-flop.Spartan/XL devices have a feature called "Soft Start-up," designed to reduce ground bounce when all outputs are turned on simultaneously at the end of configuration. When the configuration process is finished and the device starts up, the first activation of the outputs is automatically slew-rate limited. Immediately following the initial activation of the I/O, the slew rate of the individual outputs is deter-mined by the individual configuration option for each IOB. Pull-up and Pull-down NetworkProgrammable pull-up and pull-down resistors are used fortying unused pins to V CC or Ground to minimize power con-sumption and reduce noise sensitivity. The configurablepull-up resistor is a p-channel transistor that pulls to V CC.The configurable pull-down resistor is an n-channel transis-tor that pulls to Ground. The value of these resistors is typi-cally 20KΩ − 100KΩ (See "Spartan DC Characteristics Figure 7: AND and MUX Symbols in Spartan-XL IOB10DS060 (v1.6) September 19, 2001Over Operating Conditions" on page 43.). This high value makes them unsuitable as wired-AND pull-up resistors.After configuration, voltage levels of unused pads, bonded or unbonded, must be valid logic levels, to reduce noise sensitivity and avoid excess current. Therefore, by default,unused pads are configured with the internal pull-up resistor active. Alternatively, they can be individually configured with the pull-down resistor, or as a driven output, or to be driven by an external source. To activate the internal pull-up, attach the PULLUP library component to the net attached to the pad. To activate the internal pull-down, attach the PULL-DOWN library component to the net attached to the pad.Set/ResetAs with the CLB registers, the GSR signal can be used to set or clear the input and output registers, depending on the value of the INIT attribute or property. The two flip-flops can be individually configured to set or clear on reset and after configuration. Other than the global GSR net, no user-con-trolled set/reset signal is available to the I/O flip-flops (Figure 5). The choice of set or reset applies to both the ini-tial state of the flip-flop and the response to the GSR pulse.Independent ClocksSeparate clock signals are provided for the input (IK) and output (OK) flip-flops. The clock can be independently inverted for each flip-flop within the IOB, generating eitherfalling-edge or rising-edge triggered flip-flops. The clock inputs for each IOB are mon Clock EnablesThe input and output flip-flops in each IOB have a common clock enable input (see EC signal in Figure 5), which through configuration, can be activated individually for the input or output flip-flop, or both. This clock enable operates exactly like the EC signal on the Spartan/XL CLB. It cannot be inverted within the IOB.Routing Channel DescriptionAll internal routing channels are composed of metal seg-ments with programmable switching points and switching matrices to implement the desired routing. A structured,hierarchical matrix of routing channels is provided to achieve efficient automated routing.This section describes the routing channels available in Spartan/XL devices. Figure 8 shows a general block dia-gram of the CLB routing channels. The implementation soft-ware automatically assigns the appropriate resources based on the density and timing requirements of the design.The following description of the routing channels is for infor-mation only and is simplified with some minor details omit-ted. For an exact interconnect description the designer should open a design in the FPGA Editor and review the actual connections in this tool.The routing channels will be discussed as follows;•CLB routing channels which run along each row and column of the CLB array.•IOB routing channels which form a ring (called a VersaRing) around the outside of the CLB array. It connects the I/O with the CLB routing channels.•Global routing consists of dedicated networks primarily designed to distribute clocks throughout the device with minimum delay and skew. Global routing can also be used for other high-fanout signals.CLB Routing ChannelsThe routing channels around the CLB are derived from three types of interconnects; single-length, double-length,and longlines. At the intersection of each vertical and hori-zontal routing channel is a signal steering matrix called a Programmable Switch Matrix (PSM). Figure 8 shows the basic routing channel configuration showing single-length lines, double-length lines and longlines as well as the CLBs and PSMs. The CLB to routing channel interface is shown as well as how the PSMs interface at the channel intersec-tions.T able 7: Supported Destinations for Spartan/XL OutputsNotes:1.Only if destination device has 5V tolerant inputs.CLB InterfaceA block diagram of the CLB interface signals is shown in Figure9. The input signals to the CLB are distributed evenly on all four sides providing maximum routing flexibility. In general, the entire architecture is symmetrical and regular. It is well suited to established placement and routing algo-rithms. Inputs, outputs, and function generators can freely swap positions within a CLB to avoid routing congestion during the placement and routing operation. The exceptions are the clock (K) input and CIN/COUT signals. The K input is routed to dedicated global vertical lines as well as four single-length lines and is on the left side of the CLB. The CIN/COUT signals are routed through dedicated intercon-nects which do not interfere with the general routing struc-ture. The output signals from the CLB are available to drive both vertical and horizontal channels.Programmable Switch MatricesThe horizontal and vertical single- and double-length lines intersect at a box called a programmable switch matrix (PSM). Each PSM consists of programmable pass transis-tors used to establish connections between the lines (see Figure10).For example, a single-length signal entering on the right side of the switch matrix can be routed to a single-length line on the top, left, or bottom sides, or any combination thereof, if multiple branches are required. Similarly, a dou-ble-length signal can be routed to a double-length line on any or all of the other three edges of the programmable switch matrix.Single-Length LinesSingle-length lines provide the greatest interconnect flexibil-ity and offer fast routing between adjacent blocks. There are eight vertical and eight horizontal single-length lines associ-ated with each CLB. These lines connect the switching matrices that are located in every row and column of CLBs. Single-length lines are connected by way of the program-mable switch matrices, as shown in Figure10. Routing con-nectivity is shown in Figure8.Single-length lines incur a delay whenever they go through a PSM. Therefore, they are not suitable for routing signals for long distances. They are normally used to conduct sig-nals within a localized area and to provide the branching for nets with fanout greater than one.Figure 8: Spartan/XL CLB Routing Channels and Interface Block DiagramFigure 9: CLB Interconnect Signals。

EP1C6Q144C8资料

1

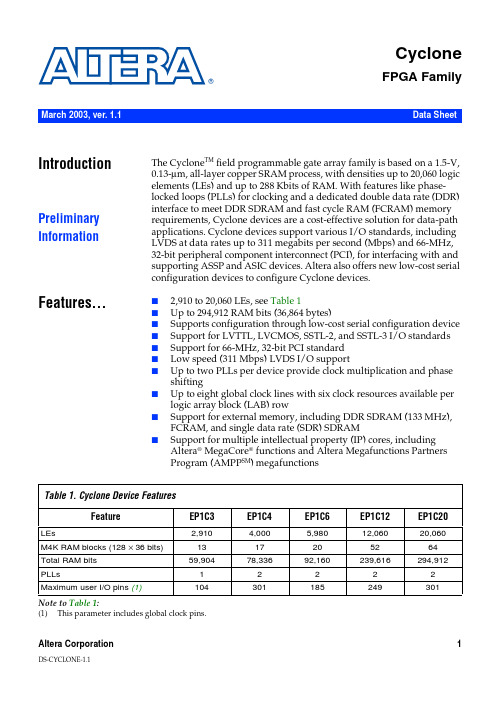

Cyclone FPGA Family Data Sheet

Preliminary Information

Cyclone devices are available in quad flat pack (QFP) and space-saving FineLine BGA packages (see Tables 2 through 3). Table 2. Cyclone Package Options & I/O Pin Counts Device 100-Pin TQFP (1)

65

144-Pin TQFP (1), (2)

104

240-Pin PQFP (1)

256-Pin FineLine BGA

324-Pin FineLine BGA

400-Pin FineLine BGA

EP1C3 EP1C4 EP1C6 EP1C12 EP1C20 Notes to Table 2:

EP1C3

2,910 13 59,904 1 104

EP1C4

4,000 17 78,336 2 301

EP1C6

5,98060 52 239,616 2 249

EP1C20

20,060 64 294,912 2 301

Altera Corporation

1.0 289 17 × 17

324-Pin FineLine BGA

1.0 361 19 × 19

400-Pin FineLine BGA

1.0 441 21 × 21

Pitch (mm) Area (mm 2) Length × width (mm × mm)

电子流压差控6路6位线程(EPIV)说明书

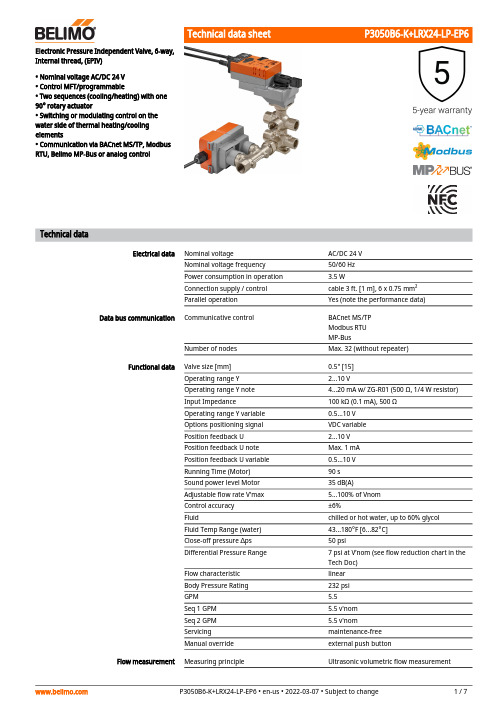

Electronic Pressure Independent Valve, 6-way,Internal thread, (EPIV)• Nominal voltage AC/DC 24 V• Control MFT/programmable• Two sequences (cooling/heating) with one90° rotary actuator• Switching or modulating control on thewater side of thermal heating/coolingelements• Communication via BACnet MS/TP, ModbusRTU, Belimo MP-Bus or analog controlTechnical dataElectrical data Nominal voltage AC/DC 24 VNominal voltage frequency50/60 HzPower consumption in operation 3.5 WConnection supply / control cable 3 ft. [1 m], 6 x 0.75 mm²Parallel operation Yes (note the performance data) Data bus communication Communicative control BACnet MS/TPModbus RTUMP-BusNumber of nodes Max. 32 (without repeater)Functional data Valve size [mm]0.5" [15]Operating range Y 2...10 VOperating range Y note 4...20 mA w/ ZG-R01 (500 Ω, 1/4 W resistor)Input Impedance100 kΩ (0.1 mA), 500 ΩOperating range Y variable0.5...10 VOptions positioning signal VDC variablePosition feedback U 2...10 VPosition feedback U note Max. 1 mAPosition feedback U variable0.5...10 VRunning Time (Motor)90 sSound power level Motor35 dB(A)Adjustable flow rate V'max 5...100% of VnomControl accuracy±6%Fluid chilled or hot water, up to 60% glycolFluid Temp Range (water)43...180°F [6...82°C]Close-off pressure ∆ps50 psiDifferential Pressure Range7 psi at V’nom (see flow reduction chart in theTech Doc)Flow characteristic linearBody Pressure Rating232 psiGPM 5.5Seq 1 GPM 5.5 v'nomSeq 2 GPM 5.5 v'nomServicing maintenance-freeManual override external push buttonFlow measurement Measuring principle Ultrasonic volumetric flow measurement••••Flow measurementMeasuring accuracy flow ±2%Min. flow measurement 1% of V'nom Measurement Repeatability±0.5% (Flow)Safety dataDegree of protection IEC/EN IP54Degree of protection NEMA/UL NEMA 2Enclosure UL Enclosure Type 2Agency ListingcULus acc. to UL60730-1A/-2-14, CAN/CSA E60730-1:02, CE acc. to 2014/30/EU and2014/35/EU; Listed to UL 2043 - suitable for use in air plenums per Section 300.22(c) of the NEC and Section 602.2 of the IMC Quality Standard ISO 9001Ambient temperature -22...122°F [-30...50°C]Storage temperature -40...176°F [-40...80°C]Ambient humidityMax. 95% RH, non-condensing MaterialsValve body Nickel-plated brass body Spindle nickel-plated brass Spindle seal EPDM (lubricated)SeatPTFECharacterized disc chrome plated steel O-ring EPDMBallchrome plated brassSafety notesThis device has been designed for use in stationary heating, ventilation and air-conditioning systems and must not be used outside the specified field of application, especially in aircraft or in any other airborne means of transport.Outdoor application: only possible in case that no (sea) water, snow, ice, insolation or aggressive gases interfere directly with the actuator and that is ensured that the ambient conditions remain at any time within the thresholds according to the data sheet.Only authorized specialists may carry out installation. All applicable legal or institutional installation regulations must be complied during installation.The device contains electrical and electronic components and must not be disposed of as household refuse. All locally valid regulations and requirements must be observed.Product featuresFlow/Mounting detailsMode of operationFlow measurementDefinitionCreep flow suppressionConfigurable actuatorsHydronic balancingProduct featuresThe final controlling device consists of three components: 6-way characterized control valve, measuring pipe with volumetric flow sensor and the actuator itself. The adjusted maximum flows for sequence 1 (V'max1) and sequence 2 (V'max2) are assigned to the positioning signal (2V/0% for sequence 1, 10 V/100% for sequence 2).The performance device can be controlled communicatively or by an analog signal. The fluid is detected by the sensor in the measuring pipe and is applied as the flow value. The measured value is balanced with the setpoint. The actuator corrects the deviation by changing the valve position.All flow tolerances are at 68°...77°F [20°... 25°C] and 0% glycol.V'nom is the maximum possible flow. (V'nom=V'nom1=V'nom2)V'max1 is the maximum flow rate which has been set with the smallest positioning signal, 2 V / 0%.V'max2 is the maximum flow rate which has been set with the highest positioning signal, 10 V / 100%.V'max1 and V'max2 can be adjusted 5...100% of V'nom.V'min 0% (non-variable).Given the very low flow speed in the opening point, this can no longer be measured by the sensor within the required tolerance. This range is overridden electronically.Opening sequenceThe valve remains closed until the volumetric flow required by the positioning signal Ycorresponds to 1% of V'nom. The control along the valve characteristic curve is active after this value has been exceeded.Closing sequenceThe control along the valve characteristic curve is active up to the required flow rate of 1% of V'nom. Once the level falls below this value, the flow rate is maintained at 1% of V'nom. If the level falls below the flow rate of 0.5% of V'nom required by the reference variable Y, then thevalve will close.The factory settings cover the most common applications.With the ZTH US and the Belimo Assistant App, the maximum flow rates of sequence 1 and sequence 2 can be adjusted individually on-site in a few simple reliable steps.Combination analogue - communicative(hybrid mode)Manual override High functional safetyPosition feedbackPressure compensationWith conventional control by means of an analog positioning signal, BACnet or Modbus can be used for the communicative position feedback.Manual override with push-button possible (the gear is disengaged for as long as the button is pressed or remains locked).The actuator is overload protected, requires no limit switches and automatically stops when the end stop is reached.Regardless of the setting of the control mode, the feedback signal U5 is always assigned to the flow V'max1 and V'max2.In cases of combined heating/cooling control elements, the fluid remains in the control element when in the closed position (no heating or cooling). The pressure of the enclosed fluid can rise or fall due to changes in fluid temperature caused by the ambient temperature. The 6-way characterized control valves have an integrated pressure relief function for the purpose of compensating for such pressure changes.The pressure relief function is active in the closed position (45°) of the valve; reliable separation of Sequences 1 and 2 continues. For additional information, consult the notes for project planning for the 6-way characterized control valve.Electrical installationSupply from isolating transformer.Parallel connection of other actuators possible. Observe the performance data.The wiring of the line for BACnet MS/TP / Modbus RTU is to be carried out in accordance with applicable RS485 regulations.Modbus / BACnet: Supply and communication are not galvanically isolated. Connect earth signal of the devices with one another.AC/DC 24 V, modulatingCable colors:1 = black 2 = red 3 = white 5 = orange 6 = pink 7 = greyOperation on the MP-BusCable colors:1 = black 2 = red 3 = white 5 = orange 6 = pink 7 = greyBACnet MS/TP / Modbus RTUC₁ = D- = A C₂ = D+ = BRecommended installation positionsWater quality requirementsServicingFlow directionModbus RTU / BACnet MS/TP with analogue setpoint (hybrid mode)C₁ = D- = A C₂ = D+ = BInstallation notesThe ball valve can be installed upright to horizontal. The ball valve may not be installed in ahanging position, i.e. with the spindle pointing downwards.Belimo valves are regulating devices. For the valves to function correctly in the long term, they must be kept free from particle debris (e.g. welding beads during installation work). The installation of a suitable strainer is recommended.Ball valves, rotary actuators and sensors are maintenance-free.Before any service work on the final controlling device is carried out, it is essential to isolate the rotary actuator from the power supply (by unplugging the electrical cable if necessary). Any pumps in the part of the piping system concerned must also be switched off and theappropriate slide valves closed (allow all components to cool down first if necessary and always reduce the system pressure to ambient pressure level).The system must not be returned to service until the ball valve and the rotary actuator have been correctly reassembled in accordance with the instructions and the pipeline has been refilled by professionally trained personnel.The flow direction must be observed. The position of the ball can be identified from the L-marking on the damper shaft.Heating and cooling in position accuracyValve characteristic curveNFC connectionThe lower diagram shows the flow characteristic depending on the control signal.Valve characteristic curveServiceBelimo devices marked with the NFC logo can be operated with the Belimo Assistant App.Requirement:- NFC- or Bluetooth-capable smartphone- Belimo Assistant App (Google Play & Apple AppStore)Align NFC-capable smartphone on the device so that both NFC antennas are superposed.Connect Bluetooth-enabled smartphone via the Bluetooth-to-NFC Converter ZIP-BT-NFC to thedevice. Technical data and operation instructions are shown in the ZIP-BT-NFC data sheet.Service Tools connectionZTH EU connectionDimensionsDimensional drawingsA B C D E F G10.2" [260]9.5" [241]7.4" [187] 5.9" [150] 4.3" [110]7.9" [201] 2.6" [65]。

FPGA可编程逻辑器件芯片EP1C6T144I6中文规格书

SPI-Compatible Port Controllers For transmit DMA operations, the master SPI initiates a word transfer only when there is data in the DMA FIFO. If the DMA FIFO is empty, the SPI waits for the DMA engine to write to the DMA FIFO before start-ing the transfer. All aspects of SPI receive operation should be ignored when configured in transmit DMA mode, including the data in theSPIx_RDBR register, and the status of the RXS and RBSY bits. The RBSY over-run conditions cannot generate an error interrupt in this mode. The TXE underrun condition cannot happen in this mode (master DMA TXmode), because the master SPI will not initiate a transfer if there is no data in the DMA FIFO.Writes to the SPIx_TDBR register during an active SPI transmit DMA oper-ation should not occur because the DMA data will be overwritten. Writes to the SPIx_TDBR register during an active SPI receive DMA operation are allowed. Reads from the SPIx_RDBR register are allowed at any time.DMA requests are generated when the DMA FIFO is not empty (when TIMOD=b#10), or when the DMA FIFO is not full (when TIMOD=b#11).Error interrupts are generated when there is an RBSY overflow error condi-tion (when TIMOD=b#10).A master SPI DMA sequence may involve back-to-back transmissionand/or reception of multiple DMA work units. The SPI controller sup-ports such a sequence with minimal core interaction.Slave Mode DMA OperationWhen enabled as a slave with the DMA engine configured to transmit or receive data, the start of a transfer is triggered by a transition of the SPIxSS signal to the active-low state or by the first active edge of SPIxSCK,depending on the state of CPHA.ADSP-BF54x Blackfin Processor Hardware ReferenceSPI-Compatible Port ControllersSPI RegistersThe SPI peripheral includes a number of user-accessible registers. Some of these registers are also accessible through the DMA bus. Four registers contain control and status information: SPIx_BAUD, SPIx_CTL, SPIx_FLG, and SPIx_STAT. Two registers are used for buffering receive and transmit data: SPIx_RDBR and SPIx_TDBR. For more information aboutDMA-related registers see Chapter7, “Direct Memory Access”.See “Error Signals and Flags” on page22-23 for more information about how the bits in these registers are used to signal errors and otherconditions.Table22-8 shows the functions of the SPI registers. Figure22-12 through Figure22-18 on page22-49 provide details.Table 22-8. SPI RegistersRegister Name Description NotesSPIx_BAUD SPIx port baud rateregisters on page22-44Value of 0 or 1 disables the serial clockSPIx_CTL SPIx port controlregisters on page22-45SPE and MSTR bits can also be modified by hardware (when MODF is set)SPIx_FLG SPIx port flagregisters on page22-46Bits 0 and 8 are reservedSPIx_STAT SPIx port status registerson page22-48SPIF bit can be set by clearing SPE in SPIx_CTLSPIx_TDBR SPIx port transmit databuffer registerson page22-48Register contents can also be modified by hard-ware (by DMA and/or when SZ = 1 inSPIx_CTL)SPIx_RDBR SPIx port receive databuffer registerson page22-49When register is read, hardware events can be trig-geredSPIx_SHADOW SPIx port RDBR shadowregisters on page22-49Register has the same contents as SPIx_RDBR, but no action is taken when it is readADSP-BF54x Blackfin Processor Hardware Reference。

FPGA可编程逻辑器件芯片EP1C6F256C8N中文规格书

Interface OverviewADSP-BF54x Blackfin Processor Hardware ReferenceThe CAN mailbox identification (CANx_MBxx_ID0/1) register pair includes:•The 29 bit identifier (base part BASEID plus extended partEXTID_LO/HI )•The acceptance mask enable bit (AME )•The remote transmission request bit (RTR )•The identifier extension bit (IDE )Do not write to the identifier of a message object while the mailboxis enabled for the CAN module (the corresponding bit in CANx_MCx is set).The other mailbox area registers are:•The data length code (DLC ) in CANx_MBxx_LENGTH . The upper 12bits of CANx_MBxx_LENGTH of each mailbox are marked as reserved.These 12 bits should always be set to 0.•Up to eight bytes for the data field, sent MSB first from the CANx_MBxx_DATA3/2/1/0 registers, respectively, based on the number of bytes defined in the DLC . For example, if only one byte is trans-mitted or received (DLC = 1), then it is stored in the mostsignificant byte of the CANx_MBxx_DATA3 register.•Two bytes for the time stamp value (TSV ) in theCANx_MBxx_TIMESTAMP registerThe final registers in the mailbox area are the acceptance mask registers (CANx_AMxxH and CANx_AMxxL ). The acceptance mask is enabled when the AME bit is set in the CANx_MBxx_ID1 register. If the “filtering on data field” option is enabled (DNM = 1 in the CANx_CONTROL register and FDF = 1 in the corresponding acceptance mask), the EXTID_HI[15:0] bits ofCANx_MBxx_ID0 are reused as acceptance code (DFC ) for the data field filter-ing. For more information, see “Receive Operation” on page 31-16.CAN OperationADSP-BF54x Blackfin Processor Hardware ReferenceAs could be concluded with regards to the RTR field, a dominant bit in the IDE field wins arbitration against an extended frame with the same lower 11-bits, therefore, standard frames are higher priority than extended frames. The substitute remote request bit (SRR , always sent as recessive),the reserved bits r0 and r1 (always sent as dominant), and the checksum (CRC ) are generated automatically by the internal logic.CAN OperationThe CAN controller is in configuration mode when coming out of proces-sor reset or hibernate. It is only when the CAN is in configuration mode that hardware behavior can be altered. Before initializing the mailboxes themselves, the CAN bit timing must be set up to work on the CAN bus that the controller is expected to connect to.Bit TimingThe CAN controller does not have a dedicated clock. Instead, the CAN clock is derived from the system clock (SCLK ) based on a configurable number of time quanta. The Time Quantum (TQ) is derived from the formula TQ = (BRP +1)/SCLK , where BRP is the 10-bit BRP field in the CANx_CLOCK register. Although the BRP field can be set to any value, it is recommended that the value be greater than or equal to 4, as restrictions apply to the bit timing configuration when BRP is less than 4.The CANx_CLOCK register defines the TQ value, and multiple time quanta make up the duration of a CAN bit on the bus. The CANx_TIMING register controls the nominal bit time and the sample point of the individual bitsFigure 31-6. Extended CAN Frame。

FPGA开发板EP1C6(二版)

使用手册目录综述 (1)EP1C6核心板资源介绍 (1)FPGA开发平台资源介绍 (3)系统模块 (6)EP1C6核心板模块说明FPGA EP1C6Q240C8芯片说明 (9)F P G A接口I/O说明 (9)调试接口JTAG、AS说明 (16)其它功能模块 (18)E P1C6核心板使用注意事项 (20)FPGA开发平台模块说明液晶显示模块 (22)RTC实时时钟模块 (23)USB接口模块 (24)音频CODEC接口模块 (26)EEPROM存储模块 (30)数字温度传感器模块 (31)其它功能模块 (31)F P G A开发平台使用注意事项 (32)附表一核心板载资源与FPGAEP1C6I/O接口对照表 (107)附表二E P1C6与开发板硬件资源I/O接口对照表 (111)第一章综述FPGA开发来台是根据现代电子发展的方向,集EDA和SOPC系统开发为一体的综合性实验开发系统,除了满足高校专、本科生和研究生的SOPC教学实验开发之外,也是电子设计和电子项目开发的理想工具。

整个开发系统由核心板EP1C6、SOPC开发平台和扩展板构成,根据用户不同的需求配置成不同的开发系统。

EP1C6核心板EP1C6核心板为基于Altera Cyclone器件的嵌入式系统开发提供了一个很好的硬件平台,它可以为开发人员提供以下资源:1主芯片采用Altera Cyclone器件EP1C6Q240C82EPCS1I8配置芯片34个用户自定义按键44个用户自定义LED51个七段码LED6标准AS编程接口和JTAG调试接口750MHz高精度时钟源8三个高密度扩展接口9系统上电复位电路10支持+5V直接输入,板上电源管理模块系统主芯片采用240引脚、贴片封装的E1C6FPGA,它拥有6030个LE,26个M4K片上RAM(共计239616bits),2个高性能PLL以及多达185个用户自定义IO。

同时,系统还可以根据用户不同的设计需求来更换其它不同系列的核心板,如:EP1C12、EP2C20、EP3C25等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1

Cyclone FPGA Family Data Sheet

Preliminary Information

Cyclone devices are available in quad flat pack (QFP) and space-saving FineLine BGA packages (see Tables 2 through 3). Table 2. Cyclone Package Options & I/O Pin Counts Device 100-Pin TQFP (1)

EP1C3

2,910 13 59,904 1 104

பைடு நூலகம்

EP1C4

4,000 17 78,336 2 301

EP1C6

5,980 20 92,160 2 185

EP1C12

12,060 52 239,616 2 249

EP1C20

20,060 64 294,912 2 301

Altera Corporation

65

144-Pin TQFP (1), (2)

104

240-Pin PQFP (1)

256-Pin FineLine BGA

324-Pin FineLine BGA

400-Pin FineLine BGA

EP1C3 EP1C4 EP1C6 EP1C12 EP1C20 Notes to Table 2:

Preliminary Information

Cyclone FPGA Family Data Sheet

Table of Contents