数字集成电路--电路、系统与设计(第二版)复习资料

数字电子技术(第二版)复习题册答案

《数字电子技术(第二版)》习题册部分参考答案课题一认识数字电路任务一认识数制与数制转换一、填空题1.时间数值 1 02.1 8 153.1 128 2554.75.96.16二、选择题1.C 2.B 3.C 4.B 5.C 6.A 7.D三、判断题1.√ 2.√ 3.× 4.× 5.√ 6.× 7.√ 8.√ 9.×四、问答题1.答:数字电路中的信号为高电平或低电平两种状态,它正好与二进制的1和0相对应,因此,采用二进制更加方便和实用。

2.答:十六进制具有数据读写方便,与二进制相互转换简单,较直观地表示位状态等优点。

五、计算题1.(1)7 (2)15 (3)31 (4)2132.(1)[1010]2 (2)[1 0000]2(3)[100 0000 0000]2 (4)[100 0000 0110]23.(1)[27]8(2)[35]8(3)[650]8(4)[3153]84.(1)[010 111]2(2)[001 101 110]2(3)[010 000 000]2(4)[001 110 101 101]25.(1)0FH (2)1FH(3)36H (4)0AE63H6.(1)0001 0110 B (2)0010 1010 1110 B(3)1011 1000 1111 1100B (4)0011 1111 1101 0101B任务二学习二进制数算术运算一、填空题1.加减乘除2.0+0=0 0+1=1 1+0=1 1+1=103.0-0=0 1-0=1 1-1=0 10-1=14.0×0=0 0×1=0 1×0=0 1×1=15.1 06.最高正负原码7.字节8.半字节9.字二、选择题1.C 2.B 3.C 4.B 5.B 6.B 7.C三、判断题1.√ 2.× 3.× 4.√四、问答题1.答:将二进制数0011移位至0110,是向左移动一位,应做乘2运算。

数字集成电路考试 知识点

数字集成电路考试知识点一、数字逻辑基础。

1. 数制与编码。

- 二进制、十进制、十六进制的相互转换。

例如,将十进制数转换为二进制数可以使用除2取余法;将二进制数转换为十六进制数,可以每4位二进制数转换为1位十六进制数。

- 常用编码,如BCD码(8421码、余3码等)。

BCD码是用4位二进制数来表示1位十进制数,8421码是一种有权码,各位的权值分别为8、4、2、1。

2. 逻辑代数基础。

- 基本逻辑运算(与、或、非)及其符号表示、真值表和逻辑表达式。

例如,与运算只有当所有输入为1时,输出才为1;或运算只要有一个输入为1,输出就为1;非运算则是输入和输出相反。

- 复合逻辑运算(与非、或非、异或、同或)。

异或运算的特点是当两个输入不同时输出为1,相同时输出为0;同或则相反。

- 逻辑代数的基本定理和规则,如代入规则、反演规则、对偶规则。

利用这些规则可以对逻辑表达式进行化简和变换。

- 逻辑函数的化简,包括公式化简法和卡诺图化简法。

卡诺图化简法是将逻辑函数以最小项的形式表示在卡诺图上,通过合并相邻的最小项来化简逻辑函数。

二、门电路。

1. 基本门电路。

- 与门、或门、非门的电路结构(以CMOS和TTL电路为例)、电气特性(如输入输出电平、噪声容限等)。

CMOS门电路具有功耗低、集成度高的优点;TTL门电路速度较快。

- 门电路的传输延迟时间,它反映了门电路的工作速度,从输入信号变化到输出信号稳定所需要的时间。

2. 复合门电路。

- 与非门、或非门、异或门等复合门电路的逻辑功能和实现方式。

这些复合门电路可以由基本门电路组合而成,也有专门的集成电路芯片实现其功能。

三、组合逻辑电路。

1. 组合逻辑电路的分析与设计。

- 组合逻辑电路的分析方法:根据给定的逻辑电路写出逻辑表达式,化简表达式,列出真值表,分析逻辑功能。

- 组合逻辑电路的设计方法:根据逻辑功能要求列出真值表,写出逻辑表达式,化简表达式,画出逻辑电路图。

2. 常用组合逻辑电路。

(整理)集成电路原理学习指南-第二版

沟道等效电阻

(1)与W/L反比,

(2)与电压有关,

(3)VDD大的时候较小(饱和工作区)

(4)VDD接近Vt的时候急剧增大

(5)一般使用工作区平均电阻

掌握

3.18

电阻的近似

平均电阻,并估算其误差(保守估计还是过估计)

掌握

3.19

结构电容

栅电容,覆盖电容

掌握

3.20

沟道电容

在不同工作区域的变化和原因,在阈值附近最小

f=Cext/Cint=Cext/γCg,尺寸决定电容,所以也是扇出尺寸,为工艺决定的系数,代表自电容与栅电容的关系

掌握

5.13

反相器链的最优尺寸设计

每一级为前后级的几何平均

扇出系数公式(5.35),公式(5.36)

掌握

5.14

最佳等效扇出

图5.21(pp 152),一般取4

掌握

5.15

上升下降时间对延时的影响

了解

3.26

电容估算

(1)栅电容,扩散电容大致相当(定义单位NMOS和PMOS的栅电容为C)

(2)它们随沟道宽度等比增加(kC)

(3)最小晶体管C值可初略估计为1fF/um宽度(65nm工艺,宽0.1um晶体管的C值约为0.1fF)

[Weste,4.3.2]

掌握

第四章导线

序号

概念

知识点和关键词

掌握程度

掌握

3.13

MOS IV特性

画出IV图,标出工作区,图3.24(pp 74)

掌握并会定性画图

3.14

手工分析的局限

在电阻区和过度区之间的区域偏差较大

了解

3.15

设计测试点验证IV

知道晶体管几个端口的电压,固定哪个,量哪个电流,可以提取以上列出的某个参数。

数字逻辑与数字集成电路第2版

CATALOGUE

06

平均无故障时间、平均修复时间、可用性等,这些指标用于衡量数字系统的可靠性水平。

采用冗余设计、容错技术、故障检测与恢复机制等手段,提高数字系统的可靠性,确保系统稳定运行。

设计方法

可靠性指标

故障诊断

通过监控系统的运行状态、分析异常数据等方式,快速定位故障原因,为故障排除提供依据。

详细描述

总结词

可编程逻辑器件是一种可以通过编程实现各种数字逻辑功能的集成电路。

详细描述

可编程逻辑器件是一种可以通过编程实现各种数字逻辑功能的集成电路。它由可编程的逻辑门电路组成,用户可以通过编程来配置这些门电路的连接和参数,从而实现所需的数字逻辑功能。常见的可编程逻辑器件包括可编程逻辑阵列(PLA)、可编程门阵列(FPGA)和复杂可编程逻辑器件(CPLD)等。由于其灵活性高、可重复编程的特点,可编程逻辑器件被广泛应用于数字系统设计、数字信号处理和嵌入式系统等领域。

数字系统设计

CATALOGUE

03

将数字系统设计分为逻辑抽象、功能抽象和行为抽象三个层次,以便更好地理解和设计复杂的数字系统。

抽象化设计

从系统总体功能和行为出发,逐步细化设计,直至完成每个最小单元的设计。

自顶向下设计

将复杂的数字系统划分为若干个相对独立、功能明确的模块,便于设计、调试和维护。

模块化设计

数字逻辑与数字集成电路第2版

contents

目录

数字逻辑基础数字电路基础数字系统设计数字信号处理数字通信与网络数字系统安全与可靠性

数字逻辑基础

CATALOGUE

01

03

逻辑表达式的化简

通过逻辑代数的基本定理和运算规则,将复杂的逻辑表达式化简为简单的形式,便于分析和理解。

数字集成电路--电路、系统与设计(第二版)课后练习题 第六章 CMOS组合逻辑门的设计

Chapter 6 Problem Set

Chapter 6 PROBLEMS

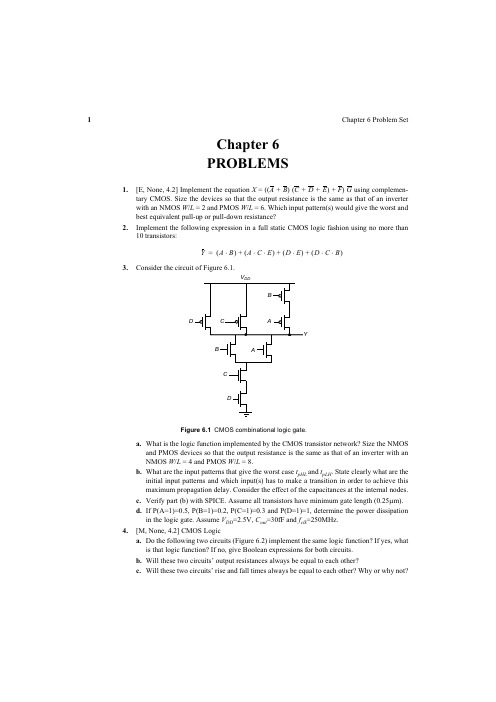

1. [E, None, 4.2] Implement the equation X = ((A + B) (C + D + E) + F) G using complementary CMOS. Size the devices so that the output resistance is the same as that of an inverter with an NMOS W/L = 2 and PMOS W/L = 6. Which input pattern(s) would give the worst and best equivalent pull-up or pull-down resistance? Implement the following expression in a full static CMOS logic fashion using no more than 10 transistors: Y = (A ⋅ B) + (A ⋅ C ⋅ E) + (D ⋅ E) + (D ⋅ C ⋅ B) 3. Consider the circuit of Figure 6.1.

2

VDD E 6 A A 6 B 6 C 6 D 6 E F A B C D 4 4 4 4 E 1 A B C D 4 4 4 4 E 1 6 F 6 B 6 C 6 D

Chapter 6 Problem Set

VDD 6

Circuit A

Circuit B

Figure 6.2 Two static CMOS gates.

数字集成电路-电路系统与设计第二版课程设计

数字集成电路-电路系统与设计第二版课程设计

一、课程设计介绍

数字集成电路是现代电路设计中的重要组成部分,也是计算机科学与工程的重要分支。

本课程设计旨在通过对数字集成电路的系统与设计进行探究,并结合具体的案例来设计和实现数字集成电路,使学生能够熟悉数字集成电路的基本原理、设计方法和实现技术。

本课程设计主要包含以下内容:

1.数值系统和编码

2.逻辑功能设计:组合逻辑电路和时序逻辑电路

3.集成电路设计方法和流程

4.VHDL和FPGA实现数字逻辑电路

5.数字信号处理器

通过本次课程设计,学生将掌握数字集成电路的系统性设计思路和实现方法,具备数字电路设计的基本能力和实际操作技术,能够针对具体应用场景提出解决方案,实现数字电路的设计、验证和调试。

二、课程设计要求

1. 课程设计题目

本次课程设计的题目为“4位计数器设计”。

2. 软件工具

VHDL编程软件和EDA工具

1。

【精品】数字集成电路电路、系统与设计第二版课后练习题第六章CMOS组合逻辑门的设计

【精品】数字集成电路--电路、系统与设计(第二版)课后练习题第六章CMOS组合逻辑门的设计第六章 CMOS组合逻辑门的设计1.为什么CMOS电路逻辑门的输入端和输出端都要连接到电源电压?CMOS电路采用了MOSFET(金属氧化物半导体场效应管)作为开关元件,其中N沟道MOSFET(NMOS)和P沟道MOSFET(PMOS)分别用于实现逻辑门的输入和输出。

NMOS和PMOS都需要连接到电源电压,以使其能够正常工作。

输入端连接到电源电压可以确保信号在逻辑门中正常传递,输出端连接到电源电压可以确保输出信号的正确性和稳定性。

2.为什么在CMOS逻辑门中要使用两个互补的MOSFET?CMOS逻辑门中使用两个互补的MOSFET是为了实现高度抗干扰的逻辑功能。

其中,NMOS和PMOS分别用于实现逻辑门的输入和输出。

NMOS和PMOS的工作原理互补,即当NMOS导通时,PMOS截止,当PMOS导通时,NMOS截止。

这样的设计可以在逻辑门的输出上提供高电平和低电平的稳定性,从而提高逻辑门的抗干扰能力。

3.CMOS逻辑门的输入电压范围是多少?CMOS逻辑门的输入电压范围通常是在0V至电源电压之间,即在低电平和高电平之间。

在CMOS逻辑门中,低电平通常定义为输入电压小于0.3Vdd(电源电压的30%),而高电平通常定义为输入电压大于0.7Vdd(电源电压的70%)。

4.如何设计一个基本的CMOS逻辑门?一个基本的CMOS逻辑门可以由一个NMOS和一个PMOS组成。

其中,NMOS的源极连接到地,栅极连接到逻辑门的输入,漏极连接到PMOS的漏极;PMOS的源极连接到电源电压,栅极连接到逻辑门的输入,漏极连接到输出。

这样的设计可以实现逻辑门的基本功能。

5.如何提高CMOS逻辑门的速度?可以采取以下方法来提高CMOS逻辑门的速度:•减小晶体管的尺寸:缩小晶体管的尺寸可以减小晶体管的电容和电阻,从而提高逻辑门的响应速度。

•优化电源电压:增加电源电压可以提高晶体管的驱动能力,从而加快逻辑门的开关速度。

数字集成电路--电路、系统与设计(第二版)课后练习题第六.

数字集成电路--电路、系统与设计(第⼆版)课后练习题第六.Digital Integrated Circuits - 2nd Ed 11 DESIGN PROJECT Design, lay out, and simulate a CMOS four-input XOR gate in the standard 0.25 micron CMOS process. You can choose any logic circuit style, and you are free to choose how many stages of logic to use: you could use one large logic gate or a combination of smaller logic gates. The supply voltage is set at 2.5 V! Your circuit must drive an external 20 fF load in addition to whatever internal parasitics are present in your circuit. The primary design objective is to minimize the propagation delay of the worst-case transition for your circuit. The secondary objective is to minimize the area of the layout. At the very worst, your design must have a propagation delay of no more than 0.5 ns and occupy an area of no more than 500 square microns, but the faster and smaller your circuit, the better. Be aware that, when using dynamic logic, the precharge time should be made part of the delay. The design will be graded on themagnitude of A × tp2, the product of the area of your design and the square of the delay for the worst-case transition.。

数字集成电路复习要点

数字集成电路复习要点⼀、简答题1.集成电路发展的特点:速度变快,I/O增多,⼯作电压下降……A,特征尺⼨越来越⼩,B,单个芯⽚晶体管数⽬越来越多,速度越来越快,电压越来越⼩,层数越来越多,端⼝越来越多,功耗越来越低2.P181⼤扇⼊的“设计技术”。

A,调整晶体管尺⼨B,逐级加⼤晶体管尺⼨C,重新安排输⼊D,重组逻辑结构(把光键路径上的晶体管靠近门的输出端)3.简述集成电路⼯艺中典型的光刻步骤及其相互关系。

(P28)氧化层,涂光刻胶,光刻机曝光,光刻胶的显影和烘⼲,酸刻蚀,旋转清洗和⼲燥,各种⼯艺加⼯步骤,去除光刻胶4.什么是多晶⾃对准⼯艺,有哪些优点?(P32)在掺杂之前形成图形的多晶硅栅实际确定了沟道区的确切位置,从⽽也确定了源区和漏区的位置。

它使源和漏这两个区域相对于栅具有⾮常精确的位置,有助于减⼩晶体管中的寄⽣电容。

5.CMOS逻辑门特性:(全摆幅,⽆⽐性,低输出阻抗,⾼输⼊阻抗,⽆静态功耗。

)A,电压摆幅等于电源电压,噪声容很⼤,B,逻辑电平与器件的相对尺⼨⽆关,⽆⽐逻辑,C,具有低输出阻抗,⾼输⼊阻抗,D,不消耗任何静态功率6.伪NCMOS门逻辑的特点A,减少晶体管的数⽬,由2N减到N+1,B,速度快缺点:⼩的噪声容限和⼤的静态功耗6.传输管逻辑的优点是什么?有哪些缺点,解决的办法是什么?优点:结构简单,阀值损失⼩,硬件开销⼩缺点:延时⾼,仅含NMOS的传输管将引起静态功耗并减⼩噪声容限解决办法:避免开关长串联以减⼩延时,增加电平恢复晶体管以消除静态功耗7.什么是时钟馈通,有何危害?(P215)原理:电容耦合的特殊情况,由在预充电器件的时钟输⼊和动态输出节点之间电容耦合引起的效应,当下拉⽹络不导通时,这⼀电容耦合会在时钟由低⾄⾼翻转时,引起的动态节点输出上升到VDD以上;⽽快速上升和下降时时钟边沿会耦合到信号节点上。

特点:a)可能使预充电管正常情况下反偏结⼆极管变为正向偏置,使电⼦注⼊到衬底中,被附近处于⾼电平的⾼阻节点收集,导致出错。

数字集成电路--电路、系统与设计

数字集成电路是现代电子产品中不可或缺的一部分,它们广泛应用于计算机、手机、汽车、医疗设备等领域。

数字集成电路通过在芯片上集成大量的数字电子元件,实现了电子系统的高度集成和高速运算。

本文将从电路、系统与设计三个方面探讨数字集成电路的相关内容。

一、数字集成电路的电路结构数字集成电路的电路结构主要包括逻辑门、寄存器、计数器等基本元件。

其中,逻辑门是数字集成电路中最基本的构建元件,包括与门、或门、非门等,通过逻辑门的组合可以实现各种复杂的逻辑功能。

寄存器是用于存储数据的元件,通常由触发器构成;而计数器则可以实现计数和计时功能。

这些基本的电路结构构成了数字集成电路的基础,为实现各种数字系统提供了必要的支持。

二、数字集成电路与数字系统数字集成电路是数字系统的核心组成部分,数字系统是以数字信号为处理对象的系统。

数字系统通常包括输入输出接口、控制单元、运算器、存储器等部分,数字集成电路在其中充当着处理和控制信号的角色。

数字系统的设计需要充分考虑数字集成电路的特性,包括时序和逻辑的正确性、面积和功耗的优化等方面。

数字集成电路的发展也推动了数字系统的不断完善和创新,使得数字系统在各个领域得到了广泛的应用。

三、数字集成电路的设计方法数字集成电路的设计过程通常包括需求分析、总体设计、逻辑设计、电路设计、物理设计等阶段。

需求分析阶段需要充分了解数字系统的功能需求,并将其转化为具体的电路规格。

总体设计阶段需要根据需求分析的结果确定电路的整体结构和功能分配。

逻辑设计阶段是将总体设计转化为逻辑电路图,其中需要考虑逻辑函数、时序关系、并行性等问题。

电路设计阶段是将逻辑电路图转化为电路级电路图,包括门电路的选择和优化等。

物理设计阶段则是将电路级电路图转化为实际的版图设计,考虑布线、功耗、散热等问题。

在每个设计阶段都需要充分考虑电路的性能、面积、功耗等指标,以实现设计的最优化。

结语数字集成电路作为现代电子系统的关键组成部分,对于数字系统的功能和性能起着至关重要的作用。

数字集成电路--电路、系统与设计(第二版)课后练习题-第四章 导线-Chapter 4 The Wire

1Chapter 4 Problem SetChapter 4Problems1.[M, None, 4.x] Figure 0.1 shows a clock-distribution network. Each segment of the clock net-work (between the nodes) is 5 mm long, 3 μm wide, and is implemented in polysilicon. Ateach of the terminal nodes (such as R ) resides a load capacitance of 100 fF.a.Determine the average current of the clock driver, given a voltage swing on the clock linesof 5 V and a maximum delay of 5 nsec between clock source and destination node R . Forthis part, you may ignore the resistance and inductance of the networkb.Unfortunately the resistance of the polysilicon cannot be ignored. Assume that eachstraight segment of the network can be modeled as a Π-network. Draw the equivalent cir-cuit and annotate the values of resistors and capacitors.c.Determine the dominant time-constant of the clock response at node R .2.[C, SPICE, 4.x] You are designing a clock distribution network in which it is critical to mini-mize skew between local clocks (CLK 1, CLK 2, and CLK 3). You have extracted the RC net-work of F igure 0.2, which models the routing parasitics of your clock line. Initially, you notice that the path to CLK 3 is shorter than to CLK 1 or CLK 2. In order to compensate for this imbalance, you insert a transmission gate in the path of CLK 3 to eliminate the skew.a.Write expressions for the time-constants associated with nodes CLK 1,CLK 2 and CLK 3.Assume the transmission gate can be modeled as a resistance R 3.b.If R 1 = R 2 = R 4 = R 5 = R and C 1 = C 2 = C 3 = C 4 = C 5 = C , what value of R 3 is required to balance the delays to CLK 1, CLK 2, and CLK 3?c.For R =750Ω and C =200fF, what (W /L )’s are required in the transmission gate to elimi-nate skew? Determine the value of the propagation delay.d.Simulate the network using SPICE, and compare the obtained results with the manually obtained numbers.3.[M, None, 4.x]Consider a CMOS inverter followed by a wire of length L . Assume that in thereference design, inverter and wire contribute equally to the total propagation delay t pref . Youmay assume that the transistors are velocity-saturated. The wire is scaled in line with the idealwire scaling model . Assume initially that the wire is a local wire .a.Determine the new (total) propagation delay as a a function of t p ref , assuming that technol-ogy and supply voltage scale with a factor 2. Consider only first-order effects.b.Perform the same analysis, assuming now that the wire scales a global wire , and the wire length scales inversely proportional to the technology.Figure 0.1Clock-distribution network.SR2Chapter 4 Problem Setc.Repeat b, but assume now that the wire is scaled along the constant resistance model. You may ignore the effect of the fringing capacitance.d.Repeat b, but assume that the new technology uses a better wiring material that reduces the resistivity by half, and a dielectric with a 25% smaller permittivity.e.Discuss the energy dissipation of part a. as a function of the energy dissipation of the orig-inal design E ref .f.Determine for each of the statements below if it is true, false, or undefined, and explain in one line your answer. - When driving a small fan-out, increasing the driver transistor sizes raises the short-circuit power dissipation. - Reducing the supply voltage, while keeping the threshold voltage constant decreases the short-circuit power dissipation.- Moving to Copper wires on a chip will enable us to build faster adders.- Making a wire wider helps to reduce its RC delay.- Going to dielectrics with a lower permittivity will make RC wire delay more impor-tant.4.[M, None, 4.x] A two-stage buffer is used to drive a metal wire of 1 cm. The first inverter is of minimum size with an input capacitance Ci=10 fF and an internal propagation delay t p0=50 ps and load dependent delay of 5ps/fF. The width of the metal wire is 3.6 μm. The sheet resis-tance of the metal is 0.08 Ω/, the capacitance value is 0.03 fF/μm 2and the fringing field capacitance is 0.04fF/μm.a.What is the propagation delay of the metal wire?pute the optimal size of the second inverter. What is the minimum delay through the buffer?c.If the input to the first inverter has 25% chance of making a 0-to-1 transition, and the whole chip is running at 20MHz with a 2.5 supply voltage, then what’s the power con-sumed by the metal wire?5.[M, None, 4.x]To connect a processor to an external memory an off -chip connection is neces-sary. The copper wire on the board is 15 cm long and acts as a transmission line with a charac-teristic impedance of 100Ω.(See F igure 0.3). The memory input pins present a very highimpedance which can be considered infinite. The bus driver is a CMOS inverter consisting ofvery large devices: (50/0.25) for the NMOS and (150/0.25) for the PMOS, where all sizes areClock CLK 1CLK 2CLK 3R 1R 2R 5R 4R 3Model as:Figure 0.2RC clock-distribution network.driver C 1C 3C 4C 5C 2Digital Integrated Circuits - 2nd Ed3 in μm. The minimum size device, (0.25/0.25) for NMOS and (0.75/0.25) for PMOS, has theon resistance 35 kΩ.a.Determine the time it takes for a change in the signal to propagate from source to destina-tion (time of flight). The wire inductance per unit length equals 75*10-8 H/m.b.Determine how long it will take the output signal to stay within 10% of its final value. Youcan model the driver as a voltage source with the driving device acting as a series resis-tance. Assume a supply and step voltage of 2.5V. Hint: draw the lattice diagram for thetransmission line.c.Resize the dimensions of the driver to minimize the total delay.L=15cmMemoryZ=100ΩFigure 0.3The driver, the connecting copper wire and thememory block being accessed.6.[M, None, 4.x] A two stage buffer is used to drive a metal wire of 1 cm. The first inverter is aminimum size with an input capacitance C i=10 fF and a propagation delay t p0=175 ps whenloaded with an identical gate. The width of the metal wire is 3.6 μm. The sheet resistance ofthe metal is 0.08 Ω/, the capacitance value is 0.03 fF/μm2 and the fringing field capacitanceis 0.04 fF/μm.a.What is the propagation delay of the metal wire?pute the optimal size of the second inverter. What is the minimum delay through thebuffer?7.[M, None, 4.x] For the RC tree given in Figure 0.4 calculate the Elmore delay from node A tonode B using the values for the resistors and capacitors given in the below in Table 0.1.Figure 0.4RC tree for calculating the delay4Chapter 4 Problem SetTable 0.1Values of the components in the RC tree of Figure 0.4Resistor Value(Ω)Capacitor Value(fF)R10.25C1250R20.25C2750R30.50C3250R4100C4250R50.25C51000R6 1.00C6250R70.75C7500R81000C82508.[M, SPICE, 4.x] In this problem the various wire models and their respective accuracies willbe studied.pute the 0%-50% delay of a 500um x 0.5um wire with resistance of 0.08 Ω/,witharea capacitance of 30aF/um2, and fringing capacitance of 40aF/um. Assume the driverhas a 100Ω resistance and negligible output capacitance.•Using a lumped model for the wire.•Using a PI model for the wire, and the Elmore equations to find tau. (see Chapter 4, figure4.26).•Using the distributed RC line equations from Chapter 4, section 4.4.4.pare your results in part a. using spice (be sure to include the source resistance). Foreach simulation, measure the 0%-50% time for the output•First, simulate a step input to a lumped R-C circuit.•Next, simulate a step input to your wire as a PI model.•Unfortunately, our version of SPICE does not support the distributed RC model as described in your book (Chapter 4, section 4.5.1). Instead, simulate a step input to yourwire using a PI3 distributed RC model.9.[M, None, 4.x] A standard CMOS inverter drives an aluminum wire on the first metal layer.Assume Rn=4kΩ, Rp=6kΩ. Also, assume that the output capacitance of the inverter is negli-gible in comparison with the wire capacitance. The wire is .5um wide, and the resistivity is0.08 Ω/..a.What is the "critical length" of the wire?b.What is the equivalent capacitance of a wire of this length? (For your capacitance calcula-tions, use Table 4.2 of your book , assume there’s field oxide underneath and nothingabove the aluminum wire)Digital Integrated Circuits - 2nd Ed510.[M, None, 4.x] A 10cm long lossless transmission line on a PC board (relative dielectric con-stant = 9, relative permeability = 1) with characteristic impedance of 50Ω is driven by a 2.5Vpulse coming from a source with 150Ω resistance.a.If the load resistance is infinite, determine the time it takes for a change at the source toreach the load (time of flight).Now a 200Ω load is attached at the end of the transmission line.b.What is the voltage at the load at t = 3ns?c.Draw lattice diagram and sketch the voltage at the load as a function of time. Determinehow long does it take for the output to be within 1 percent of its final value.11.[C, SPICE, 4.x] Assume V DD =1.5V . Also, use short-channel transistor models forhand analy-sis.a.The Figure 0.5 shows an output driver feeding a 0.2 pF effective fan-out of CMOS gates through a transmission line. Size the two transistors of the driver to optimize the delay.Sketch waveforms of V S and V L , assuming a square wave input. Label critical voltages and times.b.Size down the transistors by m times (m is to be treated as a parameter). Derive a first order expression for the time it takes for V L to settle down within 10% of its final voltage pare the obtained result with the case where no inductance is associated with the wire.Please draw the waveforms of V L for both cases, and comment.e the transistors as in part a). Suppose C L is changed to 20pF. Sketch waveforms of V S and V L , assuming a square wave input. Label critical voltages and instants.d.Assume now that the transmission line is lossy. Perform Hspice simulation for three cases:R=100 Ω/cm; R=2.5 Ω/cm; R=0.5 Ω/cm. Get the waveforms of V S , V L and the middle point of the line. Discuss the results.12.[M, None, 4.x] Consider an isolated 2mm long and 1μm wide M1(Metal1)wire over a silicon substrate driven by an inverter that has zero resistance and parasitic output capccitance. How will the wire delay change for the following cases? Explain your reasoning in each case.a.If the wire width is doubled.b.If the wire length is halved.c.If the wire thickness is doubled.d.If thickness of the oxide between the M1 and the substrate is doubled.13.[E, None, 4.x] In an ideal scaling model, where all dimensions and voltages scale with a fac-tor of S >1 :L=350nH/m 10cm C=150pF/m inV DDV DD V S V LC L =0.2pF Figure 0.5Transmission line between two inverters6Chapter 4 Problem Seta.How does the delay of an inverter scale?b.If a chip is scaled from one technology to another where all wire dimensions,including thevertical one and spacing, scale with a factor of S, how does the wire delayscale? How doesthe overall operating frequency of a chip scale?c.Repeat b) for the case where everything scales, except the vertical dimension of wires (itstays constant).。

《数字集成电路设计》复习提纲

《数字集成电路设计》复习提纲(1-7,10,11章)2011-121. 数字集成电路的成本包括哪几部分?2. 数字门的传播延时是如何定义的?3. 集成电路的设计规则(design rule)有什么作用?4. 什么是MOS晶体管的体效应?什么是沟道长度调制效应?5. 写出一个NMOS晶体管处于截止区、线性区、饱和区的判断条件,以及各工作区的源漏电流表达式(考虑短沟效应即沟道长度调制效应,不考虑速度饱和效应)注:NMOS晶体管的栅、源、漏、衬底分别用G、S、D、B表示。

6. MOS晶体管的本征电容有哪些来源?7. 对于一个CMOS反相器的电压传输特性,请标出A、B、C三点处NMOS管和PMOS管各自处于什么工作区?Vin=0、VDD、VM时,两个管子什么区?V DD8. 在CMOS 反相器中,NMOS 管的平均导通电阻为R eqn ,PMOS 管的平均导通电阻为R eqp ,请写出该反相器的总传播延时定义。

9. 减小一个数字门的延迟的方法有哪些?列出三种,并解释可能存在的弊端。

10. CMOS 电路的功耗有哪三类?这三类功耗分别由什么引起的?11. 同步寄存器的建立时间、维持时间、传播延时的含义是什么?V outV in0.511.522.512. 以下三级反相器链,请问使得总延迟最小的每级反相器的f 是多少?最小的总延迟是多少?假设标准反相器的延迟为t p0。

1C L = 8 C13.(1)用静态互补CMOS 门实现如下功能,画出电路连接图。

Out=AB+CD(2)为使上述逻辑门的延迟与以下尺寸的反相器相同,请给出各晶体管的尺寸。

反相器尺寸:NMOS 管=1,PMOS 管=2。

14. 分析下列动态电路的功能。

OutClkClkAB CM pM e15. 下面的电路是什么功能?16.描述超前进位加法器的基本原理。

17.CLK1和CLK2存在正时钟偏差,即CLK2比CLK1晚。

(1)给出最小时钟周期的约束表达式,考虑时钟偏差。

数字集成电路:电路系统与设计(第二版)

数字集成电路:电路系统与设计(第二版)简介《数字集成电路:电路系统与设计(第二版)》是一本介绍数字集成电路的基本原理和设计方法的教材。

本书的内容覆盖了数字电路的基础知识、逻辑门电路、组合逻辑电路、时序逻辑电路、存储器和程序控制电路等方面。

通过学习本书,读者可以了解数字集成电路的概念、设计方法和实际应用。

目录1.数字电路基础知识 1.1 数字电路的基本概念 1.2 二进制系统与数制转换 1.3 逻辑运算与布尔代数2.逻辑门电路 2.1 与门、或门、非门 2.2 与非门、或非门、异或门 2.3 多输入门电路的设计方法3.组合逻辑电路 3.1 组合逻辑电路的基本原理 3.2 组合逻辑电路的设计方法 3.3 编码器和译码器4.时序逻辑电路 4.1 时序逻辑电路的基本原理 4.2 同步时序电路的设计方法 4.3 异步时序电路的设计方法5.存储器电路 5.1 存储器的基本概念 5.2 可读写存储器的设计方法 5.3 只读存储器的设计方法6.程序控制电路 6.1 程序控制电路的基本概念 6.2 程序控制电路的设计方法 6.3 微程序控制器的设计方法内容概述1. 数字电路基础知识本章主要介绍数字电路的基本概念,包括数字电路与模拟电路的区别、数字信号的表示方法以及数制转换等内容。

此外,还介绍了数字电路中常用的逻辑运算和布尔代数的基本原理。

2. 逻辑门电路逻辑门电路是数字电路中的基本组成单元,本章主要介绍了与门、或门、非门以及与非门、或非门、异或门等逻辑门的基本原理和组成。

此外,还介绍了多输入门电路的设计方法,以及逻辑门电路在数字电路设计中的应用。

3. 组合逻辑电路组合逻辑电路是由逻辑门电路组成的,本章主要介绍了组合逻辑电路的基本原理和设计方法。

此外,还介绍了编码器和译码器的原理和应用,以及在数字电路设计中的实际应用场景。

4. 时序逻辑电路时序逻辑电路是在组合逻辑电路的基础上引入了时序元件并进行时序控制的电路。

本章主要介绍了时序逻辑电路的基本原理和设计方法,包括同步时序电路和异步时序电路的设计。

《集成电路原理与设计》重点内容总结

《集成电路原理与设计》重点内容总结引言集成电路(Integrated Circuit, IC)作为现代电子工程的核心,其设计和制造技术的发展极大地推动了信息技术的进步。

《集成电路原理与设计》课程涵盖了IC设计的基础理论、工艺技术、设计流程和应用实例,对于电子工程领域的学生和专业人士具有重要意义。

第一部分:集成电路基础1.1 集成电路概述集成电路是将大量电子元件(如晶体管、电阻、电容等)集成在一块半导体材料(通常是硅)上的微型电子器件。

IC的出现极大地减小了电子设备的体积,提高了性能,降低了成本。

1.2 半导体物理基础半导体物理是IC设计的基础。

重点内容包括:半导体材料的特性,如硅和锗的电子结构。

PN结的形成和特性。

载流子(电子和空穴)的行为。

半导体中的扩散和漂移现象。

1.3 晶体管原理晶体管是IC中最基本的放大和开关元件。

重点内容包括:双极型晶体管(BJT)和金属氧化物半导体场效应晶体管(MOSFET)的工作原理。

晶体管的电流-电压特性。

晶体管的开关时间和速度。

第二部分:集成电路设计2.1 设计流程IC设计包括前端设计和后端设计两个主要阶段。

重点内容包括:系统规格定义和功能模块划分。

逻辑设计和电路设计。

物理设计,包括布局、布线和验证。

2.2 设计工具和方法IC设计涉及多种计算机辅助设计(CAD)工具和方法。

重点内容包括:硬件描述语言(如VHDL和Verilog)的使用。

逻辑综合和优化技术。

时序分析和仿真。

2.3 工艺技术IC的制造工艺对设计有重要影响。

重点内容包括:CMOS工艺流程。

工艺参数对IC性能的影响。

新型工艺技术,如FinFET和SOI。

第三部分:集成电路应用3.1 数字集成电路数字IC是实现数字逻辑功能的核心。

重点内容包括:门电路和触发器的设计。

算术逻辑单元(ALU)和微处理器的设计。

存储器的设计,如SRAM、DRAM和Flash。

3.2 模拟集成电路模拟IC用于处理模拟信号。

重点内容包括:放大器、滤波器和振荡器的设计。

数字集成电路——电路、系统与设计(第二版)Chapter10_timing

Contamination and Propagation Delays

Settle to a final value

Begin to change

Settle to a final value

Begin to change as the last time D begins to change

Settle to a final value as the last time D settles to a final value

Digital Integrated Circuits A Design Perspective

Chapter10: Timing Issues

EE141

Timing Issues

Timing Issues

10.1 Timing Classification

10.2 Synchronous Design

Datapath Structure with Feedback

- Routing the clock so that only negative skew occurs is not feasible

- Design of a low-skew clock network is essential

10.2.5 Clock Distribution Techniques

10.3 Summary

EE141

Timing Issues

Sequencing Methods

Registers

2-Phase Latches

EE141

Timing Issues

Timing Diagrams

数字集成电路--电路、系统与设计(第二版)复习资料

第一章 数字集成电路介绍第一个晶体管,Bell 实验室,1947第一个集成电路,Jack Kilby ,德州仪器,1958 摩尔定律:1965年,Gordon Moore 预言单个芯片上晶体管的数目每18到24个月翻一番。

(随时间呈指数增长)抽象层次:器件、电路、门、功能模块和系统 抽象即在每一个设计层次上,一个复杂模块的内部细节可以被抽象化并用一个黑匣子或模型来代替。

这一模型含有用来在下一层次上处理这一模块所需要的所有信息。

固定成本(非重复性费用)与销售量无关;设计所花费的时间和人工;受设计复杂性、设计技术难度以及设计人员产出率的影响;对于小批量产品,起主导作用。

可变成本 (重复性费用)与产品的产量成正比;直接用于制造产品的费用;包括产品所用部件的成本、组装费用以及测试费用。

每个集成电路的成本=每个集成电路的可变成本+固定成本/产量。

可变成本=(芯片成本+芯片测试成本+封装成本)/最终测试的成品率。

一个门对噪声的灵敏度是由噪声容限NM L (低电平噪声容限)和NM H (高电平噪声容限)来度量的。

为使一个数字电路能工作,噪声容限应当大于零,并且越大越好。

NM H = V OH - V IH NM L = V IL - V OL 再生性保证一个受干扰的信号在通过若干逻辑级后逐渐收敛回到额定电平中的一个。

一个门的VTC 应当具有一个增益绝对值大于1的过渡区(即不确定区),该过渡区以两个有效的区域为界,合法区域的增益应当小于1。

理想数字门 特性:在过渡区有无限大的增益;门的阈值位于逻辑摆幅的中点;高电平和低电平噪声容限均等于这一摆幅的一半;输入和输出阻抗分别为无穷大和零。

传播延时、上升和下降时间的定义传播延时tp 定义了它对输入端信号变化的响应有多快。

它表示一个信号通过一个门时所经历的延时,定义为输入和输出波形的50%翻转点之间的时间。

上升和下降时间定义为在波形的10%和90%之间。

对于给定的工艺和门的拓扑结构,功耗和延时的乘积一般为一常数。

数字集成电路--电路、系统与设计(第二版)课后练习题 第五章 CMOS反相器

C H A P T E R5T H E C M O S I N V E R T E R Quantification of integrity,performance,and energy metrics of an inverterOptimization of an inverter design5.1Exercises and Design Problems5.2The Static CMOS Inverter—An IntuitivePerspective5.3Evaluating the Robustness of the CMOSInverter:The Static Behavior5.3.1Switching Threshold5.3.2Noise Margins5.3.3Robustness Revisited5.4Performance of CMOS Inverter:The DynamicBehavior5.4.1Computing the Capacitances5.4.2Propagation Delay:First-OrderAnalysis5.4.3Propagation Delay from a DesignPerspective5.5Power,Energy,and Energy-Delay5.5.1Dynamic Power Consumption5.5.2Static Consumption5.5.3Putting It All Together5.5.4Analyzing Power Consumption UsingSPICE5.6Perspective:Technology Scaling and itsImpact on the Inverter Metrics180Section 5.1Exercises and Design Problems 1815.1Exercises and Design Problems1.[M,SPICE,3.3.2]The layout of a static CMOS inverter is given in Figure 5.1.(λ=0.125µm).a.Determine the sizes of the NMOS and PMOS transistors.b.Plot the VTC (using HSPICE)and derive its parameters (V OH ,V OL ,V M ,V IH ,and V IL ).c.Is the VTC affected when the output of the gates is connected to the inputs of 4similargates?.d.Resize the inverter to achieve a switching threshold of approximately 0.75V .Do not lay-out the new inverter,use HSPICE for your simulations.How are the noise margins affected by this modification?2.Figure 5.2shows a piecewise linear approximation for the VTC.The transition region isapproximated by a straight line with a slope equal to the inverter gain at V M .The intersectionof this line with the V OH and the V OL lines defines V IH and V IL .a.The noise margins of a CMOS inverter are highly dependent on the sizing ratio,r =k p /k n ,of the NMOS and PMOS e HSPICE with V Tn =|V Tp |to determine the valueof r that results in equal noise margins?Give a qualitative explanation.b.Section 5.3.2of the text uses this piecewise linear approximation to derive simplifiedexpressions for NM H and NM L in terms of the inverter gain.The derivation of the gain isbased on the assumption that both the NMOS and the PMOS devices are velocity saturatedat V M .For what range of r is this assumption valid?What is the resulting range of V M ?c.Derive expressions for the inverter gain at V M for the cases when the sizing ratio is justabove and just below the limits of the range where both devices are velocity saturated.What are the operating regions of the NMOS and the PMOS for each case?Consider theeffect of channel-length modulation by using the following expression for the small-signalresistance in the saturation region:r o,sat =1/(λI D ).Figure 5.1CMOS inverter layout.InOutGND V DD =2.5V.Poly Metal1NMOSPMOSPolyMetal12λ182THE CMOS INVERTER Chapter 53.[M,SPICE,3.3.2]Figure 5.3shows an NMOS inverter with resistive load.a.Qualitatively discuss why this circuit behaves as an inverter.b.Find V OH and V OL calculate V IH and V IL .c.Find NM L and NM H ,and plot the VTC using HSPICE.d.Compute the average power dissipation for:(i)V in =0V and (ii)V in =2.5Ve HSPICE to sketch the VTCs for R L =37k,75k,and 150k on a single graph.ment on the relationship between the critical VTC voltages (i.e.,V OL ,V OH ,V IL ,V IH )and the load resistance,R L .g.Do high or low impedance loads seem to produce more ideal inverter characteristics?4.[E,None,3.3.3]For the inverter of Figure 5.3and an output load of 3pF:a.Calculate t plh ,t phl ,and t p .b.Are the rising and falling delays equal?Why or why not?pute the static and dynamic power dissipation assuming the gate is clocked as fast as possible.5.The next figure shows two implementations of MOS inverters.The first inverter uses onlyNMOS transistors.V OH V OL inV outFigure 5.2A different approach to derive V IL and V IH .V outV in M 1W/L =1.5/0.5+2.5VFigure 5.3Resistive-load inverterR L =75k ΩSection 5.1Exercises and Design Problems183a.Calculate V OH ,V OL ,V M for each case.e HSPICE to obtain the two VTCs.You must assume certain values for the source/drain areas and perimeters since there is no layout.For our scalable CMOS process,λ =0.125μm,and the source/drain extensions are 5λfor the PMOS;for the NMOS the source/drain contact regions are 5λx5λ.c.Find V IH ,V IL ,NM L and NM H for each inverter and comment on the results.How can you increase the noise margins and reduce the undefined region?ment on the differences in the VTCs,robustness and regeneration of each inverter.6.Consider the following NMOS inverter.Assume that the bulk terminals of all NMOS deviceare connected to GND.Assume that the input IN has a 0V to 2.5V swing.a.Set up the equation(s)to compute the voltage on node x .Assume γ=0.5.b.What are the modes of operation of device M2?Assume γ=0.c.What is the value on the output node OUT for the case when IN =0V?Assume γ=0.d.Assuming γ=0,derive an expression for the switching threshold (V M )of the inverter.Recall that the switching threshold is the point where V IN =V OUT .Assume that the devicesizes for M1,M2and M3are (W/L)1,(W/L)2,and (W/L)3respectively.What are the limitson the switching threshold?For this,consider two cases:i)(W/L)1>>(W/L)2V DD =2.5V V IN V OUTV DD =2.5V V IN V OUT M 2M 1M 4M 3W/L=0.375/0.25W/L=0.75/0.25W/L=0.375/0.25W/L=0.75/0.25Figure 5.4Inverter ImplementationsV DD =2.5V OUTM1IN M2M3V DD =2.5Vx184THE CMOS INVERTER Chapter 5ii)(W/L)2>>(W/L)17.Consider the circuit in Figure 5.5.Device M1is a standard NMOS device.Device M2has allthe same properties as M1,except that its device threshold voltage is negative and has a valueof -0.4V.Assume that all the current equations and inequality equations (to determine themode of operation)for the depletion device M2are the same as a regular NMOS.Assume thatthe input IN has a 0V to 2.5V swing.a.Device M2has its gate terminal connected to its source terminal.If V IN =0V ,what is the output voltage?In steady state,what is the mode of operation of device M2for this input?pute the output voltage for V IN =2.5V .You may assume that V OUT is small to simplify your calculation.In steady state,what is the mode of operation of device M2for this input?c.Assuming Pr (IN =0)=0.3,what is the static power dissipation of this circuit?8.[M,None,3.3.3]An NMOS transistor is used to charge a large capacitor,as shown in Figure5.6.a.Determine the t pLH of this circuit,assuming an ideal step from 0to 2.5V at the input node.b.Assume that a resistor R S of 5k Ωis used to discharge the capacitance to ground.Deter-mine t pHL .c.Determine how much energy is taken from the supply during the charging of the capacitor.How much of this is dissipated in M1.How much is dissipated in the pull-down resistanceduring discharge?How does this change when R S is reduced to 1k Ω.d.The NMOS transistor is replaced by a PMOS device,sized so that k p is equal to the k n ofthe original NMOS.Will the resulting structure be faster?Explain why or why not.9.The circuit in Figure 5.7is known as the source follower configuration.It achieves a DC levelshift between the input and the output.The value of this shift is determined by the current I 0.Assume x d =0,γ=0.4,2|φf |=0.6V ,V T 0=0.43V ,k n ’=115μA/V 2and λ=0.V DD =2.5VOUTM1(4μm/1μm)IN M2(2μm/1μm),V Tn =-0.4VFigure 5.5A depletion load NMOSinverterV DD =2.5VOutFigure 5.6Circuit diagram with annotated W/L ratios=5pFSection 5.1Exercises and Design Problems 185a.Suppose we want the nominal level shift between V i and V o to be 0.6V in the circuit in Figure 5.7(a).Neglecting the backgate effect,calculate the width of M2to provide this level shift (Hint:first relate V i to V o in terms of I o ).b.Now assume that an ideal current source replaces M2(Figure 5.7(b)).The NMOS transis-tor M1experiences a shift in V T due to the backgate effect.Find V T as a function of V o for V o ranging from 0to 2.5V with 0.5V intervals.Plot V T vs.V oc.Plot V o vs.V i as V o varies from 0to 2.5V with 0.5V intervals.Plot two curves:one neglecting the body effect and one accounting for it.How does the body effect influence the operation of the level converter?d.At V o (with body effect)=2.5V,find V o (ideal)and thus determine the maximum error introduced by the body effect.10.For this problem assume:V DD =2.5V ,W P /L =1.25/0.25,W N /L =0.375/0.25,L =L eff =0.25μm (i.e.x d =0μm),C L =C inv-gate ,k n ’=115μA/V 2,k p ’=-30μA/V 2,V tn0=|V tp0|=0.4V,λ =0V -1, γ=0.4,2|φf |=0.6V ,and t ox =e the HSPICE model parameters for parasitic capacitance given below (i.e.C gd0,C j ,C jsw ),and assume that V SB =0V for all problems except part (e).Figure 5.7NMOS source follower configuration V DD =2.5V V iV oV DD =2.5VV i V oV bias =(a)(b)I o1um/0.25um M1186THE CMOS INVERTER Chapter 5##Parasitic Capacitance Parameters (F/m)##NMOS:CGDO=3.11x10-10,CGSO=3.11x10-10,CJ=2.02x10-3,CJSW=2.75x10-10PMOS:CGDO=2.68x10-10,CGSO=2.68x10-10,CJ=1.93x10-3,CJSW=2.23x10-10a.What is the V m for this inverter?b.What is the effective load capacitance C Leff of this inverter?(include parasitic capacitance,refer to the text for K eq and m .)Hint:You must assume certain values for the source/drain areas and perimeters since there is no layout.For our scalable CMOS process,λ =0.125μm,and the source/drain extensions are 5λfor the PMOS;for the NMOS the source/drain contact regions are 5λx5λ.c.Calculate t PHL ,t PLH assuming the result of (b)is ‘C Leff =6.5fF’.(Assume an ideal step input,i.e.t rise =t fall =0.Do this part by computing the average current used to charge/dis-charge C Leff .)d.Find (W p /W n )such that t PHL =t PLH .e.Suppose we increase the width of the transistors to reduce the t PHL ,t PLH .Do we get a pro-portional decrease in the delay times?Justify your answer.f.Suppose V SB =1V,what is the value of V tn ,V tp ,V m ?How does this qualitatively affect C Leff ?ing Hspice answer the following questions.a.Simulate the circuit in Problem 10and measure t P and the average power for input V in :pulse(0V DD 5n 0.1n 0.1n 9n 20n),as V DD varies from 1V -2.5V with a 0.25V interval.[t P =(t PHL +t PLH )/2].Using this data,plot ‘t P vs.V DD ’,and ‘Power vs.V DD ’.Specify AS,AD,PS,PD in your spice deck,and manually add C L =6.5fF.Set V SB =0Vfor this problem.b.For Vdd equal to 2.5V determine the maximum fan-out of identical inverters this gate candrive before its delay becomes larger than 2ns.c.Simulate the same circuit for a set of ‘pulse’inputs with rise and fall times of t in_rise,fall =1ns,2ns,5ns,10ns,20ns.For each input,measure (1)the rise and fall times t out_rise andV DD =2.5VV IN V OUTC L =C inv-gateL =L P =L N =0.25μmV SB-+(W p /W n =1.25/0.375)Figure 5.8CMOS inverter with capacitiveSection 5.1Exercises and Design Problems 187t out_fall of the inverter output,(2)the total energy lost E total ,and (3)the energy lost due to short circuit current E short .Using this data,prepare a plot of (1)(t out_rise +t out_fall )/2vs.t in_rise,fall ,(2)E total vs.t in_rise,fall ,(3)E short vs.t in_rise,fall and (4)E short /E total vs.t in_rise,fall.d.Provide simple explanations for:(i)Why the slope for (1)is less than 1?(ii)Why E short increases with t in_rise,fall ?(iii)Why E total increases with t in_rise,fall ?12.Consider the low swing driver of Figure 5.9:a.What is the voltage swing on the output node (V out )?Assume γ=0.b.Estimate (i)the energy drawn from the supply and (ii)energy dissipated for a 0V to 2.5V transition at the input.Assume that the rise and fall times at the input are 0.Repeat the analysis for a 2.5V to 0V transition at the input.pute t pLH (i.e.the time to transition from V OL to (V OH +V OL )/2).Assume the input rise time to be 0.V OL is the output voltage with the input at 0V and V OH is the output volt-age with the input at 2.5V .pute V OH taking into account body effect.Assume γ =0.5V 1/2for both NMOS and PMOS.13.Consider the following low swing driver consisting of NMOS devices M1and M2.Assumean NWELL implementation.Assume that the inputs IN and IN have a 0V to 2.5V swing andthat V IN =0V when V IN =2.5V and vice-versa.Also assume that there is no skew between INand IN (i.e.,the inverter delay to derive IN from IN is zero).a.What voltage is the bulk terminal of M2connected to?V in V out V DD =2.5V W L 3μm 0.25μm =p 2.5V0V C L =100fFW L 1.5μm 0.25μm=n Figure 5.9Low Swing DriverV LOW =0.5VOutM1ININ M225μm/0.25μm 25μm/0.25μmC L =1pFFigure 5.10Low Swing Driver188THE CMOS INVERTER Chapter 5b.What is the voltage swing on the output node as the inputs swing from 0V to 2.5V .Showthe low value and the high value.c.Assume that the inputs IN and IN have zero rise and fall times.Assume a zero skewbetween IN and IN.Determine the low to high propagation delay for charging the outputnode measured from the the 50%point of the input to the 50%point of the output.Assumethat the total load capacitance is 1pF,including the transistor parasitics.d.Assume that,instead of the 1pF load,the low swing driver drives a non-linear capacitor,whose capacitance vs.voltage is plotted pute the energy drawn from the lowsupply for charging up the load capacitor.Ignore the parasitic capacitance of the driver cir-cuit itself.14.The inverter below operates with V DD =0.4V and is composed of |V t |=0.5V devices.Thedevices have identical I 0and n.a.Calculate the switching threshold (V M )of this inverter.b.Calculate V IL and V IH of the inverter.15.Sizing a chain of inverters.a.In order to drive a large capacitance (C L =20pF)from a minimum size gate (with inputcapacitance C i =10fF),you decide to introduce a two-staged buffer as shown in Figure5.12.Assume that the propagation delay of a minimum size inverter is 70ps.Also assumeV DD =0.4VV IN V OUTFigure 5.11Inverter in Weak Inversion RegimeSection 5.1Exercises and Design Problems 189that the input capacitance of a gate is proportional to its size.Determine the sizing of thetwo additional buffer stages that will minimize the propagation delay.b.If you could add any number of stages to achieve the minimum delay,how many stages would you insert?What is the propagation delay in this case?c.Describe the advantages and disadvantages of the methods shown in (a)and (b).d.Determine a closed form expression for the power consumption in the circuit.Consider only gate capacitances in your analysis.What is the power consumption for a supply volt-age of 2.5V and an activity factor of 1?16.[M,None,3.3.5]Consider scaling a CMOS technology by S >1.In order to maintain compat-ibility with existing system components,you decide to use constant voltage scaling.a.In traditional constant voltage scaling,transistor widths scale inversely with S,W ∝1/S.To avoid the power increases associated with constant voltage scaling,however,youdecide to change the scaling factor for W .What should this new scaling factor be to main-tain approximately constant power.Assume long-channel devices (i.e.,neglect velocitysaturation).b.How does delay scale under this new methodology?c.Assuming short-channel devices (i.e.,velocity saturation),how would transistor widthshave to scale to maintain the constant power requirement?1InAdded Buffer StageOUTC L =20pF C i =10fF‘1’is the minimum size inverter.??Figure 5.12Buffer insertion for driving large loads.190THE CMOS INVERTER Chapter5DESIGN PROBLEMUsing the0.25μm CMOS introduced in Chapter2,design a static CMOSinverter that meets the following requirements:1.Matched pull-up and pull-down times(i.e.,t pHL=t pLH).2.t p=5nsec(±0.1nsec).The load capacitance connected to the output is equal to4pF.Notice that thiscapacitance is substantially larger than the internal capacitances of the gate.Determine the W and L of the transistors.To reduce the parasitics,useminimal lengths(L=0.25μm)for all transistors.Verify and optimize the designusing SPICE after proposing a first design using manual -pute also the energy consumed per transition.If you have a layout editor(suchas MAGIC)available,perform the physical design,extract the real circuitparameters,and compare the simulated results with the ones obtained earlier.。

数字集成电路复习笔记

数集复习笔记By 潇然2018.6.29名词解释专项摩尔定律:一个芯片上的晶体管数目大约每十八个月增长一倍。

传播延时:一个门的传播延时t p定义了它对输入端信号变化的响应有多快。

它表示一个信号通过一个门时所经历的延时,定义为输入和输出波形的50%翻转点之间的时间。

由于一个门对上升和下降输入波形的响应时间不同,所以需定义两个传播延时。

t pLH定义为这个门的输出由低至高翻转的响应时间,而t pHL则为输出由高至低翻转的响应时间。

传播延时t p定义为这两个时间的平均值:t p=(t pLH+t pHL)/2。

设计规则:设计规则是指导版图掩膜设计的对几何尺寸的一组规定。

它们包括图形允许的最小宽度以及在同一层和不同层上图形之间最小间距的限制与要求。

定义设计规则的目的是为了能够很容易地把一个电路概念转换成硅上的几何图形。

设计规则的作用就是电路设计者和工艺工程师之间的接口,或者说是他们之间的协议。

速度饱和效应:对于长沟MOS管,载流子满足公式:υ = -μξ(x)。

公式表明载流子的速度正比于电场,且这一关系与电场强度值的大小无关。

换言之,载流子的迁移率是一个常数。

然而在(水平方向)电场强度很高的情况下,载流子不再符合这一线性模型。

当沿沟道的电场达到某一临界值ξc时,载流子的速度将由于散射效应(即载流子间的碰撞)而趋于饱和。

时钟抖动:在芯片的某一个给定点上时钟周期发生暂时的变化,即时钟周期在每个不同的周期上可以缩短或加长。

逻辑综合:逻辑综合的任务是产生一个逻辑级模型的结构描述。

这一模型可以用许多不同的方式来说明,如状态转移图、状态图、电路图、布尔表达式、真值表或HDL 描述。

噪声容限:为了使一个门的稳定性较好并且对噪声干扰不敏感,应当使“0”和“1”的区间越大越好。

一个门对噪声的灵敏度是由低电平噪声容限NM L 和高电平噪声容限NM H来度量的,它们分别量化了合法的“0”和“1”的范围,并确定了噪声的最大固定阈值:NM L =V IL - V OLNM H =V OH - V IH沟道长度调制:在理想情况下,处于饱和区的晶体管的漏端与源端的电流是恒定的,并且独立于在这两个端口上外加的电压。

数字集成电路--电路、系统与设计(第二版)复习资料

第一章 数字集成电路介绍第一个晶体管,Bell 实验室,1947第一个集成电路,Jack Kilby ,德州仪器,1958 摩尔定律:1965年,Gordon Moore 预言单个芯片上晶体管的数目每18到24个月翻一番。

(随时间呈指数增长)抽象层次:器件、电路、门、功能模块和系统 抽象即在每一个设计层次上,一个复杂模块的内部细节可以被抽象化并用一个黑匣子或模型来代替。

这一模型含有用来在下一层次上处理这一模块所需要的所有信息。

固定成本(非重复性费用)与销售量无关;设计所花费的时间和人工;受设计复杂性、设计技术难度以及设计人员产出率的影响;对于小批量产品,起主导作用。

可变成本 (重复性费用)与产品的产量成正比;直接用于制造产品的费用;包括产品所用部件的成本、组装费用以及测试费用。

每个集成电路的成本=每个集成电路的可变成本+固定成本/产量。

可变成本=(芯片成本+芯片测试成本+封装成本)/最终测试的成品率。

一个门对噪声的灵敏度是由噪声容限NM L (低电平噪声容限)和NM H (高电平噪声容限)来度量的。

为使一个数字电路能工作,噪声容限应当大于零,并且越大越好。

NM H = V OH - V IH NM L = V IL - V OL 再生性保证一个受干扰的信号在通过若干逻辑级后逐渐收敛回到额定电平中的一个。

一个门的VTC 应当具有一个增益绝对值大于1的过渡区(即不确定区),该过渡区以两个有效的区域为界,合法区域的增益应当小于1。

理想数字门 特性:在过渡区有无限大的增益;门的阈值位于逻辑摆幅的中点;高电平和低电平噪声容限均等于这一摆幅的一半;输入和输出阻抗分别为无穷大和零。

传播延时、上升和下降时间的定义传播延时tp 定义了它对输入端信号变化的响应有多快。

它表示一个信号通过一个门时所经历的延时,定义为输入和输出波形的50%翻转点之间的时间。

上升和下降时间定义为在波形的10%和90%之间。

对于给定的工艺和门的拓扑结构,功耗和延时的乘积一般为一常数。

数字集成电路--电路、系统与设计(第二版)课后练习题 第六章 CMOS组合逻辑门的设计-Chapter 6 Designing

4

Chapter 6 Problem Set

VDD F G

A B

A

A B

A

Figure 6.6 Two-input complex logic gate.

11.

Design and simulate a circuit that generates an optimal differential signal as shown in Figure 6.7. Make sure the rise and fall times are equal.

2

VDD E 6 A A 6 B 6 C 6 D 6 F A B C D 4 4 4 4 E 1 A B C D E 4 4 4 4 E 1 6 F 6 B 6 C 6 D

Chapter 6 Problem SetVDD 6Circ来自it ACircuit B

Figure 6.2 Two static CMOS gates.

Digital Integrated Circuits - 2nd Ed

3

2.5 V

PMOS

M2 W/L = 0.5μm/0.25μm Vout Vin M1 W/L = 4μm/0.25μm NMOS Figure 6.4 Pseudo-NMOS inverter.

a. What is the output voltage if only one input is high? If all four inputs are high? b. What is the average static power consumption if, at any time, each input turns on with an (independent) probability of 0.5? 0.1? c. Compare your analytically obtained results to a SPICE simulation.

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第一章 数字集成电路介绍第一个晶体管,Bell 实验室,1947第一个集成电路,Jack Kilby ,德州仪器,1958 摩尔定律:1965年,Gordon Moore 预言单个芯片上晶体管的数目每18到24个月翻一番。

(随时间呈指数增长)抽象层次:器件、电路、门、功能模块和系统 抽象即在每一个设计层次上,一个复杂模块的内部细节可以被抽象化并用一个黑匣子或模型来代替。

这一模型含有用来在下一层次上处理这一模块所需要的所有信息。

固定成本(非重复性费用)与销售量无关;设计所花费的时间和人工;受设计复杂性、设计技术难度以及设计人员产出率的影响;对于小批量产品,起主导作用。

可变成本 (重复性费用)与产品的产量成正比;直接用于制造产品的费用;包括产品所用部件的成本、组装费用以及测试费用。

每个集成电路的成本=每个集成电路的可变成本+固定成本/产量。

可变成本=(芯片成本+芯片测试成本+封装成本)/最终测试的成品率。

一个门对噪声的灵敏度是由噪声容限NM L (低电平噪声容限)和NM H (高电平噪声容限)来度量的。

为使一个数字电路能工作,噪声容限应当大于零,并且越大越好。

NM H = V OH - V IH NM L = V IL - V OL 再生性保证一个受干扰的信号在通过若干逻辑级后逐渐收敛回到额定电平中的一个。

一个门的VTC 应当具有一个增益绝对值大于1的过渡区(即不确定区),该过渡区以两个有效的区域为界,合法区域的增益应当小于1。

理想数字门 特性:在过渡区有无限大的增益;门的阈值位于逻辑摆幅的中点;高电平和低电平噪声容限均等于这一摆幅的一半;输入和输出阻抗分别为无穷大和零。

传播延时、上升和下降时间的定义传播延时tp 定义了它对输入端信号变化的响应有多快。

它表示一个信号通过一个门时所经历的延时,定义为输入和输出波形的50%翻转点之间的时间。

上升和下降时间定义为在波形的10%和90%之间。

对于给定的工艺和门的拓扑结构,功耗和延时的乘积一般为一常数。

功耗-延时积(PDP)----门的每次开关事件所消耗的能量。

一个理想的门应当快速且几乎不消耗能量,所以最后的质量评价为。

能量-延时积(EDP) = 功耗-延时积2。

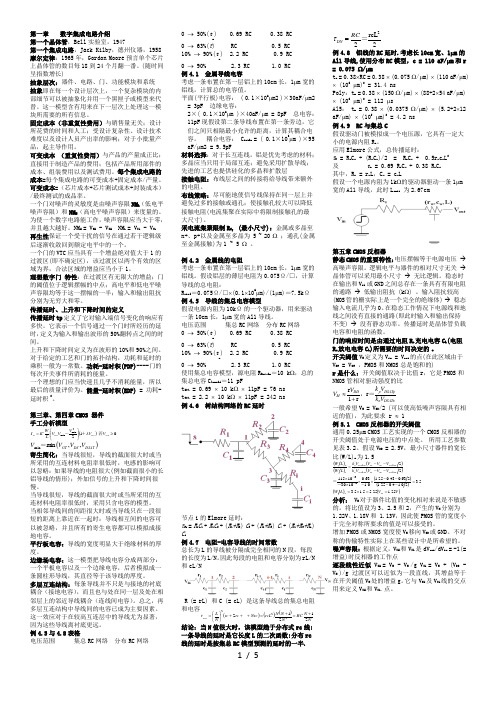

第三章、第四章CMOS 器件 手工分析模型()0 12'2min min ≥⎪⎪⎭⎫ ⎝⎛=GT DS GT D V V V V V LW K I 若+-λ()DSAT DS GT V V V V ,,m in min =寄生简化:当导线很短,导线的截面很大时或当所采用的互连材料电阻率很低时,电感的影响可以忽略:如果导线的电阻很大(例如截面很小的长铝导线的情形);外加信号的上升和下降时间很慢。

当导线很短,导线的截面很大时或当所采用的互连材料电阻率很低时,采用只含电容的模型。

当相邻导线间的间距很大时或当导线只在一段很短的距离上靠近在一起时:导线相互间的电容可以被忽略,并且所有的寄生电容都可以模拟成接地电容。

平行板电容:导线的宽度明显大于绝缘材料的厚度。

边缘场电容:这一模型把导线电容分成两部分:一个平板电容以及一个边缘电容,后者模拟成一条圆柱形导线,其直径等于该导线的厚度。

多层互连结构:每条导线并不只是与接地的衬底耦合(接地电容),而且也与处在同一层及处在相邻层上的邻近导线耦合(连线间电容)。

总之,再多层互连结构中导线间的电容已成为主要因素。

这一效应对于在较高互连层中的导线尤为显著,因为这些导线离衬底更远。

例4.5与4.8表格 电压范围 集总RC 网络 分布RC 网络 0 → 50%(t p) 0.69 RC 0.38 RC0 → 63%(τ) RC 0.5 RC 10% → 90%(t r) 2.2 RC 0.9 RC0 → 90% 2.3 RC 1.0 RC例4.1 金属导线电容考虑一条布置在第一层铝上的10cm 长,1μm 宽的铝线,计算总的电容值。

平面(平行板)电容: ( 0.1×106μm2 )×30aF/μm2 = 3pF 边缘电容:2×( 0.1×106μm )×40aF/μm = 8pF 总电容: 11pF 现假设第二条导线布置在第一条旁边,它们之间只相隔最小允许的距离,计算其耦合电容。

耦合电容: C inter = ( 0.1×106μm )×95 aF/μm2 = 9.5pF材料选择:对于长互连线,铝是优先考虑的材料;多晶应当只用于局部互连;避免采用扩散导线;先进的工艺也提供硅化的多晶和扩散层接触电阻:布线层之间的转接将给导线带来额外的电阻。

布线策略:尽可能地使信号线保持在同一层上并避免过多的接触或通孔;使接触孔较大可以降低接触电阻(电流集聚在实际中将限制接触孔的最大尺寸)。

采电流集聚限制R C , (最小尺寸):金属或多晶至n+、p+以及金属至多晶为 5 ~ 20 Ω ;通孔(金属至金属接触)为1 ~ 5 Ω 。

例4.2 金属线的电阻考虑一条布置在第一层铝上的10cm 长,1μm 宽的铝线。

假设铝层的薄层电阻为0.075Ω/□,计算导线的总电阻:R wire =0.075Ω/□⨯(0.1⨯106μm)/(1μm)=7.5k Ω 例4.5 导线的集总电容模型假设电源内阻为10k Ω的一个驱动器,用来驱动一条10cm 长,1μm 宽的Al1导线。

电压范围 集总RC 网络 分布RC 网络 0 → 50%(t p) 0.69 RC 0.38 RC0 → 63%(τ) RC 0.5 RC10% → 90%(t r) 2.2 RC 0.9 RC0 → 90% 2.3 RC 1.0 RC使用集总电容模型,源电阻R Driver =10 k Ω,总的集总电容C lumped =11 pFt 50% = 0.69 ⨯ 10 k Ω ⨯ 11pF = 76 ns t 90% = 2.2 ⨯ 10 k Ω ⨯ 11pF = 242 ns 例4.6 树结构网络的RC 延时节点i 的Elmore 延时: τDi = R 1C 1 + R 1C 2 + (R 1+R 3) C 3 + (R 1+R 3) C 4 + (R 1+R 3+R i ) C i 例4.7 电阻-电容导线的时间常数 总长为L 的导线被分隔成完全相同的N 段,每段的长度为L/N 。

因此每段的电阻和电容分别为rL/N 和cL/N R (= rL) 和C (= cL) 是这条导线总的集总电阻和电容()()()N N RC N N N rcL Nrc rc rc N L DN 2121 (22)22+=+=+++⎪⎭⎫⎝⎛=τ 结论:当N 值很大时,该模型趋于分布式rc 线;一条导线的延时是它长度L 的二次函数;分布rc 线的延时是按集总RC 模型预测的延时的一半.2rcL 22=RC DN =τ例4.8 铝线的RC 延时.考虑长10cm 宽、1μm 的Al1导线,使用分布RC 模型,c = 110 aF/μm 和r = 0.075 Ω/μm t p = 0.38⨯RC = 0.38 ⨯ (0.075 Ω/μm) ⨯ (110 aF/μm)⨯ (105 μm)2= 31.4 ns Poly :t p = 0.38 ⨯ (150 Ω/μm) ⨯ (88+2⨯54 aF/μm)⨯ (105 μm)2= 112 μsAl5: t p = 0.38 ⨯ (0.0375 Ω/μm) ⨯ (5.2+2⨯12aF/μm) ⨯ (105 μm)2= 4.2 ns 例4.9 RC 与集总C假设驱动门被模拟成一个电压源,它具有一定大小的电源内阻R s 。

应用Elmore 公式,总传播延时:τD = R s C w + (R w C w )/2 = R s C w + 0.5r w c w L 2 及 t p = 0.69 R s C w + 0.38 R w C w 其中,R w = r w L ,C w = c w L假设一个电源内阻为1k Ω的驱动器驱动一条1μm 宽的Al1导线,此时L crit 为2.67cm第五章CMOS 反相器 静态CMOS 的重要特性:电压摆幅等于电源电压 → 高噪声容限。

逻辑电平与器件的相对尺寸无关 → 晶体管可以采用最小尺寸 → 无比逻辑。

稳态时在输出和V dd 或GND 之间总存在一条具有有限电阻的通路 → 低输出阻抗 (k Ω) 。

输入阻抗较高 (MOS 管的栅实际上是一个完全的绝缘体) → 稳态输入电流几乎为0。

在稳态工作情况下电源线和地线之间没有直接的通路(即此时输入和输出保持不变) → 没有静态功率。

传播延时是晶体管负载电容和电阻的函数。

门的响应时间是由通过电阻R p 充电电容C L (电阻R n 放电电容C L )所需要的时间决定的 。

开关阈值V M 定义为V in = V out 的点(在此区域由于V DS = V GS ,PMOS 和NMOS 总是饱和的)r 是什么:开关阈值取决于比值r ,它是PMOS 和NMOS 管相对驱动强度的比DSATnn DSATp p DD M V k V k VV =,r r 1r +≈ 一般希望V M = V DD /2 (可以使高低噪声容限具有相近的值),为此要求 r ≈ 1例5.1 CMOS 反相器的开关阈值 通用0.25μm CMOS 工艺实现的一个CMOS 反相器的开关阈值处于电源电压的中点处。

所用工艺参数见表3.2。

假设V DD = 2.5V ,最小尺寸器件的宽长比(W/L)n 为1.5()()()()()()()()V V L W V V V V k V V V V k L W L W M p DSATp Tp M DSATp p DSATn Tn M DSATn n n p 25.125.55.15.35.320.14.025.1263.043.025.10.163.01030101152266==⨯==----⨯-⨯⨯⨯----=---= 分析: V M 对于器件比值的变化相对来说是不敏感的。

将比值设为3、2.5和2,产生的V M 分别为1.22V 、1.18V 和 1.13V ,因此使PMOS 管的宽度小于完全对称所要求的值是可以接受的。

增加PMOS 或NMOS 宽度使V M 移向V DD 或GND 。

不对称的传输特性实际上在某些设计中是所希望的。

噪声容限:根据定义,V IH 和V IL 是dV out /dV in = -1(= 增益)时反相器的工作点 逐段线性近似V IH = V M - V M /g V IL = V M + (V DD - V M )/g 过渡区可以近似为一段直线,其增益等于在开关阈值V M 处的增益g 。