《数字集成电路》课件

合集下载

《数字集成电路》课件

1 滤波

去除噪声、增强信号的关键技术。

2 变换

将信号在时域与频域之间转换的方法。

3 压缩

减少数据量,方便存储和传输。

数字信号处理中的滤波器设计

FIR滤波器

时域响应仅有有限个点,稳定性好。

IIR滤波器

时域响应呈指数衰减,延时较小。

模拟/数字混合信号集成电路

1

基础理论

混合信号电路设计所需的模拟电路与数字电路基础知识。

时序逻辑电路

触发器与锁存器

用于存储时钟信号冲突消除和数 据暂存。

计数器

移位寄存器

用于计算和记录触发事件的数量。

用于数据移位操作,实现数据的 串行传输。

数字信号处理技术

数字信号处理(DSP)是用数字计算机或数字信号处理器对原始信号进行处理、分析和存储的一 种技术。它在通信、音频处理和图像处理等领域具有广泛应用。

《数字集成电路》PPT课 件

数字集成电路PPT课件大纲: 1. 什么是数字集成电路 2. 数字集成电路的分类和结构

数字电路设计的流程

1

需求分析

确定数字电路的功能与性能要求,并定义输入输出及约束条件。

2

电路设计

利用逻辑门、触发器等基本组件进行数字电路设计。

3

电路仿真

使用仿真软件验证数字电路中的电气特性和功能。

2 低功耗设计

3 增强型通信

减少功耗,延长电池寿命。

提升通信性能和速度。

2

模拟数字转换

模拟和数字信号之间的转换方法和技术。

3

功耗与噪声

如何平衡功耗Βιβλιοθήκη 噪声性能。电路模拟与仿真SPICE仿真

使用电路仿真软件模拟电路 的工作状态。

参数提取与建模

数字集成电路设计课件

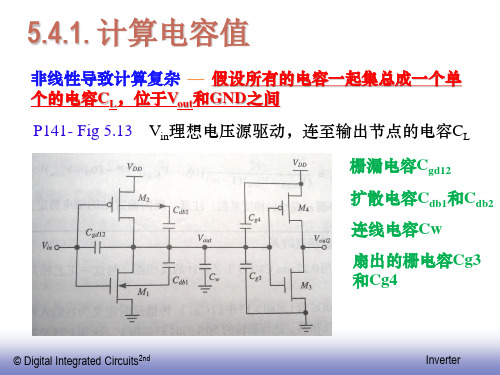

5.4.1. 计算电容值

非线性导致计算复杂 — 假设所有的电容一起集总成一个单 个的电容CL,位于Vout和GND之间

P141- Fig 5.13 Vin理想电压源驱动,连至输出节点的电容CL

栅漏电容Cgd12

扩散电容Cdb1和Cdb2 连线电容Cw 扇出的栅电容Cg3 和Cg4

© Digital Integrated Circuits2nd

本征电容:由扩散电容和覆盖电容组成

外部负载电容:由导线和所连接的门组成

Inverter

© Digital Integrated Circuits2nd

CMOS Inverters

VDD

PMOS 9l/2l

5+5+9=19 λ (PD) 5×9 λ2=45λ2(AD)

0.25 mm =2l Out Metal1 In

Inverter

• 栅漏电容Cgd12 在输出过渡的前半部,M1和M2不是断开就是处在饱和模式,

Cgd12只包括M1和M2的覆盖电容,沟道电容不起作用(处于栅-体

或栅-源之间)。 集总电容模型要求用接地电容来代替浮空的栅漏电容,通过

密勒效应实现:一个在其两端经历大小相同但相位相反的电压

摆幅的电容可以用一个两倍于该电容值的接地电容代替。 P141- Fig 5.14 Cgd=2Cgd0W

© Digital Integrated Circuits2nd

Inverter

• 扩散电容Cdb1和Cdb2

漏和体之间的电容来自反向偏置的pn结。这样的电容是高 度非线性的,并且在很大程度上取决于所加的电压。

可用一个线性电容来代替非线性电容,使这个线性电容在

所关注的电压范围内的电荷变化与非线性电容相同。 Ceq = KeqCj0

非线性导致计算复杂 — 假设所有的电容一起集总成一个单 个的电容CL,位于Vout和GND之间

P141- Fig 5.13 Vin理想电压源驱动,连至输出节点的电容CL

栅漏电容Cgd12

扩散电容Cdb1和Cdb2 连线电容Cw 扇出的栅电容Cg3 和Cg4

© Digital Integrated Circuits2nd

本征电容:由扩散电容和覆盖电容组成

外部负载电容:由导线和所连接的门组成

Inverter

© Digital Integrated Circuits2nd

CMOS Inverters

VDD

PMOS 9l/2l

5+5+9=19 λ (PD) 5×9 λ2=45λ2(AD)

0.25 mm =2l Out Metal1 In

Inverter

• 栅漏电容Cgd12 在输出过渡的前半部,M1和M2不是断开就是处在饱和模式,

Cgd12只包括M1和M2的覆盖电容,沟道电容不起作用(处于栅-体

或栅-源之间)。 集总电容模型要求用接地电容来代替浮空的栅漏电容,通过

密勒效应实现:一个在其两端经历大小相同但相位相反的电压

摆幅的电容可以用一个两倍于该电容值的接地电容代替。 P141- Fig 5.14 Cgd=2Cgd0W

© Digital Integrated Circuits2nd

Inverter

• 扩散电容Cdb1和Cdb2

漏和体之间的电容来自反向偏置的pn结。这样的电容是高 度非线性的,并且在很大程度上取决于所加的电压。

可用一个线性电容来代替非线性电容,使这个线性电容在

所关注的电压范围内的电荷变化与非线性电容相同。 Ceq = KeqCj0

数字集成电路第1章PPT课件

离子反应刻蚀 扩散

双极集成电路的基本制造工艺

掺硼P型硅作为衬底材料并进行初始氧化,以形 成二氧化硅表层,然后再进行隐埋层光刻以形 成一个窗口后进行N+层掺杂,接着就用外延层 所覆盖,故称隐埋层

制作隐埋层后,去除表面的二氧化硅,再进行N 型外延层生长

掺P型材料进行隔离扩散. 用第三块掩模版完成基区光刻

双极集成电路的基本制造工艺

基区重掺杂 制作晶体管发射极和集电极 形成表面金属互连接的接触区 完成一层金属铝膜的沉积,然后再介质淀积 在介质层上蚀刻出连接通孔 成第二层金属铝膜的沉积 后续工序,划片,粘片,压焊,封装,测试分类,筛选,

成品测试,入库

双极集成电路应用

TTL,DTL,RTL,HTL,ECL STLL,SLTTL,I2L,I3L ASTLL.ASLTTL

环 长PSG 引线孔光刻 铝引线光刻 压焊块光刻

N阱硅栅CMOS工艺(略)

▪ 双阱硅栅CMOS工艺

BI---CMOS工艺

双极工艺特点: 速度高、驱动能力强、模拟精度高 但功耗、集成度无法满足VLSI的

要求

BI---CMOS工艺

CMOS工艺特点: 功耗低、集成度高、抗干扰能力强 但速度低、驱动能力差

成

P+

NPN管的基区扩散 PMOS管的源、漏区扩散 横向PNP管集电区、发射区扩散 纵向PNP管的发射区扩散可以同时进行完成

以双极性工艺为基础的P阱BICMOS工艺

栅氧化在PMOS管沟道注入以后进行 可获的大电流、高压 LDMOS-LOW DOUBLE MOS VDMOS-VERTICAL DOUBLE MOS

以双极性工艺为基础的BI-CMOS工艺

以双极性工艺为基础的P阱BI-CMOS工艺 以双极性工艺为基础的双阱BI-CMOS工艺 特点是对双极器件有利

双极集成电路的基本制造工艺

掺硼P型硅作为衬底材料并进行初始氧化,以形 成二氧化硅表层,然后再进行隐埋层光刻以形 成一个窗口后进行N+层掺杂,接着就用外延层 所覆盖,故称隐埋层

制作隐埋层后,去除表面的二氧化硅,再进行N 型外延层生长

掺P型材料进行隔离扩散. 用第三块掩模版完成基区光刻

双极集成电路的基本制造工艺

基区重掺杂 制作晶体管发射极和集电极 形成表面金属互连接的接触区 完成一层金属铝膜的沉积,然后再介质淀积 在介质层上蚀刻出连接通孔 成第二层金属铝膜的沉积 后续工序,划片,粘片,压焊,封装,测试分类,筛选,

成品测试,入库

双极集成电路应用

TTL,DTL,RTL,HTL,ECL STLL,SLTTL,I2L,I3L ASTLL.ASLTTL

环 长PSG 引线孔光刻 铝引线光刻 压焊块光刻

N阱硅栅CMOS工艺(略)

▪ 双阱硅栅CMOS工艺

BI---CMOS工艺

双极工艺特点: 速度高、驱动能力强、模拟精度高 但功耗、集成度无法满足VLSI的

要求

BI---CMOS工艺

CMOS工艺特点: 功耗低、集成度高、抗干扰能力强 但速度低、驱动能力差

成

P+

NPN管的基区扩散 PMOS管的源、漏区扩散 横向PNP管集电区、发射区扩散 纵向PNP管的发射区扩散可以同时进行完成

以双极性工艺为基础的P阱BICMOS工艺

栅氧化在PMOS管沟道注入以后进行 可获的大电流、高压 LDMOS-LOW DOUBLE MOS VDMOS-VERTICAL DOUBLE MOS

以双极性工艺为基础的BI-CMOS工艺

以双极性工艺为基础的P阱BI-CMOS工艺 以双极性工艺为基础的双阱BI-CMOS工艺 特点是对双极器件有利

数字集成电路_课件4

1

电阻负载反相器设计

下降时间: 2(VOH VT ) 2VT tf f ln 1 VOL (VOH VT )

下降延迟时间 : 4(VOH VT ) 2VT t pf f ln 1 (VOH VOL ) (VOH VT ) Cout 下降时间常数: f k (VOH VT )

电阻负载型MOS反向器的瞬态特性

上升时间一般公式: t r dt Cout

t1 t2 V1 V0

dVout I L V (out)

VDD Vout 其中: I L RL dVout 得 : t r RL Cout V0 V DD Vout

V1

上升时间: t r RL Cout

上升延迟功率积的计算 : dVout 上升电流: I L Cout dt dVout VDD VOL VDD 近似 : dt tr tr VDD 上升时平均电流: I av Cout tr 上升延迟功率积: ( pav t p ) r CoutV

2 DD

tp tr

电阻负载型功率延时乘积

2 Vout 导通电阻的设计 : I D k (Vin VT )Vout 2 2 VOL 进入非线性区 : I D k (VOH VT )VOL 2

电阻负载反相器设计

VOL ID 得: k (Vin VT ) VOL 2 VOL 导通电阻为 : Ron k (Vin VT ) 2

电阻负载型MOS反相器的瞬态特性

下降延迟时间: t pf 4(VOH VT ) Cout 2VT ln 1 k (VOH VT ) (VOH VOL ) (VOH VT )

电阻负载反相器设计

下降时间: 2(VOH VT ) 2VT tf f ln 1 VOL (VOH VT )

下降延迟时间 : 4(VOH VT ) 2VT t pf f ln 1 (VOH VOL ) (VOH VT ) Cout 下降时间常数: f k (VOH VT )

电阻负载型MOS反向器的瞬态特性

上升时间一般公式: t r dt Cout

t1 t2 V1 V0

dVout I L V (out)

VDD Vout 其中: I L RL dVout 得 : t r RL Cout V0 V DD Vout

V1

上升时间: t r RL Cout

上升延迟功率积的计算 : dVout 上升电流: I L Cout dt dVout VDD VOL VDD 近似 : dt tr tr VDD 上升时平均电流: I av Cout tr 上升延迟功率积: ( pav t p ) r CoutV

2 DD

tp tr

电阻负载型功率延时乘积

2 Vout 导通电阻的设计 : I D k (Vin VT )Vout 2 2 VOL 进入非线性区 : I D k (VOH VT )VOL 2

电阻负载反相器设计

VOL ID 得: k (Vin VT ) VOL 2 VOL 导通电阻为 : Ron k (Vin VT ) 2

电阻负载型MOS反相器的瞬态特性

下降延迟时间: t pf 4(VOH VT ) Cout 2VT ln 1 k (VOH VT ) (VOH VOL ) (VOH VT )

数字集成电路(时序逻辑电路)

数字集成电路(时序 逻辑电路)

目录

• 引言 • 时序逻辑电路的基本概念 • 数字集成电路的组成 • 时序逻辑电路的分析方法

目录

• 引言 • 时序逻辑电路的基本概念 • 数字集成电路的组成 • 时序逻辑电路的分析方法

目录

• 时序逻辑电路的设计方法 • 时序逻辑电路的应用 • 时序逻辑电路的发展趋势和挑战

逻辑门

01

逻辑门是数字集成电路的基本组成单元,用于实现逻辑运算(如AND、 OR、NOT等)。

02

常见的逻辑门有TTL(Transistor-Transistor Logic)和CMOS (Complementary Metal-Oxide Semiconductor)等类型。

03

逻辑门通常由晶体管组成,通过不同的组合和连接方式实现各种逻辑 功能。

目录

• 时序逻辑电路的设计方法 • 时序逻辑电路的应用 • 时序逻辑电路的发展趋势和挑战

01

引言

01

引言

主题简介

数字集成电路

数字集成电路是利用半导体技术将逻 辑门、触发器等数字逻辑单元集成在 一块衬底上,实现数字信号处理功能 的集成电路。

时序逻辑电路

时序逻辑电路是一种具有记忆功能的 电路,其输出不仅取决于当前的输入 ,还与电路的先前状态有关。常见的 时序逻辑电路有寄存器、计数器等。

时序图

通过图形方式表示时序逻辑电路的输入和输出随时间变化的规律,能够直观地展 示电路的工作过程。

逻辑方程和时序图

逻辑方程

描述时序逻辑电路输入和输出关系的数学表达式,通常由触发器的状态方程和输 出方程组成。

时序图

通过图形方式表示时序逻辑电路的输入和输出随时间变化的规律,能够直观地展 示电路的工作过程。

目录

• 引言 • 时序逻辑电路的基本概念 • 数字集成电路的组成 • 时序逻辑电路的分析方法

目录

• 引言 • 时序逻辑电路的基本概念 • 数字集成电路的组成 • 时序逻辑电路的分析方法

目录

• 时序逻辑电路的设计方法 • 时序逻辑电路的应用 • 时序逻辑电路的发展趋势和挑战

逻辑门

01

逻辑门是数字集成电路的基本组成单元,用于实现逻辑运算(如AND、 OR、NOT等)。

02

常见的逻辑门有TTL(Transistor-Transistor Logic)和CMOS (Complementary Metal-Oxide Semiconductor)等类型。

03

逻辑门通常由晶体管组成,通过不同的组合和连接方式实现各种逻辑 功能。

目录

• 时序逻辑电路的设计方法 • 时序逻辑电路的应用 • 时序逻辑电路的发展趋势和挑战

01

引言

01

引言

主题简介

数字集成电路

数字集成电路是利用半导体技术将逻 辑门、触发器等数字逻辑单元集成在 一块衬底上,实现数字信号处理功能 的集成电路。

时序逻辑电路

时序逻辑电路是一种具有记忆功能的 电路,其输出不仅取决于当前的输入 ,还与电路的先前状态有关。常见的 时序逻辑电路有寄存器、计数器等。

时序图

通过图形方式表示时序逻辑电路的输入和输出随时间变化的规律,能够直观地展 示电路的工作过程。

逻辑方程和时序图

逻辑方程

描述时序逻辑电路输入和输出关系的数学表达式,通常由触发器的状态方程和输 出方程组成。

时序图

通过图形方式表示时序逻辑电路的输入和输出随时间变化的规律,能够直观地展 示电路的工作过程。

数字集成电路设计PPT课件

parameter size=4’d8;

第19页/共55页

2、变量

变量是指在程序运行过程中其值可以改变的量。 在Verilog中,变量分为两种:

网络数据类型(nets型)和寄存器类型(reg型)。

ⅰ. nets型变量

Verilog中提供多种nets型变量:wire、wor、wand等等,这里主要介绍wire型变量。 wire型数据类型用来表示以assign语句赋值的组合逻辑信号。 在Verilog模型中,输入输出信号类型缺省时自动定义为wire型。 wire型变量的格式定义如下:

wire是定义网络数据类型变量(nets)的关键词,信号变量类型缺省时默认 为wire型。reg是定义寄存器型变量(register)的关键词。

第14页/共55页

4、逻辑功能定义

模块中最重要的部分是逻辑功能定义,它描述输入输出变量及中间变量的 逻辑功能。在模块中描述逻辑功能有三种方法:

(1)用“assign”语句 assign语句一般用于适用于对组合逻辑进行描述,称为连续赋值方式。

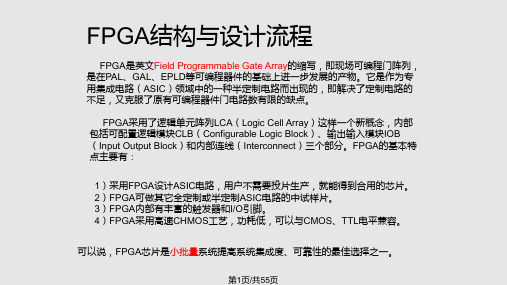

查找表(Look-Up-Table)简称为LUT,LUT本质上就是一个RAM。 目前FPGA中 多使用4输入的LUT,所以每一个LUT可以看成一个有4位地址线的16×1的RAM。

实际逻辑电路

LUT的实现方式

a,b,c,d 输入 0000 0001 .... 1111

逻辑输出 0 0 0 1

地址 0000 0001

ispLEVER是Lattice公司继ispDesignerEXPRET后的新一代 集成工具,该软件同时集成了许多第三方工具,如 Synplicity/Synplicity Pro和Leonardo Spectrum,仿真软件 Modelsim等。

第19页/共55页

2、变量

变量是指在程序运行过程中其值可以改变的量。 在Verilog中,变量分为两种:

网络数据类型(nets型)和寄存器类型(reg型)。

ⅰ. nets型变量

Verilog中提供多种nets型变量:wire、wor、wand等等,这里主要介绍wire型变量。 wire型数据类型用来表示以assign语句赋值的组合逻辑信号。 在Verilog模型中,输入输出信号类型缺省时自动定义为wire型。 wire型变量的格式定义如下:

wire是定义网络数据类型变量(nets)的关键词,信号变量类型缺省时默认 为wire型。reg是定义寄存器型变量(register)的关键词。

第14页/共55页

4、逻辑功能定义

模块中最重要的部分是逻辑功能定义,它描述输入输出变量及中间变量的 逻辑功能。在模块中描述逻辑功能有三种方法:

(1)用“assign”语句 assign语句一般用于适用于对组合逻辑进行描述,称为连续赋值方式。

查找表(Look-Up-Table)简称为LUT,LUT本质上就是一个RAM。 目前FPGA中 多使用4输入的LUT,所以每一个LUT可以看成一个有4位地址线的16×1的RAM。

实际逻辑电路

LUT的实现方式

a,b,c,d 输入 0000 0001 .... 1111

逻辑输出 0 0 0 1

地址 0000 0001

ispLEVER是Lattice公司继ispDesignerEXPRET后的新一代 集成工具,该软件同时集成了许多第三方工具,如 Synplicity/Synplicity Pro和Leonardo Spectrum,仿真软件 Modelsim等。

数字集成电路

数字集成电路

用于处理数字信号的集成电路

01 基本介绍

03 逻辑功能

目录

02 型号组成 04 内部设计

05 类别说明

07 注意事项

目录

06 一般特性

数字集成电路是将元器件和连线集成于同一半导体芯片上而制成的数字逻辑电路或系统。根据数字集成电路 中包含的门电路或元、器件数量,可将数字集成电路分为小规模集成(SSI)电路、中规模集成MSI电路、大规模 集成(LSI)电路、超大规模集成VLSI电路和特大规模集成(ULSI)电路。

·输入端信号幅度不能大于VDD和小于0V;

·消除电源上的干扰;

·在条件允许的情况下,尽可能降低电源电压,如果电路工作频率比较低,用+5V电源供电最好;

·对使用的电源加限流措施,看

②电源电压的极性千万不能接反,电源正负极颠倒、接错,会因为过大电流而造成器件损坏。

③CM0S电路要求输人信号的幅度不能超过VDD~VSS,即满足VSS=V1=VDD。当 CM0S电路输入端施加的电压过 高(大于电源电压)或过低(小于0V),或者电源电压突然变化时,电路电流可能会迅速增大,烧坏器件,这种 现象称为可控硅效应。预防可控硅效应的措施主要有:

从功能上来看,数字集成电路内部可以分为数据通路(Data-path,也称为数据路径)和控制逻辑两大部分。 这两大部分都是由大量的时序逻辑电路集成的,而且绝大部分都是同步的时序电路,因为时序电路被多个触发器 或寄存器分成若干节点,而这些触发器在时钟的控制下会按同样的节拍来工作,可以简化设计。在长期的设计过 程中,已经积累了很多标准的通用单元,比如选择器(也叫多路器,可以从多个输入数据中选一个输出)、比较 器(用于比较两个数的大小)、加法器、乘法器、移位寄存器等等,这些单元电路形状规则,便于集成(这也是 数字电路在集成电路中得到更好的发展的原因)。这些单元按设计要求连接在一起,形成数据通路,待处理的数 据从输入端经过这条通路到输出端,便得到处理后的结果。同时,还需要由专门设计的控制逻辑,控制数据通路 的各组成部件,按各自的功能要求和特定的时序关系和来配合工作。

用于处理数字信号的集成电路

01 基本介绍

03 逻辑功能

目录

02 型号组成 04 内部设计

05 类别说明

07 注意事项

目录

06 一般特性

数字集成电路是将元器件和连线集成于同一半导体芯片上而制成的数字逻辑电路或系统。根据数字集成电路 中包含的门电路或元、器件数量,可将数字集成电路分为小规模集成(SSI)电路、中规模集成MSI电路、大规模 集成(LSI)电路、超大规模集成VLSI电路和特大规模集成(ULSI)电路。

·输入端信号幅度不能大于VDD和小于0V;

·消除电源上的干扰;

·在条件允许的情况下,尽可能降低电源电压,如果电路工作频率比较低,用+5V电源供电最好;

·对使用的电源加限流措施,看

②电源电压的极性千万不能接反,电源正负极颠倒、接错,会因为过大电流而造成器件损坏。

③CM0S电路要求输人信号的幅度不能超过VDD~VSS,即满足VSS=V1=VDD。当 CM0S电路输入端施加的电压过 高(大于电源电压)或过低(小于0V),或者电源电压突然变化时,电路电流可能会迅速增大,烧坏器件,这种 现象称为可控硅效应。预防可控硅效应的措施主要有:

从功能上来看,数字集成电路内部可以分为数据通路(Data-path,也称为数据路径)和控制逻辑两大部分。 这两大部分都是由大量的时序逻辑电路集成的,而且绝大部分都是同步的时序电路,因为时序电路被多个触发器 或寄存器分成若干节点,而这些触发器在时钟的控制下会按同样的节拍来工作,可以简化设计。在长期的设计过 程中,已经积累了很多标准的通用单元,比如选择器(也叫多路器,可以从多个输入数据中选一个输出)、比较 器(用于比较两个数的大小)、加法器、乘法器、移位寄存器等等,这些单元电路形状规则,便于集成(这也是 数字电路在集成电路中得到更好的发展的原因)。这些单元按设计要求连接在一起,形成数据通路,待处理的数 据从输入端经过这条通路到输出端,便得到处理后的结果。同时,还需要由专门设计的控制逻辑,控制数据通路 的各组成部件,按各自的功能要求和特定的时序关系和来配合工作。

数字集成电路课件

Y2 Y1 Y0

000 001 010 011 100 101 110 111

3.4.1 编码器

逻辑函数表达式

Y 2 I 7 I 6 I 7 I 5 I 6 I 7 I 4 I 5 I 6 I 7 I 4 I 5 I 6 I 7

Y2I4I5I6I7

利用公式A+AB=A+B

Y 1 I 7 I 6 I 7 I 3 I 4 I 5 I 6 I 7 I 2 I 3 I 4 I 5 I 6 I 7

如何化简 ?

Y 2 I 4 I 0 I 1 I 2 I 3 I 5 I 6 I 7 I 5 I 0 I 1 I 2 I 3 I 4 I 6 I 7 I 6 I 0 I 1 I 2 I 3 I 4 I 5 I 7 I 7 I 0 I 1 I 2 I 3 I 4 I 5 I 6 Y 1 I 2 I 0 I 1 I 3 I 4 I 5 I 6 I 7 I 3 I 0 I 1 I 2 I 4 I 5 I 6 I 7 I 6 I 0 I 1 I 2 I 3 I 4 I 5 I 7 I 7 I 0 I 1 I 2 I 3 I 4 I 5 I 6 Y 0 I 1 I 0 I 2 I 3 I 4 I 5 I 6 I 7 I 3 I 0 I 1 I 2 I 4 I 5 I 6 I 7 I 5 I 0 I 1 I 2 I 3 I 4 I 6 I 7 I 7 I 0 I 1 I 2 I 3 I 4 I 5 I 6

10 ≥1

11 12

15 18

13

14 15

α 14

16

17

5

0α ENα/V18 1α

2α

9 7 6

YEX Y2 Y1 Y0

S

74LS148

YS

数字集成电路课件

Introduction

EE141 Integrated Circuits2nd © Digital

介绍大纲

什么是IC

将来会如何发

展?

EE141 Integrated © Digital

Circuits2nd

Introduction

7

第一台自动计算机

Babbage DifferenceEngine I (1832) 25,000个机械部件 总成本 17,470

Circuits2nd

Courtesy, Intel

Introduction

30

功率密度

10000 功率密度(W/cm2) 1000

Rocket Nozzle Nhomakorabea100

Nuclear Reactor

8086 10 4004 Hot Plate P6 8008 8085 Pentium® proc 386 286 486 8080 1 1970 1980 1990 2000 2010 年

Introduction

19

2007年英特尔推出45nm正式量 产工艺,45nm技术是全新的技 术,可以让摩尔定律至少再服 役10年。

EE141 Integrated © Digital

Circuits2nd

Introduction

20

集成电路的应用领域

军事国防 工业控制

工控设备 智能仪表 汽车电子 网络设备 电子商务 集成电路

8086

Source: Intel

1 Billion Transistors

Pentium® III Pentium® II Pentium® Pro Pentium®

i486 i386 80286

EE141 Integrated Circuits2nd © Digital

介绍大纲

什么是IC

将来会如何发

展?

EE141 Integrated © Digital

Circuits2nd

Introduction

7

第一台自动计算机

Babbage DifferenceEngine I (1832) 25,000个机械部件 总成本 17,470

Circuits2nd

Courtesy, Intel

Introduction

30

功率密度

10000 功率密度(W/cm2) 1000

Rocket Nozzle Nhomakorabea100

Nuclear Reactor

8086 10 4004 Hot Plate P6 8008 8085 Pentium® proc 386 286 486 8080 1 1970 1980 1990 2000 2010 年

Introduction

19

2007年英特尔推出45nm正式量 产工艺,45nm技术是全新的技 术,可以让摩尔定律至少再服 役10年。

EE141 Integrated © Digital

Circuits2nd

Introduction

20

集成电路的应用领域

军事国防 工业控制

工控设备 智能仪表 汽车电子 网络设备 电子商务 集成电路

8086

Source: Intel

1 Billion Transistors

Pentium® III Pentium® II Pentium® Pro Pentium®

i486 i386 80286

第10章数字集成电路基本单元与版图精品PPT课件

(1) CMOS反相器的具体电路

(2) CMOS反相器物理结构的剖面图

(3)开关特性

我们希望反相器的上升时间和下降时间近似相等,

则需要使PMOS管的沟道宽度必须加宽到NMOS管沟道

宽度的 n / p倍左右。

Vi(t)

+VDD

0

Vo(t) +VDD 0.9VDD 0.1VDD

0

td tf

t

t tr

(10)以上有关尺寸的设计必须符合版图设计规则。

TTL与非门的版图设计

• 评价版图好坏的几个因素: ① 符合原电路设计指标; ② 面积最小; ③ 成品率高; ④ 可靠性高; ⑤ 具有可测试性。

TTL与非门的版图设计

• 双极型集成电路版图设计步骤: (1)划分隔离区 (2)元器件的版图设计 (3)元器件的布局 (4)布线

10.2 TTL基本电路及版图实现

10.2.1 TTL基本电路

• TTL反相器电路

VCC(5V)

Rb1 Rc2

Rc4

+

T1

υ1

-

T2 Re2

T4

D +

T3 负 v0 载 -

GND

TTL基本电路及版图实现

(1)电路组成 该电路由三部分组成:

1)由双极型晶体管T1和电阻Rb1组成电路的输入级; 2)由T2、Re2和Rc2组成的中间驱动电路,将单端信号 υB2转换为双端信号υB3和υB4; 3)由T3、T4、Rc4和二极管D组成的输出级。 (2)工作原理 输入为高电平时,输出为低电平。 输入为低电平时,输出为高电平。

(b)为三输入端TTL与非门的代表符号

TTL基本电路及版图实现

• 或非门路

VCC

R1A

(2) CMOS反相器物理结构的剖面图

(3)开关特性

我们希望反相器的上升时间和下降时间近似相等,

则需要使PMOS管的沟道宽度必须加宽到NMOS管沟道

宽度的 n / p倍左右。

Vi(t)

+VDD

0

Vo(t) +VDD 0.9VDD 0.1VDD

0

td tf

t

t tr

(10)以上有关尺寸的设计必须符合版图设计规则。

TTL与非门的版图设计

• 评价版图好坏的几个因素: ① 符合原电路设计指标; ② 面积最小; ③ 成品率高; ④ 可靠性高; ⑤ 具有可测试性。

TTL与非门的版图设计

• 双极型集成电路版图设计步骤: (1)划分隔离区 (2)元器件的版图设计 (3)元器件的布局 (4)布线

10.2 TTL基本电路及版图实现

10.2.1 TTL基本电路

• TTL反相器电路

VCC(5V)

Rb1 Rc2

Rc4

+

T1

υ1

-

T2 Re2

T4

D +

T3 负 v0 载 -

GND

TTL基本电路及版图实现

(1)电路组成 该电路由三部分组成:

1)由双极型晶体管T1和电阻Rb1组成电路的输入级; 2)由T2、Re2和Rc2组成的中间驱动电路,将单端信号 υB2转换为双端信号υB3和υB4; 3)由T3、T4、Rc4和二极管D组成的输出级。 (2)工作原理 输入为高电平时,输出为低电平。 输入为低电平时,输出为高电平。

(b)为三输入端TTL与非门的代表符号

TTL基本电路及版图实现

• 或非门路

VCC

R1A