CPLD和虚拟仪器的频率计综合设计

基于CPLD的简易数字频率计的设计

184

现代电子技术

2011 年 第 34 卷

控 制 电 路 是 对 计 数 电 路 、锁 存 电 路 和 译 码 电 路 进 行 时序的控制。其控制要求为:先使计数电路 在 1s内 进 行计数,接着在下 一 个 1s内 锁 存 计 数 的 结 果,最 后 将 锁存的数据进行译码和显示。在第一个测量显示周期 结束后,控制电路将再 次 发 出 控 制 信 号,先 对 功 能 电 路 清 零 ,然 后 使 系 统 开 始 第 二 个 测 量 周 期 的 工 作 。

译码电路的功能是将锁存器保存并将输出的4位 二 进 制 代 码 表 示 的 十 进 制 数 进 行 译 码 转 换 ,将 其 转 换 为 能直接驱动数码管显示的十进制数字字符的输出信号。

显示电路由共阴数码管电路构成。由于被测信号 的频率测频范 围 为 1 Hz~1 MHz,因 此 需 要 6 个 数 码 管对其进行显示。

基于CPLD和单片机的频率计设计

正文:

一、实验设计原理

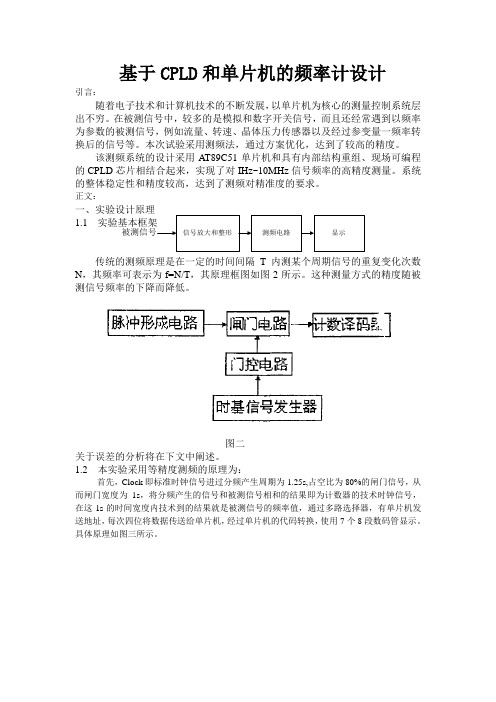

1.1实验基本框架

图一

传统的测频原理是在一定的时间间隔T内测某个周期信号的重复变化次数N,其频率可表示为f=N/T,其原理框图如图2所示。这种测量方式的精度随被测信号频率的下降而降低。

{

Counter = 0;

TMOD = 0x11; //定时器工作方式

TH0 = T0_High_Init;

TL0 = T0_Low_Init; //设置定时器初值

TR0 = 1; //启动定时器

ET0 = 1; //允许定时器中断

EA = 1; //开中断

}

//延时

void delay()

{

int ti;

基于CPLD和单片机的频率计设计

引言:

随着电子技术和计算机技术的不断发展,以单片机为核心的测量控制系统层出不穷。在被测信号中,较多的是模拟和数字开关信号,而且还经常遇到以频率为参数的被测信号,例如流量、转速、晶体压力传感器以及经过参变量一频率转换后的信号等。本次试验采用测频法,通过方案优化,达到了较高的精度。

Dig_sel1 = 0;

Dig_sel0 = 0;

delay();

indata = P0;

Digit7 = indata & 0x0f;

Dig_sel0 = 1;

delay();

indata = P0;

Digit6 = indata & 0x0f;

Dig_sel1 = 1;

基于CPLD的频率计设计

基于CPLD的频率计设计摘要本文介绍了一种基于复杂可编程逻辑器件(CPLD)的频率计设计。

频率计是一种测量信号频率的仪器,广泛应用于电子工程、通信工程等领域。

本文首先简要介绍了频率计的原理和应用场景,然后详细阐述了基于CPLD的频率计的设计思路和实现步骤。

最后,通过实验验证了设计的可行性和准确性。

本文通过Markdown文本格式输出,便于阅读和理解。

引言频率计作为一种常用的测量设备,广泛应用于各个领域。

传统上,频率计主要使用模拟电路实现。

然而,随着数字电子技术的发展,CPLD逐渐成为一种流行的可编程逻辑器件,其具有体积小、功耗低和灵活性高等优点。

本文将介绍如何利用CPLD设计出一种精确可靠的频率计。

频率计原理频率计的基本原理是测量信号周期的倒数,即计算出信号的频率。

实现频率计需要以下几个步骤:1.输入信号经过滤波器,去除噪音和干扰。

2.使用计数器模块对输入信号进行频率计数。

3.使用定时器模块来确定计数的时间窗口。

4.根据计数结果和时间窗口的长度计算出信号的频率。

基于CPLD的频率计设计思路基于CPLD的频率计设计可以分为以下几个关键步骤:1.确定输入信号的范围和要求。

根据应用的具体需求,确定输入信号的频率范围和精度要求。

2.选择合适的CPLD芯片。

根据输入信号的要求,选择具有足够的计数器和定时器资源的CPLD芯片。

3.编写计数器和定时器的Verilog代码。

根据选定的CPLD芯片的特性,使用Verilog语言编写计数器和定时器的逻辑代码。

4.设计输入和输出接口。

根据具体的应用场景,设计CPLD芯片的输入和输出接口。

基于CPLD的频率计设计实现步骤1:确定输入信号的范围和要求在本设计中,假设输入信号的频率范围为1Hz到10MHz,要求测量精度为0.1Hz。

步骤2:选择合适的CPLD芯片根据步骤1的要求,选择支持至少10MHz频率计数的CPLD芯片。

步骤3:编写计数器和定时器的Verilog代码在这一步骤中,我们使用Verilog语言编写计数器和定时器的逻辑代码。

基于CPLD直接测频法的数字频率计设计

图( 3. 图 ) 此测 量模 块 的测量 位数 为 6 , 位 若想 改变频 率计 的测量位 数 , 可适 当 的改变 计数 器 的个数 , 则 并且 相 应模 块更 改相应 的参 数 , 如此就 可 以增 加或 者减 少频率计 的测量 范 围. 其顶层 电路仿 真 图见 图 4 .

器、 测频 控 制 信 号 发 生器 、 带有 时钟 使 能 端 的 计数 器 、 锁存 器 D G、 码 器 EN ODE 串联 动 态 扫描 模 块 RE 译 C 、

D MI 以及 6个 L D 显示 管组 成. 4 TS AO E 用 OMHz 的有 源 晶振作 为 F GA 的测 试标 准 频率 , P 经分 频 电 路最

过 计 算 在 一 定 时 间 内通 过 的 周 期 数 . 就 要 求 该模 块 的 能 产 生 一 个 周 期 为 1s的 技 术 使 能 信 号 E 这 NA,

并 且 还 要 同 步 对 每 一 个 计 数 器 的 使 能 端 进 行 控 制 . 数 器 在 使 能 端 为 高 电平 时 开 始 计 数 , 低 电 平 时 计 在 停 止 计 数 , 且 还要 保 持 计 数值 . 此 期 间 , 存 器 的 使 能 端 接 收 到 一 个 锁 存 的 上 升 信 号 , 且 将 计 数 并 在 锁 并 值 送 到 锁存 器 中 , 过 译 码 电路 译 码 再 经 显示 模 块 最 终 在 七 段 数 码 管 上 显 示 计 数 结 果 . 过 锁 存 器来 通 通

终得 到 1Hz 频率 . 信 号作 为 测频 控制 信 号发 生器 的输 入信 号 , 到 1s的 闸 门信号 用 来 控制 计 数 器计 1Hz 得

基于CPLD实现的DDS&频率计

基于STC89C51和CPLD实现的DDS与频率计系统框图功能描述:以STC89C51为控制核心,实现任意频率值fa(小于10KHz)的输入,经单片机出来后,生成相应的频率字,然后送给DDS模块,DDS模块开始工作,生成以频率值fs;但键盘测频键按下后,单片机控制频率计,让其开始控制,频率计输出值送回单片机处理,得出测量到的频率值fc,最后单片机控制LCD1602显示人为输入的频率值fa和频率计测得的频率值fc,两个值的差异可以直观的显示出系统的误差。

基于CPLD/FPGA的DDS原理图如下:基于CPLD/FPGA的频率计的原理图如下:DDS模块代码:(1)MUX832LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY MUX832 ISPORT( DATAINN : IN STD_LOGIC_VECTOR(7 DOWNTO 0);clk : in std_logic;DATAOUTT : OUT STD_LOGIC_VECTOR(31 DOWNTO 0);SELL :IN STD_LOGIC_VECTOR(1 DOWNTO 0));END MUX832;ARCHITECTURE behav OF MUX832 ISBEGINPROCESS(SELL,DATAINN,clk)BEGINif clk'event and clk='1' thenCASE SELL ISWHEN "00" => DATAOUTT(7 DOWNTO 0) <= DATAINN;WHEN "01" => DATAOUTT(15 DOWNTO 8) <= DATAINN;WHEN "10" => DATAOUTT(23 DOWNTO 16) <= DATAINN;WHEN "11" => DATAOUTT(31 DOWNTO 24) <= DATAINN;END CASE;end if;END PROCESS;END behav;(2)32位加法器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ADDER32B ISPORT ( A: IN STD_LOGIC_VECTOR(31 DOWNTO 0);B: IN STD_LOGIC_VECTOR(31 DOWNTO 0);S: OUT STD_LOGIC_VECTOR(31 DOWNTO 0));END ADDER32B;ARCHITECTURE behav OF ADDER32B ISBEGINS<=A+B;END behav;(3)32位寄存器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY REG32B ISPORT( LOAD : IN STD_LOGIC;DIN : IN STD_LOGIC_VECTOR(31 DOWNTO 0);DOUT : OUT STD_LOGIC_VECTOR(31 DOWNTO 0));END REG32B;ARCHITECTURE behav OF REG32B ISBEGINPROCESS(LOAD,DIN)beginIF LOAD'EVENT AND LOAD ='1' THENDOUT<=DIN;END IF;END PROCESS;END behav;频率计模块代码:(1)标准频率计数器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY BZHH ISPORT (BCLK: IN STD_LOGIC; --FsBENA: IN STD_LOGIC;CLR : IN STD_LOGIC; --清零BZQ : inOUT STD_LOGIC_VECTOR(31 DOWNTO 0));END BZHH;ARCHITECTURE behav OF BZHH ISBEGINPROCESS(BCLK, CLR) --标准频率计数开始BEGINIF CLR = '1' THEN BZQ <= (OTHERS=>'0');ELSIF BCLK'EVENT AND BCLK ='1' THENIF BENA ='1' THEN BZQ <= BZQ + 1;END IF;END IF;END PROCESS;END behav;(2)待测频率计数器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY TTFF ISPORT (TCLK: IN STD_LOGIC; --FsENA: IN STD_LOGIC;CLR : IN STD_LOGIC; --清零TSQ : inOUT STD_LOGIC_VECTOR(31 DOWNTO 0));END TTFF;ARCHITECTURE behav OF TTFF ISBEGINPROCESS(TCLK, CLR,ENA)BEGINIF CLR = '1' THEN TSQ <= (OTHERS=>'0');ELSIF TCLK'EVENT AND TCLK ='1' THENIF ENA ='1' THEN TSQ <= TSQ + 1;END IF;END IF;END PROCESS;END behav;(3)MUX648LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY MUX648 ISPORT( DATAIN1 : IN STD_LOGIC_VECTOR(31 DOWNTO 0);DATAIN2 : IN STD_LOGIC_VECTOR(31 DOWNTO 0);DATAOUT : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);SEL :IN STD_LOGIC_VECTOR(2 DOWNTO 0));END MUX648;ARCHITECTURE behav OF MUX648 ISBEGINDATAOUT <= DATAIN1(7 DOWNTO 0) WHEN SEL="000" ELSE --标准频率计低八位输出DATAIN1(15 DOWNTO 8) WHEN SEL="001" ELSEDATAIN1(23 DOWNTO 16) WHEN SEL="010" ELSEDATAIN1(31 DOWNTO 24) WHEN SEL="011" ELSE --标准频率计最高八位输出DATAIN2(7 DOWNTO 0) WHEN SEL="100" ELSE --待测频率计数值低八位输出DATAIN2(15 DOWNTO 8) WHEN SEL="101" ELSEDATAIN2(23 DOWNTO 16) WHEN SEL="110" ELSEDATAIN2(31 DOWNTO 24) WHEN SEL="111" ELSE --待测频率计数值最高八位输出DATAIN2(31 DOWNTO 24) ;END behav;单片机程序如下:主程序#include<reg52.h>#include<intrins.h>#include"key.h" //scankey(); keyexe(); setfre(); testfre(); #include"lcd1602.h" //display();void main(void){lcd_init();bena=0;clr=1;load_dds=0;oe=0;start=1;lcd_str(0,2,"dds.and.testfre!");while(1){keyexe();}}键盘程序:#ifndef __KEY_H__#define __KEY_H__#include<reg52.h>#include<intrins.h>#include "lcd1602.h"#define dinout P3;unsigned char keybuffer[8],longtochar[4],recieve[8];unsigned long freword,setdispbuf;unsigned long tfrecount,bfrecount; //Fs、Fx计数值unsigned long tfreword;//-----------pin define for dds and testfre------sbit sel2=P1^2;sbit sel1=P1^1;sbit sel0=P1^0;sbit oe=P2^3;//-----------pin define for dds loading ----------sbit load_dds=P2^4;//-----------pin define for testfre--------------sbit clr=P2^0;sbit bena=P2^1;sbit start=P2^2;//-----------delay programm----------------------void delay(unsigned int n){while(n--) _nop_();}//-----------format exchange---------------------void keytofreword(void){freword=keybuffer[0]*10000000+keybuffer[1]*1000000+keybuffer[2]*100000+k eybuffer[3]*10000+keybuffer[4]*1000+keybuffer[5]*100+keybuffer[6]*10+keybuffer [7];//合成输入频率值setdispbuf=freword;freword=(unsigned long)(freword*214.7493648);//计算相应的频率字longtochar[0]=(freword>>24)&0xff; //频率字最高八位longtochar[1]=(freword>>16)&0xff; //频率字次高八位longtochar[2]=(freword>> 8)&0xff; //频率字次低八位longtochar[3]=(freword) &0xff; //频率字最低八位}//-----------select channel-----------------------void select(unsigned char sel){unsigned char i,j;j=sel;sel=sel&0x07;i=P1;i=i&0xf8;i=i|sel;P1=i;}//-----------setting frequency--------------------void setfre(void){unsigned char i;keytofreword();display(setdispbuf,1); //显示输入的频率值lcd_str(0,2,"--setting.fre!-");oe=0;load_dds=0;for(i=0;i<4;i++){select(i);P3=longtochar[i];_nop_();_nop_();_nop_();load_dds=1;_nop_();_nop_();_nop_();load_dds=0;}lcd_str(0,2,"--setting.succ!-");}//----------test frequency------------------------void testfre(void){unsigned char i;unsigned int j;lcd_str(0,2,"--testing.fre---");bena=0;clr=0;_nop_();_nop_();_nop_();_nop_();clr=1; //-----clear register--------清零bena=1; //允许频率计开始工作delay1ms_x(1000); //门控时间2Sdelay1ms_x(1000);bena=0; //------count until start equals 0------------j=10000;while((start==1)&&(j--)); //----wait for end of testting or time out--- if(j==0)lcd_str(0,2,"--test.fre.err!-");elselcd_str(0,2,"-test.fre.succ!-");oe=1; //双向口for(i=0;i<8;i++){select(i);P3=0xff; //P3作为输入口_nop_();_nop_();_nop_();_nop_();recieve[i]=P3; //读取频率计计数值}oe=0;bfrecount=0;tfrecount=0;for(i=0;i<4;i++){bfrecount=(bfrecount<<8)+recieve[i]; //合成标准频率计数值tfrecount=(tfrecount<<8)+recieve[i+4]; //合成待测频率计数值}tfrecount=(unsigned long)tfrecount/3.5200886+1;//??????display(tfrecount,0);}//-------------------scan key value-------------------------unsigned char scankey(void) //键盘扫描{unsigned char i=0xff,k=0xfe,buf;unsigned code table[4]={0xfe,0xfd,0xfb,0xf7};for(i=0;i<4;i++){P1=table[i];buf=P1;if(buf!=table[i]){delay(1000);if(buf==P1){while(buf==P1);break;}}}switch(buf){case 0xee: return 1;case 0xed: return 2;case 0xeb: return 3;case 0xe7: return 10; //4case 0xde: return 4;//5case 0xdd: return 5;//6case 0xdb: return 6;//7case 0xd7: return 11; //8case 0xbe: return 7;//9case 0xbd: return 8;//0case 0xbb: return 9;//11case 0xb7: return 12;//12case 0x7e: return 13;//13case 0x7d: return 0;//14case 0x7b: return 14;//15case 0x77: return 15;//16default : return 16;//10}P1=0xff;}//-----------------key execution----------------------- void keyexe(void){unsigned char i,buf;buf=scankey(); //调键盘扫描,读取键值switch(buf){case 0:case 1:case 2:case 3:case 4:case 5:case 6:case 7:case 8:case 9: for(i=0;i<7;i++)keybuffer[i]=keybuffer[i+1];keybuffer[7]=buf;lcd_data1(0,1,'i');lcd_data1(1,1,'n');lcd_data1(2,1,'p');lcd_data1(3,1,'u');lcd_data1(4,1,'t');lcd_data1(5,1,':');lcd_data1(6,1,keybuffer[0]+'0');lcd_data1(7,1,keybuffer[1]+'0');lcd_data1(8,1,keybuffer[2]+'0');lcd_data1(9,1,keybuffer[3]+'0');lcd_data1(10,1,keybuffer[4]+'0');lcd_data1(11,1,keybuffer[5]+'0');lcd_data1(12,1,keybuffer[6]+'0');lcd_data1(13,1,keybuffer[7]+'0');lcd_data1(14,1,'H');lcd_data1(15,1,'z');break;case 10: lcd_cmd(clear);setfre();break;case 11: testfre();break;case 12: for(i=0;i<8;i++){keybuffer[i]=0;lcd_data1(i+6,1,keybuffer[i]+'0');}lcd_data1(14,1,'H');lcd_data1(15,1,'z');break;default: break;}}#endif。

基于cpld的简易数字频率计的设计

基于cpld的简易数字频率计的设计

基于CPLD的简易数字频率计的设计如下:

首先,将CPLD作为主控芯片,实现信号的采集、处理和控制。

通过输入的信号,经过滤波器去除噪音和干扰,然后使用计数器模块对输入信号的频率进行测量。

计数器模块将信号的周期转换成相应的脉冲数,再通过单片机进行数据处理,计算出信号的频率。

其次,利用单片机进行数据处理和显示。

单片机通过接收计数器模块的脉冲数,根据测量公式计算出信号的频率,并将结果显示在LCD屏幕上。

同时,单片机还负责控制CPLD的工作流程,实现整个系统的协调工作。

最后,通过仿真和测试验证设计的正确性和可行性。

测试结果表明,该数字频率计具有测量精度高、抗干扰能力强、稳定性好等优点,可以广泛应用于各种需要测量频率的场合。

基于CPLD的简易数字频率计的设计方法包括硬件设计和软件设计两部分。

硬件设计主要是利用CPLD和单片机等芯片进行电路设计和搭建;软件设计主要是利用CPLD编程语言和单片机编程语言进行程序编写和调试。

在实际应用中,需要根据具体需求和条件进行选择和调整。

cpld频率计课程设计

cpld频率计课程设计一、课程目标知识目标:1. 理解 CPLD 的基本概念、结构和工作原理;2. 掌握频率计的设计原理和实现方法;3. 学会运用 CPLD 技术设计简单的数字电路系统。

技能目标:1. 能够运用 CPLD 设计并实现一个功能完整的频率计;2. 培养学生动手实践能力,提高电路搭建和调试技巧;3. 提高学生分析问题、解决问题的能力。

情感态度价值观目标:1. 培养学生热爱科学,积极探索的精神;2. 培养团队合作意识,增强沟通与协作能力;3. 提高学生的创新意识,激发创新潜能。

课程性质:本课程为电子信息类专业的实践课程,旨在让学生通过实际操作,掌握 CPLD 技术及其在数字电路设计中的应用。

学生特点:学生已具备一定的电子技术和数字电路基础知识,具有一定的动手能力和探究精神。

教学要求:结合课程特点和学生实际情况,注重理论与实践相结合,强调实践操作和创新能力培养,确保学生能够达到课程目标所要求的知识和技能水平。

通过课程学习,使学生能够将所学知识应用于实际工程设计中,提高学生的职业素养和综合能力。

二、教学内容1. CPLD 基础知识回顾:CPLD 的基本概念、结构、工作原理及其特点,涉及课本第三章第一、二节内容。

2. 频率计设计原理:频率计的工作原理、电路组成和设计方法,包括课本第四章第三节内容。

3. CPLD 设计流程:设计输入、综合、布局布线、仿真和下载等步骤,参考课本第五章内容。

4. 频率计电路设计:使用 CPLD 设计频率计电路,包括时钟信号产生、计数器、显示驱动等模块,结合课本实例进行讲解。

5. 实践操作:分组进行频率计电路的搭建、调试和测试,培养学生动手实践能力。

6. 教学大纲:(1)第1周:CPLD 基础知识回顾,频率计设计原理学习。

(2)第2周:CPLD 设计流程讲解,频率计电路设计方法学习。

(3)第3周:分组进行频率计电路设计,教师指导与答疑。

(4)第4周:实践操作,完成频率计电路搭建、调试和测试。

基于CPLD的数字频率计的设计实现

基于 C L P D的 数 字 频 率计 的 设 计 实现

耿兴 隆, 李振川 , 马晓涛

( 北 软 件 职 业技 术 学 院 。 北 保 定 0 10 ) 河 河 7 0 0

摘要 : 频率计是常用的测量仪器 , 它通过对单位 时间内的信 号脉冲进行计 数测量 出信 号的频率。 L tc 用 ai t e公司生产 的

种 , 设 计介 绍 了使 用 一 片 IP S13 本 S L I02芯 片来

2 软 件 设 计

频率计工作时 , 先要产生一个计数允许信号 , 即闸门信号 , 闸门信号的宽度为单位时间, 例如 1 S 或 10m 。 闸门信号有效 的时 间内对被测信号 0 s 在 计数 , 即为信号频率 。 测量过程结束 , 需要锁存计

设 计数 字频率 计 的硬件 电路 和软 件设 计方 法 。 本设 计 为一 个 6位 数 字 频 率 计 , 以 测 量 1 9 9 可 9999

H 的信号频率。 z 设计过程主要分为 : 硬件设计 、 软 件设 计两 部分 。

收稿 日期 :0 0 0 — 2 2 1— 5 1

作者简介 : 耿兴隆(9 2 ) 男, 1 8一 , 河北衡水人 , 助教 , 在读工程硕士 , 要从 事嵌 入式系统、 主 数据 库和计算机控制等方 面的研 究; 李振川(9 0 )男 , 18 一 , 河北 辛集人 , 助教, 主要从事建筑工程 、 计算机 等方面的研 究。

5 2

河 北 软 件 职 业 技 术 学 院 学 报

语言 生成 相应的 目标 文件 , 过下载 电缆将代 码传送 到 目 通 标芯片 中进而完成设计的数字 系统 。 该方法设计灵活 , 便于

实现 。

为 1M z 脉冲发生器芯 片采用 C 4 6 。 D 00 0 h, D 0 0 C 46

基于CPLD的简易数字频率计设计

基于CPLD的简易数字频率计设计作者:毛会琼王军牛小玲来源:《电子技术与软件工程》2016年第19期摘要简易数字频率计的有效使用,为实际测量问题的有效处理带来了重要的参考依据。

在此形势影响下,合理地使用CPLD器件,可以优化简易数字频率计的设计方案,完善这种频率计的服务功能。

文中通过对频率计测频原理相关内容的阐述,客观地说明了实现基于CPLD简易数字频率计设计的重要性。

【关键词】CPLD 简易数字频率计设计方案服务功能在可靠的EDA技术及CPLD芯片支持下,可以设计出集成程度高、速度快的数字频率计,优化频率计各部分的组成功能。

基于CPLD简易数字频率计设计目标的实现,有利于增强电路仿真的准确性,扩大数字频率计的实际应用范围。

在具体的设计过程中,技术人员需要对CPLD的相关特点及简易数字频率计的设计要求进行必要地了解,确保最终得到的频率计在实际的应用中能够达到预期的效果。

1 基于CPLD的简易数字频率计各模块的设计1.1 设计原理结合CPLD芯片的优势,在具体的设计过程中,需要明确设计流程。

简易数字频率计设计的流程包括:被测信号fm输入到CPLD芯片里完成对被测信号的测频、计数、锁存、译码,输出信号接数码管显示。

通过这样的设计流程可知,CPFD芯片在简易数字频率计设计中占据着重要的地位,确保了规定时间内可以获得准确的被测信号。

1.2 CPLD模块原理相比一般的芯片,这种芯片的集成程度高,定制过程中充分地考虑了用户的实际需求。

在CPLD芯片的支持下,有利于完善简易数字频率计的测试功能,扩大测频范围。

设计方案制定的过程中,合理地运用CPLD芯片,可以雅虎硬件电路的设计方案,为数字频率计构建出控制、计数、锁存、译码的功能模块,并通过合理的方式构建出性能可靠的系统,深入理解COLD模块原理,可以增强简易数字频率计设计方案的适用性,最大限度地满足设计生产活动的各种需求。

1.3 控制电路模块的有效设计控制电路模块的有效使用,有利于增强系统的控制效果,优化数字频率计的服务功能。

基于cpld的频率测量计

基于cpld的频率测量计一、引言频率是指单位时间内重复发生的事件次数,是电子工程学中经常用到的概念之一。

例如,计算机系统中的频率就是指每秒钟的时钟脉冲数量。

而在电子测试和测量领域中,频率的测量也是非常重要的。

本文将介绍一种基于CPLD(Complex Programmable Logic Device)的频率测量计,它采用了基于数字技术的方法,能够非常准确地测量输入信号的频率。

二、系统设计CPLD是一种可编程逻辑器件,它可以根据用户的需求进行逻辑设计和综合实现。

该器件具有可重复使用性强、可编程性高、芯片密度大的特点,因此被广泛用于数字电路设计中。

在该频率测量计中,我们选用了普遍使用的CPLD型号——EPM240-F100C5。

系统设计中的各个部分功能如下所示:1. 信号输入模块:该模块用于接收原始的输入信号。

它实现了输入信号的滤波和防抖,保证了输入信号的稳定性。

在该模块中,我们使用了RC滤波电路和Schmitt触发器,对输入信号进行处理,以保证信号质量。

2. 信号计数模块:该模块用于对输入信号进行计数,并通过一个计数器来实现。

当计数器的值达到一定值时,我们就可以计算出输入信号的频率。

在该模块中,我们使用了CE (Clock Enable)触发器来实现计数器的计数功能,具有同时输入时钟和使能信号的特点。

3. 数字显示模块:该模块用于将测量出的频率通过数字方式显示出来。

我们采用了常见的七段数码管进行显示。

在该模块中,我们通过对七段数码管的控制来实现数字的显示。

4. 系统控制模块:该模块用于对整个测量系统进行控制和管理。

它包括开关机控制、复位控制、频率计算等功能。

我们使用了一个简单的有限状态机(FSM)来控制这部分功能。

三、实现过程除了上述四个模块之外,该频率测量计还需要使用一些额外的器件,如RC滤波电路、Schmitt触发器、CE触发器、七段数码管等。

这些器件的选型和接线将直接影响到最终的测量结果,因此要特别注意。

基于cpld的频率计设计

本科生毕业设计基于CPLD的频率计设计Design of the Frequency Meter based on CPLD学生姓名专业学号指导教师学院毕业设计(论文)原创承诺书1.本人承诺:所呈交的毕业设计(论文)《基于CPLD的频率计设计》,是认真学习理解学校的《长春理工大学本科毕业设计(论文)工作条例》后,在教师的指导下,保质保量独立地完成了任务书中规定的内容,不弄虚作假,不抄袭别人的工作内容。

2.本人在毕业设计(论文)中引用他人的观点和研究成果,均在文中加以注释或以参考文献形式列出,对本文的研究工作做出重要贡献的个人和集体均已在文中注明。

3.在毕业设计(论文)中对侵犯任何方面知识产权的行为,由本人承担相应的法律责任。

4.本人完全了解学校关于保存、使用毕业设计(论文)的规定,即:按照学校要求提交论文和相关材料的印刷本和电子版本;同意学校保留毕业设计(论文)的复印件和电子版本,允许被查阅和借阅;学校可以采用影印、缩印或其他复制手段保存毕业设计(论文),可以公布其中的全部或部分内容。

以上承诺的法律结果将完全由本人承担!作者签名:• 年•• 月•••日摘要频率测量是电子测量领域最基本也是最重要的测量之一。

但基于传统测频原理的频率计在测频时测量精度将随被测信号频率的下降而降低,在实用中有较大的局限性。

因此,本文提出了一种基于CPLD的数字频率计的设计方法。

该设计电路简洁,软件潜力得到充分挖掘,低频段测量精度高,有效防止了干扰的侵入,把CPLD具有的编程灵活,适用范围宽,价格大众化等优点用于实现频率计的设计。

该频率计采用先进的EDA技术及自上而下的设计,使用流行的VHDL语言编程,并在Max+plusII软件平台上进行编译仿真。

经过硬件调试和软件仿真后结果证明此设计方案符合毕设要求和技术参数。

关键词:频率计 EDA技术 CPLDABSTRACTFrequency measurement is the most basic electronic and also one of the most important measure in the measurement field. But the accuracy of frequency meter which is based on the traditional principle will vary depending on the measured signal frequency and the lower, has great limitations in the practical in frequency measurement. Therefore, this article puts forward a design method of digital frequency meter based on CPLD. The advantage such as the CPLD programming flexibility, wide applicable scope, and the popular price etc, are used to implement the frequency meter design by the simple circuit design, the fully excavate of software potential, the precision in low frequency measurement, and the effectively prevent of the invasion of the interference. The frequency meter design which is from top to bottom adopts the advanced EDA technology and popular VHDL language programming, and compiling on Max + plusII software platform simulation.Key words: frequency meter; EDA; CPLD目录摘要 (I)ABSTRACT .......................................................... I I 第1章绪论 .. (1)1.1背景 (1)1.2频率计设计的目的和意义 (1)1.3论文所做的工作及研究内容 (2)第2章设计环境介绍 (3)2.1EDA技术的发展及VHDL简介 (3)2.1.1 EDA技术的发展 (3)2.1.2 VHDL简介 (3)2.1.3 CPLD器件及其特点 (4)2.2基于EDA的CPLD/FPGA设计流程 (4)2.2.1 设计输入 (4)2.2.2 综合 (5)2.2.3 适配 (5)2.2.4 时序仿真与功能仿真 (5)2.2.5 编程下载 (5)2.2.6 硬件测试 (5)2.3M AX+P LUSⅡ开发工具 (6)2.3.1 Max+PlusⅡ开发系统的特点 (6)2.3.2 Max+PlusⅡ的功能 (6)2.3.3 Max+PlusⅡ的设计过程 (6)第3章频率计的设计原理及方案 (8)3.1频率计的设计原理 (8)3.1.1 直接测频法原理 (9)3.1.2 等精度测频法原理 (9)3.2频率计的设计方案 (10)3.2.1 基于直接测频法的设计方案 (10)3.2.2 基于等精度测频法的设计方案 (11)第4章频率计硬件与软件 (14)4.1频率计硬件 (14)4.1.1 电源部分 (14)4.1.2 整形部分 (15)4.1.3 CPLD芯片 (15)4.1.4 显示部分 (16)4.1.5 键盘部分 (17)4.2频率计软件 (18)4.2.1 分频器模块 (18)4.2.2 闸门定时模块 (19)4.2.3 测频控制信号发生器模块 (20)4.2.4 计数器模块 (22)4.2.5 锁存器模块 (23)4.2.6 显示模块 (24)第5章调试 (25)5.1硬件调试 (25)5.1.1 静态调试 (25)5.1.2 连机仿真、在线动态调试 (25)5.2软件调试 (26)参考文献 (28)致谢 (29)附录1 设计源程序 (30)直接测频法 (30)等精度测频法 (33)附录2 电路图 (44)基于CPLD的频率计顶层电路设计图(1)---直接测频法 (44)基于CPLD的频率计顶层电路设计图(2)---等精度测频法 (45)基于CPLD的频率计硬件电路设计图(3)---直接测频法 (46)基于CPLD的频率计硬件电路设计图(4)---等精度测频法 (47)第1章绪论1.1 背景20世纪后期,随着信息技术、电子技术的飞速发展,现代电子产品几乎渗透了社会的各个领域,有力地推动了社会信息化程度的大大提高和社会生产力的发展。

基于CPLD的数字频率计

湖南工程学院课程设计课程名称嵌入式系统课题名称基于CPLD的简易数字频率计专业电子信息工程班级学号姓名指导教师2011年12 月日湖南工程学院课程设计任务书课程名称:嵌入式系统题目:基于CPLD的简易数字频率计专业班级:学生姓名:指导老师:审批:任务书下达日期 2011 年12 月日设计完成日期 2011 年 12月日目录任务书 (4)1 设计目的和要求 (4)2任务日期 (5)一、设计总体思路和基本框图 (6)1 设计总体思路 (6)2 基本原理 (8)3 总体框图 (8)二、各单元模块设计…………………………………………………………………………..错误!未定义书签。

1模块FEN…………………………………………………………………………...错误!未定义书签。

2模块SEL……………………………………………………………………………错误!未定义书签。

3 模块CORNA (19)4 模块LOCK (19)5 模块CH (19)6 模块DISP (19)7 模块YM (19)三、顶层文件设计……………………………………………………………………………..错误!未定义书签。

1 总体电路图 (19)四、调试下载………………………………………………………………………….错误!未定义书签。

五、心得体会…………………………………………………………………………………..错误!未定义书签。

六、参考文献…………………………………………………………………………………...错误!未定义书签。

七、评分表……………………………………………………………………………………..错误!未定义书签。

一.设计总体思路,基本原理和框图1.设计总体思路采用现场可编程门阵列(FPGA)为控制核心,利用VHDL语言编程,下载烧制实现。

将所有器件集成在一块芯片上,体积大大减小的同时还提高了稳定性,可实现大规模和超大规模的集成电路,测频测量精度高,测量频率范围大,而且编程灵活、调试方便.2.基本原理众所周知,频率信号易于传输,抗干扰性强,可以获得较好的测量精度。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

wae c ru t e in i u i gt e C L e h oo y w i e d sg f n— ma h n n efc n ot r rg a o efe u n y me r i i d s s sn P D tc n lg hl t e in o c g h eh ma ・ c i ei tra e a d s f wa ep o r m f h r q e c - t -

Abs r t te e tng o r wae a ot r rs a c m p e o tac :Af rtsi fhad r nd s fwae pat , o lx c mprh nsv x e me sc mp ee n t i p r e e ie e p r nti o l td i h spa i e ,wh s a d oe h r—

维普资讯

第 6卷

第 2期

实 验 科 学 与 技 术

・l 3・

CL P D和 虚 拟 仪 器 的 频 率 计 综 合 设 计

詹 惠琴 ,古 军

( 电子科技大学 自动化工程学院 ,成都 6 05 ) 10 4

摘 要 :在 自制 的 虚 拟 仪 器 实验 箱 和 C L 实验 板及 通 用计 算 机 上 ,采 用 C L 技 术 设 计 了测 量 频 率 的 硬 件 电路 和 虚 拟 仪 器 PD PD 的 Lb IW 图形 语 言 开发 平 台 ,设 计 了频 率计 的 人 机 界 面 和软 件 程 序 ;通 过 软 硬 件 调 试 和 测试 , 完成 了一 个 较 复 杂 的 综 合 aV E 性 、设 计 性 实验 。 文 中的 实验 综合 应 用 了电子 测 量 原 理 、数 字 电路 技 术 、C L 术 、虚 拟仪 器 、程 序 设 计 等 课 程 的 知 识 P D技

s n n s in v t e ne si g d a c d e p o aie fe e u i g o u d a hn ,ah e a c ia n d l rd sg sa i i g i n o a v ,i tr t ,a v e a x l rt .A t r sn fg i et c i g ir rh c a d mo u a e in i - g i e n n d n v h t e l d pe o td,w ih ma e t e e p r n r p r t e a d o ih p bi i . h c d h x i e me tmo e o ai hs u l t e v n f cy Ke r s:s n e i x rme t y wo d y t sse p i n ;CP D d s n;vr a n t me t me u rq e c h e L ei g i u i sr tl u n; s e a r fe u n y

中图分类号 :T 9 ;T 3 1 M33 P 1

文献标识码 :A

文章编号 :17 45 (0 8 0 0 1 0 62— 5 0 2 0 )2— 0 3— 4

A e u n y M e e p rm e twih S n h ss a d De i n Fr q e c t r Ex e i n t y t e i n sg

Ba e o s n CPLD n ru lI sr m e t a d Vit a n tu n

Z N Hu— i ,GU J n HA iqn u

( ol eo uo ai ,U i ri fEet ncSineadTc nl yo hn ,C egu 6  ̄ 5 C lg f tm t n nv syo l r i c c n ehoo f ia hnd 1 4,C ia e A o e t co e g C hn )

和技 术,理论结合 实际,其设计思想新颖 ,具有启发性 、设计性 、趣味性 、先进性 、探 索性 等特点。分析过程 中应 用引导

式教 学 ,进 行 了层 次 化 、模 块 化 设 计 ,使 实验 更 具 可 操 作 性 和 推 广 意 义 。 关 键 词 :综 合 实验 ;C L P D设 计 ;虚 拟 仪 器 ;频 率测 量

me u m n , i t i ut C L Vr a isu n , r a ei ig e . hoy on t i rc c , i t u h o — se a r et D ga c ci, P D, iu t met Po m D s nn , t T er cn e e wt pat e t sh gt f e i lr tl n r s r g g c cd h i h o d

t ra eba e n t e G a g a e La e r s d o l n u g bVI h EW fv ru lisr me t .Th se p rme s b s d o h o it a n tu n s i x i nti a e n t e CPLD h p o h it a n tu nt e c i rt e v ru li sr me s e pe me tb x a d g ne a o utr The e e rme ti e ae ai u n wl g n e hn lg e s c s Prn i l f ee to i x r i n o n e rlc mp e . xp i n ntg td v ro s k o e e a d t c oo is. u h a i c p e o l cr n c r d