第7章 混合集成电路失效分析典型案例(134-159)

最新失效经典案例分享

失效分析经典案例-设计缺陷失效

485通讯电路 设计缺陷案例

结论: 100Ω与MOV串联,30V、nS级的脉冲 在MOV上的电压为5.4V。(约1/6)

对MOV直接放电 放电电压=50V

通过100Ω对MOV放电 放电电压=30V 100 Ω上的电压波形(24.6V)

Vz=10V

4

功能 环境 极端条件 可靠性 维修性 测试性 安全性 保障性 …

温度应力 潮湿应力 振动应力 冲击应力 电磁应力 综合应力 软件运行 …

电应力 温度应力 …

可靠性因素

设计

样机

中试

试产

批产

老炼

使用

设计

物料

结构

工艺

原理 结构 元器件 容差 热 电磁兼容 防浪涌 装配工艺 …

暴露缺陷 完善设计: 原理 结构 物料 工艺

中国赛宝实验室 15

失效分析经典案例-电梯控制板失效

信息

电梯控制的PCBA,进口,对PCBA进行功能检测时, 100块板有20块板发生故障——占20%。 PCBA故障定位:所有故障的PCBA均发生在IC6(板 上位号)集成电路(CPLD)——同一器件 所有失效的CPLD均发生在Pin39,表现为与地(电 源负端)漏电、短路——同一引脚 怀疑:PCBA漏电,IC6漏电、损伤 PCB? 焊接? IC? 过电? 陷? …

失效分析经典案例-设计缺陷失效

485通讯电路 设计缺陷案例

通过L1对MOV放电 放电电压=80V MOV上的电压波形(10.4V)

现场通讯线上的电压波形 9峰峰=42.6V 9最大=24.8V

•同一机柜中 •通讯线长≈60cm •柜。门均接地 •线槽无动力线

电子元器件失效分析具体案列

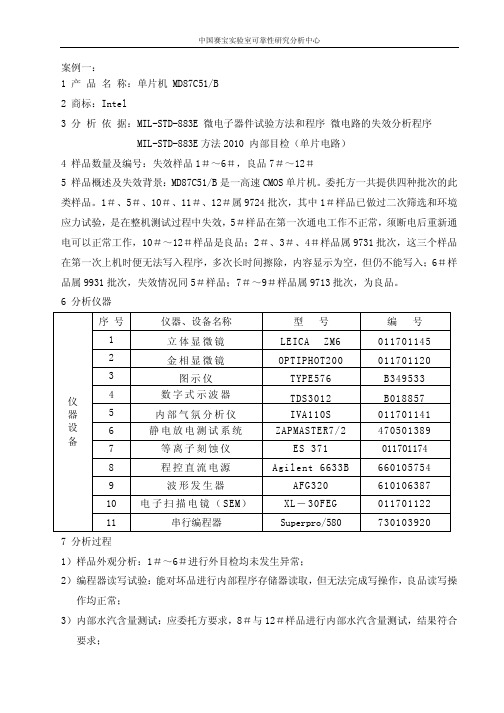

中国赛宝实验室可靠性研究分析中心案例一:1产品名称:单片机MD87C51/B2商标:Intel3分析依据:MIL-STD-883E 微电子器件试验方法和程序微电路的失效分析程序MIL-STD-883E 方法2010 内部目检(单片电路)4样品数量及编号:失效样品1#~6#,良品7#~12#5样品概述及失效背景:MD87C51/B是一高速CMOS单片机。

委托方一共提供四种批次的此类样品。

1#、5#、10#、11#、12#属9724 批次,其中1#样品已做过二次筛选和环境应力试验,是在整机测试过程中失效,5#样品在第一次通电工作不正常,须断电后重新通电可以正常工作,10#~12#样品是良品;2#、3#、4#样品属9731 批次,这三个样品在第一次上机时便无法写入程序,多次长时间擦除,内容显示为空,但仍不能写入;6#样品属9931 批次,失效情况同5#样品;7#~9#样品属9713 批次,为良品。

6分析仪器7 分析过程1)样品外观分析:1#~6#进行外目检均未发生异常;2)编程器读写试验:能对坏品进行内部程序存储器读取,但无法完成写操作,良品读写操作均正常;3)内部水汽含量测试:应委托方要求,8#与12#样品进行内部水汽含量测试,结果符合要求;中国赛宝实验室可靠性研究分析中心4)端口I -V 特性测试:使用静电放电测试系统剩下的样品进行I-V 端口扫描测试,发现:4#样品的Pin3、Pin4 、Pin5 、Pin7 对地呈现明显的电阻特性,使用图示仪测试后测得Pin3 对地呈现约660Ω 阻值、Pin4 与Pin5 对地呈现约300Ω 阻值、Pin7 对地呈现约140 Ω 阻值,且在1#与4#样品的Pin31(EA/Vpp)发现特性曲线异常,但并非每次都能出现;其他样品的管脚未发现明显异常;5)开封和内部分析:对1#~5#样品进行开封,内目检时发现:芯片的铝键合丝与键合台以外相邻的金属化层(有钝化层覆盖)存在跨接现象。

电子元器件失效分析具体案列

图 1 Pin17 已熔断内引线

图 2 Pin17 已熔断内引线

中国赛宝实验室可靠性研究分析中心

图 3 击穿点及引线损坏形貌

图 4 过电形貌

图 5 内部电路过电形貌

图 6 内部电路击穿点形貌

图 7 内部电路击穿点形貌

图 8 内部电路击穿点形貌

中国赛宝实验室可靠性研究分析中心

案例三:

1 产品名称及型号:通信 IC PMB6850E V2.10

作均正常;

3)内部水汽含量测试:应委托方要求,8#与 12#样品进行内部水汽含量测试,结果符合

要求;

中国赛宝实验室可靠性研究分析中心

4)端口 I-V 特性测试:使用静电放电测试系统剩下的样品进行 I-V 端口扫描测试,发现: 4#样品的 Pin3、Pin4、Pin5、Pin7 对地呈现明显的电阻特性,使用图示仪测试后测得 Pin3 对地呈现约 660Ω阻值、Pin4 与 Pin5 对地呈现约 300Ω阻值、Pin7 对地呈现约 140

___

Ω阻值,且在 1#与 4#样品的 Pin31( EA /Vpp)发现特性曲线异常,但并非每次都能 出现;其他样品的管脚未发现明显异常; 5)开封和内部分析:对 1#~5#样品进行开封,内目检时发现: 芯片的铝键合丝与键合台以外相邻的金属化层(有钝化层覆盖)存在跨接现象。在拉 断铝丝后,可见到铝丝通过超声键合已粘接在相邻的地连线或膜电阻上,并粘附着铝丝被 粘连的铝屑见图 2~图 4。拉断铝丝后均能观察到键合台邻近的工作金属线或膜电阻上存在 铝丝残存的碎屑,说明铝丝存在键合跨接。 统计发现,在 3#与 4#样品中,每只样品的 40 个键合台均有 27 个存在铝丝键合 与其相连的工作金属化铝连线(地线或膜电阻)跨接粘连的问题。

集成电路失效分析新技术

超声换能器在样品上方以光栅的方式作机械扫描 , 通过改变换能器的水平位置, 在平面上以机械扫 描的方式产生一幅超声图像 。 在 C-SAM 的图像中 , 与背景相比的衬度变化 构成了重要的信息, 在有空洞、 裂缝、 不良粘接 和分层剥离的位置产生高的衬度, 因而容易从背 景中区分出来。 衬度的高度表现为回波脉冲的正 负极性, 其大小是由组成界面的两种材料的声学 阻抗系数决定, 回波的极性和强度构成一幅能反 映界面状态缺陷的超声图像 。 超声探头的主要技术指标是声波的频率。 其 横向分辨率、 穿透深度与声波频率有关。 频率越 低 , 横向分辨率越差 , 但穿透深度越大 。 用 C-SAM 来检测塑封 IC 的照片如图 2 所示 。 由于再流焊引起的热效应, 渗入塑封材料内的水 汽发生膨胀 , 塑料与管脚间出现明显的分层 。

对准被测节点、 失效分析速度加快的特点, 在钝 化层较薄的情况下可以不去掉钝化层 。 用电子束测试技术进行信号寻迹失效定位必 须多次选择探测点 。 一种叫 Navigation 的软件能把

EBT 与现代电子设计自动化 (EDA ) 技术相结合 ,

可根据设计版图、 网表和线路图在实际芯片的扫 描电镜图像上实时地确定电子束在芯片上的探测 点, 提取被测节点的逻辑波形信号, 进而迅速地 对电路的失效节点进行失效定位或设计验证, 如 图 3、 4 所示 。

失效分析用 X 射线透视技术的原理与医用完全 相同。 样品局部缺陷造成该处吸收系数异常, 引 起 X 射线透视像 的局部衬度 异常 。 此 技 术 主 要 用 于电子元器件的内引线断裂、 金属化层断裂的观 察 。 X 射线透视像的横向分辨率为 10 !m , 这是由

X 射线的波长决定的 。 过电应力引起的 FPGA 电源 内引线烧断的 X 射线透视照片如图 1 所示 。 C-SAM 利用超声脉 冲探测样品 内部空隙等 缺

集成电路测试技术五_芯片失效模式及分析

芯片失效模式及影响分析集成电路常见的失效(续)雷鑑铭1、聚焦离子束(FIB)介绍与应用在去封胶、打线或封装后必须再次测试建议提供GDSII电路图文件以利导引指定区块线路•电子束探测系统(E-Beam Prober)是利用极精准的聚焦电子束来取代一般的机械式探针,以VC4、新型FIB电路修正技术也面临同样的定位问题。

面对IC表面没有高低起伏而无法成像,FIB 必须配合IC设计布局图数据(GDSII)及自动定位系统来找到工作点。

先进的FIB机型皆配备有CAD 导航迭图的软件(CAD Navigation) 可以将IC表面与IC设计者提供的线路布局图作重去大量扫瞄IC表面造成的离子轰击伤害,有效的减少IC特性漂移,提高FIB的2、信号引出: 藉由金属导线将目标点信号引出进行验证测试。

因为整个联机路径的电阻、电感较使用探针小而且稳定度较雷鑑铭1、超音波扫瞄检测•超音波显微镜(SAT)是指Scanning AcousticTomography的简称,而Tomography 的意思即是”断层扫瞄摄影”。

又称为SAM (Scanning Acoustic Microscope),应用于电子产品之超音波频率是指高于20KHz者,可以穿透一定厚度的固态与液态物质,以检测其结构组成之变异。

目前使用之介质,通常为纯水,为最便宜与安全之物质。

•超音波检测之基本原理系利用超音波信号发射源(Transducer,俗称探头)并以纯水为介质而传导到待测物体上,经由超音波的回声反射或穿透等的动作,让此信号在机台经过特定软件处理呈现影像。

Transducer的选择会因为待测物之厚度与材质而有不同选择。

•电子产品主要使用SAT来进行结构脱层(Delamination)或裂缝(Crack)等的检测之用X光射线(以下简称X-RAY) 是利用一阴极射线管,发出高能量的电子,使其撞击到金属靶上,在撞击过程中,因电子突然减速,其损失的动能芯片尺寸量测,打线线弧量测,组件吃锡面积比例量测。

集成电路中esd失效机理分析

1.2静电放电危害

由于物体间的接触分离(如摩擦、剥离、撕裂和搬运中的碰撞等)或电场感应,都会因物体之间或物体内部带电粒子的扩散、转移或迁移而形成物体表面电荷的积聚,即呈现带电现象。这种现象的存在,有可能导致物体表面电荷对空气中带异性电荷的微粒子尘埃的吸引造成电子敏感元器件绝缘性能的降低、结构腐蚀或破坏。当外界条件适宜时,这种积聚电荷还会产生静电放电,使元器件局部破损或击穿,严重时,还会引起火灾、爆炸等。曾报道某厂在修理程控交换机上的半导体集成电路时因静电引起爆炸事故的文章[1]。应当指出,静电引起电子元器件局部结构破损和性能降低,是对元器件使用寿命的一种潜在威胁,因为它难于检验,故造成事故的随机性更大,并且易于与其他失效原因混淆而被掩盖。

ESD保护电路的作用在于将出现在芯片管脚上的高电荷按照预先设计好的路径泄放掉,进而防止静电对内部电路的损坏。所以通过对ESD引起失效的器件进行物理失效分析,将有利于改善ESD电路性能和提高ESD防护等级。本文将对静电产生的危害及相关静电模型和ESD失效机理以及失效特征和如何进行预防进行阐述。

1

1.1静电产生的物理原理

(a)典型I/O接口

(b)I-V曲线

图1典型I/O电路及其I-V曲线

2.1.2突发性完全失效和潜在性失效

1.突发性完全失效

突发性完全失效是器件的一个或多个电参数突然劣化,完全失去规定功能的一种失效。通常表现为开路、短路以及电参数严重漂移。

半导体器件ESD损伤失效现象主要表现为:

• 介质击穿

集成电路失效分析及案例分享

G O A

Vcom 8

Vcom 9 Vcom 10

Rx

TFT-LCD结构分析

ITO (Rx)

ITO Dummy

Half pitch ITO(Rx)

TFT-LCD模组结构厚度

LC Gap

LTPS TFT

Al LTPS Gate

V pixel ITO

Al to LTPS contact

V pixel ITO

3D X-Ray应用介绍-Wire Bonding

• • • •

•

IC 整体观察 裂键观察 楔键倾斜观察 最大倍率自上到下楔形键合金属 线的观察 堆叠芯片的观察

3D X-Ray应用介绍-焊接检查

• • • 自动计算芯片贴敷孔隙率 手动和自动区域检测 通过/失败的信息提示

3D X-Ray应用介绍-元器件、PCBA及IC Package

×

0.1 ~ 1 at.% 2 ~ 10nm 10µ m

×

ppm 3nm 10mm

×

0.1 ~ 1 at.% 0.5µ m 0.3µ m

×

0.1 ~ 1 at.% 1um~3um 10 ~ 100µ m

×

-~ 10nm < 1nm

×

×

√

×

×

√

×

Mapping

NDT

√

√

√

√

√

√

×

√

√

√

×

√

√

√

电性失效分析

元器件2维图像 元器件3维重构 多层板的横截面

3D X-Ray应用介绍-Chip Level

3D X-Ray应用介绍-LED

Measurement

集成电路的失效分析方法以及相应技术分析

集成电路的失效分析方法以及相应技术分析作者:高乘源来源:《中国新技术新产品》2016年第17期摘要:伴随着科学技术在我国不断地发展以及应用,集成电路在我国有了非常广泛的应用和发展。

我国集成电路现在已经向着尺寸更小的方向发展,具有了集成程度非常高的技术。

伴随着集成电路在我国的不断应用,集成电路应用中的失效分析变得越来越重要。

集成电路的芯片上有上千甚至上万个电气元件,在失效的集成电路芯片中寻找失效的器件是一件非常困难的工作。

本文主要针对我国集成电路的失效问题进行详细地分析以及阐述,希望通过本文的阐述以及分析能够有效地提升我国集成电路失效分析的能力,同时也为我国集成电路的进一步发展以及创新贡献力量。

关键词:集成电路;电性分析;失效分析;物理分析;方法;技术中图分类号:TN43 文献标识码:A集成电路在我国的失效分析主要就是一种失效问题的判断模式,通过集成电路的失效分析,找出导致集成电路失效的主要原因,分析并且清楚集成电路失效的主要机理,通过失效分析来采取技术措施有效地规避集成电路类似的失效问题的再次发生。

在集成电路的正常运行过程中,失效分析是一项非常重要的工作,通过失效分析的正常开展能够有效提升集成电路的可靠性以及安全性。

对于相关企业来说,进行集成电路的失效分析可以有效地提升企业相关问题的分析以及试验能力,通过失效分析,企业能够实行相应的控制和改进,能够防止集成电路的再次失效,以及减少集成电路的失效种类。

在分析集成电路的失效过程中,我们要求采用先进的分析设备,科学的分析技术,专业的分析人员来有针对性地进行分析,这样才能够有效地保障集成电路失效分析的准确性以及合理性。

1.简要叙述我国集成电路在失效分析过程中的主要步骤现阶段在集成电路的失效分析过程中,我们主要有4个步骤来进行失效分析。

步骤一:针对失效集成电路开封前的检查。

步骤二:针对失效集成电路开封并且采取镜检。

步骤三:失效集成电路的电性分析。

步骤四:失效集成电路的物理分析。

集成电路失效分析方法与技术探究

集成电路失效分析方法与技术探究【摘要】集成电路的应用十分广泛,随着集成电路向着更小工艺尺寸,更高集成度方向发展,集成电路失效分析扮演着越来越重要的角色。

一块芯片上集成的器件可达几千万,要想找到失效器件实属大海捞针,因此进行集成电路失效分析必须具备先进、准确的技术和设备,并由具有专业知识的半导体分析人员开展分析工作。

【关键词】集成电路;失效分析;电性分析;物理分析失效分析就是判断失效的模式,查找失效原因,弄清失效机理,并且预防类似失效情况再次发生。

集成电路失效分析在提高集成电路的可靠性方面有着至关重要的作用,对集成电路进行失效分析可以促进企业纠正设计、实验和生产过程中的问题,实施控制和改进措施,防止和减少同样的失效模式和失效机理重复出现,预防同类失效现象再次发生。

本文主要讲述集成电路失效分析的技术和方法。

1.集成电路失效分析步骤集成电路的失效分析分为四个步骤。

在确认失效现象后,第一步是开封前检查。

在开封前要进行的检查都是无损失效分析。

开封前会进行外观检查、X光检查以及扫描声学显微镜检查。

第二步是打开封装并进行镜检。

第三步是电性分析。

电性分析包括缺陷定位技术、电路分析以及微探针检测分析。

第四步是物理分析。

物理分析包括剥层、聚焦离子束(FIB)、扫描电子显微镜(SEM)、透射电子显微镜(TEM)以及VC定位技术。

通过上述分析得出分析结论,完成分析报告,将分析报告交给相关技术人员。

相关技术人员根据相应的缺陷进行改进,以此来实现对集成电路失效分析的意义。

2.无损失效分析技术所谓无损失效分析,就是在不损害分析样品,不去掉芯片封装的情况下,对该样品进行失效分析。

无损失效分析技术包括外观检查、X射线检查和扫描声学显微镜检查。

在外观检查中,主要是凭借肉眼检查是否有明显的缺陷,如塑脂封装是否开裂,芯片的管脚是否接触良好等等。

X射线检查则是利用X射线的透视性能对被测样品进行X射线照射,样品的缺陷部分会吸收X射线,导致X射线照射成像出现异常情况。

集成电路可靠性研究中的失效机理分析

集成电路可靠性研究中的失效机理分析集成电路(Integrated Circuit,简称IC)是实现电子系统功能的基本组成部分,是现代通讯、计算机、消费电子等领域中不可或缺的关键技术之一。

在集成电路的应用过程中,由于在电气和物理环境下的各种影响,不同程度的失效问题会不可避免地出现。

因此,对于集成电路可靠性研究中失效机理的分析和研究是至关重要的。

本文将介绍集成电路可靠性方面的一些基本概念和失效机理,并探讨在集成电路可靠性研究中失效机理分析的方法和技术。

一、集成电路可靠性概述集成电路可靠性指的是在集成电路运行过程中,其功能性能能够在一定时间和环境下保持稳定的能力。

集成电路可靠性研究是为了保证集成电路长期运行的可靠性和稳定性,避免集成电路失效所带来的经济和社会成本。

集成电路失效问题采用的原因比较复杂,包括以下因素:1.工艺和制造因素。

因为每个集成电路都需要经过工艺制造的过程,一旦制造中有质量问题,就很有可能会导致集成电路中失效问题的产生。

2.环境和应力因素。

包括温度、湿度、气体氛围、电场、电磁干扰等因素,这些因素都会对集成电路的正常工作产生不同程度的影响。

3.设计和电路因素。

设计、电路和构造缺陷也会导致集成电路失效,如电路不稳定、噪声和振荡问题等。

针对这些原因,集成电路可靠性研究主要从以下几个方面入手:1.制造和工艺问题,着重解决集成电路质量的问题。

2.环境和应力问题,对集成电路进行外界环境下的可靠性测试。

3.设计和电路问题,进行电路的分析与优化,消除电路缺陷和提高可靠性。

二、失效机理分析1.封装失效集成电路封装是将芯片封装在外露引脚的封装体中,保护芯片免受环境和机械影响。

集成电路封装失效主要包括以下因素:(1)焊接裂纹焊接裂纹是由于制造和装配过程中的高温应力和冷却过程中的温度梯度导致的。

当芯片和封装之间的焊点裂纹时,电路间可能会产生断路或短路现象。

(2)接触不良接触不良是指由于封装中引脚连接不牢固,或引脚与板间距离太小等因素导致引脚接触不良,从而导致电路的性能下降或直接失效。

ESD引起集成电路损坏原理模式及实例

ESD引起集成电路损坏原理模式及实例一.ESD引起集成电路损伤的三种途径(1)人体活动引起的摩擦起电是重要的静电来源,带静电的操作者与器件接触并通过器件放电。

(2)器件与用绝缘材料制作的包装袋、传递盒和传送带等摩擦,使器件本身带静电,它与人体或地接触时发生的静电放电。

(3)当器件处在很强的静电场中时,因静电感应在器件内部的芯片上将感应出很高的电位差,从而引起芯片内部薄氧化层的击穿。

或者某一管脚与地相碰也会发生静电放电。

根据上述三种ESD的损伤途径,建立了三种 ESD损伤模型:人体带电模型、器件带电模型和场感应模型。

其中人体模型是主要的。

二.ESD损伤的失效模式(1)双极型数字电路a.输入端漏电流增加b.参数退化c.失去功能,其中对带有肖特基管的STTL和LSTTL电路更为敏感。

(2)双极型线性电路a.输入失调电压增大b.输入失调电流增大c.MOS电容(补偿电容)漏电或短路d.失去功能(3)MOS集成电路a.输入端漏电流增大b.输出端漏电流增大c.静态功耗电流增大d.失去功能(4)双极型单稳电路和振荡器电路a.单稳电路的单稳时间发生变化b.振荡器的振荡频率发生变化c.R.C连接端对地出现反向漏电。

三.ESD对集成电路的损坏形式a.MOS电路输入端保护电路的二极管出现反向漏电流增大b.输入端MOS管发生栅穿c.MOS电路输入保护电路中的保护电阻或接触孔发生烧毁d.引起ROM电路或PAL电路中的熔断丝熔断e.集成电路内部的MOS电容器发生栅穿f.运算放大器输入端(对管)小电流放大系数减小g.集成电路内部的精密电阻的阻值发生漂移h.与外接端子相连的铝条被熔断i.引起多层布线间的介质击穿(例如:输入端铝条与n+、间的介质击穿)四.ESD损伤机理(1)电压型损伤a.栅氧化层击穿(MOS电路输入端、MOS电容)b.气体电弧放电引起的损坏(芯片上键合根部、金属化条的最窄间距处、声表面波器件的梳状电极条间)c.输入端多晶硅电阻与铝金属化条间的介质击穿d.输入/输出端n+扩区与铝金属化条间的介质击穿。

集成电路故障分析技术研究

集成电路故障分析技术研究集成电路是现代电子产业的关键领域之一。

而集成电路的故障分析技术则是保障集成电路品质与可靠性的重要手段。

本文将从引言、集成电路故障类型分析、故障分析技术研究、应用案例等方面展开,全面探讨集成电路故障分析技术研究。

引言近年来,随着电子设备的普及和应用,集成电路的发展也越来越迅速,成为电子信息产业中发展最为重要的一个领域之一。

然而,由于集成电路元器件的微缩和复杂化,使得集成电路的故障诊断越来越具有挑战性。

对于集成电路的故障,有很多种类型。

它们常常因为不同的原因和不同的造成方式而导致故障的形成。

针对这些故障,相关专家进行了长期的技术研究,研究出了一系列的故障分析技术,用于解决集成电路的故障问题。

下面将对这些故障类型和故障分析技术逐一进行探讨。

集成电路故障类型分析当我们在使用电子产品的过程中遇到了故障,很多时候都是由于集成电路出现了问题而导致的。

在集成电路故障类型方面,它们主要可分为以下几类:1、时序故障时序故障是指由于操作或采样时序的问题导致的电路故障。

这类故障主要出现在时钟信号的设计和接口传输方面,如时钟频率不合适、时钟缺失等。

对于时序故障,应采用静态或动态的时序分析方法进行故障定位。

其中,动态时序分析方法是观察回波或宏单元状态的行为,以较高的分辨率检测故障。

2、温度故障由于电子元器件的自身特性和使用条件(如气温、室内温度等)造成的故障称为温度故障。

这类故障可能在工作过程中产生不良的板载元器件,涉及不合格设备和环境错误。

为了解决温度问题,可以通过温控系统自动控制温度,或借助于热成像设备来发现局部温度差异并采取措施。

3、电源故障电源故障是指由于供电电压或电流异常导致的故障。

这种故障可能是因为电压波动、电源削减、内存使用不正确、电源过载等原因而产生。

处理电源故障的关键是确定干扰源和确定电源质量问题。

要想排除这种故障,必须对电路进行全面的评估,包括它的实施,设备必须有一个可靠的供电电源。

第07章厚膜电路的失效机理

第七章厚/薄膜集成电路失效机理厚/薄膜集成电路是一种非常重要的微电子器件。

它是将厚/薄膜集成电路技术制造的无源元件与半导体技术制造的有源器件(包括半导体集成电路芯片)采用灵活的组装技术组装在绝缘基片上所形成的集成电路,因此又称为混合集成电路。

其中,“二次集成电路”的混合集成电路发展较快,它主要是在作有厚膜或薄膜无源网络的绝缘基片上,组装上多个半导体集成电路芯片所形成的混合集成电路。

在这类电路中,膜集成电路技术通常是制作精细的互连线/交叉线和多层布线,以及某些无源元件,然后组装上半导体集成电路芯片,形成规模更大的/功能更为复杂的混合集成电路。

厚薄膜集成电路的失效不仅有硅芯片失效,而且还包括厚/薄膜元件/互连导带/组装和封装的失效模式和失效机理。

硅芯片的失效模式和机理在有关章节中已经介绍,不再重复,本章仅介绍厚/薄膜集成电路的失效模式和机理。

1* 薄膜集成电路的失效模式和机理目前,对薄膜集成电路的失效分析表明,外贴硅芯片的失效约占50%---70%,薄膜电容失效约占10---20%,薄膜电阻失效约占10%,焊接不良占10---20%,断腿失效约占5%。

一.薄膜电阻器的失效薄膜电阻材料中用得最广的是电阻率为100---300的镍铬合金和镍铬合金和氧化钽。

薄膜电阻器失效的原因是:1.温度/湿度效应。

空气中的氧可使镍铬系薄膜氧化,电阻值增大。

环境温度和电阻器本身的温升可促使氧化加速进行。

空气中的氧化扩散到钽膜晶粒间界中时,沿膜厚方向存在着氧浓度梯度。

这使钽膜老化的最大原因,温度可加速氧化过程。

如果再加上湿度,不但使表面氧的浓度增加促进氧扩散,而且还会引起电化学反应使电阻膜被腐蚀。

特别在电负荷下,温度/湿度效应更加严重。

2.针孔和工艺缺陷。

电阻膜中难免存在针孔其产生的原因与电介质膜相同。

电阻膜有效面积减小,电流密度增大并且分布不均匀,因而引起局部温度过高,严重时可使电阻膜局部烧毁而导致电阻器失效。

3.基片内Na/K离子的影响。

集成电路输出异常失效研究分析案例

集成电路输出异常失效分析案例————————————————————————————————作者:————————————————————————————————日期:Ag迁移致集成电路输出异常失效分析1.案例背景某功能模块在用户端出现功能失效,经返厂检修,发现该模块上的一片IC输出异常,经更换IC后,功能模块恢复正常。

2.分析方法简述对样品进行外观观察,未发现明显异常。

经X-RAY无损检测,未发现明显异常。

通过C-SAM扫描发现了IC内部存在分层现象。

图5.NG样品C-SAM图片通过IV曲线测试,发现引脚间存在漏电通道。

图6.NG样品IV曲线图DE-CAP后,利用SEM/EDS进行分析,确认了引脚间存在银迁移问题。

表1.开封后的NG样品内部EDS测试结果(Wt%)3.结论IC内部存在分层,由于水汽的入侵,加上集成电路各引脚之间存在电位差,导致了引脚间的银迁移,从而在引脚间形成微导通电路,致IC输出异常。

4.参考标准GJB 548B-2005 微电子器件失效分析程序-方法5003。

IPC-TM-650 2.1.1-2004手动微切片法。

GB/T 17359-2012 电子探针和扫描电镜X射线能谱定量分析通则。

简介美信检测是一家具有CNAS和CMA资质认证的第三方检测机构,提供检测服务●形貌观察与测量●显微结构分析●表面元素分析●表面异物分析●成分分析●力学性能测试●热学性能测试●焊接工艺评定●CT扫描●无损检测●切片分析●阻燃性能测试●油品检测●清洁度测试●可靠性测试●失效分析●配方分析●有毒物质检测●涂镀层厚度......。

厚膜混合集成电路的失效分析 .doc

厚膜混合集成电路的失效分析及其缺陷产品的筛选淘汰摘要:介绍了厚膜混合集成电路的失效分析程序 ,总结了在生产与使用中发现的主要失效模式 ,对失效机理进行了研究 ,提出了对存在缺陷产品的有效筛选淘汰方法。

关键词:厚膜混合集成电路;失效分析;失效机理;筛选。

1引言厚膜混合集成电路 (以下简称 H I C)不仅弥补了半导体集成电路 (简称 SI C)的一些不足 ,而且能够充分发挥 SI C高集成度、高速等特点 ,是一种高级的微电子产品。

近年来它对实现武器装备小型化、多功能化、高性能化发挥了重要作用。

但是随着现代化高科技武器装备的发展 ,对军用H I C的可靠性要求也越来越高 ,其可靠性指标已被提到与性能指标同等重要的程度。

面对此种高要求 ,除加强可靠性设计等工作以提高 H I C固有可靠性水平外 ,认真开展 H I C 的失效分析工作 ,发现、研究并总结常见的失效模式和失效机理 ,提出并采取切实有效的筛选试验方法 ,剔除有缺陷的 H I C,对于提高 H I C的使用可靠性水平、满足武器装备的高可靠性要求 ,具有十分重要的意义。

2失效分析程序对 H I C失效产品进行深入细致的分析工作 ,准确定位其失效部位 ,了解其失效的性质、特征和原因 ,能够为如何消除失效因素或剔除有缺陷产品以及评估整批产品的质量水平等发挥重要作用。

一个完整的失效分析程序应当包括以下几个方面:2 . 1 失效模式的验证例如 ,在进行 H I C的电性能测试时 ,表现出开路、短路、失去功能或者电参数恶化等现象。

2 . 2 失效部位确定指出失效现象或效应可能与电路的哪一部分或哪一个元器件有关。

2 .3 失效特征描述根据与失效现象有关的形状、大小、位置、颜色、化学组份、物理结构、物理性质等 ,科学地表达或阐明与上述失效模式有关的失效现象或效应。

2 . 4 失效机理假设根据上述失效特征的描述 ,结合材料性质及有关制造工艺的实际情况 ,提出可能导致产生该失效模式的内在原因或规律性 ,亦即提出可能导致产生该失效模式的物理或化学机理。

集成电路失效机理分析及其PHM技术实现

集成电路失效机理分析及其PHM技术实现杨德才【摘要】With the feature size of ICs (integrated circuits) scaling down and the integration density increasing up, their reliability problems become more and more severe. Implementation of PHM (prognostics and health management) to ICs based on physics of failure is to prevent catastrophes from occurring. In the paper, the failure mechanism of IC is introduced at first. Then method of prognostic cell to semiconductor-level PHM is illustrated with some cases. Finally, the precursor circuit to EM (electro-migration) is presented and validated to show the efficiency of the proposed PHM scheme.%集成电路的可靠性问题随着制造工艺尺寸的缩小与集成度的增加而变得越来越重要,开展针对集成电路的失效物理为基础的故障预测与健康管理技术,用于预测和评估集成电路产品在实际环境中的可靠性,已成为当今研究的热点。

通过阐述集成电路的失效机理,介绍了集成电路目前故障预测与健康管理的基本方法。

针对关键失效机理的基于预警单元法的PHM技术方案,提出了对电迁移失效的监控原理、监控方法,通过设计电迁移预警电路,验证了该PHM 技术的可行性。

混合集成电路DC_DC电源失效分析浅析

混合集成电路DC/DC电源失效分析浅析发布时间:2021-12-23T06:36:33.990Z 来源:《科学与技术》2021年第27期作者:郑莉冯枫王甜[导读] 混合集成电路失效分析在提高集成电路的可靠性方面有着至关重要的作用。

对混合集成电路进行失效分析可以促进企业纠正设计、实验和生产过程中的问题,实施控制和改进措施,郑莉冯枫王甜陕西华经微电子股份有限公司摘要:混合集成电路失效分析在提高集成电路的可靠性方面有着至关重要的作用。

对混合集成电路进行失效分析可以促进企业纠正设计、实验和生产过程中的问题,实施控制和改进措施,防止和减少同样的失效模式和失效机理重复出现,预防同类失效现象再次发生。

本文从测试工艺角度出发,结合多年工作经验,论述了DC/DC电源电路故障的几种有效的分析方法。

关键词:DC/DC电源混合集成电路故障现象分析方法引言混合集成电路(Hybrid Integrated Circuit)是由半导体集成工艺与厚膜或薄膜工艺结合而制成的集成电路。

混合集成电路是在基片上用成膜方法制作厚膜或薄膜元件及其互连线,并在同一基片上将分立的半导体芯片、单片集成电路或微型元件混合组装,再外加封装而成。

具有组装密度大、可靠性高、电性能好等特点。

随着电路板尺寸变小、布线密度加大以及工作频率的不断提高,使其在生产中会遇到各种各样的功能故障。

要在大量的元器件和线路中迅速、准确地找出故障是不容易的。

一般故障诊断过程,就是从故障现象出发,通过反复测试,做出分析判断,逐步找出故障的过程。

因故障产生的原因繁多,有的产品情况较为复杂,所以这里就混合集成电路的一些常见故障现象分别给出相应的分析方法。

一、DC/DC电源产品无输出现象1.1 DC/DC电源产品无输出无电流或电流过大过小这种故障现象出现频率较高,优先查找混合集成电路的前级问题,着重检查功率回路和集成电路管芯是否正常运作。

故障查找分不通电观察法和通电检查法两种检查方法。

PCB失效分析技术与典型案例

在 PCB 或焊点的失效分析方面,SEM 主要用来作失效机理的分析, 具体说来就是用来观察焊 盘表明的形貌结构、焊点金相组织、测量金属间化物、可焊性镀层分析以及做锡须分析测量等。与 光学显微镜不同, 扫描电镜所成的是电子像, 因此, 只有黑白两色, 并且扫描电镜的试样要求导,电 对非导体和部分半导体需要喷金或碳处理,否则电荷聚集在样品表面就影响样品的观察。此外,扫 描电镜图象景深远远大于光学显微镜,是金相结构、显微断口以及锡须等不平整的样品的重要分析 方法。

Abstract Due to the trend of PCB developing toward high density and the environmental requirements of lead free and halogen free for PCB,all kinds of failure issues including bad wetting, blast, delamination and CAF are apt to take place more and more oftenly. In this paper analysis technologies for these failures will be firstly introduced,which includes SEM/EDS,XPS, microsection,t hermal analysis(TGA/DSC/TMA),FTIR , wetting balance test and so on. Followingly, the applications of these analysis technologies are presented in some typical failure cases. To discover the mechanism and rooted causes for PCB failure will make for the quality control of PCB and free of re-happening of similar cases in the coming days. Keywords:PCB Failure Analysis Analysis Technology