TPA3005D2中文资料

PQ05RD21中文资料

PQ05RD21 series Low Power-Loss Voltage Regulator

2.0A Output Type, High Cost Performance Low Power-Loss Voltage Regulator

General Description Sharp's PQ05RD21 series is 2.0A output type low power-loss voltage regulator(TO-220). It contributes to energy and space saving of various electronic equipment such as AV, OA equipment.

1

Input

Specific IC 3 GND

2

Output

4 ON/OFF control terminal

Model Line-up 2.0A output

3.3V output 5.0V output 9.0V output 12.0V output

PQ3RD23 PQ05RD21 PQ09RD21 PQ12RD21

*6 Input voltage shall be the value when output voltage is 95% in comparison with the initial value. PQ3RD23:Vin=3.7V *7 In case of opening control teminal 4 , output voltage turns on.

(Internet)

• Data for Sharp's optoelectronic/power devices is provided for internet. ( Address http://www.sharp.co.jp/ecg/)

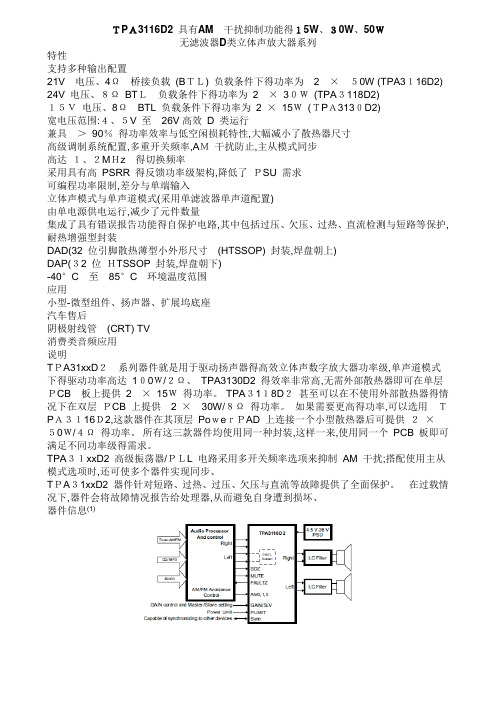

TPA3116D2中文数据表

TPA3116D2 具有AM干扰抑制功能得15W、30W、50W无滤波器D类立体声放大器系列特性支持多种输出配置21V电压、4Ω桥接负载(BTL) 负载条件下得功率为2×50W (TPA3116D2) 24V 电压、8ΩBTL负载条件下得功率为2×30W(TPA3118D2)15V电压、8ΩBTL 负载条件下得功率为 2 ×15W(TPA3130D2)宽电压范围:4、5V 至26V高效 D 类运行兼具>90%得功率效率与低空闲损耗特性,大幅减小了散热器尺寸高级调制系统配置,多重开关频率,AM干扰防止,主从模式同步高达1、2MHz得切换频率采用具有高PSRR 得反馈功率级架构,降低了PSU 需求可编程功率限制,差分与单端输入立体声模式与单声道模式(采用单滤波器单声道配置)由单电源供电运行,减少了元件数量集成了具有错误报告功能得自保护电路,其中包括过压、欠压、过热、直流检测与短路等保护,耐热增强型封装DAD(32 位引脚散热薄型小外形尺寸(HTSSOP) 封装,焊盘朝上)DAP(32 位HTSSOP 封装,焊盘朝下)-40°C至85°C环境温度范围应用小型-微型组件、扬声器、扩展坞底座汽车售后阴极射线管(CRT) TV消费类音频应用说明TPA31xxD2系列器件就是用于驱动扬声器得高效立体声数字放大器功率级,单声道模式下得驱动功率高达100W/2Ω、TPA3130D2 得效率非常高,无需外部散热器即可在单层PCB板上提供2×15W得功率。

TPA3118D2甚至可以在不使用外部散热器得情况下在双层PCB 上提供 2 ×30W/8Ω得功率。

如果需要更高得功率,可以选用TPA3116D2,这款器件在其顶层PowerPAD 上连接一个小型散热器后可提供2×50W/4Ω得功率。

所有这三款器件均使用同一种封装,这样一来,使用同一个PCB 板即可满足不同功率级得需求。

美国特色产品说明:0215型设备中文版说明书

verviewWell-suited for low traffic areas, this unit is similar to the 0210 but reduced capacity to dispense 200 C-fold or 275 multi-fold paper towels without adjustment or adapters and is fitted with tumbler lock and heavy-duty stainless steel piano hinge.American Specialties, I nc. | 441 Saw Mill River Road, Yonkers, NY 10701 | (914) 476-9000 | Model:#0215Issued:11/1/2021Revised:3/10/2023Page:1 of 2Revision :R1uStainability /lEEDPaper Towel Dispenser - Petite (Multi - C-Fold) -Surface MountedToilet Accessories CSI:10 28 13MR 6 (1)EQ 4.1 (1)EQ 4.2 (1)EQ 4.4 (1)661_1O peratiOn & M aintenancet echnical i nfOrMatiOn / p rOduct p rOpertiesi nstallatiOnW arrantySurface mount unit on wall or partition using five #10 self-threading screws (by others) through concealed mounting holes provided. Four mounting holes through back are keyhole slots for ease in hanging unit on pre-installed screws. Center top mounting hole is horizontal slot for ease of adjustment and vandal resistant locking. For compliance with 2010 ADA Accessibility Standars install unit so that centerline of towel dispenser slot is 48" [1219] maximum above finished floor (AFF).Manufacturer reserves the right to make changes to the design, dimensions or functionality of the product without formal notice.Towels are self-feeding as withdrawn by hand until supply is depleted. Unit may be reloaded with a partial load in-place and will continue to feed properly. Low level of towel supply is indicated from 35% capacity to empty. Unit is a reduced-size model and has less capacity than larger models, therefore it is recommended to use this unit in space-restricted or low traffic areas. Locking door prevents unauthorized access or removal.One (1) Y ear from date of InvoiceAmerican Specialties, I nc. | 441 Saw Mill River Road, Yonkers, NY 10701 | (914) 476-9000 | Model:CSI:#021510 28 13Toilet Accessories Issued:11/1/2021Revised:3/10/2023Page:Revision :Type 304 Stainless Steel - Matte Black Powder Coated Concealed multi-staked hinge - 3/16" Dia. [Ø5]200 C-fold or 275 multi-fold paper towelsPropertyValueDimensions Construction 11" [279] W x 8" [203] H x 4" [102] DManual - Pull T ype Surface MountedN/A2 of 2R1Power Operation Mounting Capacity。

3005使用说明书

第4页

DCAP-3005(V2.0D)自闭贯通保护测控装置:使用说明书

说明

装置工作电源 控制回路电源

1 可以是 DC220V 或 DC110V,在订货时须注明。 1 可以是 DC220V 或 DC110V,在订货时须注明。

开关控制回路

1

交流输入(AD) 14

开关量输入

12

(DI)

有内置防跳继电器及合闸保持继电器。

途径:交流量→内部小互感器(隔离变换)→低通滤波→A/D 转换 (数字信号)→DSP(计算处理)。 均经光电隔离。其中,开入量 1~9 为 DC220V 或 DC110V 输入的 普通信号;开入量 10 可作为 GPS 对时信号,开入量 11~12 可 作为电度脉冲信号,此时它们都是 DC24V 输入,而当它们作为 普通信号时,输入电压同开入量 1~9。

可检测 12 路遥信量,遥信变位信息及同时产生的 SOE 可上传给主机。

遥控量 当地报告记录

对时功能

可接受并执行主机的遥控命令,遥控出口可整定。

故障告警记录。 变位报告记录。 操作记录。 主机软件对时 GPS 对时

第3页

DCAP-3005(V2.0D)自闭贯通保护测控装置:使用说明书

数据的掉电保存 其它

录波数据、故障告警记录、变位记录、操作记录等保存在有备用电池支 持的 RAM 中,在装置掉电时数据不会丢失。 保护或控制参数保存在 EEPROM 中,在装置掉电或电池耗尽时数据不会 丢失。 测量量显示方式:“一次值/二次值”可选择; 电度测量方式:“脉冲方式/计算方式”可选择。

3 装置硬件资源配置

名称 数量

第2页

DCAP-3005(V2.0D)自闭贯通保护测控装置:使用说明书

数通达DP3005B直流电源供应器使用手册说明书

简介

DP3005B 可调式直流稳压稳流电源采用先进的单片机技术,结合高品质编 码开关实现输出电压与限流电流均连续可调、且稳压与稳流自动转换的高稳定性 直流电源。粗调与细调可按需一键切换,可分别对电压步进 1V 与步进 10mV 精 确调整;对电流步进 100mA 与步进 1mA 精确调整。

与细调(步进 1mA)模式 (6) 输出开关:电压电流设定完成后,按此键控制输出的接通和关断 (7) 输出接线柱正极(+)红色

(8) 机壳接地接线柱( )绿色

(9) 输出接线柱负极(-)黑色 (10)LED 显示说明:4 位数字电压电流显示,(CV)灯指示恒压状态;

(CC)灯指示恒流状态;(OUTPUT)灯指示输出关断状态。

型号

DP3005B

额定输出电压 额定输出电流

0~30V 0~5A

1 技术参数

1.1 输入电压: 104~127V AC(60Hz) 或 207~253V AC (50Hz)

1.2 电源效应: CV≤0.1%+3mV

CC≤0.2%+3mA

1.3 负载效应: CV≤0.05%+3mV(I≤3A) CC≤0.5%+10mV(I≤3A)

CV≤0.01%+5mV(I>3A) CC≤0.2%+5mV(I>3A)

1.4 纹路与噪声: CV≤5mVr.m.s

CC≤20mAr.m.s

1.5 保护:电流限制及短路保护

1.6 电压指示精度:LED±0.5%+5 个字

1.7 电流指示精度:LED±0.5%+5 个字

1.8 使用环境: 0~﹢40℃

(11) 锁定功能:同时按住旋钮(4)&(5)约三秒钟,显示屏闪烁一次,输出 设定值即被锁定,锁定状态不受断电影响。

AD8005中文资料

TMIN to TMAX Offset Drift +Input Bias Current TMIN to TMAX –Input Bias Current Input Bias Current Drift (± ) Open-Loop Transimpedance INPUT CHARACTERISTICS Input Resistance Input Capacitance Input Common-Mode Voltage Range Common-Mode Rejection Ratio OUTPUT CHARACTERISTICS Output Voltage Swing Output Current Short Circuit Current POWER SUPPLY Quiescent Current Power Supply Rejection Ratio OPERATING TEMPERATURE RANGE

元器件交易网

a

FEATURES Ultralow Power 400 A Power Supply Current (4 mW on ؎5 VS) Specified for Single Supply Operation High Speed 270 MHz, –3 dB Bandwidth (G = +1) 170 MHz, –3 dB Bandwidth (G = +2) 280 V/ s Slew Rate (G = +2) 28 ns Settling Time to 0.1%, 2 V Step (G = +2) Low Distortion/Noise –63 dBc @ 1 MHz, V O = 2 V p-p –50 dBc @ 10 MHz, VO = 2 V p-p 4.0 nV/√Hz Input Voltage Noise @ 10 MHz Good Video Specifications (RL = 1 k⍀, G = +2) Gain Flatness 0.1 dB to 30 MHz 0.11% Differential Gain Error 0.4؇ Differential Phase Error APPLICATIONS Signal Conditioning A/D Buffer Power-Sensitive, High-Speed Systems Battery Powered Equipment Loop/Remote Power Systems Communication or Video Test Systems Portable Medical Instruments PRODUCT DESCRIPTION

香港龙威TPR3005-2D直流电源操作规程序,

4.2.5 调节“VOLTAGE”和“CURRENT”旋钮到需要的输出电压和电流值; 4.2.6 连接外部负载到“+”“—”输出端子; 4.2.7 当用在要求较高的场所,输出“—”接线柱必须与“GND”接线柱可靠连接,这样可以 减少输出纹波电压。 5.记录 5.1 按时填写设备保养记录。 5.2 按时填写设备运行记录。

拟 审 批

制 核 准

许明坤 2016 年 6 月 6 日 徐玉平 2016 年 6 月 6 日 张华 2016 年 6 月 6 日

修 改 记 录

修改单号

修改人/日期

设备操作规程文件 文件名称:香港龙威 TPR3005-2D 直流电源操作规程 序 号: 版 页 次: A/0 码: 第 1 页 共 2 页

香港龙威 TPR3005-2D 直流电源操作规程序

1. 范围 本标准规定了香港龙威 TPR3005-2D 直流电源操作规程及安全。 本标准适用于以下设备的操作: 设备型号: TPR3005-2D 设备厂家:香港龙威仪器仪表有限公司 2.设备作业环境要求: 保持环境清洁、整齐、电气部分严禁受潮、保持干燥、无不安全状态 3.设备安全要求: 3.1 禁止用湿手操作; 3.2 使用完毕后,放在干燥通风的地方,并保持清洁,若长期不使用应将电源插头拔掉后再存 放; 3.3 对稳定电源进行维修时,必须将输入电源断开; 3.4 因电源使用不当或使用环境异常及机内元器件失效等均可能引起电源故障,当电源发生故 障时,输出电压有可能超过额定输出最高电压,使用时务必请注意!谨防造成不必要的负载损 坏; 3.5 三芯电源线的保护接地端,必须可靠接地,以确保使用安全! 4.设备的操作程序和方法: 4.1 技术参数: 4.1.1.输入电压: AC220V± 10% 50Hz± 2Hz(输出电流小于 5A) AC220V+10% 50Hz± 2Hz(输出电流等于 5A) AC220V-5% 50Hz± 2Hz(输出电流等于 5A) 4.1.2 双路可调整电源: 额定输出电压:2×0-30V 拟 审 批 制 核 准

德特威勒产品手册可编辑

DMD

内模板

外模板

模板

(5-8um半径)

(0-23um半径)

1

0.33ps/m

0.33ps/m

2

0.27ps/m

0.35ps/m

3

0.26ps/m

1300nm

台阶(双向平均值)

≤0.10

dB

不均匀性(整个光纤长度)和衰减点不连续性

≤0.10

dB

背向散射衰减系数差异(双向测试)

≤0.10

dB/km

几何特性

芯径

62.5±2.5

um

包层直径

125.0±1.0

um

包层不圆度

≤1.0

%

涂层直径

242±7

um

涂层/包层同心度误差

≤12.0

um

涂层不圆度

≤6.0

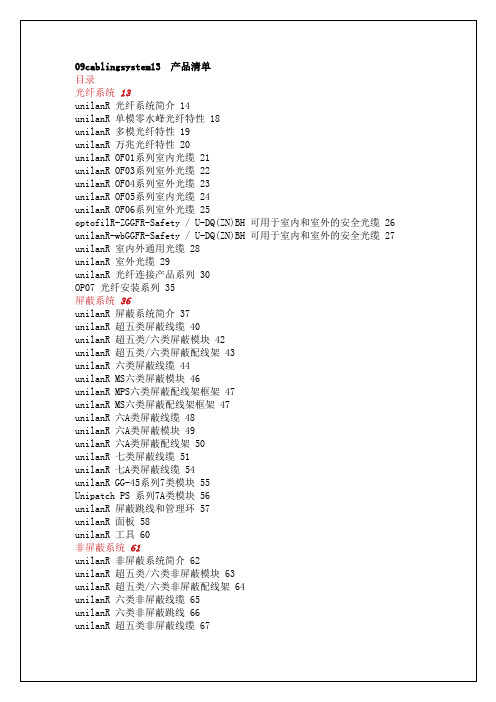

unilanR MPS六类屏蔽配线架框架47

unilanR MS六类屏蔽配线架框架47

unilanR六A类屏蔽线缆48R六A类屏蔽配线架50

unilanR七类屏蔽线缆51

unilanR七A类屏蔽线缆54

unilanR GG-45系列7类模块55

Unipatch PS系列7A类模块56

%

芯/包层同心度误差

≤1.5

um

Unilan?万兆光纤特性

Unilan?德特威勒万兆多模光纤特性:

满足IEC60793-2-10A1b、IEEE802.3ae、Bellcore、EIA/TIA-492AAAC、ISO11801OM3、TIA/EIA-455和TIA568C.3-2009标准,在850nm处可以支持万兆以太网速率达300米及支持1000Base-SX达900米距离,同时又可向下兼容目前的1G,100Mbps,10Mbps以太网应用。

TPAD中文数据表

T P A D中文数据表Revised on July 13, 2021 at 16:25 pmTPA3116D2 具有AM 干扰抑制功能的15W、30W、50W无滤波器D类立体声放大器系列特性支持多种输出配置21V 电压、4Ω桥接负载 BTL 负载条件下的功率为 2 × 50W TPA3116D224V 电压、8Ω BTL 负载条件下的功率为 2 × 30W TPA3118D215V 电压、8Ω BTL 负载条件下的功率为 2 × 15W TPA3130D2宽电压范围:4.5V 至 26V高效 D 类运行兼具 > 90% 的功率效率与低空闲损耗特性;大幅减小了散热器尺寸高级调制系统配置;多重开关频率;AM 干扰防止;主从模式同步高达 1.2MHz 的切换频率采用具有高 PSRR 的反馈功率级架构;降低了 PSU 需求可编程功率限制;差分和单端输入立体声模式和单声道模式采用单滤波器单声道配置由单电源供电运行;减少了元件数量集成了具有错误报告功能的自保护电路;其中包括过压、欠压、过热、直流检测和短路等保护;耐热增强型封装DAD32 位引脚散热薄型小外形尺寸 HTSSOP 封装;焊盘朝上DAP32 位 HTSSOP 封装;焊盘朝下-40°C 至 85°C 环境温度范围应用小型-微型组件、扬声器、扩展坞底座汽车售后阴极射线管 CRT TV消费类音频应用说明TPA31xxD2 系列器件是用于驱动扬声器的高效立体声数字放大器功率级;单声道模式下的驱动功率高达 100W/2Ω.. TPA3130D2 的效率非常高;无需外部散热器即可在单层 PCB 板上提供 2 × 15W 的功率.. TPA3118D2 甚至可以在不使用外部散热器的情况下在双层 PCB 上提供 2 × 30W/8Ω的功率.. 如果需要更高的功率;可以选用 TPA3116D2;这款器件在其顶层PowerPAD 上连接一个小型散热器后可提供 2 × 50W/4Ω的功率.. 所有这三款器件均使用同一种封装;这样一来;使用同一个 PCB 板即可满足不同功率级的需求..TPA31xxD2 高级振荡器/PLL 电路采用多开关频率选项来抑制 AM 干扰;搭配使用主从模式选项时;还可使多个器件实现同步..TPA31xxD2 器件针对短路、过热、过压、欠压和直流等故障提供了全面保护.. 在过载情况下;器件会将故障情况报告给处理器;从而避免自身遭到损坏..器件信息1详细描述概述tpa31xxd2装置是一种高效的D类音频放大器集成120mΩMOSFET;允许输出电流高达7.5 A 的高效率允许放大器提供一个极好的音频性能不需要一个庞大的散热片..该装置可配置为使用同步引脚的主从操作..这有助于防止声音节拍噪音..功能块图特征描述增益设置和主人和奴隶家庭的tpa31xxd2增益设置连接增益/ SLV控制引脚的电压分压器..硕士或从属模式也由同一个引脚控制..一个内部的ADC是用于检测8个输入状态..前四阶段设置在主模式中获得的收益为20;26;32;36分贝;而下一个四个阶段集在从模式增益为20;26;32;36分贝增益..增益设置在电源锁存当设备供电时;不能改变..表1列出推荐的电阻值和状态增益:(1)电阻公差应为5%或更好..在主模式;同步终端是一个输出;在从模式;同步终端是一个输入时钟输入..TTL逻辑电平与符合GVDD..输入阻抗家庭的tpa31xxd2输入级是一个全差分输入级;输入阻抗的变化增益设置从9 KΩ在增益36分贝至60 KΩ在20 dB的增益..表1列出从最小到最大增益值..这的输入电阻值误差±20%最小值将高于7.2 KΩ..输入需要AC耦合到输出直流偏移和确保斜坡的输出电压在电源正确—论与权力..输入交流耦合电容与输入阻抗形成一个高通滤波器有以下截止频率:如果一个平坦的低音响应是必需的下降到20赫兹的建议截止频率为十分之一;2赫兹..表2 列出了建议的交流耦合电容器的每一个增益步..如果一个- 3分贝是接受在20赫兹10倍低电容器可以使用;例如;可以使用1μf所使用的输入电容应是一种低泄漏;如优质电解;钽或陶瓷的类型..如果一个偏光式是用积极的连接应面偏3 VDC输入引脚..启动和关闭操作tpa31xxd2家庭使用操作旨在降低电源电流关断模式ICC的绝对最低水平在电力节约使用期..SDZ输入端应举行在正常运行时;在正常运行时;在正常运行时;在正常运行时见表..拉低作用将输出静音和放大器进入低电流状态..不建议离开SDZ无关的;因为放大器的操作将是不可预知的..最流行的性能将放大器断电;在关断模式;消除电源之前供应..在启动周期结束时选择增益设置..在启动周期结束时;增益是选定并不能更改;直到下一次电源..plimit操作tpa31xxd2家族有一个内置的电压限制器可用于限制输出电压水平以下电源轨;放大器的简单地工作;如果它是由一个较低的电源电压供电;从而限制了输出功率..加一个电阻分压器的GVDD地面设置的电压在plimit销..一个外部的如果需要更严格的公差;也可使用参考..添加一个1μF的电容μ针plimit地保证稳定性..建议连接到使用1spw plimit GVDD调制方式时..plimit电路上设置输出电压峰峰值限制..限制是通过限制的占空比以一个固定的最大值..这个极限可以被认为是一个“虚拟”的电压轨道;这是低于供应连接到PVCC..这个“虚拟”的轨道大约是4倍的电压在plimit销..此输出电压可用于计算最大输出功率为给定的最大输入电压和扬声器阻抗..在哪儿输出功率10%的THD= 1.25×输出功率移除RL负载电阻..RS是总串联电阻RDSON;包括输出过滤器的阻力..副总裁是峰值幅度VP = 4×plimit电压如果plimit<4×VP(1)plimit taken with EVM测量增益集to 26dB与输入电压set to 1Vrms..GVDD供应用于电力供应的GVDD的全桥式输出晶体管的大门..它也可以用来供应plimit和增益/ SLV 电压分压器..解耦GVDD与X5R陶瓷1μμF的电容到GND..这GVDD供应不可用于外部电源..建议限制当前消费采用电阻分压器的增益/ SLV和100 KΩ或更plimitbspx和bsnx电容器全桥输出阶段只使用NMOS晶体管..因此;他们需要为每个输出的高边依次打开..220 nF陶瓷电容器质量X5R或更好;额定电压至少16伏;必须从每个输出连接到其相应的引导输入..见应用电路在图37图..bsxx引脚连接和相应的输出函数之间的自举电容器;作为一个浮动电源的高侧N通道功率MOSFET的栅极驱动电路..在每一个高边开关周期;自举电容保持的栅极至源极电压高到足以保持高边MOSFET的开启..差分输入该放大器的差分输入级取消任何出现在通道的输入线的噪声..以使用tpa31xxd2家庭和一个差分源;连接音频源正导致RINP或linp输入和音频源负导致里恩或属输入..使用tpa31xxd2家庭用一个单一的结束源;交流地负输入通过一个电容等于输入电容论积极的和适用的音频源;无论是输入..在单端输入应用程序中;未使用的输入应该是交流接地在音频源;而不是在设备输入的最佳噪声性能..为了好瞬态性能;在每一个差分输入看到的阻抗应该是相同的..在输入阻抗的阻抗应该被限制在一个钢筋混凝土的时间常数为1毫秒或更少;如果可能的话..这是允许输入直流阻挡电容器成为完全充电在10毫秒的时间..如果输入电容器是不允许完全充电;将有一些额外的灵敏度组件匹配如果输入组件没有很好的匹配;它会导致弹出..设备保护系统tpa31xxd2家族包括一套完整的保护电路;精心设计;使系统的设计有效的;以及保护设备免受任何类型的永久性故障;由于短路;过载;过温、欠压..的faultz引脚信号如果按照表4中检测到错误:直流检测保护tpa31xxd2家庭电路将保护扬声器免受直流电流可能发生的印刷电路板上的输入或短路上有缺陷的电容器..一个直流检测故障将报告故障引脚为低状态..直流检测故障也会导致放大器关机改变输出状态为高阻..如果从短路保护自动恢复所需的锁存器;连接faultz引脚直接到SDZ销..这让faultz引脚功能来自动驱动SDZ引脚低清除直流检测保护锁..直流检测故障时;输出差分占空比任何一个通道超过60%;超过420毫秒在相同的极性..下面的表格显示了典型的直流检测保护的一些例子电源电压的几个值的阈值..此功能保护扬声器从大的直流电流或交流电流小于2Hz..为了避免滋扰故障由于直流检测电路;将SD引脚低电直到输入信号稳定..此外;要小心;以匹配的阻抗看到的正面和负输入;以避免扰直流检测故障..表5列出的最小输出偏置电压需要触发直流检测..输出必须保持在或上面的电压表中列出了420多毫秒触发的直流检测..短路保护和自动恢复功能tpa31xxd2家庭保护过电流条件下的短路引起的输出级..短路保护故障报告的faultz引脚为低状态..放大器输出切换当短路保护锁存器的时候;可以在高阻抗状态下进行..锁存器可通过循环清零SDZ引脚通过低状态..如果从短路保护自动恢复所需的锁存器;连接faultz引脚直接到SDZ销..这让faultz引脚功能来自动驱动SDZ引脚低清除短路保护锁..在系统中;可能永久短从输出PVDD或高电压电池一样汽车电池可以发生;与逆变晶体管保证高的faultz信号拉低静音引脚—重新启动;如下图所示:热保护在tpa31xxd2家庭热保护防止设备损坏时;模内温度超过150°C;有一个15°C的公差;从设备到设备..一旦模具温度超过热行程点;该设备进入关机状态和输出被禁用..这是一个锁存故障..热保护故障报告的faultz终端低状态..如果从热保护锁自动恢复的需要;将faultz引脚直接到SDZ销..这让faultz引脚功能来自动驱动SDZ引脚低清除热保护锁..装置调制方案tpa31xxd2家族在BD调制或1spw调制运行选项;这是由模式销..模式= GND:BD调制这是一个调制方案;允许在没有经典的液晶重建滤波器的运算放大器用短喇叭线驱动感应负载..每一个输出开关从0伏到电源电压..的outpx和outnx是相互不输入;在很少或没有电流演讲者..outpx的占空比是大于50% outnx小于正输出电压50%..outpx的占空比小于50%;outnx大于负输出电压的50%..这个在负载电压在0V在大多数的开关周期;降低开关电流;这减少在任何负载的I2R损耗..模式=高:1spw调制1spw模式改变了正常的调制方案;以轻微的刑罚实现更高的效率在THD降解和更多的关注在输出滤波器的选择要求..在1spw模式的输出操作在空闲状态下的15%调制..当一个音频信号被施加一个输出将减少和一个将增加..降低输出信号将很快轨到GND;此时所有的音频调制发生通过不断上升的输出..其结果是;只有一个输出是在大多数的音频周期切换..在这种模式下;由于减少开关损耗的效率提高..在1spw模式THD处罚最小化的高性能反馈回路..由此产生的音频信号在每个半输出间断每次到GND输出轨..这可能会导致在音频重建过滤器;除非在选择过滤器组件和使用过滤器的类型..效率:LC滤波器所要求的与传统的D类调制方案最主要的原因;基于AD调制需要输出滤波器的传统的D类放大器;最大电流流量的开关波形..这会导致更多的损失;这会导致更低的负荷效率..对于传统的调制方案;纹波电流较大;因为纹波电流较大电压乘以电压乘以时间..差分电压摆幅为2×VCC;和在每个电压的时间是一半的周期为传统的调制方案..一个理想的液晶过滤器是必要的存储每一个周期为下一个周期的纹波电流;而任何电阻会导致功耗..这个扬声器是电阻和反应性;而一个液晶滤波器几乎是纯粹的反应性..的tpa3116d2调制方案无滤波器在负载损耗小;因为脉冲短电压变化而不是2×VCC VCC..随着输出功率的增加;脉冲展宽;使纹波电流较大..纹波电流可以用液晶过滤器过滤;以提高效率;但对于大多数应用该过滤器是不需要的..LC滤波器的截止频率小于D类开关频率允许开关电流通过过滤器来代替负载..该过滤器具有较小的电阻;但更高的阻抗在切换频率比扬声器;这导致在功耗较小;因此提高效率..磁珠滤波器的考虑采用先进的排放抑制技术在tpa3116d2放大器能够设计高效率D类音频放大器的同时最大限度地减少干扰周边电路..这也是可能的用低成本的铁氧体珠来实现这一..在这种情况下;它是必要的仔细选择铁素体在过滤器中使用..铁素体的选择的一个重要方面是在铁素体中使用的材料的类型珠..不是所有的铁素体材料是一样的;所以重要的是选择一个在10到100兆赫的材料是有效的范围是关键的D类放大器的操作..规范消费的许多规范电子产品的排放限制低至30兆赫..重要的是要使用的铁素体珠过滤器;以阻止辐射在30兆赫和以上的范围内;从扬声器电线和电源线;这是好的出现这些信号的天线..铁氧体的阻抗可以与一个小电容器一起使用在1000个范围内的值;以减少到一个可接受的水平的信号的频谱的范围..最好的性能;谐振频率的铁素体珠/电容滤波器应小于10兆赫..此外;重要的是;铁素体的珠是足够大;以维持其在峰值电流的阻抗对于放大器..一些铁氧体珠制造商在不同的电流水平指定珠阻抗..在这种情况下;它是可能的;以确保铁氧体珠保持足够量的阻抗在峰值电流放大器将看到..如果这些规格不可用;也可以估算出胎圈在低功耗和最大限度的滤波器输出的谐振频率测量的电流处理能力权力..在这种情况下;小于百分之五十的谐振频率的变化是可取的..实例铁氧体磁珠进行与tpa3130d2工作可以在tpa3130d2evm看到用户指南slou341..一种高质量的陶瓷电容器也需要的铁氧体珠过滤器..一个好的低ESR电容器温度和电压特性将工作最好..额外的EMC改进可以通过增加电路网络的每个D类输出得到地..一个简单的RC串联电路网络建议值将在330ΩPF系列1电容器虽然缓冲网络设计是具体到每一个应用和设计必须以考虑印刷电路板的寄生电抗;以及音频放大器..照顾评估应力对构件在缓冲网络特别是如果功放是运行在高氯化聚氯乙烯..也做确定缓冲网络布局紧凑;直接返回到IC的GND引脚..何时使用输出滤波器抑制电磁干扰tpa3116d2已经用一个简单的铁氧体磁珠滤波器的各种应用;包括久经考验的扬声器电线高达125厘米;高功率..的tpa3116d2 EVM通过FCC B类规格下这些条件用扭曲的喇叭线..的大小和类型的铁素体珠可以选择以满足应用需求..此外;如果必要的话;过滤器电容器可以增加一些对效率的影响..有可能是一些电路实例;有必要添加一个完整的液晶重建过滤器..这些如果有附近的电路;这是敏感的噪音可能会发生的情况..在这些情况下经典二阶Butterworth滤波器类似下图所示可以用..有些系统几乎没有电源去耦;从交流线路;但也受到线进行干涉LCI条例..这些措施包括:“墙疣”和“动力砖”的系统..例;LC重构滤波器可以是成本最低的方式通过LCI试验..共模扼流圈使用低频铁氧体材料也可有效防止线路传导干扰..避免电磁干扰减少在AM广播频段的干扰;这tpa3116d2拥有改变开关频率的能力经是<< 2:0 >引脚..推荐的频率是在表6上市..基频及其秒谐波在AM波段上市..这消除了由于切换而导致的音调频率的AM收音机解调..设备功能模式单模式PBTLtpa31xxd2家庭可以连接在单声道模式使输出功率100W..这是通过:连接装置和innl直接接地无电容这套装置在单声道模式中上电..连接outpr和outnr一起积极发言终端和outnl和outpl一起负脚..模拟输入信号的应用效果和innr..应用与实现注:in the following应用信息部分is not part of the TI组件规范和Ti does not权证及其精度金完备..ti' S customers areresponsible for测定的适宜性of components for their用途..客户应他们的设计实现与测试validate to confirm系统功能..8.1应用信息这部分有硕士学位和斯拉夫describes 2.1应用..大师是构型有立体声输出and the你是pbtl斯拉夫构型单输出..典型的应用..解决了2.1;U1 tpa3116d2硕士模式在400千赫;BTL增益20dB;如果不实施;权力的限制..U2 in 斯拉夫语、pbtl增益20db模式..输入是连通for差动输入..典型应用8.2.1设计要求8.2.2详细设计过程tpa31xxd2的家庭是一个非常灵活和易于使用的D类放大器;因此设计过程直截了当..在开始设计之前;收集以下有关音频系统的信息..PVCC铁路计划的设计扬声器或负载阻抗最大输出功率要求所需的脉宽调制频率选择PWM频率采用AM0设置PWM频率;AM1;AM2引脚..选择放大器的增益和主/从模式为了选择放大器增益设置;设计人员必须确定最大功率目标和扬声器阻抗..一旦这些参数已被确定;计算所需的输出电压摆幅提供最大输出功率..选择最低的模拟增益设置;对应于产生一个输出电压摆幅比所需的最大功率输出摆幅..模拟增益和主/从模式可以通过选择设置电压分压电阻R1和R2的增益/ SLV销..选择输入电容选择大容量电容器在PVCC输入适当的电压裕度和足够的容量来支持功率要求..在实践中;一个设计良好的电源;两个100μF轴;应将电容充足..一个电容应放置在设备两侧PVCC输入..PVCC电容器应该是一个低ESR的类型;因为他们被用在高速开关应用..选择去耦电容质量好的去耦电容需要在每个PVCC输入添加到提供良好的可靠性;良好的音频性能;并符合法规要求..X5R或更好的评级应采用应用..考虑温度;纹波电流和电压过冲;当选择去耦电容..同时;这些去耦电容应靠近PVCC和GND连接为设备为了减少串联电感..选择自举电容器每个输出需要启动电容器提供高侧FET的栅极驱动输出..为此设计;使用0.22μF;25-V X5R或更高质量的电容器应用曲线电源推荐为tpa3116d2电源要求由一个高电压功率输出扬声器放大器的阶段..几片上稳压器;包括在tpa3116d2生成音频路径的内部电路所需的电压..重要的是要注意的是;电压调节器已被集成的大小只提供必要的电源的内部电路的电流..这个外部引脚只提供作为一个连接点的芯片旁路电容器来过滤电源..连接外部电路;这些调节器输出可能会导致性能降低和损坏的装置..高压电源;在4.5 V和26 V;提供模拟电路内部和功率阶段PVCC..AVCC供应饲料内部LDO包括GVDD..该LDO输出连接外部引脚用于过滤的目的;但不应该连接到外部电路..GVDD LDO输出为内部函数提供当前所需的大小;但不提供外部负载..布局布局指南tpa3116d2可以用一个小的;廉价的铁氧体磁珠输出滤波器对于大多数应用程序..不过由于D类开关边缘快速;需要照顾的时候打印布局规划电路板..以下建议将有助于满足电磁兼容的要求..电容器的高频去耦电容应尽量靠近放置PVCC解耦尽可能计算机终端..大100μF或更大的散装的电源去耦电容应被放置在PVCC供应tpa3116d2..本地;高频旁路电容应靠近PVCC引脚尽可能..这些限制可以连接到集成电路直接接地垫一个极好的接地连接..考虑添加一个小的;质量好的低ESR陶瓷电容器之间100 pF和1核因子和一个更大的中间频率上限值在220个核因子和1μF之间也有良好的质在芯片两端PVCC连接..保持电流环从每一个输出;通过铁素体珠和小过滤器帽和回GND和紧尽可能小..电流环的大小决定了其作为天线的有效性..接地去耦电容应连接到GND PVCC..所有地面应连接集成电路的接地;应作为一个中央接地或星地面的tpa3116d2..输出滤波器的铁氧体电磁干扰滤波器见图35应放置在靠近输出端的可能对于最好的电磁干扰性能..该过滤器应放置在接近输出..用电容器铁氧体和液晶过滤器应接地..布局指南比如布局;看到tpa3116d2评价模块tpa3116d2evm用户指南slou336..两EVM用户手册和热垫的应用报道;SLMA002和slma004;可在钛在网站..布局实例散热器上使用的EVM热沉零件号ats-ti 10 op-521-c1-r1使用的EVM是一个14x25x50毫米铝型材散热片有三散热片见下图..在散热器的附加信息;去..这个大小的散热片已显示出足够的连续输出功率..音乐的顶峰因素气流将降低散热片大小的要求;可以使用较小的类型..11 器件和文档支持11.2 商标All trademarks are the property of their respective owners.11.3 静电放电警告ESD 可能会损坏该集成电路..德州仪器TI 建议通过适当的预防措施处理所有集成电路..如果不遵守正确的处理措施和安装程序;可能会损坏集成电路..ESD 的损坏小至导致微小的性能降级; 大至整个器件故障..精密的集成电路可能更容易受到损坏; 这是因为非常细微的参数更改都可能会导致器件与其发布的规格不相符..11.4 术语表SLYZ022 —TI 术语表..这份术语表列出并解释术语、首字母缩略词和定义..12 机械、封装和可订购信息以下页中包括机械、封装和可订购信息..这些信息是针对指定器件可提供的最新数据..这些数据会在无通知且不对本文档进行修订的情况下发生改变..欲获得该数据表的浏览器版本;请查阅左侧的导航栏..重要声明德州仪器TI 及其下属子公司有权根据JESD46 最新标准; 对所提供的产品和服务进行更正、修改、增强、改进或其它更改; 并有权根据JESD48 最新标准中止提供任何产品和服务..客户在下订单前应获取最新的相关信息; 并验证这些信息是否完整且是最新的..所有产品的销售都遵循在订单确认时所提供的TI 销售条款与条件..TI 保证其所销售的组件的性能符合产品销售时TI 半导体产品销售条件与条款的适用规范..仅在TI 保证的范围内;且TI 认为有必要时才会使用测试或其它质量控制技术..除非适用法律做出了硬性规定;否则没有必要对每种组件的所有参数进行测试..TI 对应用帮助或客户产品设计不承担任何义务..客户应对其使用TI 组件的产品和应用自行负责..为尽量减小与客户产品和应用相关的风险;客户应提供充分的设计与操作安全措施..TI 不对任何TI 专利权、版权、屏蔽作品权或其它与使用了TI 组件或服务的组合设备、机器或流程相关的TI 知识产权中授予的直接或隐含权限作出任何保证或解释..TI 所发布的与第三方产品或服务有关的信息;不能构成从TI 获得使用这些产品或服务的许可、授权、或认可..使用此类信息可能需要获得第三方的专利权或其它知识产权方面的许可;或是TI 的专利权或其它知识产权方面的许可..对于TI 的产品手册或数据表中TI 信息的重要部分;仅在没有对内容进行任何篡改且带有相关授权、条件、限制和声明的情况下才允许进行复制..TI 对此类篡改过的文件不承担任何责任或义务..复制第三方的信息可能需要服从额外的限制条件..在转售TI 组件或服务时;如果对该组件或服务参数的陈述与TI 标明的参数相比存在差异或虚假成分;则会失去相关TI 组件或服务的所有明示或暗示授权;且这是不正当的、欺诈性商业行为..TI 对任何此类虚假陈述均不承担任何责任或义务..客户认可并同意;尽管任何应用相关信息或支持仍可能由TI 提供;但他们将独力负责满足与其产品及在其应用中使用TI 产品相关的所有法律、法规和安全相关要求..客户声明并同意;他们具备制定与实施安全措施所需的全部专业技术和知识;可预见故障的危险后果、监测故障及其后果、降低有可能造成人身伤害的故障的发生机率并采取适当的补救措施..客户将全额赔偿因在此类安全关键应用中使用任何TI 组件而对TI 及其代理造成的任何损失..在某些场合中;为了推进安全相关应用有可能对TI 组件进行特别的促销..TI 的目标是利用此类组件帮助客户设计和创立其特有的可满足适用的功能安全性标准和要求的终端产品解决方案..尽管如此;此类组件仍然服从这些条款.. TI 组件未获得用于FDA Class III或类似的生命攸关医疗设备的授权许可;除非各方授权官员已经达成了专门管控此类使用的特别协议..只有那些TI 特别注明属于军用等级或“增强型塑料”的TI 组件才是设计或专门用于军事/航空应用或环境的..购买者认可并同意;对并非指定面向军事或航空航天用途的TI 组件进行军事或航空航天方面的应用;其风险由客户单独承担;并且由客户独力负责满足与此类使用相关的所有法律和法规要求..TI 已明确指定符合ISO/TS16949 要求的产品;这些产品主要用于汽车..在任何情况下;因使用非指定产品而无法达到ISO/TS16949 要求;TI不承担任何责任..产品应用数字音频通信与电信放大器和线性器件计算机及周边数据转换器消费电子。

烽火通信 2.5’’ SATA SSD DSS200-B 产品规格书说明书

烽火通信 2.5’’ SATA SSDDSS200-B产品规格书烽火通信科技股份有限公司 Fiberhome Telecommunication Technologies Co., LTD容量240/480/960GBSATA 接口SATA Revision 3.2SATA Gen3Flash 接口支持 Toggle 2.0/ONFI 3.0传输速度可达 533MBps最大支持 32 片 BGA132/152 Nand Flash 读写性能MTBF不少于 2,000,000 小时 UBER< 1 sector per 1017 bits read TBW240GB 337TB480GB 674TB960GB 1347TBFlash 管理技术时延顺序读: up to 530 MB/s顺序写: up to 500 MB/s随机读: up to 96K IOPS随即写: up to 70K IOPS顺序读写时延(typ.):34/37us 随机读写时延(typ.):114/26us功耗写操作功耗(Typ.)<3.80W读操作功耗 (Typ.) < 3.50W静态功耗 <1.1W支持静态及动态磨损均衡技术坏块管理技术TRIM 指令技术SMART 技术支持 OP 调节固件升级支持硬件断电保护温度范围工作温度: 0°C ~ 70°C存储温度: -40°C ~ 85°C产品认证RoHS FCC CE修改时间2019.03 2019.03 2019.05 2019.061.概述,采用标准 2.5具有低功耗,支持热插拔等优点。

SSD 的备 DDR3,连续写可达到 2.产品规格4K 随机 写一致性3.环境及可靠性DSS200-B 的4.电气特性5.指令列表SET FEATURES: Enable CFA power SET FEATURES: Enable Write-Read-Verify feature setSET FEATURES: Enable use of SerialDescriptionSET FEATURES: Disable use of Serial SET FEATURES: Disable Software Settings Preservation (SSP)SET FEATURES: Disable Device Automatic Partial to Slumber6.接口图 6-1 DSS200-B 2.5’’ SATA SSD 接口7.外形尺寸❖ 100.00mm(L)x69.85mm (W)x7.00mm (H)下视图 上视图侧视图8.产品保修政策9.参考资料。

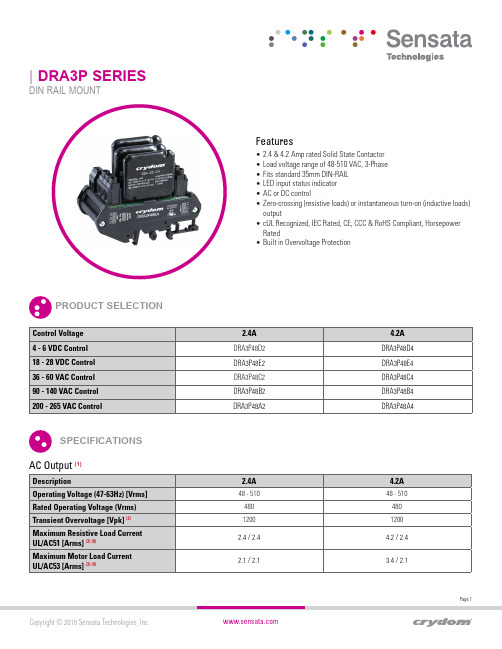

感测技术有限公司产品说明书:DRA3P48D2、DRA3P48D4、DRA3P48E2、DRA3P4

SPECIFICATIONSAC Output (1)Features• 2.4 & 4.2 Amp rated Solid State Contactor • Load voltage range of 48-510 VAC, 3-Phase • Fits standard 35mm DIN-RAIL • LED input status indicator • AC or DC control• Zero-crossing (resistive loads) or instantaneous turn-on (inductive loads) output• cUL Recognized, IEC Rated, CE, CCC & RoHS Compliant, Horsepower Rated• Built in Overvoltage ProtectionControl Voltage 4 - 6 VDC Control 18 - 28 VDC Control 36 - 60 VAC Control 90 - 140 VAC Control 200 - 265 VAC Control| DRA3P SERIESDIN RAIL MOUNTPRODUCT SELECTIONInput(1)DIAGRAMSWiring DiagramBlock DiagramGeneral (1)MECHANICAL SPECIFICATIONS Tolerances: ±0.02 in / 0.5 mmAll dimensions are in inches [millimeters]THERMAL DERATE INFORMATIONGENERAL NOTES(1) All parameters at 25 °C unless otherwise specified.(2)Relay will self trigger between 900-1200 Vpk. Not suitable for capacitive loads.(3)For AC control AC53 maximum current is 1.6A (4)Mounted in the vertical position (Din Rail in horizontal position).(5)For AC control, rating is ½ HP / 0.25 KW (6)For AC control, rating is 1 HP / 0.37 KW (7)For AC control, rating is 1 HP / 0.55 KW (8)Resistive Load Current rating for DRA3P48x4 (A,B & C suffix only) is 3.4 A (9)Turn-on time for DC control instantaneous turn-on versions is 0.1 msec.(10)Three Controlled legs versions only. Otherwise L2-T2 are connected internally.For additional information or specific questions, contact Sensata Technical Support.ORDERING OPTIONS3 Phase Function, 48-510 VAC Operating Voltage, 4-6 VDC Control Voltage, 4.2 Amp/ 2HP @ 480 VAC Rated Load Current, Instantaneous Turn-On Switching Type, 2 Controlled LegsRequired for Valid Part Number For Options Only and not Required for Valid Part NumberBlank: 3 Legs 2: 2 LegsAGENCY APPROVALS & CERTIFICATIONS• UL: E116950• CCC: Except DRA3P48xxx2)Page 6Americas+1 (877) 502 5500 – Option 2************************Europe, Middle East & Africa +44 (1202) 416170***********************Asia Pacific*************************.com China +86 (21) 2306 1500Japan +81 (45) 277 7117Korea +82 (31) 601 2004India +91 (80) 67920890Rest of Asia +886 (2) 27602006 ext 2808CONTACT USSensata Technologies, Inc. (“Sensata”) data sheets are solely intended to assist designers (“Buyers”) who are developing systems that incorporate Sensata products (also referred to herein as “components”). Buyer understands and agrees that Buyer remains responsible for using its independent analysis, evaluation and judgment in designing Buyer’s systems and products. Sensata data sheets have been created using standard laboratory conditions and engineering practices. Sensata has not conducted any testing other than that specifically described in the published documentation for a particular data sheet. Sensata may make corrections, enhancements, improvements and other changes to its data sheets or components without notice.Buyers are authorized to use Sensata data sheets with the Sensata component(s) identified in each particular data sheet. HOWEVER, NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER SENSATA INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY THIRD PARTY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT, IS GRANTED HEREIN. SENSATA DATA SHEETS ARE PROVIDED “AS IS”. SENSATA MAKES NO WARRANTIES OR REPRESENTATIONS WITH REGARD TO THE DATA SHEETS OR USE OF THE DATA SHEETS, EXPRESS, IMPLIED OR STATUTORY, INCLUDING ACCURACY OR COMPLETENESS. SENSATA DISCLAIMS ANY WARRANTY OF TITLE AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, QUIET ENJOYMENT, QUIET POSSESSION, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS WITH REGARD TO SENSATA DATA SHEETS OR USE THEREOF.All products are sold subject to Sensata’s terms and conditions of sale supplied at SENSATA ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR THE DESIGN OF BUYERS’ PRODUCTS. BUYER ACKNOWLEDGES AND AGREES THAT IT IS SOLELY RESPONSIBLE FOR COMPLIANCE WITH ALL LEGAL, REGULATORY AND SAFETY-RELATED REQUIREMENTS CONCERNING ITS PRODUCTS,WARNINGSRISK OF MATERIAL DAMAGE AND HOT ENCLOSURE• The product’s side panels may be hot, allow the product to cool before touching • Follow proper mounting instructions including torque values • Do not allow liquids or foreign objects to enter this productFailure to follow these instructions can result in serious injury, or equipment damage.HAZARD OF ELECTRIC SHOCK, EXPLOSION OR ARC FLASH• Disconnect all power before installing or working with this equipment • Verify all connections and replace all covers before turning on powerFailure to follow these instructions will result in death or serious injury.。

ARTISAN TECHNOLOGY GROUP 产品目录说明书

mini-OTDRAQ7250mini-OTDR AQ72502Automatic detection of splice or return loss values exceeding preset thresholds. It is also possible to edit the data generat-ed, deleting unnecessary splice points or adding points that were not detected.Measures the total return loss between two marker-selected points. Return loss is calculated from the difference between the backscatter level and the reflection level.Up to four waveforms can be displayed on a screen, simplify-ing waveform comparison. Differential display is also possible — convenient for monitoring change over time.Return loss measurementAuto-search function event display s Light power measurements Automatic search function event tableDisplays distance to event, splice loss, and return loss, as well as the total return loss of a section, for each of the automatical-ly detected waveforms. This is possible because the instru-ment captures all reflected light (returned light), including that from optical connectors, the far end, and backscattering light.It then calculates how much these various types of light have been attenuated with respect to the emitted light, to provide the total return loss for the optical fiber under measurement.Combined with the AQ7255B single mode fiber optical unit,long distance fibers up to approximately 200km can be mea-sured.When used with the AQ2761 sensor unit option, the AQ7250functions as an optical power meter.4Screen descriptionModeSelect TRACE, FILE, SPECIAL, and SETUP function screens. MenuItems change depending on the selected mode.LabelInput of up to 36 alphanumeric characters.Vertical-axis scale (dB/)Currently active settingsLNK: Cursor link.Used for simple splice loss measurement.RPT:Repeat measurement function.TPA, LSA:Approximation methods.Two-point (TPA), least square (LSA).FIL: Filter function.OBO, AUT, ATT:Automatic measurement functions.One-button measurement (OBO), auto-distance range (AUT), auto-attenuation (ATT).20k, 5k:Sample data count.Horizontal-axis scale (m/, km/)Overview display screenFull screen display of measurement waveform.The selected portion of the main waveform display is shown in a window.Date and timeFunction keysDisplays key functions.Vertical-axis display start levelDisplays the level value for the top of the waveform display window.Vertical-axis waveform display regionIndicates the display waveform range for the vertical full scale with a bar.Horizontal-axis display start distanceDisplays the distance value for the left side of the waveform display window.Horizontal-axis waveform display region312132223Print-outCommon I/O optical connectorKT-1914-2 0201 KL250Printed in JapanNOTE:q “PCMCIA” refers to PCMCIA 2.1/JEIDA Ver4.2 or higher.q All corporate, trade, and product names are the property of their respective companies.Output sampleAQ7931B OTDR Emulation SoftwareMeasurement data can be transferred from a diskette to a PC for subsequent waveform analysis by the user. In addition, the AQ7931B’s report function makes producing reports quick and easy.(Also compatible with Windows95 and Windows98)Windows95 and Windows98 are registered trademarks of Microsoft CorporationCasesq Soft carrying caseHolds: Main unit, AC adapter, spare battery pack, printer unit or optical switch unit, printer paper, power cord, and instruction manual (one each).q Hard carrying caseHolds: Main unit, AC adapter, spare battery pack, printer unit,optical switch unit, VLS unit or sensor unit, power cord, instruc-tion manual (one each), and printer paper (2 pcs.).Display screenOptional Accessoriesq Spare battery pack q AC adapter q Mouse q Hard-disk card q Keyboard q IC memory cardq AQ4253(*)VLS UnitVisible LD light-source unit capable of detecting even near-end faults.Wavelength: 635 ±10 nmOptical output level: -6 ±1.5 dBmApplicable optical fiber: SM (10/125 µm)Connector: FC or SC (factory option)q AQ2761 Sensor UnitWavelength range: 850, 1310, 1550, 1625nm Absolute accuracy: ±5% (at λ= 1310 nm)Application: Light emitted from small-diameter silica fibers (Core dia. 162.5 µm, NA 0.29)Power measurement range: -60 to +10 dBm Input: AQ9431(*)Connector Adapter (option)(* Specify FC, SC or ST connector)q GP-IB Unit for AQ7250q Centronics Unit for AQ7250q Optical Switch Unit for AQ7250 ( [ ] ch)Number of channels: 4, 8, 12, 16Wavelength range: 1270 nm to 1670 nm Insertion loss: 1.5 dB (typical value)Return loss: 40 dBApplicable optical fiber: SM (10/125 µm)Optical input/output connector: AQ9441(*)Universal Adapter (option) (*Specify FC, SC, ST or DIN connector)One extra connector adapter above the number of channels is required.Dimensions: Approx. 250 (W) x 150 (H) x 70 (D) mmq Printer Unit for AQ7250Dimensions: Approx. 250 (W) x 150 (H) x 70 (D) mmExtension Units(Any one of these extension units can be mounted on the back of the main unit)Sub Units(Any one of these sub units can be mounted on the top of the main unit)Ando Electric Co., Ltd.3-484, Tsukagoshi, Saiwai-ku, Kawasaki, Kanagawa, 212-8519 Japan Phone: +81 (0)44 549 7300 Fax: +81 (0)44 549 7450Ando Corporation20420 Century Boulevard Germantown, MD 20874, U.S.A. Phone: +1 301 916 0409 Fax: +1 301 916 1498SAN JOSE OFFICE: 2021 N. Capitol Avenue, San Jose, CA 95132, U.S.A. Phone: +1 408 941 0100 Fax: +1 408 941 0103Ando Europe B.V.“Vijverdam”, Dalsteindreef 57, 1112XC Diemen, The Netherlands Phone: +31(0)20 698 1441 Fax: +31(0)20 699 8938NIEDERLASSUNG DEUTSCHLAND: Nymphenburger Straße 119 B, D-80636 München, Germany Phone: +49(0)89 143 8150 Fax: +49(0)89 143 81555Ando Electric Singapore Pte. Ltd.19 Kim Keat Road #05-03, Fu Tsu Building, Singapore 328804 Phone: +65 251 1391 Fax: +65 251 1987Please visit our website for more information:Specifications are subject to change without notice.。

tpa3004d2英文资料

SD = 0VGNDFigure 44. Differential Output With FADE (Terminal 30) Held LowFigure 45 shows a scope capture of the differential output with the fade effect disabled. The outputs transition to the lowest gain state within 1ms of applying a logic low to the SD terminal.SD = 0 VFigure 45. Differential Output With FADE Terminal Held HighSELECTION OF COSC AND ROSCThe switching frequency is determined using the values of the components connected to ROSC (pin 27) and COSC (pin 28) and may be calculated with the following equation:Power−UpAV DD(pin 29)AV CC(pin 33)Ch1 2 V/div Ch2 5 V/div M 10.0Figure 46. Power-Up ResponseThe differential input stage of the amplifier cancels any noise that appears on both input lines of the channel. To use the TPA3004D2 EVM with a differential source, connect the positive lead of the audio source to the INP input and the negative lead from the audio source to the INN input. T o use the TPA3004D2 with a single-ended source, ac ground the INP input through a capacitor equal in value to the input capacitor on INN and apply the audio source to the INN input. In a single-ended input application, the INP input should be ac-grounded at thePACKAGING INFORMATIONOrderable Device Status (1)Package Type Package Drawing Pins Package Qty Eco Plan (2)Lead/Ball Finish MSL Peak Temp (3)TPA3004D2PHP ACTIVE HTQFP PHP 48250Green (RoHS &no Sb/Br)CU NIPDAU Level-4-260C-72HR TPA3004D2PHPG4ACTIVE HTQFP PHP 48250Green (RoHS &no Sb/Br)CU NIPDAU Level-4-260C-72HR TPA3004D2PHPR ACTIVE HTQFP PHP 481000Green (RoHS &no Sb/Br)CU NIPDAU Level-4-260C-72HR TPA3004D2PHPRG4ACTIVEHTQFPPHP481000Green (RoHS &no Sb/Br)CU NIPDAULevel-4-260C-72HR(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan -The planned eco-friendly classification:Pb-Free (RoHS),Pb-Free (RoHS Exempt),or Green (RoHS &no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free (RoHS):TI's terms "Lead-Free"or "Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all 6substances,including the requirement that lead not exceed 0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free (RoHS Exempt):This component has a RoHS exemption for either 1)lead-based flip-chip solder bumps used between the die and package,or 2)lead-based die adhesive used between the die and leadframe.The component is otherwise considered Pb-Free (RoHS compatible)as defined above.Green (RoHS &no Sb/Br):TI defines "Green"to mean Pb-Free (RoHS compatible),and free of Bromine (Br)and Antimony (Sb)based flame retardants (Br or Sb do not exceed 0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI basesits knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.PACKAGE OPTION ADDENDUM26-Oct-2009TAPE AND REELINFORMATION*Alldimensions are nominalDevicePackage Type Package Drawing Pins SPQReel Diameter (mm)Reel Width W1(mm)A0(mm)B0(mm)K0(mm)P1(mm)W (mm)Pin1Quadrant TPA3004D2PHPR HTQFPPHP481000330.016.49.69.6 1.512.016.0Q2PACKAGE MATERIALS INFORMATION11-Mar-2008*Alldimensions are nominal DevicePackage Type Package Drawing Pins SPQ Length (mm)Width (mm)Height (mm)TPA3004D2PHPR HTQFP PHP 481000346.0346.033.0PACKAGE MATERIALS INFORMATION 11-Mar-2008Pack Materials-Page 2IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers AudioData Converters AutomotiveDLP®Products BroadbandDSP Digital ControlClocks and Timers MedicalInterface MilitaryLogic Optical NetworkingPower Mgmt SecurityMicrocontrollers TelephonyRFID Video&ImagingRF/IF and ZigBee®Solutions WirelessMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2009,Texas Instruments Incorporated。

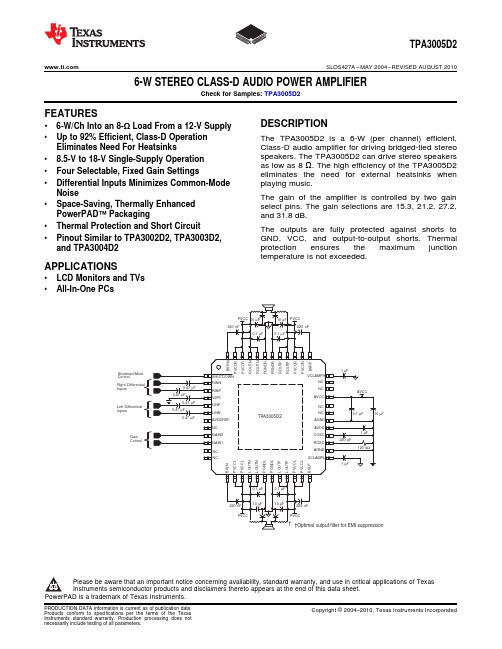

tpa3005d2

Left DifferentialInputsRight DifferentialInputsShutdown/MuteGainControlµFControlTPA3005D2 SLOS427A–MAY2004–REVISED AUGUST2010 6-W STEREO CLASS-D AUDIO POWER AMPLIFIERCheck for Samples:TPA3005D2FEATURESDESCRIPTION•6-W/Ch Into an8-ΩLoad From a12-V Supply•Up to92%Efficient,Class-D Operation The TPA3005D2is a6-W(per channel)efficient,Class-D audio amplifier for driving bridged-tied stereo Eliminates Need For Heatsinksspeakers.The TPA3005D2can drive stereo speakers •8.5-V to18-V Single-Supply Operationas low as8Ω.The high efficiency of the TPA3005D2•Four Selectable,Fixed Gain Settings eliminates the need for external heatsinks when •Differential Inputs Minimizes Common-Mode playing music.Noise The gain of the amplifier is controlled by two gain •Space-Saving,Thermally Enhanced select pins.The gain selections are15.3,21.2,27.2, PowerPAD™Packaging and31.8dB.•Thermal Protection and Short Circuit The outputs are fully protected against shorts toGND,VCC,and output-to-output shorts.Thermal •Pinout Similar to TPA3002D2,TPA3003D2,protection ensures the maximum junction and TPA3004D2temperature is not exceeded.APPLICATIONS•LCD Monitors and TVs•All-In-One PCsPlease be aware that an important notice concerning availability,standard warranty,and use in critical applications of TexasInstruments semiconductor products and disclaimers thereto appears at the end of this data sheet.PowerPAD is a trademark of Texas Instruments.PRODUCTION DATA information is current as of publication date.Copyright©2004–2010,Texas Instruments Incorporated Products conform to specifications per the terms of the TexasInstruments standard warranty.Production processing does notnecessarily include testing of all parameters.TPA3005D2SLOS427A–MAY2004–REVISED These devices have limited built-in ESD protection.The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.AVAILABLE OPTIONSPACKAGED DEVICET A48-PIN HTQFP(PHP)(1)(2)-40°C to85°C TPA3005D2PHP(1)The PHP package is available taped and reeled.To order a taped and reeled part,add the suffix R to the part number(e.g.,TPA3005D2PHPR).(2)For the most current package and ordering information,see the Package Option Addendum at the end of this document,or see the TIwebsite at .ABSOLUTE MAXIMUM RATINGSover operating free-air temperature range(unless otherwise noted)(1)TPA3005D2Supply voltage range AV CC,PV CC-0.3V to20VLoad Impedance,R L≥6ΩSHUTDOWN-0.3V to VCC+0.3VInput voltage range,V IGAIN0,GAIN1,RINN,RINP,LINN,LINP-0.3V to6VContinuous total power dissipation See Thermal Information Table Operating free–air temperature range,T A-40°C to85°COperating junction temperature range,T J-40°C to150°CStorage temperature range,T stg-65°C to150°C(1)Stresses beyond those listed under“absolute maximum ratings”may cause permanent damage to the device.These are stress ratingsonly,and functional operation of the device at these or any other conditions beyond those indicated under“recommended operating conditions”is not implied.Exposure to absolute–maximum–rated conditions for extended periods may affect device reliability.THERMAL INFORMATIONTPA3005D2THERMAL METRIC(1)(2)UNITSPHP(48PINS)q JA Junction-to-ambient thermal resistance27.7q JCtop Junction-to-case(top)thermal resistance14.8q JB Junction-to-board thermal resistance9.4°C/Wy JT Junction-to-top characterization parameter0.6y JB Junction-to-board characterization parameter 5.6q JCbot Junction-to-case(bottom)thermal resistance0.3(1)For more information about traditional and new thermal metrics,see the IC Package Thermal Metrics application report,SPRA953.(2)For thermal estimates of this device based on PCB copper area,see the TI PCB Thermal Calculator.RECOMMENDED OPERATING CONDITIONSMIN MAX UNIT Supply voltage,V CC PV CC,AV CC8.518VHigh-level input voltage,V IH SHUTDOWN,GAIN0,GAIN12VLow-level input voltage,V IL SHUTDOWN,GAIN0,GAIN10.8VSHUTDOWN,V I=V CC=18V10µAHigh-level input current,I IHGAIN0,GAIN1,V I=5.5V,V CC=18V1µASHUTDOWN,V I=0V,V CC=18V1µALow-level input current,I ILGAIN0,GAIN1,V I=5.5V,V CC=18V1µAFrequency is set by selection of ROSC and COSC(see the200300Oscillator frequency,f OSC kHzApplication Information Section).Operating free–air temperature,T A-4085°C2Submit Documentation Feedback Copyright©2004–2010,Texas Instruments IncorporatedProduct Folder Link(s):TPA3005D2TPA3005D2 SLOS427A–MAY2004–REVISED AUGUST2010DC ELECTRICAL CHARACTERISTICST A=25°C,V CC=12V,R L=8Ω(unless otherwise noted)PARAMETER TEST CONDITIONS MIN TYP MAX UNIT Class-D output offset voltage INN and INP connected together,|V OO|555mV (measured differentially)Gain=36dBV2P5 2.5-V Bias voltage No load 2.5VI L=10mA,SHUTDOWN=2V,AV DD+5-V internal supply voltage 4.55 5.5VV CC=8.5V to18VPSRR Power supply rejection ratio V CC=11.5V to12.5V-80dBI CC Quiescent supply current SHUTDOWN=2V,no load1122mAQuiescent supply current inI CC(SD)SHUTDOWN=0V 1.625µAshutdown modeHigh side600V CC=12V,r DS(on)Drain-source on-state resistance I O=1A,Low side500mΩT J=25°C Total11001300GAIN0=0.8V14.615.316.2GAIN1=0.8VGAIN0=2V20.521.221.8G Gain dBGAIN1=2V GAIN0=0.8V26.427.227.8GAIN0=2V31.131.832.5t on Turn-on time C(V2P5)=1µF,SHUTDOWN=2V16mst off Turn-off time C(V2P5)=1µF,SHUTDOWN=0.8V60µs AC ELECTRICAL CHARACTERISTICST A=25°C,V CC=12V,R L=8Ω,(unless otherwise noted)PARAMETER TEST CONDITIONS MIN TYP MAX UNIT200mV PP ripple from20Hz to1kHz,k SVR Supply voltage rejection ratio-70dBGain=15.6dB,Inputs ac-coupled to GNDTHD+N=0.13%,f=1kHz,R L=8Ω3P O Continuous output power WTHD+N=0.23%,f=1kHz,R L=8Ω6THD+N Total harmonic distortion plus P O=1W,f=1kHz,R L=8Ω0.1%noise20Hz to22kHz,A-weighted filter,V n Output integrated noise floor-80dBGain=15.6dBCrosstalk P O=1W,R L=8Ω,Gain=15.6dB,-93dBf=1kHzMaximum output at THD+N<0.5%,SNR Signal-to-noise ratio97dBf=1kHz,Gain=15.6dBThermal trip point150°CThermal hystersis20°CCopyright©2004–2010,Texas Instruments Incorporated Submit Documentation Feedback3Product Folder Link(s):TPA3005D2TPA3005D2SLOS427A–MAY2004–REVISED FUNCTIONAL BLOCK DIAGRAM4Submit Documentation Feedback Copyright©2004–2010,Texas Instruments IncorporatedProduct Folder Link(s):TPA3005D2131415161718192021222324252627282930313233343536484746454443424140393837123456789101112B S R NP V C C RP V C C RR O U T NR O U T NP G N D RP G N D RR O U T PR O U T PP V C C RP V C C RB S R PVCLAMPR NC NC NC NC AGND COSC ROSC AGND VCLAMPLSHUTDOWNRINN RINP V2P5LINP LINN NC GAIN0GAIN1NC NCB S L NP V C C L P V C C LL O U T NL O U T NP G N D LP G N D LL O U T PL O U T PP V C C LP V C C LB S L PTPA3005D2AV CC AV DD AV DD REFTPA3005D2SLOS427A –MAY 2004–REVISED AUGUST 2010PHP PACKAGE (TOP VIEW)Copyright ©2004–2010,Texas Instruments Incorporated Submit Documentation Feedback5Product Folder Link(s):TPA3005D2TPA3005D2SLOS427A–MAY2004–REVISED TERMINAL FUNCTIONSPIN NAME PIN NUMBER I/O DESCRIPTIONAGND26,30-Analog ground for digital/analog cells in coreAV CC33-High-voltage analog power supply,not connected internally to PVCCR or PVCCL5-V Regulated output for use by internal cells and GAIN0,GAIN1pins only.NotAV DD29Ospecified for driving other external circuitry.AV DD REF7O5-V Reference output—connect to gain setting resistor or directly to GAIN0,GAIN1. BSLN13-Bootstrap I/O for left channel,negative high-side FETBSLP24-Bootstrap I/O for left channel,positive high-side FETBSRN48-Bootstrap I/O for right channel,negative high-side FETBSRP37-Bootstrap I/O for right channel,positive high-side FETCOSC28I/O I/O for charge/discharging currents onto capacitor for ramp generator.GAIN09I Gain select least significant bit.TTL logic levels with compliance to AV DD.GAIN110I Gain select most significant bit.TTL logic levels with compliance to AV DD.LINN6I Negative audio input for left channelLINP5I Positive audio input for left channelLOUTN16,17O Class-D1/2-H-bridge negative output for left channelLOUTP20,21O Class-D1/2-H-bridge positive output for left channel8,11,12,31,NC-No internal connection32,34,35PGNDL18,19-Power ground for left channel H-bridgePGNDR42,43-Power ground for right channel H-bridgePower supply for left channel H-bridge(internally connected to pins22and23),not PVCCL14,15-connected to PVCCR or AV CC.Power supply for left channel H-bridge(internally connected to pins14and15),not PVCCL22,23-connected to PVCCR or AV CC.Power supply for right channel H-bridge(internally connected to pins46and47), PVCCR38,39-not connected to PVCCL or AV CC.Power supply for right channel H-bridge(internally connected to pins38and39), PVCCR46,47-not connected to PVCCL or AV CC.RINP3I Positive audio input for right channelRINN2I Negative audio input for right channelROSC27I/O I/O current setting resistor for ramp generator.ROUTN44,45O Class-D1/2-H-bridge negative output for right channelROUTP40,41O Class-D1/2-H-bridge positive output for right channelShutdown signal for IC(low=shutdown,high=operational).TTL logic levels with SHUTDOWN1Icompliance to V CC.VCLAMPL25-Internally generated voltage supply for left channel bootstrap capacitors. VCLAMPR36-Internally generated voltage supply for right channel bootstrap capacitors.V2P54O 2.5-V Reference for analog cells.Connect to AGND and PGND—should be the center point for both grounds.Internal Thermal Pad--resistive connection to AGND.TYPICAL CHARACTERISTICSTable1.TABLE OF GRAPHSFIGURETHD+N Total harmonic distortion+noise vs Output power1,2vs Frequency3,4,5,6 Closed loop response7I CC Supply current vs Output power8Efficiency vs Output power9Output power vs Supply voltage10,116Submit Documentation Feedback Copyright©2004–2010,Texas Instruments IncorporatedProduct Folder Link(s):TPA3005D2T H D +N −T o t a l H a r m o n i c D i s t o r t i o n + N o i s e − %P O − Output Power − WT H D +N −T o t a l H a r m o n i c D i s t o r t i o n + N o i s e − %P O − Output Power − WT H D +N −T o t a l H a r m o n i c D i s t o r t i o n + N o i s e − %f − Frequency − HzT H D +N −T o t a l H a r m o n i c D i s t o r t i o n + N o i s e − %f − Frequency − HzTPA3005D2SLOS427A –MAY 2004–REVISED AUGUST 2010TYPICAL CHARACTERISTICS (continued)Table 1.TABLE OF GRAPHS (continued)Crosstalkvs Frequency 12k SVR Supply ripple rejection ratio vs Frequency 13CMRRCommom-mode rejection ratiovs Frequency14TOTAL HARMONIC DISTORTION +NOISETOTAL HARMONIC DISTORTION +NOISEvsvsOUTPUT POWEROUTPUT POWERFigure 1.Figure 2.TOTAL HARMONIC DISTORTION +NOISETOTAL HARMONIC DISTORTION +NOISEvsvsFREQUENCYFREQUENCYFigure 3.Figure 4.Copyright ©2004–2010,Texas Instruments Incorporated Submit Documentation Feedback7Product Folder Link(s):TPA3005D2T H D +N −T o t a l H a r m o n i c D i s t o r t i o n + N o i s e − %f − Frequency − HzT H D +N −T o t a l H a r m o n i c D i s t o r t i o n + N o i s e − %f − Frequency − Hz024681012I C C − S u p p l y C u r r e n t − AP O− Total Output Power − WG a i n − d Bf − Frequency − HzP h a s e − 5TPA3005D2SLOS427A –MAY 2004–REVISED AUGUST 2010TOTAL HARMONIC DISTORTION +NOISETOTAL HARMONIC DISTORTION +NOISEvsvsFREQUENCYFigure 5.Figure 6.SUPPLY CURRENTvsCLOSED LOOP RESPONSETOTAL OUTPUT POWERFigure 7.Figure 8.8Submit Documentation FeedbackCopyright ©2004–2010,Texas Instruments IncorporatedProduct Folder Link(s):TPA3005D2E f f i c i e n c y − %P O − Total Output Power − W012345678910111289101112131415161718P O − O u t p u t P o w e r − WV CC− Supply Voltage − V234567891011121314V CC − Supply Voltage − VP O − O u t p u t P o w e r −WC r o s s t a l k − d Bf − Frequency − HzTPA3005D2SLOS427A –MAY 2004–REVISED AUGUST 2010EFFICIENCYOUTPUT POWERvsvsTOTAL OUTPUT POWERSUPPLY VOLTAGEFigure 9.Figure 10.OUTPUT POWERCROSSTALKvsvsSUPPLY VOLTAGEFigure 11.Figure 12.Copyright ©2004–2010,Texas Instruments Incorporated Submit Documentation Feedback9Product Folder Link(s):TPA3005D2f − Frequency − HzC M R R − C o m m o n -M o d e R e j e c t i o n R a t i o − d Bf − Frequency − Hzk S V R − S u p p l y R i p p l e R e j e c t i o n R a t i o − d BTPA3005D2SLOS427A –MAY 2004–REVISED AUGUST 2010SUPPLY RIPPLE REJECTION RATIOCOMMON-MODE REJECTION RATIOvsvsFREQUENCYFigure 13.Figure 14.10Submit Documentation FeedbackCopyright ©2004–2010,Texas Instruments IncorporatedProduct Folder Link(s):TPA3005D2Right DifferentialInputsShutdown/Mutem FControl Left DifferentialInputsGain Control*APPLICATION INFORMATIONFigure 15.Stereo Class-D With Differential Inputs0 V −12 V+12 VCurrentDifferential VoltageAcross LoadCLASS-D OPERATIONThis section focuses on the class-D operation of the TPA3005D2.Traditional Class-D Modulation SchemeThe traditional class-D modulation scheme,which is used in the TPA032D0x family,has a differential output where each output is 180degrees out of phase and changes from ground to the supply voltage,V CC .Therefore,the differential prefiltered output varies between positive and negative V CC ,where filtered 50%duty cycle yields 0V across the load.The traditional class-D modulation scheme with voltage and current waveforms is shown in Figure 16.Note that even at an average of 0V across the load (50%duty cycle),the current to the load is high,causing high loss and thus causing a high supply current.Figure 16.Traditional Class-D Modulation Scheme's Output Voltage and Current Waveforms Into anInductive Load With No InputTPA3005D2Modulation SchemeThe TPA3005D2uses a modulation scheme that still has each output switching from 0to the supply voltage.However,OUTP and OUTN are now in phase with each other with no input.The duty cycle of OUTP is greater than 50%and OUTN is less than 50%for positive output voltages.The duty cycle of OUTP is less than 50%and OUTN is greater than 50%for negative output voltages.The voltage across the load sits at 0V throughout most of the switching period,greatly reducing the switching current,which reduces any I 2R losses in the load.CurrentDifferentialVoltage Across LoadCurrentDifferentialVoltage Across LoadFigure 17.The TPA3005D2Output Voltage and Current Waveforms Into an Inductive LoadEfficiency:LC Filter Required With the Traditional Class-D Modulation SchemeThe main reason that the traditional class-D amplifier needs an output filter is that the switching waveform results in maximum current flow.This causes more loss in the load,which causes lower efficiency.The ripple current is large for the traditional modulation scheme,because the ripple current is proportional to voltage multiplied by the time at that voltage.The differential voltage swing is 2x V CC ,and the time at each voltage is half the period for the traditional modulation scheme.An ideal LC filter is needed to store the ripple current from each half cycle for the next half cycle,while any resistance causes power dissipation.The speaker is both resistive and reactive,whereas an LC filter is almost purely reactive.The TPA3005D2modulation scheme has little loss in the load without a filter because the pulses are short and the change in voltage is V CC instead of 2x V CC .As the output power increases,the pulses widen,making the ripple current larger.Ripple current could be filtered with an LC filter for increased efficiency,but for most applications the filter is not needed.An LC filter with a cutoff frequency less than the class-D switching frequency allows the switching current to flow through the filter instead of the load.The filter has less resistance than the speaker,which results in less power dissipation,therefore increasing efficiency.Effects of Applying a Square Wave Into a SpeakerAudio specialists have advised for years not to apply a square wave to speakers.If the amplitude of the waveform is high enough and the frequency of the square wave is within the bandwidth of the speaker,the square wave could cause the voice coil to jump out of the air gap and/or scar the voice coil.A 250-kHz switching frequency,however,does not significantly move the voice coil,as the cone movement is proportional to 1/f 2for frequencies beyond the audio band.Efficiency (theoretical,%)+RL ǒR L )r ds(on)Ǔ100%+8(8)1.3)100%+86%P (total)+P O Efficiency +6W 0.86+6.98WOther losses +P(total)(measured)*P(total)(theoretical)+7.41*6.98+0.43WP(dis)+0.43W *(12V 22mA)+0.17WDamage may occur if the voice coil cannot handle the additional heat generated from the high-frequency switching current.The amount of power dissipated in the speaker may be estimated by first considering the overall efficiency of the system.If the on-resistance (rds(on))of the output transistors is considered to cause the dominant loss in the system,then the maximum theoretical efficiency for the TPA3005D2with an 8-Ωload is as follows:(1)The maximum measured output power is approximately 6W with an 12-V power supply.The total theoreticalpower supplied (P(total))for this worst-case condition would therefore be as follows:(2)The efficiency measured in the lab using an 8-W speaker was 81%.The power not accounted for as dissipated across the r DS(on)may be calculated by simply subtracting the theoretical power from the measured power:(3)The quiescent supply current at 12V is measured to be 22mA.It can be assumed that the quiescent current encapsulates all remaining losses in the device,i.e.,biasing and switching losses.It may be assumed that any remaining power is dissipated in the speaker and is calculated as follows:(4)Note that these calculations are for the worst-case condition of 6W delivered to the speaker.Because the 0.17W is only 3%of the power delivered to the speaker,it may be concluded that the amount of power actually dissipated in the speaker is relatively insignificant.Furthermore,this power dissipated is well within the specifications of most loudspeaker drivers in a system,as the power rating is typically selected to handle the power generated from a clipping waveform.When to use an Output FilterDesign the TPA3005D2without the filter if the traces from amplifier to speaker are short (<50cm).Powered speakers,where the speaker is in the same enclosure as the amplifier,is a typical application for class-D without a filter.Most applications require a ferrite bead filter.The ferrite filter reduces EMI around 1MHz and higher (FCC and CE only test radiated emissions greater than 30MHz).When selecting a ferrite bead,choose one with high impedance at high frequencies,but low impedance at low frequencies.Use a LC output filter if there are low frequency (<1MHz)EMI-sensitive circuits and/or there are long wires from the amplifier to the speaker.When both a LC filter and a ferrite bead filter are used,the LC filter should be placed as close as possible to the IC followed by the ferrite bead filter.Figure 18.Typical LC Output Filter,Cutoff Frequency of 27kHz,Speaker Impedance =8ΩFerriteInput Signalf +12p Z i C iFigure 19.Typical Ferrite Chip Bead Filter (Chip bead example:Fair-Rite 2512067007Y3)Gain setting via GAIN0and GAIN1inputsThe gain of the TPA3005D2is set by two input terminals,GAIN0and GAIN1.The gains listed in Table 2are realized by changing the taps on the input resistors inside the amplifier.This causes the input impedance (Z i )to be dependent on the gain setting.The actual gain settings are controlled by ratios of resistors,so the gain variation from part-to-part is small.However,the input impedance may shift by 20%due to shifts in the actual resistance of the input resistors.For design purposes,the input network (discussed in the next section)should be designed assuming an input impedance of 26k Ω,which is the absolute minimum input impedance of the TPA3005D2.At the lower gain settings,the input impedance could increase as high as 165k ΩTable 2.Gain SettingINPUT IMPEDANCEAMPLIFIER GAIN (dB)(k Ω)GAIN1GAIN0TYP TYP 0015.31370121.2881027.2521131.833INPUT RESISTANCEEach gain setting is achieved by varying the input resistance of the amplifier that can range from its smallest value,33k Ω,to the largest value,137k Ω.As a result,if a single capacitor is used in the input high-pass filter,the -3dB or cutoff frequency changes when changing gain steps.The -3-dB frequency can be calculated using Equation e Table 2for Z i values.(5)f c +12p Z i C i−3 dBf cC i +12p Z i f cINPUT CAPACITOR,C IIn the typical application an input capacitor (C i )is required to allow the amplifier to bias the input signal to the proper dc level for optimum operation.In this case,C i and the input impedance of the amplifier (Z i )form a high-pass filter with the corner frequency determined in Equation 6.(6)The value of C i is important,as it directly affects the bass (low frequency)performance of the circuit.Consider the example where Z i is 137k Ωand the specification calls for a flat bass response down to 20Hz.Equation 6is reconfigured as Equation 7.(7)In this example,C i is 58nF,so one would likely choose a value of 0.1µF as this value is commonly used.If the gain is known and is constant,use Z i from Table 2to calculate C i .A further consideration for this capacitor is the leakage path from the input source through the input network (C i )and the feedback network to the load.This leakage current creates a dc offset voltage at the input to the amplifier that reduces useful headroom,especially in high gain applications.For this reason,a low-leakage tantalum or ceramic capacitor is the best choice.When polarized capacitors are used,the positive side of the capacitor should face the amplifier input in most applications as the dc level there is held at 2.5V,which is likely higher than the source dc level.Note that it is important to confirm the capacitor polarity in the application.For the best pop performance,C I should be less than or equal to 1µF.Power Supply Decoupling,C SThe TPA3005D2is a high-performance CMOS audio amplifier that requires adequate power supply decoupling to ensure the output total harmonic distortion (THD)is as low as possible.Power supply decoupling also prevents oscillations for long lead lengths between the amplifier and the speaker.The optimum decoupling is achieved by using two capacitors of different types that target different types of noise on the power supply leads.For higher frequency transients,spikes,or digital hash on the line,a good low equivalent-series-resistance (ESR)ceramic capacitor,typically 0.1µF placed as close as possible to the device V CC lead works best.For filtering lower-frequency noise signals,a larger aluminum electrolytic capacitor of 10µF or greater placed near the audio power amplifier is recommended.The 10-µF capacitor also serves as local storage capacitor for supplying current during large signal transients on the amplifier outputs.BSN and BSP CapacitorsThe full H-bridge output stages use only NMOS transistors.Therefore,they require bootstrap capacitors for the high side of each output to turn on correctly.A 220-nF ceramic capacitor,rated for at least 25V,must be connected from each output to its corresponding bootstrap input.Specifically,one 220-nF capacitor must be connected from xOUTP to xBSP,and one 220-nF capacitor must be connected from xOUTN to xBSN.(See the application circuit diagram in Figure 15).The bootstrap capacitors connected between the BSxx pins and corresponding output function as a floating power supply for the high-side N-channel power MOSFET gate drive circuitry.During each high-side switching cycle,the bootstrap capacitors hold the gate-to-source voltage high enough to keep the high-side MOSFETs turned on.VCLAMP CapacitorsTo ensure that the maximum gate-to-source voltage for the NMOS output transistors is not exceeded,two internal regulators clamp the gate voltage.Two1-µF capacitors must be connected from VCLAMPL(pin25)and VCLAMPR(pin36)to ground and must be rated for at least25V.The voltages at the VCLAMP terminals vary with V CC and may not be used for powering any other circuitry.Internal Regulated5-V Supply(AV DD)The AV DD terminal(pin29)is the output of an internally-generated5-V supply,used for the oscillator, preamplifier,and volume control circuitry.It requires a1-µF capacitor,placed close to the pin,to keep the regulator stable.This regulated voltage can be used to control GAIN0and GAIN1terminals,but should not be used to drive external circuitry.Differential InputThe differential input stage of the amplifier cancels any noise that appears on both input lines of the channel.To use the TPA3005D2with a differential source,connect the positive lead of the audio source to the INP input and the negative lead from the audio source to the INN input.To use the TPA3005D2with a single-ended source,ac ground the INP or INN input through a capacitor equal in value to the input capacitor on INN or INP and apply the audio source to either input.In a single-ended input application,the unused input should be ac-grounded at the audio source instead of at the device input for best noise performance.SHUTDOWN OPERATIONThe TPA3005D2employs a shutdown mode of operation designed to reduce supply current(I CC)to the absolute minimum level during periods of nonuse for power conservation.The SHUTDOWN input terminal should be held high(see specification table for trip point)during normal operation when the amplifier is in use.Pulling SHUTDOWN low causes the outputs to mute and the amplifier to enter a low-current state.Never leave unconnected because amplifier operation would be unpredictable.For the best power-off pop performance,place the amplifier in the shutdown mode prior to removing the power supply voltage.USING LOW-ESR CAPACITORSLow-ESR capacitors are recommended throughout this application section.A real(as opposed to ideal)capacitor can be modeled simply as a resistor in series with an ideal capacitor.The voltage drop across this resistor minimizes the beneficial effects of the capacitor in the circuit.The lower the equivalent value of this resistance, the more the real capacitor behaves like an ideal capacitor.SHORT-CIRCUIT PROTECTIONThe TPA3005D2has short-circuit protection circuitry on the outputs that prevents damage to the device during output-to-output shorts,output-to-GND shorts,and output-to-V CC shorts.When a short-circuit is detected on the outputs,the part immediately disables the output drive.This is a latched fault and must be reset by cycling the voltage on the pin to a logic low and back to the logic high state for normal operation.This clears the short-circuit flag and allow for normal operation if the short was removed.If the short was not removed,the protection circuitry again activates.THERMAL PROTECTIONThermal protection on the TPA3005D2prevents damage to the device when the internal die temperature exceeds150°C.There is a±15degree tolerance on this trip point from device to device.Once the die temperature exceeds the thermal set point,the device enters into the shutdown state and the outputs are disabled.This is not a latched fault.The thermal fault is cleared once the temperature of the die is reduced by 20°C.The device begins normal operation at this point with no external system interaction.PRINTED-CIRCUIT BOARD(PCB)LAYOUTBecause the TPA3005D2is a class-D amplifier that switches at a high frequency,the layout of the printed-circuit board(PCB)should be optimized according to the following guidelines for the best possible performance.。

TR3005资料