FPGA中的基于oDDR技术的并行采样设计

基于FPGA的并行计算技术

基于FPGA的并行计算技术更新于2012-03-13 17:15:57 文章出处:互联网1 微处理器与FPGA微处理器普遍采用冯·诺依曼结构,即存储程序型计算机结构,主要包括存储器和运算器2个子系统。

其从存储器读取数据和指令到运算器,运算结果储存到存储器,然后进行下一次读取-运算-储存的操作过程。

通过开发专门的数据和指令组合,即控制程序,微处理器就可以完成各种计算任务。

冯·诺依曼型计算机成功地把信息处理系统分成了硬件设备和软件程序两部分,使得众多信息处理问题都可以在通用的硬件平台上处理,只需要开发具体的应用软件,从而极大地降低了开发信息处理系统的复杂性。

然而,冯·诺依曼型计算机也有不足之处,由于数据和指令必须在存储器和运算器之间传输才能完成运算,使得计算速度受到存储器和运算器之间信息传输速度的限制,形成所谓的冯·诺依曼瓶颈[1];同时,由于运算任务被分解成一系列依次执行的读取-运算-储存过程,所以运算过程在本质上是串行的,使并行计算模式在冯·诺依曼型计算机上的应用受到限制。

受到半导体物理过程的限制,微处理器运算速度的提高已经趋于缓慢,基于多核处理器或者集群计算机的并行计算技术已经逐渐成为提高计算机运算性能的主要手段。

并行计算设备中包含多个微处理器,可以同时对多组数据进行处理,从而提高系统的数据处理能力。

基于集群计算机的超级计算机已经成为解决大型科学和工程问题的有利工具。

然而,由于并行计算设备中的微处理器同样受冯·诺依曼瓶颈的制约,所以在处理一些数据密集型,如图像分析等问题时,计算速度和性价比不理想。

现场可编程门阵列(FPGA)是一种新型的数字电路。

传统的数字电路芯片都具有固定的电路和功能,而FPGA可以直接下载用户现场设计的数字电路。

FPGA技术颠覆了数字电路传统的设计-流片-封装的工艺过程,直接在成品PFGA芯片上开发新的数字电路,极大地扩大了专用数字电路的用户范围和应用领域。

基于FPGA的Sobel算子并行计算研究

7!, # P ’ A算子

图像锐化 技 术 用 于 加 强 图 像 中 的 目 标 边 界 和 图 像 细 节 $ 微分法是图像锐化方 法 之 一 & 由 数 学 分 析 可 知 $ 可 微 函数 G! !$ "#的梯度为 % ( )5 U 52 ; 0 C !$ G! "# <G <G -9 L <! <" ! # "

!"" # $ % &算子的并行处理结构

表第 -.! 行 " 依此类推 ( 对于一般的灰度图像 " 其象 素 的 灰 度 值 一 般 用 / 位 表 示 " 考虑到计算 过 程 中 可 能 出 现 负 数 和 溢 出 问 题 ( 因 此 " 数据在开始 计 算 前 先 在 最 高 位 补 零 " 使 数 据 宽 度 变 为 ! 0 位 " 计算完成后可再裁剪为 / 位 ( 图 " 中 比 较 器 的 作 用 是 将求得的 ’ ( & ) *梯度与门限做比较 " 从而增强边界 (

由于图像并行处理技术可大 幅 度 提 高 处 理 速 度 " 因 而 获得了广泛的运用 ( 常用的并行处 理 有 两 种 最 基 本 的 连 接

"% 模式 $ &图

! # 的流水线连接和图 ! ! # 并行阵列连接 ( ! % &

’" 仿真结果

采用 1 5 ! 6 + 0 7 8 ! 9 9 !芯片进行仿 * 2 ) 3 %公司的 4

% $ ! " # $ % & ’ $ 1< 4 5: ; > B 5 3 3 8 1 ? ; 5 0 F< 8 = 5 8 = 0 55 C 55 1 4 0 1 B 5 = 5 1 < A > M 5 F > 5 ; 0 < > ; 8 3> ? < 5 19 3 5 C T_ > E< > 8 = ; > I 5 8 < 3: ; > B 5 3 3 8 1 5 5 C 2> 2 2 : : 23 : $ M 5 B 0 9 3 5> ? < 4 5 ? 0 3 < C 5 S M 5 B > = 5 30N 5 ; > M F 5 = T < 8 3C 8 ? ? 8 B 9 F < < >9 3 5: 9 ; 5 3 > ? < E 0 ; 5> ;2 5 1 5 ; 0 F 4 0 ; C E 0 ; 5 < >= 5 5 < < 4 5 ; 5 9 8 ; 5 = 5 1 < > ? ; 5 0 F < 8 = 5 G: j I 5 F > = 5 1 < ? > ;V & R)$ E 5B 0 19 3 5 8 < < >8 = ; > I 5B 0 F B 9 F 0 < 8 > 13 5 5 C? > ;A > M 5 F> 5 ; < > ; T% 4 8 3: 0 5 ;: ; 5 3 5 1 < 30N 8 1 C> ?: 0 ; 0 F F 5 F: ; > B 5 3 3 8 1 > 1 S : : : : : 2B $ 3 < ; 9 B < 8 > 1> ? A > M 5 F > 5 ; 0 < > ; 0 1 C 8 < 3V & R) M 0 3 5 C 8 = F 5 = 5 1 < 8 1 5 < 4 > C T% 4 5 B > ; ; 5 B < 1 5 3 3 0 1 C ? 5 0 3 8 M 8 F 8 < 0 I 5M 5 5 1: ; > I 5 CM < 4 5 > ; 5 < 8 B 0 1 0 F S : : 2= G4 G $ 3 8 30 1 C3 8 = 9 F 0 < 8 > 1 T% 4 5: ; > B 5 3 3 8 1 5 5 CB 0 1M 52 ; 5 0 < F 1 4 0 1 B 5 CM 3 8 1 0 ; 0 F F 5 F: ; > B 5 3 3 8 1 > 1 3 < ; 9 B < 8 > 1 0 1 C= 5 5 < < 4 50 B < 9 0 F < 0 3 N T G 23 : G5 G9 2: 2B % " " ( ) + , % # A > M 5 F > 5 ; 0 < > ; V & R)" 0 ; 0 F F 5 F: ; > B 5 3 3 8 1 8 = 0 55 C 55 1 4 0 1 B 5 = 5 1 < : : 2 2 2 *

基于FPGA的多通道采样系统设计课程设计论文

FPGA课程设计题目:基于FPGA的多通道采样系统设计院(系):电气工程及其自动化学院专业:电子信息工程12-01摘要本论文介绍了基于FPGA的多通道采样系统的设计。

用FPGA设计一个多通道采样控制器,利用VHDL语言设计有限状态机来实现对AD7892的控制。

由于FPGA器件的特性是可以实现高速工作,为此模拟信号选用音频信号。

由于音频信号的频率是20Hz-20KHz,这样就对AD转换的速率有很高的要求.因为FPGA的功能很强大,所以我们把系统的许多功能都集成到FPGA器件中,例如AD通道选择部分,串并输出控制模块,这样使得整个系统的外围电路简单、系统的稳定性强。

FPGA的配置模式选用被动串行模式,这样就增强了系统的可扩展性。

输出模式可选择性使得系统的应用相当广泛,串行输出可以用于通信信号的采集,方便调制后发射到远程接受端,远程接收端对采集的数据进行解调;而并行输出模式则可以通过高速存储器将采集的信号放到微机或者其他的处理器上,根据采集的数据进行相应的控制。

此系统的缺点是由于FPGA器件配置是基于SRAM查找表单元,编程的信息是保持在SRAM中,但SRAM在掉电后编程信息立即丢失,所以每次系统上电都需要重新配置芯片,这对在野外作业的工作人员很不方便,解决的方法是专用的配置器件来配置FPGA,在每次系统上电的时候会自动把编程信息配置到FPGA芯片中。

但设计中没有采用到这种配置方案主要是考虑到专用配置器件的价格问题。

本文开始介绍了多通道系统的组成部分,然后分别介绍了各个组成部分的原理和设计方法,其中重点介绍了FPGA软件设计部分。

还对当前十分流行的基于FPGA的设计技术作了简单的阐述,最后对系统的调试和应用作了简短的说明。

关键词:音频放大;滤波器;FPGA;VHDL;AD7892;有限状态机;目录摘要 (2)引言 (3)1题目来源 (3)2研究意义 (3)3多通道采样系统的组成 (3)4方案设计 (4)5 单元电路的设计 (4)5.1音频放大、滤波部分 (4)(1)音频放大部分 (4)(2)有源滤波器的设计 (4)5.2 AD采样电路 (5)5.3 FPGA控制部分 (5)(1)通道选择模块 (6)(2)延时模块的设计 (6)(3)串并输出选择控制 (7)5.4 FPGA的硬件设计 (8)6 软件介绍 (8)7 整机调试 (8)7.1 硬件电路的调试步骤 (8)(1)音频放大部分调试 (8)(2)滤波部分调试 (8)(3)FPGA硬件电路调试 (9)(4)AD采样模块调试 (9)(5) 联机调试 (9)8 结论 (9)参考文献 (10)附录 (11)引言FPGA(Field-Programmable Gate Array 现场可编程门阵列)是近年来广泛应用的超大规模、超高速的可编程逻辑器件,由于其具有高集成度(单片集成的系统门数达上千万门)、高速(200MHz 以上)、在线系统可编程等优点,为数字系统的设计带来了突破性变革,大大推动了数字系统设计的单片化、自动化,提高了单片数字系统的设计周期、设计灵活性和可靠性。

基于FPGA超高频RFID系统并行CRC模块设计

基于FPGA超高频RFID系统并行CRC模块设计【摘要】根据CRC(循环冗余校验码)算法的原理,和ISO/IEC18000-6标准中超高频射频识别系统对校验电路的要求,分析串行CRC算法,提出了一种并行CRC算法。

经Verilog-HDL语言编写该算法程序,在QuartusⅡ9.0软件上仿真。

最终给出仿真结果以及并行CRC生成模块和校验模块,仿真结果证明并行CRC算法有效提高了系统中数据的处理速度。

【关键词】循环冗余校验码;射频识别;并行算法;Verilog-HDLRFID(射频识别)技术是一种非接触式的自动识别技术,被广泛用于诸如生产自动化、身份识别、物流等领域[1]。

但在用于数据传输时,可能受噪声干扰等因素的影响使传输的数据发生错误,导致识别失败,因此RFID系统必须具备很强的发现和纠正差错的能力。

按照ISO/IEC18000-6标准规定,在超高频RFID 系统中采用CRC(循环冗余校验码)作为链路数据传输正确性校验的方法。

传统超高频RFID系统中采用串行CRC算法,此方法电路简单,通信可靠性强。

但是随着社会的发展,串行计算方法已经不能满足大信息量条件下高传输速度的要求,因此有必要采用更快计算方法完成数据校验。

本文介绍的并行CRC 算法在保证通信的可靠性的同时也提高了数据处理的速度。

1.串行CRC算法分析及并行CRC算法推导1.1 CRC的原理CRC码是一种线性分组码,它的基本思想是利用线性编码理论[2],在发送方依据要传送的位信息码,按预先约定的规则生成一个校验用的位CRC校验码,并将其附在信息码后,构成一个新的位二进制码序列数,最后发送出去。

在接收方,则根据生成CRC校验码时所遵循的规则进行校验,以确定传送的数据是否出错。

具体实现方法如下:(1)将待发送的位数据用多项式表示,其中,数据序列为多项式的系数。

将左移位,即用乘以,作为被除式。

(2)发送时,被除式与发送方和接收方预先约定的生成多项式进行模2除法运算,求得一个余数多项式:其中为商,为余数也就是生成的CRC校验码。

基于FPGA的多源异构数据并行可配置采集方法

第27卷第4期计算机集成制造系统Vol.27No.4 2021年4月Computer Integrated Manufacturing Systems Apr.2021 DOI:10.13196/j.cims.2021.04.005基于FPGA的多源异构数据并行可配置采集方法李展鹏1,邹孝付",苏雍贺1,张长志彳,陶飞1(1.北京航空航天大学自动化科学与电气工程学院,北京100191;2.国网天津市电力公司电力科学研究院,天津300384)摘要:数据是支撑智能制造的关键要素,对生产各阶段数据的有效采集是实现“人一机一物一环境”制造全要素互联互通的基础。

随着制造升级发展,车间不断引入来自不同厂家,具有不同协议、不同接口的设备,使得待采集数据多源异构且采集需求不断变化。

传统数据采集设备难以并行采集多源异构数据、难以根据采集需求的动态变化对采集设备动态配置,因此提出一种基于现场可编程门阵列(FPGA)的多源异构数据并行可配置采集方法,基于FPGA硬件并行完成对多源异构数据的监测,保证数据采集实时性;研究FPGA动态重构技术并设计了数据采集可配置方法,提升数据采集灵活性;最后,设计了验证方案,验证了所提方法的有效性。

关键词:现场可编程门阵列;多源异构;数据采集;动态重构中图分类号:TP274.2文献标识码:AConfigurable acquisition method of multi-source heterogeneous data based on FPGALIZhanpeng1,ZOUXiaofu1+,SUYonghe1,ZHANG Changzhi2,TAO Fei1(1.School of Automation Science and Electrical Engineering,Beihang University,Beijing100191,China;2.State Grid Tianjin Electronic Power Research Institute,Tianjin300384,China)Abstract:Data is a key element supporting intelligent manufacturing.With the upgrading of manufacturing,the factory continuously introduces equipment from different manufacturers with different protocols and different interfaces.Data from that equipment collected has the characteristics of multi-source heterogeneity and constantly updated.Traditional data acquisition systems are customized for specific equipment,which is difficult to achieve parallel acquisition of multi-source heterogeneous data and real-time dynamic configuration.To solve these problems,a configurable acquisition method based on Field Programmable Gate Array(FPGA)was presented.Multi-source heterogeneous data were collected in parallel to ensure the real-time data acquisition.A configurable data acquisition scheme was designed to enhance the flexibility of data acquisition.A verification scheme was designed to verify the effectiveness of the proposed method.Keywords:field programmable gate array;multi-source heterogeneity;data acquisition;dynamic reconfiguration0引言随着云计算、大数据、物联网等新一代信息技术的发展以及信息化与工业化的“深度融合”,传统制造企业不断向智能制造的方向转型升级数据是智能制造的关键要素阂,只有在制造工厂底层实现对生产数据的有效感知,才能有效地完成工厂资源管理、车间计划与排产、生产过程监控等重要工收稿日期:2020-11-12;修灯日期:2020-11-25,,Received12Nov.2020;accepted25Nov.2020.基金项目:国家重点研发计划资助项目(2018YFB1500800);北京市科技重大专项资助项目(Z191100002719004);国家电网有限公司科技资助项目(SGTJDK00DYJS2000148)0Foundation items:Project supported by the National Key Research and Develapment Program,Chi-na(No.2018YFB1500800),the Beijing Municipal Science and Technology Major Project,China(No.Z191100002719004),and the Science and Technology Foundation of State Grid Corporation,China(No.SGTJDK00DYJS2000148).第4期李展鹏等:基于FPGA的多源异构数据并行可配置采集方法1009作闪。

基于FPGA的UART 16倍频采样的VHDL设计

基于FPGA 的UART 16 倍频采样的VHDL 设计概述随着电子设计自动化(EDA)技术的发展,可编程逻辑器件FPGA/CPLD 已经在许多方面得到了广泛应用,而UART(通用异步收发器) 是在数字通信和控制系统中广泛使用的串行数据传输协议。

因此越来越多用户根据自己的需要,以EDA 技术作为开发手段,用一块FPGA/CPLD 设计出符合自己需要的UART 芯片。

基于FPGA/ CPLD 的UART 设计在诸多文献中都有论述,在此不再对UART 整个功能模块实现做太多的论述。

本文着重分析UART 接收器起始位的检测。

3 倍频采样的缺陷首先,串行异步通信规定了字符数据的传送格式。

每一帧数据由起始位、数据位、奇偶校验位、停止位和线路空闲状态组成,格式如图1 所示。

一般情况起始位为1 位,数据位为5、6、7 或8 位、奇偶校验位为1 位,停止位为1、1.5 或2 位。

其中的起始位和停止位就是用来实现字符的同步。

在空闲状态,传送线为逻辑1 状态。

数据的传送总是以一个起始位开始的,接着是要传送的若干数据位,低位先行,最后是一个1 状态的停止位;那么,当接收器检测到一个1 向0 的跳变时,便视为可能的起始位。

起始位被确认后,就知道发送器已开始发送,当接收了已协议好的位数后并接收到字符帧中停止位就是一帧字符数据已发送完毕。

这样,接收器就知道发送器何时开始发送数据和何时结束发送数据。

要提高接收器的接收准确性,减少误码率,必须要用比数据波特率高n 倍(n≥1)的速率对数据进行采样。

文献2 中采用了非常规的3 倍频采样方法:用3 倍频的波特率对每一位数据进行采样(如图2 所示),然后对3 次采样结果进行判决。

如果3 次采样中至少有2 次为高电平,则接收这一位数据被判决为。

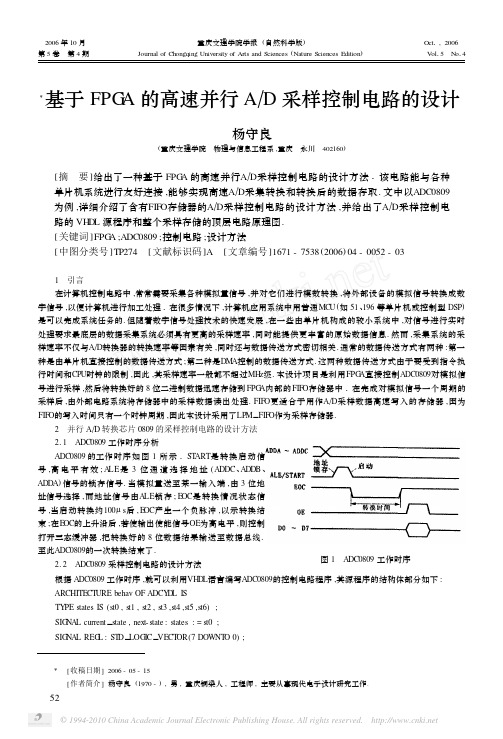

基于FPGA的高速并行A_D采样控制电路的设计

2006年10月重庆文理学院学报(自然科学版)Oct 1,2006 第5卷 第4期Journal of Chongqing University of Arts and Sciences (Nature Sciences Edition )V ol 15 N o 14Ξ基于FPG A 的高速并行A ΠD 采样控制电路的设计杨守良(重庆文理学院 物理与信息工程系,重庆 永川 402160)[摘 要]给出了一种基于FPG A 的高速并行A ΠD 采样控制电路的设计方法1该电路能与各种单片机系统进行友好连接,能够实现高速A ΠD 采集转换和转换后的数据存取.文中以ADC0809为例,详细介绍了含有FIFO 存储器的A ΠD 采样控制电路的设计方法,并给出了A ΠD 采样控制电路的VH D L 源程序和整个采样存储的顶层电路原理图.[关键词]FPG A ;ADC0809;控制电路;设计方法[中图分类号]TP274 [文献标识码]A [文章编号]1671-7538(2006)04-0052-031 引言在计算机控制电路中,常常需要采集各种模拟量信号,并对它们进行模数转换,将外部设备的模拟信号转换成数字信号,以便计算机进行加工处理1在很多情况下,计算机应用系统中用普通MC U (如51、196等单片机或控制型DSP )是可以完成系统任务的.但随着数字信号处理技术的快速发展,在一些由单片机构成的较小系统中,对信号进行实时处理要求最底层的数据采集系统必须具有更高的采样速率,同时能提供更丰富的原始数据信息.然而,采集系统的采样速率不仅与A ΠD 转换器的转换速率等因素有关,同时还与数据传送方式密切相关.通常的数据传送方式有两种:第一种是由单片机直接控制的数据传送方式;第二种是DM A 控制的数据传送方式.这两种数据传送方式由于要受到指令执行时间和CPU 时钟的限制,因此,其采样速率一般都不超过MH z 级.本设计项目是利用FPG A 直接控制ADC0809对模拟信号进行采样,然后将转换好的8位二进制数据迅速存储到FPG A 内部的FIFO 存储器中1在完成对模拟信号一个周期的采样后,由外部电路系统将存储器中的采样数据读出处理.FIFO 更适合于用作A ΠD 采样数据高速写入的存储器,因为FIFO 的写入时间只有一个时钟周期,因此本设计采用了LP M —FIFO 作为采样存储器.2 并行A ΠD 转换芯片0809的采样控制电路的设计方法图1 ADC0809工作时序2.1 ADC0809工作时序分析ADC0809的工作时序如图1所示1ST ART 是转换启动信号,高电平有效;A LE 是3位通道选择地址(ADDC 、ADDB 、ADDA )信号的锁存信号.当模拟量送至某一输入端,由3位地址信号选择,而地址信号由A LE 锁存;E OC 是转换情况状态信号,当启动转换约100μs 后,E OC 产生一个负脉冲,以示转换结束;在E OC 的上升沿后,若使输出使能信号OE 为高电平,则控制打开三态缓冲器,把转换好的8位数据结果输送至数据总线.至此ADC0809的一次转换结束了.2.2 ADC0809采样控制电路的设计方法根据ADC0809工作时序,就可以利用VH D L 语言编写ADC0809的控制电路程序,其源程序的结构体部分如下:ARCHITECT URE behav OF ADCY D L ISTY PE states IS (st0,st1,st2,st3,st4,st5,st6);SIG NA L current —state ,next-state :states :=st0;SIG NA L REG L :ST D —LOGIC —VECT OR (7DOW NT O 0);25Ξ[收稿日期]2006-05-15[作者简介]杨守良(1970-),男,重庆铜梁人,工程师,主要从事现代电子设计研究工作.SIG NA L LOCK:ST D—LOGIC;BEGI NADDA<=‘1’;LOCK1<=LOCK;PRO:PROCESS(current—state,E OC)BEGI NC ASE current—state ISWHE N st0=>A LE<=‘0’;ST ART<=‘0’;OE<=‘0’;LOCK<=‘0’;next—state<=st1;WHE N st1=>A LE<=‘1’;ST ART<=‘0’;OE<=‘0’;LOCK<=‘0’;next—state<=st2;WHE N st2=>A LE<=‘0’;ST ART<=‘1’;OE<=‘0’;LOCK<=‘0’;next—state<=st3;WHE N st3=>A LE<=‘0’;ST ART<=‘0’;OE<=‘0’;LOCK<=‘0’;IF(E OC=‘1’)THE N next—state<=st3;E LSE next—state<=st4;E ND IF;WHE N st4=>A LE<=‘0’;ST ART<=‘0’;OE<=‘0’;LOCK<=‘0’;IF(E OC=‘0’)THE N next-state<=st4;E LSE next—state<=st5;E ND IF;WHE N st5=>A LE<=‘0’;ST ART<=‘0’;OE<=‘1’;LOCK<=‘0’;next—state<=st6;WHE N st6=>A LE<=‘0’;ST ART<=‘0’;OE<=‘1’;LOCK<=‘1’;next—state<=st0;WHE N OTHERS=>A LE<=‘0’;ST ART<=‘0’;OE<=‘0’;LOCK<=‘0’;next—state<=st0;E ND C ASE;E ND PROCESS PRO;PROCESS(C LK)BEGI NIF(C LK’E VE NT AND C LK=‘1’)THE Ncurrent—state<=next—state;E ND IF;E ND PROCESS;PROCESS(LOCK)BEGI NIF LOCK=‘1’AND LOCK’E VE NT THE N REG L<=D;E ND IF;E ND PROCESS;Q<=REG L;E ND behav;2.3 对设计电路进行仿真测试利用QuartusII对其进行文本编辑输入、编译和仿真测试,得到ADC0809芯片控制电路的仿真波形,其仿真波形如图2所示1由此可见,设计已满足ADC0809各控制信号的要求.最后进行引脚锁定并下载到FPG A目标器件中进行测试,以验证设计的电路对ADC0809的控制功能.图2 ADC0809仿真波形图3 采样存储电路的设计方法采样存储电路采用lpm—FIFO参数化宏功能块,它有一个输入和一个输出共用端口,其输入端口连接ADC0809采样输出端.它的输出端连接在CPU的数据总线上,用于CPU需要读取数据时使用.其设计的顶层电路图如图3所示.AD—35FIFO的工作分两个阶段,即采样阶段和数据读取阶段.在前一阶段,输入控制信号WR—E N为高电平,C LK使能,读请求rdreq禁止.在某一采样周期中,当转换结束后,ADC0809的8位数据出现在数据总线D[7..0]上时,由ADCI NT发出的LOCK信号的上升沿将总线上的数据锁存进FIFO2中.在完成一个或数个输入模拟信号周期采样后进入数据读取阶段.在数据读取阶段中,WR—E N被置为低电平,FIFO2的读写时钟C LOCK通过M UX由RD—E N控制,在它的每一个上升沿, FIFO2中的数据将一一出现在端口Q[7..0]上.图3 ADC采样控制存储电路顶层电路图4 结语在整个系统设计过程中,数据采集与数据传送独立于CPU,选用FPG A作为采样控制电路和采样后的数据存储电路.因此,这种方式摆脱了CPU时钟的限制,这样数据采集、数据传送可以同时进行,从而大大提高了采集与传送的速度.[参考文献][1]S tefan S joholm,Lennart Lindh.边计年,薛宏熙,译.VH D L设计电子线路[M].北京:清华大学出版社,2000.[2]潘松,黄继业,王国栋.现代DSP技术[M].西安:西安电子科技大学出版社,2003.[3]潘松,黄继业.E DA技术实用教程[M].北京:科学出版社,2002.[4]徐志军,徐光辉.CP LDΠFPG A的开发与应用[M].北京:电子工业出版社,2002.[5]包明,赵明富,陈渝光.E DA技术与数字系统设计[M].北京:北京航空航天大学出版社,2002.[6]褚振勇,翁木云.FPG A设计及应用[M].西安:西安电子科技大学出版社,2002.[7]林明权.VH D L数字控制系统设计范例(第1版)[M].北京:电子工业出版社,2003.[8]侯伯亨,顾新.VH D L硬件描述语言与数字逻辑电路设计(第1版)[M].西安:西安电子科技大学出版社,1999.The Design of the AΠD Sampling Control Circuit B asing on the H igh Speed Simultaneous FPGAY ANG Shou-liang(Dept.of Physics and Information Engineering,Chongqing University of Arts and Science s,Y ongchuan Chongqing402160,China) Abstract:The author introduces a kind of designing method of the AΠD Sam pling C ontrol Circuit basing on the high speed simultaneous FPG A.The circuit can be joined well with all kinds of single-chip com puter systems, which can gather and trans form the data of AΠD at a speed and perform the data access after the conversion as well.T aking ADC0809as an exam ple in the article,the author explained the designing method of the AΠD Sam pling C ontrol circuit which includes FIFO mem orizer particularly.And the author als o presents the VH D L s ource program of the AΠD Sam pling C ontrol Circuit and the top level circuit schematic drawing of the entire sam pling mem orizer.K ey w ords:FPG A;ADC0809;controling circuit;Designing method45。

基于FPGA流水线结构并行FFT的设计与实现

基于FPGA流水线结构并行FFT的设计与实现王英喆;杜蓉【摘要】根据实时信号处理的需求,提出了一种基于FPGA的512点流水线结构快速傅里叶变换(FFT)的设计方案,采用4个蝶形单元并行处理,在Xilinx公司的Virtex7系列的FPGA上完成设计.处理器将基2算法与基4算法相结合,蝶形运算时把乘法器IP核的旋转因子输入端固定为常数,而中间结果用FIFO缓存.采用硬件描述语言verilog完成设计,并进行综合、布局布线,测试结果与MATLAB仿真结果相吻合.【期刊名称】《电子设计工程》【年(卷),期】2015(023)004【总页数】4页(P47-50)【关键词】FFT;FPGA;流水线;并行处理【作者】王英喆;杜蓉【作者单位】北京大学软件与微电子学院,北京100871;中科院国家空间中心北京100190【正文语种】中文【中图分类】TN402离散傅里叶变换DFT在通信、控制、信号处理、图像处理、生物信息学、计算物理、应用数学等领域中有着广泛的应用[1]。

FFT算法是作为DFT快速算法提出的,它将长序列的DFT分解为短序列的DFT,大大减少了运算量。

FFT的FPGA实现同时具有软件编程的灵活性和ASIC电路的快速性等优点,成为快速实时实现FFT的一种重要手段[2]。

文章意在设计一种高速率高吞吐率的FFT处理器,以满足实时处理要求。

1 数学模型FFT的基本思想是利用旋转因子的周期性、对称性和可约性将一个长度为N的序列的DFT逐次分解为较短的DFT来计算,而总的运算次数比直接DFT运算要少得多,达到提高速度的目的。

根据旋转因子的周期性、对称性和可约性,我们可以得到如式(1)的一系列有用结果[3-4]。

一般情况下,长度为N的有限长序列x(n)的DFT为:根据公式(1)(2)得到的基2与基4计算公式如下:2 结构说明2.1 流水线结构硬件结构实现FFT的常用形式有4种:递归结构,流水线结构,并行迭代结构和全并行结构[5]。

一种基于FPGA控制的多路并行数据采集设计方法

一种基于FPGA控制的多路并行数据采集设计方法马航;季振宇;史学涛;尤富生;付峰;刘锐岗;董秀珍【摘要】目的:为生物电阻抗成像设备设计出一个高精度、高速率,并能进行同步采集的多路信号采集模块.方法:通过在FPGA上定制一个Nios Ⅱ软核来作为系统的微控制器,然后通过对FPGA编程实现对多路A/D并行采集的时序控制,最后通过UART总线实现采集板与上位机之间的数据传输.结果:该系统成功地实现了对4路A/D转换器的并行控制,并实现了在100 Hz~100 kHz激励下对64路信号进行同步采集及初步的处理.结论:该设计方案达到了研究目的,能够满足EIS成像系统的数据采集需求.【期刊名称】《医疗卫生装备》【年(卷),期】2014(035)002【总页数】4页(P1-3,7)【关键词】FPGA;Nios Ⅱ软核;多路并行;数据采集【作者】马航;季振宇;史学涛;尤富生;付峰;刘锐岗;董秀珍【作者单位】710032 西安,第四军医大学生物医学工程学院;710032 西安,第四军医大学生物医学工程学院;710032 西安,第四军医大学生物医学工程学院;710032 西安,第四军医大学生物医学工程学院;710032 西安,第四军医大学生物医学工程学院;710032 西安,第四军医大学生物医学工程学院;710032 西安,第四军医大学生物医学工程学院【正文语种】中文【中图分类】R318;TP274.20 引言生物电阻抗成像是继形态、结构成像之后的新一代更为有效的无损伤功能成像技术,是医学成像技术的一个新方向[1-2]。

其中,多路信号采集是生物电阻抗成像技术的关键环节。

由成像原理可知,多路信号采集模块应该满足同步性、高精度和高速率的采集要求。

特别是在电阻抗扫描(electrical impedance scanning,EIS)中,要实现 64路(甚至更多路)信号的采集。

而且,采集信号的规模有逐渐增大的趋势,这就对多路信号采集模块的效率、性能提出了更高的要求。

基于FPGA高速并行采样技术的研究

2011年3月1日第34卷第5期现代电子技术Modern Electronics TechniqueMar.2011Vol.34No.5基于FPGA 高速并行采样技术的研究洪 萌,耿相铭(上海交通大学电子工程系,上海 200240)摘 要:介绍一种基于四通道ADC 的高速交错采样设计方法以及在FP GA 平台上的实现。

着重阐述四通道高速采样时钟的设计与实现、高速数据的同步接收以及采样数据的校正算法。

实验及仿真结果表明,同步数据采集的结构设计和预处理算法,能良好抑制并行ADC 输出信号因相位偏移、时钟抖动等造成的失配误差。

关键词:交错采样;高速采样时钟;同步接收;信号处理中图分类号:TN911234 文献标识码:A 文章编号:10042373X (2011)0520180203R esearch of High 2speed Parallel Sampling T echnology B ased on FPG AHON G Meng ,GEN G Xiang 2ming(Shanghai Jiaotong University ,Shanghai 200240,China )Abstract :The design method of a high 2speed interleaved sampling system based on four 2channel analog 2to 2digital con 2verter (ADC )and its realization on Virtex 25FP GA platform of Xilinx are introduced.The design of four 2channel high 2speed sampling clock ,the synchronus receiving method of high 2speed data and correction algorithm of sampling data are emphasized.Simulation results indicate that the structural design of the synchronus data sampling system and the pre 2processing algorithm can suppress the mismatch error of parallel ADC output signal ,which is caused by phase deviation and clock jittering.K eywords :time 2interleaved sampling ;high 2speed sampling clock ;synchronous reception ;signal processing收稿日期:20102102210 引 言高速、超宽带信号采集技术在雷达、天文和气象等领域应用广泛。