最新ARM体系结构与编程

ARM体系结构与编程试题

ARM体系结构与编程试题

一、简答题(20分)

(1)简述ARM的命名规则中后缀变量及其含义。

(2)用ARM汇编指令实现如下操作

a)R0=15

b)R0=R1/16

c)R1=R2*3

d)R0=-R0

(3)解读以下代码程序,并图示地址的走向。

LDMFDR13!,{R0,R4-R12,PC}

(4)试述用MDK软件的操作步骤。

二、编程题(60分)

(1)编写一段ARM汇编程序,实现数据块复制,将R0指向的8个字的连续数据块存到R1指向的一段连续的内存单元。

(2)下面是一段C语言程序,该程序实现了著名的Euclid最大公约数算法。

int gcd(int a,int b)

{while(a!=b)

{if(a>b)

a=a-b;

else

b=b-a;

}

return a;

}

用ARM汇编语言来重写这个例子。

(3)试编写程序,在C语言中调用汇编语言函数,用汇编语言函数实现字符串的复制。

ARM7跟ARM9的区别跟ARM体系结构新

ARM7与ARM9的区别及ARM体系结构一、 ARM7与ARM9的区别新一代的ARM9处理器,通过全新的设计,采用了更多的晶体管,能够达到两倍以上于ARM7处理器的处理能力。

这种处理能力的提高是通过增加时钟频率和减少指令执行周期实现的。

1 时钟频率的提高ARM7处理器采用3级流水线,而ARM9采用5级流水线。

增加的流水线设计提高了时钟频率和并行处理能力。

5级流水线能够将每一个指令处理分配到5个时钟周期内,在每一个时钟周期内同时有5个指令在执行。

在同样的加工工艺下,ARM9TDMI处理器的时钟频率是ARM7TDMI的1.8~2.2倍。

2 指令周期的改进指令周期的改进对于处理器性能的提高有很大的帮助。

性能提高的幅度依赖于代码执行时指令的重叠,这实际上是程序本身的问题。

对于采用最高级的语言,一般来说,性能的提高在30%左右。

2.1 loads 指令矛n stores指令指令周期数的改进最明显的是loads指令和stores指令。

从ARM7到ARM9这两条指令的执行时间减少了30%。

指令周期的减少是由于ARM7和ARM9两种处理器内的两个基本的微处理结构不同所造成的。

(1)ARM9有独立的指令和数据存储器接口,允许处理器同时进行取指和读写数据。

这叫作改进型哈佛结构。

而ARM7只有数据存储器接口,它同时用来取指令和数据访问。

(2)5级流水线引入了独立的存储器和写回流水线,分别用来访问存储器和将结果写回寄存器。

以上两点实现了一个周期完成loads指令和stores指令。

2.2 互锁(interlocks)技术当指令需要的数据因为以前的指令没有执行完而没有准备好就会产生管道互锁。

当管道互锁发生时,硬件会停止这个指令的执行,直到数据准备好为止。

虽然这种技术会增加代码执行时间,但是为初期的设计者提供了巨大的方便。

编译器以及汇编程序员可以通过重新设计代码的顺序或者其他方法来减少管道互锁的数量。

2.3 分枝指令ARM9和ARM7的分枝指令周期是相同的。

arm64体系结构编程与实践

arm64体系结构编程与实践以上Aarch64(ARM64)是由ARM Holdings开发的新一代处理器架构,在性能和功能上都有了很大的提升,在近年来流行的各种智能设备中都有应用,他的特点是强大的计算性能和可编程性,使得Aarch64加上操作系统,它成为当今EMBEDDED系统底层处理器,凭借着改良后的指令集和架构,Aarch64大大提高了处理和管理其他计算机设备、操作系统,环境变量,系统资源。

因此,在Aarch64体系结构下编程是一种新发展。

Aarch64体系结构编程在具体操作上比一般系统架构更加深刻,优势在于能够更有效的运用硬件资源,并减少执行成本。

首先,应该熟练掌握Aarch64的基础体系结构,它是基于ARMv8 (v8 ARM)运算架构,包含32套变种处理器类型,比如Cortex A,Cortex R和Cortex M,都有各自的特性和性能,不同的型号可以实现不同的功能。

其次,进行Aarch64编程需要对Linux操作系统有着深入的了解,Linux内核在Aarch64体系结构相关编程方面提供了很多有用的代码和函数,而Linux内核API也可以帮助开发人员了解其内部变量定义,以及如何将程序链接到其他文件的过程。

最后,开发人员应熟悉使用合适的开发工具,如嵌入式Linux SDK,利用其来管理和创建自定义的单元架构,从而编写出更加简洁易用,功能性更强的Aarch64体系结构程序。

Aarch64体系结构编程具有更大的发展潜力,它有着一系列具有惊人能力的新指令集和架构,使得Aarch64在EMBEDDED,计算机,手机和网络系统等设备取得了空前的受欢迎度。

借助现代高强度的计算机处理器,Aarch64可以实现更为复杂的任务,是今后的计算机程序员的首选,能够为人们带来更加高效率,高性能的设备。

ARM体系结构与编程

和嵌入式微处理器相比,微控制器的最大特点是单片化,体积大大减小 ,从而使功耗和成本下降、可靠性提高。微控制器是目前嵌入式系统工业的 主流。微控制器的片上外设资源一般比较丰富,适合于控制,因此称微控制 器。

嵌入式微控制器

嵌入式微控制器目前的品种和数量最多,比较有代表性的通用 系列包括8051、P51XA、MCS-251、MCS-96/196/296、 C166/167、MC68HC05/11/12/16、68300等。另外还有许多半通 用系列如:支持USB接口的MCU 8XC930/931、C540、C541; 支持I2C、CAN-Bus、LCD及众多专用MCU和兼容系列。目前

2021/2/5

ARM分类

基于指令集体系结构(构架ISA)的分类 ARM V1 体系是最初版本,只有26位的寻址空间,没有乘法指 令,最终没有商业化 ARM V2 体系与V1体系同为26位寻址空间,具有乘法和加法指 令,支持协处理器 ARM V3 体系的寻址范围扩展到32位,具有乘法和加法指令, 支持协处理器 ARM V4 体系增加了半字存储操作,对调试的支持以及支持嵌 入的ICE ARM V5 体系增加了DSP指令支持和对Java指令的支持 ARM V6 体系增加了媒体指令,ARMv6指令集合中加入了超过 60条SIMD单指令多数据指令 ARM V7 体系定义了三种独立的内核型--A(应用领域), R( 实时领域),M(控制领域)

4 ARM体系结构

21

ARM7与CORTEX比较

22

ARM编程模型

扩展协处 指令缓存 理器接口 器 指令存储 管理单元

ARM硬件架构

跟踪 接口

ARM9TDMI32 RISC处理器

AMBA 总线

写缓 冲

数据缓 存器 JTAG

数据存储 管理单元

回写存 储单元

23

ARM微处理器的工作状态

从编程角度看,ARM微处理器的工作状态一般有两种, 并可在两种状态之间切换: ARM状态,此时处理器执行32位的字对齐的ARM指令, 开始执行代码时处于ARM状态。 Thumb状态,此时处理器执行16位的、半字对齐的 Thumb指令。

ADR r0,ThumbProg+1

.THUMB

ThumbProg:

... ADR r0,ARMProg

BX

.ARM

r0

/*跳转到ARMProg,程序切换到ARM状态*/

/*指示编译器后面的为ARM指令*/

ARMProg: MOV r4, #4

27

ARM微处理器的工作模式(7种)

用户模式(User,usr):正常程序执行

15

ARM11微处理器系列

ARM11系列主要用于消费电子、无线和网络应用领 域,如STB、数码相机、3G移动电话、VoIP基础设 备、宽带调制解调器、WLAN介入设备和安全设备 等。

ARM11系列包含ARM1136J-S和ARM1136JF-S两种 类型。

16

SecurCore微处理器系列

SecurCore系列专为安全需要设计,除了具有ARM体 系结构各种主要特点外,在系统安全方面的特点: 带有灵活的保护单元,确保操作系统和应用数据的安全。

ARM体系结构与编程

ARM体系结构与编程

一、ARM体系结构

ARM(Advanced RISC Machine)是由英国ARM公司开发的一种低功耗、超低成本的处理器架构,是移动设备的首选处理器。

ARM架构的处理器有ARM7、ARM9、ARM11、 Cortex-A8 、Cortex-A15等,它们核心架构特点为以下几点:

1.保护模式。

ARM架构的处理器能够在用户模式和两个高级的保护模式之间来回切换。

2.对齐式存储。

ARM架构的处理器采用对齐方式,其二进制指令必须按照固定的位置排列,以便提高存储空间的利用率。

3.浮点处理单元。

ARM架构的处理器具有浮点数处理功能,使数值运算能够高效率地完成。

4.多级缓存。

ARM架构的处理器将原始数据复制到不同级别的快速缓存中,以便快速访问。

二、ARM程序的编程

1、ARM程序的编写

ARM程序的编写可以使用C语言编写,程序开发者需要掌握ARM架构各种中央处理器扩展指令集的使用方法,以便获得更好的效率。

2、编译ARM程序

ARM程序的编译是使用GNU的gcc编译器进行的,它可以将C语言编写的程序编译成ARM架构的机器码,并可以在ARM架构的处理器上运行。

3、调试ARM程序

ARM程序的调试使用GDB程序调试,它可以提供丰富的调试工具,可以跟踪程序执行的步骤,提供全面的程序反馈信息,可以帮助开发者快速定位程序运行出错的地方。

三、总结。

1、ARM体系结构

ARM全球合作伙伴(合作模型)

ARM产品应用领域

Samsung ML5100A Diamond Multimedia Rio 600 JVC "Pixstar" GC-X1 Alba Bush Internet TV

3Com 10/100 PCI NIC

Nintendo Gameboy Advance Lexmark Z52 Color Jetprinter HP Jornado 820

5TE

XScale ARM1020E

6

Thumb-2 SIMD Instructions Multi-processing

7

CoreSight

Improved ARM/Thumb ARM9E-S Interworking ARM966E-S CLZ Saturated arithmetic DSP multiplyaccumulate instructions Extensions: Jazelle (5TEJ)

• •

该例中,用6周期执行了4条指令 指令周期数 (CPI) = 1.5

分支流水线举例

Cycle 1 2 L 3 4 5 6 7 8 9

Address

0x8000 0x8004 0x8008 0x8FEC 0x8FF0 0x8FF4

Operation

BL 0x8FEC SUB ORR AND ORR EOR

Iomega HipZip

Sony MZ-R90 MiniDisc

Ericsson R38Share

Nokia Mediamaster

Psion Revo Plus

ARM体系结构的发展

4T

Halfword and signed halfword / byte support System mode Thumb instruction set ARM7TDMI ARM720T ARM9TDMI ARM940T ARM920T

物联网工程专业ARM体系架构与编程课程思政教学改革实践探索

物联网工程专业ARM体系架构与编程课程思政教学改革实践探索作者:杨树媛郭斌靳晟来源:《电脑知识与技术》2023年第28期摘要:ARM体系架构与编程是新疆农业大学计算机与信息工程学院物联网工程专业的专业拓展类课程,课程开设学期为大三上学期,在专业培养计划中,该课程起着承上启下的重要作用,挖掘该课程的思政元素,研究该课程的思政教学方法,是落实立德树人根本任务的重要途径。

文中从该课程的特点出发,说明对该课程进行思想教学改革的必要性,介绍该课程融入思政教育的教学目标、课程思政教学内容、方法及案例,提出了思政教学的改革思路,为高校物联网工程嵌入式类相关课程的课程思政教学改革提供一定的参考和借鉴。

关键词:课程思政;思政元素;思政教学;物联网工程中图分类号:G642 文献标识码:A文章编号:1009-3044(2023)28-0164-030 引言习近平总书记在全国高校思想政治工作会议上指出:“要用好课堂教学这个主渠道,思想政治理论课要坚持在改进中加强,提升思想政治教育亲和力和针对性,满足学生成长发展需求和期待,其他各门课都要守好一段渠、种好责任田,使各类课程与思想政治理论课同向同行,形成协同效应[1]。

”大学生的思政教育工作必须与专业课程同步进行,要找到一个合适的切入点,将思政教育贯穿于整个专业课程的教学全过程中,切实落实立德树人的根本任务。

专业课程的思政教学改革必须利用网络平台和课堂教学阵地,把握课程教学改革的核心环节,改革教学内容、教学目标、教学方法等教学环节,从而构建高效的课程思政教学体系[2-3]。

ARM体系架构与编程课程是国家一流本科专业——物联网工程专业的一门专业拓展类课程,具有较强的理论性和实践性,是基础课程的综合应用类课程,同时又是连接基础课程与相关嵌入式类专业课程的桥梁,在物联网专业中起到承上启下的作用,对于后续的实时操作系统课程、专业实习和毕业设计等的学习有着重要的作用。

课程以STM32F407系列开发板为例,主要讲授ARM嵌入式系统涉及的理论知识、STM32处理器的功能特点、工作原理、硬件资源、常用外设包括GPIO、中断、串口、定时器以及其他基本外设接口的程序设计方法、嵌入式系统设计方法等内容,为今后开展“智能感知与控制”相关科研训练、科技竞赛、产品研发等工作做好技术储备。

《ARM嵌入式系统结构与编程》习题答案

1章绪论1.国内嵌入式系统行业对“嵌入式系统”的定义是什么?如何理解?答:见教材1.1节。

2.嵌入式系统是从何时产生的,简述其发展历程。

答:见教材1.1节。

3.当前最常见的源码开放的嵌入式操作系统有哪些,请举出两例,并分析其特点。

答:见教材1.2.1节的嵌入式Linux和嵌入式实时操作内核UC /OS-I 。

4.举例说明嵌入式设备在工控设备中的应用。

答:见教材1.3节的“工业控制领域”。

5.未来嵌入式技术的发展趋势有哪些?答:见教材1.4节的嵌入式技术的发展趋势。

2章ARM技术与ARM体系结构1.简述ARM处理器内核调试结构原理。

答:对教材1.2节的图2-1进行描述。

2.分析ARM7TDMI-S各字母所代表的含义。

答:参考教材2.1.2 ARM核版本命名规则说明。

3.ARM处理器的工作模式有哪几种,其中哪些为特权模式,哪些为异常模式,并指出处理器在什么情况下进入相应的模式。

ARM处理器共有7种工作模式:用户模式:非特权模式,也就是正常程序执行的模式,大部分任务在这种模式下执行。

在用户模式下,如果没异常发生,不允许应用程序自行改变处理器的工作模式,如果有异常发生,处理器会自动切换工作模式FIQ模式:也称为快速中断模式,支持高速数据传输和通道处理,当一个高优(fast)中断产生时将会进入这种模式。

IRQ模式:也称为普通中断模式,:当一个低优先级中断产生时将会进入这种模式。

在这模式下按中断的处理器方式又分为向量中断和非向量中断两种。

通常的中断处理都在IRQ 模式下进行。

SVC模式:称之为管理模式,它是一种操作系统保护模式。

当复位或软中断指令执行时处理器将进入这种模式。

中止模式:当存取异常时将会进入这种模式,用来处理存储器故障、实现虚拟存储或存储保护。

未定义指令异常模式:当执行未定义指令时会进入这种模式,主要是用来处理未定义的指令陷阱,支持硬件协处理器的软件仿真,因为未定义指令多发生在对协处理器的操作上。

ARM7TDMI体系架构

ARM7TDMI-S(Rev 4) 技术参考手册- 1 -第1章介绍这一章介绍ARMTDMI-S处理器包含以下小节z 关于ARM7TDMI-S 处理器z ARM7TDMI-S结构z ARM7TDMI-S模块内核和功能框图z ARM7TDMI-S指令集汇总z Rev 3a和Rev 4之间的差异1.1 关于ARM7TDMI-S处理器ARM7TDMI-S处理器是ARM通用32位微处理器家族的成员之一ARM处理器具有优异的性能但功耗却很低使用门的数量也很少ARM结构是基于精简指令集计算机(RISC)原理而设计的指令集和相关的译码机制比复杂指令集计算机要简单得多这样的简化实现了z 高的指令吞吐量z 出色的实时中断响应z 小的高性价比的处理器宏单元1.1.1指令流水线ARM7TDMI-S处理器使用流水线来增加处理器指令流的速度这样可使几个操作同时进行并使处理和存储器系统连续操作流水线使用3个阶段因此指令分3个阶段执行z 取指z 译码z 执行3阶段流水线如图1-1所示ARM ThumbPC PC 指令从存储器中取出PC-4 PC-2 对指令使用的寄存器进行译码PC-8 PC-4 从寄存器组中读出寄存器执行移位和ALU操作寄存器写回到寄存器组图1-1 指令流水线注程序计数器(PC)指向被取指的指令而不是指向正在执行的指令在正常操作过程中在执行一条指令的同时对下一条指令进行译码并将第三条指令从存储器中取出1.1.2 存储器访问ARM7TDMI-S处理器使用了冯诺依曼Von Neumann结构指令和数据共用一条32位总线只有装载存储和交换指令可以对存储器中的数据进行访问数据可以是8位字节16位半字或者32位字字必须分配为占用4字节而半字必须分配为占用2字节1.1.3 存储器接口ARM7TDMI-S处理器的存储器接口可以使潜在的性能得到实现这样减少了存储器的使用对速度有严格要求的控制信号使用流水线这样使系统控制功能以标准的低功耗逻辑实现这些控制信号使许多片内和片外存储器技术所支持的快速突发访问模式得到充分利用ARM7TDMI-S处理器的存储器周期有4种基本类型z 内部周期z 非连续的周期z 连续的周期z 协处理器寄存器传输周期1.2 ARM7TDMI-S的结构ARM7TDMI-S处理器有两个指令集z 32位ARM指令集z 16位Thumb指令集ARM7TDMI-S处理器使用了ARM结构v4T关于ARM和Thumb指令集的详细信息请参阅ARM 体系结构参考手册1.2.1 指令压缩传统的微处理器结构对于指令和数据有相同的带宽因此和16位结构相比32位结构处理32位数据具有更高的性能并且在寻址更大的地址空间时要有效得多16位结构比32位结构具有更高的代码密度并且超过32位结构50%的性能Thumb在32位结构上实现了16位的指令集这样可提供z 比16位结构更高的性能z 比32位结构更高的代码密度1.2.2 Thumb指令集Thumb指令集是最通用的ARM指令的子集Thumb指令长度为16位每条指令都对应一条32位ARM 指令它对处理器模型有相同的效果Thumb指令使用标准的ARM寄存器配置进行操作这样ARM和Thumb状态之间具有极好的互用性在执行方面Thumb具有32位内核所有的优点z 32位地址空间z 32位寄存器z 32位移位器和算术逻辑单元(ALU)z 32位存储器传输Thumb因此提供了长的分支范围强大的算术操作和巨大的地址空间Thumb代码仅为ARM代码规模的65%但其性能却相当于连接到16位存储器系统的ARM处理器性能的160%因此Thumb使ARM7TDMI-S处理器非常适用于那些只有有限的存储器带宽并且代码密度很高的嵌入式应用16位Thumb和32位ARM指令集使设计者极大的灵活性使他们可以根据各自应用的需求在子程序一级上实现对性能或者代码规模的优化例如应用中的快速中断和DSP算法可使用完全的ARM指令集编写并使用Thumb代码连接1.3 ARM7TDMI-S 模块内核和功能框图ARM7TDMI-S 处理器结构内核和功能框图见下z ARM7TDMI-S 模块见图1-2 z ARM7TDMI-S 内核见图1-3z ARM7TDMI-S 功能框图见图1-4WDATA[31:RDATA[31:图1-2 ARM7TDMI-S 模块注数据总线上没有双向路径图1-2对这些作了简化C L KC L KE N C FG B IGEND nIRQ nF IQ nRE S E T AB O R T C P CPDBG DBG TRANS[1:0]PROT[1:0]S I ZE[1:0]WRITE LOCK WDAT A[31:0]RDAT A[31:0]ADDR [31:0]态寄存器地址增加器增加器总线筒形移位器指令管线读数据寄存器图1-3 ARM7TDMI-S 内核Embe de dICE-RT图1-4 ARM7TDMI-S功能框图1.4 ARM7TDMI-S指令集汇总该节提供了ARM和Thumb指令集的汇总z ARM指令汇总z Thumb指令汇总指令集详见ARM体系结构参考手册1.5 Rev 3a和Rev 4之间的差异ARM7TDMI-S(Rev 4)的变更见下面的章节z 增加的EmbeddedICE-RT逻辑z 改进的调试通信通道(DCC)带宽z 通过JTAG对DCC进行访问z TAP控制器ID寄存器z 更加有效的多路传输1.5.1 增加的EmbeddedICE-RT逻辑EmbeddedICE-RT对ARM7TDMI-S(Rev 3)当中的EmbeddedICE逻辑作了改进EmbeddedICE-RT可以使您在监控模式下执行调试在监控模式下内核在遇到断点或观察点时执行异常处理并不像在暂停模式中那样进入调试状态如果内核在遇到断点或观察点时不进入调试状态它仍然可以像正常情况下一样响应硬件中断请求如果内核构成了机械系统反馈环的一部分那么在监控模式下进行调试非常有用因为如果停止内核会导致系统运转中断更详细的信息请查阅第5章调试您的系统节电当DBGEN被拉低时大部分的EmbeddedICE-RT逻辑都被禁止以实现最低功耗程序员模式的改变程序员模式的改变如下调试控制寄存器增加了两个新的位Bit4 监控模式使能使用该位来控制器件对断点或观察点的反应z 置位时内核执行指令或数据的异常中止z 当清零时内核进入调试状态Bit5 EmbeddedICE-RT禁止在更改观察点和断点时使用该位z 置位时该位禁止断点和观察点断点或观察点寄存器可以编程为新的值z 清零时新的断点或观察点值生效协处理器寄存器映射协处理器寄存器映射中的一个新的寄存器R2指示处理器是因为一个真实的中止还是因为断点或观察点而进入预取指或数据异常中止更详细的信息请参阅第5章的中止状态寄存器1.5.2 改进的调试通信通道(DCC)带宽在ARM7TDMI-S处理器(Rev 3)中读取DCC数据需要对扫描链2进行两次访问第一次访问状态位第二次访问数据本身为了改进DCC带宽在ARM7TDMI-S处理器(Rev 4)中读取数据和状态位只需要一次访问状态位包含在扫描链所读取的地址区域的最低位当中DCC控制寄存器中的状态位保持不变以确保向下兼容性更多信息参考第5章的调试通信通道一节1.5.3 通过JTAG访问DCCDCC控制寄存器可通过ARM7TDMI-S处理器(Rev 4)中的JTAG接口进行控制处理器写操作清零bit0数据读控制位更多信息请参考第5章的调试通信通道一节1.5.4 TAP控制器ID寄存器TAP控制器ID寄存器值为0x7F1F0F0F更多信息请参考第5章的ARM7TDMI-S器件标识(ID)代码寄存器一节第2章编程模型这一章讲述ARM7TDMI-S处理器的编程模型包含以下小节z 关于编程模型z 处理器操作状态z 存储器格式z 指令长度z 数据类型z 操作模式z 寄存器z 程序状态寄存器z 异常z 状态延迟z 复位2.1 关于编程模型ARM7TDMI-S处理器内核使用ARM v4T结构实现该结构包含32位ARM指令集和16位Thumb指令集在ARM体系结构参考手册中详细讲述了编程模型2.2 处理器操作状态ARM7TDMI-S处理器有两种操作状态ARM状态32位这种状态下执行的是字方式的ARM指令Thumb状态 16位半字方式的Thumb指令在Thumb状态中程序计数器PC使用bit1来选择切换半字注ARM和Thumb状态间的切换并不影响处理器模式或寄存器内容2.2.1 状态切换您可以使用BX指令将ARM7TDMI-S内核的操作状态在ARM状态和Thumb状态之间进行切换详见ARM体系结构参考手册所有的异常处理都在ARM状态中执行如果异常发生在Thumb状态中处理器会返回ARM状态在异常处理返回时自动切换回Thumb状态2.3 存储器格式ARM7TDMI-S处理器将存储器看作是一个从0开始的线性递增的字节集合z 字节0到3保存第1个存储的字z 字节4到7保存第2个存储的字z 字节8到11保存第3个存储的字ARM7TDMI-S处理器可以将存储器中的字以下列格式存储z 大端Big-endian格式z 小端Little-endian格式2.3.1 大端格式在大端格式中ARM7TDMI-S 处理器将最高位字节保存在最低地址字节最低位字节保存在最高地址字节因此存储器系统字节0连接到数据线3124843124231615870低地址字地址图2-1 字内字节的大端地址2.3.2 小端格式在小端格式中一个字当中最低地址的字节被看作是最低位字节最高地址字节被看作是最高位字节因此存储器系统字节0连接到数据线70如图2-2所示843124231615870低地址字地址图2-2 字内字节的小端地址2.4 指令长度指令长度为下面两种之一z 32位长度在ARM状态中z 16位长度在Thumb状态中2.5 数据类型ARM7TDMI-S处理器支持下列数据类型z 字32位z 半字16位z 字节8位您必须这样进行分配z 字量必须分配为占用4个字节z 半字量必须分配为占用2个字节z 字节量可放置在任何一个字节内2.6 操作模式ARM7TDMI-S处理器具有7种操作模式z 用户模式这是ARM程序通常执行的状态用于执行大多数应用程序z 快速中断FIQ模式支持数据传输或通道处理z 中断IRQ模式用于通用中断处理z 超级用户模式是操作系统一种受保护的模式z 中止模式在数据或指令预取指中止时进入该模式z 系统模式是操作系统一种特许的用户模式z 未定义模式当执行未定义的指令时进入该模式除了用户模式之外其它模式都被归为特权模式特权模式用于服务中断异常或者访问受保护的资源2.7 寄存器ARM7TDMI-S处理器总共有37个寄存器z 31个通用32位寄存器z 6个状态寄存器这些寄存器并不是在同一时间全都可以被访问的处理器状态和操作模式决定了程序员可以访问哪些寄存器2.7.1 ARM状态寄存器集在ARM状态中16个通用寄存器和1个或2个状态寄存器可在任何时候同时被访问在特权模式中与模式相关的分组寄存器可以被访问图2-3所示为每种模式所能访问的寄存器ARM状态寄存器集包含16个可直接访问的寄存器r0r15一个附加的寄存器当前程序状态寄存器CPSR包含条件代码标志和当前模式位寄存器r0r13为保存数据或地址值的通用寄存器寄存器r14和r15具有下面的特殊功能连接寄存器寄存器14作为一个子程序连接寄存器LR当执行连接分支BL指令时r14接收r15的备份在其它时候可将r14当成一个通用寄存器对应的分组寄存器r14_svc, r14_irq, r14_fiq, r14_abt和r14_und与之相似当发生中断和异常或者当中断或异常子程序中的BL指令执行时用于保存r15的返回值程序计数器寄存器15用于保存程序计数器PC在ARM状态中r15中的bits[1:0]为0bits[31:2]包含PC值在Thumb状态中bit[0]为0bits[31:1]包含PC值在特权模式中另外一个寄存器被保存的程序状态寄存器SPSP可以被访问它包含了条件代码标志和作为异常的结果所保存的模式位此异常导致进入当前模式关于程序状态寄存器的描述见后面的章节分组寄存器有一个模式标识符用于指示它们被映射到哪个用户模式寄存器这些模式标识符如表2-1所示表2-1 寄存器模式标识符模式模式标识符用户 usr快速中断 fiq中断 irq超级用户 svc中止 abt系统 sys未定义 undFIQ 模式有7个分组寄存器分别映射到r8r14r8_fiqr14_fiq在ARM 状态中大多数FIQ 处理程序都不必保存任何寄存器用户IRQ 超级用户中止和未定义模式各有2个分组寄存器分别映射到r13和r14每种模式允许有一个专用的堆栈指针和LR图2-3所示为ARM状态寄存器ARM r0r1r2r3r4r5r6r7r8r9r10r11r12r13r14r15(PC)=状态通用寄存器和程序计数器系统和用户超级用户快速中断中断ARM 状态程序寄存器分组寄存器图2-3 ARM 状态中的寄存器结构2.7.2 Thumb 状态寄存器集Thumb 状态寄存器集时ARM 状态集的子集程序员可直接访问z 8个通用寄存器r0r7z PC z 堆栈指针SPz 连接寄存器LRz CPSR每个特权模式都有分组的SPLR 和SPSR该寄存器集如图2-4所示r0r1r2r3r4r5r6r7SP LR PC=状态通用寄存器和程序计数器系统和用户Thumb 状态程序寄存器分组寄存器Thumb图2-4 Thumb 状态中的寄存器结构2.7.3 ARM 状态寄存器和Thumb 状态寄存器之间的关系Thumb 状态寄存器与ARM 状态寄存器有如下的关系z Thumb 状态r0r7与ARM 状态r0r7相同z Thumb 状态CPSR 和SPSR 与ARM 状态CPSR 和SPSR 相同 z Thumb 状态SP 映射到ARM 状态r13 z Thumb 状态LR 映射到ARM 状态r14 z Thumb 状态PC 映射到ARM 状态PC(r15) 这些关系如图2-5所示图2-5 Thumb 寄存器在ARM 状态寄存器上的映射注寄存器r0r7为低寄存器寄存器r8r15为高寄存器2.7.4 在Thumb 状态中访问高寄存器在Thumb 状态中高寄存器r8r15不是标准寄存器集的一部分汇编语言程序员对它们的访问受到限制但可以将它们用于快速暂存可以使用MOV 指令的特殊变量将一个值从低寄存器r0r7转移到高寄存器或者从高寄存器到低寄存器CMP 指令可用于比较高寄存器和低寄存器的值ADD 指令可用于将高寄存器的值与低寄存器的值相加详细信息请参考ARM体系结构参考手册2.8 程序状态寄存器ARM7TDMI-S 内核包含1个CPSR 和5个SPSR 供异常处理程序使用程序状态寄存器z 保持条件代码标志 z 控制中断的使能和禁止 z 设置处理器操作模式 位的分配如图2-6所示图2-6 程序状态寄存器格式注为了保持与将来的ARM 处理器兼容并且作为一种良好的习惯在更改CPSR 时我们强烈建议您使用读写修改的方法2.8.1 条件代码标志N, Z, C 和V 位都是条件代码标志可以通过算术和逻辑操作来设置这些位这些标志还可通过MSR和LDM 指令进行设置ARM7TDMI-S 处理器对这些位进行测试以决定是否执行一条指令在ARM 状态中所有指令都可按条件来执行在Thumb 状态中只有分支指令可条件执行更详细的信息请参考ARM 体系结构参考手册2.8.2 控制位PSR 的最低8位为控制位它们分别是z 中断禁止位 z T 位 z 模式位 当发生异常时控制位改变当处理器在一个特权模式下操作时可用软件操作这些位中断禁止位I 和F 位都是中断禁止位z 当I 位置位时IRQ 中断被禁止 z 当F 位置位时FIQ 中断被禁止T位T位反映了正在操作的状态z 当T位置位时处理器正在Thumb状态下运行z 当T位清零时处理器正在ARM状态下运行操作状态通过CPTBIT外部信号反映警告绝对不要强制改变CPSR寄存器中的T位如果这样做处理器会进入一个无法预知的状态模式位M4, M3, M2, M1和M0位M[4:0]都是模式位这些位决定处理器的操作模式见表2-2不是所有模式位的组合都定义了有效的处理器模式因此请小心不要使用表中所没有列出的组合表2-2 PSR模式位值M[4:0] 模式可见的Thumb状态寄存器可见的ARM状态寄存器10000 用户r0~r7, SP, LR, PC, CPSR r0~r14,PC, CPSR10001 FIQ r0~r7,SP_fiq,LR_fiq,PC,CPSR, SPSR_fiq r0~r7,r8_fiq~r14_fiq,PC,CPSR, SPSR_fiq 10010 IRQ r0~r7,SP_irq,LR_irq,PC,CPSR,SPSR_fiqr0~r12,r13_irq,r14_irq,PC,CPSR,SPSR_irq10011 超级用户 r0~r7,SP_svc,LR_svc,PC,CPSR,SPSR_svc r0~r12,r13_svc,r14_svc,PC,CPSR, SPSR_svc10111 中止 r0~r7,SP_abt,LR_abt,PC,CPSR,SPSR_abtr0~r12,r13_abt,r14_abt,PC,CPSR,SPSR_abt11011 未定义 r0~r7,SP_und,LR_und,PC,CPSR,SPSR_und r0~r12,r13_und,r14_und,PC,CPSR, SPSR_und11111 系统 r0~r7,SP,LR,PC,CPSR注如果将非法值写入M[4:0]中处理器将进入一个无法恢复的模式2.8.3 保留位PSR中的保留位被保留将来使用当改变PSR标志和控制位时请确认没有改变这些保留位另外请确保您的程序不依赖于包含特定值的保留位因为将来的处理器可能会将这些位设置为1或者02.9 异常只要正常的程序流被暂时中止处理器就进入异常模式例如响应一个来自外设的中断在处理异常之前ARM7TDMI-S内核保存当前的处理器状态这样当处理程序结束时可以恢复执行原来的程序如果同时发生两个或更多异常那么将按照固定的顺序来处理异常见异常优先级一节该节将会详细讲述ARM7TDMI-S处理器的异常处理z 异常入口/出口汇总z 进入异常z 退出异常2.9.1 异常入口/出口汇总表2-3所示为异常入口处变量r14所保存的PC值以及退出异常处理程序所推荐使用的指令表2-3 异常入口/出口异常或入口 返回指令 之前的状态ARM r14_x Thumb r14_x 备注BL MOV PC,R14 PC+4PC+2 SWIMOVS PC,R14_svcPC+4 PC+2 未定义的指令 MOVS PC,R14_undPC+4PC+2 预取指中止 SUBS PC,R14_abt,#4 PC+4 PC+4 此处PC 为BL, SWI, 未定义的指令取指或者预取中止指令的地址FIQ SUBS PC,R14_fiq,#4 PC+4PC+4 IRQSUBS PC,R14_irq,#4 PC+4 PC+4 此处PC 为由于FIQ 或IRQ 占先而没有被执行的指令的地址数据中止SUBS PC,R14_abt,#4 PC+8PC+8此处PC 为产生数据中止的装载或保存指令的地址复位无复位时保存在r14_svc 中的值不可预知2.9.2 进入异常当处理异常时ARM7TDMI-S 内核会1.在适当的LR 中保存下一条指令的地址当异常入口来自ARM 状态ARM7TDMI-S 将下一条指令的地址复制到LR 中当前PC+4或PC+8取决于异常的类型Thumb状态ARM7TDMI-S 将PC 加偏移值PC+4或PC+8取决于异常的类型写入LR当进入异常时异常处理程序不必确定状态例如在SWI 情况下MOVS PC,r14_svc 总是返回到下一条指令而不管SWI 是在ARM 还是在Thumb 状态下执行2. 将CPSR 复制到适当的SPSR3. 根据异常将CPSR 模式强制设为某一值4. 强制PC 从相关的异常向量处对下一条指令取指ARM7TDMI-S 内核在中断异常时置位中断禁止标志这样可防止不受控制的异常嵌套注异常总是在ARM 状态中进行处理当处理器处于Thumb 状态时发生了异常在异常向量地址装入PC 时会自动切换到ARM 状态2.9.3 退出异常当异常结束时异常处理程序必须1. 将LR 中的值减去偏移量后移入PC 偏移量根据异常的类型而有所不同见表2-32. 将SPSR 的值复制回CPSR3. 清零在入口置位的中断禁止标志注恢复CPSR 的动作会将T, F 和I 位自动恢复为异常发生前的值2.9.4 快速中断请求快速中断请求(FIQ)异常支持数据转移或通道处理在ARM 状态中FIQ 模式有8个专用的寄存器可用来满足寄存器保护的需要这是上下文切换的最小开销将nFIQ 信号拉低可实现外部产生FIQ不管异常入口是来自ARM 状态还是Thumb 状态FIQ 处理程序都会通过执行下面的指令从中断返回 SUBS PC,R14_fiq,#4在一个特权模式中可通过置位CPSR 中的F 标志来禁止FIQ 异常当F 标志清零时ARM7TDMI-S 在每条指令结束时检测FIQ 同步器输出端的低电平2.9.5 中断请求中断请求IRQ异常是一个由nIRQ输入端的低电平所产生的正常中断IRQ的优先级低于FIQ对于FIQ序列它是被屏蔽的任何时候在一个特权模式下都可通过置位CPSR中的I 位来禁止IRQ,不管异常入口是来自ARM状态还是Thumb状态IRQ处理程序都会通过执行下面的指令从中断返回SUBS PC,R14_irq,#42.9.6 中止中止表示当前存储器访问不能被完成这是通过外部ABORT输入指示的不管异常入口是来自ARM 状态还是Thumb状态FIQ处理程序都会通过执行下面的指令从中断返回SUBS PC,R14_fiq,#4在存储器访问周期结束时检测中止异常有两种类型的中止z 预取指中止发生在指令预取指过程中z 数据中止发生在对数据访问时预取指中止当发生预取指中止时ARM7TDMI-S内核将预取的指令标记为无效但在指令到达流水线的执行阶段时才进入异常如果指令在流水线中因为发生分支而没有被执行中止将不会发生在处理中止的原因之后不管处于哪种处理器操作状态处理程序都会执行下面的指令SUBS PC,R14_abt,#4这个动作恢复了PC和CPSR并重试被中止的指令数据中止当发生数据中止时根据指令的类型产生不同的动作z 数据转移指令LDR,STR回写到被修改的基址寄存器中止处理程序必须注意这一点z 交还指令SWP中止好像没有被执行过一样中止必须发生在SWP指令进行读访问时z 块数据转移指令LDM,STM完成当回写被设置时基址寄存器被更新在指示出现中止后ARM7TDMI-S内核防止所有寄存器被覆盖这意味着ARM7TDMI-S内核总是会保护被中止的LDM指令中的r15总是最后一个被转移的寄存器中止的机制使指令分页的虚拟存储器系统能够被实现在这样一个系统中处理器允许产生仲裁地址当某一地址的数据无法访问时存储器管理单元MMU通知产生了中止中止处理程序必须找出中止的原因使请求的数据可以被访问并重新执行被中止的指令应用程序不必知道可用存储器的数量也不必知道它的被中止时所处的状态在修复产生中止的原因后不管处于哪种处理器操作状态处理程序都必须执行下面的返回指令SUBS PC,R14_abt,#8这个动作恢复了PC和CPSR并重试被中止的指令2.9.7 软件中断指令软件中断(SWI)用于进入超级用户模式通常用于请求一个特定的超级用户函数SWI处理程序通过执行下面的指令返回MOVS PC,R14_svc这个动作恢复了PC和CPSR并返回到SWI之后的指令SWI处理程序读取操作码以提取SWI函数编号2.9.8 未定义的指令当ARM7TDMI-S处理器遇到一条系统内任何协处理器都无法处理的指令时ARM7TDMI-S内核执行未定义指令陷阱软件可使用这一机制通过仿真未定义的协处理器指令来扩展ARM指令集注ARM7TDMI-S处理器完全遵循ARM结构v4T可以捕获所有分类未被定义的指令位格式在防止失败的指令后捕获处理器执行下面的指令MOVS PC,R14_und这个动作恢复了PC和CPSR并返回到未定义指令之后的指令关于未定义指令更详细的信息请参考ARM体系结构参考手册2.9.9 异常向量表2-4所示位异常向量地址在表中I和F表示先前的值表2-4 异常向量地址异常进入时的模式进入时I的状态进入时F的状态0x00000000 复位超级用户禁止禁止0x00000004 未定义指令未定义 I F 0x00000008 软件中断超级用户禁止 F 0x0000000C 中止预取指中止 I F 0x00000010 中止数据中止 I F 0x00000014 保留保留0x00000018 IRQ IRQ 禁止 F 0x0000001C FIQ FIQ 禁止禁止2.9.10 异常优先级当多个异常同时发生时一个固定的优先级系统决定它们被处理的顺序1. 复位最高优先级2. 数据中止3. FIQ4. IRQ5. 预取指中止6. 未定义指令7. SWI最低优先级有些异常不能一起发生z 未定义的指令和SWI异常互斥它们分别对应于当前指令的一个特定非重叠译码z 当FIQ使能并且在发生FIQ的同时产生了一个数据中止ARM7TDMI-S内核进入数据中止处理程序然后立即转到FIQ向量从FIQ的正常返回使数据中止处理程序恢复执行数据中止的优先级必须高于FIQ以确保数据转移错误不会被漏过必须将异常入口的时间增加到系统中最坏情况下FIQ的延迟时间2.10 中断延迟中断延迟被描述为z 最大中断延迟z 最小中断延迟2.10.1 最大中断延迟当FIQ使能时最坏情况下FIQ的延迟时间包含z Tsyncmax请求通过同步器的最长时间Tsyncmax为2个处理器周期z Tldm最长的指令执行需要的时间最长的指令是装载包括PC在内所有寄存器的LDM指令Tldm在零等待状态系统中的执行时间为20个周期z Texc数据中止入口的时间Texc为3个周期z Tfiq FIQ入口的时间Tfiq为2个周期因此总的延迟时间为27个周期在系统使用40MHz处理器时钟时略微小于0.7微妙在此时间结束后ARM7TDMI-S执行位于0x1c处的指令最大的IRQ延迟时间与之相似但必须考虑到这样一个事实即有更高优先级的FIQ可能会因为仲裁的时间而延迟IRQ处理程序的进入2.10.2 最小中断最小中断延迟延迟FIQ或IRQ的最小中断延迟是请求通过同步器的时间Tsyncmin加上Tfiq4个处理器周期2.11 复位当nRESET信号被拉低时ARM7TDMI-S处理器放弃正在执行的指令当nRESET信号再次变为高电平时nRESET处理器1. 强制M[4:0]变为b10011超级用户模式2. 置位CPSR中的I和F位3. 清零CPSR中的T位4. 强制PC从地址0x00开始对下一条指令进行取指5. 返回到ARM状态并恢复执行在复位后除PC和CPSR之外的所有寄存器的值都不确定。

ARM嵌入式系统结构与编程习题答案 清华大学出版社 最详细版

ARM嵌入式系统结构与编程习题答案清华大学出版社最详细版arm嵌入式系统结构与编程习题答案清华大学出版社最详细版一《arm嵌入式系统结构与编程》习题答案第一章为绪论1.国内嵌入式系统行业对“嵌入式系统”的定义是什么?如何理解?答:国内嵌入式行业普遍接受的定义是:以应用为中心,以计算机技术为基础,软硬件可定制,满足应用系统在功能、可靠性、成本、体积和功耗等方面的严格要求的专业计算机系统。

从这个定义可以看出,嵌入式系统与应用紧密结合,具有很强的特殊性。

它必须根据实际系统需求进行合理定制和使用。

因此,嵌入式系统是“为特定的人定制的”。

2.嵌入式系统是从何时产生的,简述其发展历程。

答:从20世纪70年代单片机的出现到目前各式各样的嵌入式微处理器,微控制器的大规模应用,嵌入式系统已经有了30多年的发展历史。

嵌入式系统的出现最初是基于单片机的。

英特尔于1971年开发了第一款4位总线结构的微处理器4004,可以说是嵌入式系统的雏形。

80年代初的8051是单片机历史上值得纪念的一页。

20世纪80年代初,出现了一种商业化的“实时操作系统内核”。

在实时内核下编写应用软件,可以加快新产品的开发速度,节约资金。

在20世纪90年代,实时内核发展为实时多任务操作系统。

进入21世纪以来,嵌入式系统得到了极大的发展。

在硬件方面,单片机的性能有了很大的提高,尤其是ARM技术的出现和改进,为嵌入式操作系统提供了强大的硬件载体,将嵌入式系统推向了一个新的阶段。

3.当前最常用的源码开放的嵌入式操作系统有哪些,请举出两例,并分析其特点。

答:主要有嵌入式linux和嵌入式实时操作内核uc/os-ii嵌入式Linux操作系统是一种针对嵌入式微控制器的特点而定制的Linux操作系统,包括通用的嵌入式通信协议和通用驱动程序,并支持多种文件系统。

它主要具有以下特点:开源、易移植、内核小、功能强大、运行稳定、效率高。

uc/os是源码工卡的实时嵌入式系统内核,主要有以下特点:源码公开,可移植性强,可固化,可剪裁,占先式,多任务,可确定性,提供系统服务等。

第三节ARM体系结构

一般的通用寄存器

寄存器类别 寄存器在汇编中的名称

用户

系统

R0(a1)

R1(a2)

R2(a3)其中R0~R7为

R3(a4)

未R分4(v1) 组的寄存器,也

通用寄存器 和程序计数

器

就R是5(v2) 说对于任何处理 R6(v3)

器R模7(v4) 式,这些寄存器 都对应于相同的32位 R8(v5)

管理 (svc) 操作系下统保访护问代码用户模系统式复位的和寄软件存中器断响就应比时进较入方此模式

中止 (abt) 未定义 (und)

用或于存支储便 可持器虚 保,以拟护而使内存且用和操这/ 作个在A系模RM统式7TD的访MI一问没有些一大用特 些处权 受任 控务 的 支软持件硬仿资件真协源处。理器的 未定义指令异常响应时进入此模式

各模式下实际访问的寄存器

用户

系统

管理

中止

未定义

RR00

在汇编语言中寄存

R1

器R0~R13为保存数据

R2

或地址值的通用寄存器。

R3

它们是完全通用的寄存器, R4

不会被体系结构作为特殊

R5

用途,并且可用于任何使

R6

用通用寄存器的指令。

R7

R8

R9

R10

R11

R12

R13

RR1133__ssvc

R13_abt

SSPPSSRR__fifqiq

ARM状态各模式下可以访问的寄存器

寄存器类别 寄存器在汇编中的名称

通用寄存器和 程序计数器

状态寄存器

R0 R1 R2 R3 R4 R5 R6 R7 R8 R9 R10 R11 R12 R13(SP) R14(LR) R15(PC) CPSR SPSR

《ARM嵌入式系统结构与编程》习题答案 邱铁编著

《ARM嵌入式系统结构与编程》邱铁编著. 清华大学出版社.年月第版 年月第二次印刷20093120108 《ARM嵌入式系统结构与编程》第1~4章思考与练习题答案 此答案仅供教师教学用 第1章绪论思考与练习题答案 1. 国内嵌入式系统行业对“嵌入式系统”的定义是什么 如何理解答 见教材1.1节。

2. 嵌入式系统是从何时产生的 简述其发展历程。

答 见教材1.1节。

3. 当前最常见的源码开放的嵌入式操作系统有哪些 请举出两例 并分析其特点。

答 见教材1.2.1节的嵌入式Linux和嵌入式实时操作内核μC /OS-II。

4. 举例说明嵌入式设备在工控设备中的应用。

答 见教材1.3节的“工业控制领域”。

5. 未来嵌入式技术的发展趋势有哪些 答 见教材1.4节的嵌入式技术的发展趋势。

第2章 ARM技术与ARM体系结构思考与练习题答案 1 简述ARM处理器内核调试结构原理。

答 对教材1.2节的图2-1进行描述。

2 分析ARM7TDMI-S各字母所代表的含义。

答 参考教材2 1 2 ARM核版本命名规则说明。

课后答案网《ARM嵌入式系统结构与编程》邱铁编著. 清华大学出版社. 年月第版 年月第二次印刷200931201083 ARM处理器的工作模式有哪几种 其中哪些为特权模式 哪些为异常模式并指出处理器在什么情况下进入相应的模式。

答 ARM处理器共有7种工作模式用户模式 非特权模式 也就是正常程序执行的模式 大部分任务在这种模式下执行。

在用户模式下 如果没异常发生 不允许应用程序自行改变处理器的工作模式 如果有异常发生 处理器会自动切换工作模式FIQ模式 也称为快速中断模式 支持高速数据传输和通道处理 当一个高优先级(fast)中断产生时将会进入这种模式。

IRQ模式 也称为普通中断模式 :当一个低优先级中断产生时将会进入这种模式。

在这模式下按中断的处理器方式又分为向量中断和非向量中断两种。

通常的中断处理都在IRQ模式下进行。

ARM7体系结构详细介绍

ARM7体系结构详细介绍简介ARM(Advanced RISC Machines)是一种32位的RISC(Reduced Instruction Set Computer)处理器架构,广泛应用于嵌入式系统、智能手机和平板电脑等领域。

ARM7是ARM体系结构中的一代经典产品,采用了精简指令集,具有低功耗、高效能和高性价比等特点。

架构特性处理器核心ARM7处理器核心是一个半导体芯片,包含了用于指令解码、执行、访存等任务的硬件单元。

ARM7采用了5级流水线架构,可以实现超过20万条指令每秒的处理性能。

此外,ARM7支持可选的乘法器、除法器和调试接口,以满足不同的应用需求。

寄存器ARM7提供了一组寄存器来存放指令和数据。

寄存器分为通用寄存器和特殊目的寄存器两种。

通用寄存器包括16个32位的寄存器,用于存储临时数据和计算结果。

特殊目的寄存器包括程序计数器(PC)、堆栈指针(SP)等,用于指导程序执行和管理堆栈。

存储器ARM7的存储器包括内部存储器和外部存储器两部分。

内部存储器分为指令存储器和数据存储器,用于存放程序指令和数据。

外部存储器通常是闪存、RAM等,用于扩展存储容量。

ARM7支持32位的地址总线,可以寻址最多4GB的内存空间。

性能与功耗ARM7采用了先进的CMOS工艺,使得它具有低功耗和高性能的特性。

ARM7的功耗通常在几个毫瓦到几十个毫瓦之间,可以满足嵌入式系统对功耗的严格要求。

同时,ARM7的高性能使得它可以处理复杂的计算任务,例如图像处理、音视频处理等。

调试与开发ARM7支持ARM公司定义的JTAG调试接口,可以通过调试器进行程序的单步调试、断点设置等操作。

此外,ARM7还提供了丰富的开发工具和软件支持,开发者可以使用C语言、汇编语言等进行编程,方便快捷地开发ARM7的应用程序。

应用领域由于ARM7具有低功耗、高效能和高性价比等特点,因此广泛应用于各种嵌入式系统和移动设备。

下面是一些主要的应用领域:嵌入式系统ARM7在嵌入式系统中得到了广泛的应用,例如工业控制、智能家居、汽车电子等领域。

ARM体系结构与程序设计知到章节答案智慧树2023年齐鲁师范学院

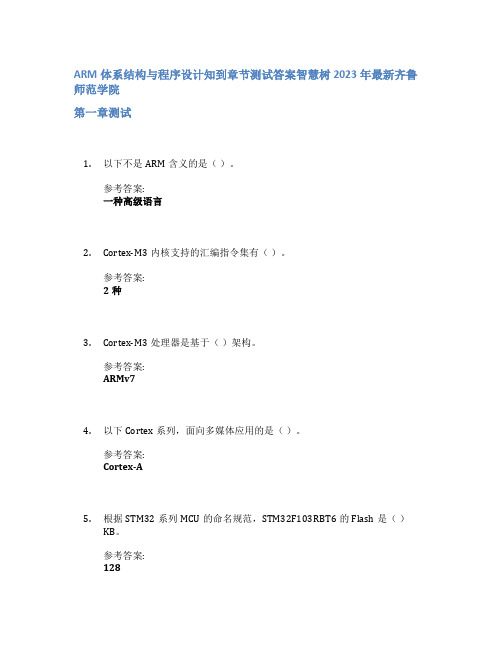

ARM体系结构与程序设计知到章节测试答案智慧树2023年最新齐鲁师范学院第一章测试1.以下不是ARM含义的是()。

参考答案:一种高级语言2.Cortex-M3内核支持的汇编指令集有()。

参考答案:2种3.Cortex-M3处理器是基于()架构。

参考答案:ARMv74.以下Cortex系列,面向多媒体应用的是()。

参考答案:Cortex-A5.根据STM32系列MCU的命名规范,STM32F103RBT6的Flash是()KB。

参考答案:1286.ARM公司本身不生产和销售半导体芯片,也不对外设计和许可。

()参考答案:错7.对于授权公司获得ARM授权的内核后,根据不同的应用领域,加入适当的外设,形成自己的ARM微处理器芯片。

()参考答案:对8.哈佛结构的数据和指令是分开编址的。

()参考答案:对9.对于内嵌有ARM处理器核心和采用ARM构架的处理器,被统称为____________。

参考答案:null10.对于STM32F107的最高主频是____MHz。

参考答案:null第二章测试1.关于CM3内核,下列说法正确的是()。

参考答案:CM3内核含有NVIC向量中断控制器2.CM3内核()GB的存储空间。

参考答案:43.CM3的堆栈方向为()生长。

参考答案:向下4.CM3中的数据总线和指令总线是()bit。

参考答案:325.流水线的三级流水不包括()。

参考答案:访存6.基于CM3内核的MCU大部分都使用的是大端模式。

()参考答案:错7.CM3有R0-R15寄存器组,其中R13为堆栈指针寄存器。

()参考答案:对8.CM3不支持32位的ARM指令集。

()参考答案:对9.STM32F107中,三条总线与其他外设相连,分别是____________、D-Code和系统总线。

参考答案:null10.APB2桥上挂接的设备是全速设备,最高可达____MHz。

参考答案:null第三章测试1.以下不是GPIO的配置模式的是()。

ARM体系结构

ARM体系结构

ARM作为一种微处理器体系结构,具有广泛应用范围、高性价比、低功耗等优势,在晶体管规模以及架构方面有着很大的节省,因而受到了越来越多应用者的青睐。

ARM体系结构包括处理器(Processor)、片外存储器(External Memory)、I/O接口(Input/Output Interface)、外围器件(Peripheral Devices)、软件支持(Software Support)等内容。

从处理器来说,ARM体系结构提供了一系列非常细分的机型,它们有不同的特性和操作速度,可以满足不同的性能需求,而且这些机型一般都有较高的可缩放性,所以在产品设计的过程中可以根据实际要求选择合适的特性和速度。

从片外存储器来说,ARM体系结构支持使用不同类型的存储器,比如SRAM、DRAM、Flash等,可以根据应用性能和耗电量的需求,来选择合适的存储器以满足不同应用场景的需求,而且存储器容量也比较可观,一般可以满足大部分应用场景的要求。

从I/O接口来说,ARM体系结构支持多种接口,如USB、I2C、SPI、UART等,通过这些接口可以与周边的外设进行连接,而这些接口的功耗和速度也比较低。

ARM体系结构与编程一arm开发板上运行第一个程序Hello World

今天是第一讲arm体系结构与编程一arm开发板上运行Hello World后续我们会讲解ARM指令,和中断机制,SDRAM原理等等后续会讲解linux驱动,让嵌入式更平民化欢迎加入我们深嵌这里以s3c2440为主,我们都知道2440内存有效的应用范围是地址SRAM的0-1000(16进制),还有就是30000000-34000000。

那么我们要运行一个程序的话就要选用一个内存来运行我们的程序,要想办法把程序放进去,我们一般放到sd 一般sram是用作一些初始化的。

在sdram中33000000以上的空间已被uboot所占用,我们只能用33000000以下的空间。

我们用C语言来写,最简单的莫过于hello world!我们就用这个例子来讲解,命令为test.c。

#include<stdio.h>int main(int argc,char **argv){printf("hello world!\n")return 0;}该程序在x86平台上编译时很简单的,gcc test.c -o test运行./test在X86上面是装着linux操作系统的,但是在我们一开始开发板没有装操作系统的话那怎么办呢?要是我们在arm开发板上运行怎么办?我们知道编译的过程是先把C语言编程汇编,再把汇编编程机器代码,但是ARM和X86不是同一个体系。

汇就是说运算的指令是不一样的!那么我们就不能用上面的来编译了!那么怎么办呢?我们只能用arm编译器,那么我们要安装交叉工具链,如何安装呢?下面就讲解交叉编译器的安装我们先下载arm-linux-gcc-3.4.1.tar.bz2(这个有不同版本,各取所爱)下载地址:/thread-36-1-1.html首先我们用tar jxf arm-linux-gcc-3.4.1.tar.bz2解压出来解压出来了就是我们的编译器,支持的汇编或者机器指令是arm的,为什么要叫arm-linux-gcc呢?意思是在arm平台上装一个Linux,写出来的程序就能再我们arm开发板上运行。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2020/10/14

9

ARM分类

基于指令集体系结构(构架ISA)的分类

ARM V1 体系是最初版本,只有26位的寻址空间,没有乘法指 令,最终没有商业化

ARM V2 体系与V1体系同为26位寻址空间,具有乘法和加法指 令,支持协处理器

ARM V3 体系的寻址范围扩展到32位,具有乘法和加法指令, 支持协处理器

采用上述的架构,形成一系列的处理器。有时候还要区分处理器核和处理器 系列。不过,在这里其实不用区分太细,毕竟这是功能的小部分的变化,核 心是相同的。

规则:ARM{x}{y}{z}{T}{D}{M}{I}{E}{J}{F}{-S}

·x -- 处理器系列 ·y -- 存储管理/保护单元

·z -- cache ·T -- 支持Thumb指令集 ·D -- 支持片上调试 ·M -- 支持快速乘法器 ·I -- 支持Embedded ICE,支持嵌入式跟踪调试 ·E -- 支持增强型DSP指令 ·J -- 支持Jazelle ·F -- 具备向量浮点单元VFP ·-S -- 可综合版本

V4 V4T V5TE V5TE V6

12

ARM体系的变种

1)Thumb指令集(T变种) Thumb指令集是把32位的ARM指令集的一个子集重新编码后而 形成的一个特殊的16位的指令集

2)长乘指令(M变种) 长乘指令是一种生成64位相乘结果的乘法指令(此指令为ARM指

令),

M变种增加了两条长乘指令 3)增强型DSP指令(E变种)

E变种的ARM体系增加了一些增强处理器对典型的DSP算法 处理能力的附加指令。 4)Java加速器Jazelle(J变种)

ARM的Jazelle技术是Java语言和先进的32位RISC芯片完美结 合的产物 。

5)ARM媒体功能扩展(SIMD变种)

2020/10/14

13

ARM的命名规则

ARM的命名分成两类: 基于ARM Architecture的版本命名规则; 基于ARM Architecture版本的处理器系列命名规则。

2020/10/14

10Leabharlann ARM系列处理器基于处理器内核的分类 ARM7 系列 ARM9 系列 ARM9E 系列 ARM10E 系列 SecurCore 系列 StrongARM/Xscale (Intel) ARM11

2020/10/14

11

ARM命名举例

核 ARM1 ARM2 ARM2aS,ARM3 ARM6,ARM600,ARM610 ARM7,ARM700,ARM710 ARM7TDMI,ARM710T,ARM720T ARM740T

ARM发展的历程

第一片ARM处理器是1983年10月到1985年4月间 在位于英国剑桥的Acorn Computer公司开发

1990年,为广泛推广ARM技术而成立了独立的公司 ꝴAdvance RISC Machine(ARM) 主要设计ARM系列RISC处理器内核 授权ARM内核给生产和销售半导体的合作伙伴

ARM体系结构与编程

第一章 ARM概述和分类

内容

ARM简介 ARM的分类 ARM的命名规则 基于ARM的嵌入式系统概述

2020/10/14

3

ARM介绍

什么是ARM ?

其实,人人都用ARM!

2020/10/14

4

什么是ARM

ARM是一个公司的名字 ARM代表一项技术,即Advanced RISC Machine ARM是一个内核,而不是我们看到的具体的芯片

·T -- Thumb指令集 ·M -- 长乘法指令 ·E -- 增强型DSP指令 ·J -- Java加速器Jazelle ·SIMD -- ARM媒体功能扩展

例如,ARMv5TxM表示ARM指令集版本为5,支持T变种, 不支持M变种

2020/10/14

15

基于ARM Architecture版本的处理器系列命名

ARM V4 体系增加了半字存储操作,对调试的支持以及支持嵌 入的ICE

ARM V5 体系增加了DSP指令支持和对Java指令的支持

ARM V6 体系增加了媒体指令,ARMv6指令集合中加入了超过 60条SIMD单指令多数据指令

ARM V7 体系定义了三种独立的内核型--A(应用领域), R( 实时领域),M(控制领域)

Strong ARM,ARM8,ARM810 ARM9TDMI,ARM920T,ARM940T ARM9E-S ARM10TDMI,ARM1020E ARM11,ARM1156T2-S,ARM1156T2F-S,ARM1176JZ-S, ARM201210J/Z10F/-1S4

体系结构 V1 V2 V2a V3 V3 V4T

举个例子,s3c2410采用ARMv4T架构版本,ARM920T处理 器系列,其中处理器核为ARM9TDMI。

2020/10/14

14

基于ARM Architecture的版本命名

规则: | ARMv | n | variants | x(variants) | 分成四个组成部分:

·ARMv -- 固定字符,即ARM Version ·n -- 指令集版本号。迄今为之,ARM架构版本发布了7个系列, 所以n=[1:7]。其中最新的版本是第7版 ·variants -- 变种。 ·x(variants) -- 排除x后指定的变种 常见的变种有:

ARM 公司不生产芯片 IP(Intelligence Property) 另外也提供基于ARM架构的开发设计技术 软件工具, 评估板, 调试工具,应用软件, 总线架构, 外围设备单元,等等 20世纪90年代, ARM快速进入世界市场 。

ARM Offices Worldwide

England Cambridge, Maidenhead, Sheffield, Blackburn Germany Munich France Paris, Sophia Antipolis Korea Seoul

US Seattle, Los Gatos, Walnut Creek, Austin, Boston, San Diego China Taiwan and Shanghai Japan Shin-Yokohama (Tokyo)

800+ 雇员 全球

ARM Partnership Model

ARM的应用