微机原理及应用第八章中断系统

中断系统工作原理及应用

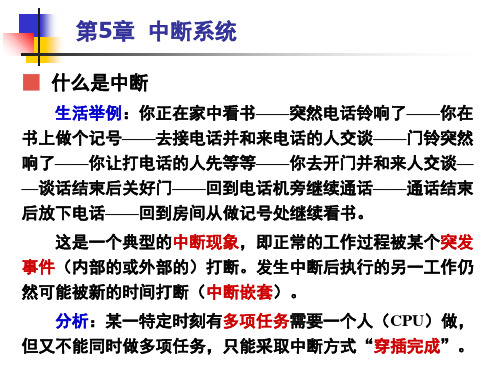

中断系统工作原理及应用中断是指在计算机运行过程中,发生某个特定事件时,系统会暂停当前任务,转而去处理这个事件,待事件处理完毕后再回到原来的任务上继续执行。

中断的工作原理是通过计算机的硬件和软件来实现的。

中断可以分为硬件中断和软件中断两种类型。

硬件中断是由外部设备发出的中断信号,例如键盘输入、鼠标移动等。

当这些设备发出中断信号时,CPU会暂停当前任务,保存当前执行上下文,并跳转到相应的中断处理程序去处理该事件。

中断处理程序负责处理特定的中断事件,处理完毕后会恢复之前的执行上下文,继续执行原来的任务。

软件中断是由程序内部生成的中断信号,例如系统调用、异常等。

中断的应用非常广泛,几乎所有的计算机系统都会使用中断来处理外部事件。

以下是一些中断的应用:1. 外部设备控制:计算机系统中的各种外部设备,例如键盘、鼠标、打印机等,都可以通过中断与计算机系统进行通信。

当外部设备有输入或输出需要处理时,会发出中断信号,从而通知计算机系统进行相应的操作。

2. 实时处理:中断可以用于实时处理系统中,当实时事件发生时可以立即进行处理。

例如在工业自动化控制系统中,可以利用中断来实时响应传感器的信号,实现对生产过程的实时监控和控制。

3. 操作系统:中断也是操作系统中的一个重要机制。

操作系统中有很多例程需要通过中断来实现,例如时钟中断、异常处理、系统调用等。

时钟中断可以用于实现多任务调度,让不同的任务轮流执行;异常处理可以处理非法操作或错误情况,保证系统的稳定性;系统调用可以实现用户程序与操作系统之间的交互。

4. 数据通信:中断可以用于实现计算机之间的数据通信。

例如网络数据传输中,当数据包到达时,计算机可以通过中断来通知操作系统进行相应的处理。

中断可以提高数据通信的效率和响应速度。

中断的工作原理主要包括以下几个步骤:1. 中断发生:当外部设备发生需要处理的事件时,会向CPU发送中断信号。

中断信号可以通过硬件触发中断,例如外部设备通过中断控制器发送中断请求。

微机原理CH8 微型计算机的中断系统(ok)

这一过程称为中断。

(2)特点

中断方式是一种常用的数据传送的控制方式

,利用中断可以避免不断检测外部设备状态,提 高CPU的效率。

3

第八章

2、中断源 引起程序中断的事件称为中断源。中断源有内部 中断和外部中断两种。内部中断由程序预先安排的指

令(INT n)引起,或CPU运算中产生某些错误引起;外

部中断是外部设备向CPU发出中断申请引起的。

13

第八章

2、CPU响应可屏蔽中断的过程 (1)CPU在每条指令的最后一个T周期,检测INTR,若

为高电平,且IF=1,则CPU响应中断。

(2)响应过程中自动依次完成以下工作:

① CPU向外设发两个/INTA ,外设收到第2个/INTA 后

,立即往数据线上给CPU送中断类型号。

② CPU从数据线上读取中断类型号; ③ 将PSW入栈;

8

第八章

2、内部中断(软件中断) 由三种情况引起: (1)由软中断指令INT n引起 INT n指令,类型号n(0-255)。

(2)由CPU运算错误引起

① 除法错中断:类型号0; ② 溢出中断:类型号4,由INTO指令引起的中断。

9

第八章

(3)由调试程序debug设置的中断

① 单步中断:

类型号1,TF=1时产生(当前指令需执行完), Debug状态下的T命令执行时产生;

绍可屏蔽中断的处理过程。

可屏蔽中断处理过程:

中断请求 中断响应 保护现场 转入执行中断服务子程序 恢复现场 中断返回

12

第八章

一、CPU响应可屏蔽中断过程

1、CPU响应可屏蔽中断的条件

(1)外设提出中断申请;

(2)本中断未被中断控制器屏蔽;

微型计算机系统原理与应用&中断大全

无论8086还是8088都会在执行指令的同时,从内存中取下面一条或几条指令放在指令队列中。

(2)执行部件EU

执行部件由ALU、寄存器阵列、标志寄存器等几个部分组成,其任务就是从指令队列流中取出指令,然后分析和执行指令,还负责计算操作数的16位偏移地址。

(3)BIU和EU的管理

标志寄存器FLAG有16位,用了其中的九位,分两组:状态标志和控制标志。前者用以记录状态信息,由6位组成,后者用以记录控制信息由3位组成。6位状态标志,包括CF、AF、OF、SF、PF和ZF,它反映前一次涉及ALU操作的结果,对用户它“只读不写”。控制标志包括方向标志DF,中断允许标志IF及陷阱标志TF,中断允许标志IF及陷阱标志TF,可通过指令设置。

第一章 微型计算机的基础知识

第二章 8086/8088微处理器及其体系结构

第三章 8086/8088指令系统

第四章 汇编语言及汇编程序设计

第五章 存储器

第六章 输入输出及DMA控制器

第七章 中断系统和中断控制器8259A

第八章பைடு நூலகம்接口技术

第九章 总线技术

第一章 微型计算机的基础知识

浮点数中小数点的位置是不固定的,用阶码和尾数来表示。通常尾数为纯小数,阶码为整数,尾数和阶码均为带符号数。尾数的符号表示数的正负;阶码的符号则表明小数点的实际位置。

定点表示法运算直观,但数的表示范围较小,不同的数运算时要考虑比例因子的选取,以防止溢出。浮点表示法运算时可以不考虑溢出,但浮点运算,编程较难。

8088中,由于数据总线8位,每个总线周期只能完成一个字节的操作,不存在上述问题,CPU也没有 ——BHE引脚。

3)复位引脚RESET

408《微机原理及应用》复习大纲

412《微机原理及应用》复习大纲课程名称微机原理及应用英文名称Micro Computer Principle and Application教学要求熟悉并掌握微型计算机系统的整体概念,理解硬软件间的辩证关系。

具体要掌握:CPU和基本接口的结构和工作原理;学会用汇编语言编程,重点放在如何根据具体要求来确定系统硬软件结构;合理选用存贮器和接口芯片;了解如何设计监控(管理)程序来统一管理系统硬软件资源的方法和技巧。

考试内容第一章:计算机中的数制和码制1数和数制数的位置表示法及各种进位制数;各种进位制数的换算方法;二进制数的运算方法2原码、补码、反码及其相应的运算法则原码;反码和补码;补码的求法;补码的运算;溢出判别;算术移位;移码3小数点问题定点法;浮点法4十进制数的二进制编码及ASCII码组合BCD码;非组合BCD码;ASCII码;奇偶校验码第二章;计算机基本软硬件知识与80486微处理器1计算机系统组成2存储器38086/8088微处理器内部结构*8086CPU内部结构、寄存器4工作模式简介:实地址模式和保护虚拟地址模式58086/8088的外部引脚介绍:数据总线、地址总线和控制总线第三章寻址方式及指令系统1寻址方式操作数寻址方式;程序转移地址的寻址方式2指令系统1)数据传送指令;累加器专用传送指令;地址传送指令;标志传送指令2)算术运算指令二进制加/减法指令;二进制乘/除法运算指令;符号位扩展指令;十进制(BCD)运算指令3)逻辑运算和移位指令逻辑运算指令;移位与循环移位指令4)串操作指令字符串操作指令;重复前缀指令5)控制转移类指令无条件与条件转移指令;循环转移指令;子程序调用与返回;中断和中断返回6)处理器控制类指令标志操作指令;外部同步指令;空操作指令3DEBUG命令简介第四章汇编语言程序设计1汇编语盲的基本概念计算机程序设计语言(机器语言、汇编语言、高级语言);汇编语言的语句格式(指令语句、伪指令语句);常数、标号、变量及表达式、伪指令2汇编程序的功能和汇编语言程序的运行汇编语言源程序的汇编、连接和装入运行;汇编过程;汇编语言与PC-DOS 的接口3汇编语言程序设计的基本方法汇编语言程序设计步骤;分支程序设计;循环程序设计;子程序设计;4宏汇编宏指令、宏定义和宏调用;宏嵌套;宏定义中的标号与变量;宏指令与子程序5多模块程序设计多模块的连接;模块间标识符的交叉访问6DOS功能调用7BIOS功能调用第五章半导体存贮器与存贮系统1概述存储器的分类;半导体存储器的结构与组成;`内存储器的性能指标2RAM、ROM典型芯片Intel 2114(1K×4)、HM6116(2K×8)、HM6264(8K×8);DRAM 2118(16K×1);UVEPROM 2764(8K×8);EEPROM Intel2864(8K×8)38086/8088CPU存储器的硬件组织地址/数据总线分离;地址空间组织4存储器的扩充5存储器扩充实例存储器扩充的步骤;存储器位的扩展;地址译码;存储器扩展举例第六章中断处理1概述中断的概念;中断处理过程;中断系统要解决的问题28086/8088的中断系统中断结构;内部中断;外部中断3中断优先级管理器 8259A PIC8259A内部结构与外部引脚;8259APIC编程;8259A在PC系统中的应用第七章输入/输出方法及常用的接口电路1概述时序配合;信号转换;数据缓冲;I/O电路代替CPU对外设的控制功能。

微机原理 第8章 中断控制器8259A 习题及参考

第八章中断控制器8259A1. 8259A的初始化命令字和操作命令字在设置上有什么不同?答:初始化命令字:是在计算机系统启动时,由初始化程序设置的,且一旦设定,一般在系统工作过程中就不再改变。

操作命令字:是由应用程序设定的,用来对中断处理过程作动态控制。

在系统运行过程中,可被多次设置。

2. 8259A中的中断屏蔽寄存器(IMR)与8086的中断允许标志(IF)有何差别?在中断响应过程中,它们是怎样配合工作的?答:差别有三:差别1——IMR中的某位为1时,说明对应此位的中断请求当前是受到屏蔽的;而IF位为0时,说明可屏蔽中断请求是受到屏蔽的。

差别2——IMR可以屏蔽部分中断请求;而IF为0时,屏蔽的是所有可屏蔽中断请求。

差别3——IMR是8259A中的一个8位寄存器;而IF是CPU中16位标志寄存器中的1位控制标志。

配合:只有当IMR中的某位为0且IF=1时,CPU才有可能响应对应此位的中断请求。

具体过程是:由中断请求寄存器(IRR)接收外部的中断请求并锁存中断请求,IMR中的对应位决定是否让这些请求通过。

如果IMR的对应位为1,则说明此中断当前受到屏蔽,即对它进行了封锁,而不让其进入优先级裁决器(PR);如果IMR的对应位为0,则PR把新进入的中断请求与当前服务寄存器(ISR)中指示的当前正在处理的中断作比较,若判断出新进入的中断请求具有足够高的优先级,则PR通过相应的逻辑电路使8259A的INT端为1,从而向CPU发出一个中断请求;如果此时CPU的IF=1,则CPU执行完当前指令后,就会响应该中断请求;否则,若IF=0,则CPU不予响应。

3. 8259A的全嵌套工作方式与特殊全嵌套工作方式有何不同?答:工作在全嵌套方式下,当处理某一级中断时,只有当优先级更高的中断请求到来,才会实施中断嵌套。

当同级中断请求到来时,不会给予响应;而工作在特殊全嵌套方式下,当处理某一级中断时,若有同级的中断请求到来,也会给予响应,从而实现对同级中断请求的特殊嵌套。

微机原理及单片机应用技术第8章 80C51的中断与定时计数器

定时/计数器的结构

T1引脚

TH1

TL1

TH0

T0引脚

TL0

机器周 期脉冲

TH1、TL1

内部总线

TH0、TL0

TF1 TR1 TF0 TR0 GATE C/T M1 M0 GATE C/T M1 M0

TCON

TMOD

TCON

外部中断相关位

T1方式

T0方式

TMOD

2020/10/27

21

计数脉冲源

定时/计数器的工作原理

76543210

TCON TF1 TR1 TF0 TR0

字节地址:88H

TFx:Tx溢出标志位。响应中断后TFx有硬件自动清0。 用软件设置TFx可产生同硬件置1或清0同样的效果。

TRx:Tx运行控制位。置1时开始工作;清0时停止工作。 TRx要由软件置1或清0(即启动与停止要由软件控制)。

2020/10/27

2020/10/27

24

定时/计数器的控制示意图

M1M0 工作方式

说

明

00 方式0 13位定时/计数器

01 方式1 16位定时/计数器

10 方式2 8位自动重装定时/计数器

11

方式3

T0分成两个独立的8位定时/计数器; T1此方式停止计数

注意:TMOD不能进行位寻址

2020/10/27

26

控制寄存器TCON

第八章 80C51的中断系统与定时计数器

8.1 80C51单片机的中断系统 8.2 80C51中断处理过程 8.3 80C51单片机的串行口

8.1 80C51单片机的中断系统

5.1.1 80C51中断系统的结构

中断的概念

与子程序调用相似 但有本质的区别

单片机原理及应用中断系统ppt课件

中断控制方式

■ 中断系统需解决的基本问题

◆ 中断源:

中断请求信号的来源。包括中断请求信号的产生及该信号 怎样被CPU有效地识别。而且要求中断请求信号产生一次,只 能被CPU接收和处理一次,即不能一次中断申请被CPU多次响 应。这就涉及到中断请求信号的及时撤除问题。

◆ 中断响应与返回:

CPU采集到中断请求信号后,怎样转向特定的中断服务子 程序及执行完中断服务子程序怎样返回被中断的程序继续正确 地执行。中断响应与返回的过程中涉及到CPU响应中断的条件、 现场保护等问题。

5.2

MCS-51单片机的中断系统

■ 51单片机中断源 ◆ 外部中断

特殊功能寄存器TCON的格式定义如下:

Байду номын сангаас

D7

D6

D5

D4

D3

D2

D1

D0

TCON

字节地址

IE1 IT1 IE0 IT0

88H

IT0(IT1):外部中断0(或1)触发方式控制位。 IT0(或IT1)被设置为“0”,则选择外部中断为电 平触发方式;IT0(或IT1)被设置为“1”,则选择 外部中断为跳变触发方式。

为了规范事业单位聘用关系,建立和 完善适 应社会 主义市 场经济 体制的 事业单 位工作 人员聘 用制度 ,保障 用人单 位和职 工的合 法权益

5.1

中断控制方式

■ 中断系统需解决的基本问题

◆ 中断嵌套:

当CPU响应某个中断请求而正在进行中断处理时,若有更 高优先级别的中断源发出中断申请,则CPU将自动中断正在执 行的中断服务程序,并保存该中断程序断点(类似于子程序嵌 套),转而去执行高级别中断的中断服务程序;当高级别中断 处理完毕后,再继续执行被中断的中断处理程序。这个过程被 称为中断嵌套。

第 8 章 中断——微机原理课件PPT

2. 设置中断屏蔽触发器

在实际系统中,往往有多个中断源。为了增加控制的 灵活性,在每一个外设的接口电路中,增加一个中断屏蔽 触发器,只有当此触发器为“1”时,外设的中断请求才能 被送出至CPU。可把8个外设的中断屏蔽触发器组成一个 端口,用输出指令来控制它们的状态。

3. 中断是开放的

在CPU内部有一个中断允许触发器。只有当其为“1” 时(即中断开放时),CPU才能响应中断;若其为“0”(即中 断是关闭的),即使INTR线上有中断请求,CPU也不响应。 而这个触发器的状态可由STI和CLI指令来改变。当CPU复 位时,中断允许触发器为“0”,即关中断,所以必须要用 STI指令来开中断。当中断响应后,CPU就自动关中断, 所以必须在中断服务程序中用STI指令来开中断。

在中断服务程序的最后,要开中断(以便CPU能响应新 的中断请求)和安排一条返回指令,将堆栈内保存的IP和 CS值弹出,运行就恢复到主程序。

8.3 中断优先权

同时有多个中断源发出中断请求。

1、用软件确定中断优先权

优点: (1)程序决定优先权的次序; (2)不需要有判断与确定优先权的硬件排 队电路。

缺点:由询问转至相应的服务程序入口的时间长,尤其是在中断源较多 的情况下。

8.1.2 中断源

引起中断的原因,或能发出中断申请的来源。

中断源有以下几种: (1) 一般的输入输出设备。如键盘、行打印

机等。 (2) 数据通道中断源。如磁盘、磁带等。 (3) 实时时钟。 (4) 故障源。 (5) 为调试程序而设置的中断源。

8.1.3 中断系统的功能

1. 实现中断及返回 2. 实现优先权排队 3. 高级中断源能中断低级的中断处理

单步 中断

INTR 8259A 中断

微机原理--第八章-中断系统

裁决器

0

IR6

0

IR7

选 CS 译 码

RD

WR

INTA INT

ICW1 芯片控制 A0

A0

1 × I3 I4 0 1 0 0 1 0 1 0 0 1

ICW2 中断类型号 1

ICW3 主从片连接关系

1 ICW4 方式控制

1

OCW1 中断屏蔽寄存器 IMR

00

0

SP/EN

CA0

OCW2 优先级设置、发EOI

上有中断申请,则将IRR相应位置1;

总线

D0 ~ D7 A0

A5 ~ A9

IOR IOW INTA INTR

数据线 D0 ~ D7

A0

ISR 0

当前 0

中断 服务

• 非屏蔽中断 – 由NMI引脚引起的中断,称非屏蔽中断。 – 当NMI引脚上产生上升沿信号,CPU必响应此中断请 求,即NMI引脚上的中断请求不受IF标志的控制, – IF不能屏蔽NMI引脚上的中断请求。

8086/8088CPU的中断分类图

中断源

外部中断 内部中断

非屏蔽中断 可屏蔽中断 内部硬件中断

SP/EN CA0 CA1 CA2

GND

+ 5V

电子钟时间基准

键盘 保留 串 口2 串 口1 硬盘 软盘 打印机

用于多片 8259A

级连情况

7.3.4 8259A的控制字

8259A中断控制器

处理部分

0

ISR 0

当前 0

中断 0

服务 0

寄存器

0 0

0

IRR

中断申请

0 0

寄存器 0

0

PR

0

优先级

微机原理及应用(第五版)

-2x109到2x109

长整数

Байду номын сангаас

64

-9x1018到9x1018

压缩BCD

80

-99…99到99..99(18位)

短实数

32

-3.39x10-38到3.39x1038

长实数

64

-1.19x10-308到1.19x10308

临时实数

80

-1.19x10-4932到1.19x104932

微机原理及应用

1.2.1 整型数 80387支持长整型数,而80386支持字节整型数.

微机原理及应用

2.1.3 输入/输出设备及其接口电路

输入设备:将程序、原始数据及现场信息以计算机能 识别的形式送到计算机中,供计算机自动计 算或处理。(键盘 鼠标 数字化仪 扫描仪 A/D等)

[-0]原=10000000 综上述

[X]原={

X 2n-1-X

X为正 X为负

微机原理及应用

2).补码和反码

举一实例:3点钟-7小时=8时

3点钟+5小时=8时

即:3-7=3+5

为什么?

答:时钟是以12为模,5是-7的补码.

在计算机中采用补码主要原因有二,一是 可以将减法变成加法来运算.二是补码的符号 位可以参加运算.

微机原理及应用

3).移码

针对补码不易比较大小的缺点而出现了移码

[X]移= 2n-1 -1+X 2n-1-1为偏移量

X>-2n-1 且X<=2n-1

例如:X=+10010B=+18,Y=-10010B=-18

[X]移= 26-1 -1+X=011111+010010=110001B [Y]移= 26-1 -1+Y=011111-010010=001101B

微机原理第八章:中断技术讲解

1.中断源识别

★ 软件查询法:

★ 中断矢量法:中断源提供中断类型号,CPU根据类型确定中断源 2.中断判优

★ 对同时产生的中断,首先处理优先级别较高的中断;

若优先级别相同,则按先来先服务的原则。

★ 对非同时产生的中断:

低优先级的中断程序允许被高优先级的中断源所中断

1.中断服务子程序的特点: 为“远过程”,用 IRET 指令返回

2.中断服务程序完成的工作

1)保护现场(通用寄存器的内容)

2)开中断(STI)

3)中断处理

4)关中断(CLI)

5)恢复现场 6)IRET

中断服务程序结构

保护有关寄存器内容 开中断

执行中断服务程序 关中断

恢复有关寄存器内容 执行IRET

精品资料

④ 执行 IRET 指令

4.退出中断(zhōngduàn) ① 关中断(zhōngduàn)

退

出

② 恢复现场中

③ 恢复断点 ④ 开中断(zhōngduàn) 断

精品资料

关中断 保存断点,保存现场

判别中断源 转入中断服务程序 保护寄存器、开中断 执行中断服务程序

IRET

关中断 恢复现场,恢复断点

开中断

STOSW

;串存储(字)

;AX→ES∶[DI]、 [DI+1]

MOV AX,SEG_INTR

;中断服务程序段基址送AX

STOSW

;串存储(字)

STI

;开中断

精品资料

2.用 MOV将直接(zhíjiē)中断向量写入中断向量表中

;将中断向量直接(zhíjiē)写入中断向量表中的程序段为

中断-微型计算机原理及应用.PPT

。

菊花链方式具有中断响应速度快的优点 ,缺点是 各中断源的优先级因硬件连接固定而不易修改 。

② 中断控制专用硬件方式

③ 图5 .4所示是一个典型的向量中断优先控制器原理框

④ ⑤ ⑥ ⑦ ⑧

2 、 中断的多级嵌套

CPU总是首先响应优先级最高的中断 请求 。当CPU正在执行优先级别较低的中 断服务程序时 , 允许响应优先级别高的中 断源的中断请求 , 中止起正在处理的中断 , 这就是中断嵌套和称多重中断 。此时 , CPU暂停正在执行着的级别较低的中断服 务程序 , 为优先级别高的中断源服务 , 待 优先权高的中断服务结束后 , 再返回到刚 才被中断的那一级 , 继续为它进行中断服 务 。直至处理结束返回主程序 , 如图5.5 所示。

软件中断是CPU处理某些内部事件时引起的中断 , 软件中断也叫内部中断。

5.2.2 中断向量和中断向量表

中断向量是中断服务程序的入口地址 ,每 一个中断服务程序都有一个唯一确定的入口地 址 , 即中断向量 。把系统中的全部中断向量集 中存放到存储器的某一 区域内 ,这个存放中断 向量的存储区就叫中断向量表 , 即中断服务程 序入口地址表。

图5.3所示是菊花链法的原线

接口1

接口2

接口3

菊花链 逻辑电

路

菊花链 逻辑电

路

菊花链 逻辑电

路

INTA INTR

_____

图5 3 菊花链优先级查询示意图

当外设通过接口和中断请求电路向CPU发出 中断申请号INTR , 并且满足中断响应条件时, CPU在执行完当前指令后便发出中断响应信号 , 该响应信号在所有中断源形成的链形结构中逐级 传送 ,位于链首的1#设备首先得到响应。

微机原理(中断概念)

必要性及应用 中断功能便于实现 1.分时操作

CPU和外设同时工作;CPU可以通过 分时操作启动多个外设同时工作,统一 管理。大大提高了CPU的利用率,也提 高了输入、输出的速度。

2.实时处理

3.故障处理

4.主机与外设之间的速度匹配

计算机在运行过程中,往往会出现事 先预料不到的情况,或出现一些故障: 如电源突跳,存储出错,运算溢出等等。 计算机就可以利用中断系统自行处理, 而不必停机或报告工作人员。

3. 8086从0030H开始读取4字节中断处理程 序的入口地址,前两字节装入IP,后两 字节装入CS,8086执行中断处理程序。

中断向量的装入

• 中断向量的装入方法:用MOV指令 • 假设中断类型号为60H,中断服务程序的偏移地

址是1234H,段地址5678H

• MOV AX,00H • MOV ES,AX; 0段 • MOV BX,60H*4; (=180H)中断向量指针 • MOV AX,1234; 中断服务程序偏移地址 • MOV ES:[BX],AX;装入偏移地址 • MOV AX,5678H; 中断服务程序段地址 • MOV ES:[BX+2],AX;装入段地址

8086中断时序

➢ 8086对外部硬件中断请求INTR的响应:

当INTR有一高电平,即有可屏蔽中断请求。 若此时IF=1且当前指令执行完,进入中断响 应周期,处理过程如下:

1. INTA*在两个总线周期中分别发出有效信号, 在第二个周期中8086读到中断类型码,然后 乘以4,得到中断向量。

2. 下一条指令地址CS和IP入栈,标志寄存器入 栈,清除IF和TF标志位。

中断嵌套

CPU正在执行 主程序

CPU正在执行 低级中断服务

微机原理及应用第八章中断系统

微机原理及应⽤第⼋章中断系统第⼋章: 中断系统输⼊, 输出设备是⼈机交换信息的必要外设., 中断控制⽅式是CPU经I/O接⼝与外设传送数据的最佳⽅式, CPU被动响应外设的中断请求, 提⾼CPU的⼯作效率§8.1 8086CPU的中断结构⼀: 8086CPU的中断源1: 内部中断源(软中断)由中断指令INT 获得的中断2: 外部中断源(硬中断)A: ⾮屏蔽中断源——8086CPU引脚NMI获得上升沿触发B: 可屏蔽中断源——8086CPU引脚INTR获得⾼电平触发⼆: 8086CPU中断优先级别1: 软中断2: 不可屏蔽中断NMI3: 可屏蔽中断INTR三: 8086CPU中断处理过程(311页图2.8)1: CPU获得中断请求2: CPU执⾏完当前指令3: CPU判断中断请求的优先级别4: 保护现场, F ,CS, IP ⼊栈5: CPU执⾏中断服务程序6: 恢复现场, IP, CS, F出栈7: CPU执⾏下⼀条指令重复1 ~ 7四: 中断向量表的设置将中断服务程序的⼊⼝地址置⼊中断向量表中1: 编程写⼊法A: 数据段定义法DATA SEGMENT A T 0000H ; 定义数据段(DS) = 0000HORG n * 4 ; n为中断类型号SUB DW noffset ; 中断服务程序的⼊⼝IPDW nseg ; 中断服务程序的⼊⼝CSDATA ENDSB: 指令传送法DATA SEGMENT A T 0000HORG n * 4SUB DW 2DUP(?)DATA ENDSCODE SEGMENTASSUME CS:CODE, DS:DA TAMOV AX, DATAMOV DS, AXMOV SUB, noffset ; 中断服务程序的⼊⼝IPMOV SUB + 2, nseg ; 中断服务程序的⼊⼝CS2: INT 21H功能设置法A: 置中断向量功能1): 功能号25H → AH2): 中断号n → AL3): ⼊⼝参数中断服务程的⼊⼝地址CS:IP → DS:DX4): INT 21H注: 中断服务程的⼊⼝地址CS:IP值将放⼊中断向量表的n * 4处连续4个存储单元中B: 读中断向量功能1): 功能号35H → AH2): 中断号n → AL3): INT 21H4): 出⼝参数ES:BX注: ES:BX中为中断号n的中断服务程的⼊⼝地址CS:IP值《例》某中断服务程序的中断号为40H,中断服务程序的⼊⼝地址CS:IP = 3500H:4830H,⽤INT 21H功置中断向量到中断向量表解:MOV AH, 25HMOV AL, 40HPUSH DS ; 下述指要⽤DS, 故暂时放⼊堆栈MOV AX, 3500HMOV DS, AX ; (DS) = (CS) = 3500HMOV DX, 4830H ; (DX) = (IP) = 4830HINT 21HPOP DS ; 恢复原DS值40H*4§8.2 外部中断⽅式⼀: PC/XT 的外部中断源314页图8.3⽰外部中断源⼆: INTR 中断源1: 8259A 与8个外部中断源A: 8253定时器, 键盘中断源直接到主机板B: 其余6个中断源经扩展槽到主机板2: 8259A 与8086CPU 的连接A: 8259A 获得外部中断请求B: 8259A 的INT = H 输出C: 8086CPU 的INTR = H, 获得中断请求输⼊3: 中断请求, 中断屏蔽, 中断响应A: 中断请求 —— 输⼊INTR ← HB: 中断屏蔽 —— 清中断屏蔽控制标志位IF = 0中断允许 —— 置中断屏蔽控制标志位IF = 1C: 中断⽆响应 —— 若IF = 0, 输出/INTA = H中断有响应 —— 若IF = 1, 输出/INTA = L4: INTR 的中断过程A: 8086CPU 引脚INTR ← HB: 程序判断中断控制标志IF 的值C: 若IF = 0, 8086CPU 引脚/INTA → H, ⽆中断响应D: 若IF = 1, 8086CPU 引脚/INTA → L, 有中断响应E: 程序判断多中断优先级F: 执⾏中断类型号08H ~ 0FH 中的⼀个中断服务程序注: 对可屏蔽中断, 当中断请求有效时,要获得中断响应的条件是置IF = 1三: NMI 中断源1: PC/XT 的NMI 外部中断源2: NMI 中断请求 NMI ←3: NMI⽆中断响应输出, NMI与标志位IF⽆关4: NMI的中断过程A: 8086CPU的引脚NMI ←B: 执⾏02H§8.3 中断优先级管理当外部中断源为多个时, 必须定义其优先级别并对其管理⼀: 软件查询法1: 硬件电路A: 多中断源输⼊B: 或门输出接8086CPU的INTR2: 功能A: 输⼊中断源有⼀个为⾼时输出为⾼B: 可屏蔽中断请求由多中断源提供3: 优先级流程法先判断那⼀个输⼊中断源, 则此中断源优先级最⾼⼆: 硬件菊花链法由数字逻辑电路构成优先级电路, 现⼰不常⽤三: 专⽤芯⽚法软件法, 硬件法的结合——可编程中断控制器§8.4 可编程中断控制芯⽚—— 8259A特点A: 可程序控制芯⽚的功能B: 可提供中断源的中断类型码C: 可屏蔽输⼊端的中断源形式A: 单⽚⽅式——有8个中断源B: 级联⽅式——最多64个中断源⼀: 8259A的结构及功能1: 8259A的内部逻辑结构A: 中断请求寄存器——IRR1): 可输⼊IR0 ~ IR8共8个外部中断源2): IRR寄存器中的值可经DB读⼊CPU注: IRR有⼝地址, 即可编程读B: 中断服务寄存器——ISR1): 为中断源IR0 ~ IR8服务, 为CPU服务若IRR请求, CPU响应, 则ISR中相对应位为1若中断服务程序结束, 则ISR中相对应位为0 2): ISR寄存器中的值可经DB读⼊CPU 注: ISR有⼝地址, 即可编程读C: 中断屏蔽寄存器——IMR1): IMR中IMR0 ~ IMR7与IRR中IR0 ~ IR7位对应若IMRn = 1, 则对应中断源IRn屏蔽若IMRn = 0, 则对应中断源IRn允许2): 寄存器IMR与中断标志IF的区别IMR屏蔽IRR, 当IMRn = 1时IF屏蔽CPU的中断请求INTR, 当IF = 0时IF的级别⽐IMR⾼3): IMR寄存器与CPU间可经DB读写操作注: IMR有⼝地址, 即可编程读写D: 优先权分析器——PR1): 对IRR中的IRR0 ~ IRR7中断源进⾏优先权分析2): IRR0 ~ IRR7的优先权分配可编程确定注: PR有⼝地址, 即可编程写E: 芯⽚控制逻辑1): 8259A的中断请求INT →8086CPU的INTR2): 8086CPU的/INTA →8259A的/INTAF: 芯⽚读写逻辑1): 8259A的⽚内地址线仅有A0(⼀线⼆址)注: 学习8259A的难点, 解决多寄存器读写与⼀线两址的⽭盾2): 8259A的⽚选线/CS由地址译码产⽣注: PC/XT微机中8259A的地址为20H, 21H3): 8259A的读写线/RD, /WR直接与8086CPU的/RD, /WR连接G: 芯⽚数据线8259A的数据线为8位即D0 ~ D7H: 芯⽚的级联线1): 当外部中断源≤8个时, 仅有单⽚8259A当外部中断源>8个时, 需⽤多⽚8259A级联2): 级联线仅在8259A级联⽅式下有作⽤注: 级联线CAS0 ~ CAS2, /EN即/SP接线⽅式2: 8259A的引脚图A: 8259A为DIP28封装B: 8259A为+5V供电⼆: 8259A的中断优先权中断源IR0 ~ IR7的优先权序可编程确定1: 固定优先权(完全嵌套⽅式)A: 优先权序IR0(⾼) →IR7(低)B: 该优先权序始终不变2: 等优先权(普通循环⽅式)A: 初始优先权序IR0(⾼) →IR7(低)B: 若响应了IRn中断, 则IRn中断权最低, IRn-1中断权最⾼C: 每个中断优先权相同3: 特殊优先权(特殊循环⽅式)A: 初始优先权序由编程确定若定义IR5为初始最⾼优先权,则初始优先权序IR5 → IR7 → IR0 → IR4B: 其后⼯作同等优先权三: 中断源IR0 ~ IR7的中断触发⽅式1: 电平触发⽅式—— IR0 ~ IR7输⼊⾼电平有效A: 现象——中断源持续⾼电平B: 问题——造成连续中断请求C: 解决——在中服程序中令IF = 02: 边沿触发⽅式—— IR0 ~ IR7输⼊上升沿有效A: 特点—— IRR寄存器锁存触发信号B: 脉宽——上升沿脉冲宽度符合要求C: ⽅法——采⽤负脉冲的后沿触发四: 8259A的初始化命令字和操作命令字若要使⽤8259A, 必须按规定向其写⼊初始化命令字使8259A进⼊⼯作状态(⼀般由系统程序完成)若要改变8259A的功能, 可随时向其写⼊操作命令字使8259A按要求⼯作(⼀般由⽤户程序完成) (⼀): 8259A⼝地址讨论1: 8259A实际⼝地址⼀线⼆址, 址1 — A = 0, 址2 — A = 12: 8259A操作⼝地址A: 4个写初始化命令字操作B: 3个写操作命令字操作C: 3个读寄存器IRR, ISR, IMR操作D: 1个读中断类型号操作注: 2个地址怎样完成11个读写操作3: 地址分配表及应⽤特点表8.2 8259A的读写操作A: A0 = 0时的读操作, IRR, ISR, 中断类型号→ CPU注: 解决1址3读问题, ⽤位控制定义读⼊法B: A0 = 1时的读操作, 仅IMR → CPUC: A0 = 0时的写操作, CPU → OCW2, OCW3, ICW1注: 解决1址3写问题, ⽤同址顺序写⼊法D: A0 = 1时的写操作, CPU → OCW1, ICW2, ICW3, ICW4注: 解决1址4写问题, ⽤位识别写⼊法(⼆): 初始化命令字ICW的写⼊⽅法1: ICW1 ~ ICW4的写⼊流程A: ICW1, ICW2为必写初始化命令字ICW3, ICW4为选写初始化命令字B: ICW2, ICW3, ICW4采⽤同址顺序写⼊法2: ICW1 ——芯⽚控制初始化命令字A: ⼝地址A0 = 0, PC/XT⼝地址= 20HB: 位定义1): D4 = 1 为同址识别位注: 若D4 = 1 CPU对ICW1命令字写操作若D4 = 0 CPU对0CW2, OCW3命令字写操作2): D0 = 0 不写ICW4命令字D0 = 1 要写ICW4命令字3): D1 = 0 多⽚8259A⽅式, 要写ICW3命令字D1 = 1 单⽚8259A⽅式, 不写ICW3命令字4): D3 = 0 IR0 ~ IR7为边沿触发⽅式D3 = 1 IR0 ~ IR7为电平触发⽅式5): D2, D5, D6, D7位不⽤(8086CPU时)3: ICW2 ——中断类型号初始化命令字A: ⼝地址A0 = 1, PC/XT⼝地址= 21HB: 位定义1): D2 ~ D0 IR0 ~ IR7的编码, 即中断类型号的低3位2): D7 ~ D3 中断类型号的⾼5位注: 中断类型号的⾼5位由⽤户编程定义,中断类型号的低3位⾃动产⽣, 保证IR0 ~ IR7连续《例》定义8259A的8个中断类型号为08H ~ 0FH 解: 08H = 00001000B, 0FH = 00001111B低3位为000B ~ 111B表⽰中断源IR0 ~ IR7的编码⾼5位为00001BMOV AL, 08HOUT 21H, AL4: ICW3 ——主/从8259A初始化命令字A: 写操作条件在ICW1中, D1 = 0B: ⼝地址A0 = 1, PC/XT⼝地址= 21HC: 写操作⽅法同址顺序写⼊法注: ICW2, ICW3, ICW4, OCW1均为同址( A0 = 1), 写顺序为写ICW2→写ICW3(若要)→写ICW4(若要)→写OCW1 D: 主8259A位定义1): 若D0 ~ D7 为1, 则IR0 ~ IR7对应端接有从8259A芯⽚2): 若D0 ~ D7 为0, 则IR0 ~ IR7对应端未接从8259A芯⽚E: 从8259A位定义1): D2 ~ D0 从8259A的INT端接主8259A的IRn端编码2): D7 ~ D3 未⽤5: ICW4 ——⽅式控制初始化命令字A: 写操作条件在ICW1中, D0 = 1B: ⼝地址A0 = 1, PC/XT⼝地址= 21HC: 写操作⽅法同址顺序写⼊法D: 位定义1): D0 = 0 ⽤于8080CPUD0 = 1 ⽤于8086CPU2): D1 = 0 普通, 特殊EIO结束⽅式D1 = 1 ⾃动EIO结束⽅式3): D3,D2 = 00, 01 级联⾮缓冲⽅式D3,D2 = 10, 11 级联缓冲⽅式4): D4 = 0 单⽚8259A固定优先权D4 = 1 级联8259A固定优先权5): D7 ~ D5 未⽤《例》PC/XT系统BIOS对8259A的初始化命令字写⼊程序MOV AL, 00010011B ; D0 = 1, 要写ICW4, D1 = 1, 不写ICW3 OUT 20H, AL ; 写ICW1, D3 = 0, IR0 ~ IR7为边沿触发⽅式MOV AL, 00001000B ; IR0 ~ IR7 对应中断类型号为08H ~ 0FH OUT 21H, AL ; 写ICW2MOV AL, 00001001B ;D0 = 1, 8086⽅式, D1 = 0, ⾮⾃动EIO OUT 21H, AL ; 写ICW4, ,D4 = 0, 固定优先权(三): 操作命令字OCW的写⼊⽅法注: ICW按顺序写⼊(先写), OCW按需要写⼊(后写)1: OCW1 ——写IMR寄存器命令字A: ⼝地址A0 = 1, PC/XT⼝地址= 21HB: 位定义1): D0 ~ D7对应寄存器IMR中的IMR0 ~ IMR72): Dn = 0 对应中断源IRn中断允许Dn = 1 对应中断源IRn中断屏蔽2: OCW2 ——中断优先权选择命令字注: ICW4可定义8259A⼯作于固定优先权, 8259A的等优先权, 特殊优先权在此定义A: ⼝地址A0 = 0, PC/XT⼝地址= 20HB: 识别位D4, D3 = 0, 0 (同址识别位法, 对OCW2, OCW3)C: 位定义1): D2 ~ D0 特殊优先权中断源IRn编码2): D6 = 0 ⾃动循环优先权D6 = 1 特殊循环优先权3): D7 = 0 固定优先权D7 = 1 循环优先权注: 仅当D6 = 1, D7 = 1时, D2 ~ D0值才有意义4): D5 = 0 ⾃动EIO结束⽅式D5 = 1 ⾮⾃动EIO结束⽅式3: OCW3 ——运⾏⽅式命令字A: ⼝地址A0 = 0, PC/XT⼝地址= 20HB: 识别位D4, D3 = 0, 1 (同址识别位法, 对OCW2, OCW3) C: 位定义1): D2 = 0 CPU下次同址读操作读⼊IRR, ISR中的值D2 = 1 CPU下次同址读操作读⼊中断类型号的值2): D1,D0 = 00, 01 ⽆意义D1,D0 = 10 CPU下次同址读操作读⼊IRR中的值D1,D0 = 11 CPU下次同址读操作读⼊ISR中的值3): D6, D5 级联⽅式下中断屏蔽的应⽤(约)4): D7 未⽤(四): 8259A的读操作⽅法1: 读IMR寄存器A: ⼝地址A0 = 1, PC/XT⼝地址= 21HB: 地址唯⼀, ⽆同址2: 读IRR寄存器A: ⼝地址A0 = 0, PC/XT⼝地址= 20HB: 条件先写OCW3中的D2,D1,D0 = 0103: 读ISR寄存器A: ⼝地址A0 = 0, PC/XT⼝地址= 20HB: 条件先写OCW3中的D2,D1,D0 = 0114: 读中断类型号A: ⼝地址A0 = 0, PC/XT⼝地址= 20HB: 条件先写OCW3中的D2 = 1C: 读⼊数据位定义1): D7 = 0 ⽆中断请求IR0 ~ IR7D7 = 1 有中断请求IR0 ~ IR72): D2 ~ D0 为IR0 ~ IR7编码(当D7 = 1时)3): D6 ~ D3 未⽤。

第八章 中断系统解析资料

类来自 CPU 的内部,由执行指令时引起,称为软件中断 ( 又称内 部中断)。

8.2.1 外部中断

1. 非屏蔽中断NMI(中断类型号为2) 整个系统只有一个非屏蔽中断,它不受IF标志位的屏蔽。 出现在NMI上的请求信号是上升沿触发的,一旦出现,CPU将 予以响应。非屏蔽中断一般用于紧急故障处理。

8位寄存器,记录当前正在被服务的所有中断级,包括尚

未服务完而中途被更高优先级打断的中断级。每位对应输入端 IR7~IR0中的一位。若某个引脚上的中断请求被响应,则ISR中

对应位被置1。ISR的置位也允许嵌套。

8.4.2 8259A的内部结构及外部引脚

8.4

可编程中断控制器 8259A

8259A具有如下功能:

① 以接收多个外部中断源的中断请求,并进行优先级别判 断,选中当前优先级别最高的中断请求,再将此请求送到微 处理器的中断输入端。 ② 具有提供中断向量、 屏蔽中断输入等功能。 ③ 可用于管理8级优先权中断,最多构成64级优先权中断管 理系统。中断服务程序入口地址构成的中断向量表存放在内 存固定区域。 ④ 有多种工作方式,自动提供中断服务程序 入口地址

通过命令在程序中任意指定断点地址,当CPU执行到断点时便

产生中断,同时显示当前各寄存器的内容和标志位的值以及下 一条要执行的指令,供用户检查在断点以前的程序运行是否正

常。

8.2.2 内部中断

(4)溢出中断INTO(类型号为04H) CPU进行带符号数的算术运算时,若发生了溢出,则标志位 OF=1,如果此时执行INTO指令,会产生溢出中断。若OF=0,则 INTO不产生中断,CPU继续执行下一条指令。INTO指令通常安排 在算术指令之后,以便在溢出时能及时处理。 (5)指令中断 CPU执行INT n指令后,会立即产生一个类型码为n的中断,

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第八章: 中断系统输入, 输出设备是人机交换信息的必要外设., 中断控制方式是CPU经I/O接口与外设传送数据的最佳方式, CPU被动响应外设的中断请求, 提高CPU的工作效率§8.1 8086CPU的中断结构一: 8086CPU的中断源1: 内部中断源(软中断)由中断指令INT 获得的中断2: 外部中断源(硬中断)A: 非屏蔽中断源——8086CPU引脚NMI获得上升沿触发B: 可屏蔽中断源——8086CPU引脚INTR获得高电平触发二: 8086CPU中断优先级别1: 软中断2: 不可屏蔽中断NMI3: 可屏蔽中断INTR三: 8086CPU中断处理过程(311页图2.8)1: CPU获得中断请求2: CPU执行完当前指令3: CPU判断中断请求的优先级别4: 保护现场, F ,CS, IP 入栈5: CPU执行中断服务程序6: 恢复现场, IP, CS, F出栈7: CPU执行下一条指令重复1 ~ 7四: 中断向量表的设置将中断服务程序的入口地址置入中断向量表中1: 编程写入法A: 数据段定义法DATA SEGMENT A T 0000H ; 定义数据段(DS) = 0000HORG n * 4 ; n为中断类型号SUB DW noffset ; 中断服务程序的入口IPDW nseg ; 中断服务程序的入口CSDATA ENDSB: 指令传送法DATA SEGMENT A T 0000HORG n * 4SUB DW 2DUP(?)DATA ENDSCODE SEGMENTASSUME CS:CODE, DS:DA TAMOV AX, DATAMOV DS, AXMOV SUB, noffset ; 中断服务程序的入口IPMOV SUB + 2, nseg ; 中断服务程序的入口CS2: INT 21H功能设置法A: 置中断向量功能1): 功能号25H → AH2): 中断号n → AL3): 入口参数中断服务程的入口地址CS:IP → DS:DX4): INT 21H注: 中断服务程的入口地址CS:IP值将放入中断向量表的n * 4处连续4个存储单元中B: 读中断向量功能1): 功能号35H → AH2): 中断号n → AL3): INT 21H4): 出口参数ES:BX注: ES:BX中为中断号n的中断服务程的入口地址CS:IP值《例》某中断服务程序的中断号为40H,中断服务程序的入口地址CS:IP = 3500H:4830H,用INT 21H功置中断向量到中断向量表解:MOV AH, 25HMOV AL, 40HPUSH DS ; 下述指要用DS, 故暂时放入堆栈MOV AX, 3500HMOV DS, AX ; (DS) = (CS) = 3500HMOV DX, 4830H ; (DX) = (IP) = 4830HINT 21HPOP DS ; 恢复原DS值40H*4§8.2 外部中断方式一: PC/XT 的外部中断源314页图8.3示外部中断源二: INTR 中断源1: 8259A 与8个外部中断源A: 8253定时器, 键盘中断源直接到主机板B: 其余6个中断源经扩展槽到主机板2: 8259A 与8086CPU 的连接A: 8259A 获得外部中断请求B: 8259A 的INT = H 输出C: 8086CPU 的INTR = H, 获得中断请求输入3: 中断请求, 中断屏蔽, 中断响应A: 中断请求 —— 输入INTR ← HB: 中断屏蔽 —— 清中断屏蔽控制标志位IF = 0中断允许 —— 置中断屏蔽控制标志位IF = 1C: 中断无响应 —— 若IF = 0, 输出/INTA = H中断有响应 —— 若IF = 1, 输出/INTA = L4: INTR 的中断过程A: 8086CPU 引脚INTR ← HB: 程序判断中断控制标志IF 的值C: 若IF = 0, 8086CPU 引脚/INTA → H, 无中断响应D: 若IF = 1, 8086CPU 引脚/INTA → L, 有中断响应E: 程序判断多中断优先级F: 执行中断类型号08H ~ 0FH 中的一个中断服务程序注: 对可屏蔽中断, 当中断请求有效时,要获得中断响应的条件是置IF = 1三: NMI 中断源1: PC/XT 的NMI 外部中断源2: NMI 中断请求 NMI ←3: NMI无中断响应输出, NMI与标志位IF无关4: NMI的中断过程A: 8086CPU的引脚NMI ←B: 执行02H§8.3 中断优先级管理当外部中断源为多个时, 必须定义其优先级别并对其管理一: 软件查询法1: 硬件电路A: 多中断源输入B: 或门输出接8086CPU的INTR2: 功能A: 输入中断源有一个为高时输出为高B: 可屏蔽中断请求由多中断源提供3: 优先级流程法先判断那一个输入中断源, 则此中断源优先级最高二: 硬件菊花链法由数字逻辑电路构成优先级电路, 现己不常用三: 专用芯片法软件法, 硬件法的结合——可编程中断控制器§8.4 可编程中断控制芯片—— 8259A✓特点A: 可程序控制芯片的功能B: 可提供中断源的中断类型码C: 可屏蔽输入端的中断源✓形式A: 单片方式——有8个中断源B: 级联方式——最多64个中断源一: 8259A的结构及功能1: 8259A的内部逻辑结构A: 中断请求寄存器——IRR1): 可输入IR0 ~ IR8共8个外部中断源2): IRR寄存器中的值可经DB读入CPU注: IRR有口地址, 即可编程读B: 中断服务寄存器——ISR1): 为中断源IR0 ~ IR8服务, 为CPU服务若IRR请求, CPU响应, 则ISR中相对应位为1若中断服务程序结束, 则ISR中相对应位为0 2): ISR寄存器中的值可经DB读入CPU注: ISR有口地址, 即可编程读C: 中断屏蔽寄存器——IMR1): IMR中IMR0 ~ IMR7与IRR中IR0 ~ IR7位对应若IMRn = 1, 则对应中断源IRn屏蔽若IMRn = 0, 则对应中断源IRn允许2): 寄存器IMR与中断标志IF的区别IMR屏蔽IRR, 当IMRn = 1时IF屏蔽CPU的中断请求INTR, 当IF = 0时IF的级别比IMR高3): IMR寄存器与CPU间可经DB读写操作注: IMR有口地址, 即可编程读写D: 优先权分析器——PR1): 对IRR中的IRR0 ~ IRR7中断源进行优先权分析2): IRR0 ~ IRR7的优先权分配可编程确定注: PR有口地址, 即可编程写E: 芯片控制逻辑1): 8259A的中断请求INT →8086CPU的INTR2): 8086CPU的/INTA →8259A的/INTAF: 芯片读写逻辑1): 8259A的片内地址线仅有A0(一线二址)注: 学习8259A的难点, 解决多寄存器读写与一线两址的矛盾2): 8259A的片选线/CS由地址译码产生注: PC/XT微机中8259A的地址为20H, 21H3): 8259A的读写线/RD, /WR直接与8086CPU的/RD, /WR连接G: 芯片数据线8259A的数据线为8位即D0 ~ D7H: 芯片的级联线1): 当外部中断源≤8个时, 仅有单片8259A当外部中断源>8个时, 需用多片8259A级联2): 级联线仅在8259A级联方式下有作用注: 级联线CAS0 ~ CAS2, /EN即/SP接线方式2: 8259A的引脚图A: 8259A为DIP28封装B: 8259A为+5V供电二: 8259A的中断优先权中断源IR0 ~ IR7的优先权序可编程确定1: 固定优先权(完全嵌套方式)A: 优先权序IR0(高) →IR7(低)B: 该优先权序始终不变2: 等优先权(普通循环方式)A: 初始优先权序IR0(高) →IR7(低)B: 若响应了IRn中断, 则IRn中断权最低, IRn-1中断权最高C: 每个中断优先权相同3: 特殊优先权(特殊循环方式)A: 初始优先权序由编程确定若定义IR5为初始最高优先权,则初始优先权序IR5 → IR7 → IR0 → IR4B: 其后工作同等优先权三: 中断源IR0 ~ IR7的中断触发方式1: 电平触发方式—— IR0 ~ IR7输入高电平有效A: 现象——中断源持续高电平B: 问题——造成连续中断请求C: 解决——在中服程序中令IF = 02: 边沿触发方式—— IR0 ~ IR7输入上升沿有效A: 特点—— IRR寄存器锁存触发信号B: 脉宽——上升沿脉冲宽度符合要求C: 方法——采用负脉冲的后沿触发四: 8259A的初始化命令字和操作命令字✓若要使用8259A, 必须按规定向其写入初始化命令字使8259A进入工作状态(一般由系统程序完成)✓若要改变8259A的功能, 可随时向其写入操作命令字使8259A按要求工作(一般由用户程序完成)(一): 8259A口地址讨论1: 8259A实际口地址一线二址, 址1 — A = 0, 址2 — A = 12: 8259A操作口地址A: 4个写初始化命令字操作B: 3个写操作命令字操作C: 3个读寄存器IRR, ISR, IMR操作D: 1个读中断类型号操作注: 2个地址怎样完成11个读写操作3: 地址分配表及应用特点表8.2 8259A的读写操作A: A0 = 0时的读操作, IRR, ISR, 中断类型号→ CPU注: 解决1址3读问题, 用位控制定义读入法B: A0 = 1时的读操作, 仅IMR → CPUC: A0 = 0时的写操作, CPU → OCW2, OCW3, ICW1注: 解决1址3写问题, 用同址顺序写入法D: A0 = 1时的写操作, CPU → OCW1, ICW2, ICW3, ICW4注: 解决1址4写问题, 用位识别写入法(二): 初始化命令字ICW的写入方法1: ICW1 ~ ICW4的写入流程A: ICW1, ICW2为必写初始化命令字ICW3, ICW4为选写初始化命令字B: ICW2, ICW3, ICW4采用同址顺序写入法2: ICW1 ——芯片控制初始化命令字A: 口地址A0 = 0, PC/XT口地址= 20HB: 位定义1): D4 = 1 为同址识别位注: 若D4 = 1 CPU对ICW1命令字写操作若D4 = 0 CPU对0CW2, OCW3命令字写操作2): D0 = 0 不写ICW4命令字D0 = 1 要写ICW4命令字3): D1 = 0 多片8259A方式, 要写ICW3命令字D1 = 1 单片8259A方式, 不写ICW3命令字4): D3 = 0 IR0 ~ IR7为边沿触发方式D3 = 1 IR0 ~ IR7为电平触发方式5): D2, D5, D6, D7位不用(8086CPU时)3: ICW2 ——中断类型号初始化命令字A: 口地址A0 = 1, PC/XT口地址= 21HB: 位定义1): D2 ~ D0 IR0 ~ IR7的编码, 即中断类型号的低3位2): D7 ~ D3 中断类型号的高5位注: 中断类型号的高5位由用户编程定义,中断类型号的低3位自动产生, 保证IR0 ~ IR7连续《例》定义8259A的8个中断类型号为08H ~ 0FH解: 08H = 00001000B, 0FH = 00001111B低3位为000B ~ 111B表示中断源IR0 ~ IR7的编码高5位为00001BMOV AL, 08HOUT 21H, AL4: ICW3 ——主/从8259A初始化命令字A: 写操作条件在ICW1中, D1 = 0B: 口地址A0 = 1, PC/XT口地址= 21HC: 写操作方法同址顺序写入法注: ICW2, ICW3, ICW4, OCW1均为同址( A0 = 1), 写顺序为写ICW2→写ICW3(若要)→写ICW4(若要)→写OCW1 D: 主8259A位定义1): 若D0 ~ D7 为1, 则IR0 ~ IR7对应端接有从8259A芯片2): 若D0 ~ D7 为0, 则IR0 ~ IR7对应端未接从8259A芯片E: 从8259A位定义1): D2 ~ D0 从8259A的INT端接主8259A的IRn端编码2): D7 ~ D3 未用5: ICW4 ——方式控制初始化命令字A: 写操作条件在ICW1中, D0 = 1B: 口地址A0 = 1, PC/XT口地址= 21HC: 写操作方法同址顺序写入法D: 位定义1): D0 = 0 用于8080CPUD0 = 1 用于8086CPU2): D1 = 0 普通, 特殊EIO结束方式D1 = 1 自动EIO结束方式3): D3,D2 = 00, 01 级联非缓冲方式D3,D2 = 10, 11 级联缓冲方式4): D4 = 0 单片8259A固定优先权D4 = 1 级联8259A固定优先权5): D7 ~ D5 未用《例》PC/XT系统BIOS对8259A的初始化命令字写入程序MOV AL, 00010011B ; D0 = 1, 要写ICW4, D1 = 1, 不写ICW3 OUT 20H, AL ; 写ICW1, D3 = 0, IR0 ~ IR7为边沿触发方式MOV AL, 00001000B ; IR0 ~ IR7 对应中断类型号为08H ~ 0FH OUT 21H, AL ; 写ICW2MOV AL, 00001001B ;D0 = 1, 8086方式, D1 = 0, 非自动EIO OUT 21H, AL ; 写ICW4, ,D4 = 0, 固定优先权(三): 操作命令字OCW的写入方法注: ICW按顺序写入(先写), OCW按需要写入(后写)1: OCW1 ——写IMR寄存器命令字A: 口地址A0 = 1, PC/XT口地址= 21HB: 位定义1): D0 ~ D7对应寄存器IMR中的IMR0 ~ IMR72): Dn = 0 对应中断源IRn中断允许Dn = 1 对应中断源IRn中断屏蔽2: OCW2 ——中断优先权选择命令字注: ICW4可定义8259A工作于固定优先权, 8259A的等优先权, 特殊优先权在此定义A: 口地址A0 = 0, PC/XT口地址= 20HB: 识别位D4, D3 = 0, 0 (同址识别位法, 对OCW2, OCW3)C: 位定义1): D2 ~ D0 特殊优先权中断源IRn编码2): D6 = 0 自动循环优先权D6 = 1 特殊循环优先权3): D7 = 0 固定优先权D7 = 1 循环优先权注: 仅当D6 = 1, D7 = 1时, D2 ~ D0值才有意义微机原理第八章: 中断系统4): D5 = 0 自动EIO结束方式D5 = 1 非自动EIO结束方式3: OCW3 ——运行方式命令字A: 口地址A0 = 0, PC/XT口地址= 20HB: 识别位D4, D3 = 0, 1 (同址识别位法, 对OCW2, OCW3) C: 位定义1): D2 = 0 CPU下次同址读操作读入IRR, ISR中的值D2 = 1 CPU下次同址读操作读入中断类型号的值2): D1,D0 = 00, 01 无意义D1,D0 = 10 CPU下次同址读操作读入IRR中的值D1,D0 = 11 CPU下次同址读操作读入ISR中的值3): D6, D5 级联方式下中断屏蔽的应用(约)4): D7 未用(四): 8259A的读操作方法1: 读IMR寄存器A: 口地址A0 = 1, PC/XT口地址= 21HB: 地址唯一, 无同址2: 读IRR寄存器A: 口地址A0 = 0, PC/XT口地址= 20HB: 条件先写OCW3中的D2,D1,D0 = 0103: 读ISR寄存器A: 口地址A0 = 0, PC/XT口地址= 20HB: 条件先写OCW3中的D2,D1,D0 = 0114: 读中断类型号A: 口地址A0 = 0, PC/XT口地址= 20HB: 条件先写OCW3中的D2 = 1C: 读入数据位定义1): D7 = 0 无中断请求IR0 ~ IR7D7 = 1 有中断请求IR0 ~ IR72): D2 ~ D0 为IR0 ~ IR7编码(当D7 = 1时)3): D6 ~ D3 未用微机原理第11 页。