第8章 PIE中断系统及其应用

DSP的外围中断PIE

PIE标志位寄存器(PIEIFRx=1,12)

INTx.8 7 INTx.7 INTx.6 INTx.5 INTx.4 INTx.3 INTx.2 INTx.1 0

外设中断标志位。每一位对应一个外设级中断。

当某一外设产生中断时,相应标志位置1,中断被响应

后,被清0

INTx中断X指CPU级中断INT1-INT12。

struct PIE_CTRL_REGS { union PIECTRL_REG PIECRTL; union PIEACK_REG PIEACK; union PIEIER_REG PIEIER1; union PIEIFR_REG PIEIFR1; union PIEIER_REG PIEIER2; union PIEIFR_REG PIEIFR2; 。。。。。。。 union PIEIER_REG PIEIER9; union PIEIFR_REG PIEIFR9; union PIEIER_REG PIEIER10; union PIEIFR_REG PIEIFR10; union PIEIER_REG PIEIER11; union PIEIFR_REG PIEIFR11; union PIEIER_REG PIEIER12; union PIEIFR_REG PIEIFR12; }; // PIE control register // PIE acknowledge // PIE INT1 IER register // PIE INT1 IFR register // PIE INT2 IER register // PIE INT2 IFR register 。。。。。。。。 // PIE INT9 IER register // PIE INT9 IFR register // PIE INT10 IER register // PIE INT10 IFR register // PIE INT11 IER register // PIE INT11 IFR register // PIE INT12 IER register // PIE INT12 IFR register

第8章 中断系统的基本应用

Page 8

机械工业出版社

2012-6-15

• •

• • • • • •

8.3.3 AVR的中断响应过程 通常,当某个中断条件成立后,硬件会自动将该中断的标志位 置“1”,表示中断产生,同时也作为申请中断服务的请求信号。 如果该中断的允许位为“1”,同时AVR的全局中断允许标志位I 也是“1”时,那么MCU在执行完当前一条指令之后就会响应该 中断。 1.中断响应的过程 AVR在响应中断请求时,MCU会使用4个时钟周期自动顺序的 完成以下任务: 清零状态寄存器SREG中的全局中断允许标志位I,禁止响应其 他中断。 将被响应中断的标志位清零(注意:仅对于部分中断有此操作 )。 将中断断点的地址(即当前程序计数器PC的值)压入堆栈,并 将SP寄存器中的堆栈指针减二。 自动将相应的中断向量地址压入程序计数器PC,即强行转入执 行中断入口地址处的指令。

Page 7

机械工业出版社

2012-6-15

• • • • • • • •

• •

8.3.2 ATmega16的中断控制 1.中断优先级的确定 在AVR单片机中,一个中断在中断向量区中的位置决定了它的优先级,位于 低地址的中断优先级高于位于高地址的中断。 2.中断标志 AVR有两种机制不同的中断:带有中断标志的中断(可挂起)和不带中断标 志的中断 (不能挂起)。 3.中断屏蔽与管理 为了能够灵活地管理中断, AVR对中断采用两级控制方式。所谓两级控制是 指AVR有一个中断允许的总控制位 I(既AVR标志寄存器SREG中的I标志位 ”),通常称为全局中断允许控制位。同时 AVR为每一个中断源都 “SREG.7 SREG.7” 设置了独立的中断允许位,这些中断允许位分散位于各中断源所属模块的控 制寄存器中。 4.中断嵌套 由于AVR在响应一个中断的过程中通过硬件将 I标志位自动清零,这样就阻 止了MCU响应其它中断。因此通常情况下, AVR是不能自动实现中断嵌套 的。如要系统中必须要实现中断嵌套的应用,用户可在中断服务程序中使用 指令将全局中断允许位开放,通过间接的方式实现中断的嵌套处理。

DSP第08章 中断系统及其应用+页码

be fetched from INTR1.1 to INTR12.1 locations if the respective interrupt flag is set.

All other TRAP, INTR, OR IFR,#16-bit operations fetch

the vector from the respective table location. You should avoid using such operations for INTR1 to INTR12.

The TRAP #0 operation returns a vector value of 0x000000

PIEIER&PIEIFR的数据结构

25

典型的PIEICPU响应流程图

一旦PIE控制器有中

断产生,相应的中 断标志位(PIEIFRx.y) 将被臵1。 若相应的PIE中断使 能位被臵1,PIE将 检查相应PIEACKx 确定CPU是否准备响 应该中断。 如果相应PIEACKx 被清零,PIE向CPU 申请中断。 如果PIEACKx被臵1 ,PIE将等待直到相 应的IEACKx被清零 才向CPU申请中断。

外部中断源

XINT1 XINT2

ቤተ መጻሕፍቲ ባይዱ

• • •

INT12 INT13 INT14

PDPINTx

RS XNMI_XINT13

F2812的中断类别

1. 硬件中断

所有外设中断(EV、ADC、SCI、SPI、ECAN等)和引 脚(XINT1、XINT2、XNMI_XINT13)引起的中断。

PIC单片机中断系统详细汇总

精选版课件ppt

9

§8.4 中断相关的寄存器

与中断有关的特殊功能寄存器SFR共有6个, 分别是:

选 项 寄 存 器 OPTION_REG 、 中 断 控 制 寄 存 器INTCON、第一外围设备中断标志寄存器PIR1、 第一外围设备中断屏蔽寄存器PIE1(也称中断使能 寄存器)、第二外围设备中断标志寄存器PIR2和第 二外围设备中断屏蔽寄存器PIE2,如表9.2所列。

1=选择RB0/INT上升沿触发;

精选版课件ppt

12

0=选择RB0/INT下降沿触发 ⒉中断控制寄存器INTCON

中断控制寄存器是一个可读/可写的寄存 器,各位的分布形式如下:

它将第一梯队中的3个中断源的标志位和屏 蔽位,以及PEIE和GIE包含在其中:

RBIF : 端 口 RB 的 引 脚 RB4 ~ RB7 电 平 变 化 中 断标志位。

TMR2IF:定时/计数器TMR2模块溢出中断标 志位。

➢ 1=发生了TMR2溢出; 0=未发生TMR2溢出。

CCP1IF:输入捕捉/输出比较/脉宽调制CCP1 模块中断标志位。

❖ 输入捕捉模式下:

1=发生了捕捉中断请求;

0=未发生捕捉中断请求。

精选版课件ppt

17

❖ 输出比较模式下: 1=发生了比较输出中断请求; 0=未发生比较输出中断请求。

后5个SFR,共有40位,但仅使用了30位来控 制中断,分别与图9.l中的中断逻辑电路的输入信 号成严格的对应关系。

精选版课件ppt

10

精选版课件ppt

11

⒈选项寄存器OPTION _REG

OPTION_REG选项寄存器是可读写的, 各位的分布形式:

该寄存器包含了与定时/计数器TMR0、 分频器和端口RB有关的控制位。RB端口引脚 RB0和外部中断INT复用一脚,与该脚有关的一 个控制位含义如下: INTEDG:外部中断INT触发信号边沿选择位:

中断系统及应用 PPT

CPU响应中断,就是CPU要去执行相应的中断服务程序,其响应过程是CPU将现执行程序的指令 地址压入堆栈,跳转到中断服务程序入口地址,中断服务程序的入口地址就是中断向量,这个中 断向量用2个16位寄存器存放。入口地址是22位的,地址的低16位保存在该向量的低16位;地址 的高16位则保存在它的高6位,更高的10位保留。

CPU级使能可屏蔽中断采纳CPU中断使能寄存器(IER)依然中断调试使能寄存器(DBGIER)与中 断处理方式有关。标准处理模式下,不使用中断调试使能寄存器(DBGIER)。只有当F28335使用 实时调试(Real-time Debug)且CPU被停止(Halt)时,才使用中断调试使能寄存器(DBGIER),此时 INTM不起作用。假如F28335使用实时调试而CPU仍然工作运行,则采纳标准的中断处理。

中断向量表

INT1、1 INT1、2 INT1、3 INT1、4 INT1、5 INT1、6 INT1、7 INT1、8

PIE 组2 向量-复用CPU的INT2中断

32 0x0000 0D40

2

SEQ1INT(ADC)

5

33 0x0000 0D42

2

SEQ2INT(ADC)

第8章 中断系统课件

中断向量在表中的位置称为 中断向量地址

中断向量地址=中断类型号 ×4

返回

IP 000 类型0中断入口(除法出错) CS

专 004 类型1中断入口(单步中断) IP

用 中 008

类型2中断入口(NMI)

CS

断 00C 类型3中断入口(断点中断)

3.专用硬件方式

在微型机中普遍使用一种可编程的中断控制 器(如Intel 8259A)实现中断优先级的管理 。

8.2 8086的中断结构

8.2.1 8086的中断类型

外部中断

内部中断

8.2.2 中断向量和中断向量表

8.2.3 中断向量的装入

8.2.4 8086的中断响应过程

外部中断响应过程

1.中断屏蔽方式

(1)普通屏蔽方式。利用操作命令字OCW1,使屏蔽 寄存器IMR中的一位或数位置1来屏蔽一个或数个中断 源的中断请求。

(2)特殊屏蔽方式。在某些场合,执行某一个中断服 务程序时,要求允许另一个优先级比它低的中断请求被 响应,此时可采用特殊屏蔽方式。

2.中断嵌套方式

(1)全嵌套方式。

③ 内部中断何时发生是可以预测的,这有点类似于子程序调用。

2.外部中断响应过程

(1)非屏蔽中断响应。

NMI中断不受IF标志的影响,也不用外部接口给出中断类型号,CPU响应NMI中断时也没 有中断响应周期。

(2)可屏蔽中断响应。

当INTR信号有效时,如果中断允许标志IF=1,则CPU就在当前指令执行完毕后,产生两 个连续的中断响应总线周期。

010 类型4中断入口(溢出中断)

014 系 统 备 用

07C

中断系统及外设课件PPT教学

定时器溢出 A/D转换完毕 HSI数据有效 HSO事件 HSI.0 软件定时器 串行口 外部中断

中断登记寄存器的功能

开始

第10页/共181页

通过修改其内容可以人为设置一个中断(将对应 位置1) 或清除某个中断(将对应位清0) 。

例:清除高速输出

LDB ANDB STB

▪ 当T1记满时,将IOS1.5置位,并触发定时器溢出 中断,中断向量2000H。 IOC1.2是T1溢出中断的允 许控制位。

开始

第24页/共181页

4.2 定时器及监视定时器

▪ 系统正常工作时,T1一直处于循环计数状态,任 何时刻都可读取其计数值(只能按字读),仅当系统 复位时T1才停止计数并复位。

4.1.2 MCS-96中断系 一、中统断源

引起中断的原因,或能发出中断申请的源, 称为“中断源”。

MCS-96单片机有九种中断源,分为外部中断 (EXTINT、HSI.0)和内部中断两类。

二、中断向量 内存中存放中断服务程序入口地址的两个存

储单元叫中断向量。硬件不提供中断服务程序入 口地址,只提供中断向量。中断向量中存放的内 容是中断服务程序入口地址

第2页/共181页

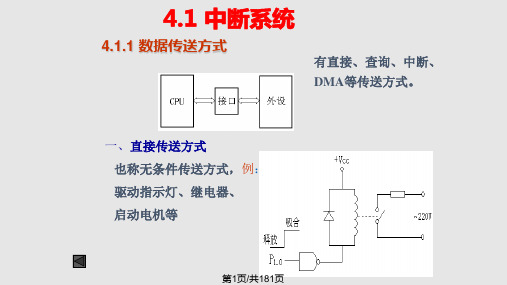

三、中断传送方式

CPU不主动查询中断源,只执行自己的程序,当中断源 准备好时,提出申请,若CPU准于请求,放下正在执行 的程序,去传送外设的数据。

查询

第3页/共181页

中断录像1 录像2

中断的好处

1、CPU分时操作(与多个外设并行工作) 2、实现实时处理 3、故障处理

CPU

外设 外设 外设

CPU 处理

温度 压力 断电

如何实现中断?

数字信号处理 外设中断扩展(PIE)

• 若CPU在实时仿真模式下处于运行状态,DBGIER被忽略。

8. 外部中断控制寄存器(XINTnCR,n=1~7)

Reserved

Polarity

Reserved Enable

• Polarity:用来确定外部引脚的上升沿或下降沿信号产生中断 • Enable:该位用来使能或禁止外部中断XINTn

• 为了清除CPU IFR标志位,用户需要向IFR寄存器相应位写0。

6. CPU中断使能寄存器(IER)

RTOSINT

DLOGINT

INT14

INT13

INT12 INT11

INT10

INT9

INT8

INT7

INT6

INT5

INT4

INT3

INT2

INT1

• 使能或禁止相应的中断

外设中断扩展(PIE)寄存器

• CPU无法在CPU级处理这么 多的外设中断请求,因此 用PIE控制器来仲裁来自 外设和外部管脚的中断请 求

外设中断扩展(PIE)

PIE中断源和外部中断 3~7

外设中断扩展(PIE)

利用PIE模块复用中断

96个中断源 进行8组选 组1(8组指 PIE中断有8 组),选出 的一组有12 的CPU中断, 从12中选1 个触发

外设中断扩展(PIE)

PIE中断:外设级、PIE级、CPU级

外设级: • 外设中,触发中断的事件发生时,会将寄存器中相应的中断

标志位(IF)置位。 • 在外设级,如果该中断的使能位(IE)被置位,则外设会向

PIE模块产生中断请求; • 如果该中断没有被使能,则IF将保持置位状态直至被软件清

中断系统的工作原理及应用

中断系统的工作原理及应用1. 引言中断系统是计算机系统中非常重要的一个组成部分,它负责处理硬件或软件发出的信号并中断当前程序的执行。

本文将介绍中断系统的工作原理及应用。

2. 工作原理中断系统的工作原理主要基于计算机的硬件设计。

当系统中某个设备发生了特定事件,例如键盘输入、鼠标移动或定时器到期时,设备会发送中断请求信号给中断控制器。

中断控制器会根据优先级处理这些中断请求,并在适当的时候暂停当前程序的执行,跳转到中断处理程序。

具体流程如下: 1. 介绍中断请求信号:每个设备都会有一个中断请求引脚,当设备发生中断事件时,会向中断控制器发送中断请求信号。

2. 中断向量表:中断控制器收到中断请求信号后,会查找中断向量表,将对应的中断号保存在中断描述符寄存器中。

3. 中断控制器的处理:中断控制器会根据中断号的优先级,对中断请求进行排序,并将最高优先级的中断请求发送给处理器。

4. 中断处理程序的执行:处理器接收到中断请求后,在当前指令的执行过程中暂停,并将控制权转移到中断处理程序。

5. 中断处理程序的执行:中断处理程序会执行一系列的指令,处理中断事件,然后返回到原来的程序继续执行。

3. 应用中断系统在计算机系统中有广泛的应用。

下面列举了一些常见的应用场景:•输入设备的处理:中断系统可以处理用户输入设备(如键盘、鼠标)的中断事件,实现用户与计算机的交互。

•定时器的使用:中断系统可以通过定时器中断来实现计算机系统中的定时功能,例如定时器中断用于触发操作系统的调度机制、刷新显示器等。

•网络通信:中断系统可以处理网络接口卡的中断事件,实现计算机系统与外部网络的通信。

•异常处理:中断系统可以处理程序中的异常事件,例如除零错误、非法指令等。

当发生异常时,中断系统会转入异常处理程序并执行相应的操作。

•硬件设备状态监测:中断系统可以用于监测硬件设备的状态,当设备发生故障或状态变化时,中断系统会及时处理并采取相应的措施。

18_F28335中断系统及其应用

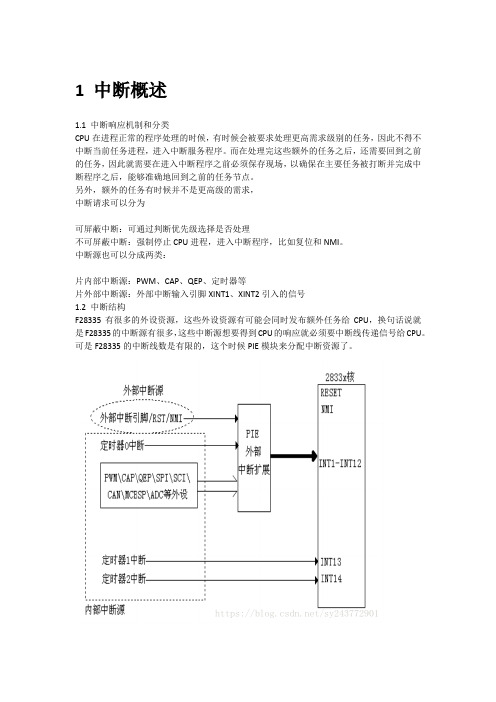

1 中断概述1.1 中断响应机制和分类CPU在进程正常的程序处理的时候,有时候会被要求处理更高需求级别的任务,因此不得不中断当前任务进程,进入中断服务程序。

而在处理完这些额外的任务之后,还需要回到之前的任务,因此就需要在进入中断程序之前必须保存现场,以确保在主要任务被打断并完成中断程序之后,能够准确地回到之前的任务节点。

另外,额外的任务有时候并不是更高级的需求,中断请求可以分为可屏蔽中断:可通过判断优先级选择是否处理不可屏蔽中断:强制停止CPU进程,进入中断程序,比如复位和NMI。

中断源也可以分成两类:片内部中断源:PWM、CAP、QEP、定时器等片外部中断源:外部中断输入引脚XINT1、XINT2引入的信号1.2 中断结构F28335有很多的外设资源,这些外设资源有可能会同时发布额外任务给CPU,换句话说就是F28335的中断源有很多,这些中断源想要得到CPU的响应就必须要中断线传递信号给CPU。

可是F28335的中断线数是有限的,这个时候PIE模块来分配中断资源了。

从图中可以看出,外部中断源均通过PIE模块进行判断处理内部中断源中定时器1和定时器2单独通过INT13 和INT14处理,其他也通过PIE模块处理PIE模块处理INT1-INT12总共16路中断线2 中断管理模块PIEPIE模块作用是在有限中断线的情况下用来管理多个中断源触发。

2.1 PIE模块结构PIE的结构如上图所示,PIE模块是由多个中断组和每个中断组的多路选择器构成的。

从INT1~INT12均为PIE模块管理的可屏蔽中断,而这12个中断每个都由8个外设计中断组成,比如途中INT1.X对应的就是由INT1.1 ~ INT 1.8组成,这8个外设级中断就是我们对应的外部中断源引脚。

PIE模块通过一个8选1的多路选择器将这8个外设中断组成一组。

我们在程序中配置的时候也是以这个结构为基础来配置的。

补充PIE响应的优先级INT1>INT2>…INT12INT1.1>INT1.2>…INT1.82.2 PIE模块的响应机制PIE模块有这么多的外设需要管理,就必定由相应的响应顺序和寄存器需要配置。

中断系统与基本应用

CVAVR中断程序的编写:

CVAVR中断程序的编写:

ATmega16的中断系统:

外部中断源

ATmega16有3个外部中 断源:

管脚

PD2 PD3 PB2

外部中断

INT0(外部中断0输入) INT1(外部中断1输入) INT2(外部中断2输入)

外部中断的控制

ATmega16的外部中断用户可以控制:

主 程 序

中 断 服 务 程 序 1

中断源:

内部中断源:定时器、串行通信接口,ADC 外部中断源:能够产生中断请求信号的外部设备

中断信号:

脉冲的上跳沿或下降沿(上升沿触发型或下降沿触发型) 高电平或低电平(电平触发型) 电平的变化(状态变化触发型) 一旦检测到中断信号会将相应的中断标志位置1,通知CPU处理

中断向量

CPU响应中断后会转去执行一个固定的程序空间地址中的指 令。这个固定的地址称作中断入口地址,也叫做中断向量。中 断入口地址往往是由单片机内部硬件决定的。程存空间中包含 中断向量区。中断向量区内一般不放置中断服务程序,而是一 条跳转指令。

中断优先级:

通常,一个单片机会有若干个中断源,MCU可以接收若 干个中断源发出的中断请求。但在同一时刻,MCU只能响 应这些中断请求中的其中一个。为了避免MCU同时响应多 个中断请求带来的混乱,在单片机中为每一个中断源赋 予一个特定的中断优先级。一旦有多个中断请求信号, MCU先响应中断优先级高的中断请求,然后再逐次响应优 先级次一级的中断。

ATmega16的中断控制: 中断嵌套

由于AVR在响应一个中断的过程中通过硬件将I标志位自动清零, 这样就阻止了MCU响应其它中断。因此通常情况下,AVR是不能 自动实现中断嵌套的。如要系统中必须要实现中断嵌套的应用, 用户可在中断服务程序中使用指令将全局中断允许位开放,通过 间接的方式实现中断的嵌套处理。

第8章YA及专题 中断系统资料

;端口地址

ROL AL,1 ; JC FWA ;服务程序A ROL AL,1 JC FWB ROL AL,1 JC FWC ……

6.1 中断系统的基本概念

中断响应 每条指令最后一个时钟周期,CPU检测INTR和NMI信号。 执行完当前指令并下列条件成立,则CPU响应中断:

③能向CPU提供中断类型码。可使不能提供中断类型码 的可编程接口芯片8255A、8253、8251A等采用中断方 式。

④具有多种中断优先权管理方式。

6.3 可编程中断控制器8259A

一、8259A内部结构和引脚功能

组成部分?

D7 ~ D0 数据总线 缓冲器 INTA INT

8259A 内部结构

第6 章 中断系统

本章重点

中断基本概念

中断过程

8086CPU中断系统

8259A中断控制器的功能及应用

6.1 中断系统的基本概念

中断系统是完成中断功能的软件及硬件电路的总 称,它可以使计算机实现如下操作: (1) 故障检测和自动处理。 (2) 实时信息处理。 (3) 分时处理。 (4) 并行工作。 什么是中断?

中 断 向 量 表

6.2 8086/8088中断系统

中断向量表的初始化 方法1:直接编程填写中断向量表 CLI ;关中断 MOV AX,0000H MOV DS,AX ;向量表段基址 MOV SI,48H*4 ;n=48H,向量表偏移地址 MOV AX,OFFSET int48h;服务程序int48h入口偏移地址 MOV [SI],AX MOV AX,SEG int48h ;服务程序int48h入口段基址 MOV [SI+2],AX STI ;开中断 方法2:采用DOS系统功能调用25H号: 例:将中断向量 码为48H的服务 程序入口地址放 入向量表

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2013年2月1日

3.2 中断向量的映射方式

根据上面的表格可以知道:控制位的不同设 置,中断向量表有不同的映射方式。

2013年2月1日

3. PIE中断向量表:见表8.6(P129)

2013年2月1日

4 可屏蔽中断处理

可屏蔽中断的响应过程实质上是中断产生、使 能到处理的过程。 使能/禁止复用外设中断 PIE寄存器: PIECTRL、PIEIFR PIEIER、PIEACK 外设向CPU发出的复用中断请求

2013年2月1日

处理流程:某个可屏蔽中断产生后 首先将中断标志寄存器(IFR)置位为1 单独使能IER和全局使能INTM 涉及到的寄存器:IFR、IER、INTM

2013年2月1日

4.1 PIE配置及控制寄存器

…………………………………

2013年2月1日

PIEVECT:这些位表明获取PIE矢量表的起始地址; ENPIE:使能PIE模块 ENPIE=1表明所有矢量都从PIE矢量表中获取; ENPIE=0时表明所有数量都从boot ROM或外部 接口zone 7中获取;

2013年2月1日

3.1 中断向量的分配

复用中断模式在使用中断过程中多个中断源共 用一条中断线,每条中断线连接地中断向量都在 中断向量表中占32位地址空间,用来存放中断服 务程序的入口地址; 中断复用程序必须处理所有输入的中断请求, 这就要求编程人员在服务程序的入口处采用软件 方法将这些中断分离开,以便能够正确地处理; 但软件分离的方法势必会影响中断的响应速度, 因此,在实时性要求高的应用中不能使用。因此 就涉及到如何加快中断服务程序的问题。

IFR、IER、DBGIER、INTM

2013年2月1日

4.2 CPU中断涉及的寄存器

中断使能寄存器

中断使能设置:置1使能中断 IER |= 0x0008; //使能中断INT4 IER&= 0xFFF7;//禁止中断INT4 系统复位或CPU中断响应后,CPUIFR将自动清零

2013年2月1日

2013年2月1日

1、中断源

两个不可屏蔽中断RESET和NMI各自占用独立 的专用中断,同时NMI中断也可以选择同定时器1 复用INT13;

2013年2月1日

2013年2月1日

CPU一共支持16个中断(RESET、NMI、 INT1~INT14);其中RESET、NMI是不可屏蔽中 断;INT1~INT14是可屏蔽中断(INT13、INT14留 给实时操作系统);

2013年2月1日

3) CPU级中断

一旦向CPU请求中断,相应于INTx的CPU级中 断标志位(IFR)置1。中断标志位锁存到IFR后, 只有CPU中断使能寄存器(IER)或调试中断使能 寄存器(DBGIER)和全局中断屏蔽位(INTM)被使 能时才会响应中断请求;

2013年2月1日

3) CPU级中断

2013年2月1日

2013年2月1日

3.2 中断向量的映射方式

在F2812中采用外设中断扩展模块(PIE)以 加快中断服务程序; 中断向量表可以映射到5个不同的存储空 间。实际应用中,只使用PIE中断向量表映 射;

PIE中断向量映射地址:0x0000D00 ~ 0x0000 0DFF,

2013年2月1日

2) PIE级中断

一旦PIE控制器有中断请求,相应的中断标志位 被置1(PIEIFRx.y); 如果相应的PIE中断使能位(PIEIERx.y)被置1, 则PIE检查相应的PIEACKx位以确定CPU是否准 备响应该中断; 如果PIEACKx清零,则PIE向CPU发出中断请 求;如果PIEACKx置1,则PIE将等待直到 PIEACKx被清0才向CPU发出中断请求; 返回

2013年2月1日

实际用户可以修改使用的外设中断只有45个

2013年2月1日

2.1 中断操作流程

包含三部分中断 外设级中断、PIE级中断、CPU级中断

2013年2月1日

2.1 中断操作流程

2013年2月1日

1) 外设级中断

外部设备中断事件发生,则其对应的寄存器 中的中断标志位被设为1(Interrupt Flag: IF); 若相应的中断使能位(Interrupt Enable: IE)被 设为1,则外部设备向PIE控制器发出一个中 断请求;

当定时器被使能(TCR.Bit4=0),定时器时钟 经过预定标计数器(PSCH:PSC)递减计数,预 定标计数器产生下溢后向定时器的32位计数 器(TIMH:TIM)借位; 定时器计数器(TIMH:TIM)递减计数,当产 生溢出后,会向CPU发送中断;

2013年2月1日

5.2 定时器工作原理

若中断被使能,则中断请求提交给PIE,IF仍为1; 若中断未被使能,则IF仍为1,直至软件清0;

外设寄存器中的IF位需手动清0;

2013年2月1日

1) 外设级中断

外设级中断通过IFR与IER使能控制; 注意:外设寄存器的中断标志必须采用软件 进行清零;

返回

2013年2月1日

2) PIE级中断

1. 定时器寄存器地址名称

0x0000 0C18~0C3F 保留

2013年2月1日

2. 定时器控制寄存器(TCR)

每个字段含义 见教材P136

2013年2月1日

3. 定时器预定标寄存器(TPR)

2013年2月1日

4. 定时器计数器(TIM)

2013年2月1日

4. 定时器周期寄存器

2013年2月1日

2013年2月1日

PIEACKx:每一位对应一个中断 BIT 0对应INT1; BIT 11对应INT12

2013年2月1日

这些寄存器位表明中断是否产生 x=1~12;INTx表示CPU INT1~INT12

2013年2月1日

这些寄存器位表明是否使能中断

2013年2月1日

4.2 CPU中断涉及的寄存器

可屏蔽中断通过相应的中断使能寄存器使能或 禁止产生的中断;

2013年2月1日

1、中断源

在F2810和F2812处理器中,定时器1和定时器2 预留给实时操作系统DSP/BIOS使用,其中断分配 给INT14和INT13,用户在程序中不可以修改;

2013年2月1日

1、中断源

其余12个可屏蔽中断直接连接在外设中断扩展模 块,供外部中断和处理器内部的外设单元使用;

CPU级使能可屏蔽中断采用CPU中断使能寄存 器(IER)还是中断调试使能寄存器(DBGIER)与中 断处理方式有关。

标准处理模式下,不使用中断调试使能寄存器 (DBGIER); 当F281x使用实时调试且CPU被停止时,才使用中 断调试使能寄存器(DBGIER),此时INTM不起作用;

4.2 CPU中断涉及的寄存器

全局中断使能

全局中断使能设置:置1时禁止所有的中断 asm(“CLRC INTM”); //使能全局中断 asm(“SETC INTM”); //禁止全局中断

2013年2月1日

5 定时器中断应用举例

5.1 定时器基本操作

F2812有三个32位CPU定时器(TIMER0/1/2) TIMER1/2预留给实时操作系统使用 TIMER0可以供给用户使用 定时器的功能框图如下图

2013年2月1日

2013年2月1日

3 中断向量

中断向量的分配 中断向量的映射方式

2013年2月1日

3.1 中断向量的分配

PIE支持96个中断,每个中断都有自己的中 断向量存放在RAM中,构成整个系统的中断 向量表,如表8.2所示; 在相应中断时,CPU将自动地从中断向量表 中获取相应的中断向量; CPU获取中断向量和保存重要的寄存器需要 花费9个CPU时钟周期,因此CPU能够快速地 响应中断;

2013年2月1日

5) PIE寄存器及其地址

PIE寄存器地址:0x0000 0CE0~0x00000CFF PIECTRL(PIE控制寄存器):0x0000 0CE0 PIEACK(PIE响应寄存器):0x0000 0CE1 PIEIER1:0x0000 0CE2 PIEIFR1:0x0000 0CE3 … … PIEIER12:0x0000 0CF8 PIEIFR12:0x0000 0CF9 保留:0x0000 0CFA~0x0000 0CFF

8.6 定时器中断应用举例

具体见教材P139

2013年2月1日

2013年2月1日

用户可以操作修改的中断是INT1~INT12,其中 每一个中断组又复用了8个外设中断;所以外设中 断一共有96个;

都能产生1个或多个中断; 但由于CPU并不能同时处理所有的外设中断请求; 因此需要一个PIE控制器对这些外设和外部管脚 的中断请求进行仲裁; PIE矢量表用来存放每一个中断服务的地址;不 论是复用还是非复用的中断都对应着一个矢量表;

2013年2月1日

2013年2月1日

5.2 定时器工作原理

工作时钟

若处理器采用30MHz的外部时钟,经过锁相 环10/2倍频后,系统的时钟工作在150MHz; 定时器选择SYSCLKOUT作为定时器时钟, 所以工作频率也是150MHz;

2013年2月1日

5.2 定时器工作原理

计数原理

2013年2月1日

3) CPU级中断

中断标志寄存器(IFR) 中断使能寄存器(IER) 全局中断屏蔽使能(INTM)

2013年2月1日

4)中断优先级

CPU中断的优先级:由高到低分别为RS, NMI,INT1~INT14; PIE控制每组8个中断的优先级:由高到低为 INTx.1~INTx.8。

PIE模块复用8个外设中断引脚向CPU申请中断; 这些中断被分为12组,每组有一个中断信号向 CPU申请中断;