第八章 中断和中断

微型计算机原理与接口技术(第4版)___题解及实验指导

微型计算机原理与接口技术(第4版)___题解及实验指导这份大纲旨在为《微型计算机原理与接口技术(第4版)吴宁题解及实验指导》给出一个概览,请参考以下内容。

概述介绍微型计算机原理与接口技术的基本概念引言微型计算机的发展和应用阐述微型计算机系统的组成和层次结构计算机硬件描述计算机硬件的基本组成包括中央处理器、存储器和输入输出设备讨论硬件的功能和特点计算机软件介绍计算机软件的概念和分类强调操作系统的作用和功能讨论软件的开发和应用微型计算机接口研究计算机与外部设备之间的连接和通信介绍接口的原理和技术分析接口的设计和实现实验指导实验准备介绍进行实验所需的基本准备工作包括实验器材、软件环境和实验原理的研究实验内容提供各章节相关实验的具体内容和步骤引导学生逐步完成实验任务强调实验中的关键点和注意事项实验总结总结每个实验的目的和结果分析实验过程中遇到的问题和解决方法提供实验的评价和改进建议通过这份《微型计算机原理与接口技术(第4版)吴宁题解及实验指导》大纲,学生可以了解该教材的内容和结构,对于研究和实验有一个整体的认识和预期。

本章介绍微型计算机原理与接口技术的基本概念和背景。

首先,讲解了计算机系统的组成和发展历程,帮助读者了解计算机系统的基本结构和演化过程。

其次,介绍了微型计算机的特点和分类。

通过本章的研究,读者能够建立起对微型计算机原理与接口技术的整体认识和理解。

本章将深入探讨微型计算机的结构和各个功能部件的作用。

首先,介绍了微型计算机的总线结构和数据流动方式,帮助读者了解信息在计算机系统中的传输过程。

然后,讨论了微型计算机的存储器层次结构和主要存储器的特点。

随后,讲解了微型计算机的中央处理器(CPU)的功能和内部结构。

最后,介绍了微型计算机的输入输出系统,包括输入设备和输出设备的种类和原理。

通过本章的研究,读者能够全面了解微型计算机的内部结构和各个功能部件的作用。

本章重点介绍微型计算机的编程技术,包括指令系统和汇编语言编程。

计算机组成原理课件第08章

一、接口的功能和组成

1、总线连接方式的I/O接口电路 、总线连接方式的 接口电路 在总线结构的计算机系统中,每一台 I/O设备都是通过I/O接口挂到系统总线上 的。如图示:

数据线: 数据线:传送数据信息 ,其根数一般等于存储 字长的位数或字符的位 数。双向。 设备选择线: 设备选择线:传送设备 码,其根数取决于I/O指 令中设备码的位数。单 向。 命令线: 命令线:传输CPU向设 备发出的各种命令信号 ,其根数与命令信号多 少有关。单向总线。 状态线: 状态线:向主机报告I/O 设备状态的信号线。单 向总线。

CPU在任何瞬间只能接受一个中断源 CPU在任何瞬间只能接受一个中断源 的请求。 的请求。因此,当多个中断源提出中断请 求时,CPU必须对各中断源的请求进行排 队,且只能接受级别最高的中断源的请求 ,不允许级别低的中断源中断正在运行的 中断服务程序。此时,就可用MASK来改 变中断源的优先级别。 另外,CPU总是在统一的时间,即执 CPU总是在统一的时间, 总是在统一的时间 行每一条指令的最后时刻, 行每一条指令的最后时刻,查询所有设备 是否有中断请求。 是否有中断请求。 接口电路中D、INTR、MASK和中断 查询信号的关系如图示:

2、排队器 、 当多个中断源同时向CPU提出请求时,经 排队器的排队,只有优先级高的中断源排上 队,这样就能实现CPU按中断源优先级的高 低响应中断请求。 下图是设在各个接口电路中的排队电路— —链式排队器。

其中首尾相接的虚线部分组成的门电路是排 当各中断源均无中断请求时,各INTRi 为高电 队器的核心,由一个非门和一个与非门构成。 平,其INTP1 '、 INTP2' 、 INTP3 '……均为高电平 中断源优先级最高的是1号中断源。当多个中 。一旦某中断源提出中断请求,就迫使比其优先级 断源提出中断请求时,排队器输出端INTPi, 低的中断源之INTPi '变为低电平,封锁其发中断 只有一个为高电平,表示该中断源排上队。 请求。

中断技术是计算机中重要的技术之一,它既和硬件有关,又和软件有关正

89S51中断系统主要由几个与中断有关的特殊功

能寄存器、中断入口、顺序查询逻辑电路等组成。

89S51的中断系统结构框图示于图8-3。如图所示, 与中断有关的特殊功能寄存器有4个,分别为中断源 寄存器(即专用寄存器TCON、SCON的相关位)、 中断允许控制寄存器IE和中优先级,即可实现二级中 断嵌套。5个中断源的排列顺序由中断有限级控制寄 存器IP和顺序查询逻辑电路(图中的硬件查询)共同 决定。5个中断源对应5个固定的中断入口地址,亦称 矢量地址。

2、实现是实时处理

在实时控制中,现场的各个参数、信息是随时间和现场情况 不断变化的。有了中断功能,外界的这些变化量可根据要求, 随时向CPU发出中断请求,要求CPU及时处理,CPU就可以马 上响应(若中断响应条件满足)。这样的及时处理在查询方式 下是做不到的。

3、故障处理

计算机在运行过程中,出现一些事先无法预料的故障是难 免的,如电源突跳,在储出错,运算溢出等。有了中断功能, 计算机就能自行处理,而不必停机处理。

序事先却无法确知,因为“中断”的发生是由外部 的

因素决定的,程序中无法事先安排调用指令,因而 调用中断服务程序的过程是由硬件自动完成的。

8.1.2 引进中断技术的优点

计算机引进中断技术之后主要有如下优点:

1、分时操作

有了中断功能就解决了快速的CPU与慢速的外设之间的矛 盾。可以使CPU和外设同时工作。CPU在启动外设工作后,继 续执行主程序,同时外设也在工作,每当外设做完一件事,就 发出中断申请,请求CPU中断它正在执行的程序,转去执行中 断服务程序(一般情况是处理输入输出数据),中断处理完之 后,CPU恢复执行主程序,外设仍继续工作。这样CPU可以命 令多个外设同时工作,从而大大提高了CPU的利用率。

第八章中断系统第九章DMA控制器

为CPU专用;一部分是由磁盘操作系统DOS保留为 系统使用,用户可以使用200个左右中断。

§8.5 IBM PC/XT的中断方式

第九章 DMA控制器

DMA:direct memory access

直接存储器访问技术,适合高速的数据交换

2. 硬件优先权排队电路

(1)中断优先权编码电路

若有8个中断源,当任意一个有中断请求时,通过或门, 即可有一个中断请求信号产生,能否送至CPU的中断请 求线,还要受比较器的控制。

(2)雏菊花环(Daisy Chain)式或称为链式优先权排队电 路

§8.3 中断优先权及多重中断

中断响应(来自CPU)

§8.3 中断优先权及多重中断

8.3.1 中断优先权

(2)移位法 XOR AL,AL IN AL,[20H] RCL AL, 1 JC PWF RCL AL, 1 JC DISS ……

;输入中断请求触发器的状态 ;外设A中断服务程序 ;外设B中断服务程序

§8.3 中断优先权及多重中断

8.3.1 中断优先权

§8.4 8086/8088的中断方式

3.中断向量表 o 每一种中断类型对应一个中断向量; o 每个中断向量占4个字节,前两个字节存放中断处 理子程序入口地址的偏移量(IP),后两个字节存放 中断处理子程序入口地址的段地址(CS); o 256个中断中:0-4为专用中断,5-31为系统保留 (21个),32以上共224个为用户自定义中断。

内部中断

INT n指令—类型为n的中断指令

软件中断 INT 3指令—断点中断指令 INT0指令—溢出中断指令

IRET指令—中断返回

计算机硬件基础——第八章(中断系统)

AJMP MAIN

AJMP IT0P MAIN: MOV SP,#60H MOV TMOD, #01H MOV TH0 ,#M

DJNZ R7,DD2

DJNZ R5,DD1 RET

MOV TL0,#N

SETB TR0 SETB EA SETB ET0 SJMP $

从上例可看出中断大大提高了CPU的工作效率。

中建立堆栈。 ②在中断服务程序的开始应有保护现场的指令。 即将中断服务程序中用到的各寄存器的内容压入堆栈保存,在中 断结束之前弹回恢复,然后返回。这样就能保证返回原断点时各

寄存器内容与中断服务前相同,使原程序能正确运行。

③中断与调用子程序的异同: 中断过程中由主程序转向中断服务程序的请求是由外部设备提出 的,发生中断的时刻不确定,而在何处调用子程序则是由程序确 定的。

3

一.8031的中断请求源

有5个中断源,它们是:串行口 T1 INT1 T0 INT0

TCON (88H)中相应的位锁存它们的中断标志:

TF1 其中:

TR1

TF0

TR0

IE1

IT1

IE0

IT0

IT0 :INT0触发方式选择,0:低电平触发,1:负跳变触发

IE0 :INT0选择负跳变触发时的中断标志,0:INT0未申请中断, 1:INT0申请中断 INT0选择低电平触发时此标志无用。 IT1、IE1同上定义对INT1控制。

10

例

8000H

MOV A, #06H

①

8002H

8005H

MOV B, #05H

MUL AB MOV IE , #05H MOV R0 , #30H …………….

②

8006H 8009H 800BH

计算机硬件技术--中断技术知识考试题

第八章习题参考答案8.1 什么是中断?采用中断技术有哪些好处?答:中断是指由CPU内/外部事件引起或由程序的预先安排,使CPU中断正在运行的正常程序(主程序),而转到为该内部/外部事件或预先安排的事件服务程序,待服务完毕,再返回被暂时中断的正常程序处继续执行正常程序的过程。

采用中断技术,可以使计算机方便地实现如下一些操作:(1)分时操作。

有了中断系统,CPU可以命令多个外部设备同时工作,CPU分时控制这些外设,大大提高了CPU的吞吐率。

(2)实现实时处理。

当计算机用于实时控制,系统要求计算机为它服务的时间是随机的,而中断系统中这种请求--响应模式正好迎合了实时系统的需求。

(3)故障处理。

计算机在运行过程中,往往会出现一些故障,如电源掉电、存储出错、运算溢出等。

有了中断系统,当出现上述情况时,CPU可以随时转去执行故障处理程序,自行处理故障而不必停机。

随着微型计算机的发展,中断系统不断增加新的功能,中断系统甚至可以实现计算机系统中软硬件资源的自动管理。

8.2 什么叫中断系统?它具备哪些功能?答:把能够实现中断全部功能的软件、硬件的总称称为中断系统。

不同计算机的中断系统,其具体实现可能不尽一样,但中断系统的基本功能是相同的。

中断系统的基本功能如下:1.能实现中断响应、中断处理(服务)、中断返回和中断屏蔽。

这是中断系统最基本的功能。

2.能实现中断优先级排队(管理)。

即当有多个中断源同时申请中断时,CPU如何能够优先响应最紧急的中断申请。

3.能实现中断嵌套。

即当CPU正在为优先级较低的中断源服务时,具有较高优先级的中断源提出中断申请,此时中断系统应当允许较高优先级的中断源中断较低优先级的中断源,待较高优先级的中断处理完成后,再接着处理较低优先级的中断,这种中断服务程序再被中断的过程称为中断嵌套。

8.3 何谓非屏蔽中断和可屏蔽中断?答:非屏蔽中断是指用户不能用软件屏蔽的中断。

它是通过8086的NMI引脚进入。

408中计算机组成原理选择题各章节分

408中计算机组成原理选择题各章节分408中计算机组成原理是一门重要的课程,它涵盖了计算机组成原理的各个方面。

在这门课程中,选择题是一种常见的考试形式,它能够帮助学生巩固知识,提高解题能力。

下面将对408中计算机组成原理选择题的各章节进行分析。

第一章:计算机系统概述。

这一章主要介绍了计算机系统的基本概念和组成部分。

选择题主要涉及计算机的发展历程、计算机的基本组成和计算机的性能指标等内容。

第二章:数据的表示和运算。

这一章主要介绍了计算机中数据的表示方式和运算方法。

选择题主要涉及二进制数的表示和转换、定点数和浮点数的表示和运算等内容。

第三章:存储器。

这一章主要介绍了计算机中的存储器的种类和组织方式。

选择题主要涉及存储器的层次结构、存储器的访问方式和存储器的容量等内容。

第四章:指令系统。

这一章主要介绍了计算机中的指令系统的设计和实现。

选择题主要涉及指令的格式和编码、指令的执行过程和指令的寻址方式等内容。

第五章:中央处理器。

这一章主要介绍了计算机中的中央处理器的结构和功能。

选择题主要涉及中央处理器的组成和工作原理、中央处理器的时序控制和数据通路设计等内容。

第六章:总线。

这一章主要介绍了计算机中的总线的种类和工作原理。

选择题主要涉及总线的分类和特点、总线的传输方式和总线的控制方式等内容。

第七章:输入输出系统。

这一章主要介绍了计算机中的输入输出系统的组成和工作原理。

选择题主要涉及输入输出设备的分类和特点、输入输出接口的设计和输入输出控制方式等内容。

第八章:中断和异常处理。

这一章主要介绍了计算机中的中断和异常处理的机制和方法。

选择题主要涉及中断的分类和处理过程、异常的产生和处理方式等内容。

通过对408中计算机组成原理选择题的各章节进行分析,我们可以看出,这门课程的内容非常丰富,涵盖了计算机组成原理的各个方面。

选择题能够帮助学生巩固知识,提高解题能力。

因此,学生在学习这门课程时,应该注重理论知识的学习,同时也要多做选择题,加强对知识的理解和应用能力。

计算机操作系统名词解释

第一章引论1操作系统:操作系统是管理和控制计算机系统内各种硬件和软件资源,有效地组织多道程序运行的系统软件(或程序集合),是用户与计算机之间的接口。

2管态:当执行操作系统程序时,处理机所处的状态3目态:当执行普通用户程序时,处理机所处的状态。

4多道程序设计:在这种设计技术下,内存中能同时存放多道程序,在管理程序的控制下交替的执行。

这些作业共享CPU和系统中的其他资源。

5并发:是指两个或多个活动在同一给定的时间间隔中进行。

它是宏观上的概念。

6并行:是指两个或多个活动在同一时刻同时执行的情况。

7吞吐量:在一段给定的时间内,计算机所能完成的总工作量。

8分时:就是对时间的共享。

在分时系统中,分时主要是指若干并发程序对CPU时间的共享。

9实时:表示“及时”或“既时”。

10系统调用:是用户在程序中能以“函数调用”形式调用的、由操作系统提供的子功能的集合。

每一个子功能称作一条系统调用命令。

它是操作系统对外的接口,是用户级程序取得操作系统服务的唯一途径。

11特权指令:指指令系统中这样一些指令,如启动设备指令、设置时钟指令、中断屏蔽指令和清内存指令,这些指令只能由操作系统使用。

12命令解释程序:其主要功能是接收用户输入的命令,然后予以解释并且执行。

13脱机I/O:是指输入/输出工作不受主机直接控制,而由卫星机专门负责完成I/O,主机专门完成快速计算任务,从而二者可以并行操作。

14联机I/O:是指作业的输入、调入内存及结果输出都在CPU直接控制下进行。

15资源共享:是指计算机系统中的资源被多个进程所功用。

例如,多个进程同时占用内存,从而对内存共享;它们并发执行时对CPU进行共享;各个进程在执行过程中提出对文件的读写请求,从而对磁盘进行共享等等。

第二章进程和线程1顺序性:是指顺序程序所规定的每个动作都在上个动作结束后才开始的特性。

2封闭性:是指只有程序本身的动作才能改变程序的运行环境。

3可再现性:是指程序的执行结果与程序运行的速度无关。

微机原理 第8章 中断控制器8259A 习题及参考

第八章中断控制器8259A1. 8259A的初始化命令字和操作命令字在设置上有什么不同?答:初始化命令字:是在计算机系统启动时,由初始化程序设置的,且一旦设定,一般在系统工作过程中就不再改变。

操作命令字:是由应用程序设定的,用来对中断处理过程作动态控制。

在系统运行过程中,可被多次设置。

2. 8259A中的中断屏蔽寄存器(IMR)与8086的中断允许标志(IF)有何差别?在中断响应过程中,它们是怎样配合工作的?答:差别有三:差别1——IMR中的某位为1时,说明对应此位的中断请求当前是受到屏蔽的;而IF位为0时,说明可屏蔽中断请求是受到屏蔽的。

差别2——IMR可以屏蔽部分中断请求;而IF为0时,屏蔽的是所有可屏蔽中断请求。

差别3——IMR是8259A中的一个8位寄存器;而IF是CPU中16位标志寄存器中的1位控制标志。

配合:只有当IMR中的某位为0且IF=1时,CPU才有可能响应对应此位的中断请求。

具体过程是:由中断请求寄存器(IRR)接收外部的中断请求并锁存中断请求,IMR中的对应位决定是否让这些请求通过。

如果IMR的对应位为1,则说明此中断当前受到屏蔽,即对它进行了封锁,而不让其进入优先级裁决器(PR);如果IMR的对应位为0,则PR把新进入的中断请求与当前服务寄存器(ISR)中指示的当前正在处理的中断作比较,若判断出新进入的中断请求具有足够高的优先级,则PR通过相应的逻辑电路使8259A的INT端为1,从而向CPU发出一个中断请求;如果此时CPU的IF=1,则CPU执行完当前指令后,就会响应该中断请求;否则,若IF=0,则CPU不予响应。

3. 8259A的全嵌套工作方式与特殊全嵌套工作方式有何不同?答:工作在全嵌套方式下,当处理某一级中断时,只有当优先级更高的中断请求到来,才会实施中断嵌套。

当同级中断请求到来时,不会给予响应;而工作在特殊全嵌套方式下,当处理某一级中断时,若有同级的中断请求到来,也会给予响应,从而实现对同级中断请求的特殊嵌套。

第八章 外部中断

EXTPOLAR[0] = 1 EXTMODE[0] = 0 上升沿 EINT0 0 1 电平 中断 边沿 中断 0 1 0 1 低电平中断 高电平中断 外 部 中 断 0

ARM 处理器核

系统控制模块功能汇总

• 寄存器汇总

名称 EXTINT EXTMODE EXTPOLAR 描述 外部中断标志寄存器 外部中断方式寄存器 外部中断极性寄存器 访问 R/W R/W R/W 复位值 0 0 0

外部中断输入

• 寄存器汇总

可以通过设置 PINSELx EXTPOLAR 寄存器选择对应引脚为外部中 和EXTMODE确定外部中断 有效中断信号设置中断标志。 可以控制把CPU 从掉电模式唤醒。 断输入引脚。 的触发信号。

LPC1700系列ARM的电平中断可以设置为高电平触发和 低电平触发。 当EXTPOLAR[0] = 0时,外部中断0设置为低电平触发。 当EXTPOLAR[0] = 1时,外部中断0设置为高电平触发。

EXTPOLAR[0] = 1 EXTMODE[0] = 0 高电平 EINT0 0 1 电平 中断 边沿 中断 0 1 0 1 低电平中断 高电平中断 外 部 中 断 0

上升沿

下降沿中断

上升沿中断

VIC

注意:这里仅以EINT0为例来进行讲解,EINT1~EINT3与之类似,此处不再重复。

外部中断输入

• 电平中断设置

LPC1700系列ARM的电平中断可以设置为高电平触发和 低电平触发。 当EXTPOLAR[0] = 0时,外部中断0设置为低电平触发。 当EXTPOLAR[0] = 1时,外部中断0设置为高电平触发。

微机原理--第八章-中断系统

裁决器

0

IR6

0

IR7

选 CS 译 码

RD

WR

INTA INT

ICW1 芯片控制 A0

A0

1 × I3 I4 0 1 0 0 1 0 1 0 0 1

ICW2 中断类型号 1

ICW3 主从片连接关系

1 ICW4 方式控制

1

OCW1 中断屏蔽寄存器 IMR

00

0

SP/EN

CA0

OCW2 优先级设置、发EOI

上有中断申请,则将IRR相应位置1;

总线

D0 ~ D7 A0

A5 ~ A9

IOR IOW INTA INTR

数据线 D0 ~ D7

A0

ISR 0

当前 0

中断 服务

• 非屏蔽中断 – 由NMI引脚引起的中断,称非屏蔽中断。 – 当NMI引脚上产生上升沿信号,CPU必响应此中断请 求,即NMI引脚上的中断请求不受IF标志的控制, – IF不能屏蔽NMI引脚上的中断请求。

8086/8088CPU的中断分类图

中断源

外部中断 内部中断

非屏蔽中断 可屏蔽中断 内部硬件中断

SP/EN CA0 CA1 CA2

GND

+ 5V

电子钟时间基准

键盘 保留 串 口2 串 口1 硬盘 软盘 打印机

用于多片 8259A

级连情况

7.3.4 8259A的控制字

8259A中断控制器

处理部分

0

ISR 0

当前 0

中断 0

服务 0

寄存器

0 0

0

IRR

中断申请

0 0

寄存器 0

0

PR

0

优先级

微机原理第八章:中断技术讲解

1.中断源识别

★ 软件查询法:

★ 中断矢量法:中断源提供中断类型号,CPU根据类型确定中断源 2.中断判优

★ 对同时产生的中断,首先处理优先级别较高的中断;

若优先级别相同,则按先来先服务的原则。

★ 对非同时产生的中断:

低优先级的中断程序允许被高优先级的中断源所中断

1.中断服务子程序的特点: 为“远过程”,用 IRET 指令返回

2.中断服务程序完成的工作

1)保护现场(通用寄存器的内容)

2)开中断(STI)

3)中断处理

4)关中断(CLI)

5)恢复现场 6)IRET

中断服务程序结构

保护有关寄存器内容 开中断

执行中断服务程序 关中断

恢复有关寄存器内容 执行IRET

精品资料

④ 执行 IRET 指令

4.退出中断(zhōngduàn) ① 关中断(zhōngduàn)

退

出

② 恢复现场中

③ 恢复断点 ④ 开中断(zhōngduàn) 断

精品资料

关中断 保存断点,保存现场

判别中断源 转入中断服务程序 保护寄存器、开中断 执行中断服务程序

IRET

关中断 恢复现场,恢复断点

开中断

STOSW

;串存储(字)

;AX→ES∶[DI]、 [DI+1]

MOV AX,SEG_INTR

;中断服务程序段基址送AX

STOSW

;串存储(字)

STI

;开中断

精品资料

2.用 MOV将直接(zhíjiē)中断向量写入中断向量表中

;将中断向量直接(zhíjiē)写入中断向量表中的程序段为

鲁滨逊漂流记第八章的好词好句好段

鲁滨逊漂流记第八章的好词好句好段全文共1篇示例,供读者参考好词摘抄:惊魂甫定怡然自得中庸克己妒火攻心心烦意乱郑重其事归心顿消闻所未闻油然升起难以抑制日趋淡薄九霄云外正直无私付诸实施满身黑斑冻饿之虞千里迢迢举目无亲悔恨不已仔细倾听逐浪飘流狂喜极悲大喜过望孤立无援搁浅、兜底、吞噬、烟搁浅、兜底、吞噬、烟波弥漫、泅水、山坳、恭顺、忏悔日晒雨淋夺眶而出好句摘抄:1、我感到自己前景暗淡。

因为,我被凶猛的风暴刮到这荒岛上,远离原定的航线,远离人类正常的贸易航线有数百海里之遥。

我想,这完全是出于天意,让我孤苦伶仃,在凄凉中了却余生了。

想到这些,我眼泪不禁夺眶而出。

有时我不禁犯疑,苍天为什么要这样作践自己所创造的生灵,害得他如此不幸,如此孤立无援,又如此沮丧寂寞呢!在这样的环境中,有什么理由要我们认为生活于我们是一种恩赐呢?2、我按上述条件去寻找一个合适的地点,发现在一个小山坡旁,有一片平地。

小山靠平地的一边又陡又直,像一堵墙,不论人或野兽都无法从上面下来袭击我。

在山岩上,有一块凹进去的地方,看上去好像是一个山洞的进口,但实际上里面并没有山洞。

3、事后想起来,我父亲最后这几句话,成了我后来遭遇的预言;当然我相信我父亲自己当时未必意识到有这种先见之明。

我注意到,当我父亲说这些话的时候,老泪纵横,尤其是他讲到我大哥陈尸战场,讲到我将来呼援无门而后悔时,更是悲不自胜,不得不中断了他的谈话。

最后,他对我说,他忧心如焚,话也说不下去了。

4、然后,我用从船上截下来的那些缆索,沿着半圆形,一层一层地堆放在两排木桩之间,一直堆到顶上,再用一些两英尺半高的木桩插进去支撑住缆索,仿佛柱子上的横茶。

这个篱笆十分结实牢固,不管是人还是野兽,都无法冲进来或攀越篱笆爬进来。

这项工程,花了我不少时间和劳力,尤其是我得从树林里砍下粗枝做木桩,再运到草地上,又一一把它们打入泥土,这工作尤其费力费时。

5、前面我已描述过自己的住所。

那是一个搭在山岩下的帐篷,四周用木桩和缆索做成坚固的木栅环绕着。

PIC单片机中断系统详细汇总

精选版课件ppt

9

§8.4 中断相关的寄存器

与中断有关的特殊功能寄存器SFR共有6个, 分别是:

选 项 寄 存 器 OPTION_REG 、 中 断 控 制 寄 存 器INTCON、第一外围设备中断标志寄存器PIR1、 第一外围设备中断屏蔽寄存器PIE1(也称中断使能 寄存器)、第二外围设备中断标志寄存器PIR2和第 二外围设备中断屏蔽寄存器PIE2,如表9.2所列。

1=选择RB0/INT上升沿触发;

精选版课件ppt

12

0=选择RB0/INT下降沿触发 ⒉中断控制寄存器INTCON

中断控制寄存器是一个可读/可写的寄存 器,各位的分布形式如下:

它将第一梯队中的3个中断源的标志位和屏 蔽位,以及PEIE和GIE包含在其中:

RBIF : 端 口 RB 的 引 脚 RB4 ~ RB7 电 平 变 化 中 断标志位。

TMR2IF:定时/计数器TMR2模块溢出中断标 志位。

➢ 1=发生了TMR2溢出; 0=未发生TMR2溢出。

CCP1IF:输入捕捉/输出比较/脉宽调制CCP1 模块中断标志位。

❖ 输入捕捉模式下:

1=发生了捕捉中断请求;

0=未发生捕捉中断请求。

精选版课件ppt

17

❖ 输出比较模式下: 1=发生了比较输出中断请求; 0=未发生比较输出中断请求。

后5个SFR,共有40位,但仅使用了30位来控 制中断,分别与图9.l中的中断逻辑电路的输入信 号成严格的对应关系。

精选版课件ppt

10

精选版课件ppt

11

⒈选项寄存器OPTION _REG

OPTION_REG选项寄存器是可读写的, 各位的分布形式:

该寄存器包含了与定时/计数器TMR0、 分频器和端口RB有关的控制位。RB端口引脚 RB0和外部中断INT复用一脚,与该脚有关的一 个控制位含义如下: INTEDG:外部中断INT触发信号边沿选择位:

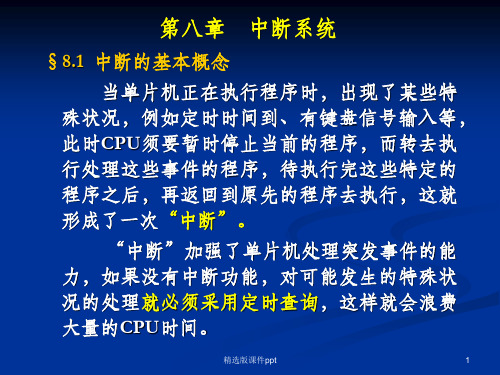

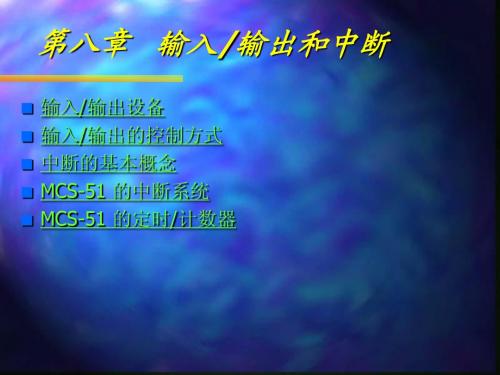

单片机_接口

输入/输出设备 输入/输出的控制方式 中断的基本概念 MCS-51 的中断系统 MCS-51 的定时/计数器

输入/输出设备

输入设备:

– 定义:往主机传送信息的设备 – 常用的输入设备:

键盘、鼠标、扫描仪、读卡机等

输出设备

– 定义:接收主机信息并送出信息呈现给人们的 设备 – 常用的输出设备:

MCS-51 的多中断源系统设计

MCS-51 的定时/计数器

定时/计数器结构 定时/计数器特相关的殊功能寄存器

– TMOD – TCON

定时/计数器工作方式

– – – – 方式 方式 方式 方式 0 1 2 3

MCS-51 的定时/计数器应用举例

RD

WR

movx A,@DPTR

movx @DPTR,A

AB

条件传送方式(查询方式)

CPU查询外设状态信息(Ready,Busy),条 件满足时,进行数据传送 程序简单 高速CPU查询低速外设 浪费CPU时间,效率低 输入接口原理图 输出接口原理图 程序流程图

中断方式

中断:要求继行输入、输出的外设,

中断入口地址表

中断源 入地址 同级中断 优先级

IE0 TF0 IE1 TR1 TI+ RI

0003H 000BH 0013H 001BH 0023H

MCS-51 的中断程序设计举例

ORG 0000H Ex1Svr: push PSW

+5V

P1.7

ajmp Main ORG 0003H

P1.4

CSAPP第八章

CSAPP第⼋章CSAPP第⼋章参考8.1异常异常是异常控制流的⼀种形式,⼀部分由硬件实现,⼀部分由操作系统实现a transfer of control to the OS kernel in responseto some event异常(exception)控制流的突变,⽤来响应处理器状态的某些变化。

事件(event)状态变化事件可能与当前执⾏指令有关存储器缺页,算数溢出除0也可能与当前执⾏指令⽆关I/O请求定时器产⽣信号通过异常表(exception table)的跳转表,进⾏间接过程调⽤(异常),到专门设计处理这种事件的操作系统⼦程序(异常处理程序(exception handler)异常处理程序在执⾏结束后,会发⽣以下三种情况之⼀:1. 返回应⽤程序当前指令Icurr2. 返回应⽤程序的下⼀条指令Inext3. 异常处理程序终⽌被中断的应⽤程序8.1.1 异常处理系统启动时,操作系统分配和初始化⼀张称为异常表的跳转表。

条⽬k包含异常k的处理程序的地址。

异常表的起始地址放在叫异常表基址寄存器的特殊CPU寄存器中。

异常类似过程调⽤,不过有以下不同过程调⽤,跳转到处理程序前,处理器将返回地址压⼊栈中。

对于异常,返回地址是当前,或下⼀跳指令。

处理器会把额外的处理器状态压⼊栈中。

如果控制⼀个⽤户程序到内核,那么所有这些项⽬会被压⼊内核栈中,⽽是⽤户栈。

异常处理程序运⾏在内核模式下,这意味他们对所有系统资源有完整访问权限。

8.1.2 异常的类别同步 synchronous 当⼀个⽅法被调⽤时,调⽤者需等待该⽅法执⾏完毕返回才能继续执⾏异步 asynchronous 当⼀个⽅法被调⽤时,⽴即返回,并获取⼀个线程执⾏该⽅法内部的业务,调⽤者不⽤等待该⽅法执⾏完毕1.中断中断异步发⽣,来⾃处理器外部的I/O设备的信号的结果硬件中断不是由任何⼀条专门的指令造成,从⼀定意义上时异步的。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

在一个微型计算机系统中,优先级常采用分层优先的方法。以16位机 为例,第一层优先是系统层的优先级,中断系统的优先次序依次为:

“3.优先级(权)分类”和P181 的”8.2.3 中断嵌套”综合 起来讲解的)

80X86系列微机通过8259A管理中断,它对优先级的管理

有几种不同的管理方式,下面对它们进行展开。 (1) 完全嵌套方式(固定优先级) (2) 特殊的完全嵌套方式 (3) 自动循环方式 (4) 特殊循环方式

(1) 完全嵌套方式(固定优先级) 这是单片8259A中断系统中最常见的优先级管理方式,IR0的

中断响应过程中CPU完成如下工作: 1)将中断类型码乘以4,得到中断向量在中断向量表的位置。 2)将FLAGS寄存器内容入栈保护。 3)将FLAGS中的IF和TF清0,禁止单步中断和任何可屏蔽中 断得到响应。

(4)特殊优先级自动循环方式

在上面的优先级自动循环方式中,初始的优先级与完全 嵌套方式完全一样,即IR0最高,IR7最低。而在特殊优先级 自动循环方式中,初始的优先级可以由程序员在对中断系统 初始化时指定。

8.2.2 CPU对可屏蔽中断的响应

这一部分的讨论仅限于通过INTR引脚向CPU提出中断请 求的硬件可屏蔽中断。

8.1 中断基础 (1)中断

中断是指CPU在运行程序时,由于一个事件的出现,致使CPU暂时中断正在执

行的程序,而去为事件服务(即执行中断服务程序),服务完毕,再返回被中断 的程序继续执行。

(2)中断源

这个事件可能是外部或内部的随机事件,也可能是由程序预先安排的事件。因

为这个事件会引起中断,所以又称为中断源。

第八章 中断和中断控制器

【内容提要]本章主要内容有三个:①中断基拙,这是为理解中断控制器和 中断系统的知识准备;②中断控制器的硬件和控制字,这是编程应用的基础, 既是难点,也是重点;③ CPU中断的管理。

【学习指导】本章的学习主要要抓住几个问题:①中断的全过程,着重理清 CPU-8259A一中断源(I/0设备)之间的联系;着重理清中断向量表、堆栈、存 储器之间的联系;着重理清主程序、中断服务程序、中断处理程序之间的联系; 也就是将I/O设备、中断控制器、CPU、中断响应周期、中断向量表、中断服 务程序等联系起来综合考虑。② 82C59A级联,32位机的82C59A是在级联方式 下工作的。③实验和应用

CPU总是在当前正在被执行指令的功能执行完毕时采样 INTR引脚,若INTR引脚为高电平,则说明有可屏蔽中断 请求发生,(相对于80X86计算机来说)这时若CPU的标 志寄存器的IF位被置1,则CPU必须响应该中断请求,CPU 执行一个中断响应周期。在这里,我们已经得出了CPU响 应可屏蔽中断的条件。

断请求。任一个分支程序段都要查询是否有本级中断请求,

如果有则转移至相关中断服务程序去处理;如果没有则进 人下一级查询。8分支程序是按优先级顺序连接的,CPU 查询的次序就是优先级的次序,最先查询的一定是优先级 最高的中断。如图8-4所示。

3. 优先级的几个不同的管理方式

(注意:这一部分的内容是将教材P180的

在2片以上的8259A组成级联的情况下,完全嵌套方式显然不适 用的,在这种情况下应当使用特殊完全嵌套方式。

(2)特殊完全嵌套方式 在完全嵌套方式的基础上作了一点点的修改,这个修

改同学们可能已经猜到了,即:允许同级中断相互打断。 例如在图8-20的情况下,我们应当将主8259A的优先

级方式设置成特殊完全嵌套方式,而将从8259A的优先级 设置成完全嵌套方式。

INTR中断是可以被CPU完全屏蔽的,这一类的中断也可以被8259中断控制 器部分屏蔽的。

2 . 中断系统

一个完整的计算机中断系统必须要有下面的几个模块。

(1)硬件系统

这一部分由外加的一片中断控制器芯片和CPU中的中断 控制逻辑所组成,它们的主要功能如下所述。

●中断控制器完成的功能主要是: 实现中断屏蔽,接受中断请求,进行中断联络,进行中

●CPU从发出第一个中断应答信号INTA开始直到从数据总线 上获得中断类型码为止的这一段时间称做中断响应周期。

● 从CPU得到中断类型码开始,到CPU执行中断服务程序第 一条指令前的这一时刻称中断响应过程。(P181)

●后面给出的中断响应周期图说明一次中断响应要经历二 个总线周期,图中的ALE信号在任何一个总线周期的第一 个时钟状态一定是有效的高电平,但这里并不存在要锁存 的地址信息,ALE时序线在这里的作用是标示总线周期的 起止位置。

●中断向量表位于内存最低端1024个字节处, 其中可存储256个中断服务子程序的入口地址, CPU响应中断时,从数据总线上得到中断向量 号,根据中断向量号,CPU可以很容易的从中 断向量表中得到中断服务子程序的入口地址。

8.1.2 中断类型

前面已经讲过,根据中断源在计算机系统中的位置不同,我们把中断分成外部 中断和内部中断两类。

(2)非屏蔽中断(不可屏蔽中断) 这是由非屏蔽中断控制线路产生的中断。当协处理器工作

异常或存储器奇偶校验出错时会产生NMI中断请求,此中断请 求通过非屏蔽中断控制线路用NMI向CPU请求中断。这种中断 不会被CPU的IF位所屏蔽(禁止),因此这种中断叫做非屏蔽 中断。非屏蔽中断一旦出现,CPU就会立即响应。

(3) 优先级自动循环方式 上面的两种方式的优先级是固定不变的,即IR0最高,IR7

最低,有的时候,我们认为这不太公平,比如在一个智能 抢答系统中,这个时候我们可以采用优先级自动循环方式。 在这个方式中,初始的优先级设置与完全嵌套方式一样, 即IR0最高,IR7最低,但在使用过程中这个优先级是会变 化的,如某一个中断源的中断请求被响应,那么下一次排 队时,这个中断源的级别就是最低的。而原先排在它后面 一个的中断源的优先级就是最高的。每一次都是这样操作 的。

断排序判优,传送中断类型码,实现中断嵌套,完成中断结 束等。 ●CPU中断控制逻辑在CPU功能中是隐含的。它的主要功能是: 允许/禁止中断请求,执行中断响应周期,保护中断断点, 关中断,转向中断服务程序执行等。

(2)软件系统

软件系统主要包含中断服务程序和中断 向量表这两个部分。

●中断服务程序是程序员事先写好的一个子 程序,它为某个特定的中断源服务,其核心 如右图中的中断处理部分,这一部分可以是 对I/O进行数据传送和处理,也可以是对某些 紧急事件进行应急处理,功能十分的丰富多 变。(要对右边流程图中的各个细分框图进 行说明。)

例如,要执行一条访存指令,若被访问的存储段不在内存中, 则发生“段不存在”的异常情况,于是将由INT13中断转去执 行相应的异常处理程序,以解决“段不存在”的问题。因此, 异常中断可用在系统保护和虚拟存储中。

在32位机中,将除数为零中断也归为异常中断。

8.1.3中断类型号 简称中断号,又称中断类型码。中断类型号是一个微

注:INTA、INTR 全部高电平有效,而中断响应输出为低电平有效进行分析。

(2)软件查询法 软件查询法通常是用于系统层的优先级排队,也可用于

可屏蔽中断。软件查询法也需要简单电路支持,但主要是 一个查询程序。这个查询线路由8级分支程序段组成,每 一个分支程序段相当于一级链路。每一级链路对应一级中

优先级最高,IR1次之,……IR7最低,同时若有多个中断源提 出中断请求,级别高的先响应,若已有一个中断服务子程序正

在执行中,这时若有其它的中断源提出中断请求,只有级别高

的可以打断级别低的从而实现中断嵌套,级别低的不能打断级 别高的,同级的也不能相互打断。

优先级一经设定,就不能更改。(除非你重新对8259A初始化)

在中断响应周期中,CPU和中断控制器互动过程如下:

1)CPU发出第一个INTA信号在第一个INTA到达8259A相应引 脚时,8259A对提出申请的若干个中断源进行判优排序,确定 优先级最高的那一个,将符合条件的中断源的中断类型号置 入中断类型码寄存器。

2)过一个总线周期之后,CPU发出第二个INTA信号,这个信 号到达8259A的相应引脚之后,8259A将其内部的中断类型号 寄存器中保存的中断号通过数据总线缓冲器送到系统数据总 线由CPU接收。

中断类型号0, 1, 3, 4为内部中断。 中断类型号2为非屏蔽中断。 中断类型号08一OFH为可屏蔽中断,分为8级,中断类型 号08H优先级最高,0FH最低。 中断类型号10H一IFH为指令中断,大致为BIOS调用。 中断类型号20H一FFH为指令中断,大致为DOS调用。

8.2 中断管理

8.2. 1 中断优先级管理

.外部中断

由CPU外部事件引起的中断就叫做外部中断,因为这是硬

件电路产生的中断,因此又称为硬件中断。硬件中断又分为 可屏蔽中断(INTR )与非屏蔽中断(NMI) 。

(1)可屏蔽中断 这是经由中断控制器(82C59A)转发的中断。I/O设备的 中断请求信号经82C59A用INTR线向CPU请求中断。CPU可 以用IF(=0)来屏蔽(禁止)它的中断请求,因此这种中断 叫做可屏蔽中断执行中断响应周期时发出两次中断应答(INTA)信号 予以响应,从而读取从82C59A送来的中断源的中断类型码。

(3)中断源的分类

中断源分成内部 (软件)中断和外部(硬件)中断两类, 内部中断分成指令中断(如INT 21H等)和故障中断两个子类 外部中断分成不可屏蔽中断(NMI )和可屏蔽中断(INTR )两个子类。 注:

指令中断(INT N)是程序员安排的,它发生在程序中位置是可知的,而硬 件中断和内部故障中断是随机的,不可以预知的。

● 指令中断

● 不可屏蔽中断

● 可屏蔽中断