主板相关信号详解

电脑主板线路图信号解释

I 热断路信号: 当THRMTRIP#信号为低电平型号时,从处理器发出热断路型号,ICH9马上转换为S5状态。ICH9将不等待来自处理器的准予停止的信号返回便进入S5状态。 SLP_S3# O S3 休眠控制信号: SLP_S3# 是电源层控制。

注释: 1. 在正常的三个RTC时钟周期里南桥使电源完全复位并生成完整的PLTRST#信号输出,PWROK必须是最小值处于无效状态。

PWROK必须无假信号,即使RSMRST#是低电平。

控制LINK电源正常信号:当CLPWROK有效时,表示从电源到控制LINK子系统(北桥、南桥等)是稳定的以及通知南桥使CL_RST#无效直到北桥收到这个信号在PWROK有效之后CLPWROK不许有效。

在桌面平台上这个信号能转换成为GPIO信号,这时它就不支持Intel AMT或者ASF。 BATLOW# (仅用于笔记本电脑) / TP0 (仅用于桌面电脑) I 电池低信号: 这个输入信号来自于笔记本电脑的电池组,当电池电量不足以维持系统发出一个信号。该信号有效时它会阻止系统从S3、S4、S5唤醒,也能引起一个SMI# 信号有效。 DPRSLPVR (仅用于笔记本电脑) / GPIO16 O 更深层睡眠-稳压信号:这个信号用于VRM在C4状态下将电压降到更低。当这个信号为高电平,稳压器输出更低的深睡眠电压。该信号为低电平时(默认值为低电平),稳压器输出正常的电压。(稳压器指VRM) DPRSTP# (仅用于笔记本电脑) / TP1 (仅用于桌面电脑) O 深度停机信号:这是DPRSLPVR信号的一个复制,低电平有效。在这1ms内PLT_RST#为低,而正是由于这1ms的低有效,系统才识别到PLT_RST#.该信号会对SIO,FWH,LAN,G(MCH),IDE,TPM等进行reset的动作.也就是说如果该信号异常,这些device都没办法被激活.该信号发出后立刻就会发出PCI_3S_RST#,可以当做是作用相似的第二次reset。

NB各种信号说明

主板上各种信号说明一、CPU接口信号说明1. A[31:3]# I/O Address(地址总线)ν这组地址信号定义了CPU的最大内存寻址空间为4GB.在地址周期的第一个子周期中,这些Pin传输的是交易的地址,在地址周期的第二个子周期中,这些Pin传输的是这个交易的信息类型.2. A20M# I Adress-20 Mask(地址位20屏蔽)ν此信号由ICH(南桥)输出至CPU的信号.它是让CPU在Real Mode(真实模式)时仿真8086只有1M Byte(1兆字节)地址空间,当超过1 Mbyte位空间时A20M#为Low,A20被驱动为0而使地址自动折返到第一个1Mbyte地址空间上.3.ADS#(ADS# 是RESET CPU後的第一個系統訊號去和北橋溝通)I/O Address Strobe(地址选通)ν当这个信号被宣称时说明在地址信号上的数据是有效的.在一个新的交易中,所有Bus上的信号都在监控ADS#是否有效,一但ADS#有效,它们将会作一些相应的动作,如:奇偶检查、协义检查、地址译码等操作.4. ADSTB[1:0]# I/O Address Strobesν这两个信号主要用于锁定A[31:3]#和REQ[4:0]#在它们的上升沿和下降沿.相应的ADSTB0#负责REQ[4:0]#和A[16:3]#,ADSTB1#负责A[31:17]#.5. AP[1:0]# I/O Address Parity(地址奇偶校验)ν这两个信号主要用对地址总线的数据进行奇偶校验.6.BCLK[1:0] I Bus Clock(总线时钟)这两个Clock主要用于供应在Host Bus上进行交易所需的Clock.ν7. BNR# I/O Block Next Request(下一块请求)ν这个信号主要用于宣称一个总线的延迟通过任一个总线代理,在这个期间,当前总线的拥有者不能做任何一个新的交易.8. BPRI# I Bus Priority Request(总线优先权请求)ν这个信号主要用于对系统总线使用权的仲裁,它必须被连接到系统总线的适当Pin .当BPRI#有效时,所有其它的设备都要停止发出新的请求,除非这个请求正在被锁定.总线所有者要始终保持BPRI#为有效,直到所有的请求都完成才释放总线的控制权.9. BSEL[1:0] I/O Bus Select(总线选择)ν这两组信号主要用于选择CPU所需的频率,下表定义了所选的频率:10. D[63:0]# I/O Data(数据总线)ν这些信号线是数据总线主要负责传输数据.它们提供了CPU与NB(北桥)之间64 Bit的通道.只有当DRDY#为Low时,总在线的数据才为有效,否则视为无效数据.11. DBI[3:0]# I/O Data Bus Inversion(数据总线倒置)ν这些信号主要用于指示数据总线的极性,当数据总在线的数据反向时,这些信号应为Low.这四个信号每个各负责16个数据总线,见下表:12. DBSY# I/O Data Bus Busy(数据总线忙)ν当总线拥有者在使用总线时,会驱动DBSY#为Low表示总线在忙.当DBSY#为High时,数据总线被释放.13. DP[3:0]# I/O Data Parity(数据奇偶校验)ν这四个信号主要用于对数据总在线的数据进行奇偶校验.14. DRDY# I/O Data Ready(数据准备)ν当DRDY#为Low时,指示当前数据总在线的数据是有效的,若为High时,则总在线的数据为无效.15. DSTBN[3:0]# I/O Data StrobeData strobe used to latch in D[63:0]#ν :16. DSTBP[3:0]# I/O Data StrobeData strobe used to latch inν D[63:0]# :17. FERR# O Floating Point Error(浮点错误)ν这个信号为一CPU输出至ICH(南桥)的信号.当CPU内部浮点运算器发生一个不可遮蔽的浮点运算错误时,FERR#被CPU驱动为Low.18. GTLREF I GTL Reference(GTL参考电压)这个信号用于设定GTLν Bus的参考电压,这个信号一般被设为Vcc电压的三分之二.19. IGNNE# I Ignore Numeric Error(忽略数值错误)ν这个信号为一ICH输出至CPU的信号.当CPU出现浮点运算错误时需要此信号响应CPU.IGNNE#为Low时,CPU会忽略任何已发生但尚未处理的不可遮蔽的浮点运算错误.但若IGNNE#为High时,又有错误存在时,若下一个浮点指令是FINIT、FCLEX、FSAVE等浮点指令中之一时,CPU会继续执行这个浮点指令但若指令不是上述指令时CPU会停止执行而等待外部中断来处理这个错误.20. INIT# I Initialization(初始化)ν这个信号为一由ICH输出至CPU的信号,与Reset功能上非常类似,但与Reset不同的是CPU内部L1 Cache和浮点运算操作状态并没被无效化.但TLB(地址转换参考缓存器)与BTB(分歧地址缓存器)内数据则被无效化了.INIT#另一点与Reset不同的是CPU必须等到在指令与指令之间的空档才会被确认,而使CPU进入启始状态.21. INTR I Processor Interrupt(可遮蔽式中断)ν这个信号为一由ICH输出对CPU提出中断要求的信号,外围设备需要处理数据时,对中断控制器提出中断要求,当CPU侦测到INTR为High时,CPU先完成正在执行的总线周期,然后才开始处理INTR中断要求.22. PROCHOT# I/O Processor Hot(CPU过温指示)ν当CPU的温度传感器侦测到CPU的温度超过它设定的最高度温度时,这个信号将会变Low,相应的CPU的温度控制电路就会动作.23. PWRGOOD(H_PWRGD)I Power Good(电源OK)ν这个信号通常由ICH(南桥)发给CPU,来告诉CPU电源已OK,若这个信号没有供到CPU,CPU将不能动作.24. REQ[4:0]# I/O Command Request(命令请求)ν这些信号由CPU接到NB(北桥),当总线拥有者开始一个新的交易时,由它来定义交易的命令.25. RESET# I Reset(重置信号)ν当Reset为High时CPU内部被重置到一个已知的状态并且开始从地址0FFFFFFF0H读取重置后的第一个指令.CPU 内部的TLB(地址转换参考缓存器)、BTB(分歧地址缓存器)以及SDC(区段地址转换高速缓存)当重置发生时内部数据全部都变成无效.26. RS[2:0]# I Response Status(响应状态)ν这些信号由响应方来驱动,具体含义请看下表:27. STKOCC# O Socket Occupied(CPU插入)ν这个信号一般由CPU拉到地,在主机板上的作用主要是来告诉主机板CPU是不是第一次插入.若是第一次插入它会让你进CMOS对CPU进行重新设定.28. SMI# I System Management Interrupt(系统管理中断)ν此信号为一由ICH输出至CPU的信号,当CPU侦测到SMI#为Low时,即进入SMM模式(系统管理模式)并到SMRAM(System Management RAM)中读取SMI#处理程序,当CPU在SMM模式时NMI、INTR及SMI#中断信号都被遮蔽掉,必需等到CPU执行RSM(Resume)指令后SMI#、NMI及INTR中断信号才会被CPU认可.29. STPCLK# I Stop Clock(停止时钟)ν当CPU进入省电模式时,ICH(南桥)将发出这个信号给CPU,让它把它的Clock停止.28. TRDY# I/O Target Ready(目标准备)ν当TRDY#为Low时,表示目标已经准备好,可以接收数据.当为High时,Target没有准备好.29. VID[4:0](CPU核心工作电压) O Voltage ID(电压识别)ν这些讯号主要用于设定CPU的工作电压,二、VGA接口信号说明1. HSYNC O CRT Horizontal Synchronization(水平同步信号)ν这个信号主要提供CRT水平扫描的信号.2. VSYNC O CRT Vertical Synchronization(垂直同步信号)这个信号主要提供CRT垂直扫描的信号.ν3. RED O RED analog video output(红色模拟信号输出)ν这个信号主要为CRT提供红基色模拟视频信号.4. GREEN O Green analog video output(绿色模拟信号输出)这个信号主要为CRT提供绿基色模拟视频信号.ν5. BLUE O Blue analog video output(蓝色模拟信号输出)ν这个信号主要为CRT提供蓝基色模拟视频信号.6. REFSET I Resistor Set(电阻设置)ν这个信号将会连接一颗电阻到地,主要用于内部颜色调色板DAC.这颗电阻的阻值一般为169奥姆,精度为1%.7. DDCA_CLK I/O Analog DDC Clockν这个信号连接NB(北桥)与显示器,这个Clock属于I²C接口,它与DDCA_DATA组合使用,用于读取显示器的数据.8. DDCA_DATA I/O Analog DDC Clockν这个信号连接NB(北桥)与显示器,这个Data与Clock 一样也属于I²C接口,它与DDCA_CLK组合使用,用于读取显示器的数据.三、AGP接口信号说明1. GPIPE# I/O Pipelined Read(流水线读)ν这个信号由当前的Master来执行,它可以使用在AGP 2.0模式,但不能在AGP 3.0的规范使用.在AGP 3.0的规范中这个信号由DBI_HI(Dynamic Bus Inversion HI)代替.2. GSBA[7:0] I Sideband Address(边带地址)这组信号提供了一个附加的总线去传输地址和命令从AGPν Master(显示卡)到GMCH(北桥).3. GRBF# I Read Buffer Full(读缓存区满)这个信号说明Master是否可以接受先前以低优先权请求的要读取的ν数据.当RBF#为Low时,中裁器将停止以低优先权去读取数据到Master.4. GWBF# I Write Buffer Full(写缓存区满)ν这个信号说明Master是否可以准备接受从核心控制器的快写数据.当WBF#为Low时,中裁器将停止这个快写数据的交易.5. ST[2:0] O Status Bus(总线状态)ν这组信号有三BIT,可以组成八组,每组分别表示当前总线的状态.6. ADSTB0 I/O AD Bus Strobe 0(地址数据总线选通)这个信号可以提供2X的时序为AGP,它负责总线AD[15:0].ν7. ADSTB0# I/O AD Bus Strobe 0(地址数据总线选通)ν这个信号可以提供4X的时序为AGP,它负责总线AD[15:0].8. ADSTB1 I/O AD Bus Strobe 1(地址数据总线选通)这个信号可以提供2X的时序为AGP,它负责总线AD[31:16].ν9. ADSTB1# I/O AD Bus Strobe 1(地址数据总线选通)ν这个信号可以提供4X的时序为AGP,它负责线总AD[31:16].10. SB_STB I SideBand Strobe(SideBand选通)这个信号主要为SBA[7:0]提供时序,它总是由AGPν Master驱动.11. SB_STB# I SideBand Strobe(SideBand选通)这个信号为SBA[7:ν0]提供时序只在AGP 4X 模式,它总是由AGP Master驱动.12. CLK O CLOCK(频率)ν为AGP和PCI控制信号提供参考时序.13. PME# Power Management Event(电源管理事件)这个信号在AGPν协议中不使用,但是它用在PCI协议中由操作系统来管理.关于PME#的详细定义请参加PCI协议规范.14. TYPEDET# Type Detect(类型检查)ν从AGP发展来看,有1X、2X、4X和8X四种模式,每种模式所使用的电压也不尽相同,那AGP控制器怎么知到你插的是什么样的显卡呢?就是通过这个信号来告诉AGP Control的.用这个信号来设定当前显卡所需的电压.15. FRAME# I/O Frame(周期框架)在AGP管道传输时这个信号不使用,这个信号只用在AGP的快写方式.ν16. IRDY# I/O Initiator Ready(起始者备妥)这个信号说明AGPν Master已经准备好当前交易所需的数据,它只用在写操作,AGP Master不允许插入等待状态. 17. TRDY# I/O Target Ready(目标备妥)这个信号说明AGPν Target已经准备好整个交易所需要读的数据,这个Target可以插入等待状态.18. STOP# I/O Stop(停止)ν这个信号在AGP交易时不使用.对于快写方式,当STOP#为Low时,停止当前交易.19. DEVSEL# I/O Device Select(设备选择)ν在AGP交易时不使用.在快写方式,当在一个交易不能完成时,它就会被使用.20. REQ# I Request(请求)这个信号用于向中裁器请求当前总线使用权为开始一个PCI orν AGP交易.21. GNT# O Grant(保证)ν当中裁器收到Initiator发出请求后,若当前总线为空闲,中裁器就会通过GNT#把总线控制权交给Initiator.22. AD[31:0] I/O Address Data Bus(数据地址总线)ν这些信号用来传输地址和数据.23. C/BE[3:0]# I/O Command/Byte Enable(命令/位致能)当一个交易开始时,提供命令信息.在AGPν Master做写交易时,提供有效的位信息.四、Memory 接口信号说明1. SCMDCLK[5:0] O Differential DDR Clock(时钟输出)ν SCMDCLK与SCMDCLK#是差分时钟输出对,地址和控制信号都在这个两个Clock正负边沿的交叉点采样.每个DIMM 共有三对.2. SCMDCLK[5:0]# O Differential DDR Clock(时钟输出)ν这个Clock信号的意义同上.3. SCS[3:0]# O Chip Select(芯片选择)当这些信号有效时,表示一个Chip已被选择了,每个信号对应于SDRAM的一行.ν4. SMA[12:0] O Memory Address(内存地址)ν这些信号主要用于提供多元的行列地址给内存.5. SBA[1:0] O Bank Address(Bank选择)ν这个些信号定义了在每个内存行中哪个Bank被选择.Bank选择信号和内存地址信号联合使用可寻址到内存的任何单元.6. SRAS# O Row Address(行地址)ν行地址,它和SCAS#、SWE#一起使用,用来定义内存的命令.7. SCAS# O Column Address(列地址)ν列地址,它和SRAS#、SWE#一起使用,用来定义内存的命令.8. SWE# O Write Enable(写允许)写允许信号,它与SRAS#、SCAS#一起使用,用来定义内存的命令.ν9. SDQ[63:0] I/O Data Lines(数据线)ν这些信号线用于传输数据.10. SDM[7:0] O Data Mask(数据屏蔽)当在写周期有效时,在内存中传输的数据被屏蔽.在这八个信号中每个信号负责八根数据线.ν11. SDQS[7:0] I/O Data Strobe(数据选通)ν这些信号主要用于捕获数据.这八个信号每个信号负责八根数据线.12. SCKE[3:0] O Clock Enable(时钟允许)这个信号在上电时对内存进行初始化,它们也可以用于关闭不使用的内存数据行. ν五、HUB 接口信号说明1. HL[10:0] I/O Packet Data(数据包)这些信号主要用于Hub Interface读写操作时传输数据.ν2. HISTRS I/O Packet Strobe(数据选通)3. HISTRF I/O Packet Strobe Complement这个信号与HISTRS一起在HUBν inteface上传输与接收数据.六、LAN LINK接口信号说明1. LAN_CLK I Lan I/F Clock(网络时钟)这个信号由Lanν Chipset驱动输出,它的频率范围在5~50Mhz.2. LAN_RXD[2:0] I Received Data(接收数据)这些信号是由Lan Chipset驱动输出到南桥.ν3. LAN_TXD[2:0] O Transmit Data(传输数据)这些信号是南桥驱动输出到Lan Chipset.ν4. LAN_RSTSYNC O Lan Reset(Lan Chip 复位信号)七、EEPROM 接口信号说明1. EE_SHCLK O EEPROM Shift Clock(EEPROM时钟)ν这个信号由南桥驱动输出到EEPROM.2. EE_DIN I EEPROM Data In(EEPROM数据输入)这个信号是由EEPROM传数据到南桥.ν3. EE_DOUT O EEPROM Data Out(EEPROM数据输出)ν这个信号是由南桥传数据到EEPROM.4. EE_CS O EEPROM Chip Select(片选信号)当这个信号有效时EEPROM被选择.ν八、PCI接口信号说明1. AD[31:0] I/O Address Data Bus(地址数据总线)ν是用来传送起始地址.在内存或组态的交易期间,此地址的分辨率是一个双字组(Double Word)(即地址可被四整除),在读取或写入的交易期间,它是一个字节特定地址.2. PAR I/O Parity Signal(同位信号)ν在地址阶段完成后一个频率,或是所有写入交易的数据阶段期间,在IDRY#被驱动到僭态后一个频率,由Initiator驱动.所有读取交易的数据阶段期间,在TRDY#被驱动到僭态后一个频率,它也会被目前所寻址的Target驱动.在地址阶段完成后的一个频率,Initiator将PAR驱动到高或低态,以保证地址总线AD[0:31]与四条指令/位组致能线C/BE#[0:3]是偶同位(Even Parity).3. C/BE[3:0]# I/O Command/Byte Enable(指令或字节致能)由Initiator驱动,在AD Bus上传输地址时,用来表示当前要动作的指令.在ADν Bus上传输数据时,用来表示在目前被寻址之Dword 内将要被传输的字节,以及用来传输数据的数据路径.4. RST# O PCI Reset(复位信号)当重置信号被驱动成低态时,它会强迫所有PCI组态缓存器νMaster及Target状态机器与输出驱动器回到初始化状态.RST#可在不同步于PCI CLK边缘的状况下,被驱动或反驱动.RST#的设定也将其它的装置特定功能初始化,但是这主题超出PCI规格的笵围.所有PCI输出信号必须被驱动成最初的状态.通常,这表示它们必须是三态的.5. FRAME# I/O Cycle Frame(周期框架)ν是由目前的Initiator驱动,它表示交易的开始(当它开始被驱动到低态时)与期间(在它被驱动支低态期间).为了碓定是否已经取得总线拥有权,Master必须在同一个PCI CLK信号的上边缘,取样到FRAME#与IRDY#都被反驱动到高态,且GNT#被驱动到低态.交易可以是由在目前的Initiator与目前所寻址的Target间一到多次数据传输组成.当Initiator准备完成最后一次数据阶段时,FRAME#就会被反驱动到高态.6. IRDY# I/O Initiator Ready(备妥)Initiatorν备妥被目前的Bus Master(交易的Initiator)驱动.在写入期间,IRDY#被驱动表示Initiator准备接收从目前所寻址的Target传来的资料.为了确定Master已经取得总线拥有权,它必须在同一个PCI CLK信号的上升边缘,取样到FRAME#与IRDY#都被反驱动到高态,且GNT#被驱动到低态.7. TRDY# I/O Target Ready(目标备妥)ν Target备妥被目前所寻址的Target驱动.当Target准备完成目前的数据阶段(数据传输)时,它就会被驱动到低态.如果在同一个PCI CLK信号的上升边缘,Target 驱动TRDY#到低态且Initiator驱动IDRY#到低态的话,则此数据阶段便告完成.在读取期间,TRDY#被驱动表示Target正在驱动有效的数据到数据总线上.在写入期间,TRDY#被驱动表示Target准备接收来自Master的资料.等待状态会被插入到目前的资料阶段里,直到取样到TRDY#与IRDY#都被驱动到低态为止.8. STOP# I/O Stop(停止)ν Target驱动STOP#到低态,表示希望Initiator停止目前正在进行的交易.9. DEVSEL# I/O Device Select(设备选择信号)ν该信号有效时,表示驱动它的设备已成为当前防问的目标设备.换言之,该信号的有效说明总在线某处的某一设备已被选中.如果一个主设备启动一个交易并且在6个CLK周期内设有检测到DEVSEL#有效,它必须假定目标设备没能反应或者地址不存在,从而实施主设备缺省.10. IDSEL I Initialization Device Select(初始化设备选择)IDSEL是PCI装置的一个输入端,并且在存取某个装置的组态缓存器期间,它用来选择芯片.ν11. LOCK# I/O Lock(锁定)ν这是在一个单元(Atomic)交易序列期间(列如:在读取/修改/写入操作期间),Initiator用来锁定(Lock)目前所寻址的Target的.12. REQ# I Request(请求)ν表示管理者要求使用总线,此为一对一之信号,每一管理者都有与其相对应之REQ#信号.13. GNT# O Grant(保证)ν表示管理者对总线使用之要求已被同意,此为一对一之信号,每一管理者都有与其相对应之GNT#信号.九、Serial ATA接口信号说明1. SATA0TXP O Serial ATA 0 Transmit(串行ATA0 传送)2. SATA0TXN O Serial ATA 0 Transmit(串行ATA0 传送)这个信号与SATA0TXP组成差分信号对,用于传输数据.ν3. SATA0RXP I Serial ATA 0 Receive(串行ATA0 接收)4. SATA0RXN I Serial ATA 0 Receive(串行ATA0 接收)ν这个信号与SATA0RXP组成差分信号对,用于接收数据.5. SATARBIAS I Serial ATA Resistor Bias(串行ATA电阻偏置)6. SATARBIAS# I Serial ATA Resistor Bias(串行ATA电阻偏置)这个信号与SATARBIAS一样外接一颗与GND相接的电阻,为SATA提供一个电压偏置. ν7. SATALED# OD SATA Drive Activity Indicator(SATA 读写指示)ν当这个信号为Low时,表示当前的SATA硬盘正在读写数据.十、IDE 接口信号说明1. DCS1# O Device Chip Select(设备芯片选择)ν这个信号为设备选择信号For Rang 100 .2. DCS3# O Device Chip Select(设备芯片选择)这个信号为设备选择信号For Rang 300.ν3. DA[2:0] O Device Address(设备地址)这些信号用于传输地址信号.ν4. DD[15:0] I/O Device Data(设备数据)ν这些信号用于传输数据信号.5. DREQ I Device Request(设备请求)当IDE Device要做一个DMA读写动作时,就会驱动这个信号向南桥发DMνA请求.6. DACK# O Device DMA Acknowledge(设备DMA确认)当IDEν Device已做了一个DMA请求后,若当前总线空闲,南桥就会驱动个信号,把控制权受权给IDE Device.7. DIOR# O Disk I/O Read(磁盘I/O读)ν这个信号由南桥来驱动,当它有效时,表示要对磁盘进行一个读操作.8. DIOW# O Disk I/O Write(磁盘I/O写)这个信号由南桥来驱动,当它有效时,表示要对磁盘进行一个写操作.ν9. IORDY I I/O Channel Ready(I/O通道备妥)这个信号由IDEν Device来驱动,当它有效时,表示IDE Device已经准备OK.十一、LPC接口信号说明1. LAD[3:0] I/O LPC Command、Address、Data这四信号线用来传输LPCν Bus的命令、地址和数据.2. LFRAME# I/O LPC Frame(LPC框架)ν当这个信号有效时,指示开始或结束一个LPC周期.3. LDRQ# I DMA Request(DMA请求)当Super I/O上的Device需要用DMA Channel时,就会驱动这个信号向南桥发出请求. ν十二、USB 接口信号说明1. USBP+ I/O USB Signal(USB 信号)2. USBP- I/O USB Signal(USB 信号)ν这个信号与USBP+组成差分信号对,组成一个USB Port,用来传输地址、数据和命令.3. OC# I Over Current(过电流保护)当有USBν Device过电流时,这个信号会拉Low,告知南桥有过电流发生.十三、SMBus接口信号说明1. SMBDATA I/O SMBus Data(数据线)2. SMBCLK I/O SMBus Clock(时钟线)ν上面两个信号线为系统管理总线,以南桥为控制中心,对主机板的一些Device进行读写操作,如时钟IC、SPD(SPD是一组关于内存模组的配置信息)等等.这两个信号在外部必须通过电阻进行Pull High.十四、AC-Link接口信号说明1. RST# O Reset(复位信号)这个讯信号由南桥驱动,对Audioν Chip进行初始化.2. SYNC O Sync(同步信号)3. BIT_CLK I Bit Clock(时钟输入)ν这是一个由Codec产生一个12.288Mhz串行数据时钟给南桥.4. SDOUT O Serial Data Out(串行数据输出)由南桥发出数据到Codec.ν5. SDIN I Serial Data In(串行数据输入)ν由Codec发出数据到南桥.十五、FDC接口信号说明1. DRVDEN0 OD Drive Density Select Bit(驱动器密度选择位)ν驱动器密度选择信号.2. INDEX# I INDEX(索引)ν此Pin为施密特触发器输入,当这个为Low(有效时),通过索引孔把磁头定位起始磁道.3. MOA# OD Motor A On(马达A打开)当此信号为Low时,马达A起动.ν4. DSA# OD Drive Select A(驱动A选择)当此信号为Low时,驱动器A被选择.ν5. DIR# OD DIR(列目录)ν磁头步进马达移动方向,为High时,向外移动,为Low时向内移动.6. STEP# OD Step(步进)步进输出脉冲,当此信号为Low时,将产生一个脉冲移动磁头到另一个磁道.ν7. WD# OD Write Data(写数据)ν写数据,当此信号为Low时,写数据到被选择的驱动器.8. WE# OD Write Enable(写允许)写允许,当为Low表示允许写入盘片.ν9. TRACK0# I Track 0(0磁道)0磁道,当此信号为Low时,磁头将被定位到最外的一个磁道(0磁道).ν10. WP# I Write Protected(写保护)ν写保护,当此信号为Low时,磁盘片被写保护,只能读出数据不能写入.11. RDATA# I Read Data(读数据)当为Low时从软盘读数据.ν12. HEAD# OD Head(磁头)磁头选择,当为High时选择0面的磁头,当为Low时选择1面的磁头.ν13. DSKCHG# I Diskette Change(更换磁盘)ν盘片更换,当此信号为Low时,在上电状态可随时取出盘片.十六、Parallel Port 接口信号说明1. SLCT I Printer Select Status(打印机状态选择)ν这个Pin主要用于选择打印机模式,为High时,表示打印机被选择.打印有两种模式可以被设定ECP和EEP.2. PE I Page End(页面结束)当这个信号为High时,表示打印机已检测到页面结束.ν3. BUSY I Busy(打印机忙)ν当这个信号为High时,表示打印机很忙没有准备去接收数据.4. ACK# I Acknowledge(确认)当这个信号为Low时,表示打印机已接收数据,并准备接受更多的数据.ν5. ERR# I Error(错误)ν当这个信号为Low时,表示打印机在打印时出错.6. SLIN# O Printer Select(打印机选择)这个信号为打印机输出线检查.ν7. INIT# O Initialization(初始化)当这个信号为Low时,表示对打印机进行初始化.ν8. AFD# O Auto Line Feed(自动走线)ν当打印机打印针出问题时,这个信号会被拉Low,打印机会自动再打一遍.9. STB# O Strobe(锁定)当这个信号为Low时,表示要把并行数据锁定到打印机里.ν10. PD[7:0] I/O Printer Data(打印机数据)ν这些信号用于传输打印机数据.十七、Serial Port 接口数据说明1. CTS# I Clear To Send(清楚发送)ν这个信号用于Modem控制输入,这个功能可以通过读握手状态寄存器Bit 4来测试.2. DSR# I Data Set Ready(数据准备)这个信号为Low时,表示Modem或数据放置已准备可以传输数据.ν3. RTS# I/O Request To Send(请求发送)ν这个信号为Low时,表示Modem或调制解调器可准备去发送数据.4. DTR# I/O Data Terminal Ready(数据终端准备)这个信号为Low时,表示数据终端已准备可以进行通信.ν5. SIN I Serial Data In(串行数据输入)ν这个信号用于去接收数据.6. SOUT O Serial Data Out(串行数据输出)这个信号用于去发送数据.ν十八、开机重要信号说明RSMRST#:RSMRST#信号是用来通知南桥5VSB和3VSB待机电压正常的信号,这个信号如果为低,则南桥收到错误的信息,认为相应的待机电压没有OK,所以不会进行下一步的上电动作SLP_S3#:S3 休眠控制信号: SLP_S3# 是电源层控制。

pwrbtn信号分析

电脑主板工作信号名词解释之PWRBTN#及IO_PWRBTN#

PWRBTN 主板上电时的一个信号,即电脑开关就是这个信号,在电脑接通电源的时候,

3VSB或5VSB通过一个4.7K或8.2K等的电阻给该信号提供上拉,所以在接通电源时该信号的电压是3.3V或5V的高电平,

而按下开关的时候该信号变为0V低电平(开关的另一端是接地的,按下开关时就是把PWRBTN信号接到地上了),

然后松开开关PWRBTN又回到3.3V或5V的高电平。

这一高低高的变化信号会送给IO或南桥或其它专门的开机复位芯片(有些中间会有一些电阻或门芯片中转一下)

IO或南桥或其它专门的开机复位芯片收到这一个方波信号后(在其它工作条件正常的情况下)就会发出下一步的工作信号(IO_PWRBTN)

IO_PWRBTN 就是IO收到开关信号后发出的一个同PWRBTN#一样的高低高变化的方波信号,这个信号送给南桥通知南桥开机

PWRBTN#及IO_PWRBTN#这个名称并不是唯一的在不同的电图图上标示的可能不一样,仅供参考!

PWRBTN#信号波形

PWRBTN#与IO_PWRBTN#波形关系。

主板信号

主板上各种信号说明一2007年08月26日星期日 13:20六、LAN LINK接口信号说明1. LAN_CLK I Lan I/F Clock(网络时钟)这个信号由Lann Chipset驱动输出,它的频率范围在5~50Mhz。

2. LAN_RXD[2:0] I Received Data(接收数据)这些信号是由Lan Chipset驱动输出到南桥。

n3. LAN_TXD[2:0] O Transmit Data(传输数据)这些信号是南桥驱动输出到Lan Chipset。

n4. LAN_RSTSYNC O Lan Reset(Lan Chip 复位信号)七、EEPROM 接口信号说明1. EE_SHCLK O EEPROM Shift Clock(EEPROM时钟)n 这个信号由南桥驱动输出到EEPROM。

2. EE_DIN I EEPROM Data In(EEPROM数据输入)这个信号是由EEPROM传数据到南桥。

n3. EE_DOUT O EEPROM Data Out(EEPROM数据输出) n 这个信号是由南桥传数据到EEPROM。

4. EE_CS O EEPROM Chip Select(片选信号)当这个信号有效时EEPROM被选择。

n八、PCI接口信号说明1. AD[31:0] I/O Address Data Bus(地址数据总线)n 是用来传送起始地址。

在内存或组态的交易期间,此地址的分辨率是一个双字组(Double Word)(即地址可被四整除),在读取或写入的交易期间,它是一个字节特定地址。

2. PAR I/O Parity Signal(同位信号)n 在地址阶段完成后一个频率,或是所有写入交易的数据阶段期间,在IDRY#被驱动到僭态后一个频率,由Initiator驱动。

所有读取交易的数据阶段期间,在TRDY#被驱动到僭态后一个频率,它也会被目前所寻址的Target驱动。

主板RESET信号介绍

主板上電時序

POST: Power On Self Test, 即主板開機自檢過程.主要任務是用來測試安裝於主機板上的各種硬體,如偵測到有硬體錯誤,即會依主機板廠商設計發出警示聲,或是產生Post Error Code輸出至位址Port 80H HA HD DMI LPC

RESET相關信號

PWRBTN#: (Power Button) 電源按鈕, 如果系統處在睡眠狀態,那麼按下此按鈕後將會喚醒系統(開機). 此信號如果按下超過4S, 將會無條件進入S5狀態.

RESET相關信號

NOTES: 除非Cleared CMOS, 當RTC電源OK後,此信號必須保持高電平. 如果主板上RTC電池漏裝或NG, RTCRST#信號必須在RSMRST#之前至high.

PWROK_3V

PWRGD_PS

ATX_PSON#

RSMRSH_PLTRST#

PIDE_PRST#

PCIE_RST_SLOT#

PCIE_RST_SLOT#

PCI_RST_SLOT#

PCI_RST_SLOT#

CPUPWRGD#

ICH_PLTRST#

CPURESET#

RESET相關信號

VRMPWRGD:(VRM Power Good) 此信號為VCORE電源管理芯片發出, 以通知南橋CPU VCORE電壓已經穩定.

RESET相關信號

SYSRESET#: (System Reset) 系統RESET信號, 當此信號被拉低時系統將被直接Reset. 在被reset之前,系統將會等待25ms ±2ms 讓SMBus 空閒.

笔记本主板信号详解

一 主板各芯片的功能及名词解释主板芯片组(chipset )(pciset) :分为南桥和北桥:分为南桥和北桥南桥(主外):即系统I/O 芯片(SI/O ):主要管理中低速外部设备;集成了中断控制器、DMA 控制器。

功能如下:功能如下:PCI 、ISA 与IDE 之间的通道。

之间的通道。

PS/2鼠标控制。

(间接属南桥管理,直接属I/O 管理)管理) KB 控制(keyboard )。

(键盘) USB 控制。

(通用串行总线)控制。

(通用串行总线) SYSTEM SYSTEM CLOCK CLOCK 系统时钟控制。

系统时钟控制。

I/O 芯片控制。

芯片控制。

ISA 总线。

总线。

IRQ 控制。

(中断请求)控制。

(中断请求) DMA 控制。

(直接存取)控制。

(直接存取) RTC 控制。

控制。

IDE 的控制。

的控制。

南桥的连接:南桥的连接: ISA ISA——PCI CPU CPU——外设之间的桥梁外设之间的桥梁 内存—外存外存北桥(主内):系统控制芯片,主要负责CPU 与内存、CPU 与AGP 之间的通信。

掌控项目多为高速设备,如:CPU 、Host Host Bus Bus 。

后期北桥集成了内存控制器、Cache 高速控制器;功能如下:高速控制器;功能如下: CPU 与内存之间的交流。

与内存之间的交流。

Cache 控制。

控制。

AGP 控制(图形加速端口)控制(图形加速端口) PCI 总线的控制。

总线的控制。

CPU 与外设之间的交流。

与外设之间的交流。

支持内存的种类及最大容量的控制。

(标示出主板的档次)内存控制器:决定是否读内存(高档板集成于北桥)。

586FX 82438FX VX 82438VX Cache :高速缓冲存储器。

:高速缓冲存储器。

(1)、high high——speed 高速高速 (2)、容量小)、容量小主要用于CPU 与内存北桥之间加速(坏时死机,把高速缓冲关掉)CPU Cache 内 存 I/O 芯片input/output ,(局部I/O )。

主板相关信号详解

主板相关信号详解1.A[31:3]# (I/O) Address(地址总线)& l1 f t$ r$ E$ |这组地址信号定义了CPU的最大内存寻址空间为4GB。

在地址周期的第一个子周期中,这些Pin传输的是交易的地址,在地址周期的第二个子周期中,这些Pin传输的是这个交易的信息类型。

9 S5 a9 [1 K8 D' o1 _" p+ ?2.A20M# (I) Adress-20 Mask(地址位20屏蔽)此信号由ICH(南桥)输出至CPU的信号。

它是让CPU在Real Mode(真实模式)时仿真8086只有1M Byte(1兆字节)地址空间,当超过1 Mbyte位空间时A20M#为Low,A20被驱动为0而使地址自动折返到第一个1Mbyte地址空间上。

3.ADS# (I/O) Address Strobe(地址选通)当这个信号被宣称时说明在地址信号上的数据是有效的。

在一个新的交易中,所有Bus上的信号都在监控ADS#是否有效,一但ADS#有效,它们将会作一些相应的动作,如:奇偶检查、协义检查、地址译码等操作。

: g: V6 P; l- w; J: K+ @' _4.ADSTB[1:0]# (I/O) Address Strobes" w5 l5 W: j% m, W" n% H这两个信号主要用于锁定A[31:3]#和REQ[4:0]#在它们的上升沿和下降沿。

相应的ADSTB0#负责REQ[4:0]#和A[16:3]#,ADSTB1#负责A[31:17]#。

# ]' K8 c$ O6 a- F- d* e% P5.AP[1:0]# (I/O) Address Parity(地址奇偶校验)这两个信号主要用对地址总线的数据进行奇偶校验。

6.BCLK[1:0] (I) Bus Clock(总线时钟)这两个Clock主要用于供应在Host Bus上进行交易所需的Clock。

主板信号说明

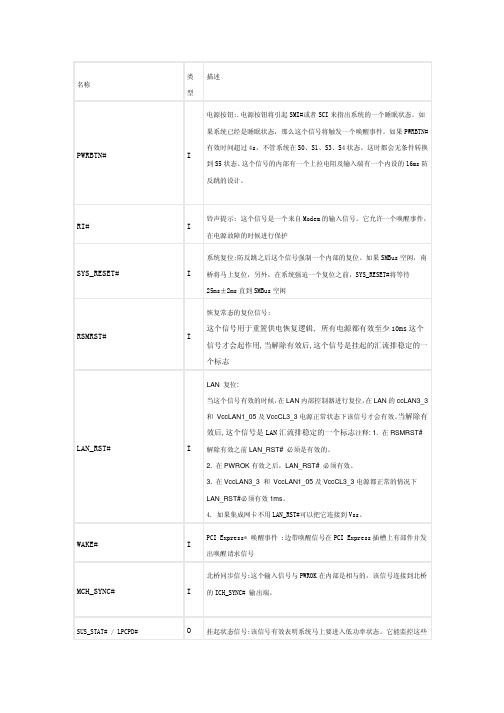

PWRBTN# RI# SYS_RESET# RSMRST#

LAN_RST#

WAKE# MCH_SYNC#

SUS_STAT# / LPCPD#

类 描述 型

电源按钮:.电源按钮将引起 SMI#或者 SCI 来指出系统的一个睡眠状态。如 果系统已经是睡眠状态,那么这个信号将触发一个唤醒事件。如果 PWRBTN# 有效时间超过 4s,不管系统在 S0、S1、S3、S4 状态,这时都会无条件转换

S3 休眠控制信号: SLP_S3# 是电源层控制。 , P( A* q! m 0 i( t . i" e

O 当进入 S3(挂起到内存)、S4(挂起到硬盘)、S5(软关机)状态时这个

信号关掉所有的非关键性系统电源。

SLP_S4#

S4 休眠控制信号: SLP_S4# i 是电源层控制信号. 当进入 S4(挂起到硬 盘)、S5(软关机)状态时这个信号关掉所有的非关键性系统电源。

I

到 S5 状态。这个信号的内部有一个上拉电阻及输入端有一个内设的 16ms 防 反跳的设计。

铃声提示: 这个信号是一个来自 Modem 的输入信号。它允许一个唤醒事件,

I

在电源故障的时候进行保护

系统复位:防反跳之后这个信号强制一个内部的复位。如果 SMBus 空闲,南

I 桥将马上复位,另外,在系统强迫一个复位之前,SYS_RESET#将等待

总复位信号: PLTRST#是 Intel® ICH9 整个平台的总复位(如:I/O、 BIOS 芯片、网卡、 北桥等等)。在加电期间及当 S/W 信号通过复位控制寄存器 (I/O 寄存器 CF9h)初始化一个硬复位序列时 ICH9 确定 PLTRST#的状

O 态。在 PWROK 和 VRMPWRGD 为高电平之后 ICH9 驱动 PLTRST#最少 1

常用主板信号名词,电子缩写解释.

ADJ 可调 Adjustable 比如大小和方向控制的意思是通断了VID 电压识别 Voltage IdentificationSS 软启动 (soft Start两个单词的缩写FB 反馈 (feedback单词的缩写COMP 补偿 (Compensatory单词的缩写VSEN 电压侦测 voltage senserISP 电流侦测 p 正端与 isn n负端对应IRMP 没查到Ramp amplitude PWM ramp amplitude set by external resistor. Rampamplitude 脉宽调制用的用这个电阻调节振幅斜率DVD 没查到 uvlo 欠压锁定脚低于某值就保护IMAX 最大电流 (不知道对不对对 Over current protection amplitude set. 过流保护幅度设置PWM 脉宽调制 Pulse-Width ModulationISN 没查到CAS#:列选信号RAS#:行选信号WE#:允许信号(高电平允许读,低电平允许写CS#:片选信号SCL:串行时钟,SDA:串行数据,由南桥提供3.3V电压FRAME#:帧周期信号TRDY#:从设备准备好IRDY#:主设备准备好DEVSEL#:设备选择信号C/BE#(0、C/BE#(1、C/BE(2、C/BE(3,是命令/字节允许信号OVP 是过压保护,OCP是过流保护INV-PWM 是高压板驱动控制信号CLK:时钟INPUT CPU:初始化 RESET:复位ADS:地址状态BEO#-7#:字节使能 AP:地址偶校验AP:地址偶校验DP0-7:数据偶校验 INIR:可屏蔽中断请求DBSY:数据忙SCYC:裂开周期输出HIT#:命中指示NMI:非屏蔽中断请求INV:无效输入IERR:内部检验错BREQ:内部总线占用请求BUSCHK:总线检查输入A20M#:地址位20屏蔽PWT:页面高速缓存内存通写PCD:页面高速缓存禁止EWBE#:外部写缓冲器输入APCHK#:地址校验检测状态FLUSH#:高速缓存清洗AHOLD:地址占用请求M/IO#:内存/IO指示LOCK:总线封锁 SMIACT#:系统管理中断请求SMT#:系统管理中断FERR#:浮点数值出错BOFF#:总线屏蔽IGNNE#:忽略数值出错HLDA:总线占用响应HOLD:总线占用请求NMI:非屏蔽中断请求EADS#:有效外部地址INIR:可屏蔽中断请求KEN#:高速缓存使能PCHK#:奇偶校验错使能SDONE:监听完成信号SERR:系统错误报告PAK64:奇偶双字节校验DEVSEL:设备选择 STOP:停止数据传送TP_CLK TOUCH PAD CLOCK 触摸板时钟信号TP_DATA TOUCH PAD DATA 触摸板数据信号3S/4S# 这个不知道65W/90W# 适配器功率识别信号SBPWR_EN 这个不知道是哪个电压开启信号TV_THERM# 过温信号EC_SPIDI/FWR# BIOS数据输入信号EC_SPIDO/FRD# BIOS数据输出信号EC_SPICLK BIOS时钟同步信号EC_SPICS# BIOS片选信号FSTCHG FAST CHARGE快速充电?不确定BATT_GRN_LED# 电池绿色信号灯BATT_AMB_LED 电池黄SE闪烁灯CAPS_LED 大小写信号灯PWR_LED 电源指示灯SYSON 主电压开启信号VR_ON CPU核心供电开启信号ACIN 电源电压检测信号EC_RSMRST EC复信信号EC_LID_OUT# 待机信号EC_PWROK PG信号一般发给南桥BKOFF# 背光开启信号WL_OFF# 无线开启信号MEDIA_LED 音乐播放器快捷键SATA_LED# SATA硬盘指示灯信号IDE_LED# IDE硬盘指示信号EC_SMB_CK[2:1] EC系统管理总线时钟EC_SMB_CK[2:1] EC系统管理总线数据PM_SLP_S3# S3状态信号南桥发到EC的开关信号PM_SLP_S5# S5状态信号南桥发到EC的开关信号LID_SW# 待机信号PBTN_OUT# EC发给南桥的开机信号FAN_SPEED1 风扇控制信号BT_ON# 蓝牙开启信号ON/OFF 来自开关按钮的开机信号'NUM_LED# 小键盘数字键信号PWR_SUSP_LED 待机指示灯信号D/C# 适配器检测信号Shutdown的简写关闭 ,SHDN IN 应该就是关闭信号输入。

电脑主板工作信号名词解释集合

电脑主板工作信号名词解释之RSMRST# (1)电脑主板工作信号名词解释之PWRBTN#及IO_PWRBTN# (2)电脑主板工作信号名词解释之SLP_S3# SLP_S5#及SUSB# SUSC# (3)电脑主板工作信号名词解释之PSON# (4)电脑主板工作信号名词解释之VCORE_EN VTT_PWRGD (4)电脑主板工作信号名词解释之PWROK SB_PWROK NB_PWROK (5)电脑主板工作信号名词解释之RSMRST#RSMRST# IO芯片的准备好信号,就是IO的供电3VSB,BATT正常后IO就会送出该信号RSMRST#正常后IO芯片才会正常工作,所以在修不触发的板子时,这是一个关键测试点该信号在电脑接通电源后就应该一直保持在3V左右的高电平该信号一般是3VSB经过一个K级以上电阻提供上拉,常见的4.7K,8.2K等如果该信号没有或偏低,需检查其上拉电阻,有时主板该信号会连着网卡芯片,所以此信号不正常时需拆掉网卡芯片看是否是网卡芯片把它拉低了,然后就是更换IO芯片,然后就是南桥了,有部分主板(SIS芯片组的最常见)RSMRST#信号同时也会送给北桥,如华硕的P5SD2-A P5SD2-VM等电脑主板工作信号名词解释之RTCRST# BATOK# SYSRST#RTCRST# BATOK# SYSRST# 这几个信号其实就是同一个信号,只是在不同的芯片组中表示的不一样RTCRST#一般在INTEL芯片组及NVIDIA芯片组的电路图中标识(有些地方标识的RTC_RST#)BATOK#一般在SIS芯片组的电路图中标识SYSRST#一般在AMD芯片组的电路图中标识这些信号一般可以理解为CMOS跳线电压准备好,如BATOK#就很好理解,BAT代表CMOS电池电压,OK那就是准备好了的意思,连起来就是CMOS电池电压准备好这些信号大部分是从CMOS跳线的中间一针直接连着南桥给南桥提供最基本的供电,使南桥的32.768晶振起振,不过也有少数主板会经过一些电阻再接到南桥我们都知道32.768晶振不起振电脑就不能开机(部分主板可以开机),所以这个RTCRST# BATOK# S YSRST# 不正常时就会影响到开机,造成不能触发另外像图中那个双二极管会经常损坏,造成CMOS不能保存的问题RTCRST#简易图示电脑主板工作信号名词解释之PWRBTN#及IO_PWRBTN#PWRBTN 主板上电时的一个信号,即电脑开关就是这个信号,在电脑接通电源的时候,3VSB或5VSB通过一个4.7K或8.2K等的电阻给该信号提供上拉,所以在接通电源时该信号的电压是3. 3V或5V的高电平,而按下开关的时候该信号变为0V低电平(开关的另一端是接地的,按下开关时就是把PWRBTN信号接到地上了),然后松开开关PWRBTN又回到3.3V或5V的高电平。

维修主板初学者如何理解各种电信号

本人没有一点电子电路基础,听了饼哥教学20天课,依然是一头雾水,不知道如何学习如何理解什么rsmrst、vccrtc/cpurst等等这些信号。

听了20天课,一直纠结了20天,终于在一天早上梳头的时候顿悟。

现在写出来与大家共享,希望大家不要拍砖。

其实,在生活中,我们用的大部分是强电,就是大电流大电压的东西,这些都已经习以为常了。

一接触主板的这些小电流小电压的东西,理解肯定想套用哪些强电的东西。

这们就走入了一个误区。

其实,主板要这样理解,在主板电路中有控制电和工作电两种,就好比电视机的遥控电和正常工作电,遥控中只有两节小电池,电压小,电流小,但他可以控制电视机开机,可以控制大电流和大电压的开启和关闭。

就好像三极管用小信号电流控制大工作电流,场管用小信号电压控制大工作电流一样。

控制电当然就是为了控制,就是各种信号,像rsmrst;vccrtc/cpurst,就是这种,他们的特点是有电压,电流很小,几乎可以忽略不计。

工作电就是主板中为保证正常工作的正常供电,像网卡和声卡的5V供电,cpu的供电。

主板的上电时序可以理解为,各种控制和检测信号5Vsb/32.768/rsmrst正常后,按下电源开关,pwrbtn/slp_s3/ps_on信号发出,开始正常供电。

就写到这吧,希望对初学者能有些启发,帮助大家学的更好。

本文来自:迅维网(),出处:/forum.php?mod=viewthread&tid=396969。

主板上各种信号说明

主板上各种信号说明一、CPU接口信号说明1. A[31:3]# I/O Address(地址总线)ν这组地址信号定义了CPU的最大内存寻址空间为4GB。

在地址周期的第一个子周期中,这些Pin传输的是交易的地址,在地址周期的第二个子周期中,这些Pin传输的是这个交易的信息类型。

2. A20M# I Adress-20 Mask(地址位20屏蔽)ν此信号由ICH(南桥)输出至CPU的信号。

它是让CPU在Real Mode(真实模式)时仿真8086只有1M Byte(1兆字节)地址空间,当超过1 Mbyte位空间时A20M#为Low,A20被驱动为0而使地址自动折返到第一个1Mbyte地址空间上。

3. ADS# I/O Address Strobe(地址选通)ν当这个信号被宣称时说明在地址信号上的数据是有效的。

在一个新的交易中,所有Bus上的信号都在监控ADS#是否有效,一但ADS#有效,它们将会作一些相应的动作,如:奇偶检查、协义检查、地址译码等操作。

4. ADSTB[1:0]# I/O Address Strobesν这两个信号主要用于锁定A[31:3]#和REQ[4:0]#在它们的上升沿和下降沿。

相应的ADSTB0#负责REQ[4:0]#和A[16:3]#,ADSTB1#负责A[31:17]#。

5. AP[1:0]# I/O Address Parity(地址奇偶校验)ν这两个信号主要用对地址总线的数据进行奇偶校验。

6. BCLK[1:0] I Bus Clock(总线时钟)这两个Clock主要用于供应在Host Bus上进行交易所需的Clock。

ν7. BNR# I/O Block Next Request(下一块请求)ν这个信号主要用于宣称一个总线的延迟通过任一个总线代理,在这个期间,当前总线的拥有者不能做任何一个新的交易。

8. BPRI# I Bus Priority Request(总线优先权请求)ν这个信号主要用于对系统总线使用权的仲裁,它必须被连接到系统总线的适当Pin 。

常用主板信号名词,电子缩写解释

ADJ 可调 Adjustable 比如大小和方向控制的意思是通断了VID 电压识别 Voltage IdentificationSS 软启动 (soft Start两个单词的缩写)FB 反馈 (feedback单词的缩写)COMP 补偿 (Compensatory单词的缩写)VSEN 电压侦测 voltage senserISP 电流侦测 p 正端与 isn n负端对应IRMP 没查到Ramp amplitude PWM ramp amplitude set by external resistor. Rampamplitude 脉宽调制用的用这个电阻调节振幅斜率DVD 没查到 uvlo 欠压锁定脚低于某值就保护IMAX 最大电流 (不知道对不对)对 Over current protection amplitude set. 过流保护幅度设置PWM 脉宽调制 Pulse-Width ModulationISN 没查到CAS#:列选信号RAS#:行选信号WE#:允许信号(高电平允许读,低电平允许写)CS#:片选信号SCL:串行时钟,SDA:串行数据,由南桥提供3.3V电压FRAME#:帧周期信号TRDY#:从设备准备好IRDY#:主设备准备好DEVSEL#:设备选择信号C/BE#(0)、C/BE#(1)、C/BE(2)、C/BE(3),是命令/字节允许信号OVP 是过压保护,OCP是过流保护INV-PWM 是高压板驱动控制信号CLK:时钟INPUT CPU:初始化 RESET:复位ADS:地址状态BEO#-7#:字节使能 AP:地址偶校验AP:地址偶校验DP0-7:数据偶校验 INIR:可屏蔽中断请求DBSY:数据忙SCYC:裂开周期输出HIT#:命中指示NMI:非屏蔽中断请求INV:无效输入IERR:内部检验错BREQ:内部总线占用请求BUSCHK:总线检查输入A20M#:地址位20屏蔽PWT:页面高速缓存内存通写PCD:页面高速缓存禁止EWBE#:外部写缓冲器输入APCHK#:地址校验检测状态FLUSH#:高速缓存清洗AHOLD:地址占用请求M/IO#:内存/IO指示LOCK:总线封锁 SMIACT#:系统管理中断请求SMT#:系统管理中断FERR#:浮点数值出错BOFF#:总线屏蔽IGNNE#:忽略数值出错HLDA:总线占用响应HOLD:总线占用请求NMI:非屏蔽中断请求EADS#:有效外部地址INIR:可屏蔽中断请求KEN#:高速缓存使能PCHK#:奇偶校验错使能SDONE:监听完成信号SERR:系统错误报告PAK64:奇偶双字节校验DEVSEL:设备选择 STOP:停止数据传送TP_CLK TOUCH PAD CLOCK 触摸板时钟信号TP_DATA TOUCH PAD DATA 触摸板数据信号3S/4S# 这个不知道65W/90W# 适配器功率识别信号SBPWR_EN 这个不知道是哪个电压开启信号TV_THERM# 过温信号EC_SPIDI/FWR# BIOS数据输入信号EC_SPIDO/FRD# BIOS数据输出信号EC_SPICLK BIOS时钟同步信号EC_SPICS# BIOS片选信号FSTCHG FAST CHARGE快速充电?不确定BATT_GRN_LED# 电池绿色信号灯BATT_AMB_LED 电池黄SE闪烁灯CAPS_LED 大小写信号灯PWR_LED 电源指示灯SYSON 主电压开启信号VR_ON CPU核心供电开启信号ACIN 电源电压检测信号EC_RSMRST EC复信信号EC_LID_OUT# 待机信号EC_PWROK PG信号一般发给南桥BKOFF# 背光开启信号WL_OFF# 无线开启信号MEDIA_LED 音乐播放器快捷键SATA_LED# SATA硬盘指示灯信号IDE_LED# IDE硬盘指示信号EC_SMB_CK[2:1] EC系统管理总线时钟EC_SMB_CK[2:1] EC系统管理总线数据PM_SLP_S3# S3状态信号南桥发到EC的开关信号PM_SLP_S5# S5状态信号南桥发到EC的开关信号LID_SW# 待机信号PBTN_OUT# EC发给南桥的开机信号FAN_SPEED1 风扇控制信号BT_ON# 蓝牙开启信号ON/OFF 来自开关按钮的开机信号'NUM_LED# 小键盘数字键信号PWR_SUSP_LED 待机指示灯信号D/C# 适配器检测信号Shutdown的简写关闭 ,SHDN IN 应该就是关闭信号输入。

主板相关信号讲解

Confidential Document

LPC Interface Signals

LAD[3:0]

I/O :LPC的多元复用信号,可以传输命令,地址和数据.

LFRAME# O

:LPC 帧,当LFRAME#有效时表示一个LPC周期的开始或结束.

LDRQ#

I

:LPC串行DMA请求输入,LDRQ#被用於DMA请求或总线存取.

Confidential Document

HUB-Link Interface Signals

HL[10:0]# :HUB-LINK 信号线,用於传送命令,地址和数据. HL-STBS :HUB-LINK选通信号. HL-STBF :HUB-LINK选通信号补尝.

Confidential Document

LAN_RXD[2:0] I :Received Data 数据接收,由Lan Chiset驱动这些信号传输数据和控 制信息到南桥.

LAN_TXD[2:0] O :Transmit Data 传输数据,由南桥驱动这些信号传输数据和控制信息 到Lan Chipset.

LAN_RSTSYNC O:Lan Reset/Sync 复位/同步信号,这个信号为多元信号可以作为 Reset也可以作为Sync,它是由南桥发出的.

C/BE[3:0]# T/S: 总线命令和字节使能多路复用信号线.在交易的地址期中,这四条线 上传输的是总线命令;在交易的数据期内,它们传输的是字节使能信号,并在整个数 据期中有效,用来确定AD[31:0]线上哪些字节为有效数据.C/BE[0]#应用於字节0(最 低字节),C/BE[3]#应用於字节3(最高字节).

Confidential Document

AC LINK Interface Signals

常用主板信号名词,电子缩写解释.

ADJ 可调Adjustable 比如大小和方向控制的意思是通断了VID 电压识别Voltage IdentificationSS软启动(soft Start两个单词的缩写FB反馈(feedback单词的缩写COMP补偿(Compe nsatory单词的缩写VSEN 电压侦测voltage senserISP 电流侦测p 正端与isn n 负端对应IRMP 没查到Ramp amplitude PWM ramp amplitude set by external resistor. Ramp amplitude 脉宽调制用的用这个电阻调节振幅斜率DVD 没查到uvlo 欠压锁定脚低于某值就保护IMAX 最大电流(不知道对不对对Over current protection amplitude set过流保护幅度设置PWM 脉宽调制Pulse-Width ModulationISN 没查到CAS#:列选信号RAS#:行选信号WE#:允许信号(高电平允许读,低电平允许写CS# :片选信号SCL:串行时钟,SDA:串行数据,由南桥提供3.3V电压FRAME#: 帧周期信号TRDY#: 从设备准备好IRDY#: 主设备准备好DEVSEL#:设备选择信号C/BE#(O、C/BE#(1、C/BE(2、C/BE(3,是命令/字节允许信号OVP是过压保护,OCP是过流保护INV-PWM 是高压板驱动控制信号CLK:时钟INPUT CPU:初始化RESET:复位ADS:地址状态BEO#-7#:字节使能AP:地址偶校验AP:地址偶校验DP0-7:数据偶校验INIR:可屏蔽中断请求DBSY:数据忙SCYC:裂开周期输出HIT#:命中指示NMI:非屏蔽中断请求INV:无效输入IERR:内部检验错BREQ:内部总线占用请求BUSCHK:总线检查输入A20M#:地址位20屏蔽PWT:页面高速缓存内存通写PCD:页面高速缓存禁止EWBE#:外部写缓冲器输APCHK#:地址校验检测状态FLUSH#:高速缓存清洗AHOLD:地址占用请求M/IO#:内存/IO指示LOCK:总线封锁SMIACT#:系统管理中断请求SMT#:系统管理中断FERR#:浮点数值出错BOFF#:总线屏蔽IGNNE# :忽略数值出错HLDA: 总线占用响应HOLD: 总线占用请求NMI: 非屏蔽中断请求EADS# :有效外部地址INIR: 可屏蔽中断请求KEN#: 高速缓存使能PCHK#:奇偶校验错使能SDONE:监听完成信号SERR:系统错误报告PAK64:奇偶双字节校验DEVSEL:设备选择STOP:停止数据传送TP_CLK TOUCH PAD CLOCK 触摸板时钟信号TP_DATA TOUCH PAD DATA 触摸板数据信号3S/4S#这个不知道65W/90W# 适配器功率识别信号SBPWR_EN 这个不知道是哪个电压开启信号TV_THERM# 过温信号EC_SPIDI/FWR# BIOS 数据输入信号EC_SPIDO/FRD# BIOS 数据输出信号EC_SPICLK BIOS 时钟同步信号EC_SPICS# BIOS 片选信号FSTCHG FAST CHARGE 快速充电?不确定BATT_GRN_LED# 电池绿色信号灯BATT_AMB_LED电池黄SE闪烁灯CAPS_LED 大小写信号灯PWR_LED 电源指示灯SYSON 主电压开启信号VR_ON CPU 核心供电开启信号ACIN 电源电压检测信号EC_RSMRST EC 复信信号EC_LID_OUT# 待机信号EC_PWROK PG 信号一般发给南桥BKOFF# 背光开启信号WL_OFF# 无线开启信号MEDIA_LED 音乐播放器快捷键SATA_LED# SATA 硬盘指示灯信号IDE_LED# IDE 硬盘指示信号EC_SMB_CK[2:1] EC 系统管理总线时钟EC_SMB_CK[2:1] EC 系统管理总线数据PM_SLP_S3# S3状态信号南桥发到EC的开关信号PM_SLP_S5# S5状态信号南桥发到EC的开关信号LID_SW# 待机信号PBTN_OUT# EC 发给南桥的开机信号FAN_SPEED1 风扇控制信号BT_ON# 蓝牙开启信号ON/OFF 来自开关按钮的开机信号'NUM_LED# 小键盘数字键信号PWR_SUSP_LED 待机指示灯信号D/C# 适配器检测信号Shutdown的简写关闭,SHDN IN应该就是关闭信号输入。

主板信号点解释

這四個訊號主要用於對數據總線上的數據進行奇偶校驗。 13. DRDY# I/O Data Ready(數據准備)

當DRDY#為Low時,指示當前數據總線上的數據是有效的,若為 High時,則總線上的數據為無效。

Confidential

Document

7

14. DSTBN[3:0]# I/O Data Strobe Data strobe used to latch in D[63:0]# :

主機板信號講解

Edit By Gemi 2004.8

1

一、CPU接口訊號說明 接口訊號說明

1. A[31:3]# I/O Address(地址總線)

這組地址信號定義了CPU的最大內存尋址空間為4GB。在地址周期 的第一個子周期中,這些Pin傳輸的是交易的地址,在地址周期的 第二個子周期中,這些Pin傳輸的是這個交易的信息類型。 2. A20M# I Adress-20 Mask(地址位元20屏蔽)

Confidential Document

9

19. INIT#

I

Initialization(初始化)

這個訊號為一由ICH輸出至CPU的訊號,與Reset功能上非常類似, 但與Reset不同的是CPU內部L1 Cache和浮點運算操作狀態並沒被 無效化。但TLB(位址轉換參考暫存器)與BTB(分歧位址暫存器) 內資料則被無效化了。INIT#另一點與Reset不同的是CPU必須等 到在指令與指令之間的空檔才會被確認,而使CPU進入啟始狀態。 20. INTR I Processor Interrupt(可遮蔽式中斷)

I/O

AD Bus Strobe 0(地址數據總線選通)

Confidential

电脑主板常见信号功能解释

电脑主板常见信号功能解释VCCRTC 实时时钟供电,(VBAT),电池+跑线,经过1k(有点板不是)电阻,到达二极管+,从-出来RTCRST# 实时时钟复位这两步满足后产生晶振32.768KHZ 晶振这三步没上ATX,都有V5REF-SUS 5V待机电压,主用于USB和键盘VCCSUS3-3 SB的3.3V待机电压(经1117,1084等转换而来)PCI 14脚.RSMRST# 待机电压好信号,正常工作为高电平,(低电平引起不开机)PWRBTN# 1 电源开关,送到南桥SLP-S5# 2 南桥发出 3 PS_ON# 这三个为开机信号SLP-S4# 2 南桥发出SLP-S3# 2 南桥发出三个S#有一个是开启内存供电的VDIMM 内存供电VCOREVCC CPU的核心电压,VRMPWRGD CPU供电好信号,当CPU供电电压值正常后,供电电源芯片发出高电平送到SB,用于SB内部产生CPUPWRGD和PLTRST#的重要条件.CLKCEN 时钟开启信号,用于开启时钟芯片工作,SB收到VRMPWRGD后发出高电平开启时钟PWROK 电源好信号,ATX电源供电正常后发出灰色线PG5V,经门电路,IO,后发送到SB,通知SB各路供电已正常CPUPWRGD cpu电源好信号,由SB发送到CPU,是CPU工作PLTRST# 平台复位/总复位,SB供电,时钟正常并收到两个PG信号后将PLTRST#置高发送到NB,IO(两个PG指PWROK,VRMPWRGD) PCIRST# PCI设备复位信号,PLTRST#在SB内部延时后发出到各个PCI设备,正常3.3V,在A15脚测量CPURST# 1.2V左右,由北桥收到PLTRST#产生,(NB没复位。

CPU就没有复位)INTEL的上电流程(五大待机条件和三大信号)VCCRTC--RTCRST#--32.768KHZ--3VSB(插电源5VSB-3VSB)--RSMRST#--PWRBTN#--SLP_S3#--PS_ON#--ATX输出5V,3V.12V.....待机时VCCRTC 3V 高电平RTCRST# 3V 高电平32.768KHZ--3VSB(插电源5VSB-3VSB)--RSMRST# 3V 高电平 !开机触发 PWRBTN# 高--低--高 SLP_S3# 低--高 PS_ON# 高--低ATX输出5V,3V.12V.....。

主板上各种信号说明及中断

主板上各种信号说明及中断一、CPU接口信号说明1. A[31:3]# I/O Address(地址总线)这组地址信号定义了CPU的最大内存寻址空间为4GB。

在地址周期的第一个子周期中,这些Pin传输的是交易的地址,在地址周期的第二个子周期中,这些Pin传输的是这个交易的信息类型。

2. A20M# I Adress-20 Mask(地址位20屏蔽)此信号由ICH(南桥)输出至CPU的信号。

它是让CPU在Real Mode(真实模式)时仿真8086只有1M Byte(1兆字节)地址空间,当超过1 Mbyte位空间时A20M#为Low,A20被驱动为0而使地址自动折返到第一个1Mbyte地址空间上。

3. ADS# I/O Address Strobe(地址选通)当这个信号被宣称时说明在地址信号上的数据是有效的。

在一个新的交易中,所有Bus上的信号都在监控ADS#是否有效,一但ADS#有效,它们将会作一些相应的动作,如:奇偶检查、协义检查、地址译码等操作。

4. ADSTB[1:0]# I/O Address Strobes这两个信号主要用于锁定A[31:3]#和REQ[4:0]#在它们的上升沿和下降沿。

相应的ADSTB0#负责REQ[4:0]#和A[16:3]#,ADSTB1#负责A[31:17]#。

5. AP[1:0]# I/O Address Parity(地址奇偶校验)这两个信号主要用对地址总线的数据进行奇偶校验。

6. BCLK[1:0] I Bus Clock(总线时钟)这两个Clock主要用于供应在Host Bus上进行交易所需的Clock。

7. BNR# I/O Block Next Request(下一块请求)这个信号主要用于宣称一个总线的延迟通过任一个总线代理,在这个期间,当前总线的拥有者不能做任何一个新的交易。

8. BPRI# I Bus Priority Request(总线优先权请求)这个信号主要用于对系统总线使用权的仲裁,它必须被连接到系统总线的适当Pin 。

主板信号走向(全)

(1)DS#:CPU地址选通信号,低电平有效。地址选通信号,就是好像我们出行一样,有几条路可供选择,具体选择走哪一条,在CPU与北桥之间的地址线是单向传输的。

(2)BSY#:FSB总线忙信号,高电平表示总线不忙,低电平表示总线忙。总线忙表示地址线上正在传输信号。

(2)北桥与南桥

北桥使PCI帧周期信号FRAME#为低电平,启动PCI总线工作,建立起北桥和南桥的连接,然后主设备准备好信号IRDY#转换为低电平,通过IRDY#信号线告诉南桥,我要发数据给你,准备接收吧!

如果南桥准备好了,南桥会把从设备准备好信号TRDY#变为低电平送到北桥,告诉北桥我己准备好接收数据,请发送数据吧!北桥接到低电平的TRDY#信号后(这时FRAME#、IRDY#和TRDY#全部为低电平,低电平有效),北桥把收到的地址信号通过北桥的PCI总线接口译码,将A31一A0这32根地址线发送到南桥,这些地址信号经南桥的HC总线接口译码后送给南桥。

(3)南桥与BIOS

南桥将A17一A0地址信号线送到BIOS(1SA列BIOS的地址线为A17一A0,共18根),这个地址信号到BIOS内部的地址译码器译码,知道了CPU需要的是哪一部分指令。然后会选择这部分数据的相应存储体(存储体将不同的指令存放在不同的存储器上),这时南桥的ISA总线给BIOS的WE持高电平(只读),还通过南桥内部X总线X—BUS向BIOS发出一个低电平的片选信号,这时允许BIOS把数据调入数据缓冲器,这时X-BUS会把OE#变为低电平,允许数据输出,这些数据通过D7一D0传输给南桥内部的ISA总线。

(3)FRAME#:PCI帧周期信号,低电平表示PCI总线启动工作,高电平表示PCI总线没有工作。

(4)IRDY#:主设备淮备好信号,低电平有效。主设备就绪信号和从设备就绪信号,从北桥到南桥传输数据的时候,以北桥为主,南桥为从;如果南桥到北桥传输数据的时候,南桥为主,北桥为从。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

当总线拥有者在使用总线时,会驱动DBSY#为Low表示总线在忙。当DBSY#为High时,数据总线被释放。

13.DP[3:0]# (I/O) Data Parity(数据奇偶校验)6 Q3 M, S w) e# D( o7 `

11.DBI[3:0]# (I/O) Data Bus Inversion(数据总线倒置). O# H7 s6 B( X

这些信号主要用于指示数据总线的极性,当数据总在线的数据反向时,这些信号应为Low。这四个信号每个各负责16个数据总线,见下表:9 J$ { [* x! ^' m% G5 N" n2 \7 X6 w

当TRDY#为Low时,表示目标已经准备好,可以接收数据。当为High时,Target没有准备好。; R. v1 z, t- `) e3 f( t; b

32.VID[4:0] (O) Voltage ID(电压识别)/ E# S$ d" [* |1 r) X+ y* |

这个信号主要为CRT提供红基色模拟视频信号。

4.GREEN (O) Green analog video output(绿色模拟信号输出)1 q/ c* R3 M9 A4 Q2 j9 z C8 q

这四个信号主要用于对数据总在线的数据进行奇偶校验。3 x% |" M# Z; U; p# L6 m

14.DRDY# (I/O) Data Ready(数据准备)5 y. _! `+ J. P: \9 D4 u+ x

当DRDY#为Low时,指示当前数据总在线的数据是有效的,若为High时,则总在线的数据为无效。

这些讯号主要用于设定CPU的工作电压,在主机板中这些信号必须被提升到最高3V。

二、VGA接口信号说明2 C! Z( ^9 Y. i8 J5 k

1.HSYNC (O) CRT Horizontal Synchronization(水平同步信号)

这个信号主要提供CRT水平扫描的信号。

这个信号主要用于对系统总线使用权的仲裁,它必须被连接到系统总线的适当Pin 。当BPRI#有效时,所有其它的设备都要停止发出新的请求,除非这个请求正在被锁定。总线所有者要始终保持BPRI#为有效,直到所有的请求都完成才释放总线的控制权。2 O' q: Q( H& H

9.BSEL[1:0] (I/O) Bus Select(总线选择)

1.A[31:3]# (I/O) Address(地址总线)& l1 f t$ r$ E$ |

这组地址信号定义了CPU的最大内存寻址空间为4GB。在地址周期的第一个子周期中,这些Pin传输的是交易的地址,在地址周期的第二个子周期中,这些Pin传输的是这个交易的信息类型。9 S5 a9 [1 K8 D' o1 _" p+ ?

7.BNR# (I/O) Block Next Request(下一块请求)

这个信号主要用于宣称一个总线的延迟通过任一个总线代理,在这个期间,当前总线的拥有者不能做任何一个新的交易。

8.BPRI# (I) Bus Priority Request(总线优先权请求). y! ^4 W8 g3 F. L0 R. q% U: D

18.GTLREF (I) GTL Reference(GTL参考电压)

这个信号用于设定GTLn Bus的参考电压,这个信号一般被设为Vcc电压的三分之二。4 }5 O% i- o6 P- w

19.IGNNE# (I) Ignore Numeric Error(忽略数值错误)

30.STPCLK# (I) Stop Clock(停止时钟)

当CPU进入省电模式时,ICH(南桥)将发出这个信号给CPU,让它把它的Clock停止。

31.TRDY# (I/O) Target Ready(目标准备)2 H. N' i |( I: Z1 f H

2.VSYNC (O) CRT Vertical Synchronization(垂直同步信号)

这个信号主要提供CRT垂直扫描的信号。% T& C+ G) K Q- `7 S3 _

3.RED (O) RED analog video output(红色模拟信号输出)5 }4 Y& {$ L- S A7 I) P+ q8 D

这个信号为一ICH输出至CPU的信号。当CPU出现浮点运算错误时需要此信号响应CPU。IGNNE#为Low时,CPU会忽略任何已发生但尚未处理的不可遮蔽的浮点运算错误。但若IGNNE#为High时,又有错误存在时,若下一个浮点指令是FINIT、FCLEX、FSAVE等浮点指令中之一时,CPU会继续执行这个浮点指令但若指令不是上述指令时CPU会停止执行而等待外部中断来处理这个错误。" V0 O/ p( h! M9 z/ Y

4.ADSTB[1:0]# (I/O) Address Strobes" w5 l5 W: j% m, W" n% H

这两个信号主要用于锁定A[31:3]#和REQ[4:0]#在它们的上升沿和下降沿。相应的ADSTB0#负责REQ[4:0]#和A[16:3]#,ADSTB1#负责A[31:17* e% P

5.AP[1:0]# (I/O) Address Parity(地址奇偶校验)

这两个信号主要用对地址总线的数据进行奇偶校验。

6.BCLK[1:0] (I) Bus Clock(总线时钟)

这两个Clock主要用于供应在Host Bus上进行交易所需的Clock。

26.RS[2:0]# (I) Response Status(响应状态)* u+ R3 q: a' K2 G/ Z. o" M. T+ z

这些信号由响应方来驱动,具体含义请看下表:+ v6 u! U' L: c$ v

27.STKOCC# (O) Socket Occupied(CPU插入)

这个信号一般由CPU拉到地,在主机板上的作用主要是来告诉主机板CPU是不是第一次插入。若是第一次插入它会让你进CMOS对CPU进行重新设定。

28.SMI# (I) System Management Interrupt(系统管理中断)

此信号为一由ICH输出至CPU的信号,当CPU侦测到SMI#为Low时,即进入SMM模式(系统管理模式)并到SMRAM(System Management RAM)中读取SMI#处理程序,当CPU在SMM模式时NMI、INTR及SMI#中断信号都被遮蔽掉,必需等到CPU执行RSM(Resume)指令后SMI#、NMI及INTR中断信号才会被CPU认可。 ( |- M u/ X6 w

Data strobe used to latch inn D[63:0]# :

17.FERR# (O) Floating Point Error(浮点错误)* d+ E& K; v* f& Y2 k9 L

这个信号为一CPU输出至ICH(南桥)的信号。当CPU内部浮点运算器发生一个不可遮蔽的浮点运算错误时,FERR#被CPU驱动为Low。) e4 t) t" h. H, o2 G8 Z

23.PWRGOOD (I) Power Good(电源OK)

这个信号通常由ICH(南桥)发给CPU,来告诉CPU电源已OK,若这个信号没有供到CPU,CPU将不能动作。

24.REQ[4:0]# (I/O) Command Request(命令请求)

15.DSTBN[3:0]# (I/O) Data Strobe4 _$ D# |+ r6 v% l4 h

Data strobe used to latch in D[63:0]# :4 I% ^$ f$ A. ]: a* z% H

16.DSTBP[3:0]# (I/O) Data Strobe

这些信号由CPU接到NB(北桥),当总线拥有者开始一个新的交易时,由它来定义交易的命令。+ H7 L+ \/ ?+ |) @1 _& p

25.RESET# (I) Reset(重置信号)" {. d' T: a2 T: J+ A% x1 x

当Reset为High时CPU内部被重置到一个已知的状态并且开始从地址0FFFFFFF0H读取重置后的第一个指令。CPU内部的TLB(地址转换参考缓存器)、BTB(分歧地址缓存器)以及SDC(区段地址转换高速缓存)当重置发生时内部数据全部都变成无效。

2.A20M# (I) Adress-20 Mask(地址位20屏蔽)

此信号由ICH(南桥)输出至CPU的信号。它是让CPU在Real Mode(真实模式)时仿真8086只有1M Byte(1兆字节)地址空间,当超过1 Mbyte位空间时A20M#为Low,A20被驱动为0而使地址自动折返到第一个1Mbyte地址空间上。

21.INTR (I) Processor Interrupt(可遮蔽式中断)0 k3 }# G" v% T2 r. S

这个信号为一由ICH输出对CPU提出中断要求的信号,外围设备需要处理数据时,对中断控制器提出中断要求,当CPU侦测到INTR为High时,CPU先完成正在执行的总线周期,然后才开始处理INTR中断要求。

22.PROCHOT# (I/O) Processor Hot(CPU过温指示)3 d+ K+ m7 X0 e/ H3 [0 Q' s

当CPU的温度传感器侦测到CPU的温度超过它设定的最高度温度时,这个信号将会变Low,相应的CPU的温度控制电路就会动作。7 Y( r- J1 A" ?( L5 s0 O. B