基于FPGA的视频帧同步机的设计

基于FPGA的视频监控跟踪系统的设计与实现的开题报告

基于FPGA的视频监控跟踪系统的设计与实现的开题报告一、课题背景和研究意义视频监控技术在实际应用中具有重要意义,广泛用于各种领域,如安防监控、交通监控、环境监控等。

视频监控技术的高效性和实时性对算法和硬件设备的要求都很高,因此利用FPGA实现视频监控跟踪系统,不仅可以提高实时性能,还可以适应不同的监控场景,实现更精确的目标跟踪。

本课题的研究意义在于:1.提高视频监控技术的实时性能和准确性;2.利用FPGA实现视频处理硬件,提高处理效率;3.研究视频跟踪算法,实现目标实时定位和跟踪;4.探索适用于不同场景的监控跟踪方案,提高监控效果。

二、研究内容和研究方法1.研究基于FPGA的视频处理系统设计,包括视频采集、预处理、编码、解码等模块的设计与实现;2.研究基于深度学习的视频目标检测算法,在FPGA硬件平台上实现目标检测,并将结果传输至下一级处理模块;3.研究视频跟踪算法,实现目标的实时定位和跟踪;4.探索不同场景下的视频处理方案,提高监控效果和灵活性。

研究方法:1.对视频采集、处理、传输等模块进行需求分析,设计相应的视频处理系统;2.调查目标检测与跟踪算法,建立相应的模型;3.将开发好的算法和模型应用于FPGA平台上,并进行性能测试;4.根据实验结果和用户反馈,对系统进行优化和改进。

三、研究目标和预期成果1.完成基于FPGA的视频监控跟踪系统设计与实现;2.实现视频的实时采集、处理、传输和存储;3.实现目标检测和跟踪算法,提高监控效果和准确性;4.提高系统的可靠性、实时性和处理效率;5.验证系统在不同场景下的监控能力和应用性。

四、进度计划第一阶段:系统需求分析和设计(2个月)1.对视频监控需求进行分析,确定系统的功能和性能指标;2.设计视频采集、处理、传输和存储模块;3.研究并选择合适的目标检测和跟踪算法。

第二阶段:系统开发与实现(6个月)1.搭建完整的视频监控跟踪系统,实现视频的预处理、编码、解码等模块;2.学习深度学习等相关技术,实现目标检测和跟踪算法;3.进行系统测试和调试,优化系统性能。

基于FPGA的音视频编码与解码算法实现

基于FPGA的音视频编码与解码算法实现近年来,音视频编码技术的飞速发展已经成为媒体领域发展的一个重要驱动力。

FPGA(Field-Programmable Gate Array,现场可编程门阵列)作为一种被广泛应用于数字电路设计的可编程器件,也逐渐成为实现音视频编码与解码的重要工具。

本文将探讨基于FPGA的音视频编码与解码算法实现的问题。

一、音视频编码和压缩算法音视频编码和压缩是提高传输和存储效率的重要手段。

在传输和储存大量音视频数据时,采用压缩技术显然可以减小数据量,从而提高传输和储存效率。

音视频编码算法可以将无损或有损的编码算法应用到声音和图像数据上,压缩得到的音视频数据在保证人眼可接受的情况下,减小数据量,达到储存、传输方面的目的。

目前使用最广泛的编码标准包括MPEG、H.264、H.265等。

MPEG,指传输和压缩共同组成的多媒体专家组(Moving Picture Experts Group),是一种广泛使用的视频压缩标准,由ISO/IEC组织批准。

H.264和H.265是ITU-T标准,与MPEG相比,具有更高的压缩比和更好的编码效率,并且适用于广泛的视频编码应用,已经成为广泛采用的视频编码标准。

二、FPGA处理在音视频编码中的优势FPGA具有硬件可重构性和可编程性,可以快速实现高速数据处理和优化,适用于机器视觉、音频处理、信号处理、无线通信等领域。

在音视频编码领域中,FPGA拥有以下优势:1.高性能:FPGA可以实现硬件并行运算,同时对大量数据进行高速处理,具有优秀的实时性和低延迟。

2.可灵活配置:FPGA硬件结构可编程,允许用户灵活配置其内部处理器和函数单元,以满足各种不同的应用需求。

3.低功耗:采用FPGA进行计算和处理可以减少功耗,同时提高处理效率。

4.可扩展性:FPGA的结构具有良好的可扩展性,可以根据应用需求增加资源,提高处理性能。

基于FPGA的音视频编码实现可以结合FPGA的优势,利用其高效率和低延迟的性能,实现高速音视频解码和编码的应用。

基于FPGA的OFDM时频同步系统的设计与仿真

基于FPGA的OFDM时频同步系统的设计与仿真

段鹏;何明一;薛敏彪

【期刊名称】《测控技术》

【年(卷),期】2009(028)011

【摘要】同步技术是OFDM中的一项关键技术.但由于无线信道的随机性,传统方法在门限设定上无法兼顾判断准确性和计算复杂度两方面性能.针对这一问题,提出了一种将相对门限和浮动门限相结合的同步判决方法,它能够在保持判断准确性的同时降低计算时的复杂度.此外,通过交叠计算训练序列相关值的方法来提高频偏估计精度.在此基础上,详细阐述了算法关键模块的电路结构和硬件实现.仿真结果表明该算法在多径信道环境下具有较高的时间同步和频偏估计精度,能够有效地降低硬件资源消耗,节省传输带宽.

【总页数】6页(P63-67,72)

【作者】段鹏;何明一;薛敏彪

【作者单位】西北工业大学电子信息学院,陕西,西安,710072;西北工业大学电子信息学院,陕西,西安,710072;西北工业大学电子信息学院,陕西,西安,710072

【正文语种】中文

【中图分类】TN914

【相关文献】

1.基于CAZAC序列的OFDM时频同步方案及FPGA实现 [J], 常凝;闫瑞军;胡涵飞

2.基于概率同步算法的计算机外时钟同步系统设计与仿真 [J], 李明国;宋海娜;庄钊文

3.基于时频联合的OFDM系统载波频偏估计方案及FPGA实现 [J], 刘晓明;吴德松;汪梦柔;王潇瀛

4.基于FPGA的OFDM时间同步系统串并结构设计 [J], 周毅;薛敏彪;胡永红

5.基于E1接口的时间同步系统关键模块设计与仿真 [J], 闫辉;胡永辉;侯雷

因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA的实时视频信号处理平台的设计

r eq dr

.

>r c k d

一 . 一

U — 【. 0 Vq7.】 r bd t 【. 0 g —a a 8 . ] yv Sg a 【. u — in I 9 .

t f gf 0 l 8 4

.

r rbsga 【 : _ g—i l8 斫… … n ~

图像 处 理 部 分 内 部 功 能模 块 如 图 2所 示 。

I 墨 卜 塑 丝 . 壅 选 堂 奎 竺 卜 鐾 堡 叫 生卜1 苤 H 皇 矍 l查 I 整

图 2 图像 处 理 部 分 内 部 功 能框 图

F g Di g a o ma e p o e sn a to t r a u c in i .2 a r m fi g r c s i g p r i e n lf n to f n

缚 . 且 数 字 图像 传 感 器 输 出 的 图像 帧 率 也 比较 低 , 辨 率 而 分

也 随 着 半 导 体 行 业 的 发 展 有 了 很 大 的提 高 , 此 为 了输 出 的 因

图 像 能 直 接 在 V A 显 示 器 上 显 示 ,需 要 对 图 像 进 行 帧 率 提 G

【. 0 7.]

w Q RE

CK L 广

R B F F C IO

d a【 0 at 8 】

d t 7 0 a a【 】

.

CKt0 L 0

—

wr re q

>w c k r I

r 呈 b

一 1 ck y v r r q u + d e

wr e q r

RRQ D ̄.

rb g

—

×l _ —

S A R M

—

> ]l wck 7

基于FPGA的视频的采集、处理和显示

基于FPGA的视频的采集、处理和显示

基于FPGA的视频的采集、处理和显示

1.利用FPGA开发板及其外部电路是实现PAL制式到VGA制式的转换。

系统框图如图1所示。

图1

2.摄像头采用的是CCD 摄像头以其感光性好、灵敏度高、信噪比高、抗干扰能力强等优点成为本文采集模块的首选,其输出格式为PAL(Phase Alteration Line 逐行倒相)制式的复合模拟信号。

标准的PAL视频信号图像输出频率为50Hz,即每秒视频显示50帧。

显示一行数据所需的时间为64μs。

图2给出采用的CCD摄像头模块。

图2

3、视频解码芯片,即AD转换。

ADV7180是一种多用途的单芯片多格式视频解码器。

电路

图如图3所示。

图3

4. 视频采集模块电路板如图4所示。

图4

5. 系统采用VGA显示器作为视频图像的输出媒介,其显示数据为RGB三色的模拟视频数据,而FPGA处理完成的视频图像数据为数字信号,视频数模转换芯片,采用AD公司的ADV7123作为视频数模转换芯片。

ADV7123是一款单芯片、三通道、低功耗高速数模转换器,内置三个高速、10位、带互补输出的视频数模转换器、一个标准TTL 输入接口以及一个高阻抗、模拟输出电流源。

如图5所示。

图5

6.结果图如图6所示。

图6 既是采用本文的系统实现的7.作品整体结构图。

基于FPGA的帧同步实现

基于FPGA 的帧同步实现(1) 假设帧同步码为13位巴克码,在ISE或Quartus等FPGA 软件内实现巴克码的帧同步,并仿真给出帧同步算法的性能(虚警概率,漏检概率等)。

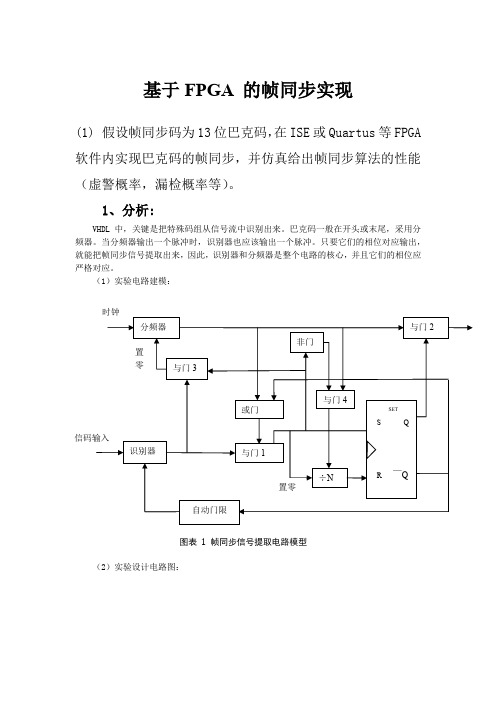

1、分析:VHDL中,关键是把特殊码组从信号流中识别出来。

巴克码一般在开头或末尾,采用分频器。

当分频器输出一个脉冲时,识别器也应该输出一个脉冲。

只要它们的相位对应输出,就能把帧同步信号提取出来,因此,识别器和分频器是整个电路的核心,并且它们的相位应严格对应。

(1)实验电路建模:图表1 帧同步信号提取电路模型(2)实验设计电路图:(3)识别器模块:2、V HDL实验流程图:(1)译码器流程图模型:(2)判决器建模流程图:(3)自动门限建模流程图:(4)时钟控制器建模流程图:三源代码解析verilog HDL:sbq:instlibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all; entity sbq isport(din,clk :in std_logic;q12,q11,q10,q9,q8,q7,q6,q5,q4,q3,q2,q1,q0:out std_logic); end sbq;architecture rtl of sbq issignal tmp:std_logic_vector (12 downto 0);beginprocess(clk,din)beginif(clk'event and clk='1') thentmp(12)<=din;for i in 1 to 12 looptmp(12-i)<=tmp(13-i);end loop;end if;end process;q12<=tmp(12);q11<=not tmp(11);q10<=tmp(10);q9<=not tmp(9);q8<=tmp(8);q7<=tmp(7);q6<=not tmp(6);q5<=not tmp(5);q4<=tmp(4);q3<= tmp(3);q2<=tmp(2);q1<= tmp(1);q0<=tmp(0);end rtl;yimaqilibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity yimaqi isport(Q12,Q11,Q10,Q9,Q8,Q7,Q6,Q5,Q4,Q3,Q2,Q1,Q0:in std_logic;selt :out std_logic_vector(3 downto 0));end yimaqi;architecture rtl of yimaqi issignal sel:std_logic_vector (12 downto 0);beginsel<=Q12&Q11&Q10&Q9&Q8&Q7&Q6&Q5&Q4&Q3&Q2&Q1&Q0;process(sel)begincase sel iswhen"1111111111111" =>selt<="1101";when"1111111111110" =>selt<="1100";when"1111111111101" =>selt<="1100";when"1111111111011" =>selt<="1100";when"1111111110111" =>selt<="1100";when"1111111101111" =>selt<="1100";when"1111111011111" =>selt<="1100";when"1111110111111" =>selt<="1100";when"1111101111111" =>selt<="1100";when"1111011111111" =>selt<="1100";when"1110111111111" =>selt<="1100";when"1101111111111" =>selt<="1100";when"1011111111111" =>selt<="1100";when"0111111111111" =>selt<="1100";when others=>selt<="0000";end case;end process;end rtl;panjueqi:inst2library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity panjueqi isport(a,b:in std_logic_vector(3 downto 0);c:buffer std_logic);end panjueqi;architecture rtl of panjueqi isbeginc<='1'when a>=b else'0';end rtl;xuanzeqi:inst3library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity panjueqi isport(a,b:in std_logic_vector(3 downto 0);c:buffer std_logic);end panjueqi;architecture rtl of panjueqi isbeginc<='1'when a>=b else'0';end rtl;fenpin5:inst4library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity fenpin5 isport(en ,clk :in std_logic;fenp_5_output:out std_logic);end fenpin5;architecture rtl of fenpin5 isbeginprocess(clk,en)variable sum:std_logic_vector(2 downto 0);beginif rising_edge(clk)thenif en='1' thensum:="000";elsesum:=sum+'1';if sum=5 thensum:="000";fenp_5_output<='1'after 10ns;else fenp_5_output<='0';end if;end if;end if;end process;end rtl;Fenpin45:inst5library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity fenpin45 isport(en ,clk :in std_logic;fenp_45_output:out std_logic);end fenpin45;architecture rtl of fenpin45 isbeginprocess(clk,en)variable sum :std_logic_vector(4 downto 0);beginif rising_edge(clk)thenif en='1' thensum:="00000";elsesum:=sum+'1';if sum=44 thensum:="00000";fenp_45_output<='1' after 10ns;else fenp_45_output<='0';end if;end if;end if ;end process;end rtl;clkcontr:inst6library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity clkcontr isport(clk: in std_logic;q: out std_logic);end clkcontr;architecture rtl of clkcontr isbeginprocess(clk)beginif(clk'event and clk='1')thenq<='1';end if;end process;end rtl;rs_clk:inst19library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all; entity rs_clk isport(r,s,res: in std_logic;Q,not_Q: out std_logic);end rs_clk;architecture rtl of rs_clk is signal sel1,sel2:std_logic;beginprocess(res,r,s)beginif(res='0')thensel1<='0';sel2<='1';elsif (s='1'and r='0')thensel1<='1';sel2<='0';elsif (s='0'and r='1')thensel1<='0';sel2<='1';elsif (s='0'and r='0')thensel1<='0';sel2<='1';end if;Q<=sel1;not_Q<=sel2;end process;end rtl;VHDL:分频模块输出45:识别器模块仿真结果选择器输出来确定判决门限帧同步输出波形仿真:参考文献:黄智伟 .基于FPGA数字通信系统建模设计.电子工业出版社。

AOS帧同步系统的FPGA设计

AOS帧同步系统的FPGA设计

王晓勇;李健

【期刊名称】《微计算机信息》

【年(卷),期】2008(024)002

【摘要】本文从时分复接系统对帧同步系统的性能要求出发,根据AOS系统的要求和特点,提出了一种采用FPGA实现帧同步系统的设计方案,重点介绍了同步保护电路的设计,并给出了FPGA设计的实验仿真,实验结果表明该电路系统工作正确可靠,满足设计要求.

【总页数】3页(P201-202,211)

【作者】王晓勇;李健

【作者单位】010051,内蒙古呼和浩特,内蒙古工业大学信息工程学院;010051,内蒙古呼和浩特,内蒙古工业大学信息工程学院

【正文语种】中文

【中图分类】TP311;TN919

【相关文献】

1.帧同步系统的FPGA设计与实现 [J], 范寒柏;谷力伟;赵冉

2.高级在轨系统(AOS)帧同步信号发送器的设计与实现 [J], 苏鹏冲;李维忠

3.帧同步系统的FPGA设计 [J], 管立新;沈保锁;柏劲松

4.帧同步系统的FPGA设计 [J], 管立新;沈保锁;柏劲松

5.AOS系统中的帧同步技术性能分析与仿真 [J], 肖志东;李帅;田野;毕明雪;陆健

因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA的跳频系统快速同步算法设计与实现

( 1 . C o m m a n d A u t o ma t i o n Wo r k s t a t i o n o fX i n j i a n g Mi l i t a r y R e g i o n , U r u m q i 8 3 0 0 4 2 , C h i n a ; 2 . U n i t 6 9 2 4 0 f 咒 A, o U r u m q i 8 3 0 0 4 2 , C h i n a )

试表 明, 该 快 速 同 步 算 法 建 立 时 短 、 同步 稳 定 可 靠 。

关键词 : 跳 频 ;快 速 同步 ; F P G A; 独 立 信 道 法 ;同步 头法

中图 分 类 号 : T N 9 2 5 + . 1 文献标识码 : A 文 章 编 号 :1 6 7 4 — 6 2 3 6 ( 2 0 1 3 ) 0 7 — 0 1 5 2 — 0 3

第2 1 卷 第 7期

Vo 1 . 21

No . 7

— —

电子设 计 工程

El e c t r o n i c De s i g n En g i n e e r i n g

2 0 1 3年 4月

Ap r .2 01 3

基于 F P G A 的跳频 系统快 速 同步算 法设计 与实现

付睿 智 ,杨 玉彬 ,汤华军

( 1 . 新 疆 军 区指 挥 自动化 工作 站 新 疆 鸟 鲁 木 齐 8 3 0 0 4 2 ; 2 . 6 9 2 4 0部 队 新 疆 乌 鲁 木 齐 8 3 0 0 4 2 ) 摘 要 :同 步技 术是 跳 频 系统 的核 心 。本 文针 对 F P G A 的跳 频 系统 , 设计 了 一 种基 于独 立信 道 法 , 同步 字 头 法和 精 准 时 钟 相 结 合 的 快 速 同步 方 法 , 同 时设 计 了基 于双 图案 的 改进 型 独 立 信 道 法 , 同 步算 法协 议 , 协议帧格式等。该设计使 用 V H D L硬 件 语 言 实现 , 采用 A l t e r a公 司的 E P 3 C 1 6 E 1 4 4 C 8作 为 核 心 芯 片 , 并 在 此 硬 件 平 台上 进 行 了功 能验 证 。 实 际 测

基于FPGA技术的视频信息采集系统的设计与实现的开题报告

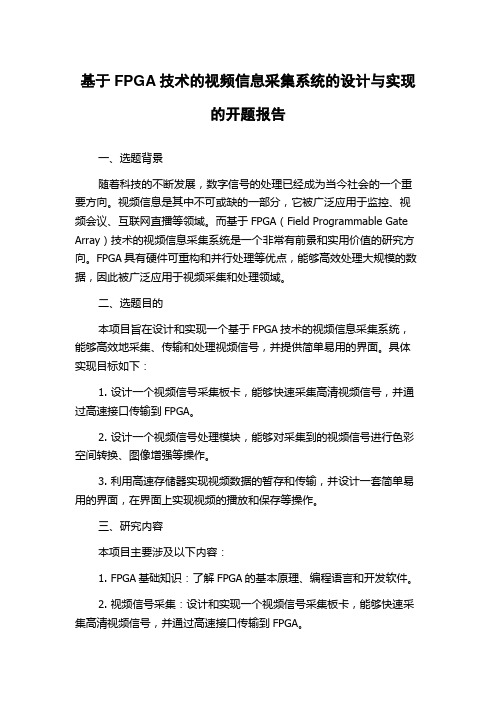

基于FPGA技术的视频信息采集系统的设计与实现的开题报告一、选题背景随着科技的不断发展,数字信号的处理已经成为当今社会的一个重要方向。

视频信息是其中不可或缺的一部分,它被广泛应用于监控、视频会议、互联网直播等领域。

而基于FPGA(Field Programmable Gate Array)技术的视频信息采集系统是一个非常有前景和实用价值的研究方向。

FPGA具有硬件可重构和并行处理等优点,能够高效处理大规模的数据,因此被广泛应用于视频采集和处理领域。

二、选题目的本项目旨在设计和实现一个基于FPGA技术的视频信息采集系统,能够高效地采集、传输和处理视频信号,并提供简单易用的界面。

具体实现目标如下:1. 设计一个视频信号采集板卡,能够快速采集高清视频信号,并通过高速接口传输到FPGA。

2. 设计一个视频信号处理模块,能够对采集到的视频信号进行色彩空间转换、图像增强等操作。

3. 利用高速存储器实现视频数据的暂存和传输,并设计一套简单易用的界面,在界面上实现视频的播放和保存等操作。

三、研究内容本项目主要涉及以下内容:1. FPGA基础知识:了解FPGA的基本原理、编程语言和开发软件。

2. 视频信号采集:设计和实现一个视频信号采集板卡,能够快速采集高清视频信号,并通过高速接口传输到FPGA。

3. 视频信号处理:设计一个视频信号处理模块,能够对采集到的视频信号进行色彩空间转换、图像增强等操作。

4. 高速存储器设计:利用高速存储器实现视频数据的暂存和传输。

5. 界面设计:设计一套简单易用的界面,在界面上实现视频的播放和保存等操作。

四、研究方法本项目采用以下研究方法:1. 文献查阅法:通过查阅相关的专业书籍、学术论文和网络资料,掌握FPGA技术的基本原理和应用。

2. 实验研究法:通过设计和实现一个视频信息采集系统,验证所学理论知识的正确性和实用性。

3. 数据分析法:通过对实验结果的数据分析,总结经验和发现问题,进一步完善和优化系统的性能。

一种基于FPGA帧同步电路设计

( a c n nvri , a ca g302 , h a N nt gU i syN n hn 309 C i ) m e t n

A s a t h r c l o f m nhoi t ni d t o m nco ae nF G e r e .hn bt c :T e i i e f a es cr z i i a cm u i i bsdo P A idsi d T e r p n p ar y n ao n 舀 l tn s cb

等缺点…, 可编程器件的广泛应用 , 为数字系统的设

计 带 来 了极大 的灵 活性 。 由于 可 编程逻 辑 器件可 以 通 过软件 编程 对硬 件 的 结 构 和工 作 方 式 进 行重 构 , 使得 硬件 的设计 可 以如 同 软件 设 计 那 样 快 捷方 便 ; 当今高 速发 展 的 FG /P D兼 有 串 、 P AC L 并行 工作 方 式 和 高速 、 靠性 的特点 L , 可 以结 合具 有 强大 的 高可 2并 ] 行 为描 述能 力和 丰富 的仿真语 句 的 V D H L语 言进 行 描 述 。使其 在 电子 系 统设 计 中得 到 广 泛 的应 用 。 ] 本文 给 出了一种 由全 数字 电路 构成 的帧 同步 电路 的

Th i uti ne rtd i hp o GA.ti h a e o ii z t n a d itga o n c n mmia o y tm . e cr i si tgee n c i fFP c I ste b s fdgt a o n ne rt n i o T i i i c t n sse i Ke r s: F GA;fa y c r nz t n;VIDL lng a e;d gtlc m u c t n y wo d P l me s h i ai n o o - a u g I iia o i n ai o

基于FPGA的视频编码系统设计与实现

基于FPGA的视频编码系统设计与实现基于FPGA的视频编码系统设计与实现摘要:随着数字视频的快速发展,视频编码成为了计算机视觉领域的重要研究方向。

本文主要介绍了基于FPGA的视频编码系统的设计与实现过程。

首先,简要回顾了视频编码的基本原理和常用算法。

然后,详细讨论了FPGA作为硬件加速平台的优势,并介绍了FPGA平台上常用的视频编码算法。

接着,详细描述了视频编码系统的硬件架构设计,包括编码器和解码器的模块划分以及模块之间的通信和数据传输。

最后,进行了实验验证并进行了性能分析,结果表明,基于FPGA的视频编码系统在实时性和编码效率方面均具有较好的性能。

关键词:FPGA、视频编码、编码器、解码器、硬件架构1. 引言随着互联网技术的飞速发展和宽带网络的普及,视频数据的传输和处理需求日益增加。

视频编码作为一种将原始视频信号转换为压缩格式的技术,已经成为了现代多媒体应用中不可或缺的环节。

在视频编码中,编码器将原始视频转换为压缩的码流,而解码器将压缩的码流解码为可视的视频图像。

目前,H.264、H.265等压缩标准已经成为了主流视频编码标准。

2. 视频编码原理和算法视频编码的核心思想是利用视频序列中的时空冗余性进行压缩。

在时域上,视频序列中的相邻帧之间存在大量的冗余信息,可以通过运动估计和运动补偿来减少冗余。

在空域上,同一帧中相邻像素之间也存在冗余,可以通过空间预测编码来提高压缩效率。

常用的视频编码算法主要包括运动估计、变换编码和熵编码等。

3. FPGA在视频编码中的应用优势FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,具有高度灵活性和可编程性。

与传统的视频编码器相比,基于FPGA的视频编码系统具有以下优势:(1)硬件加速平台:FPGA可以提供并行计算和硬件加速的能力,能够显著提高视频编码的处理速度和性能;(2)可嵌入性:FPGA可以嵌入到视频采集设备、摄像头等设备中,具有较小的体积和功耗;(3)可定制性:FPGA可以根据不同的视频编码需求进行定制开发,提供更灵活的编码方案。

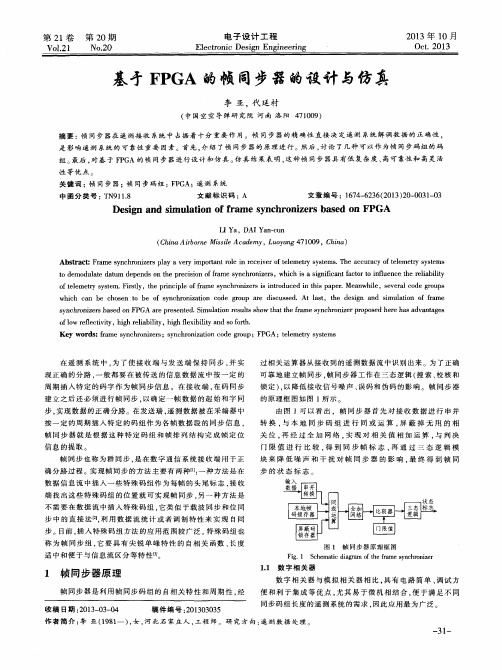

基于FPGA的帧同步器的设计与仿真

( 中 国 空 空 导 弹研 究 院 河 南 洛 阳 4 7 1 0 0 9)

摘要: 帧 同步 器 在 遥 测 接 收 系统 中 占据 着十 分 重要 作 用 。 帧 同步 器 的精 确 性 直接 决 定 遥 测 系统 解 调 数 据 的 正 确 性 , 是 影 响 遥 测 系统 的 可 靠 性 重 要 因素 。首先 , 介 绍 了帧 同 步 器 的 原 理 进 行 。然 后 , 讨 论 了几 种 可 以 作 为 帧 同 步 码组 的码

De s i g n a n d s i mu l a t i o n o f f r a me s y nc h r o n i z e r s b a s e d o n FPGA

LI Ya,DAI Ya n— cu n

( C h i n a Ai r b o r n e Mi s s i l e Ac a d e my, Lu o y a n g 4 7 1 0 0 9,C h i n a )

t o d e mo d u l a t e d a t u m d e p e n d s o n t h e p r e c i s i o n o f f r a me s y n c h r o n i z e r s ,w h i c h i s a s i g n i f i c a n t f a c t o r t o i n lu f e n c e t h e r e l i a b i l i t y

wh i c h c a n b e c h o s e n t o b e o f s y n c h r o n i z a t i o n c o d e g r o u p a r e d i s c u s s e d .At l a s t ,t h e d e s i g n a n d s i mu l a t i o n f o f r a me s y n c h r o n i z e r s b a s e d o n F P G A a r e p r e s e n t e d . S i mu l a t i o n r e s u l t s s h o w t h a t t h e f r a me s y n c h r o n i z e r p r o p o s e d h e r e h a s a d v a n t a g e s f o l o w r e l f e c t i v i t y , h i g h r e l i a b i l i t y , h i g h l f e x i b i l i t y a n d S O f o r t h .

FPGA_ASIC-基于FPGA的快速位同步系统设计

基于FPGA的快速位同步系统设计管立新(赣南师范学院电子信息学院 江西赣州, 341000)摘 要:从时分复接系统对位同步系统的性能要求出发,提出了一种基于FPGA的快速位同步系统的设计方案,给出了位同步系统的实验仿真,结果表明该系统有较快的位同步建立时间,节省了FPGA的耗用资源,系统工作稳定、可靠。

关键词:位同步;同步建立时间;现场可编程门阵列;仿真中图分类号:TP311;TN919 文献标识码:AFast Bit Synchronization System Design Based on FPGAGUAN Li-XinElectronic Information Science Department Of Gannan Teacher’s College,GanZhou JiangXi, 341000,china Abstract: According to the performance requirement of bit synchronization in Time Division Multiplexer system, the paper proposed a method to design fast bit synchronization system based on FPGA. The imitation and experiment of bit synchronization system were given, experiment result shows, the system can build synchronization quickly, the circuit work stably and reliable.Keywords: Bit synchronization;Synchronization Build Time;FPGA;Imitation1 引言在时分复接通信系统中,位同步是收、发两端的时钟频率必须同频、同相,这样在接收端才能正确地判决发送端送来的每一个码元。

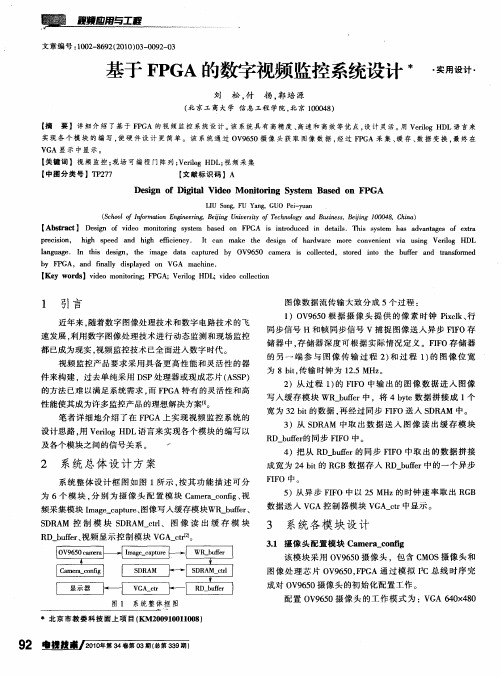

基于FPGA的数字视频监控系统设计

【 src 】 D s n o i o m n ̄r g ss m b sd o F G s it d cd n dti .r i ss m hs a vn gs f et Abtat ei fvd o i i yt ae n P A i n oue i e l r s yt a d at e o xr g e n e r as h e a a

的另一 端 参 与 图像 传 输 过程 2 和 过 程 1 的 图像位 宽 ) )

为 8bt传 输 时 钟 为 l . MHz i. 25 。

2 )从 过 程 1 的 FF 中 输 出 的 图 像 数 据 进 入 图 像 ) IO

写 人 缓 存 模 块 W R b f r ,将 4 b t 据 拼 接 成 1个 _ uf 中 e ye数 宽 为 3 i 的数 据 , 经 过 同步 F F 2bt 再 IO送 人 S RA 中 。 D M

速发展 , 利用数字图像处理技术进行动态监测 和现场监控 都已成为现实 , 视频监控技术 已全面进入数字时代。

视 频 监 控 产 品要 求 采 用 具 备 更 高性 能 和灵 活 性 的器 件 来构 建 ,过 去单 纯 采 用 D P处 理 器 或 现成 芯 片 ( S P S A S)

的方法 已难 以满 足 系统 需 求 . F GA特有 的灵 活 性 和高 而 P

LI S n ,F Ya g U o g U n ,GUO P i y a e- u n

(c olo fr ain E gn eig e ig U iesy o eh ooy ad B s s,B rn 0 0 8 hn ) Sho f I om t n i r ,B in nvri f Tc nlg n ui s e i 10 4 ,C i n o e n j t e n g a

CameraLink数字视频光纤传输系统的FPGA实现

收稿日期:2012-08-19作者简介:李志强(1980-),男,硕士,助理研究员,主要从事电子学硬件和软件设计方面的研究,E-mail:mybugatti@ 。

长春理工大学学报(自然科学版)Journal of Changchun University of Science and Technology (Natural Science Edition )第35卷第4期2012年12月Vol.35No.4Dec.2012Camera Link 数字视频光纤传输系统的FPGA 实现李志强,张建华(中国科学院长春光学精密机械与物理研究所;中国科学院航空光学成像与测量重点实验室,长春130033)摘要:为解决实时转动的光电平台中高速Camera Link 数字视频信号的传输问题,在光电平台设计中采用了光纤滑环替代传统的导电滑环作为传输介质,为此提出了一种基于FPGA 的Camera Link 接口转光纤信号传输的设计方案。

利用FP-GA 强大的并行处理能力,采用乒乓缓存技术将Camera Link 视频信号编解码并传输,解决了Camera Link 数字视频信号数据量大导电滑环难以实时传输的问题。

试验结果表明,在传输速率120Mb/s 的条件下系统可长时间稳定工作,最高传输速率可达到1.25Gb/s 。

关键词:Camera Link ;光纤传输;FPGA ;乒乓缓存;FIFO 中图分类号:TP394.1;TH691.9文献标识码:A 文章编号:1672-9870(2012)04-0109-04Realization of Camera Link Digital Video FiberTransmission System Based on FPGALI Zhiqiang ,ZHANG Jianhua(Key Laboratory of Airborne Optical Imaging and Measurement ,Changchun Institute of Optics ,Fine Mechanics and Physics ,Chinese Academy of Sciences ,Changchun 130033)Abstract:In order to transmit the high-speed Camera Link digital video signal in the continuous rotate Opto-electronic platform ,we used a fiber-optical rotating connecter instead of the traditional electrical rotating connecter as the transmis-sion medium ,and designed a Camera Link to fiber transmission system based on FPGA.By its strong ability of parallel processing ,it can decode and encode Camera Link digital video by ping-pang operation ,then transmit them.The data of camera link digital video signal is large and the slip ring is difficult to real-time transmisson.But now ,these problems are all resolved by this system in some degree.The result of the examination has proved that the system can work steadily in a long time on the transmit speed of 120Mb/s ,and its top transmit speed can reach 1.25Gb/s.Key words:Camera Link interface ;fiber transmission ;FPGA ;ping-pang cache ;FIFO随着基于数字成像技术的遥感相机和光电设备在视场和分辨率指标要求上的不断提高,所采用的数字CCD 图像数据量急剧增加,同时要将图像传送到上位机实时显示,对传输通道带宽的要求大幅度提高,传统的电传输方式已经很难满足传输速度和传输距离的要求,因此光纤传输技术越来越多地被应于数字图像的传输。

基于FPGA的视频图像处理系统的研究与设计

1 引 言

FG P A具 有结 构 灵 活 、 用性 强 、 于 维 护 和 通 便

( L ) 1 2个 IO管 脚 。 D L ,8 /

芯片 驱 动 单 元 采 用 F G P A专 用 X 1 V 1的 C8 O P A , 系统更稳 定 , 大 。 R M 使 更强 视频 处理 单元采 用 A I 司的 A V 19 具 D公 D 77 ,

关键词: P A; F G 视频 处理 ; 号发 生 ; 频编码 芯 片 ;IO 信 视 FF

中 图分 类号 :N 4 T 95

文献标识 码 :A

Re e r h a d De in o d o I g r c sig s a c n sg fVi e ma eP o e sn

8 4计 数 时输 出一 个 t m信 号 , 其 作 为垂 直 行 6 e r 将 计数器 的 使 能 信 号 , 垂 直 行 计 数 器 开 始 计 数 。 使 图 2为 同步时序部 分波形 图 。

I . 一行消隐一. 1 .

V y  ̄ I .. J s n . .__ .. .. .

识情 况如 下 : 1 )场 同 步 开 槽 脉 冲 期 间 :A = V C, = C B

GND;

3 原 理 设计

图 1 系统 框 图。 为

2 前后 均衡 脉冲期 间 : =V C, V C; ) A C B: C

视频

显 示 时序

竺一

3 行 同步期 间 : ) A=G D, N B=V C; C

图 1 系统 框 图

号, 设置 输 入 不 同 组 合 可 以 产 生 不 同 的 同 步 信 号 , 而 清 晰 地 看 出不 同 的 同 步 信 号 对 电 视 图 从 像 的影 响 。

基于FPGA的视频采集系统设计

Ab st r a c t The p a p e r a i ms t o s t u d y t h e r e a l i z a t i o n o f FPGA- ba s e d v i d e o c a pt ur e s y s t e m. I t u s e s Ve r i l o g h a r dwa r e d e s c r i pt i o n 1 a n g u a g e t o d e s i g n a n d v e r i f y t h e mo d u l e s o f t h e s y s t e m ,i n c l u d i n g I C b u s s y s t e m c o n f i g u r a t i o n mo d u l e ,I TU

a l — t i me d i s pl a y a s we l 1 . Th e s y s t e m a l s o pr o v i de s a mor e f l e x i b l e a n d e f f i c i e n t p o s s i b i l i t y f o r v i d e o c o l l e c t i o n b a s e d o n FPGA. Th e s y s t e m h a s t h e a d v a n t a g e s o f s ma l l s i z e,h i g h e f f i c i e n c y,l o w c O S t ,a n d c a n b e wi d e l y us e d i n v i d e o p r o c e s s i n g s ys t e ms ,s e c u r i t y mo n i t o r i n g s y s t e ms a n d

基于FPGA的立体视频画面分割模块的设计与实现

l 【 要】 摘 在偏光式立体投影机领域, 复合立体视频的分解主要通过计算机显卡的双屏输出功能来 》实现 , 系统的视频接收模块和外部连接结构复杂, 视频播放依赖于特定硬件需求的计算机。为解决这一

;问题 , 出了一种应用于偏光式 3 提 D投影 系统的视频画面分割模块的设计和实现方法。 视频画面分割模 ;块基于 F G P A技术, 采用 S R M作为图像帧缓存 , DA 对立体视频 中左右画面进行 实时分割和同步传输 , }能够替代计算机显卡的双屏输出功能。模块易于集成在投影 系统中, 可简化 系统的视频接收模块和外 ;部连接结构, 实现独立立体视频播放 功能。 l 关键词 : 立体视频 ; 画面分割 ;P A; D A FG S R M i 【 btat / e edo oai dtre dm ninl r etrcm l re dm ni a v es A s c】 nt l r hf i fp l z e- ies a Po co,o pe t e - i s nl i o re h o j xh e o d

算 i

■ ・ 卜一 i —

陈鼎如 苏 萍 马建设 ( 清华大 学 深圳研 究生院 , 深圳 5 8 5 ) 10 5 De in a d L l me t t fF sg n mp e n a i o PGA- a e D Vi e c u e Se on b s d 3 d o Pit r gme t t n Mo l n a i due o

;hpjt st , d reemdent rf ot eea 。 ei t c p t rei ye t i。e r 。 za etc, fh r nc 凡r 。 l e oc 凡 s, h e c “ dhs u t l nt 2 m e ‘。 ne “ ℃ e nc 。 e ,

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

万方数据

万方数据

拟同步信号锁定的SDI流经过数字切换台进行切换,然

后通过视频编码器将数字信号转换成模拟信号由电视

机显示。

其中一路SDI用测试好的数字帧同步机进行锁

定.另一路由本设计的帧同步模块外加并转串和电缆驱

动来生成。

如果两路切换时图像没有抖动、错位以及乱

点.则说明帧同步模块的同步效果无误。

以上平台中用到并转串和串转并模块都是由FPGA内部资源编程实现的。

用到的电视机均为模拟电视机。

接口为CVBS。

测试结果显示。

在用FPGA和SDRAM进行帧缓存从而达到视频同步的过程中。

并没有丢失任何音频数据

包.不管从示波器观察.还是从电视机发出的声音来判

断,都不会有失真。

同时系统也可以与其他被本地模拟

同步信号锁定的视频源进行切换,电视机显示的图像即

不会抖动、失真或错位,用示波器观察两路数字视频转

换为的模拟视频信号亦是同步的。

在进行系统测试的时候,为方便调试,用QUARTUSII自带的虚拟逻辑分析仪从FPGA的JTAG口采集内部数

据来方便地进行观察分析,从而判断m逻辑错误的单元

进行一一修正。

为了方便分析,采集样值时一帧数据的

起点从第7行的EAV开始。

各个信号的含义如下:sa用

于连接SDRAM的地址总线,ras~n,cas_n和we一13用于连

接SDRAM的控制线,dq用于连接SDRAM的数据总线。

new_frame—in为输入端帧起始标志。

new_frame_out为输

出端帧起始标志。

如图5所示.Sr)RAM控制模块接收到输入端帧起始标志new_frame—in信号的正脉冲后,清空写地址寄存

器,然后等待状态机进入突发写状态,开始生成写命令,

即行有效信号ras—rl的负脉冲时刻同时发送行地址,ca8

延时后列有效信号cas_n和写有效信号wen的负脉冲

时刻同时发送列地址。

此刻,数据线的第7行视频数据

将顺序存入SDRAM。

南前述章节可知,第7行数据的

EAV中XYZ的值为2D8。

与图中数据相符。

图5帧存的起始数据

如图6所示.SDRAM控制模块接收到输出端帧起始标志newframe_out信号的正脉冲后,清空读地址寄存

器,然后等待状态机进入突发读状态.开始生成读命令,321塑塑垄正丽孬i磊虿i鬲葡面再i面

即行有效信号ras—n的负脉冲时刻同时发送行地址,CAS延时后列有效信号cas—n的负脉冲时刻同时发送列地址。

此刻,数据线顺序出现南SDRAM中读取的第7行视频数据。

图6帧读取的起始数据

5结论

通过对系统的联合测试和对采集的实验数据分析,本文设计的系统运行效果良好、性能稳定、成本较低,适合在电视台演播室使用、推广。

参考文献:

【1J吴继华,王诚.AheraFPGMCPLD设汁(高级篇)【Mj.北京:人民邮电出版社,2005.

【2】陈明义。

夏海曼,周建国.高速大容量FIFO的设计【J】.电子科技.2008,21(6):1.4.

【3】黄伟,罗新民.基于FPGA的高速数据采集系统接口设计【J】.单片机与嵌入式系统设计.2006(4):10—13.

【4】郭四稳,古乐野.多通道大容量高速数据采集系统【J】.四川大学学报,200l,38(1):29—32.

责任编辑:任健男

◇

收稿日期:2009一舢仁18

今典影视传媒集团与美国科视公司

达成战略合作协议

8月26日,今典与美国科视数字系统有限公司达成战略合作。

于2010年年底前.完成800套科视

CP2000系列DLPCinema@数字电影放映机和800套

蒙太奇CDCS2000数字电影服务器的安装。

随着800

台蒙太奇2K设备的投放.2009年至2010年,中国电

影市场将会在原来的基础上新生800块数字银幕,总

量将达到2500至3000块,占目前全国银幕总量的

70%以上。

蒙太奇CDCS2000数字电影服务器,是今典影视传媒与美国Doren,i公司合作研发的完全符合好莱坞DCI

技术规范的数字电影服务器。

其2K超高图像分辨率、

JPEG2000压缩算法和250Mbiffs数据量带给观众无与

伦比的数字电影观看效果。

万方数据。