显示译码器和卡诺图_论文

显示译码器及译码器的应用

Digital Logic Circuit

教学方法设计: 强调MSI器件的应用,培养查手册的能力。

课堂讨论: 1. 二进制译码器与显示译码器有何区别? 2. 常用显示器件的应用场合?

现代教学方法与手段: 大屏幕投影

复习(提问): 1. 为何要使用显示译码器? 2. 数字0-9如何用七段来显示? 3. 字母能用七段显示吗?如何显示?

A3 A2A1A0

LT RBO RBI

A3 A2A1A0

LT RBO RBI

A3 A2A1A0

LT RBO RBI

A3 A2A1A0

0 000

0 000

10 01

0 01 1

0111

00 00

整数部分:高位的 BI / RBO 与低位的RBI 相连 小数部分:低位的 BI / RBO 与高位的RBI 相连

Digital Logic Circuit

显示译码器及译码器的应用

课时授课计划 课程内容

Digital Logic Circuit

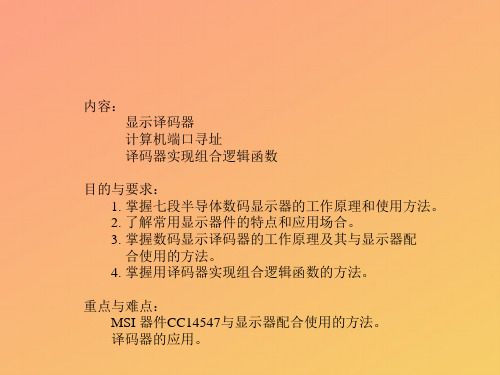

内容: 显示译码器 计算机端口寻址 译码器实现组合逻辑函数

目的与要求: 1. 掌握七段半导体数码显示器的工作原理和使用方法。 2. 了解常用显示器件的特点和应用场合。 3. 掌握数码显示译码器的工作原理及其与显示器配 合使用的方法。 4. 掌握用译码器实现组合逻辑函数的方法。

Digital Logic Circuit

功能或 十进制数 BI / RBO (灭灯)

LT (试灯) RBI (动态灭零)

0 1 2

功3 能4 表5

6 7 8 9 10 11 12 13 14 15

《数字电子技术》课期末考试复习题复习课程

《数字电子技术》课期末考试复习题复习课程一、填空题(每小题△△分,共△△分)(1)逻辑代数中的三种基本的逻辑运就是(与)运算、(或)运算和(非)运算。

(2)逻辑变量和逻辑函数的取值惟独(0)和(1)两种取值。

它们表示两种相反的逻辑状态。

(3)与逻辑运算规则能够归纳为有0出(0),全1出(1)。

(4)或逻辑运算规则能够归纳为有1出(1),全0出(0)。

(5)与非逻辑运算规则能够归纳为有(0)出1,全(1)出0。

(6)或非逻辑运算规则能够归纳为有(1)出0,全(0)出1。

(7)二极管从导通到截止所需时刻称为(开通)时刻。

(8)OC门是集电极(开路)门,使用时必须在电源VCC与输出端之间外接(电阻)。

(9)在数字电路中,三极管工作在(饱和)状态和(截止)状态。

(10)三态输出门输出的三个状态分不为(低电平)、(高电平)、(高阻态)。

(11)逻辑代数中三条重要的规则是(代入)规则、(对偶)规则和(反演)规则。

(12)化简逻辑函数的要紧办法有(代数)化简法和(卡诺图)化简法。

(13)逻辑函数的表示办法要紧有(函数表达式)、(真值表)、(逻辑)、卡诺图和波形图。

(31)编码器按功能别同分为(二进制)编码器、(二-十进制)编码器和优先编码器。

(32)译码器按功能别同分为(二进制)译码器、(二-十进制)译码器和显示译码器。

(33)8选1数据挑选器在所有输入数据都为1时,其输出标准与或表达式共有( 8 )个最小项。

(34)输入3位二进制代码的二进制译码器应有( 8 )个输出端,共输出( 8 )个最小项。

(35)共阳极LED数码管应由输出(低)电平的七段显示译码器来驱动点亮。

而共阴极LED数码管应由输出(高)电平的七段显示译码器来驱动点亮。

(41)二进制数是以( 2 )为基数的计数体制,十进制数是以( 10 )为基数的计数体制,十六进制是以( 16 )为计数体制。

(42)十进制数转换为二进制数的办法是:整数部分用(除2取余),小数部分用(乘2取整)法。

湖大数字电路与逻辑设计试卷答案

数字电路与逻辑设计1_3试卷和答案一、填空(每空1分,共45分)1.Gray码也称循环码,其最基本的特性是任何相邻的两组代码中,仅有一位数码不同,因而又叫单位距离码。

2.二进制数转换成十进制数的方法为:按权展开法。

3.十进制整数转换成二进制数的方法为:除2取余法,直到商为0 止。

4.十进制小数转换成二进制数的方法为:乘2取整法,乘积为0或精度已达到预定的要求时,运算便可结束。

5.反演规则:对于任意一个逻辑函数式F,如果将其表达式中所有的算符“·”换成“+ ”,“+ ”换成“·”,常量“0”换成“ 1 ”,“ 1 ”换成“0”,原变量换成反变量,反变量换成原变量,则所得到的结果就是。

称为原函数F的反函数,或称为补函数6.n个变量的最小项是n个变量的“与项”,其中每个变量都以原变量或反变量的形式出现一次。

对于任何一个最小项,只有一组变量取值使它为 1 ,而变量的其余取值均使它为0 。

7.n个变量的最大项是n个变量的“或项”,其中每一个变量都以原变量或反变量的形式出现一次。

对于任何一个最大项,只有一组变量取值使它为0 ,而变量的其余取值均使它为 1 。

8.卡诺图中由于变量取值的顺序按格雷码排列,任何几何位置相邻的两个最小项,在逻辑上都是相邻的。

,保证了各相邻行(列)之间只有一个变量取值不同。

9.卡诺图化简逻辑函数方法:寻找必不可少的最大卡诺圈,留下圈内没有变化的那些变量。

求最简与或式时圈 1 、变量取值为0对应反变量、变量取值为1对应原变量;求最简或与式时圈 0 、变量取值为0对应原变量、变量取值为1对应反变量。

10.逻辑问题分为完全描述和非完全描述两种。

如果对于输入变量的每一组取值,逻辑函数都有确定的值,则称这类函数为完全描述逻辑函数。

如果对于输入变量的某些取值组合逻辑函数值不确定,即函数值可以为0,也可以为1(通常将函数值记为Ø或×),那么这类函数称为非完全描述的逻辑函数。

译码器及译码显示课件

显示器选择

根据显示需求选择合适的显示器,如LED显示屏、LCD显示屏等, 考虑分辨率、亮度、色彩等方面。

性能参数

比较不同产品性能参数,如响应时间、稳定性、寿命等,选择符合实 际需求的设备。

译码器与显示器的接口连接

接口类型

了解译码器与显示器支持的接口类型,如TTL、 RS232、USB等,确保接口匹配。

译码器及译码显示 课件

目录

• 译码器概述 • 常见译码器芯片 • 译码器应用实例 • 译码显示技术 • 译码器与显示器的选择与使用

01

CATALOGUE

译码器概述

译码器的定义与功能

定义

译码器是一种多输入、多输出的 组合逻辑电路,用于将输入的二 进制代码转换为相应的输出信号 。

功能

译码器的主要功能是根据给定的 输入地址,将对应的存储单元或 电路驱动,从而实现数据的读取 、写入或控制操作。

优点

结构简单,使用方便,能够实现多路选择功能。

3

缺点

仅适用于3位二进制代码译码,扩展性有限。

用74HC4040实现BCD到7段显示译码

应用实例

在数字显示系统中,使用74HC4040驱动7段数码管 显示数字。

优点

能够直接驱动7段数码管,显示效果好。

缺点

仅适用于BCD码到7段数码管的译码,应用范围较窄 。

02

CATALOGUE

常见译码器芯片

74HC138译码器

一个3线-8线译码器,具有使能输入端,可以控制译码器在有 效电平下工作。

74HC138是一个3线-8线译码器,具有3个使能输入端和8个 输出端。当使能输入端处于有效电平时,译码器将输入的3位 二进制代码译码为对应的输出信号。这种译码器常用于地址 解码、数据分路等应用中。

三八译码器的结构、原理与设计_毕业论文

题目:三八译码器的结构、原理与设计学院:物理学院专业:电子科学与技术姓名:董少雨指导教师:赵宏亮完成日期:2014年5月20日毕业论文任务书毕业论文题目:三八译码器的结构、原理与设计选题意义、创新性、科学性和可行性论证:如今全球信息化的步伐正在不断加快,数字信号的产生、变换等方面应用的更加广泛。

三八译码器在信号处理方面起着十分重要的作用。

本文主要阐述三八译码器的基本结构和工作原理,并通过对时序逻辑电路设计方法的研究,完成三八译码器的设计。

主要内容:译码器的种类与特点,三八译码器的结构和工作原理,最后完成了三八译码器的设计。

目的要求:1、熟悉三八译码器的发展背景和趋势。

2、掌握各类译码器的工作性能。

3、了解三八译码器的基本结构和工作原理。

4、学会时序逻辑电路的设计方法。

计划进度:2013年12月21日~2014年2月25日,确定毕业论文选题,并搜集资料,查阅相关文献;2014年2月26日~4月10日,写出论文总体大纲,运用软件得到仿真数据;2014年4月11日~4月25日,论文撰写;提交初稿;2014年4月26日~5月19日,修改论文,论文定稿,准备答辩。

指导教师签字:主管院长(系主任)签字:2013年12 月25 日辽宁大学本科毕业论文(设计)指导记录表论文题目三八译码器的结构、原理与设计学生姓名董少雨学号101002103 年级、专业10级电子科学与技术指导教师姓名赵宏亮指导教师职称讲师所在院系物理学院第一次指导(对确定题目、毕业论文(设计)任务书的指导意见):由于以前对三八译码器有所了解,《三八译码器的结构、原理与设计》题目符合毕业论文设计的要求。

研究三八译码器可以加强对数字集成电路的了解,毕业论文进度安排合理,接下来按照进度写出论文总体大纲。

指导方式:(请选择)面谈√电话电子邮件指导教师签字:2013年12月24日第二次指导(对论文提纲的指导意见):查阅相关资料,进一步地掌握三八译码器的基本结构和工作原理,三八译码器的设计方法十分合理,要熟悉掌握相关软件的使用并从中得到相关数据。

中山大学数电实验四 译码显示电路

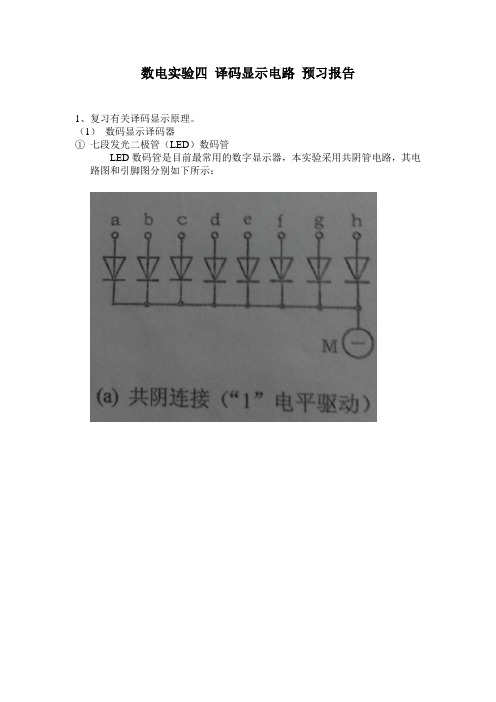

数电实验四译码显示电路预习报告1、复习有关译码显示原理。

(1)数码显示译码器①七段发光二极管(LED)数码管LED数码管是目前最常用的数字显示器,本实验采用共阴管电路,其电路图和引脚图分别如下所示:一个LED数码管可用来显示一位0—9十进制数和一个小数点。

小型数码管(0.5寸和0.36寸)每段发光二极管的正向压降,随显示光(通常为红、绿、黄、橙色)的颜色不同略有差别,通常约为2—2.5V,每个发光二极管的点亮电流在5—10mA.LED数码管要显示BCD码所表示的十进制数字就需要有一个专门的译码器,该译码器不但要完成译码功能,还要有相当的驱动能力。

②BCD码七段译码驱动器本实验采用74LS48 BCD码锁存/ 七段译码/ 驱动器,驱动共阴极LED 数码管。

下图为74LS48引脚排列,其中:A、B、C、D—BCD码输入端。

a、b、c、d、e、f、g—译码输出端,输出“1”有效,用来驱动共阴极LED数码管。

__ __LT —灯测试输入端,LT = “0”时,译码输出全为“1”.____ ____RBI —灭零输入端,RBI = “0”时,不显示多余的零。

_______BI/RBO —作为输入使用时,灭灯输入控制端;作为输出端使用时,灭零输出端。

(2)扫描式显示对多位数字显示采用扫描式显示可以节电,这一点在某些场合很重要。

对于某些系统输出的数据,应用扫描式译码显示,可使电路大为简化。

有些系统,比如计算机,某些A/D转换器,是以这样的形式输出数据的:由选通信号控制多路开关,先后送出(由高位到低位或由低位到高位)一位十进制的BCD码,如下图所示:图中的Ds称为选通信号,并假定系统按先高位后低位的顺序送出数据,当Ds1为高电平时送出千位数,Ds2为高电平时送出百位数,依此类推。

一般Ds的高电平相邻之间有一定的间隔,选通信号可用节拍发生器产生。

扫描显示时,要求扫描频率要够高,利用视觉暂留效应就可以看到所有位都稳定地亮着。

译码器的分析与应用研究_计算机科学与技术

译码器的分析与应用研究_计算机科学与技术摘要:译码器的作用是将一种编码形式转换为另一种编码形式,如将二进制数转换为十进制数或将ASCII码转换为字符。

本文主要介绍了译码器的原理、分类、应用和设计方法,并结合实例进行分析。

关键词:译码器,编码,转换,分类,应用,设计一、译码器的概念和原理译码器是一种电子器件,可以将一种编码形式转换为另一种编码形式,常见的编码形式有二进制、十进制、ASCII码等。

译码器的原理是根据输入信号的编码形式和输出信号的编码形式之间的对应关系,将输入信号转换为相应的输出信号。

二、译码器的分类根据输入与输出信号的编码形式之间的对应关系,译码器可以分为以下几种类别:1. 数字译码器:将二进制编码转换为十进制编码,也叫BCD译码器。

2. 字符译码器:将ASCII码转换为字符,也叫ASCII码译码器。

3. 时间译码器:将数字信号转换为时间信号。

4. 逻辑译码器:将逻辑信号转换为布尔运算结果。

5. 应用特定译码器:根据应用场景的需要进行设计,如将音频信号转换为数字信号等。

三、译码器的应用译码器在数字电路中有广泛的应用,如在计算机、手机、数码相机等电子产品中,译码器用于将二进制编码转换为十进制数、字符、时间等,以实现数据的输入、输出和处理。

此外,译码器还可以用于编码解码、数字信号处理、音视频处理等方面。

四、译码器的设计方法设计译码器需要考虑译码器的输入、输出信号的编码形式及其对应关系,以及设计实现的速度、功耗和面积等方面。

常用的译码器设计方法有静态译码器、动态译码器和组合译码器等。

在设计过程中需要根据应用场景的需要进行选择和优化,以满足实际需求。

五、结论译码器作为一种常见的电子器件,在数字电路的实现中发挥了重要的作用。

本文介绍了译码器的概念、原理、分类、应用和设计方法,对于理解数字电路和设计电子产品具有一定的参考价值。

数字电子技术基础第三版第三章答案

题3.10数据选择器和数据分配器各具有什么功能?若想将一组并行输入的数据转换成串行输出,应采用哪种电路?

答:数据选择器根据控制信号的不同,在多个输入信号中选择其中一个信号输出。数据分配器则通过控制信号将一个输入信号分配给多个输出信号中的一个。若要将并行信号变成串行信号应采用数据选择器。

试设计符合上述要求的逻辑电路(器件不限)。

解:题目中要求控制信号对不同功能进行选择,故选用数据选择器实现,分析设计要求,得到逻辑表达式:

。

4选1数据选择器的逻辑表达式:

。

对照上述两个表达式,得出数据选择器的连接方式为:

A0=C1,A1=C2, , , , 。

根据数据选择器的连接方程,得到电路如习题3.3图所示。

1

0

0 0

1 0 0 0

1

0

1 0

1 0 0 1

1

1

1 1

1 0 1 0

1

1

0 1

1 0 1 1

1

0

0 0

1 1 0 0

0

0

1 1

1 1 0 1

0

1

1 0

1 1 1 0

0

1

1 0

1 1 1 1

0

0

0 1

(3)由真值表,作函数卡诺图如习题3.1图(b)所示。

卡诺图化简函数,得到最简与或式:

变换F2的表达式

(2)定义逻辑变量0、1信号的含义。无论输入变量、输出变量均有两个状态0、1,这两个状态代表的含义由设计者自己定义。

(3)再根据设计问题的因果关系以及变量定义,列出真值表。

译码器应用设计实验报告

译码器应用设计实验报告引言译码器(Decoder)是数字电路中常用的逻辑电路之一,它实现了将输入数字码转换成输出端口的控制信号。

译码器被广泛应用于数字系统中,如计算机、通信、测控等领域。

通常情况下,译码器基于真值表或卡诺图设计,可以根据输入的不同编码方式,输出相应的解码结果。

本实验主要介绍译码器的应用设计。

通过实验,我们将学会如何使用译码器来实现数字系统的控制和数据处理任务。

本实验所涉及的译码器有BCD-7段译码器、数值译码器、时序译码器以及存储器译码器等。

实验器材1. 逻辑计算器2. 示波器3. 数字电路实验箱4. 5V直流电源5. 译码器(BCD-7段译码器、数值译码器、时序译码器和存储器译码器)6. LED数码管实验原理1. BCD-7段译码器BCD-7段译码器是将4位BCD码转换成7段数码管显示的译码器。

8个BCD码,分别对应着数字0~9和字母A~F,输出接到控制7个LED数码管的段选端口和1个公共阴极的位选端口。

2. 数值译码器数值译码器是将4位二进制数转换成BCD码的译码器。

通过数值译码器,可以将数字的二进制编码转换成BCD编码,从而实现数字的BCD码显示。

译码器输出接LED数码管的输入端口。

时序译码器是根据不同状态的时序信号,将输入的二进制数码转换成对应的控制信号的译码器。

将时序信号和数码信号分别输入至译码器的两个输入端口,译码器将输出对应的动作信号。

常用于时序控制电路的设计中。

4. 存储器译码器存储器译码器是将存储芯片中的地址码转换成控制芯片的输入信号的译码器。

存储芯片中的地址码分别对应着芯片的不同存储单元,译码器将地址码转换成控制信号,使控制芯片可以正确访问存储芯片中的数据。

实验设计实验步骤:(1)将BCD码8个输入引脚分别接到译码器的8个输入端口上。

(4)将5V直流电源连接到译码器和LED数码管上。

实验结果:输入BCD码0000~1111时,LED数码管正确显示相应的数字0~9和字母A~F。

卡诺图在_数字电子技术_中的应用_田瑞

科技信息引言在高职《数字电子技术》教材中,卡诺图的引入主要是为了化简逻辑函数式,通过合并最小项的方法能比较方便地获得逻辑函数的最简与—或式[1]。

而对于卡诺图的其他用法教材中却讲得很少,笔者在多年的教学中逐渐摸索出卡诺图的其他应用,这些应用将更有助于数字电子技术的教学。

1.卡诺图的基本知识卡诺图是逻辑代数中常用的图解化简法,具体画法是将n 个变量的逻辑函数填入一个平面方格图中,平面方格图包括2n 个小方格,每个小方格代表一个最小项,故又称为最小项图,几何相邻或处在对称位置上的小方格所表示的最小项是逻辑相邻项[2]。

三变量卡诺图如图1所示。

为了保证图中几何位置相邻的最小项在逻辑上也具有相邻性,这些数码不能按自然二进制数从小到大的顺序排列,而必须按图中的方式排列,以确保相邻的两个最小项仅有一个变量是不同的。

特别强调的是卡诺图中最左边与最右边的最小项在逻辑关系上是相邻的;最上边与最下边的最小项在逻辑关系上同样也是相邻的。

卡诺图的这种逻辑相邻关系说明:可以将卡诺图的左、右边闭合卷起来形成一个纵向的圆柱,也可以将卡诺图的上、下边闭合卷起来形成一个横向的圆柱,如图2。

图1三变量卡诺图图2三变量卡诺图形象表示2.卡诺图的应用由于卡诺图具有逻辑相邻的特性,所以可以充分利用卡诺图来实现其他一些应用,以便更好地辅助教学。

2.1利用卡诺图巧记格雷码格雷码是一种常用的无权BCD 码,任意两组相邻代码之间只有一位二进制数码不同,是一种典型的可靠性代码,格雷码的这种特性使它在形成和传输过程中引起的误差较小。

比如,在模拟量的转换中,当模拟量发生微小变化而可能引起数字量发生变化时,格雷码仅改变1位,这样与其他码同时改变两位或多位的情况相比更为可靠,提高电路的抗干扰能力。

由于这种编码所具有的独特性,实际应用中很难记忆。

经研究和探讨,若利用卡诺图按照一定规律取值,可用于实现记忆格雷码。

作法:以四变量ABCD 为例,先画出四变量卡诺图如图3所示,从卡诺图中发现,若按箭头所示的方向顺序取值,对应四位格雷码的输入代码依次分别为0000—0001—0011—0010—0110—0111—0101—0100—1100—1101—1111—1110—1010—1011—1001—1000—0000,其所对应的就是十进制数0~15,其所取的值变化顺序正好即为四位格雷码的编码。

(完整版)数电1-10章自测题及答案(2)

第一章绪论一、填空题1、根据集成度的不同,数字集成电路分位以下四类:小规模集成电路、中规模集成电路、大规模集成电路、超大规模集成电路。

2、二进制数是以2为基数的计数体制,十六体制数是以16为基数的计数体制。

3、二进制数只有0和1两个数码,其计数的基数是2,加法运算的进位规则为逢二进一。

4、十进制数转换为二进制数的方法是:整数部分用除2取余法,小数部分用乘2取整法,十进制数23.75对应的二进制数为10111.11。

5、二进制数转换为十进制数的方法是各位加权系数之和,二进制数10110011对应的十进制数为179。

6、用8421BCD码表示十进制时,则每位十进制数可用四位二进制代码表示,其位权值从高位到低位依次为8、4、2、1。

7、十进制数25的二进制数是11001,其对应的8421BCD码是00100101。

8、负数补码和反码的关系式是:补码=反码+1。

9、二进制数+1100101的原码为01100101,反码为01100101,补码为01100101。

-1100101的原码为11100101,反码为10011010,补码为10011011。

10、负数-35的二进制数是-100011,反码是1011100,补码是1011101。

二、判断题1、二进制数有0~9是个数码,进位关系为逢十进一。

()2、格雷码为无权码,8421BCD码为有权码。

(√)3、一个n位的二进制数,最高位的权值是2^n+1。

(√)4、十进制数证书转换为二进制数的方法是采用“除2取余法”。

(√)5、二进制数转换为十进制数的方法是各位加权系之和。

(√)6、对于二进制数负数,补码和反码相同。

()7、有时也将模拟电路称为逻辑电路。

()8、对于二进制数正数,原码、反码和补码都相同。

(√)9、十进制数45的8421BCD码是101101。

()10、余3BCD码是用3位二进制数表示一位十进制数。

()三、选择题1、在二进制技术系统中,每个变量的取值为(A)A、0和1B、0~7C、0~10D、0~F2、二进制权值为(B )A、10的幂B、2的幂C、8的幂D、16的幂3、连续变化的量称为(B )A、数字量B、模拟量C、二进制量D、16进制量4、十进制数386的8421BCD码为(B)A、0011 0111 0110B、0011 1000 0110C、1000 1000 0110D、0100 1000 01105、在下列数中,不是余3BCD码的是(C )A、1011B、0111C、0010D、10016、十进制数的权值为(D )A、2的幂B、8的幂C、16的幂D、10的幂7、负二进制数的补码等于(D )A、原码B、反码C、原码加1D、反码加18、算术运算的基础是 ( A )A 、加法运算B 、减法运算C 、乘法运算D 、除法运算9、二进制数-1011的补码是 ( D )A 、00100B 、00101C 、10100D 、1010110、二进制数最高有效位(MSB )的含义是 ( A )A 、最大权值B 、最小权值C 、主要有效位D 、中间权值第二章 逻辑代数基础一、填空题1、逻辑代数中三种最基本的逻辑运算是与运算、或运算、非运算。

卡诺图

数字电路中卡诺图的应用与研究王珊珊摘要:迄今为止,未见到一本全面阐述卡诺图知识的专著。

本文将卡诺图在数字电路中的应用进行了系统的总结,按其应用的共同特点分为:在逻辑化简上的应用、在逻辑运算上的应用和在解决电路中问题的应用三大类。

在此基础上,对发现的四个未见文献阐述过的问题:在特殊化简中的区域整体现象、用卡诺图圈“0”的方法把函数化简成与或式应该有的前提条件、奇数个逻辑变量的同或与异或相等的卡诺图证明方法和利用无关项在卡诺图化简中的相应说明作了研究,在这四个问题上作了推证,给出了结论并举例加以说明。

关键词:卡诺图应用推证The Applications and Research on The Karnaugh Map in Digital CircuitWangShanshanAbstract:So far, we have not seen any monographs of karnaugh map。

This paper summarizes any situation of applications on Karnaugh map in digital circuit, its application in common is divided into three big parts:The application of the logic simplification 、The application of the logic operation and The application solve the problems in digital circuit 。

Found four problems that no literature expounded on the basis of the summarizes:The overall regional situation in the special simplification、The prerequisite must have in the karnaugh map circle "0" simplification that make logic function into the most simplified、Prove that same-or gate equal else-or gate in odd number logic variable in Karnaugh map and The application of the related items in the K-map simplification,then do research on this four problems,Made a deduction and gives the conclusion with examples。

浅论数字电子技术中的卡诺图

浅论数字电子技术中的卡诺图1 概述卡诺图是数字电路逻辑设计中不可或缺的工具,学会应用卡诺图,能够有效地简化逻辑电路的分析和设计过程。

本文就卡诺图在分析数字电路方面的应用做了一些探讨性研究。

2 卡诺图在逻辑函数化简时的应用在化简逻辑函数过程中,首先,要先将逻辑函数改写成最小项表达式;其次,将最小项表达式填入卡诺图中,表达式中的最小项对应卡诺图方格填“1”,其余不填或填“0”;再次,合并最小项,相邻的“1”方格圈为一个包围圈,每组含个方格,新的乘积项与各个包围圈一一对应;最后,将所有乘积项相加便可。

一个包围圈方格要尽量多,圈的个数要尽量少。

另外,当0的个数远远小于1时,可以用包围0的方法化简,即可得到反函数,后两侧同时取反,便可得到原函数。

3 卡诺图在进行逻辑函数不同形式之间变化时的应用逻辑函数变化常见的形式一般分为以下5种:“与或”式、“或与”式、“与非——与”式、“或非——或非”式、“与或非”式。

其中“与或”式为逻辑函数基本形式,一般讨论将“与或”式变换为其他4种形式。

3.1 将“与或”式变为“或与”式将卡诺图中“0”方格按“1”方格的规则圈起,“0”方格中变量为原变量,“1”方格中变量为反变量,然后用或运算形式表示,最后对所有变量用与运算表示,即为最简“或与”式。

例1:将逻辑函数L=C+B写为最简“或与”式。

解:(1)逻辑函数L=C+B的卡诺图如图1(a)所示;(2)圈“0”法把能合并的“0”用圈圈出,如图1(c)所示;(3)写出逻辑函数L的最简“或与”表达式。

L=(+)·(A+C)3.2 将“与或”式变为“与非——与非”式可以通过摩根定理将“与或”式变为“与非——与非”式,也可由卡诺图将1方格圈出,每个圈内对应因子进行或运算,然后对所有因子用与运算表示,最后运用L=得出最简“与非——与非”式。

例2:将逻辑函数L=C+B写为最简“与非——与非”式。

解:(1)逻辑函数L=C+B的卡诺图如图1(a)所示;(2)根据卡诺图化简的规则将能够合并的最小项圈出,如图1(b)所示;(3)运用L=对(2)所求表达式进行变换;(4)写出逻辑函数L的最简“与非——与非”表达式。

显示译码器设计的步骤、技巧及案例分析

显示译码器设计的步骤、技巧及案例分析显示译码器是数字技术组合规律中一个很重要的器件,在数字电子技术应用中不行缺少,特殊是在信息技术数字化的今日,其应用越来越广泛,但在组织开展科技创新和电子设计制作比赛活动中,同学在设计制作抢答器、记分器、记时器等电子产品时,总是对如何精确设计出符合功能要求的显示译码器胸中很多,本文对此问题举行了分析与讨论。

从上述分析得出,显示译码器输入变量的多少,取决于输出结果的多少,即输出结果的个数N与输入变量的位数n之间满足N=2n或2n-1表1 输入、输出真值表( 一)表2 输入、输出真值表( 二) 3.2 按照显示形式确定输出变量设计显示译码器在确定了输入变量后,就要按照功能要求设计输出变量。

毕竟需要几个输出变量呢? 经过反复讨论得出其输出变量是由所挑选的种类来确定。

比如要设计一个显示数字5,4,3,2,1,一个显示字母E,L,H,F的显示译码器,虽然两个显示结果的内容和个数都不相同,但是假如两种电路都选用七段数码管,那么两种译码电路输出变量的个数都是7个。

假如显示字母E,L,H,F的电路,挑选五笔划的显示器,那么它的输出变量就惟独5个。

可见显示译码器输出变量的个数,只取决于所选显示器的形式,至于是文字、符号、数码,还是分段、重叠、点阵显示器就是设计者要确定的,假如选分段显示E,L,H,F,那么译码器输出变量的个数就是显示器的分段数,而与输出显示的内容,以及显示结果的多少无关,2,图3所示。

图2 五笔划显示器暗示图图3 七段数码显示器3.3 按照显示方式确定变量状态确定了设计显示译码器的输入、输出变量,要精确地设计出真值表,还必需明确每个变量的状态和译码还原的对应关系,这打算着设计的全过程。

对于输入变量可以把n位二进制代码组合值按递增或递减的挨次与输出结果N一一对应设计,如表1,表2所示。

假如输入符合二进制的特点,只要将全部代码组合与输出确定出对应关系即可,若不符合二进制对应关系,就要将多余的输入组合举行约束,确保功能的实现。

在数字电路设计中巧用卡诺图的探讨

在数字电路设计中巧用卡诺图的探讨

随着时代的发展,数字电路设计的应用越来越广泛。

它是一种非常有效的电路设计方法,可以在较短的时间内达到有效的电路设计。

卡诺图是一种普遍使用的数字电路设计工具,它可以帮助电路分析师提前预测结果,避免出现不可控制的情况。

因此,卡诺图在数字电路设计中至关重要。

本文从两个方面对卡诺图在数字电路设计中的应用进行详细探讨。

首先,卡诺图在数字电路设计中的优势和作用。

卡诺图以图形方式表示数字电路,比继电器原理图更容易理解,而且可以表示复杂的电路结构。

它还可以分解电路,指明每个分支的电路状态,从而将复杂的电路结构简化,减少设计周期的时间和设计的难度,使电路设计变得容易。

此外,由于不同的电路状态会反映在卡诺图上,可以清楚地了解整个电路结构,防止发生意外情况,保障电路设计的有效性和可靠性。

其次,讨论使用卡诺图时应该遵循的原则。

首先,在使用卡诺图前,应先深入了解这种工具的基本原理,并根据实际情况选择正确的图形,以便更轻松地掌握设计的流程。

其次,在制作卡诺图时,应该仔细检查每个节点及其相应的后续动作,确保每个节点的状态是正确的,以便在数字电路设计中达到最佳效果。

最后,卡诺图应该对测试样本进行范围测试,以评估电路产生的结果是否正确。

综上所述,卡诺图在数字电路设计中起着重要作用,应该在设计时巧妙地使用,以避免不必要的损失。

确保每一步都按预期进行,让

电路设计变得更加容易,更有效。

【推选】显示译码器及译码器的应用PPT资料

R

VCC VD IF

LED器件的优缺点:

优点:工作电压较低、体积小、寿命长、工作可靠性高、响应速度快、 亮度高。

缺点:工作电流大,每个字段工作电流约10mA左右。

2. 液晶显示器(LCD)

1)液晶是液态晶体的简称。它是既具有液体的流动性,又具有某些光学特 性的有机化合物。

2)其透明度和颜色受外加电场的控制。 3)控制显示原理:

&

&

&

MSI 器件CC14547与显示器配合使用的方法。

二进制译码器与显示译码器有何区别?

显示译码器主要由译码器和驱动器两部分组成,通常将这两部分集成在一块芯片中。

4)液晶显示器的优缺点

& & & & 因74LS138输出为低电平有效,故选用与非门。

它是既具有液体的流动性,又具有某些光学特性的有机化合物。

共阳极接法:当某段外接低电平时,该段被点亮。 共阴极接法:当某段外接高电平时,该段被点亮。

ab cd

a

f

b

g

ecdFra bibliotekef gh (a) 外形图

a b c d e f g h

(b) 共阴极

+VCC a b c d e f g

h (c) 共阳极

R为限流电阻。VD为工作电压(2V)。IF为工作电流(10mA) 讨论:以上参数选择不当会出现什么后果。

10

本位和为Si,向高位的进位为Ci。 常用显示器件的应用场合?

00 1

0

×

1

低电平输出有效的译码器能产生输入变量的所有最小项的非。

4)将Ai连A2、Bi连A1、Ci-1连A0,则Si、Ci式变为:

卡诺图在数字电路分析和设计中的应用物理学大学论文

Hebei Normal University of Science & Technology本科毕业论文(自然科学)题目:卡诺图在数字电路分析和设计中的应用院(系、部):物理系学生姓名:乔晨龙指导教师:尹承红职称副教授2016年5月23日河北科技师范学院教务处制资料目录1. 学术声明…………………………………………………………………1页2. 河北科技师范学院本科毕业论文(设计)…………………………1~15页3. 河北科技师范学院本科毕业论文(设计)任务书………………1~3页4. 河北科技师范学院本科毕业论文(设计)开题报告……………1~3页5. 河北科技师范学院本科毕业论文(设计)中期检查表…………1页6. 河北科技师范学院本科毕业论文(设计)答辩记录表…………1页7. 河北科技师范学院本科毕业论文(设计)成绩评定汇总表……1~2页8 河北科技师范学院本科毕业论文(设计)工作总结……………1页9 河北科技师范学院本科毕业论文(设计)文献综述……………1~4页10 河北科技师范学院本科毕业论文(设计)外文翻译……………1~15页11 河北科技师范学院本科毕业论文(设计)外文……………1~6河北科技师范学院本科毕业论文卡诺图在数字电路分析和设计中的应用院(系、部)名称:物理系专业名称:物理学学生姓名:乔晨龙学生学号:1112120113指导教师:尹承红2016年05月20日河北科技师范学院教务处制学术声明本人呈交的学位论文,是在导师的指导下,独立进行研究工作所取得的成果,所有数据、图片资料真实可靠。

尽我所知,除文中已经注明引用的内容外,本学位论文的研究成果不包含他人享有著作权的内容。

对本论文所涉及的研究工作做出贡献的其他个人和集体,均已在文中以明确的方式标明。

本学位论文的知识产权归属于河北科技师范学院。

本人签名:日期:指导教师签名:日期:摘要摘要本文简要分析并举例说明了卡诺图表达逻辑函数的方法。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

显示译码器(BCD译码器)对伪码(1010~1111)的讨论王绥成摘要:译码器是多输入、多输出的逻辑电路,它将输入编码转换为输出编码,而通常输入编码和输出编码是不同的。

通常我们所看到的电子设备显示有数字0~9,就是通过译码器连接上LED器件显示出来的。

但是当输入的是伪码的时候,显示译码器(BCD译码器)对其有何种表现值得探讨。

关键词:七段译码器;伪码;二进制代码;Discussion of display decoder (BCD decoder) for pseudo code (1010 ~ 1111)Sui-cheng WangAbstract:Decoder is logic circuit wit much input and output, it will be the logic circuit conversing the input code to output code, and usually input code and output codes are different. We usually see electronic equipment that showed digital 0 ~ 9, it is showed through the decoder connecting LED device .But when the input is pseudo code, whtat display decoder (BCD decoder) performance is for it should be discussed.Key word: Seven-segment decoder; Pseudo code; Binary code一、译码器的概念与分类译码:译码是编码的逆过程,它能将二进制码翻译成代表某一特定含义的信号.(即电路的某种状态)译码器:具有译码功能的逻辑电路称为译码器。

是数字系统和计算机常用的一种逻辑部件。

译码器的分类:唯一地址译码器:将一系列代码转换成与之一一对应的有效信号。

常见的唯一地址译码器:(1)二进制译码器(2)二—十进制译码器(3)显示译码器代码变换器:将一种代码转换成另一种代码。

二、显示译码器(七段显示译码器)在数字系统中工作的是二进制的数字信号,而人们习惯十进制的数字或运算结果,因此需要用数字显示电路,显示出便于人们观测、查看的十进制数字。

显示译码器主要由译码器和驱动器两部分组成,通常这二者都集成在一块芯片中。

概念:不仅将每一个输入代码(四位二—十进制代码)按BCD(8421码)的形式译制为二—十进制信号,而且以驱动显示器(数码管)的形式输出,输入四位二—十进制代码(原变量形式),输出七段控制信号,称为译码显示器。

工作原理实图:(1)最常用的显示器有:半导体发光二极管和液晶显示器。

(2)上图为数码显示器的外形,由七段发光二极管组成。

利用字段的不同组合,可分别显示出0~9十个数字。

脉冲信号 计数器 译码器 驱动器 显示器KHza bcdef g 共阳极显示器 abcde fg共阴极显示器在这里就介绍一个常用的七段译码器常用的集成七段显示译码器----------CMOS 七段显示译码器74HC4511引脚图CMOS 七段显示译码器74HC4511功能表(*标注*)从上面的功能表可以看出当输入为0000~1001时,LED 显示的字形分别从0~9. 但是当输入组合为对伪码(1010~1111)时,七段显示译码器不可能输出11-15的十进制数。

这时候为了排除对伪码的译码,我们可以有以下几种选择: 1)将1010~1111六个代码设定为灭灯;2)将1010~1111六个代码设定特定的符号,以便于检测。

a b c d e f gD 074HC4511 D 3 D 2 D 1 L T BL LE三:对伪码的设定1)将1010~1111六个代码设定为灭灯(*标注*)1)将1010~1111六个代码设定特定的符号,以便于检测逻辑函数功能表输入输出字形A3A2A1A0 a b c d e f g1 0 1 0 0 0 0 0 0 1 01 0 1 1 1 0 0 0 0 0 01 1 0 0 0 1 0 0 0 0 01 1 0 1 0 0 1 0 0 0 01 1 1 0 0 0 0 1 0 0 01 1 1 1 0 0 0 0 0 0 1这就是对伪码进行处理的方法,在输入1010~1111六个伪码设定特定的符号,输出时在七段显示译码器上表现出这样的字形时就可以了解到输入的伪码是哪个。

(但是由于对74HC4511各种功能不了解暂时就设计不出来到底怎么通过电路接上LED显示器显示出这样的字形)。

或者我们可以作这个如下的设定:输入输出字形A3A2A1A0 a b c d e f g1 0 1 0 0 0 0 1 1 0 11 0 1 1 0 0 1 1 0 0 11 1 0 0 0 1 0 0 0 1 11 1 0 1 1 0 0 1 0 1 11 1 1 0 0 0 0 1 1 1 11 1 1 1 0 0 0 0 0 0 0(*标注*)四、结论综上所述,BCD译码器对于伪码(0000~1111)是无效或者消隐的,当输入的编码是所需的时候,输出便是0~9数字;当输入是伪码的时候,这时候输出的都是高电平,是灭灯状态。

这时候们可以设置为当输入是伪码时可以显示出其他相当于“乱码”的字形,以提醒我们输入已经超过。

通常情况下0~9数字是需要的,因而输入伪码的就被界定都灭灯。

如若要使用伪码的话可以使用两个七段译码器,个位用一套显示电路,十位用一套显示电路。

参考文献:㈠John F.Wakerly 《数字设计原理与实践第四版》机械工业出版社,2007㈡标注的都为网上参考。

卡诺图化简所应用的逻辑代数原理与方法进行讨论王绥成摘要:从逻辑函数的逻辑代数定理引申出卡诺图化简,从而在卡诺图化简上分析是如何应用逻辑代数定理在卡诺图上表现出来的。

因而也阐述了卡诺图的特点、最小项的定义和性质、用卡诺图化简所应用的逻辑代数基本原理、这些原理是如何在卡诺图里发挥作用的以及如何达到最简形式的化简。

然后给你卡诺图的具体事例来诠释卡诺图化简时所应用到的哪些定理步骤。

关键词:卡诺图;逻辑代数定理;最小项;相邻“1”单元;格子圈The discussion of the Logic algebra theory and methods used by karnaugh mapSui-cheng WangAbstract:From the logic algebra logic function theorem which lead to the karnaugh map in minimizing approaches, thus simplifying analysis is how to applicate logic algebra theorem in the karnaugh map shows. Therefore It also expounds the karnaugh map characteristics, the definition and property of the minimizing terms, the principle of a karnaugh map reduction with applied logic algebra fundamental , these principles are how to play their role and how to achieve the minimalist form of reduction in karnaugh map. Then give you some specific examples that explaining steps which is uesd to minimizing the terms with some heorem.Keywords: Karnaugh map; Logic algebra theorem; minimizing terms; "1" unit adjacent; Grid circle0引言对于一个逻辑函数,若其函数表达式比较简单,则相应的逻辑电路所需元件少,器材节约,电路可靠性强。

因此在设计逻辑电路时,化简函数表达式是十分重要的工作。

逻辑函数的化简,通常是指对逻辑函数表达式的基本形式---“与或”表达式进行化简,将其化成最简“与或”表达式。

所谓最简“与或”表达式,即指表达式中,“乘积”项个数最少,且在满足这一条件下,“乘积”项中的变量个数也最少。

逻辑函数化简常用的化简方法有代数化简法和卡诺图化简法。

代数化简法又称为公式法,是应用逻辑代数的基本定律,基本法则呵呵基本定理等公式进行化简,适合于多变量逻辑函数化简;当变量数目、不大于5时卡诺图化简法更方便、直观、准确,容易掌控。

逻辑函数化简是逻辑电路设计中十分重要的一环。

逻辑函数化简的目的是使根据逻辑函数实现的电路最简单。

一般来说,单输出函数化简后的表达式愈简单(项数越少,每项中的变量数越少,对所需求的门数越少)则实现的逻辑电路也就愈简单,成本也将越低。

同时,还可以在少量的门电路下避免了电路测试中的延迟和功耗,增加了电路的可靠性。

通常情况下,逻辑函数的化简方法有两种:代数原理公式法和卡诺图化简法。

1、代数开关定理公式化简法大多数化简/最小化方法基于结合律的一般形式:乘积项·Y+给定乘积项·Y' =给定乘积项(给定求和项+Y)·(给定求和项+Y' )= 给定求和项就是说,如果2个乘积项或求和项的差别只是1个变量的取反和不取反,则可将其结合为单项。

这样就省下了一个门,而且其余的门也减少一个输入端。

通过重复运动这种代数方法,就差不多可以化简完全部繁琐的函数表达式。

有时还会应用到开关代数定理中的一致律:X·Y+X '·Z+Y·Z=X·Y+X '·Z(X+Y)·(X'+Z)·(Y+Z)=(X+Y)·(X'+Z)还有吸收律:X·Y+X=X(X+Y)·X=X对于有些大量复杂的逻辑表达式,用一个公式或一种方法往往不能解决问题,而要运用多种公式和不同方法。

但是为了能顺利地化简表达式,就需要熟记基本定律、基本定理和基本法则,而且还要对表达式进行观察、分析及灵活运用,这样就对化简后的结果有不确定性。