EDA西安电子科技大学版第三章3.4

EDA课件第三章

tmp2:=d1 AND (NOT sel); tmp3:=tmp1 OR tmp2; tmp<=tmp3;

q<=tmp AFTER m; END PROCESS cale;

END ARCHITECTURE connect;

(2) 端口方向

端口方向用来定义外部引脚的信号方向是输入还 是输出。

凡是用“IN”进行方向说明的端口,其信号自端口 输入到构造体,而构造体内部的信号不能从该端口输 出。相反,凡是用“OUT”进行方向说明的端口,其信 号将从构造体内经端口输出,而不能通过该端口向构 造体输入信号。

实体说明

一个模块中仅有一 个设计实体。

实体 提供设计模块的接口信息,是VHDL设计电 路的最基本部分。

实体说明具有如下的结构:

ENTITY 实体名 IS

实体说明以“ENTITTY 实体名

[类属参数说明];

IS”开始至“END ENTITTY实体 名”结束。这里大写字母表示

实体说明的框架。实际上,对

此例中的外部引脚

ARCHITECTURE connect OF mux IS SIGNAL tmp:BIT; BEGIN

cale:PROCESS(d0,d1,sel) IS VARIABLE tmp1,tmp2,tmp3:BIT;

BEGIN tmp1:=d0 AND sel;

为d0,d1,sel,q 。

库(Library)是经编译后的数据的集合,它存放包集合 定义、实体定义、构造体定义和配置定义。

设计中的子程序和 公用数据类型的集合。

程序包

IEEE标准的标准程序包 设计者自身设计的程序包

包和库具有这样的关系:多个过程和函数汇集在一起构成包 集合,而几个包汇集在一起就形成一个库。

电子科技大学EDA指导书附完整答案讲解

数字系统EDA技术实验指导书学院:学号:姓名:实验一八位全加器的设计一、预习内容1.结合教材中的介绍熟悉QuartusⅡ软件的使用及设计流程;2.八位全加器设计原理。

二、实验目的1.掌握图形设计方法;2.熟悉QuartusⅡ软件的使用及设计流程;3.掌握全加器原理,能进行多位加法器的设计。

三、实验器材PC机一台、EDA教学实验系统一台、下载电缆一根(已接好)、导线若干四、实验要求1、用VHDL设计一个四位并行全加器;2、用图形方式构成一个八位全加器的顶层文件;3、完成八位全加器的时序仿真。

五、实验原理与内容1、原理:加法器是数字系统中的基本逻辑器件。

例如:为了节省资源,减法器和硬件乘法器都可由加法器来构成。

但宽位加法器的设计是很耗费资源的,因此在实际的设计和相关系统的开发中需要注意资源的利用率和进位速度等两方面的问题。

多位加法器的构成有两种方式:并行进位和串行进位方式。

并行进位加法器设有并行进位产生逻辑,运算速度快;串行进位方式是将全加器级联构成多位加法器。

通常,并行加法器比串行级联加法器占用更多的资源,并且随着位数的增加,相同位数的并行加法器比串行加法器的资源占用差距也会越来越大。

实验表明,4 位二进制并行加法器和串行级联加法器占用几乎相同的资源。

这样,多位数加法器由4 位二进制并行加法器级联构成是较好的折中选择。

因此本实验中的8 位加法器采用两个4位二进制并行加法器级联而成。

2、实现框图:1)四位加法器四位加法器可以采用四个一位全加器级连成串行进位加法器,实现框图如下图所示,其中CSA为一位全加器。

显然,对于这种方式,因高位运算必须要等低位进位来到后才能进行,因此它的延迟非常可观,高速运算肯定无法胜任。

通过对串行进位加法器研究可得:运算的延迟是由于进位的延迟。

因此,减小进位的延迟对提高运算速度非常有效。

下图是减少了进位延迟的一种实现方法。

可见,将迭代关系去掉,则各位彼此独立,进位传播不复存在。

EDA概述

参考书籍课程名称:电子设计自动化(EDA技术)教师:杨霏Email:yangsher@参考教材:参考教材《VHDL硬件描述语言与数字逻辑电路设计》西安电子科技大学出版社安电科技大版《VHDL程序设计》清华大学出版社09:24YF1理论课程一: EDA技术:硬件设计基础课程,软硬件相结合二:设计语言:VHDL 和Verilog软件平台开发环境三:软件平台:MAX+PLUS2四:硬件载体:CPLD/FPGA 芯片要求明确EDA开发流程硬件描述语言(表达设计者的设计功能)开发工具(集成开发环境)硬件设计(硬件电路、器件的设计使用)09:24YF2理论基础数字电路数字逻辑(组合逻辑,时序逻辑)理论课程内容VHDL语言逻辑设计思想硬件设计基础实验课程内容一:软件实验程序逻辑设计基于软件平台,进行设计的输入、编译、软件仿真基于软件平台进行设计的输入编译软件仿真二:硬件实验,在实验平台上完成设计的硬件仿真。

09:24YF3重点学习的内容1、学习软件开发工具(所谓自动化的设计工具)2、学习硬件描述语言(表达手段)3、介绍大规模可编程逻辑器件(载体)介绍大规模可编程逻辑4、结合课题做实验(用软件设计硬件)09:24YF4硬件设计的发展趋势模拟数字分离元件数字集成电路电子管晶体管小规模集成电路中规模集成电路大规模集成电路超大规模集成电路微处理器存储器标准逻辑电路微处理器、存储器、标准逻辑电路AD DA转换系统09:24YF5集成电路的发展随着计算机和集成电路技术的发展,数字系统SSIC-MSIC-LSIC-VLSIC 的设计大致经历了从SS C S C S C V S C的过程SSIC mall cale ntegration 小规模集成电路(S mall-s cale I ntegration Circuit) (几十~几百门)di l t ti MSIC中规模集成电路(M edium-scale I ntegration Circuit)(几百~几千门)大规模集成电路LSIC大规模集成电路(L arge-s cale I ntegration Circuit)(几千~几万门)VLSIC超大规模集成电路(V ery L arge-s caleI ntegration Circuit)(几万门以上)09:24YF6 g)硬件设计元素ROM EPROM EEPROMRAM SRAM SDRAMRAM SRAM SDRAMASICMCU DSP (MC、MP)MCU DSPFPGA CPLDARM处理速度、访问速度处理速度访问速度逻辑资源、程序资源存储容量内置接口资源09:24YF7EDA技术实现的载体超大规模可编程逻辑器件半定制或全定制ASIC混合ASIC09:24YF8数字系统的设计方法数字逻辑器件正从通用集成电路向专用集成电路过渡。

EDA技术概述

综合及优化、逻辑布局布线、逻辑仿真,直至完成

对于特定目标芯片的适配编译、逻辑映射、编程下 载等工作,最终形成集成电子系统或专用集成芯片 的一门新技术。

EDA技术的发展历程

EDA技术伴随着计算机、集成电路、电子 系统设计的发展,经历了计算机辅助设计 (Computer Assist Design,简称CAD)、计 算机辅助工程设计(Computer Assist Engineering Design,简称CAE)和电子设 计自动化(Electronic Design Automation, 简称EDA)三个发展阶段。

1. 20世纪70年代的计算机辅助设计CAD阶 段 早期的电子系统硬件设计采用的是分立元 件,随着集成电路的出现和应用,硬件设 计进入到发展的初级阶段。初级阶段的硬 件设计大量选用中小规模标准集成电路, 人们将这些器件焊接在电路板上,做成初 级电子系统,对电子系统的调试是在组装 好的PCB(Printed Circuit Board)板上进行的。

采用该方法设计时,高层设计进行功能和 接口描述,说明模块的功能和接口,模块 功能的更详细的描述在下一设计层次说明, 最底层的设计才涉及具体的寄存器和逻辑 门电路等实现方式的描述。

EDA方法: (Top-Down)

系统规格设计 功能级描述、仿真 模块化分、仿真 逻辑综合、优化、布局布线 时序仿真、时序检查 输出门级网表

应用介绍:

数字电视传输复用系统 中的数字电视复用器

应用介绍: 雷达系统中 的信号处理与时 序控制器

1.2 传统的设计方法和EDA上(Bottom - up)的 设计方法。

上

上

设计分解

下 下

构造系统

设计分解: 1. 确定设计目标 2. 功能模块分解 3. 进一步细分,直至可用市面上买到 的元器件构建此模块为止 构造系统: 1. 用市面上可买到的元器件构建最底 层模块 2. 用较低一层模块构造较高一层模块 3. 构造顶层模块 4. 测试验证与分析

EDAPPT课件

常用EDA软件介绍

1. EDA软件的分类 2. EDA软件的发展趋势

EDA工程的设计流程 EDA工程的设计方法

1.1 EDA技术简介

EDA(Electronic Design Automation 电子设计

自动化)的定义:

1. 狭义的定义: 以计算机为工作平台; 以相关的EDA开发软件为工具; 以大规模可编程逻辑器件(包括CPLD、FPGA、 EPLD等)为设计载体; 以硬件描述语言HDL(Hardware Description Language)为系统逻辑描述的主要表达方式; 自动完成系统算法,电路设计,最终形成电子系统或 专用集成芯片的一门新技术。

20世纪70年代,由于设计师对图形符号使用数量有限, 因此传统的手工布图方法无法满足产品复杂性的要求, 更不能满足工作效率的要求,就产生了一些单独的软件 工具,主要有印制电路板(PCB)布线设计、电路模拟、 逻辑模拟及版图的绘制等。

这种应用计算机进行辅助设计的时期,就是计算机辅助 设计CAD阶段。

利用这些工具,设计师能在产品制作之前预知产品的

功能与性能,能生成产品制造文件,使设计阶段对产 品性能的分析前进了一大步,这就是真正的计算机辅 助工程设计CAE阶段。

飞速发展,其工艺水平已

达到了深亚米微米级,在一个芯片上可以集成上百万、 上千万乃至上亿个晶体管,芯片的工作频率可达到 GHz,发展到了甚超大规模集成电路阶段。

该阶段的硬件系统设计,仍然使用大量不同型号的标

准芯片,实现电子系统设计。

随着微电子工艺的发展,相继出现了集成上万只晶体

管的微处理器、集成几十万乃至上百万储存单元的随 机存储器和只读存储器的超大规模集成电路。

最新自动控制原理西安电子科技大学第三版课后答案 陕西科技大学自动控制原理考研真题优秀

最新自动控制原理西安电子科技大学第三版课后答案陕西科技大学自动控制原理考研真题优秀自动控制原理西安电子科技大学第三版课后答案陕西科技大学自动控制原理考研真题篇一1)自动控制、自动控制系统的基本概念以及自动控制系统的三种基本控制方式;2)能分析某个自动控制系统的原理并绘制原理方框图;3)自动控制系统的分类以及对控制系统的基本要求。

2.控制系统的数学模型1)掌握控制系统的时域数学模型、控制系统的复域数学模型的建立方法及其相互转换;2)通过结构图的化简或梅逊增益公式求取系统的闭环传递函数、误差传递函数及干扰信号作用下的闭环传递函数等,了解绘制系统结构图的方法。

3.线性系统的时域分析法1)掌握系统性能指标的定义;2)掌握系统稳定性概念、劳斯稳定判据及其应用;3)掌握一阶、二阶系统的动态性能分析,及动态性能指标的计算,掌握二阶系统性能的改善,了解高阶系统动态性能的分析方法;4)掌握稳态误差的定义及计算。

4.线性系统的根轨迹法1)掌握根轨迹的基本概念,根轨迹与系统性能的关系;2)掌握根轨迹绘制的基本法则,灵活应用基本法则绘制系统的根轨迹;3)利用根轨迹分析系统的性能;4)了解参数根轨迹和零度根轨迹的概念及绘制方法。

5.线性系统的频域分析法1)理解频率特性的定义及其几何表示法;2)典型环节的频率特性,掌握系统开环对数频率特性图、幅相曲线图的绘制;3)掌握利用奈奎斯特稳定判据、对数频率稳定性判据判断闭环系统的稳定性;4)掌握相角稳定裕量和幅值稳定裕量的定义及其求取方法,及它们与系统性能的关系;5)开环频率特性与闭环系统性能之间的关系,了解闭环频率特性。

6.线性系统的校正方法1)正确理解控制系统校正的基本概念,校正方式,常用校正装置的特性;2)掌握串联超前校正、滞后校正、滞后-超前校正网络的校正原理及设计方法;3)将性能指标转换为希望开环对数幅频特性,根据希望特性确定最小相位系统的校正装置;4)了解局部反馈校正、复合校正的基本思路与方法。

eda技术及应用第三版课后答案谭会生

eda技术及应用第三版课后答案谭会生【篇一:《eda技术》课程大纲】>一、课程概述1.课程描述《eda技术》是通信工程专业的一门重要的集中实践课,是通信工程专业学生所必须具备的现代电子设计技术技能知识。

eda是电子技术的发展方向,也是电子技术教学中必不可少的内容。

本课程主要介绍可编程逻辑器件在电子电路设计及实现上的应用,介绍电路原理图和pcb图的设计技术。

开设该课程,就是要让学生了解大规模专用集成电路fpga和cpld的结构,熟悉一种以上的硬件描述语言,掌握一种以上的开发工具的使用等,掌握电路原理图和pcb图的现代设计技术与方法,从而提高学生应用计算机对电子电路和高速智能化系统进行分析与设计的能力。

2.设计思路本课程坚持“以学生为中心”的原则,以项目任务驱动的方式,采取理论知识与案例相结合的方式授课,提高学生的学习主动性。

通过必要的理论知识讲授、大量的实践训练和案例分析,培养学生的动手设计和实践能力,掌握eda开发的整个流程和基本技巧。

课程采用演示讲授和实践相结合,边讲边练的方法,让学生切身体会并掌握eda开发产品的流程和方法。

本课程集中2周时间开设,注重实践性,边讲边练,让学生切身体会并掌握eda开发技术。

3.实践要求(1)纪律和安全要求①不得将食物带入实验室,每次实训后请将使用后的废弃物带走。

违反者每次扣罚平时分2分。

②实训期间不得做与实训无关的其他事情,不得大声喧哗或做其他影响实训正常进行的事宜。

违反者每次扣罚平时分2分。

③实训期间,若学生有事不能正常参加实训,须提前以书面形式请假,并按指导教师的安排补做实训。

未经指导教师许可,学生不得任意调换实训时间和实训地点。

违反者每次扣罚平时分4分。

④学生不得以任何理由替代他人进行实训,违者直接取消实训成绩。

⑤学生除操作自己所分配的计算机外,不得操作实验室内其他任何设备。

违者每次扣罚平时分2分。

(2)业务要求实训所使用的软件protel和quartus ii,所有数据均通过服务器中转以及储存在服务器上,所以重启自己所用的电脑不会造成数据丢失。

工程优化3~4章 (陈开周)

x2 3 . 2 4 4 7

由 x3 :

x3 3 2 . 1 0 4 9

∴由 x2 : x2

x2 2 . 9 3 2 7

由 x1 : x1

x1 1 . 2 1 5 0

即 x* x0 0 . 0 3 2 8 f x 驻点近似值。

2012/11/25

1 x x e e 的驻点的近似值,取 x0 1 ,x1 2 , 2

x2 3 , x3 4 。

解:由 z f‘ x 知 z0 根据公式(3.33) 由 x1 :

z1 z0 z z z z 2.4517 , x2 : 2 0 4.4213 , x3 : 3 0 8.7049 x3 x0 x2 x0 x1 x0

⑥令 x1 x2 0.8328 , f x1 0.6688

x2 a 0.618 b a 0.8754 , f 程优化(第 3~4 章) 制作人:1204121948

f x1 f x2 ,则新区间 a, b a, x2 0.764,0.8754 , b a 0.1

④令 x2 x1 0.764 , f x2 0.6873

x1 a 0.382 b a 0.6525 , f x1 0.8408 f x1 f x2 ,则新区间 a, b x1 , b 0.6525,0.9442 , b a 0.1

, n 。求出 f xk min f xi 。若 xk 1 xk 1 ,则求出了

近似最优解为 xk ; k 0 时以 xk , xk 1 代替 a, b ; k n 时以 xk 1 , xk 代替 a, b ; 其他情形以 xk 1 , xk 1 代替 a, b 。继续仿前做下去,直到满足精度为止。试画出 算法框图。 解:

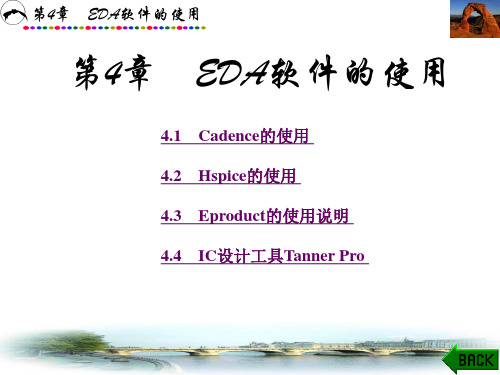

专用集成电路设计实践(西电版)第4章 EDA软件的使用

第4章 EDA软件的使用

图4-5 CreateNewFile对话框

第4章 EDA软件的使用

图4-6 电路图编辑窗口

第4章 EDA软件的使用

对于已存在的工程,可以先寻找并复制工程的路径,在

Terminal对话框中输入cd和空格后粘贴路径名,然后回车,再 输入启动命令icfb&,回车后即会出现CIW窗口。在CIW窗口 中选择Tools/LibraryManager,出现一个LibraryManager对话框, 如图4-3所示。其中最左边一栏是cds.lib里的库文件,左键双 击要打开的工程名,在Cell下就会出现工程中所有的电路图名, 双击要打开的电路图,在View中就会出现schematic,点击右键 打开即可。

第4章 EDA软件的使用

4.1.3 电路图仿真 1.添加激励 要对所设计的电路进行仿真,就需要加激励,即电源、地、 输入信号等。 加电源:按I键,点击Browse,弹出如图4-8所示的窗口。 双击analogLib,在Cell中选择常用的电源,一般为vpwl(分段线 性电压源,仿真瞬态响应时使用)和vdc(直流电源,仿真直流和 交流响应时使用)。按Q键,设置电源大小。将电源激励一端 连在电源线上,另一端接地。 加地:按I键,点击Browse,弹出如图4-8所示的框图。双 击analogLib,在Cell中选择gnd,连在需要接地的地方即可。 其他输入信号要按电路具体情况和要仿真的功能而定, 如图4-9所示。

第4章 EDA软件的使用

当把电路全部输入完毕后,点击左上角的CheckandSave

按钮,检查无错误后即可。四条线连到一个节点时会有警告, 此时不影响电路的正确性,所以要分清警告是这种情况,还是 其他情况,若是其他情况就有可能影响电路。电路检查若有 错误,则在图4-2所示窗口查看错误,然后根据具体错误逐步 改正。若要查找电路图中的某条线,点击电路图所在界面的 Edit Search Find,然后在出现的界面中点击SearchFor pin name)等。 net name。也可以查找器件名(SearchFor 名(SearchFor inst name),查找引脚

模拟电子电路及技术基础(第三版)

作者简介

孙肖子,女,西安电子科技大学退休教授,原国家级电工电子教学基地主任,致力于教材建设和教学改 革。

赵建勋,男,西安电子科技大学电子工程学院教授、硕士生导师,研究方向:计算电磁学、射频电路系统、 微波辐射与测量系统、神经元网络形态和功能实现机理。

王新怀,男,理学博士,西安电子科技大学电子工程学院教授、博士生导师、硕士生导师,研究方向:微波 毫米波电路与系统设计、智能天线与天线组阵技术研究、基于FPGA&DSP的实时信号处理系统设计。

模拟电子电路及技术基础(第 三版)

2017年西安电子科技大学出版社出版 的图书

01 成书过程

03 教材目录 05 作者简介

目录

02 内容简介 04 教学资源

《模拟电子电路及技术基础(第三版)》是由孙肖子主编,西安电子科技大学出版社于2017年3月出版的普 通高等教育“十一五”国家级规划教材。该书可作为高等学校通信工程、电子信息工程、电气与自动化工程、测 控技术与仪器、生物医学工程、微电子、电子科学与技术等有关专业的本科生或专科生“电子线路基础”“电子 技术基础”等课程的教材或教学参考书,也可作为工程技术人员的参考书。

2017年3月,《模拟电子电路及技术基础(第三版)》由西安电子科技大学出版社出版发行。

内容简介

该教材分为十三章,内容包括:绪论、集成运算放大器的基本应用电路、基于集成运放和RC反馈网络的有源 滤波器、常用半导体器件原理及特性、双极型晶体三极管和场效应管放大器基础、集成运算放大器内部电路、放 大器的频率响应、反馈、特殊用途的集成运算放大器及其应用、集成运算放大器的非线性应用、低频功率放大电 路、电源及电源管理、模拟电路系统设计及实验案例。书后的两个附录给出了部分习题答案和专用名词汉英对照 表。

汽车尾灯控制电路

课程设计说明书课程设计名称:电子课程设计课程设计题目:汽车尾灯控制电路学院名称:信息工程学院专业:计算机科学与技术班级:学号:姓名:评分:教师:20 10 年 9 月 15 日摘要随着科学技术的全方面发展,汽车制造工艺得到了长足的进步,使得汽车已经成为现代人们主要的交通工具。

人们了解到他们便捷、快速之余,也同时意识到汽车潜在的安全隐患,所以对具有汽车行驶状况提示作用的汽车尾灯进行研究是非常必要的。

本次课题设计的目的:设计汽车尾灯控制电路,由两个开关控制实现汽车正常运行、右转弯、左转弯和刹车时尾灯的情况。

尾灯分别由左右各三个灯泡组成,实验中采用发光二极管显示。

这样可以使得尾灯更清楚明显更加人性化。

本次设计是关于汽车尾灯控制电路的设计,根据汽车尾灯显示状态与汽车运行状态的关系,分析并设计电路。

整个电路由控制电路,三进制计数器,译码与显示驱动电路,尾灯状态显示4部分组成。

分析了使能控制信号与模式控制变量、时钟脉冲的关系,运用J—K触发器、3—8译码器等实现了根据汽车的运行状态,指示灯显示4种不同的模式。

本文详细的介绍了电路的设计思路及其实现过程,包括了整个设计流程。

通过上述电路组成使得汽车正常行驶时尾灯全灭,左转弯时左边三个指示灯顺序点亮,右转弯时右边三个指示灯顺序点亮,紧急刹车时左右两边指示灯同时闪烁,从而完成整个汽车尾灯控制电路的设计。

经过一系列的分析、仿真模拟等准备工作,本次课题设计基本都实现了全部的设计要求。

关键字:汽车尾灯、循环闪烁、译码、脉冲源目录前言 (4)第一章设计内容及要求 (5)第二章系统设计方案选择2.1 方案一 (6)2.2 方案二 (7)第三章系统组成及工作原理3.1 系统组成 (8)3.2 工作原理 (9)第四章单元电路设计、参数计算、器件选择4.1 CP脉冲电路的设计......................................`10 4.2 三进制计数器电路设计. (11)4.3 开关控制电路设计 (12)4.4译码及显示驱动电路 (13)第五章实验调试及测试结果与分析 (15)第六章实验总结及收获 (16)参考文献 (17)附录一 (18)附录二 (21)附录三 (22)前言汽车技术的发展趋势是电子化、智能化、信息化和集成化当前国际汽车市场上,汽车电子化竞争非常激烈,电子控制系统的应用十分普遍。

EDA课程综述

课程综述课程名称在系统编程技术任课教师专业及班级姓名学号日期在系统编程技术摘要:EDA的基本概念以及实现EDA的软件和硬件支持,和描述语言。

EDA 的设计步骤,EDA的应用及发展。

利用EDA工具,电子设计师可以从概念、算法、协议等开始设计电子系统,大量工作可以通过计算机完成,并可以将电子产品从电路设计、性能分析到设计出IC版图或PCB版图的整个过程的计算机上自动处理完成。

关键词:EDA技术HDL语言PLD正文:一、EDA技术概述EDA(Electronic Design Automation)技术是在电子CAD技术基础上发展起来的计算机软件系统,是指以计算机为工作平台,融合了应用电子技术、计算机技术、信息处理及智能化技术的最新成果,进行电子产品的自动设计。

在电子技术设计领域,可编程逻辑器件(如CPLD、FPGA)的应用,已得到广泛的普及,这些器件为数字系统的设计带来了极大的灵活性。

这些器件可以通过软件编程而对其硬件结构和工作方式进行重构,从而使得硬件的设计可以如同软件设计那样方便快捷。

这一切极大地改变了传统的数字系统设计方法、设计过程和设计观念,促进了EDA技术的迅速发展。

现在对EDA的概念或范畴用得很宽。

包括在机械、电子、通信、航空航天、化工、矿产、生物、医学、军事等各个领域,都有EDA的应用。

目前EDA技术已在各大公司、企事业单位和科研教学部门广泛使用。

例如在飞机制造过程中,从设计、性能测试及特性分析直到飞行模拟,都可能涉及到EDA技术。

本文所指的EDA技术,主要针对电子电路设计、PCB设计和IC设计。

EDA设计可分为系统级、电路级和物理实现级。

二、利用什么软件来设计EDA?EDA工具层出不穷,目前进入我国并具有广泛影响的EDA软件有:multiSIM7(原EWB的最新版本)、PSPICE、OrCAD、PCAD、Protel、Viewlogic、Mentor、Graphics、Synopsys、LSIIogic、Cadence、MicroSim等等。

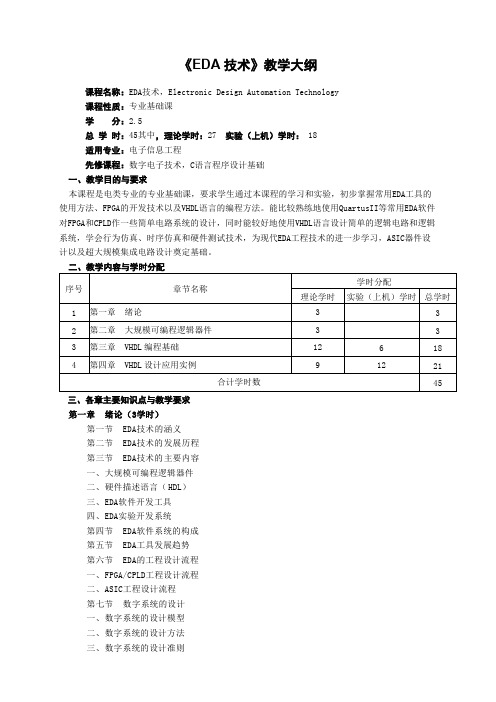

《EDA技术》教学大纲

《EDA 技术》教学大纲课程名称:EDA 技术,Electronic Design Automation Technology 课程性质:专业基础课学 分:2.5总 学 时:45其中,理论学时:27 实验(上机)学时: 18适用专业:电子信息工程先修课程:数字电子技术,C 语言程序设计基础 一、教学目的与要求本课程是电类专业的专业基础课,要求学生通过本课程的学习和实验,初步掌握常用EDA 工具的使用方法、FPGA 的开发技术以及VHDL 语言的编程方法。

能比较熟练地使用QuartusII 等常用EDA 软件对FPGA 和CPLD 作一些简单电路系统的设计,同时能较好地使用VHDL 语言设计简单的逻辑电路和逻辑系统,学会行为仿真、时序仿真和硬件测试技术,为现代EDA 工程技术的进一步学习,ASIC 器件设计以及超大规模集成电路设计奠定基础。

二、教学内容与学时分配学时分配实验上机序号章节名称理论学时实验(上机)学时总学时1第一章 绪论332第二章 大规模可编程逻辑器件3334第三章 VHDL 编程基础126184第四章 VHDL 设计应用实例91221合计学时数801045三、各章主要知识点与教学要求 第一章 绪论(3学时)第一节 EDA 技术的涵义第二节 EDA 技术的发展历程第三节 EDA 技术的主要内容一、大规模可编程逻辑器件二、硬件描述语言(HDL )三、EDA 软件开发工具四、EDA 实验开发系统第四节 EDA 软件系统的构成第五节 EDA 工具发展趋势第六节 EDA 的工程设计流程一、FPGA/CPLD 工程设计流程二、ASIC 工程设计流程第七节 数字系统的设计一、数字系统的设计模型二、数字系统的设计方法三、数字系统的设计准则四、数字系统的设计步骤第八节 EDA技术的应用展望本章重点:1、EDA技术的特点2、EDA技术的发展及应用3、数字系统的设计流程本章难点:1、EDA技术的主要特点2、ASIC技术本章教学要求:1、正确理解EDA的概念2、掌握EDA技术的特点、应用和发展趋势3、了解EDA技术的发展历程4、掌握数字系统的设计流程 第二章 大规模可编程逻辑器件(3学时)第一节 可编程逻辑器件概述一、PLD的发展进程二、PLD的分类方法三、常用的CPLD和FPGA标识的含义第二节 Altera公司的CPLD和FPGA器件一、Altera公司的CPLD和FPGA概述二、MAX系列CPLD结构三、MAXII系列CPLD结构四、Cyclone系列FPGA结构五、Stratix系列FPGA结构第三节 CPLD和FPGA的编程与配置一、CPLD和FPGA的编程配置二、CPLD和FPGA的下载接口三、CPLD器件的编程电路四、FPGA器件的编程电路第四节 FPGA和CPLD的开发应用选择本章重点:1、CPLD的结构与工作原理2、FPGA的结构与工作原理本章难点:1、CPLD的结构与工作原理 2、FPGA的结构与工作原理本章教学要求:1、了解可编程逻辑器件的基本结构、发展和分类2、理解简单PLD3、掌握CPLD和FPGA FPGA的结构与工作原4、了解在系统可编程逻辑器件第三章 VHDL编程基础(18学时)第一节 概述一、常用硬件描述语言简介二、VHDL的优点三、VHDL程序设计约定第二节 VHDL程序基本结构一、VHDL程序设计举例二、VHDL程序的基本结构三、库、程序包使用说明四、实体描述五、结构体描述六、结构体配置第三节 VHDL语言要素一、VHDL文字规则二、VHDL数据对象三、VHDL数据类型四、VHDL操作符第四节 VHDL顺序语句一、赋值语句二、转向控制语句三、等待语句四、子程序调用语句五、返回语句六、空操作语句七、其他语句和说明第五节 VHDL并行语句一、进程语句二、块语句三、并行信号赋值语句四、并行过程调用语句五、元件例化语句六、生成语句第六节子程序一、函数二、重载函数三、过程四、重载过程第七节程序包第八节 VHDL描述风格一、行为描述3二、数据流描述三、结构描述第九节基本逻辑电路设计一、组合逻辑电路设计二、时序逻辑电路设计三、存储器电路设计第十节状态机的VHDL设计一、状态机的基本结构格功能二、一般状态机的VHDL设计三、摩尔状态机的VHDL设计四、米立状态机的VHDL设计本章实验:Quartus II操作使用( 3学时)数码管扫描电路设计( 3学时)本章重点:1、VHDL程序结构2、VHDL语言要素3、VHDL基本描述语句4、组合逻辑电路和时序逻辑电路设计5、状态机和存储器的VHDL设计本章难点:1、程序包的应用和配置 2、数据类型转换3、状态机和FIFO设计本章教学要求:1、理解VHDL语言的特点2、掌握VHDL程序的结构、语言要素和语句描述,能够正确书写VHDL程序3、掌握组合逻辑电路和时序逻辑电路的设计4、熟悉状态机的应用5、正确理解存储器电路的设计第四章 VHDL程序设计基础(21学时)第一节 电子数字钟一、系统功能分析和模块划分二、分频器和计数器的设计三、数码管动态扫描电路的设计四、顶层电路的分析和设计第二节 乒乓球游戏机一、系统功能分析和模块划分二、分频器和计数器的设计三、状态机电路设计四、顶层电路的分析和设计第三节 简单电子琴一、系统功能分析和模块划分二、音频控制系统设计三、顶层电路的分析和设计第四节 16×16LED点阵汉字滚屏显示一、系统功能分析和模块划分二、LED点阵汉字显示系统设计三、顶层电路的分析和设计本章实验:数字频率计的设计( 3 学时) 数字秒表的设计( 3 学时)交通信号灯控制器的设计(3 学时) 16×16点阵汉字显示系统( 3 学时)本章重点:1、数字系统的综合设计2、VHDL语言的综合应用本章难点:1、系统模块的划分和设计分析2、顶层电路的描述和编程本章教学要求:1、掌握应用VHDL语言描述不同逻辑功能的电路2、理解数字系统的设计四、成绩与考核方式 1、课程总评成绩由平时成绩(30%)和其末考试成绩(70%)组成,其中平时成绩包括作业、实验报告和考勤以及期中考试成绩和单元测验。

EDA技术实用教程ppt

EDA技术及其发展 EDA技术的主要内容 EDA设计方法 EDA技术及EDA工具的发展趋势

第一章 EDA技术概况

1.1 EDA技术及其发展

1.什么是EDA? Electronic Design Automation 电子设计自动化

2. EDA技术定义 (广义定义)

半导体工艺设计自动化 可编程器件设计自动化 电子系统设计自动化 印刷电路板设计自动化 仿真与测试、故障诊断自动化 形式验证自动化 通称为EDA工程

1.4 EDA技术及EDA工具的发展趋势

1. EDA技术的发展趋势 (1)广度上:大型机——工作站——微机 (2)深度上: ESDA(Electronic System Design Automation ) CE(Concurrent Engineering 并行设计工程) SOC/SOPC ( system on a programmable chip 单 芯片集成)

3)计算机辅助工程设计CAE阶段

20世纪80年代初,出现了低密度的可编程逻辑 器件(PLA programmable array logic和GAL generic array logic),相应的EDA开发工具主 要解决电路设计没有完成之前的功能检测等问 题。 80年代后期,EDA工具已经可以进行初级的设 计描述、综合、优化和设计结果验证。

EDA技术极大的降低了硬件电路的设计难度,提 高了设计效率,是电子系统设计方法的质的飞跃

传统设计方法

自下而上(Bottom-up)的设计方法

优点

设计人员对于用这种方法进行设计比较熟悉 实现各个子块电路所需的时间短

缺点

一般来讲对系统的整体功能把握不足 实现整个系统的功能所需的时间长因为必须先将 各个小模块完成;使用这种方法对设计人员之间 相互进行协作有比较高的要求。

EDA课件

第三节 EDA常用软件

1.电子电路设计与仿真工具 1.电子电路设计与仿真工具 2. PCB设计软件 PCB设计软件 3. IC设计软件 IC设计软件 4. 可编程逻辑器件PLD设计软件 可编程逻辑器件PLD设计软件

第一章 绪论

EDA工具有很多,目前进入我国并具有广泛影响的EDA软件有:

第 三 节 EDA

第一章 绪论

2.PCB设计软件 2.PCB设计软件

PCB(Printed—Circuit Board)设计软件: 第 三 节 EDA 如Protel、OrCAD、PowerPCB、Cadence PSD、 MentorGraphices的Expedition PCB、 Winboard/Windraft/IvexSPICE、PCB Studio等等。

第一章 绪论

3. IC设计软件 IC设计软件

第 三 节 EDA

IC设计工具很多,其中按市场所占份额排行为Cadence、 Mentor Graphics和Synopsys。这三家都是ASIC设计领域 相当有名的软件供应商。其它公司的软件相对来说使用 者较少。

第一章 绪论

4. PLD设计软件 PLD设计软件

EDA技术及应用 EDA技术及应用

学时:54小时 54 实验:18小时 主讲:梁西银 E-mail:silver@

关于这门课

理论部分:硬件结构,软件编程。 实验部分:上机编程,下载验证,1人1套,4个题目。

参考书目: 1.《CPLD技术及其应用》,宋万杰,西安电子科技大学出版社, 25元。 2.《VHDL硬件语言描述与数字逻辑电路设计》,侯伯亨,西安电 子科技大学出版社,20.80元。 3. 《基于QuartusII的FPGA/CPLD数字系统设计实例》,周润景等, 电子工业出版社,48元。

第1章 EDA技术概述

测试电路 (硬件测试)

编程器/下载电缆 (编程、下

系统规格说明 系统划分 逻辑设计与综合 综合后仿真 版图设计 版图验证 参数提取与后仿真 制版、流片 芯片测试

26

§1.7 数字系统的设计

一、 数字系统的设计模型

数据输入 数据输出

10

2、计算机辅助工程设计CAE阶段

20世纪80年代初,出现了低密度的可编程逻 辑器件(PAL_Programmable Array Logic可编程 陈列逻辑和GAL_Generic Array Logic通用阵列逻 辑 ),相应的EDA开发工具主要解决电路设计没 有完成之前的功能检测等问题。 80年代后期,EDA工具已经可以进行初级的设 计描述、综合、优化和设计结果验证。

2、可编程器件设计自动化;

3、电子系统设计自动化; 4、印刷电路板设计自动化; 5、仿真与测试、故障诊断自动化; 6、形式验证自动化。 以上各部分统称为EDA工程 现代电子设计技术包括: PSPICE,EWB,MATLAB,PROTEL,ORCAD等

6

三、EDA技术的狭义定义:

以大规模可编程逻辑器件为设计载体,以硬

14

二、 硬件描述语言 (HDL__Hardware Description Language) VHDL: IEEE(国际电气与电子工程师学会)标 准,系统级抽象描述能力较强。

Verilog: IEEE标准,门级开关电路描述能力 较强。

ABEL: 系统级抽象描述能力差,适合于门级 电路描述。

15

数据处理子系统

控制与条件信号

时钟

控制子系统

外部控制系统

27

1、数据处理子系统

组成:存储器、运算器、数据选择器等功能电路。 任务:完成数据的采集、存储、运算和传输

西电EDA满分大作业

EDA报告题目 VHDL设计初步学院电子工程学院专业学号导师姓名朱燕目录第一章实验部分(流水灯) (2)1、程序设计: (2)2、程序代码 ............................................................................................. 错误!未定义书签。

3、程序调试 ............................................................................................. 错误!未定义书签。

第二章习题部分.............................................................................................. 错误!未定义书签。

习题一 ....................................................................................................... 错误!未定义书签。

习题二 ....................................................................................................... 错误!未定义书签。

习题三 ....................................................................................................... 错误!未定义书签。

习题四 ....................................................................................................... 错误!未定义书签。

EDA的实验报告

杭州电子科技大学实验报告实验课程名称实实班姓学指导教验验序内号容级名号师eda技术 1 分频器与频率计设计 123 吕文 123 黄某二○一四年 4月 18 日一、实验的目的与要求实验名称:分频器与频率计设计实验目的:1、初识verilog hdl语言熟练verilog 的语法2、学习quartus调用modelsim进行仿真3、掌握用fpga实现简易的分频器与频率计的原理与方法实验要求:1、设计一个可控分频器,输入20mhz或 12mhz 时钟(可选择其中一种),输出100hz~10khz,输出100hz ~ 10khz,输出频率数控可调(按键或者使用in-system sources and probes),输出波形占空比为50%,接蜂鸣器;2、设计一个简易频率计,输入为方波,测量频率的范围100hz ~ 9999hz ,测量精度<1%,频率计输出可以接数码管或者使用in-system sources and probes观察3、分频器输出接频率计的输入二、实验原理分频器的原理:把输入的信号作为计数脉冲,由于计数器的输出端口是按一定规律输出脉冲的,所以对不同的端口输出的信号脉冲,就可以看作是对输入信号的”分频“。

频率计是对信号的频率进行测量并显示测量结果。

原理就是在1秒钟内对时钟计数,得到的数字就是频率大小。

频率计的设计是用一个标准的时钟20mhz来做参照,以1s钟为周期,为20000000个周期,同时定义一个计数的变量q ,当输入的端口出现上升沿的时候,变量加1,那么在一秒钟内cout的数值即为,该波形的频率。

最后将分频器的输出端口接入频率计的输入端口,用频率计来测量波形的频率大小,通过比较实际的频率fre1与测出来的频率大小fre2,就知道了该频率计的误差。

三、实验内容实验步骤 1、大概的把框架建起来,把思路想好2、先设计一个符合要求的分频器3、进行仿真,看效果3、再设计一个符合要求的频率计4、用modelsim进行仿真5、把这两部分连接起来,最后进行仿真得到结果6、得到频率计的测频误差本实验分频器的时钟是20mhz,分频出来的是100hz~10khz的波形,那么就定义一个变量当做分频比[17:0] div ,可以用按键来控制div的大小,继而实现分频出来的大小。

西安电子科技大学半导体物理课件——第三章 半导体中的载流子

(2)费米能级和多子浓度

当温度很低时,杂质电离很弱,此时有

Ⅷ、低温弱电离区(续)

(3)费米能级与温度的关系

I)

当温度T 0K时,有 可知,当温度升至使

II) 由

这说明,当温度从低温极限开始上升时, 费米能级很快上升;当温度上升到Nc=0.11ND 时,费米能级上升到极大值;当温度继续上升 时,费米能级又开始下降。 费米能级随温度的变化关系如右图所示。

常见的分布函数

1. 麦克斯韦速度分布率 2. 波尔兹曼分布率(古典统计) ——粒子可区分! 3. 费米-狄拉克统计分布

f(v) m ⎛ ⎞ = 4π ⎜ ⎟ ⎝ 2 π kT ⎠

2

3 2

v 2e

−

−

mv 2kT

2

f B (u k ) =

π

(kT )

−

3 2

uke

uk kT

f

FD

(u)

=

1 1 + e 1

状态密度

导带底E(k)与k的关系

h2k 2 E (k ) = E c + * 2m n

能量E~(E+dE)间的量子态数

dZ = 2V × 4π k dk

2

可得

(2m ) ( E − Ec ) k= h

* n 2 1 1 2 * m n dE , kdk = h2

状态密度

代入可得

(2m ) dZ = 4π V h

E (k ) = E c k 32 h 2 k 12 + k 22 + + ( ) mt ml 2

3

设导带底的状态有s个,根据同样方法可求得

(2m ) g c ( E ) = 4π V h

四川省自考电子电路EDA技术概述

《电子电路EDA技术》(教材:西安电子科技大学出版社出版的《基于FPGA的现代数字系统设计》)一、概述:1、教材每一章节内容均有涉及,其中第一章、第三章是重点,占总分60%左右;其它章节着重考察学生对基本概念的理解,了解。

2、题型:选择题,名词解释,判断改错,简答题,程序分析题,编程题。

二、知识点总结:(一)第一章1、以图1.1为框架,了解全定制ASIC,半定制ASIC,PLD,复杂高密度PLD等概念和相互关系。

2、了解电子设计自动化(EDA)技术的概念及其发展历程。

3、理解利用EDA技术进行电子系统设计的5个特点。

4、理解“自顶向下”设计方法的特点。

5、以图1.2为框架,掌握现代数字系统设计流程,各主要步骤的作用。

注意理解设计处理的过程;设计校验中,功能仿真和时序仿真的区别。

6、理解HDL综合器把可综合的HDL转化为硬件电路的过程。

7、了解现代数字系统设计的发展趋势。

8、了解:ASIC,FPGA,CPLD,EDO,SOC,SOPC,RTL,EDA,PLD,HDL,IP CORE等名词含义(二)第二章1、了解表2.1所示ISE Foundation的主要集成工具的名称与功能。

2、了解ISE 的基本操作。

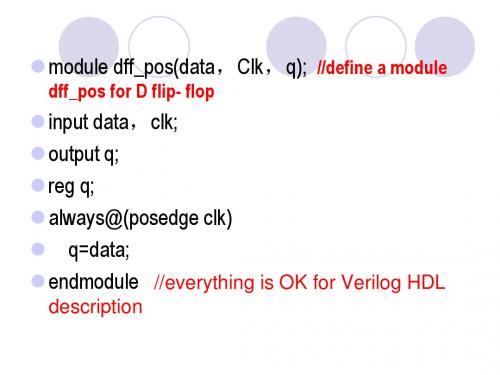

(三)第三章1、掌握Verilog HDL模块的基本结构;掌握模块的例化,常数表达,变量声明(主要要求wire,reg两类变量);了解Verilog HDL的描述层次。

2、理解VerilogHDL门级建模相关语法,掌握与/或门类,缓冲/非门类逻辑门的例化,了解门延迟的基本概念。

3、理解VerilogHDL数据流建模相关语法,掌握assign语句的使用,了解常用运算符的应用。

4、3.4节行为级建模是一个重点,需要掌握的主要语法是:begin...end,条件语句,for语句,initial,always,task,function,常用系统函数,有限状态机设计。

5、读懂测试文件,并且可以编写简单的测试代码。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

化,如此循环往复 。

第3章 VHDL编程基础

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY CODER IS PORT ( SR:IN STD_LOGIC_VECTOR(0 TO 7); SC:OUT STD_LOGIC_VECTOR(0 TO 2)); END ENTITY CODER; ARCHITECTURE ART OF CODER IS BEGIN PROCESS(SR) IS

任一给定的时刻内,在每一个进程内,只 能执行一条顺序语句。一个进程与其设计实体 的其他部分进行数据交换的方式只能通过信号 或端口。

第3章 VHDL编程基础

VHDL有如下六类基本顺序语句: 赋值语句;转向控制语句;等待语句; 子程序调用语句;返回语句;空操作 语句。

第3章 VHDL编程基础

3.4.1

变量的有效只局限于所定义的一个进程中,或一个子

程序中,是局部的、暂时性数据对象。它的赋值是立即发 生的,即是一种时间延迟为零的赋值行为。

第3章 VHDL编程基础

信号与之不同,信号具有全局性特征,它 可作为设计实体内部各单元之间数据传送的载 体,而且可通过信号与其他的实体进行通信(端 口本质上也是一种信号)。 信号赋值过程总是有某种延时的,它反映 了硬件系统并不是立即发生的 。

顺序描述语句;

END PROCESS [进程标号];

进程说明部分用于定义该进程所需的局部数据环境。

第3章 VHDL编程基础

PROCESS中规定了每个进程语句在它的某个敏感信 号(由敏感信号参量表列出)的值改变时都必须立即完 成某一功能行为。 由顺序语句定义的行为就要重复

执行一次,当进程中最后一个语句执行完成后,执行

标识符赋值目标是以简单的标识符作为被赋值的

信号或变量名。

数组单元素赋值目标的表达形式为:

数组类信号或变量名(下标名)

第3章 VHDL编程基础

下标名可以是一个具体的数字,也可以是一个文

字表示的数字名,它的取值范围在该数组元素个数范

围内。 SIGNAL SIGNAL

SVEC(0) SVEC(1)

S1,S2:STD_LOGIC; SVEC :STD_LOGIC_VECTOR(0 TO 7); <= S1; <= S2;

第3章 VHDL编程基础

(3=> E, 4=>F, 2 =>G(1),1=>G(2) ):= H;--名字关联方式赋

值

示例中的变量赋值语句属名字关联赋值方式,赋值结果等效于:

G(2) := H(1) ;G(1) := H(2) ; E := H(3) ;F := H(4) ;

第3章 VHDL编程基础

第3章 VHDL编程基础

3.4

VHDL顺序语句

顺序语句和并行语句是VHDL程序设计中两

大基本描述语句系列。

顺序语句是相对于并行语句而言的,其特 点是每一条顺序语句的执行(指仿真执行)顺序 是与它们的书写顺序基本一致的 。

第3章 VHDL编程基础

顺序语句只能出现在进程(Process)和子程 序中。 一个进程是由一系列顺序语句构成的,而进 程本身属并行语句,在同一设计实体中,所有 的进程是并行执行的。

第3章 VHDL编程基础

BEGIN IF(SR(7)=‘0’) THEN SC<="000"; --(SR(7)=„0‟) ELSIF(SR(6)=‘0’) THEN

SC <="100"; --(SR(7)=„1‟) AND (SR(6)=„0‟) ELSIF(SR (5)=‘0’) THEN

SC <="010"; --(SR (7)=„1‟)AND(SR (6)=„1‟)AND(SR (5)=„0‟)

赋值语句

赋值语句的功能就是将一个值或一个表达式的运 算结果传递给某一数据对象,如信号或变量,或由此

组成的数组。

VHDL设计实体内的数据传递以及对端口界面外部

数据的读写都必须通过赋值语句的运行来实现。

第3章 VHDL编程基础

1.信号和变量赋值

赋值语句有两种,即信号赋值语句和变量赋值语句。 变量赋值与信号赋值的区别在于:

3.4.2

转向控制语句

转向控制语句通过条件控制开关决定是否执行一 条或几条语句,或重复执行一条或几条语句,或跳过

一条或几条语句。转向控制语句共有五种:IF 语句、

CASE 语句、LOOP 语句、NEXT 语句和EXIT 语句。

第3章 VHDL编程基础

1.IF语句 IF语句是一种条件语句,它根据语句中所设置的 一种或多种条件,有选择地执行指定的顺序语句,其 语句结构如下:

执行到CASE语句时,首先计算表达式的值, 然后根据条件句中与之相同的选择值,执行对 应的顺序语句,最后结束CASE语句。表达式可 以是一个整数类型或枚举类型的值,也可以是 由这些数据类型的值构成的数组(条件句中的 “=>”不是操作符,它只相当于“THEN”的作用)。

第3章 VHDL编程基础

选择值可以有四种不同的表达方式:① 单个普通数值,如4;② 数值选择范围,如(2 TO 4),表示取值2、3或4;③ 并列数值,如3 | 5,表示取值为3或者5;④ 混合方式,以上 三种方式的混合。

第3章 VHDL编程基础

使用CASE语句需注意以下几点:

(1) 条件句中的选择值必须在表达式的取值范围内。 (2) 除非所有条件句中的选择值能完整覆盖CASE语句 中表达式的取值,否则最末一个条件句中的选择必须用 “OTHERS”表示。它代表已给的所有条件句中未能列出 的其他可能的取值,这一点对于定义为STD_LOGIC和 STD_LOGIC_VECTOR数据类型的值尤为重要,因为这些数 据对象的取值除了1和0以外,还可能有其他的取值 。

第3章 VHDL编程基础

ELSIF(SR (4)=‘0’) THEN SC <="110"; ELSIF(SR (3)=‘0’) THEN SC <="001"; ELSIF(SR (2)=‘0’) THEN

SC <="101"; ELSIF(SR (1)=‘0’) THEN

SC <="011"; ELSE SC <="111"; END IF; END PROCESS; END ARCHITECTURE ART;

第3章 VHDL编程基础

变量赋值语句和信号赋值语句的语法格式 如下: 变量赋值目标 := 信号赋值目标 <= 赋值源; 赋值源;

在信号赋值中,需要注意的是,当在同一 进程中,同一信号赋值目标有多个赋值源时, 信号赋值目标获得的是最后一个赋值源的赋值, 其前面相同的赋值目标不作任何变化。

第3章 VHDL编程基础

VARIABLE

S <=

H :STD_LOGIC_VECTOR(1 TO 4 );

(„0‟,‘1‟,‘0‟,‘0‟) ; ; --位置关联方式赋值 --其他语句

(A, B, C, D) <= S ...

示例中的信号赋值语句属位置关联赋值方式,其赋值结果等效于:

A <=„0‟;B <=„1‟;C <=„0‟ ;D <=„0‟;

第3章 VHDL编程基础

【例3.4.4】

IF (A>B) THEN OUTPUT<= „1‟;

END IF ;

若条件句(A>B)检测结果为TRUE,则向信号 OUTPUT赋值1,否则此信号维持原值。

第3章 VHDL编程基础

【例3.4.5】

IF语句完成的一个具有2输入与门 。

IF X=„1‟ AND Y=„1‟ THEN RETURN „1‟;

ELSE RETURN „0‟;

END IF;

第3章 VHDL编程基础

P1 P2 S B C A MUX2 1 MUX2 1 B B A A Z S

图3.7

双2选1多路选择器电路

P1和P2分别是两个多路选择器的通道选择开关,当为高电 平时下端的通道接通,低电平时上端接通

第3章 VHDL编程基础

SIGNAL

...

A,B,C,P1,P2,Z: BIT;

IF

(P1=„1‟) THEN Z<=A; --满足此语句的执行条件是(P1=„1‟)

ELSIF (P2=„0‟) THEN Z<=B; --满足此语句的执行条件是(P1=„0‟)AND (P2=„0‟) ELSE Z<=C; --满足此语句的执行条件是(P1=„0‟)AND (P2=„1‟) END IF;

V1 := „0‟; V2 := „0‟; S2 <=„0‟; END PROCESS;

不作赋值操作 --将V1置入新值 0 --将V2置入新值 0 --由于这是S2最后一次赋值,赋值有效, --此‘0‟将上面准备赋入的‘1‟覆盖掉

第3章 VHDL编程基础

2.赋值目标

赋值语句中的赋值目标有四种类型。 1) 标识符赋值目标及数组单元素赋值目标

SIGNAL S1,S2:STD_LOGIC; PROCESS(S1,S2) VARIABLE BEGIN V1 V2 S1 S2 := „1‟; := „1‟; <= „1‟; --立即将V1置位为1 --立即将V2置位为1 --S1被赋值为1 V1,V2:STD_LOGIC;

<= „1‟; --在本进程中,这个S2不是最后一个赋值语句 ,

【例3.4.2】

VARIABLE A,B:STD_LOGIC_VECTOR (1 TO 4);

A (1 TO 2) := "10" ;