GS88237BB-333中文资料

GS8662R18GE-250I资料

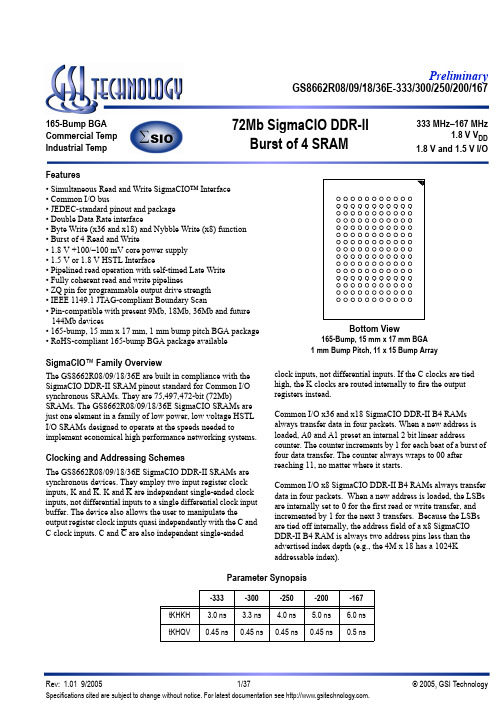

GS8662R08/09/18/36E-333/300/250/200/16772Mb SigmaCIO DDR-II Burst of 4 SRAM333 MHz–167 MHz1.8 V V DD1.8 V and 1.5 V I/O165-Bump BGA Commercial Temp Industrial Temp Features• Simultaneous Read and Write SigmaCIO™ Interface • Common I/O bus• JEDEC-standard pinout and package • Double Data Rate interface• Byte Write (x36 and x18) and Nybble Write (x8) function • Burst of 4 Read and Write• 1.8 V +100/–100 mV core power supply • 1.5 V or 1.8 V HSTL Interface• Pipelined read operation with self-timed Late Write • Fully coherent read and write pipelines• ZQ pin for programmable output drive strength • IEEE 1149.1 JTAG-compliant Boundary Scan• Pin-compatible with present 9Mb, 18Mb, 36Mb and future 144Mb devices• 165-bump, 15 mm x 17 mm, 1 mm bump pitch BGA package • RoHS-compliant 165-bump BGA package availableSigmaCIO ™ Family OverviewThe GS8662R08/09/18/36E are built in compliance with the SigmaCIO DDR-II SRAM pinout standard for Common I/O synchronous SRAMs. They are 75,497,472-bit (72Mb)SRAMs. The GS8662R08/09/18/36E SigmaCIO SRAMs are just one element in a family of low power, low voltage HSTL I/O SRAMs designed to operate at the speeds needed toimplement economical high performance networking systems.Clocking and Addressing SchemesThe GS8662R08/09/18/36E SigmaCIO DDR-II SRAMs are synchronous devices. They employ two input register clock inputs, K and K. K and K are independent single-ended clock inputs, not differential inputs to a single differential clock input buffer. The device also allows the user to manipulate theoutput register clock inputs quasi independently with the C and C clock inputs. C and C are also independent single-endedclock inputs, not differential inputs. If the C clocks are tied high, the K clocks are routed internally to fire the output registers instead.Common I/O x36 and x18 SigmaCIO DDR-II B4 RAMs always transfer data in four packets. When a new address is loaded, A0 and A1 preset an internal 2 bit linear addresscounter. The counter increments by 1 for each beat of a burst of four data transfer. The counter always wraps to 00 after reaching 11, no matter where it starts.Common I/O x8 SigmaCIO DDR-II B4 RAMs always transfer data in four packets. When a new address is loaded, the LSBs are internally set to 0 for the first read or write transfer, and incremented by 1 for the next 3 transfers. Because the LSBs are tied off internally, the address field of a x8 SigmaCIO DDR-II B4 RAM is always two address pins less than the advertised index depth (e.g., the 4M x 18 has a 1024K addressable index).Parameter Synopsis-333-300-250-200-167tKHKH 3.0 ns 3.3 ns 4.0 ns 5.0 ns 6.0 ns tKHQV0.45 ns0.45 ns0.45 ns0.45 ns0.5 ns165-Bump, 15 mm x 17 mm BGA 1 mm Bump Pitch, 11 x 15 Bump ArrayBottom View2M x 36 SigmaCIO DDR-II SRAM—Top View1234567891011ACQ MCL/SA (144Mb)SA R/W BW2K BW1LD SA SA CQ B NC DQ27DQ18SA BW3K BW0SA NC NC DQ8C NC NC DQ28V SS SA SA0SA1V SS NC DQ17DQ7D NC DQ29DQ19V SS V SS V SS V SS V SS NC NC DQ16E NC NC DQ20 V DDQ V SS V SS V SS V DDQ NC DQ15DQ6F NC DQ30DQ21 V DDQ V DD V SS V DD V DDQ NC NC DQ5G NC DQ31DQ22 V DDQ V DD V SS V DD V DDQ NC NC DQ14H Doff V REF V DDQ V DDQ V DD V SS V DD V DDQ V DDQ V REF ZQ J NC NC DQ32 V DDQ V DD V SS V DD V DDQ NC DQ13DQ4K NC NC DQ23V DDQ V DD V SS V DD V DDQ NC DQ12DQ3L NC DQ33DQ24 V DDQ V SS V SS V SS V DDQ NC NC DQ2M NC NC DQ34 V SS V SS V SS V SS V SS NC DQ11DQ1N NC DQ35DQ25 V SS SA SA SA V SS NC NC DQ10P NC NC DQ26SA SA C SA SA NC DQ9DQ0RTDOTCKSASASACSASASATMSTDI11 x 15 Bump BGA—13 x 15 mm 2 Body—1 mm Bump PitchNotes:1.BW0 controls writes to DQ0:DQ8; BW1 controls writes to DQ9:DQ17; BW2 controls writes to DQ18:DQ26; BW3 controls writes toDQ27:DQ352.MCL = Must Connect LowGS8662R08/09/18/36E-333/300/250/200/1674M x 18 SigmaCIO DDR-II SRAM—Top View1234567891011ACQ SA SA R/W BW1K NC LD SA SA CQ B NC DQ9NC SA NC K BW0SA NC NC DQ8C NC NC NC V SS SA SA0SA1V SS NC DQ7NC D NC NC DQ10V SS V SS V SS V SS V SS NC NC NC E NC NC DQ11 V DDQ V SS V SS V SS V DDQ NC NC DQ6F NC DQ12NC V DDQ V DD V SS V DD V DDQ NC NC DQ5G NC NC DQ13 V DDQ V DD V SS V DD V DDQ NC NC NC H Doff V REF V DDQ V DDQ V DD V SS V DD V DDQ V DDQ V REF ZQ J NC NC NC V DDQ V DD V SS V DD V DDQ NC DQ4NC K NC NC DQ14V DDQ V DD V SS V DD V DDQ NC NC DQ3L NC DQ15NC V DDQ V SS V SS V SS V DDQ NC NC DQ2M NC NC NC V SS V SS V SS V SS V SS NC DQ1NC N NC NC DQ16 V SS SA SA SA V SS NC NC NC P NC NC DQ17SA SA C SA SA NC NC DQ0RTDOTCKSASASACSASASATMSTDI11 x 15 Bump BGA—13 x 15 mm 2 Body—1 mm Bump PitchNotes:1.BW0 controls writes to DQ0:DQ8; BW1 controls writes to DQ9:DQ172.MCL = Must Connect LowGS8662R08/09/18/36E-333/300/250/200/1678M x 9 SigmaCIO DDR-II SRAM—Top View1234567891011ACQ SA SA R/W NC K NC LD SA SA CQ B NC NC NC SA NC K BW SA NC NC DQ4C NC NC NC V SS SA NC SA V SS NC NC NC D NC NC NC V SS V SS V SS V SS V SS NC NC NC E NC NC DQ5 V DDQ V SS V SS V SS V DDQ NC NC DQ3F NC NC NC V DDQ V DD V SS V DD V DDQ NC NC NC G NC NC DQ6 V DDQ V DD V SS V DD V DDQ NC NC NC H Doff V REF V DDQ V DDQ V DD V SS V DD V DDQ V DDQ V REF ZQ J NC NC NC V DDQ V DD V SS V DD V DDQ NC DQ2NC K NC NC NC V DDQ V DD V SS V DD V DDQ NC NC NC L NC DQ7NC V DDQ V SS V SS V SS V DDQ NC NC DQ1M NC NC NC V SS V SS V SS V SS V SS NC NC NC N NC NC NC V SS SA SA SA V SS NC NC NC P NC NC DQ8SA SA C SA SA NC NC DQ0RTDOTCKSASASACSASASATMSTDI11 x 15 Bump BGA—13 x 15 mm 2 Body—1 mm Bump PitchNotes:1.Unlike the x36 and x18 versions of this device, the x8 and x9 versions do not give the user access to A0 and A1. SA0 and SA1 are set to0 at the beginning of each access.2.MCL = Must Connect LowGS8662R08/09/18/36E-333/300/250/200/1678M x 8 SigmaCIO DDR-II SRAM—Top View1234567891011ACQ SA SA R/W NW1K NC LD SA SA CQ B NC NC NC SA NC K NW0SA NC NC DQ3C NC NC NC V SS SA NC SA V SS NC NC NC D NC NC NC V SS V SS V SS V SS V SS NC NC NC E NC NC DQ4 V DDQ V SS V SS V SS V DDQ NC NC DQ2F NC NC NC V DDQ V DD V SS V DD V DDQ NC NC NC G NC NC DQ5 V DDQ V DD V SS V DD V DDQ NC NC NC H Doff V REF V DDQ V DDQ V DD V SS V DD V DDQ V DDQ V REF ZQ J NC NC NC V DDQ V DD V SS V DD V DDQ NC DQ1NC K NC NC NC V DDQ V DD V SS V DD V DDQ NC NC NC L NC DQ6NC V DDQ V SS V SS V SS V DDQ NC NC DQ0M NC NC NC V SS V SS V SS V SS V SS NC NC NC N NC NC NC V SS SA SA SA V SS NC NC NC P NC NC DQ7SA SA C SA SA NC NC NC RTDOTCKSASASACSASASATMSTDI11 x 15 Bump BGA—13 x 15 mm 2 Body—1 mm Bump PitchNotes:1.Unlike the x36 and x18 versions of this device, the x8 and x9 versions do not give the user access to A0 and A1. SA0 and SA1 are set to0 at the beginning of each access.2.NW0 controls writes to DQ0:DQ3; NW1 controls writes to DQ4:DQ73.MCL = Must Connect LowGS8662R08/09/18/36E-333/300/250/200/167Pin Description TableSymbolDescriptionTypeCommentsSA Synchronous Address InputsInput —NC No Connect ——R Synchronous Read Input Active High W Synchronous Write Input Active Low BW0–BW3Synchronous Byte Writes Input Active Low x18/x36 only NW0–NW1Nybble Write Control Pin Input Active Low x8 only LD Synchronous Load PinInput Active Low K Input Clock Input Active High K Input Clock Input Active Low C Output Clock Input Active High C Output Clock Input Active LowTMS Test Mode Select Input —TDI Test Data Input Input —TCK Test Clock Input Input —TDO Test Data Output Output —V REF HSTL Input Reference Voltage Input —ZQ Output Impedance Matching InputInput —MCL Must Connect Low——DQ Data I/O Input/Output Three State Doff Disable DLL when low Input Active LowCQ Output Echo Clock Output —CQ Output Echo Clock Output —V DD Power Supply Supply 1.8 V Nominal V DDQ Isolated Output Buffer Supply Supply 1.5 V NominalV SSPower Supply: GroundSupply—GS8662R08/09/18/36E-333/300/250/200/167Note:NC = Not Connected to die or any other pinGS8662R08/09/18/36E-333/300/250/200/167BackgroundCommon I/O SRAMs, from a system architecture point of view, are attractive in read dominated or block transfer applications. Therefore, the SigmaCIO DDR-II SRAM interface and truth table are optimized for burst reads and writes. Common I/O SRAMs are unpopular in applications where alternating reads and writes are needed because bus turnaround delays can cut high speed Common I/O SRAM data bandwidth in half.Burst OperationsRead and write operations are “burst” operations. In every case where a read or write command is accepted by the SRAM, it will respond by issuing or accepting four beats of data, executing a data transfer on subsequent rising edges of K and K#, as illustrated in the timing diagrams. It is not possible to stop a burst once it starts. Four beats of data are always transferred. This means that it is possible to load new addresses every other K clock cycle. Addresses can be loaded less often, if intervening deselect cycles are inserted.Deselect CyclesChip Deselect commands are pipelined to the same degree as read commands. This means that if a deselect command is applied to the SRAM on the next cycle after a read command captured by the SRAM, the device will complete the four beat read data transfer and then execute the deselect command, returning the output drivers to high-Z.A high on the LD# pin prevents the RAM from loading read or write commandinputs and puts the RAM into deselect mode as soon as it completes all outstanding burst transfer operations.SigmaCIO DDR-II B4 SRAM Read CyclesThe status of the Address, LD# and R/W# pins are evaluated on the rising edge of K. Because the device executes a four beat burst transfer inresponse to a read command, if the previous command captured was a read or write command, the Address, LD# and R/W# pins are ignored. If the previous command captured was a deselect, the control pin status is checked.The SRAM executes pipelined reads. The read command is clocked into the SRAM by a rising edge of K. After the next rising edge of K, the SRAM produces data out in response to the next rising edge of C# (or the next rising edge of K#, if C and C# are tied high). The second beat of data is transferred on the next rising edge of C, then on the next rising edge of C# and finally on the next rising edge of C, for a total of four transfers per address load.SigmaCIO DDR-II B4 SRAM Write CyclesThe status of the Address, LD# and R/W# pins are evaluated on the rising edge of K. Because the device executes a four beat burst transfer in response to a write command, if the previous command captured was a read or write command, the Address, LD# and R/ W# pins are ignored at the next rising edge of K. If the previous command captured was a deselect, the control pin status is checked.The SRAM executes “late write” data transfers. Data in is due at the device inputs on the rising edge of K following the rising edge of K clock used to clock in the write command and the write address. To complete the remaining three beats of the burst of four write transfer the SRAM captures data in on the next rising edge of K#, the following rising edge of K and finally on the next rising edge of K#, for a total of four transfers per address load.GS8662R08/09/18/36E-333/300/250/200/167Power-Up Sequence for SigmaQuad-II SRAMsSigmaQuad-II SRAMs must be powered-up in a specific sequence in order to avoid undefined operations.Power-Up Sequence1. Power-up and maintain Doff at low state.1a.Apply V DD .1b. Apply V DDQ .1c. Apply V REF (may also be applied at the same time as V DDQ ).2. After power is achieved and clocks (K, K, C, C) are stablized, change Doff to high.3. An additional 1024 clock cycles are required to lock the DLL after it has been enabled.Note:If you want to tie Doff high with an unstable clock, you must stop the clock for a minimum of 30 seconds to reset the DLL after the clocks become stablized.DLL Constraints•The DLL synchronizes to either K or C clock. These clocks should have low phase jitter (t KCVar on page 20).•The DLL cannot operate at a frequency lower than 119 MHz.•If the incoming clock is not stablized when DLL is enabled, the DLL may lock on the wrong frequency and cause undefined errors or failures during the initial stage.Power-Up Sequence (Doff controlled)Power UP IntervalUnstable Clocking IntervalDLL Locking Interval (1024 Cycles)Normal OperationKKV DDV DDQV REFDoffPower-Up Sequence (Doff tied High)Power UP IntervalUnstable Clocking IntervalStop Clock IntervalDLL Locking Interval (1024 Cycles)Normal OperationKKV DDV DDQV REFDoff30ns MinNote:If the frequency is changed, DLL reset is required. After reset, a minimum of 1024 cycles is required for DLL lock.GS8662R08/09/18/36E-333/300/250/200/167Special FunctionsByte Write and Nybble Write ControlByte Write Enable pins are sampled at the same time that Data In is sampled. A high on the Byte Write Enable pin associated with a particular byte (e.g., BW0 controls D0–D8 inputs) will inhibit the storage of that particular byte, leaving whatever data may be stored at the current address at that byte location undisturbed. Any or all of the Byte Write Enable pins may be driven high or low during the data in sample times in a write sequence.Each write enable command and write address loaded into the RAM provides the base address for a 4 beat data transfer. The x18 version of the RAM, for example, may write 72 bits in association with each address loaded. Any 9-bit byte may be masked in any write sequence.Nybble Write (4-bit) write control is implemented on the 8-bit-wide version of the device. For the x8 version of the device, “Nybble Write Enable” and “NBx” may be substituted in all the discussion above.Example x18 RAM Write Sequence using Byte Write EnablesData In SampleTimeBW0BW1D0–D8D9–D17Beat 101Data In Don’t CareBeat 210Don’t Care Data InBeat 300Data In Data InBeat 410Don’t Care Data InResulting Write OperationByte 1 D0–D8Byte 2D9–D17Byte 1D0–D8Byte 2D9–D17Byte 1D0–D8Byte 2D9–D17Byte 1D0–D8Byte 2D9–D17Written Unchanged Unchanged Written Written Written Unchanged Written Beat 1Beat 2Beat 3Beat 4Output Register ControlSigmaCIO DDR-II SRAMs offer two mechanisms for controlling the output data registers. Typically, control is handled by the Output Register Clock inputs, C and C. The Output Register Clock inputs can be used to make small phase adjustments in the firing of the output registers by allowing the user to delay driving data out as much as a few nanoseconds beyond the next rising edges of the K and K clocks. If the C and C clock inputs isare tied high, the RAM reverts to K and K control of the outputs, allowing the RAM to function as a conventional pipelined read SRAM.A K R/W LDA 0–A nKBank 0Bank 1Bank 2Bank 3A KLD A K LD A K LD R/W R/W R/W DQDQDQ DQCC CCDQ 1–C R/WLD 0LD 1LD 2LD 3Note:For simplicity BWn (or NWn), K, and C are not shown.CQ CQ CQ CQ CQGS8662R08/09/18/36E-333/300/250/200/167Example Four Bank Depth Expansion SchematicGS8662R08/09/18/36E-333/300/250/200/167FLXDrive-II Output Driver Impedance ControlHSTL I/O SigmaCIO DDR-II SRAMs are supplied with programmable impedance output drivers. The ZQ pin must be connected to V SS via an external resistor, RQ, to allow the SRAM to monitor and adjust its output driver impedance. The value of RQ must be 5X the value of the desired RAM output impedance. The allowable range of RQ to guarantee impedance matching continuously is between 150Ω and 300Ω. Periodic readjustment of the output driver impedance is necessary as the impedance is affected by drifts in supply voltage and temperature. The SRAM’s output impedance circuitry compensates for drifts in supply voltage and temperature. A clock cycle counter periodically triggers an impedance evaluation, resets and counts again. Each impedance evaluation may move the output driver impedance level one step at a time towards the optimum level. The output driver isimplemented with discrete binary weighted impedance steps. Updates of pull-down drive impedance occur whenever a driver is producing a “1” or is High-Z. Pull-up drive impedance is updated when a driver is producing a “0” or is High-Z.Common I/O SigmaCIO DDR-II B4 SRAM Truth TableK nLDR/WDQOperationA + 0A + 1A + 2A + 3↑1X Hi-Z Hi-Z Hi-Z Hi-Z Deselect ↑00D@K n+1D@K n+1D@K n+2D@K n+2Write ↑1Q@K n+1or C n+1Q@K n+2or C n+2Q@K n+2or C n+2Q@K n+3or C n+3ReadNote:Q is controlled by K clocks if C clocks are not used.B4 Byte Write Clock Truth TableBW BW BW BW Current OperationD D D D K ↑(t n+1)K ↑(t n+1½)K ↑(t n+2)K ↑(t n+2½)K ↑(t n )K ↑(t n+1)K ↑(t n+1½)K ↑(t n+2)K ↑(t n+2½)TTTTWriteDx stored if BWn = 0 in all four data transfers D0D2D3D4T F F F WriteDx stored if BWn = 0 in 1st data transfer only D0X X XF T F F WriteDx stored if BWn = 0 in 2nd data transfer only X D1X XF F T F WriteDx stored if BWn = 0 in 3rd data transfer only X X D2XF F F T WriteDx stored if BWn = 0 in 4th data transfer only X X X D3F F F F Write AbortNo Dx stored in any of the four data transfersX X X XNotes:1.“1” = input “high”; “0” = input “low”; “X” = input “don’t care”; “T” = input “true”; “F” = input “false”.2.If one or more BWn = 0, then BW = “T”, else BW = “F”.GS8662R08/09/18/36E-333/300/250/200/167*Assuming stable conditions, the RAM can achieve optimum impedance within 1024 cycles.B4 Nybble Write Clock Truth TableNW NW NW NW Current OperationD D D D K ↑(t n+1)K ↑(t n+1½)K ↑(t n+2)K ↑(t n+2½)K ↑(t n )K ↑(t n+1)K ↑(t n+1½)K ↑(t n+2)K ↑(t n+2½)TTTTWriteDx stored if NWn = 0 in all four data transfers D0D2D3D4T F F F WriteDx stored if NWn = 0 in 1st data transfer only D0X X XF T F F WriteDx stored if NWn = 0 in 2nd data transfer only X D1X XF F T F WriteDx stored if NWn = 0 in 3rd data transfer only X X D2XF F F T WriteDx stored if NWn = 0 in 4th data transfer only X X X D3F F F F Write AbortNo Dx stored in any of the four data transfersX X X XNotes:1.“1” = input “high”; “0” = input “low”; “X” = input “don’t care”; “T” = input “true”; “F” = input “false”.2.If one or more NWn = 0, then NW = “T”, else NW = “F”.GS8662R08/09/18/36E-333/300/250/200/167x36 Byte Write Enable (BWn) Truth TableBW0BW1BW2BW3D0–D8D9–D17D18–D26D27–D351111Don’t Care Don’t Care Don’t Care Don’t Care 0111Data In Don’t Care Don’t Care Don’t Care 1011Don’t Care Data In Don’t Care Don’t Care 0011Data In Data In Don’t Care Don’t Care 1101Don’t Care Don’t Care Data In Don’t Care 0101Data In Don’t Care Data In Don’t Care 1001Don’t Care Data In Data In Don’t Care 0001Data In Data In Data In Don’t Care 1110Don’t Care Don’t Care Don’t Care Data In 0110Data In Don’t Care Don’t Care Data In 1010Don’t Care Data In Don’t Care Data In 0010Data In Data In Don’t Care Data In 1100Don’t Care Don’t Care Data In Data In 0100Data In Don’t Care Data In Data In 1000Don’t Care Data In Data In Data In 0Data InData InData InData Inx18 Byte Write Enable (BWn) Truth Table BW0BW1D0–D8D9–D1711Don’t Care Don’t Care 01Data In Don’t Care 10Don’t Care Data In 0Data InData Inx8 Nybble Write Enable (NWn) Truth Table NW0NW1D0–D3D4–D711Don’t Care Don’t Care 01Data In Don’t Care 10Don’t Care Data In 0Data InData InGS8662R08/09/18/36E-333/300/250/200/167GS8662R08/09/18/36E-333/300/250/200/167B4 State DiagramPower-UpNOPLoad New AddressDDR Read DDR WriteLOADREAD WRITE LOADLOADLOADLOADNotes:1.The internal burst address counter is a 4-bit linear counter (i.e., when first address is A0, next internal burst address is A0+1).2.“READ” refers to read active status with R/W = High, “WRITE” refers to write inactive status with R/W = Low.3.“LOAD” refers to read new address active status with LD = Low, “LOAD” refers to read new address inactive status with LD = High.LOAD Increment Read Address Increment Write AddressAlwaysAlwaysREADWRITEAbsolute Maximum Ratings(All voltages reference to V SS )SymbolDescriptionValueUnitV DD Voltage on V DD Pins –0.5 to 2.9V V DDQ Voltage in V DDQ Pins –0.5 to V DD V V REF Voltage in V REF Pins –0.5 to V DDQV V I/O Voltage on I/O Pins –0.5 to V DDQ +0.5 (≤ 2.9 V max.)V V IN Voltage on Other Input Pins –0.5 to V DDQ +0.5 (≤ 2.9 V max.)V I IN Input Current on Any Pin +/–100mA dc I OUT Output Current on Any I/O Pin +/–100mA dcT J Maximum Junction Temperature125o C T STGStorage Temperature–55 to 125oCNote:Permanent damage to the device may occur if the Absolute Maximum Ratings are exceeded. Operation should be restricted to Recommended Operating Conditions. Exposure to conditions exceeding the Recommended Operating Conditions, for an extended period of time, may affect reliability of this component.GS8662R08/09/18/36E-333/300/250/200/167Recommended Operating ConditionsPower SuppliesParameterSymbolMin.Typ.Max.UnitSupply Voltage V DD 1.7 1.8 1.9V I/O Supply Voltage V DDQ 1.7 1.8 1.9V Reference VoltageV REF0.68—0.95VNotes:1.Unless otherwise noted, all performance specifications quoted are evaluated for worst case at both 1.4 V ≤ V DDQ ≤ 1.6 V (i.e., 1.5 V I/O)and 1.7 V ≤ V DDQ ≤ 1.95 V (i.e., 1.8 V I/O) and quoted at whichever condition is worst case.2.The power supplies need to be powered up simultaneously or in the following sequence: V DD , V DDQ , V REF , followed by signal inputs. Thepower down sequence must be the reverse. V DDQ must not exceed V DD ..Operating TemperatureParameterSymbolMin.Typ.Max.UnitAmbient Temperature (Commercial Range Versions)T A 02570°C Ambient Temperature (Industrial Range Versions)T A–402585°CGS8662R08/09/18/36E-333/300/250/200/167HSTL I/O DC Input CharacteristicsParameterSymbolMinMaxUnitsNotesDC Input Logic High V IH (dc)V REF + 0.10V DD + 0.3 V V 1DC Input Logic LowV IL (dc)–0.3 VV REF – 0.10V1Notes:patible with both 1.8 V and 1.5 V I/O drivers2.These are DC test criteria. DC design criteria is V REF ± 50 mV. The AC V IH /V IL levels are defined separately for measuring timing parame-ters.3.V IL (Min) DC = –0.3 V, V IL (Min) AC = –1.5 V (pulse width ≤ 3 ns).4.V IH (Max) DC = V DDQ + 0.3 V, V IH (Max) AC = V DDQ + 0.85 V (pulse width ≤ 3 ns).HSTL I/O AC Input CharacteristicsParameterSymbolMinMaxUnitsNotesAC Input Logic High V IH (ac)V REF + 0.20—V 3,4AC Input Logic LowV IL (ac)—V REF – 0.20V 3,4V REF Peak to Peak AC VoltageV REF (ac)—5% V REF (DC)V1Notes:1.The peak to peak AC component superimposed on V REF may not exceed 5% of the DC component of V REF .2.To guarantee AC characteristics, V IH ,V IL , Trise, and Tfall of inputs and clocks must be within 10% of each other.3.For devices supplied with HSTL I/O input buffers. Compatible with both 1.8 V and 1.5 V I/O drivers.20% tKHKHV SS – 1.0 V50%V SS V IHUndershoot Measurement and TimingOvershoot Measurement and Timing20% tKHKHV DD + 1.0 V50%V DDV ILCapacitanceo C, f = 1 MH Z , V DDParameterSymbolTest conditionsTyp.Max.UnitInput Capacitance C IN V IN = 0 V 45pF Output Capacitance C OUT V OUT = 0 V67pF Clock CapacitanceC CLK—56pFNote:This parameter is sample tested.GS8662R08/09/18/36E-333/300/250/200/167AC Test ConditionsParameterConditionsInput high level V DDQ Input low level 0 V Max. input slew rate 2 V/ns Input reference level V DDQ /2Output reference levelV DDQ /2Note:Test conditions as specified with output loading as shown unless otherwise noted.DQVT = V DDQ /250ΩRQ = 250 Ω (HSTL I/O)V REF = 0.75 VAC Test Load DiagramInput and Output Leakage CharacteristicsParameterSymbolTest ConditionsMin.MaxNotesInput Leakage Current (except mode pins)I IL V IN = 0 to V DD –2 uA 2 uA DoffI INDOFF V DD ≥ V IN ≥ V IL 0 V ≤ V IN ≤ V IL –100 uA –2 uA 2 uA 2 uA Output Leakage CurrentI OLOutput Disable,V OUT = 0 to V DDQ–2 uA2 uA(T A = 25= 3.3 V)GS8662R08/09/18/36E-333/300/250/200/167Programmable Impedance HSTL Output Driver DC Electrical CharacteristicsParameterSymbolMin.Max.UnitsNotesOutput High Voltage V OH1 V DDQ /2V DDQ V 1, 3Output Low Voltage V OL1 Vss V DDQ /2V 2, 3Output High Voltage V OH2 V DDQ – 0.2V DDQ V 4, 5Output Low VoltageV OL2Vss0.2V4, 6Notes:1. I OH = (V DDQ /2) / (RQ/5) +/– 15% @ V OH = V DDQ /2 (for: 175Ω ≤ RQ ≤ 350Ω).2. I OL = (V DDQ /2) / (RQ/5) +/– 15% @ V OL = V DDQ /2 (for: 175Ω ≤ RQ ≤ 350Ω).3.Parameter tested with RQ = 250Ω and V DDQ = 1.5 V or 1.8 V4.Minimum Impedance mode, ZQ = V SS5.I OH = –1.0 mA6.I OL = 1.0 mAOperating CurrentsParameterSymbolTest Conditions-333-300-250-200-167Notes0to 70°C –40 to 85°C 0to 70°C –40 to 85°C 0to 70°C –40 to 85°C 0to 70°C –40 to 85°C 0to 70°C –40 to 85°C Operating Current (x36):DDR I DD V DD = Max, I OUT = 0 mA Cycle Time ≥ t KHKH Min TBDTBDTBDTBDTBDTBDTBDTBDTBDTBD2, 3Operating Current (x18):DDR I DD V DD = Max, I OUT = 0 mA Cycle Time ≥ t KHKH Min TBD TBD TBD TBD TBD TBD TBD TBD TBD TBD 2, 3Operating Current (x9):DDR I DD V DD = Max, I OUT = 0 mA Cycle Time ≥ t KHKH Min TBD TBD TBD TBD TBD TBD TBD TBD TBD TBD 2, 3Operating Current (x8):DDR I DDV DD = Max, I OUT = 0 mA Cycle Time ≥ t KHKH Min TBD TBD TBD TBD TBD TBD TBD TBD TBD TBD 2, 3Standby Current (NOP):DDRI SB1Device deselected,I OUT = 0 mA, f = Max,All Inputs ≤ 0.2 V or ≥ V DD – 0.2 VTBD TBD TBD TBD TBD TBD TBD TBD TBD TBD 2, 4Notes:1.Power measured with output pins floating.2.Minimum cycle, I OUT = 0 mA3.Operating current is calculated with 50% read cycles and 50% write cycles.4.Standby Current is only after all pending read and write burst operations are completed.GS8662R08/09/18/36E-333/300/250/200/167AC Electrical CharacteristicsParameterSymbol-333-300-250-200-167UnitsN o t e sMin Max Min Max Min Max Min Max Min MaxClockK, K Clock Cycle Time C, C Clock Cycle Time t KHKH t CHCH 3.0 3.5 3.3 4.2 4.0 6.3 5.07.88 6.08.4ns tTKC Variablet KCVar —0.2—0.2—0.2—0.2—0.2ns 5K, K Clock High Pulse Width C, C Clock High Pulse Width t KHKL t CHCL 1.2— 1.32— 1.6— 2.0— 2.4—ns K, K Clock Low Pulse Width C, C Clock Low Pulse Width t KLKH t CLCH 1.2— 1.32— 1.6— 2.0— 2.4—ns K to K High C to C Hight KHKH 1.35— 1.49— 1.8— 2.2— 2.7—ns K, K Clock High to C, C Clock High t KHCH 0 1.30 1.450 1.80 2.30 2.8ns DLL Lock Time t KCLock 1024—1024—1024—1024—1024—cycle 6K Static to DLL resett KCReset 30—30—30—30—30—nsOutput TimesK, K Clock High to Data Output Valid C, C Clock High to Data Output Valid t KHQV t CHQV —0.45—0.45—0.45—0.45—0.5ns 3K, K Clock High to Data Output Hold C, C Clock High to Data Output Hold t KHQX t CHQX –0.45—–0.45—–0.45—–0.45—–0.5—ns 3K, K Clock High to Echo Clock Valid C, C Clock High to Echo Clock Valid t KHCQV t CHCQV —0.45—0.45—0.45—0.45—0.5ns K, K Clock High to Echo Clock Hold C, C Clock High to Echo Clock Hold t KHCQX t CHCQX –0.45—–0.45—–0.45—–0.45—–0.5—ns CQ, CQ High Output Valid t CQHQV —0.25—0.27—0.30—0.35—0.40ns 7CQ, CQ High Output Hold t CQHQX –0.25—–0.27—–0.30—–0.35—–0.40—ns 7K Clock High to Data Output High-Z C Clock High to Data Output High-Z t KHQZ t CHQZ —0.45—0.45—0.45—0.45—0.5ns 3K Clock High to Data Output Low-Z C Clock High to Data Output Low-Zt KHQX1t CHQX1–0.45—–0.45—–0.45—–0.45—–0.5—ns3Setup TimesAddress Input Setup Time t AVKH 0.4—0.4—0.5—0.6—0.7—ns Control Input Setup Time t IVKH 0.4—0.4—0.5—0.6—0.7—ns 2Data Input Setup Timet DVKH0.28—0.3—0.35—0.4—0.5—ns。

美军标883的对应国内标准-概述说明以及解释

美军标883的对应国内标准-概述说明以及解释1.引言1.1 概述概述部分的内容可以包括以下几个方面:引言部分主要是对该篇文章的背景和意义进行简要介绍,可以提及以下内容:- 美军标883,也即美国军方的标准MIL-STD-883,是一份关于电子元器件可靠性测试方法的标准。

这份标准对于确保电子元器件的可靠性和性能至关重要,不仅在军事领域具有重要意义,也在民用领域有广泛应用。

- 近年来,我国的电子元器件产业迅速发展,国内对于电子元器件的测试与认证标准也日益重要。

为了满足国内市场对高质量电子元器件的需求,有必要对照美军标883制定国内对应的标准,以确保产品的质量与性能。

- 本文将对比分析美军标883与国内对应标准的内容和要求,探讨其差异与相似之处,并对其对国内电子元器件产业的影响与建议进行讨论。

通过对这两个标准的比较,可以为我国电子元器件产业的发展提供一定的借鉴和指导。

引言部分的概述应该简洁明了,能够准确介绍该文章的主题和研究方法,同时能够激发读者的兴趣,引导读者进一步阅读后续内容。

1.2文章结构文章结构部分的内容可以包括以下内容:文章结构部分的主要目的是介绍本文的组织结构和各个章节的内容,以便读者能够更好地理解和阅读文章。

本文分为引言、正文和结论三个部分。

第一部分是引言部分。

在引言部分,首先要对文章的主题进行概述,简要介绍美军标883以及国内对应的标准的背景和重要性。

其次,说明文章结构,即介绍各个章节的内容和安排。

最后,阐明本文的目的,即通过对比分析美军标883和国内对应标准的内容,探讨其差异和影响,并给出相关建议。

第二部分是正文部分。

在正文部分,首先要详细介绍美军标883的内容,包括其主要内容和要求。

可以列举一些关键点和具体规定,以帮助读者更好地理解。

然后,介绍国内对应的标准,包括其起草背景、内容和适用范围等方面。

可以结合实际案例和数据进行说明,以论证国内对应标准的有效性和实用性。

第三部分是结论部分。

AD8232 中文产品数据手册

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 Fax: 781.461.3113 ©2012 Analog Devices, Inc. All rights reserved.

6

A1 OPAMP+

7

REFOUT

8

OPAMP–

9

OUT

10

图1.

应用

健身及运动心率监护仪 便携式ECG 远程健康监护 游戏外围设备 生物电信号采集

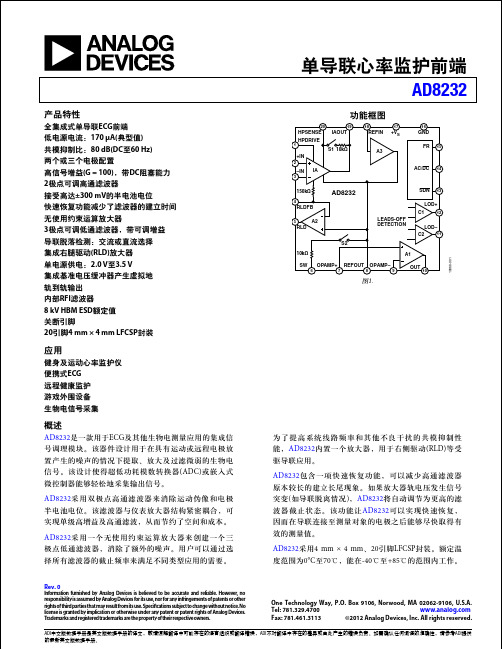

概述

AD8232是一款用于ECG及其他生物电测量应用的集成信 号调理模块。该器件设计用于在具有运动或远程电极放 置产生的噪声的情况下提取、放大及过滤微弱的生物电 信号。该设计使得超低功耗模数转换器(ADC)或嵌入式 微控制器能够轻松地采集输出信号。 AD8232采用双极点高通滤波器来消除运动伪像和电极 半电池电位。该滤波器与仪表放大器结构紧密耦合,可 实现单级高增益及高通滤波,从而节约了空间和成本。 AD8232采用一个无使用约束运算放大器来创建一个三 极点低通滤波器,消除了额外的噪声。用户可以通过选 择所有滤波器的截止频率来满足不同类型应用的需要。

Rev. 0

为了提高系统线路频率和其他不良干扰的共模抑制性 能,AD8232内置一个放大器,用于右侧驱动(RLD)等受 驱导联应用。 AD8232包含一项快速恢复功能,可以减少高通滤波器 原本较长的建立长尾现象。如果放大器轨电压发生信号 突变(如导联脱离情况),AD8232将自动调节为更高的滤 波器截止状态。该功能让AD8232可以实现快速恢复, 因而在导联连接至测量对象的电极之后能够尽快取得有 效的测量值。 AD8232采用4 mm × 4 mm、20引脚LFCSP封装。额定温 度范围为0°C至70℃,能在-40℃至+85℃的范围内工作。

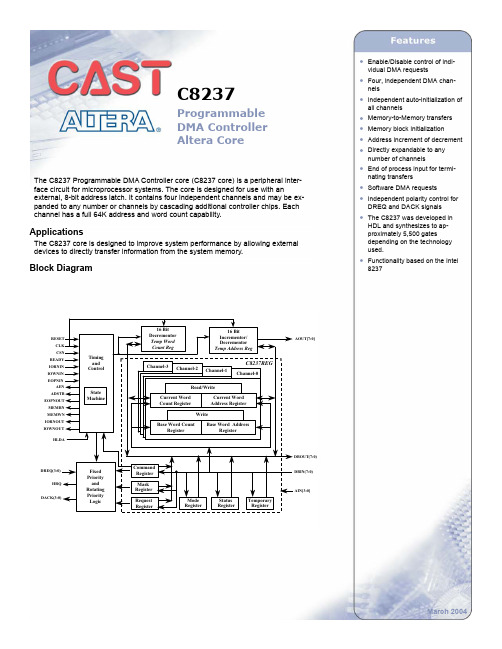

8第八章 DMA 8237控制器

0 0 0 0

0 1 0 1

A0~A7 A8~A15 A0~A7 A8~A15 W0~W7 W8~W15 W0~W7

写 读

0 0 0 0

1 1 0 0

0 0 1 1

0 0 0 0

0 0 0 0

1 1 1 1

1 1 1 1

0 1 0 1

W8~W15

第八章

DMA技术

8237通道寄存器寻址

通 道

信

寄存器 操作

号

CS IOR IOW A3 A2 A1 A0

内部先/ 后触发 器

数据总线

基本地 址寄存 器

写

2

当前地 址寄存 器

基本字 节计数 器 当前字 节计数 器

读

0 0 0 0 0 0 0 0

1 1 0 0 1 1 0 0

第八章

DMA技术

4.8237A各寄存器对应的端口地址(戴P268 )

表8-1 操作命令与有关信号的对应关系

CS

0 0 0

A3 A2 A1 A0

1 1 1 0 0 0 0 0 0 0 0 1

IOR IOW

0 1 1 1 0 0

命

令

读状态寄存器 写控制寄存器 写DMA请求标志寄存器

0

0 0

1

1 1

0

0 1

8237A在传送时有四种工作模式

① 单字节传送模式(戴P262 ) ② 块传送方式(戴P262 ) ③ 请求传送模式(戴P262)④级连传输模式 (戴P262)

在这种传送模式下,8237A可以进行连续的数据传送。当出现以下三种 情况之一时停止传送: a.字节计数器减到0,产生DMA传输结束信号,在线上输出一个有效脉冲。 b.由外界送来一个有效的信号 EOP 。 c.外界的DREQ信号变为无效(外设来的数据已送完)。

第十二章8237A_DMA控制器

DMA传输概念 DMA控制器的工作过程 1)当外设准备好,可以进行DMA传送时,外设向 DMA控制器发出“DMA传送请求”信号(DREQ); 2)DMA控制器收到请求后,向CPU发出“总线请求”信 号HOLD,表示希望占用总线 ; 3)CPU在完成当前总线周期后会立即对HOLD信号进 行响应。响应包括两个动作:一是CPU将数据总线 、地址总线和相应的控制信号线均置为高阻态,由 此放弃对总线的控制权。另一方面,CPU向DMA 控制器发出“总线响应”信号(HLDA)。 4)DMA控制器收到HLDA信号后,就开始控制总线, 并向外设发出DMA响应信号DACK;

格式:

D7

D6

D5

D4

D3

D2

D1

D0

D1~D0:选通道

不用

D2=1,设置屏蔽; D2 =0,清除屏蔽;

当屏蔽位置位时,该通道就禁止接受DREQ的DMA 请求信号。反之,屏蔽位复位则允许DREQ的请求。 当某一通道进行DMA传输后,产生EOP信号,则 这一通道在禁止自动预置工作条件下的屏蔽位置“1”。 必须再次编程, 使该通道屏蔽位复位, 才能进行下一 次的DMA传输。

8237A的组成和原理 三、8237的内部寄存器 3、命令寄存器 D3: 0=正常时序 ,1=压缩时序 D4: 0=固定优先级,通道0优先级最高,通道3优先 级最低; 1=循环优先级(顺序为:刚响应过的通道优先 级变为最低,以防止某一通道长期占用总线)。

D5: 1=扩展写信号,IOW/MEMW比正常时序提前 一个周期; 0=不扩展写信号 D6: 0= DREQ高电平有效; 1=DREQ低电平有效。 D7: 0= DACK低电平有效; 1=DACK高电平有效。

8237A的组成和原理 三、8237的内部寄存器 4、工作方式寄存器 (地址:A3 A2A1 A0 =1011B) 8位,设定DMA的传输模式,4个通道的模式寄存 器共用一个端口地址, 单字节传输模式:每次DMA操作只传送一字节后, 接着8237释放总线; 块传输模式:8237获得总线控制权后,连续传送多个 字节,直到所要求的字节数传输完(当前字节计 数器减至0),8237在EOP引脚上发出结束信 号,然后释放总线。在块传输过程中,若向8237 的EOP引脚上输入低电平,可强行结束传输; 请求传输模式:在传输过程中,8237要检测DREQ信 号(询问外设),当DREQ无效时,8237暂停传 输(不释放总线),当DREQ再次有效后,继续 进行传输;

GS882Z36BB-333IT资料

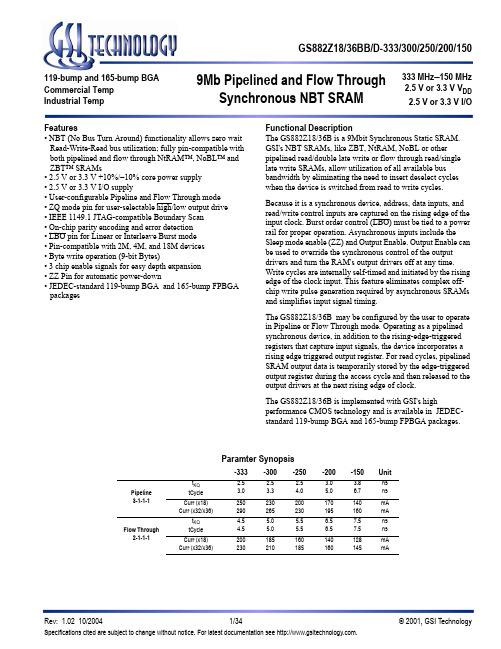

GS882Z18/36BB/D-333/300/250/200/1509Mb Pipelined and Flow ThroughSynchronous NBT SRAM333 MHz –150 MHz 2.5 V or 3.3 V V DD 2.5 V or 3.3 V I/O119-bump and 165-bump BGA Commercial Temp Industrial Temp Features• NBT (No Bus Turn Around) functionality allows zero wait Read-Write-Read bus utilization; fully pin-compatible with both pipelined and flow through NtRAM™, NoBL™ and ZBT™ SRAMs• 2.5 V or 3.3 V +10%/–10% core power supply • 2.5 V or 3.3 V I/O supply• User-configurable Pipeline and Flow Through mode • ZQ mode pin for user-selectable high/low output drive • IEEE 1149.1 JTAG-compatible Boundary Scan • On-chip parity encoding and error detection • LBO pin for Linear or Interleave Burst mode • Pin-compatible with 2M, 4M, and 18M devices • Byte write operation (9-bit Bytes)• 3 chip enable signals for easy depth expansion • ZZ Pin for automatic power-down• JEDEC-standard 119-bump BGA and 165-bump FPBGA packagesFunctional DescriptionThe GS882Z18/36B is a 9Mbit Synchronous Static SRAM. GSI's NBT SRAMs, like ZBT, NtRAM, NoBL or other pipelined read/double late write or flow through read/single late write SRAMs, allow utilization of all available bus bandwidth by eliminating the need to insert deselect cycles when the device is switched from read to write cycles. Because it is a synchronous device, address, data inputs, and read/write control inputs are captured on the rising edge of the input clock. Burst order control (LBO) must be tied to a power rail for proper operation. Asynchronous inputs include the Sleep mode enable (ZZ) and Output Enable. Output Enable can be used to override the synchronous control of the output drivers and turn the RAM's output drivers off at any time. Write cycles are internally self-timed and initiated by the rising edge of the clock input. This feature eliminates complex off-chip write pulse generation required by asynchronous SRAMs and simplifies input signal timing.The GS882Z18/36B may be configured by the user to operate in Pipeline or Flow Through mode. Operating as a pipelined synchronous device, in addition to the rising-edge-triggered registers that capture input signals, the device incorporates a rising edge triggered output register. For read cycles, pipelined SRAM output data is temporarily stored by the edge-triggered output register during the access cycle and then released to the output drivers at the next rising edge of clock.The GS882Z18/36B is implemented with GSI's highperformance CMOS technology and is available in JEDEC-standard 119-bump BGA and 165-bump FPBGA packages.Paramter Synopsis-333-300-250-200-150UnitPipeline 3-1-1-1t KQ tCycle 2.53.0 2.53.3 2.54.0 3.05.0 3.86.7ns ns Curr (x18)Curr (x32/x36)250290230265200230170195140160mA mA Flow Through 2-1-1-1t KQ tCycle 4.54.5 5.05.0 5.55.5 6.56.57.57.5ns ns Curr (x18)Curr (x32/x36)200230185210160185140160128145mA mAGS882Z36B Pad Out—119-Bump BGA—Top View (Package B)1234567A V DDQ A A NC A A V DDQB NC E2A ADV A E3NCC NC A A V DD A A NCD DQ C DQP C V SS ZQ V SS DQP B DQ BE DQ C DQ C V SS E1V SS DQ B DQ BF V DDQ DQ C V SSG V SS DQ B V DDQG DQ C DQ C B C A B B DQ B DQ BH DQ C DQ C V SS W V SS DQ B DQ B J V DDQ V DD NC V DD NC V DD V DDQ K DQ D DQ D V SS CK V SS DQ A DQ A L DQ D DQ D B D NC B A DQ A DQ A M V DDQ DQ D V SS CKE V SS DQ A V DDQ N DQ D DQ D V SS A1V SS DQ A DQ A P DQ D DQP D V SS A0V SS DQP A DQ A R NC A LBO V DD FT A PE T NC NC A A A NC ZZ U V DDQ TMS TDI TCK TDO NC V DDQGS882Z18B Pad Out—119-Bump BGA—Top View (Package B)1234567A V DDQ A A NC A A V DDQB NC E2A ADV A E3NCC NC A A V DD A A NCD DQ B NC V SS ZQ V SS DQPA NCE NC DQ B V SS E1V SS NC DQ AF V DDQ NC V SSG V SS DQ A V DDQG NC DQ B B B A NC NC DQ AH DQ B N C V SS W V SS DQ A NC J V DDQ V DD NC V DD NC V DD V DDQ K NC DQ B V SS CK V SS NC DQ A L DQ B NC NC NC B A DQ A NC M V DDQ DQ B V SS CKE V SS NC V DDQ N DQ B NC V SS A1V SS DQ A NC P NC DQP B V SS A0V SS NC DQ A R NC A LBO V DD FT A PE T NC A A NC A A ZZ U V DDQ TMS TDI TCK TDO NC V DDQ165 Bump BGA—x18 Commom I/O—Top View (Package D)1234567891011A NC A E1BB NC E3CKE ADV A17A A18AB NC A E2NC BA CK W G NC A NC BC NC NC V DDQ V SS V SS V SS V SS V SS V DDQ NC DQA CD NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA DE NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA EF NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA FG NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA GH FT MCH NC V DD V SS V SS V SS V DD NC ZQ ZZ H J DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC J K DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC K L DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC L M DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC M N DQB DNU V DDQ V SS NC NC NC V SS V DDQ NC NC N P NC NC A A TDI A1TDO A A A NC P R LBO NC A A TMS A0TCK A A A A R11 x 15 Bump BGA—13 mm x 15 mm Body—1.0 mm Bump Pitch165 Bump BGA—x36 Common I/O—Top View (Package D)1234567891011A NC A E1BC BB E3CKE ADV A17A NC AB NC A E2BD BA CK W G NC A NC BC DQC NC V DDQ V SS V SS V SS V SS V SS V DDQ NC DQB CD DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB DE DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB EF DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB FG DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB GH FT MCH NC V DD V SS V SS V SS V DD NC ZQ ZZ H J DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA J K DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA K L DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA L M DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA M N DQD DNU V DDQ V SS NC NC NC V SS V DDQ NC DQA N P NC NC A A TDI A1TDO A A A NC P R LBO NC A A TMS A0TCK A A A A R11 x 15 Bump BGA—13 mm x 15 mm Body—1.0 mm Bump PitchGS882Z18/36B BGA Pin DescriptionSymbol Type DescriptionA0, A1I Address field LSBs and Address Counter Preset InputsA I Address InputsDQ ADQ BDQ CDQ DI/O Data Input and Output pinsB A, B B, B C, B D I Byte Write Enable for DQ A, DQ B, DQ C, DQ D I/Os; active lowNC—No ConnectCK I Clock Input Signal; active highCKE I Clock Enable; active lowW I Write Enable; active lowE1I Chip Enable; active lowE3I Chip Enable; active lowE2I Chip Enable; active highG I Output Enable; active lowADV I Burst address counter advance enable; active highZZ I Sleep mode control; active highFT I Flow Through or Pipeline mode; active lowLBO I Linear Burst Order mode; active lowZQ I FLXDrive Output Impedance Control (Low = Low Impedance [High Drive], High = High Impedance [LowDrive])TMS I Scan Test Mode Select TDI I Scan Test Data In TDO O Scan Test Data Out TCK I Scan Test Clock MCH—Must Connect High DNU—Do Not UseV DD I Core power supplyV SS I I/O and Core GroundV DDQ I Output driver power supplyFunctional DetailsClockingDeassertion of the Clock Enable (CKE) input blocks the Clock input from reaching the RAM's internal circuits. It may be used to suspend RAM operations. Failure to observe Clock Enable set-up or hold requirements will result in erratic operation.Pipeline Mode Read and Write OperationsAll inputs (with the exception of Output Enable, Linear Burst Order and Sleep) are synchronized to rising clock edges. Single cycle read and write operations must be initiated with the Advance/Load pin (ADV) held low, in order to load the new address. Device activation is accomplished by asserting all three of the Chip Enable inputs (E1, E2, and E3). Deassertion of any one of the Enable inputs will deactivate the device.Function W B A B B B C B DRead H X X X XWrite Byte “a”L L H H HWrite Byte “b”L H L H HWrite Byte “c”L H H L HWrite Byte “d”L H H H LWrite all Bytes L L L L LWrite Abort/NOP L H H H HRead operation is initiated when the following conditions are satisfied at the rising edge of clock: CKE is asserted low, all three chip enables (E1, E2, and E3) are active, the write enable input signals W is deasserted high, and ADV is asserted low. The address presented to the address inputs is latched into the address register and presented to the memory core and control logic. The control logic determines that a read access is in progress and allows the requested data to propagate to the input of the output register. At the next rising edge of clock the read data is allowed to propagate through the output register and onto the output pins.Write operation occurs when the RAM is selected, CKE is active, and the Write input is sampled low at the rising edge of clock. The Byte Write Enable inputs (B A, B B, B C, and B D) determine which bytes will be written. All or none may be activated. A write cycle with no Byte Write inputs active is a no-op cycle. The pipelined NBT SRAM provides double late write functionality, matching the write command versus data pipeline length (2 cycles) to the read command versus data pipeline length (2 cycles). At the first rising edge of clock, Enable, Write, Byte Write(s), and Address are registered. The Data In associated with that address is required at the third rising edge of clock.Flow Through Mode Read and Write OperationsOperation of the RAM in Flow Through mode is very similar to operations in Pipeline mode. Activation of a Read Cycle and the use of the Burst Address Counter is identical. In Flow Through mode the device may begin driving out new data immediately after new address are clocked into the RAM, rather than holding new data until the following (second) clock edge. Therefore, in Flow Through mode the read pipeline is one cycle shorter than in Pipeline mode.Write operations are initiated in the same way, but differ in that the write pipeline is one cycle shorter as well, preserving the ability to turn the bus from reads to writes without inserting any dead cycles. While the pipelined NBT RAMs implement a double late write protocol in Flow Through mode a single late write protocol mode is observed. Therefore, in Flow Through mode, address and control are registered on the first rising edge of clock and data in is required at the data input pins at the second rising edge of clock.Synchronous Truth TableOperation Type Address CK CKE ADV W Bx E1E2E3G ZZ DQ Notes Read Cycle, Begin Burst R External L-H L L H X L H L L L QRead Cycle, Continue Burst B Next L-H L H X X X X X L L Q1,10 NOP/Read, Begin Burst R External L-H L L H X L H L H L High-Z2 Dummy Read, Continue Burst B Next L-H L H X X X X X H L High-Z1,2,10 Write Cycle, Begin Burst W External L-H L L L L L H L X L D3 Write Cycle, Continue Burst B Next L-H L H X L X X X X L D1,3,10 Write Abort, Continue Burst B Next L-H L H X H X X X X L High-Z1,2,3,10 Deselect Cycle, Power Down D None L-H L L X X H X X X L High-Z Deselect Cycle, Power Down D None L-H L L X X X X H X L High-Z Deselect Cycle, Power Down D None L-H L L X X X L X X L High-Z Deselect Cycle D None L-H L L L H L H L X L High-Z1 Deselect Cycle, Continue D None L-H L H X X X X X X L High-Z1 Sleep Mode None X X X X X X X X X H High-ZClock Edge Ignore, Stall Current L-H H X X X X X X X L-4 Notes:1.Continue Burst cycles, whether read or write, use the same control inputs. A Deselect continue cycle can only be entered into if a Dese-lect cycle is executed first.2.Dummy Read and Write abort can be considered NOPs because the SRAM performs no operation. A Write abort occurs when the Wpin is sampled low but no Byte Write pins are active so no write operation is performed.3.G can be wired low to minimize the number of control signals provided to the SRAM. Output drivers will automatically turn off duringwrite cycles.4.If CKE High occurs during a pipelined read cycle, the DQ bus will remain active (Low Z). If CKE High occurs during a write cycle, the buswill remain in High Z.5. X = Don’t Care; H = Logic High; L = Logic Low; Bx = High = All Byte Write signals are high; Bx = Low = One or more Byte/Writesignals are Low6.All inputs, except G and ZZ must meet setup and hold times of rising clock edge.7.Wait states can be inserted by setting CKE high.8.This device contains circuitry that ensures all outputs are in High Z during power-up.9. A 2-bit burst counter is incorporated.10.The address counter is incriminated for all Burst continue cycles.Pipelined and Flow Through Read Write Control State DiagramDeselectNew ReadNew WriteBurst ReadBurst WriteWRBRBWDDBBWRD BWRDDCurrent State (n)Next State (n+1)TransitionƒInput Command CodeKeyNotes1. The Hold command (CKE Low) is notshown because it prevents any state change.2. W, R, B, and D represent input commandcodes as indicated in the Synchronous Truth Table.Clock (CK)CommandCurrent StateNext Stateƒnn+1n+2n+3ƒƒƒCurrent State and Next State Definition for Pipelined and Flow through Read/Write Control State DiagramWRPipeline Mode Data I/O State DiagramIntermediateIntermediateIntermediateIntermediateIntermediateIntermediateHigh Z (Data In)Data Out (Q Valid)High Z B W B R B DRW RWDDCurrent State (n)TransitionƒInput Command CodeKeyTransitionIntermediate State (N+1)Notes1. The Hold command (CKE Low) is notshown because it prevents any state change.2. W, R, B, and D represent input command codes as indicated in the Truth Tables.Clock (CK)CommandCurrent StateIntermediate ƒn n+1n+2n+3ƒƒƒCurrent State and Next State Definition for Pipeline Mode Data I/O State DiagramNext StateStateFlow Through Mode Data I/O State DiagramHigh Z (Data In)Data Out (Q Valid)High Z B W B R B DRW RWDDCurrent State (n)Next State (n+1)TransitionƒInput Command CodeKeyNotes1. The Hold command (CKE Low) is notshown because it prevents any state change.2. W, R, B, and D represent input command codes as indicated in the Truth Tables.Clock (CK)CommandCurrent StateNext Stateƒnn+1n+2n+3ƒƒƒCurrent State and Next State Definition for: Pipeline and Flow Through Read Write Control State DiagramBurst CyclesAlthough NBT RAMs are designed to sustain 100% bus bandwidth by eliminating turnaround cycle when there is transition from read to write, multiple back-to-back reads or writes may also be performed. NBT SRAMs provide an on-chip burst address generator that can be utilized, if desired, to further simplify burst read or write implementations. The ADV control pin, when driven high, commands the SRAM to advance the internal address counter and use the counter generated address to read or write the SRAM. The starting address for the first cycle in a burst cycle series is loaded into the SRAM by driving the ADV pin low, into Load mode.Burst OrderThe burst address counter wraps around to its initial state after four addresses (the loaded address and three more) have beenaccessed. The burst sequence is determined by the state of the Linear Burst Order pin (LBO). When this pin is Low, a linear burst sequence is selected. When the RAM is installed with the LBO pin tied high, Interleaved burst sequence is selected. See the tables below for details.FLXDrive™The ZQ pin allows selection between NBT RAM nominal drive strength (ZQ low) for multi-drop bus applications and low drive strength (ZQ floating or high) point-to-point applications. See the Output Driver Characteristics chart for details.Note:There are pull-up devices on the ZQ and FT pins and a pull-down device on the ZZ pin, so those input pins can be unconnected and the chip will operate in the default states as specified in the above tables.Burst Counter SequencesBPR 1999.05.18Mode Pin FunctionsMode NamePin NameStateFunctionBurst Order Control LBO L Linear Burst H Interleaved Burst Output Register Control FT L Flow Through H or NC Pipeline Power Down ControlZZL or NC Active HStandby, I DD = I SBNote:The burst counter wraps to initial state on the 5th clock.Note:The burst counter wraps to initial state on the 5th clock.Linear Burst SequenceA[1:0]A[1:0]A[1:0]A[1:0]1st address 000110112nd address 011011003rd address 101100014th address11000110Interleaved Burst SequenceA[1:0]A[1:0]A[1:0]A[1:0]1st address 000110112nd address 010011103rd address 101100014th address11100100Sleep ModeDuring normal operation, ZZ must be pulled low, either by the user or by its internal pull down resistor. When ZZ is pulled high, the SRAM will enter a Power Sleep mode after 2 cycles. At this time, internal state of the SRAM is preserved. When ZZ returns to low, the SRAM operates normally after ZZ recovery time.Sleep mode is a low current, power-down mode in which the device is deselected and current is reduced to I SB 2. The duration of Sleep mode is dictated by the length of time the ZZ is in a High state. After entering Sleep mode, all inputs except ZZ become disabled and all outputs go to High-Z The ZZ pin is an asynchronous, active high input that causes the device to enter Sleep mode. When the ZZ pin is driven high, I SB 2 is guaranteed after the time tZZI is met. Because ZZ is an asynchronous input, pending operations or operations in progress may not be properly completed if ZZ is asserted. Therefore, Sleep mode must not be initiated until valid pending operations are completed. Similarly, when exiting Sleep mode during tZZR, only a Deselect or Read commands may be applied while the SRAM is recovering from Sleep mode.Sleep Mode Timing DiagramDesigning for CompatibilityThe GSI NBT SRAMs offer users a configurable selection between Flow Through mode and Pipeline mode via the FT signal found on Bump 5R. Not all vendors offer this option, however most mark Bump 5R as V DD or V DDQ on pipelined parts and V SS on flow through parts. GSI NBT SRAMs are fully compatible with these sockets.tZZRtZZHtZZStKLtKHtKCCKZZAbsolute Maximum Ratings(All voltages reference to V SS)Symbol Description Value UnitV DD Voltage on V DD Pins–0.5 to 4.6VV DDQ Voltage in V DDQ Pins–0.5 to 4.6VV I/O Voltage on I/O Pins–0.5 to V DDQ +0.5 (≤ 4.6 V max.)VV IN Voltage on Other Input Pins–0.5 to V DD +0.5 (≤ 4.6 V max.)VI IN Input Current on Any Pin+/–20mAI OUT Output Current on Any I/O Pin+/–20mAP D Package Power Dissipation 1.5WT STG Storage Temperature–55 to 125o CT BIAS Temperature Under Bias–55 to 125o C Note:Permanent damage to the device may occur if the Absolute Maximum Ratings are exceeded. Operation should be restricted to Recommended Operating Conditions. Exposure to conditions exceeding the Absolute Maximum Ratings, for an extended period of time, may affect reliability of this component.Power Supply Voltage RangesParameter Symbol Min.Typ.Max.Unit Notes3.3 V Supply Voltage V DD3 3.0 3.3 3.6V2.5 V Supply Voltage V DD2 2.3 2.5 2.7V3.3 V V DDQ I/O Supply Voltage V DDQ3 3.0 3.3 3.6V2.5 V V DDQ I/O Supply Voltage V DDQ2 2.3 2.5 2.7VNotes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn+2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.V DDQ3 Range Logic LevelsParameter Symbol Min.Typ.Max.Unit Notes V DD Input High Voltage V IH 2.0—V DD + 0.3V1V DD Input Low Voltage V IL–0.3—0.8V1V DDQ I/O Input High Voltage V IHQ 2.0—V DDQ + 0.3V1,3V DDQ I/O Input Low Voltage V ILQ–0.3—0.8V1,3 Notes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn+2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.3.V IHQ (max) is voltage on V DDQ pins plus 0.3 V.V DDQ2 Range Logic LevelsParameter Symbol Min.Typ.Max.Unit Notes V DD Input High Voltage V IH0.6*V DD—V DD + 0.3V1V DD Input Low Voltage V IL–0.3—0.3*V DD V1V DDQ I/O Input High Voltage V IHQ0.6*V DD—V DDQ + 0.3V1,3V DDQ I/O Input Low Voltage V ILQ–0.3—0.3*V DD V1,3 Notes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn+2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.3.V IHQ (max) is voltage on V DDQ pins plus 0.3 V.Recommended Operating TemperaturesParameter Symbol Min.Typ.Max.Unit Notes Ambient Temperature (Commercial Range Versions)T A02570°C2 Ambient Temperature (Industrial Range Versions)T A–402585°C2 Notes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn+2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.Note:These parameters are sample tested.Capacitance(T A = 25o C, f = 1 MH Z , V DD = 2.5 V)ParameterSymbolTest conditionsTyp.Max.UnitInput Capacitance C IN V IN = 0 V 45pF Input/Output Capacitance C I/OV OUT = 0 V67pFAC Test ConditionsParameterConditionsInput high level V DD – 0.2 V Input low level 0.2 V Input slew rate 1 V/ns Input reference level V DD /2Output reference levelV DDQ /2Output loadFig. 1Notes:1.Include scope and jig capacitance.2.Test conditions as specified with output loading as shown in Fig. 1unless otherwise noted.3.Device is deselected as defined by the Truth Table. 50% tKCV SS – 2.0 V50%V SS V IHUndershoot Measurement and TimingOvershoot Measurement and Timing50% tKCV DD + 2.0 V50%V DDV ILDQV DDQ/250Ω30pF *Output Load 1* Distributed Test Jig CapacitanceDC Electrical CharacteristicsParameter Symbol Test Conditions Min Max Input Leakage Current(except mode pins)I IL V IN = 0 to V DD–1 uA 1 uAZZ Input Current I IN1V DD≥V IN ≥V IH0 V≤ V IN ≤ V IH–1 uA–1 uA1 uA100 uAFT, ZQ Input Current I IN2V DD≥V IN ≥V IL0 V≤ V IN ≤ V IL–100 uA–1 uA1 uA1 uAOutput Leakage Current I OL Output Disable, V OUT = 0 to V DD–1 uA 1 uA Output High Voltage V OH2I OH = –8 mA, V DDQ = 2.375 V 1.7 V—Output High Voltage V OH3I OH = –8 mA, V DDQ = 3.135 V 2.4 V—Output Low Voltage V OL I OL = 8 mA—0.4 VNotes:1.I DD and I DDQ apply to any combination of V DD3, V DD2, V DDQ3, and V DDQ2 operation.2.All parameters listed are worst case scenario.Operating CurrentsParameterTest ConditionsModeSymbol-333-300-250-200-150Unit0to 70°C–40 to 85°C0to 70°C–40 to 85°C0to 70°C–40 to 85°C0to 70°C–40to 85°C0 to 70°C–40to 85°COperating CurrentDevice Selected; All other inputs ≥V IH o r ≤ V IL Output open(x32/x36)Pipeline I DD I DDQ 25040270402303525035200302203017025190251402016020mA Flow Through I DD I DDQ 20525225251852520525160251802514020160201301515015mA (x18)PipelineI DD I DDQ 23020250202102023020185152051515515175151301015010mA Flow Through I DD I DDQ 185152051517015190151451516515130101501012081408mA Standby CurrentZZ ≥ V DD – 0.2 V —PipelineI SB 40504050405040504050mA Flow Through I SB 40504050405040504050mA Deselect CurrentDevice Deselected; All other inputs ≥ V IH or ≤ V IL—PipelineI DD 951009095859075806065mA Flow ThroughI DD65606065606550555055mANotes:1.These parameters are sampled and are not 100% tested.2.ZZ is an asynchronous signal. However, in order to be recognized on any given clock cycle, ZZ must meet the specified setup and holdtimes as specified above.AC Electrical CharacteristicsParameterSymbol-333-300-250-200-150UnitMinMax Min Max Min Max Min Max Min Max PipelineClock Cycle Time tKC 3.0— 3.3— 4.0— 5.0— 6.7—ns Clock to Output Valid tKQ — 2.5— 2.5— 2.5— 3.0— 3.8ns Clock to Output Invalid tKQX 1.5— 1.5— 1.5— 1.5— 1.5—ns Clock to Output in Low-ZtLZ 1 1.5— 1.5— 1.5— 1.5— 1.5—ns Setup time tS 1.0— 1.0— 1.2— 1.4— 1.5—ns Hold time tH 0.1—0.1—0.2—0.4—0.5—ns Flow ThroughClock Cycle Time tKC 4.5— 5.0— 5.5— 6.5—7.5—ns Clock to Output Valid tKQ — 4.5— 5.0— 5.5— 6.5—7.5ns Clock to Output Invalid tKQX 2.0— 2.0— 2.0— 2.0— 2.0—ns Clock to Output in Low-ZtLZ 1 2.0— 2.0— 2.0— 2.0— 2.0—ns Setup time tS 1.3— 1.4— 1.5— 1.5— 1.5—ns Hold time tH 0.3—0.4—0.5—0.5—0.5—ns Clock HIGH Time tKH 1.0— 1.0— 1.3— 1.3— 1.5—ns Clock LOW Time tKL 1.2—1.2—1.5—1.5—1.7—ns Clock to Output inHigh-Z tHZ 1 1.5 2.5 1.5 2.5 1.5 2.5 1.5 3.0 1.5 3.0ns G to Output Valid tOE — 2.5— 2.5— 2.5— 3.0— 3.8ns G to output in Low-Z tOLZ 10—0—0—0—0—ns G to output in High-Z tOHZ 1— 2.5— 2.5— 2.5— 3.0— 3.8ns ZZ setup time tZZS 25—5—5—5—5—ns ZZ hold time tZZH 21—1—1—1—1—ns ZZ recoverytZZR20—20—20—20—20—nsPipeline Mode Timing (NBT)Write AWrite BWrite B+1Read CContRead DWrite ERead FDESELECTD(A)D(B)D(B+1)Q(C)Q(D)D(E)Q(F)tOLZtOEtOHZtHZtKQXtKQtLZ tHtStHtStHtStHtStHtStHtStHtStKC tKLtKHA BCD E FG*Note: E=High(False) if E1 = 1 or E2 = 0 or E3 = 1CKCKEE*ADVWBnA0–An DQa–DQd GFlow Through Mode Timing (NBT)JTAG Port OperationOverviewThe JTAG Port on this RAM operates in a manner that is compliant with IEEE Standard 1149.1-1990, a serial boundary scan interface standard (commonly referred to as JTAG). The JTAG Port input interface levels scale with V DD . The JTAG output drivers are powered by V DDQ .Write AWrite BWrite B+1Read CCont Read D Write E Read F Write GD(A)D(B)D(B+1)Q(C)Q(D)D(E)Q(F)D(G)tOLZ tOEtOHZtKQXtKQtLZtHZtKQX tKQ tLZtHtStHtStHtStHtStHtStHtStHtStKCtKLtKHABCDEFG*Note: E = High(False) if E1 = 1 or E2 = 0 or E3 = 1CKCKEEADVWBnA0–AnDQGDisabling the JTAG PortIt is possible to use this device without utilizing the JTAG port. The port is reset at power-up and will remain inactive unless clocked. TCK, TDI, and TMS are designed with internal pull-up circuits.To assure normal operation of the RAM with the JTAG Port unused, TCK, TDI, and TMS may be left floating or tied to either V DD or V SS . TDO should be left unconnected.JTAG Port Registers OverviewThe various JTAG registers, refered to as Test Access Port orTAP Registers, are selected (one at a time) via the sequences of 1s and 0s applied to TMS as TCK is strobed. Each of the TAP Registers is a serial shift register that captures serial input data on the rising edge of TCK and pushes serial data out on the next falling edge of TCK. When a register is selected, it is placed between the TDI and TDO pins.Instruction RegisterThe Instruction Register holds the instructions that are executed by the TAP controller when it is moved into the Run, Test/Idle, or the various data register states. Instructions are 3 bits long. The Instruction Register can be loaded when it is placed between the TDI and TDO pins. The Instruction Register is automatically preloaded with the IDCODE instruction at power-up or whenever the controller is placed in Test-Logic-Reset state.Bypass RegisterThe Bypass Register is a single bit register that can be placed between TDI and TDO. It allows serial test data to be passed through the RAM’s JTAG Port to another device in the scan chain with as little delay as possible.Boundary Scan RegisterThe Boundary Scan Register is a collection of flip flops that can be preset by the logic level found on the RAM’s input or I/O pins. The flip flops are then daisy chained together so the levels found can be shifted serially out of the JTAG Port’s TDO pin. The Boundary Scan Register also includes a number of place holder flip flops (always set to a logic 1). The relationship between the device pins and the bits in the Boundary Scan Register is described in the Scan Order Table following. The Boundary Scan Register, under the control of the TAP Controller, is loaded with the contents of the RAMs I/O ring when the controller is inCapture-DR state and then is placed between the TDI and TDO pins when the controller is moved to Shift-DR state. SAMPLE-Z, SAMPLE/PRELOAD and EXTEST instructions can be used to activate the Boundary Scan Register.JTAG Pin Descriptions PinPin NameI/ODescriptionTCK Test Clock In Clocks all TAP events. All inputs are captured on the rising edge of TCK and all outputs propagate from the falling edge of TCK.TMSTest Mode SelectInThe TMS input is sampled on the rising edge of TCK. This is the command input for the TAP controller state machine. An undriven TMS input will produce the same result as a logic one input level.TDI Test Data In InThe TDI input is sampled on the rising edge of TCK. This is the input side of the serial registers placed between TDI and TDO. The register placed between TDI and TDO is determined by the state of the TAP Controller state machine and the instruction that is currently loaded in the TAP Instruction Register (refer to the TAP Controller State Diagram). An undriven TDI pin will produce the same result as a logic one input level.TDO Test Data OutOut Output that is active depending on the state of the TAP state machine. Output changes inresponse to the falling edge of TCK. This is the output side of the serial registers placed betweenTDI and TDO.This device does not have a TRST (TAP Reset) pin. TRST is optional in IEEE 1149.1. The Test-Logic-Reset state is entered while TMS is held high for five rising edges of TCK. The TAP Controller is also reset automaticly at power-up.。

MEMORY存储芯片MAX823TEUK+T中文规格书

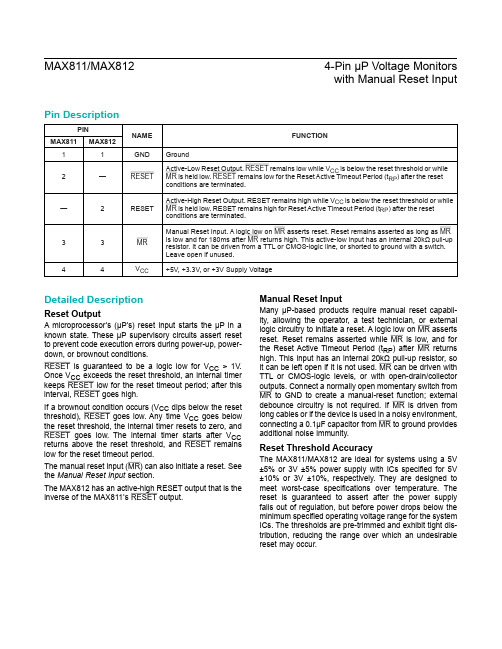

Manual Reset Input Many μP-based products require manual reset capabil -ity, allowing the operator, a test technician, or external logic circuitry to initiate a reset. A logic low on MR asserts reset. Reset remains asserted while MR is low, and for the Reset Active Timeout Period (t RP ) after MR returns high. This input has an internal 20kΩ pull-up resistor, so it can be left open if it is not used. MR can be driven with TTL or CMOS-logic levels, or with open-drain/collector outputs. Connect a normally open momentary switch from MR to GND to create a manual-reset function; external debounce circuitry is not required. If MR is driven from long cables or if the device is used in a noisy environment, connecting a 0.1μF capacitor from MR to ground provides additional noise immunity.Reset Threshold Accuracy The MAX811/MAX812 are ideal for systems using a 5V ±5% or 3V ±5% power supply with ICs specified for 5V ±10% or 3V ±10%, respectively. They are designed to meet worst-case specifications over temperature. The reset is guaranteed to assert after the power supplyfalls out of regulation, but before power drops below theminimum specified operating voltage range for the systemICs. The thresholds are pre-trimmed and exhibit tight dis -tribution, reducing the range over which an undesirable reset may occur.PINNAME FUNCTION MAX811MAX81211GND Ground 2—RESET Active-Low Reset Output. RESET remains low while V CC is below the reset threshold or while MR is held low. RESET remains low for the Reset Active Timeout Period (t RP ) after the reset conditions are terminated.—2RESET Active-High Reset Output. RESET remains high while V CC is below the reset threshold or while MR is held low. RESET remains high for Reset Active Timeout Period (t RP ) after the reset conditions are terminated.33MR Manual Reset Input. A logic low on MR asserts reset. Reset remains asserted as long as MR is low and for 180ms after MR returns high. This active-low input has an internal 20kΩ pull-up resistor. It can be driven from a TTL or CMOS-logic line, or shorted to ground with a switch. Leave open if unused.44V CC +5V, +3.3V, or +3V Supply Voltage Detailed DescriptionReset OutputA microprocessor’s (μP’s) reset input starts the μP in aknown state. These μP supervisory circuits assert resetto prevent code execution errors during power-up, power-down, or brownout conditions.RESET is guaranteed to be a logic low for V CC > 1V.Once V CC exceeds the reset threshold, an internal timerkeeps RESET low for the reset timeout period; after thisinterval, RESET goes high.If a brownout condition occurs (V CC dips below the resetthreshold), RESET goes low. Any time V CC goes belowthe reset threshold, the internal timer resets to zero, andRESET goes low. The internal timer starts after V CC returns above the reset threshold, and RESET remainslow for the reset timeout period.The manual reset input (MR ) can also initiate a reset. See the Manual Reset Input section.The MAX812 has an active-high RESET output that is theinverse of the MAX811’s RESET output.MAX811/MAX8124-Pin μP Voltage Monitorswith Manual Reset InputPin DescriptionTerminal Voltage (with respect to GND)V CC.....................................................................-0.3V to 6.0V All Other Inputs .....................................-0.3V to (V CC + 0.3V) Input Current, V CC, MR......................................................20mA Output Current, RESET or RESET ....................................20mA Continuous Power Dissipation (T A = +70°C)SOT143 (derate 4mW/°C above +70°C) .....................320mW Operating Temperature Range ...........................-40°C to +85°C Junction Temperature ......................................................+150°C Storage Temperature Range ............................-65°C to +160°C Lead Temperature (soldering, 10sec) .............................+300°C(V CC = 5V for L/M versions, V CC = 3.3V for T/S versions, V CC = 3V for R version, T A = -40°C to +85°C, unless otherwise noted. Typical values are at T A = +25°C.) (Note 1)PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITSOperating Voltage Range V CC T A = 0°C to +70°C 1.0 5.5V T A = -40°C to +85°C 1.2Supply Current I CC MAX81_L/M, V CC = 5.5V, I OUT = 0615µA MAX81_R/S/T, V CC = 3.6V, I OUT = 0 2.710Reset Threshold V TH MAX81_LT A = +25°C 4.54 4.63 4.72V T A = -40°C to +85°C 4.50 4.75MAX81_MT A = +25°C 4.30 4.38 4.46T A = -40°C to +85°C 4.25 4.50MAX81_TT A = +25°C 3.03 3.08 3.14T A = -40°C to +85°C 3.00 3.15MAX81_ST A = +25°C 2.88 2.93 2.98T A = -40°C to +85°C 2.85 3.00MAX81_RT A = +25°C 2.58 2.63 2.68T A = -40°C to +85°C 2.55 2.70Reset Threshold Tempco30ppm/°CV CC to Reset Delay (Note 2)V OD = 125mV, MAX81_L/M40µs V OD = 125mV, MAX81_R/S/T20Reset Active Timeout Period t RP V CC = V TH(MAX)140560ms MR Minimum Pulse Width t MR10µs MR Glitch Immunity (Note 3)100ns MR to Reset PropagationDelay (Note 2)t MD0.5µsMR Input Threshold V IHV CC > V TH(MAX), MAX81_L/M2.3V V IL0.8V IHV CC > V TH(MAX), MAX81_R/S/T0.7 x V CCV IL0.25 x V CCMR Pull-Up Resistance102030kΩRESET Output Voltage (MAX812)V OH I SOURCE = 150µA, 1.8V < V CC < V TH(MIN)0.8 x V CCV V OLMAX812R/S/T only, I SINK = 1.2mA,V CC = V TH(MAX)0.3MAX812L/M only, I SINK = 3.2mA,V CC = V TH(MAX)0.4MAX811/MAX8124-Pin μP Voltage Monitorswith Manual Reset Input Absolute Maximum RatingsStresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Electrical Characteristics。

GL823K Datasheet

GL823KUSB 2.0 SD Card Reader ControllerDatasheetRevision HistoryTable of ContentsCHAPTER 1GENERAL DESCRIPTION (6)CHAPTER 2FEATURES (7)CHAPTER 3PIN ASSIGMENT (8)3.1SSOP16 Pinout (8)3.2Pin Description (9)CHAPTER 4BLOCK DIAGRAM (10)4.1OCCS USB PHY (10)4.2SIE (10)4.3EPFIFO (10)4.4MCU (10)4.5MHE (11)4.6Regulator (11)4.7PMOS (11)CHAPTER 5ELECTRICAL CHARACTERISTICS (12)5.1Temperature Conditions (12)5.2Operating Conditions (12)5.3DC Characteristics (12)5.4Memory Card Clock Frequency (12)5.5Maximum Ratings (13)CHAPTER 6PACKAGE DIMENSION (14)CHAPTER 7ORDERING INFORMATION (15)List of FiguresFigure 3.1 – SSOP 16 Pinout Diagram (8)Figure 6.1 – SSOP 16 Pin Package (150 mil) (14)List of TablesTable 3.1 – Pin Description (9)Table 4.1 – Functional Block Diagram (10)Table 5.1 – Temperature Conditions (12)Table 5.2 – Operating Conditions (12)Table 5.3 – DC Characteristics (12)Table 5.4 – SD/MMC Card Clock Frequency (12)Table 5.5 – Maximum Ratings (13)Table 7.1 – Ordering Information (15)CHAPTER 1GENERAL DESCRIPTIONThe GL823K is a USB 2.0 Single-LUN card reader controller which can support SD/MMC Flash Memory Cards. It supports USB 2.0 high-speed transmission to Secure Digital TM(SD), SDHC, SDXC, miniSD TM, microSD TM(T-Flash), MultiMediaCard TM (MMC), RS MultiMediaCard TM (RS MMC), MMCmicro , HS-MMC and MMCmobile. As a single chip solution for USB 2.0 flash card reader, the GL823K complies with Universal Serial Bus specification rev. 2.0, USB Storage Class Specification ver.1.0, and each flash card interface specification.The GL823K integrates a high speed 8051 microprocessor and a high efficiency hardware engine for the best data transfer performance between USB and flash card interfaces. Its pin assignment design fits to card sockets to provide easier PCB layout. Inside the chip, it integrates 5V to 3.3V regulator, 3.3V to 1.8V regulator and power MOSFETs and it enables the function of on-chip clock source (OCCS) which means no external 12MHz XTAL is needed and that effectively reduces the total BOM cost.The GL823K implements USB disconnect function; it can be used for Mobile cable/ OTG reader/ PC card reader application.CHAPTER 2FEATURES●USB specification compliance-Comply with 480Mbps Universal Serial Bus specification rev. 2.0-Comply with USB Storage Class specification rev. 1.0-Support one device address and up to four endpoints: Control (0)/Bulk Read (1)/Bulk Write (2)/Interrupt (3) ●Integrated USB building blocks-USB2.0 transceiver macro (UTM), Serial Interface Engine (SIE), Build-in power-on reset (POR) and low-voltage detector (LVD)●Embedded 8051 micro-controller-Operate @ 60 MHz clock, 12 clocks per instruction cycle-Embedded mask ROM and internal SRAM●Secure Digital TM (SD) and MultiMediaCard TM (MMC)-Supports SD specification v1.0 / v1.1 / v2.0 / SDHC (Up to 32GB)-Compatible with SDXC (Up to 2TB)-Supports MMC specification v3.x / v4.0 / v4.1 / v4.2-Supports 1 / 4 bit data bus-Compliant with Secure Digital TM v5.0●Support boost mode for SD3.0 for better performance●Support non-SD Card Detect pin, non-MS Insertion/Removal pin design to save BOM cost●Support non-SD Write Protection pin design to save BOM cost●Support LED function to indicate power and access status●On chip clock source and no need of 12MHz Crystal Clock input●On-Chip 5V to 3.3V and 3.3V to 1.8V regulators●On-Chip power MOSFET for supplying flash media card power●Support USB disconnection by memory card unplug or manual switch for Mobile cable/ OTG reader/ PCcard reader application●Available in SSOP16 package (150 mil)CHAPTER 3 PIN ASSIGMENT3.1 SSOP16 Pinout38765214D 0D 2P M O S C M D V S S D 1D 3C L KFigure 3.1 – SSOP 16 Pinout Diagram3.2Pin DescriptionTable 3.1 – Pin DescriptionNotation:Type O OutputI InputB Bi-directionalpu internal pull-up when inputpd internal pull-down when inputP Power / GroundA AnalogCHAPTER 4BLOCK DIAGRAMTable 4.1 – Functional Block Diagram4.1OCCS USB PHYThe USB 2.0 Transceiver Macrocell is the analog circuitry that handles the low level USB protocol and signaling, and shifts the clock domain of the data from the USB 2.0 rate to one that is compatible with the general logic. On chip clock source and no need of 12MHz Crystal Clock input.4.2SIEThe Serial Interface Engine, which contains the USB PID and address recognition logic, and other sequencing and state machine logic to handle USB packets and transactions.4.3EPFIFOEndpoint FIFO includes Control FIFO (FIFO0) and Bulk In/Out FIFO●EP0 FIFO FIFO of control endpoint 0. It is 64-byte FIFO and used for endpoint 0 data transfer.●Interrupt FIFO 64-byte depth FIFO of endpoint 3 for status interrupt●Bulk FIFO It can be in the TX mode or RX mode:1. It contains ping-pong FIFO (512 bytes each bank) for transmit/receive data continuously.2. It can be directly accessed by micro-controller4.4MCU8051 micro-controller inside.●8051 Core Compliant with Intel 8051 high speed micro-controller●ROM FW code on ROM●SRAM Internal RAM area for MCU access4.5MHE●MIF Media Interface: SD/MMC●MCFIFO It can access by MCU for memory card short data packet.4.6Regulator●5V to 3.3V Band Gap Regulator for stable voltage supply for USB PHY, PMOS●3.3V to 1.8V For core logic and internal memory.4.7PMOSOn-Chip power MOSFETs for memory card powerCHAPTER 5ELECTRICAL CHARACTERISTICS 5.1Temperature ConditionsTable 5.1 – Temperature Conditions5.2Operating ConditionsTable 5.2 – Operating Conditions5.3DC CharacteristicsTable 5.3 – DC Characteristics5.4Memory Card Clock FrequencyTable 5.4 – SD/MMC Card Clock Frequency5.5Maximum RatingsTable 5.5 – Maximum RatingsCHAPTER 6PACKAGE DIMENSIONInternalNo.Lot CodeDateGL823KAAAAAAAAAAYWWXXXXVersionNo.Figure 6.1 – SSOP 16 Pin Package (150 mil)CHAPTER 7ORDERING INFORMATIONTable 7.1 – Ordering Information。

MAX823SEXK中文资料

MAX823SExKRev. ARELIABILITY REPORTFORMAX823SExKPLASTIC ENCAPSULATED DEVICESAugust 2, 2003MAXIM INTEGRATED PRODUCTS120 SAN GABRIEL DR.SUNNYVALE, CA 94086Written byReviewed byJim Pedicord Bryan J. Preeshl Quality Assurance Quality Assurance Reliability Lab Manager Executive DirectorConclusionThe MAX823S successfully meets the quality and reliability standards required of all Maxim products. In addition, Maxim’s continuous reliability monitoring program ensures that all outgoing product will continue to meet Maxim’s quality and reliability standards.Table of ContentsI. ........Device Description V. ........Quality Assurance InformationII. ........Manufacturing Information VI. .......Reliability EvaluationIII. .......Packaging InformationIV. .......Die Information ......AttachmentsI. Device DescriptionA. GeneralThe MAX823S microprocessor (µP) supervisory circuit combines reset output, watchdog, and manual reset input functions in 5-pin SOT23 and SC70 packages. It significantly improve system reliability and accuracy compared to separate ICs or discrete components. The MAX823S is specifically designed to ignore fast transients on V CC.The MAX823S has a eset threshold voltage of 2.93V. The device has an active-low reset output, which is guaranteed to be in the correct state for V CC down to 1V. The MAX823 offers a watchdog input and manual reset input..B. Absolute Maximum RatingsItem RatingVCC -0.3V to +6.0VAll Other Pins -0.3V to (VCC + 0.3V)Input Current, All Pins Except RESET and RESET 20mAOutput Current, RESET, RESET 20mAOperating Temperature RangeMAX823SEXK. -40°C to +85°CMAX823SEUK -40°C to +125°CStorage Temperature Range -65°C to +150°CLead Temperature (soldering, 10s) +300°CContinuous Power Dissipation (TA = +70°C)5-Pin SOT23 571mW5-Pin SC70 247mWDerates above +70°C5-Pin SOT23 7.1mW/°C5-Pin SC70 3.1mW/°CII. Manufacturing InformationA. Description/Function: 5-Pin Microprocessor Supervisory Circuits With Watchdog Timer and Manual ResetB. Process: B12 (Standard 1.2 micron silicon gate CMOS)C. Number of Device Transistors: 607D. Fabrication Location: California, USAE. Assembly Location: Malaysia or ThailandF. Date of Initial Production: January, 1997III. Packaging InformationA. Package Type: 5-Lead SOT23 5-Lead SC70B. Lead Frame: Copper Alloy 42C. Lead Finish: Solder Plate Solder PlateD. Die Attach: Silver-Filled Epoxy Non-Conductive EpoxyE. Bondwire: Gold (1.0 mil dia.) Gold (1.0 mil dia.)F. Mold Material: Epoxy with silica filler Epoxy with silica fillerG. Assembly Diagram: Buildsheet # 05-1601-0010 Buildsheet # 05-1601-0111H. Flammability Rating: Class UL94-V0 Class UL94-V0I. Classification of Moisture Sensitivityper JEDEC standard JESD22-112: Level 1Level 1IV. Die InformationA. Dimensions: 42 x 36 milsB. Passivation: Si3N4/SiO2 (Silicon nitride/ Silicon dioxide)C. Interconnect: Aluminum/Si (Si = 1%)D. Backside Metallization: NoneE. Minimum Metal Width: 1.2 microns (as drawn)F. Minimum Metal Spacing: 1.2 microns (as drawn)G. Bondpad Dimensions: 5 mil. Sq.H. Isolation Dielectric: SiO2I. Die Separation Method: Wafer SawV. Quality Assurance InformationA. Quality Assurance Contacts: Jim Pedicord (Manager, Reliability Operations)Bryan Preeshl (Executive Director)Kenneth Huening (Vice President)B. Outgoing Inspection Level: 0.1% for all electrical parameters guaranteed by the Datasheet.0.1% For all Visual Defects.C. Observed Outgoing Defect Rate: < 50 ppmD. Sampling Plan: Mil-Std-105DVI. Reliability EvaluationA. Accelerated Life TestThe results of the 135°C biased (static) life test are shown in Table 1. Using these results, the Failure Rate (λ) is calculated as follows:λ = 1 = 1.83 (Chi square value for MTTF upper limit)MTTFλ = 3.39 x 10-9λ = 3.39 F.I.T. (60% confidence level @ 25°C)This low failure rate represents data collected from Maxim’s reliability monitor program. In addition to routine production Burn-In, Maxim pulls a sample from every fabrication process three times per week and subjects it to an extended Burn-In prior to shipment to ensure its reliability. The reliability control level for each lot to be shipped as standard product is 59 F.I.T. at a 60% confidence level, which equates to 3 failures in an 80 piece sample. Maxim performs failure analysis on any lot that exceeds this reliability control level. Attached Burn-In Schematic (Spec. # 06-5033) shows the static Burn-In circuit. Maxim also performs quarterly 1000 hour life test monitors. This data is published in the Product Reliability Report (RR-1M).B. Moisture Resistance TestsMaxim pulls pressure pot samples from every assembly process three times per week. Each lot sample must meet an LTPD = 20 or less before shipment as standard product. Additionally, the industry standard 85°C/85%RH testing is done per generic device/package family once a quarter.C. E.S.D. and Latch-Up TestingThe MS04-3 die type has been found to have all pins able to withstand a transient pulse of ±1500V per Mil-Std-883 Method 3015 (reference attached ESD Test Circuit). Latch-Up testing has shown that this device withstands a current of ±250mA.Table 1Reliability Evaluation Test ResultsMAX823SExKTEST ITEM TEST CONDITION FAILURE SAMPLE NUMBER OFIDENTIFICATION PACKAGE SIZE FAILURES Static Life Test (Note 1)Ta = 135°C DC Parameters 320 0Biased & functionalityTime = 192 hrs.Moisture Testing (Note 2)Pressure Pot Ta = 121°C DC Parameters SOT23 77 0P = 15 psi. & functionality SC70 77 0RH= 100%Time = 168hrs.85/85 Ta = 85°C DC Parameters 77 0RH = 85% & functionalityBiasedTime = 1000hrs.Mechanical Stress (Note 2)Temperature -65°C/150°C DC Parameters 77 0Cycle 1000 Cycles & functionalityMethod 1010Note 1: Life Test Data may represent plastic DIP qualification lots.Note 2: Generic Package/Process dataAttachment #1TABLE II. Pin combination to be tested. 1/ 2/1/ Table II is restated in narrative form in 3.4 below. 2/ No connects are not to be tested. 3/ Repeat pin combination I for each named Power supply and for ground (e.g., where V PS1 is V DD , V CC , V SS , V BB , GND, +V S, -V S , V REF , etc). 3.4 Pin combinations to be tested. a.Each pin individually connected to terminal A with respect to the device ground pin(s) connected to terminal B. All pins except the one being tested and the ground pin(s) shall be open. b. Each pin individually connected to terminal A with respect to each different set of a combination of all named power supply pins (e.g., V SS1, or V SS2 or V SS3 or V CC1, or V CC2) connected to terminal B. All pins except the one being tested and the power supply pin or set of pins shall be open.c.Each input and each output individually connected to terminal A with respect to a combination of all the other input and output pins connected to terminal B. All pins except the input or output pin being tested and the combination of all the other input and output pins shall be open.Terminal A (Each pin individually connected to terminal A with the other floating) Terminal B (The common combination of all like-named pins connected to terminal B) 1. All pins except V PS1 3/ All V PS1 pins 2. All input and output pinsAll other input-output pinsMil Std 883DMethod 3015.7Notice 8TERMINAL BTERMINAL APROBE(NOTE 6) R = 1.5k Ω C = 100pf。

泡点测试仪-GS832

GS-832 全自动过滤器完整性测试仪FILTER INTEGRITY INSTRUMENT ===================================================操作手册OPERATION MANUAL上海格氏过滤设备有限公司目录测试原理 (1)一.气泡点法 (1)二.保压法 (1)仪器面板介绍 (2)一.面板 (2)二.背板介绍 (3)测试准备 (4)一.准备工作 (4)二.浸润滤材 (4)三.气路连接 (5)仪器操作 (6)一.开机 (6)二.预置日期和时间(功能1) (6)三.有预置值的自动气泡点测试(功能2) (7)四.无预置值的自动气泡点测试(功能3) (8)五.保压法测试(功能4) (9)六.手动测试功能(功能5) (10)七.气密性自检(功能6) (11)八.气流调节(功能7) (11)故障排除 (12)性能参数 (12)维护保养 (13)随机附件 (13)可选附件 (13)GS-832型全自动过滤器完整性测试仪GS-832型过滤器完整性测试仪适用于对过滤器进行完整性检测,判断过滤器的密封性是否完好、滤材有无破损以及选用的滤材过滤精度是否符合要求,以保证过滤器能按要求正常运行。

GS-832型测试仪是由微电脑控制的自动测试仪,应用经典的气泡点法和压力保持法(扩散流法的衍生方法)测试原理,能自动测试过滤器的完整性,测试精度高,操作简单方便,且所有的测试过程都在过滤器的上游进行,对过滤器的下游无污染,尤其适用于除菌过滤器的检测。

过滤器测试仪广泛运用于医药、生物工程、食品饮料、微电子等行业,也是过滤器制造商进行过滤器检测的常规仪器。

测试原理一. 气泡点法当滤材被液体(湿润液)浸润后,在滤材的两侧加上气体压差,由于毛细管效应,气体要将毛细管中的液体赶走而冒出气泡,气体的压差必须增大到某一值∆P,这个压差值就称为气泡点,其计算公式如式1。

式1表明,孔径愈小,气泡点愈高,因此可以用气泡点来检测过滤器的性能。

si823x中文数据手册

0.5 和 4.0 安 培 I S O D R I V E R ( 2. 5 和 5

特性

KVRMS)

一个封装内两个完全隔离的驱动 60 ns 传送延时 (最大) 器 独立 HS 和 LS 输入或 PWM 输入 最高 5 kVRMS 输入到输出隔离 版本 最高 1500 VDC 峰值驱动器到驱动 瞬态抑制 >45 kV/µs

宽体 SOIC-16 窄体 LGA-14

SOIC-16

应用

供电系统 电机控制系统 直流到直流隔离供电

照明控制系统 等离子显示器 太阳能和工业变换器

安全认证

UL 1577 认证

1

VDE 认证合规

60747-5-5 (VDE 0884 第 5 部分) EN 60950-1 (强化绝缘)

IEC

分钟内最多 5000 Vrms

CSA component notice 5A 认证

IEC

60950-1, 61010-1, 60601-1 CQC 认证 (强化绝缘) GB4943.1

描述