_2_1_7_维特比译码软件实现方法研究

卷积编码设计与仿真实验报告

卷积编码设计与仿真实验报告一、实验目的了解卷积码对信号的纠错性能,掌握维特比译码算法,分析卷积码不同码率下纠错能力的强弱,深刻理解CCSDS标准、信道编译码等相关概念和算法。

二、实验内容1、自己编码实现(2,1,3)卷积码的编译码,对比不同信噪比条件下,是否采用编码对于误码率性能的影响;2、基于MATLAB自带的vitdec函数实现对(2,1,7)卷积码以及2/3、3/4码率删除码的编译码,并对于不同码率抗噪声能力的强弱;3、构造BPSK调制、加性高斯白噪声的传输环境。

三、实验原理卷积码一般表示为(n,k,N)的形式,即将k个信息比特编码为n个比特的码组,N为编码约束长度,说明编码过程中相互约束的码段个数。

卷积码编码后的n个码元不仅与当前组的k个信息比特有关,还与前N-1个输入组的信息比特有关。

编码过程中相互关联的码元有N*n个。

R=k/n是编码效率。

编码效率和约束长度是衡量卷积码的两个重要参数。

典型的卷积码一般选n,k较小,但N值可取较大(>10),以获得简单而高性能的卷积码。

1、卷积码的编码原理卷积码的编码器一般比较简单,为一个具有k个输入端,n个输出端,m 级移位寄存器的有限状态有记忆系统。

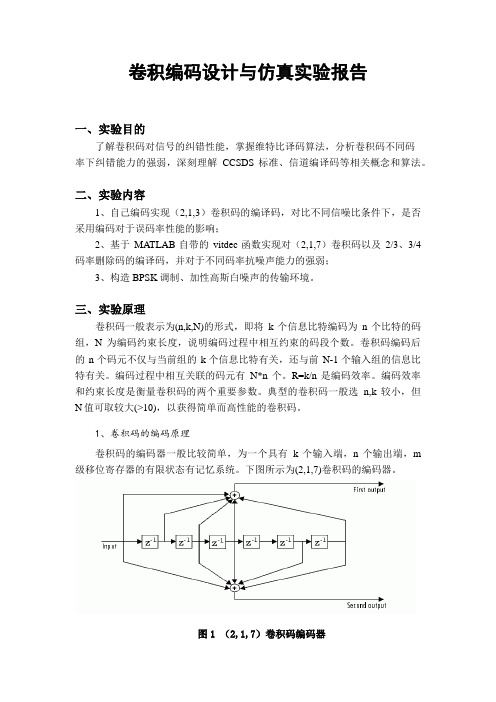

下图所示为(2,1,7)卷积码的编码器。

图1 (2,1,7)卷积码编码器若输入序列为u=(u0u1u2u3……),则对应两个码字序列 C1=(ca0ca1ca2ca3……)和C2=(cb0cb1cb2cb3……),相应的编码方程可写为 P1=u*C1,P2=u*C2,P=(P1,P2)。

“*”符号表示卷积运算,P1,P2表示编码器的两个冲激响应,即编码器的输出可以由输入序列和编码器的两个冲击响应卷积而得到,故称为卷积码。

这里的冲激响应指:当输入为[1 0 0 0 0 … … ]序列时,所观察到的两个输出序列值。

由于上图N 值为7,故冲激响应至多可持续到第7位,可写为P1=[1 1 1 1 0 0 1],P2=[1 0 1 1 0 1 1]然后将两个输出端的码字序列合并为一个码字序列为C=(ca0cb0ca1cb1ca2cb2……)。

维特比译码介绍

维特比提出了一种算法:译码器不是在篱笆图上一次就计算和比

较 2Lk 条路径,而是接收一段,就计算、比较一段,从而在每个状 态时,选择进入该状态的最可能的分支。

维特比译码的基本思想:将接收序列 R 与篱笆图上的路径逐分

支地比较,比较的长度一般取 (5~6)mn,然后留下与 R 距离最小的 路径,称为幸存路径,而去掉其余可能的路径,并将这些幸存路径 逐分支地延长并存储起来。

接收序列 R=[10,00,01,00,00,00,00,…]

2015/4/23

杭州电子科技大学通信学院

刘超

16

维特比译码的基本原理

1

S0

1 1

S1

3 2

S2

S3

2

R= 10

00

(2,1,2)码栅格图第二步

2015/4/23

杭州电子科技大学通信学院

刘超

17

维特比译码的基本原理

从第二个时刻起:第二个接收码组 R2=01 进入译码器,从

(2,1,2)码状态转移图(开放型)

编码器状态转移图

2015/4/23

杭州电子科技大学通信学院

刘超

7

卷积码的状态转移图与栅格描述

卷积码的栅格图(篱笆图)

状态图不能反映出状态转移与时间的关系 栅格图/篱笆图:将开放型的状态转移图按时间顺序 级联形成一个栅格图。 编码路径:状态序列σ在栅格图中形成的一条有向路 径。 当有向路径始于全“0”状态S0,又终于S0时,表明此 时编码器又回到全“0”状态,

S2

S2

S3

R= 10

S3

00

01

00

R= 10

00

01

_2_1_7_卷积编码及其维特比译码算法的软件实现

第4卷 第6期信息与电子工程Vo1.4,No.6 2006年12月INFORMATION AND ELECTRONIC ENGINEERING Dec.,2006 文章编号:1672-2892 (2006)06-0467-03(2,1,7)卷积编码及其维特比译码算法的软件实现刘少阳,邹永(国防科技大学电子科学与工程学院,湖南长沙 410073)摘要:提出了一种(2,1,7)卷积编码及其维特比(Viterbi)译码的软件实现方案,在Matlab环境中应用软件技术实现了(2,1,7)卷积码的Viterbi译码器功能。

测试证明,该Viterbi译码算法在低信噪比下的误码率仍能达到10-6。

关键词:卷积编码;维特比译码;Matlab中图分类号:TN957.51+3 文献标识码:ASoftware Implementation of (2,1,7) Convolutional Coding andIts Viterbi Decoding AlgorithmLIU Shao-yang,ZOU Yong(School of Electronic Science and Engineering,National University of Defense Technology,Changsha Hunan 410073,China)Abstract: A software scheme of (2,1,7) convolutional coding and Viterbi decoding technology is presented,which implements Viterbi decoder function of (2,1,7) convolutional code in the Matlab.According to the test, the BER(Bit Error Rate)of Viterbi algorithm can still reach 10-6in the lowSNR( Signal-to-Noise Ratio).Key words: convolutional coding;Viterbi decoding;Matlab1 引言卷积码是由Elias于1955年提出的。

维特比译码的仿真与实现

卷积码的码率越高 ,约束长度越大 ,所需维特比 译码的回溯长度也越长 。我们仍然就上面提出的那 个系统进行 Matlab 仿真 ,在回溯深度为 24 ,48 ,96 时分别观察其误码率曲线 (如图 2) 。可以看出回溯 深度对系统误码率的影响没有判决方式那么严重 ,但 是在误码率为 10 - 3时回溯深度为 24 的情况下所需信 噪比比 48 的情况下大约013 dB左右 ,这也是不可忽 略的 。但是回溯深度为 96 或者更长时相对于回溯深

了广泛地应用 。 本文首先使用 Matlab 分析了在无线高斯信道

中 ,对于维特比译码采用硬判决 、2 比特 、3 比特 、4 比特及 5 比特时的系统性能进行分析比较 ,同时也 分析了在回溯深度分别为 24 、48 和 96 时的系统性 能 ,得出结论 :在 3 比特软判决及回溯深度为 48 时 , 系统的性能达到最佳 。基于这些结论 ,用 Q1900 芯 片来实现卷积编码和维特比译码 ,其性能与仿真结 论一致 。

1 引 言

在无线通信系统中 ,为克服数据传输错误 ,需要 进行差错控制编码 。卷积编码是一种很好的纠错编 码方法 。它充分利用了各组之间的相关性 ,增加的 监督元不仅与本组的信息元有关 ,而且与前面若干 组的信息数字发生关系 ,这就是卷积码的基本想法 。 由于每个校验数字与更多的信息数字有关 ,无论从 理论上还是实际上均已证明其性能优于分组码 。与 卷积码相应的维特比译码算法是加性高斯白噪声 (additive white gaussian noise ,AW GN) 信道下卷积 码的最优译码算法 ,在数据通信和卫星通信中得到

第9章 Viterbi译码及其实现

“黑色经典”系列之《DSP嵌入式系统开发典型案例》第9章Viterbi译码及其实现华清远见<ARM开发培训班>培训教材在通信系统中,信息传输的可靠性和有效性是相当重要的。

信息在传输时是经由信道(Channel)传输。

当其在信道传输过程中会受到各种干扰,使得传输信息掺杂各种错误序列在其中。

因此,在通信系统中,良好的纠错码可以有效地应用在信息传输过程中,以降低信息的误码率。

信息在传输时,先由信源发出消息,如语言、图像、文字等,消息进入通信系统后,经由信源编码器编码成信息序列1。

编码过程中,为了使传输有效,还加上一些与传输信息无关的冗余度。

接着信息序列1经过信道编码器编码成信息序列2,序列2是将信息序列1加入了更多的冗余数据(Redundancy Data),以抵抗信道中的各种干扰。

数字信号一般不适合直接在信道上传输,所以调制器是将数字信号转变成模拟信号,使其在信道中传输。

而信道中难免会受到噪声干扰,使信道的输出序列不同于信道的输入序列。

解调器将信道的输出序列由原来的模拟信号转化成数字信号,既是接收序列3,信息序列中因噪声干扰会掺杂一些错误的码元在其中。

信道译码器利用序列中的冗余码元去纠正错误,并且根据信道译码器的结果,产生接近于信息序列1的接收序列1。

整个译码过程是根据信道编码的结果和噪声在信道中的特性所得到的。

理想的结果是所有的错误都被更正回来,即接收序列等同于发送序列。

9.1 Viterbi译码概述在众多的纠错码中,卷积码(Convolutional Code)是一种在实际中得到广泛应用、性能很好的纠错码。

卷积码是不同于分组码的另一种码,它虽然也是把k个信息比特编成n个比特,但k和n都很小,延时小,特别适宜于以串行形式传输信息。

与分组码不同,卷积码中编码后的n个码元不但与当前段的众个信息码元有关,而且与前面(N−1)段的信息有关,编码过程中相互关联的码元为Nn个。

在编码器复杂程度相同的情况下,卷积码的性能优于分组码。

_2_1_7_维特比译码器结构优化设计与实现(1)

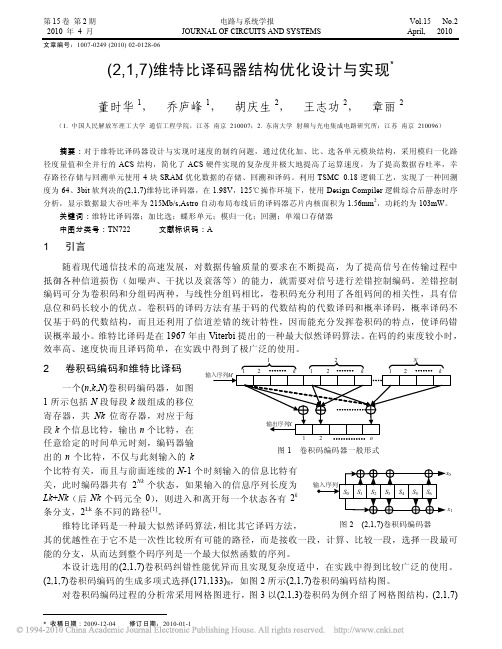

Viterbi 译码器的结构主要包含 4 个基本组成部 分[2]:分支度量单元(BMU:Branch Metric Unit)、 加比选单元(ACS:Add Compare Select)、幸存路 径存储单元(SPM:Survivor Path Memory)和回溯

a 00 b 01 c 10

Bn,i, j

−

Bn,k , j

=

⎪⎧0;

Cij = Ckj

⎪⎩⎨− 2 ynCij + 2 ynCij ; Cij

≠

Ckj

(2)

去掉式(2)中公因子 2,分支度量值可简化为:

Bn,i, j

=

− ynCij

⇒

⎪⎧− ⎪⎩⎨+

yn ; Cij yn ; Cij

=a = −a

(3)

此时仅剩下一个负号,实际算法时可以不用计算负号,而直接将求路径度量值的最小值改为求欧

SMx:表示状态 x 的状态度量值,在这里 x 为 i、j、p、q。 BMxk:表示输入比特为 k(k 为 0 或 l)时,状态 x 的分支度量。这里 x 为 i 或者 j。

130

电路与系统学报

第 15 卷

蝶形单元关系如下:

(1)状态 i 来说,蝶型的状态转移关系为: j = i + 2N−2; p = 2i; q = 2i + 1

关键词:维特比译码器;加比选;蝶形单元;模归一化;回溯;单端口存储器

中图分类号:TN722

文献标识码:A

1 引言

随着现代通信技术的高速发展,对数据传输质量的要求在不断提高,为了提高信号在传输过程中

抵御各种信道损伤(如噪声、干扰以及衰落等)的能力,就需要对信号进行差错控制编码。差错控制

无线通信系统维特比译码的FPGA仿真验证

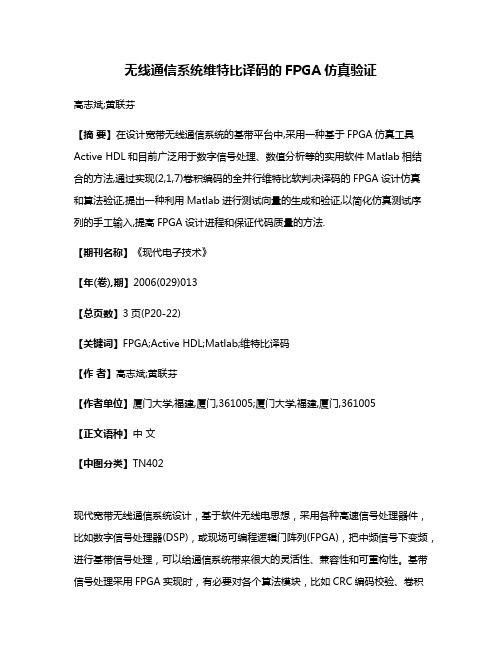

无线通信系统维特比译码的FPGA仿真验证高志斌;黄联芬【摘要】在设计宽带无线通信系统的基带平台中,采用一种基于FPGA仿真工具Active HDL和目前广泛用于数字信号处理、数值分析等的实用软件Matlab相结合的方法,通过实现(2,1,7)卷积编码的全并行维特比软判决译码的FPGA设计仿真和算法验证,提出一种利用Matlab进行测试向量的生成和验证,以简化仿真测试序列的手工输入,提高FPGA设计进程和保证代码质量的方法.【期刊名称】《现代电子技术》【年(卷),期】2006(029)013【总页数】3页(P20-22)【关键词】FPGA;Active HDL;Matlab;维特比译码【作者】高志斌;黄联芬【作者单位】厦门大学,福建,厦门,361005;厦门大学,福建,厦门,361005【正文语种】中文【中图分类】TN402现代宽带无线通信系统设计,基于软件无线电思想,采用各种高速信号处理器件,比如数字信号处理器(DSP),或现场可编程逻辑门阵列(FPGA),把中频信号下变频,进行基带信号处理,可以给通信系统带来很大的灵活性、兼容性和可重构性。

基带信号处理采用FPGA实现时,有必要对各个算法模块,比如CRC编码校验、卷积编码、维特比译码、交织、解交织等,进行功能仿真,通常也称为前仿真,本文提出一种利用Active HDL和Matlab结合的快速设计仿真的方法,实现对宽带无线通信系统中一个(2,1,7)卷积编码的维特比软判决译码的前仿真,以验证该模块的正确性。

1 Active HDL与Matlab简介Aldec公司的Active HDL软件,属于FPGA前端设计工具。

他可以结合其他公司的各种EDA工具,从而提供从程序代码编辑输入、网表综合、布局布线、甚至程序编程下载到CPLD或FPGA芯片上的整个设计平台。

他简单方便的Design Flow Manager设计,可以引导设计者完成完整的FPGA设计项目。

基于维特比算法的卷积码译码实验

基于维特比算法的卷积码译码实验摘要:本文主要简述了卷积码的编码过程,以及维特比算法译码的主要原理,是将接收到的编码序列与所有可能的发送序列作比较,选出汉明距离最小的一个序列作为译码输出。

本文根据维特比算法译码原理在matlab编写了程序仿真,对(2,1,7)卷积码数据进行加高斯白噪声,对比不同信噪比下的维特比译码误比特率。

关键词:卷积码;维特比;误比特率1引言卷积码是一种非分组码,它在1955年被伊利亚斯提出的卷积码在编码时是把k个比特的信息段编写成n个比特的码组,但是其监督码元不仅与当前编码比特信息有关,还与前面(N-1)个比特有关,N为卷积码的编码约束度,卷积码通常记为(n,k,N)[1]。

根据卷积码的特性,它更适合用于前向纠错,对于许多实际情况下它的效果好于分组码,并且运算简单,它尤其适合用在被高斯白噪声所干扰的传输信道[2]。

本文主要探索的是(2,1,7)卷积码的译码算法。

2卷积码的编码原理卷积码的编码器的主要由移位寄存器、模2加法器组成。

如图1[3]所示,为(2,1,7)卷积码的编码示意图,其卷积码的生成多项式的八进制表示为(133,171),八进制133转化为二进制为1011011,其中1比特的位置即代表那个移位寄存器的值作为模2加法器的输入,即生成多项式133描述的是图1中模2加法器输出Y,与此同理,生成多项式171描述的是模2加法器输出X。

至于生成多项式为什么是133和171,这其中涉及到编码的检错纠错能力问题、编码的复杂程度等因素,本文不深入探索这个。

很显然,共需要6个移位寄存器,和两个模2加法器来完成编码。

初始状态时,编码器的移位寄存器的值为0。

如待编码的信息序列为11,当第一个数据从最左端进去时,输出X的值为1,输出Y的值为1。

移位寄存器最右边的值不要了,然后把剩下的移位寄存器的值往右边移动一位,再把数据1放在移位寄存器的最左边。

然后再输入第二位待编码数据1,同理输出X值为0,输出Y的值为1。

(2,1,7)维特比译码软件实现方法研究

(2,1,7)维特比译码软件实现方法研究

米朔灵

【期刊名称】《微计算机信息》

【年(卷),期】2010(026)036

【摘要】(2,1,7)卷积码作为差错控制手段在卫星通讯领域得到了广泛应用.本文研究并实现了一种软件方式的基于(2,1,7)卷积编码的维特比译码(Viterbi)解决方案,测试结果表明,该方案能够使得误码率为10-3量级的数据经译码处理后误码率降低到10-6,可以满足维特比译码应用需求.

【总页数】3页(P110-111,103)

【作者】米朔灵

【作者单位】100086,中国科学院研究生院

【正文语种】中文

【中图分类】TP311.1

【相关文献】

1.(2,1,7)维特比译码器的并行算法实现 [J], 强秀丽;刘党辉;秦桂枝

2.一种串行结构的2,1,7卷积码维特比译码器的FPGA实现 [J], 黄华柱;刘荣科;王闰昕

3.(2,1,7)维特比译码器结构优化设计与实现 [J], 董时华;乔庐峰;胡庆生;王志功;章丽

4.(2,1,7)卷积编码及其维特比译码算法的软件实现 [J], 刘少阳;邹永

5.一种卷积码维特比译码算法的软件实现 [J], 张海勇;刘文予;芦东昕;吴畏

因版权原因,仅展示原文概要,查看原文内容请购买。

卷积编码和维特比译码的研究及其TMS320c54x上的实现

1.1研究背景

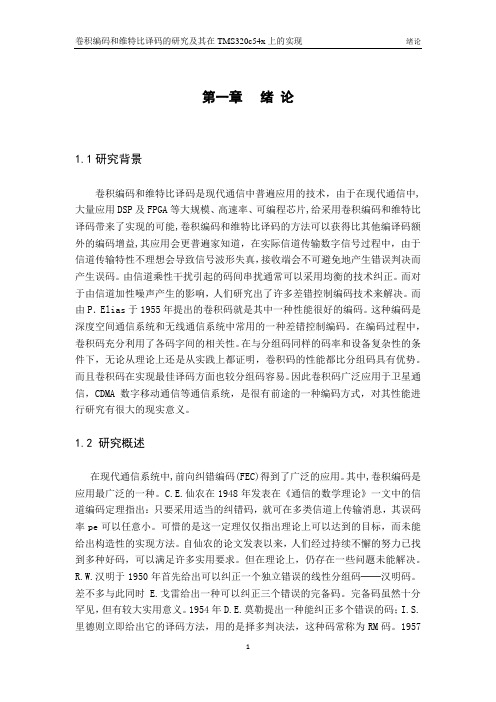

卷积编码和维特比译码是现代通信中普遍应用的技术,由于在现代通信中,大量应用DSP及FPGA等大规模、高速率、可编程芯片,给采用卷积编码和维特比译码带来了实现的可能,卷积编码和维特比译码的方法可以获得比其他编译码额外的编码增益,其应用会更普遍家知道,在实际信道传输数字信号过程中,由于信道传输特性不理想会导致信号波形失真,接收端会不可避免地产生错误判决而产生误码。由信道乘性干扰引起的码间串扰通常可以采用均衡的技术纠正。而对于由信道加性噪声产生的影响,人们研究出了许多差错控制编码技术来解决。而由P.Elias于1955年提出的卷积码就是其中一种性能很好的编码。这种编码是深度空间通信系统和无线通信系统中常用的一种差错控制编码。在编码过程中,卷积码充分利用了各码字间的相关性。在与分组码同样的码率和设备复杂性的条件下,无论从理论上还是从实践上都证明,卷积码的性能都比分组码具有优势。而且卷积码在实现最佳译码方面也较分组码容易。因此卷积码广泛应用于卫星通信,CDMA数字移动通信等通信系统,是很有前途的一种编码方式,对其性能进行研究有很大的现实意义。

第三章是研究在TMS320C54X上实现卷积码编译码的算法。

第四章用matlab语言编程和仿真,对卷积码的性能进了研究,分析了在不同码率、不同约束长度、不同回溯长度以及不同译码判决方式下viterbi译码的性能。

第五部分主要是对本课题的研究进行全文总结。

第二章 相关理论/技术研究

本章主要介绍卷积编码和维特比译码的原理以及其算法,并在文中对其性能就行了分析阐述

1.4本文工作安排

第一章讲述了卷积编码和维特比译码的研究内容和背景。

第二章论述卷积码的编码译码原理,生成矩阵法(输入信息序列与子生成元卷积运算,再将得到的编码按顺序排列得到)、状态图、网格图、树图。译码部分主要论述了viterbi译码基本原理,即以接收码流为基础,逐个计算它与其他所有可能出现的、连续的网格图路径的距离,选出其中量度最小的一条路径作为译码估值输出。

维特比译码算法

这周空时码的老师布置了一个编程的作业,有一天晚上突然兴起,熬夜到2点多,把这个程序写完了,虽然这个程序写的不算简单,于我自己毕竟是自己还是挺喜欢的,同学说我这个编程思想可以有点受C++的影响,不过我看了他写的那个,发现他在巧用矩阵方面确实比我强一点。

下面我把程序贴出来,并做一些简单的说明。

%维特比算法clear all;close all;filename=['tempdata_viterbi_v'];PAM=[-3 -1 1 3];N=10000; %产生序列的长度%x=[-3 3 1 -1 3 -1 -1 1 3 -3]; %输入xx_path=ceil(4*rand(1,N));for i=1:Nx(i)=PAM(x_path(i));endy=zeros(1,length(x)+1); %输出ypath=zeros(length(y),4); %路径存储L=zeros(length(y),4); %距离存储d=zeros(1,4);%SNR_dB=1:2:20;%count=1; %计数器for SNR_dB=1:20%检验输入序列for i=1:Nswitch x(i)case -3case -1case 1case 3otherwiseerror('wrong input.');endend%关于状态转移表(不加入噪声)y(i+1)=0.8*x(i+1)-0.6*x(i) P=[PAM;PAM;PAM;PAM];state=(0.8*P'-0.6*P); %生成状态转移表--取原表的转置,便于计算n=randn(1,length(x)); %噪声sigma=sqrt(5)*10^(-SNR_dB/20);%经过信道for i=1:length(x)if i==1y(i)=0.8*x(i)+sigma*n(i);elsey(i)=0.8*x(i)-0.6*x(i-1)+sigma*n(i);endend%viterbifor j=1:length(y);if j==1d=(y(j)-0.8*PAM).^2; %求下一状态不同电平的距离L(j,:)=d; %保存距离elsefor jj=1:4d=(y(j)-state(jj,:)).^2; %求下一状态不同电平的距离temp_L=L(j-1,:)+d;%temp_L=d;L(j,jj)=min(temp_L);r=find(temp_L(1:length(d))==min(temp_L));if length(r)==1 %min值可能有相同,这个算法应该可以改进,目前默认取第一个相等的min值path(j,jj)=r;elsepath(i,jj)=r(1);endendendend%找出最佳路径path_final=ones(1,length(y)-1);temp_L=L(length(y)-1,:);min_L=min(temp_L);path_final(end)=find(temp_L(1:length(temp_L))==min_L); for i=1:length(path_final)-1path_final(length(path_final)-i)=path(length(path_final)-i+ 1,path_final(length(path_final)-i+1));endy_final=-3*ones(1,length(path_final));for i=1:length(path_final)j=path_final(i);y_final(i)=PAM(j);end%检验译码输出for i=1:Nswitch y_final(i)case -3case -1case 1case 3otherwiseerror('wrong decoder.');endend%参数计算error_pattern(SNR_dB,:)=y_final-x; %错误图样errorNumber(SNR_dB)=nnz(error_pattern(SNR_dB,:)) %错误数FER(SNR_dB)=errorNumber(SNR_dB)/N; %错误率end%误码曲线图snr=1:SNR_dB;semilogy(snr,FER);xlabel('SNR(dB)');ylabel('FER');title('viterbi误码曲线图')grid on ;save(filename)说明输入电平 PAM=[-3 -1 1 3]序列长度 N=10000产生输入序列x经过信道输出序列yyi=0.8*xi-0.6*x(i-1)+n,其中是第i时刻输出,xi为第i时刻的输入当i=0,x0=0,表示寄存器里没有数据所以在源程序里面,用if语句把传输起始时刻和别的时刻分开计算。

结构优化的维特比译码器的实现方案

结构优化的维特比译码器的实现方案黄增先;王进华【摘要】针对维特比译码器译码过程中速度制约的问题,设计了一种结构优化的维特比译码器.该结构通过蝶形单元的直通互连,使得在状态转移过程中不需要对路径度量值进行大范围存储,简化了路径度量值的存储与读取逻辑.并且可以根据不同的应用要求灵活配置蝶形处理单元的复用次数.最后,结合FPGA平台,利用Verilog硬件描述语言和Vivado软件对译码器进行设计与实现.综合实现结果表明,该译码器占用1 564个LUT单元,能够在100 MHz系统时钟下进行有效译码.%In order to solve the problem of speed control in the decoding process of Viterbi decoder,a structure optimized Viterbi decoder is designed.Through the direct interconnection of the butterfly units,it is not necessary to store the path metric value during the state transition process,and the storage and reading logic of the path metric value is simplified.And the reuse times of butterfly processing units can be configured flexibly,according to different application requirements.Finally,combined with the FPGA platform,using Verilog hardware description language and Vivado software to design and implement the decoder.Implementation results show that the decoder occupies 1 564 LUTs of the FPGA,and can decode effectively under 100 MHz system clock.【期刊名称】《微型机与应用》【年(卷),期】2017(000)005【总页数】5页(P60-64)【关键词】维特比;回溯;蝶形单元;加比选;状态转移因子;FPGA【作者】黄增先;王进华【作者单位】福州大学电气工程与自动化学院,福建福州 350108;福州大学电气工程与自动化学院,福建福州 350108【正文语种】中文【中图分类】TN919在现代数字通信中,为降低数据传输的误码率,提高通信的质量及其可靠性,常在通信系统中采用纠错编码技术,其中卷积码就是一种具有较强纠错能力的纠错码[1]。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

摘要: (2,1,7)卷积 码 作 为 差 错 控 制 手 段 在 卫 星 通 讯 领 域 得 到 了 广 泛 应 用 。 本 文 研 究 并 实 现 了 一 种 软 件 方 式 的 基 于(2,1,7)卷 积 编 码 的 维 特 比 译 码 (Viterbi) 解 决 方 案 , 测 试 结 果 表 明 , 该 方 案 能 够 使 得 误 码 率 为 10-3 量 级 的 数 据 经 译 码 处 理 后 误 码 率 降 低 到 10-6, 可 以 满 足 维 特 比 译 码 应 用 需 求 。 关键词: 卷积码; Viterbi 译码; 蝶形运算 中图分类号: TP311.1 文献标识码: A

体汉明距离矩阵

定义如下:

应的输出

,并把

清空。

5、程序流程图

程序流程图如图 3 所示。

图 3 程序流程图

3.2 结果验证

在验证该维特比译码方案的性能时, 对多个不同的原始文

件进行测试。 这些原始文件都包含 107 个信息码元,首先对原始

文 件 进 行(2,1,7)卷 积 编 码,然 后 加 噪 声 处 理 以 后 进 行 维 特 比 译

码,最后对原始文件和维特比译码文件进行误码比较,从而统计

原始误码率和相应的维特比译码误码率。需要注意的是,噪声处

理是在卷积码文件中随机的修改固定个数的信息码元, 所以在

技 两 次测 验 中,即使 是 相 同的 原 始 误码 个 数,因为 其 误 码的 同。 表格 1 中给出测试过

路 径,减 少 传 统 的 回 溯 阶 段 。 本 文 所 述 算 法 已 经 应 用 于 单 位 科 研

项目中,稍加修改,可广泛应用于通讯等领域。

本文创新点: 使用两个路径度量寄存器,在蝶形运算模块采

用乒乓操作运算,有效简化蝶形运算。 同时,采用路径存储器及

时记录幸存路径,减少译码输出阶段的回溯时间。

5 结论

本文 的 创新 点 为:针 对 Ad hoc 接 入 网 中 Jelger 算 法 存 在 的 一些不足,引进了网关负载平衡的概念对原算法进行了改进,以 减少其网关切换次数。通过实验证明该改进算法与原算法相比, 能够降低节点平均网关切换次数,有效地平衡网关负载,可解决 因为最小跳数算法引起频繁切换网关和大量移动节点选择同 一网关而造成的负载过高等问题。 本文研究结果对于工业控 制、民用等各个方面的无线局域网接入技术的发展具有一定的 参考价值。 参考文献 [1] 郑少仁, 王海涛, 赵志峰等. Ad hoc 网络 [M]. 人民邮电出版 社, 2005.

术 程 中 得 到 的 平 均 数 据 , 从 表 格 1 中 可 以 看 到 原 始 误 码 率 在

10-3 数 量 级 时 , 维 特 比 译 码 误 码 率 达 到 10-6, 达 到 了 维 特 比

译码的目的。

创

表格 1 维特比译码前后误码率统计情况

新

假设理论输出码元比特为 ,接收到的信息码元比特为

,那么分支度量的计算公式就是:

。

3、加 -比 较 -选 择 (ACS)的 蝶 形 计 算

所谓“加”是指计算路径距离累加值。 维特比网格图中有 64

个 状 态,分 别 有 两 条 路 径 进 入 每 个 状 态 i,分 别 计 算 这 两 条 路 径

的分支度量值为

。 两条路径与相应的分支度量值相加

然后“比较”

图 2 维特比译码基本结构图

米朔灵: 硕士研究生

3.1 程序结构设计

- 110 - 360元 / 年 邮局订阅号:82-946

《现场总线技术应用 200 例》

您的论文得到两院院士关注

网络与通信

根据维特比译码原理, 一个完整的维特比译码软件包括以

下几个部分:信元输入、分支度量计算、ACS 蝶形计算、选取 最 佳

, 开辟两个数组来辅助乒乓操作

计算。 初始化为

,

其中 MAX 是 的近似值。

(2)译码深度 L,是指单次循环中处理信元的长度。 根据维特

比 译 码 截 断 定 理,译 码 深 度 最 小 为 5~10 倍 的 m,本 程 序 动 态 改

变译码深度,较理想译码深度为 L=48。

(3) 两个输出信息比特寄存器

this kind of Viterbi decoding algorithm is able to decrease the bit error rate from 10 -3 to 10 -6 and thus it can be used for error

技 control.

Key words: convolutional code; Viterbi decoding; Butterfly compute

路径和译码输出。 在一个译码周期内,读取输入信息码元后,计

算输入信息码元与各个可能输出码的分支度量值, 然后对每个

状态蝶形计算,最后选取幸存路径并译码输出。基本结构图如图

2 所示:

软件实现具体步骤如下:

1、程序初始化

在程序设计中需要首先确定三个重要参数路径度量器、译

码深度和输出信息寄存器。

(1)两 个 存 储 路 径 度 量 值 的 路 径 度 量 器

前路径度量值,避免单次循环后对 preDistance 的频繁更新。

4、输出译码信元

当输入码组超过译码深度时,开始产生译码输出,它是通过

比较 64 条幸存路径,选取其中具有最小距离的一条作 为 最 佳译

码路径, 然后输出该路径对应的路径寄存器中的相应的信息比

特,作为译码输出比特。 采用

记录

幸存路径,不需要回溯输出,只需要将与

有关。 卷积码的通用表示方式为(n,k,m),其中 k 表示在每个时间

单位, 输入编码器的信息码元个数;n 表示编码器 针对 k 个 输 入

的 输 出 码 元 个 数 ;m 则 表 示 编 码 约 束 长 度 。 本 文 将 重 点 讨 论

(2,1,7) 卷 积 码 ,(2,1,7) 卷 积 码 的 生 成 多 项 式 为 (171,133), 包 括 6

4.2 仿真结果分析 首先对两个算法 分别 进 行 了 900s 的 仿 真,统计 节 点 的平 均 网关切换次数,如图 3 所示。

图 3 节点的平均网关切换次数 我们可以看出,与原算法中网关切换次数相比,由于对网关 切换的条件做出了一定的限制, 改进算法中节点切换网关的次 数 有了 明 显 地减 少 。 在 原算 法 中 平均 每 个 节点 发 生 约 50 多 次 网 关 切 换,而 改 进 算 法 中 只 有 约 18 次,网 关 频 繁 切 换 的 问 题 得 到了较大改善。 接着又仿真了节点以 0~60 之 间 的多 个 不 同速 率 发 送 CBR 分组的情况,如图 4、图 5 所示。

网络与通信

文 章 编 号 :1008-0570(2010)12-3-0110-02

《微计算机信息》(管控一体化 )2010 年第 26 卷第 12-3 期

(2,1,7)维特比译码软件实现方法研究

Software Implementation of (2,1,7) Viterbi Decoding

(中国科学院研究生院) 米 朔 灵

但是硬件方式的解决方案使用受限, 必须要有与之配套的物理 然路径的支路,最后得到一条接近实际路径的幸存路径。维特比

接口。因此,深入研究方便使用的软件方式的维特比译码算法很 译码器有以下几个特点:

有必要。

1.(n,k,m)卷 积 码 共 有

个状态,因而一般的维特比译码

2 卷积码编 码和 Viterbi 译码

Abstract: The (2,1,7) convolutional code, as the recommended standard by CCSDS, has been applied widely in the field of com-

munication. This paper presents a software implementation of Viterbi decoding for (2,1,7) convolutional code. The result shows that

的最小值对

4 总结

本文 介 绍了 一 种(2,1,7)卷积 码 维 特比 译 码 算法 的 软 件 实 现

方案。维特比译码是一个动态编程的过程,其中“加-比较-选择”

模 块 是 核 心 模 块,该 方 案 在 “加-比 较 -选 择 ”模 块 中 引 入 乒 乓 操

作计算, 并使用输出信息比特寄存器及时记录译码过程中幸存

,

存储每个状态幸存路径的输出信息比特。 初始化为 null 矩阵。

2、计算分支度量

分支度量指的是输入信息码元和卷积编码各个可能输出

码元的距离。 一般有采用欧氏距离计算的软判决和采用汉明距

离计算的硬判决,在硬件设计中,软判决较硬判决优

。但

是,在软件设计中,分别采用软判决和硬判决的分支度量计算的

本质一样。故采用了实现较为简单的硬判决计算分支度量值,具

参考文献

[1]刘国锦,王济生等.卷积码的 Viterbi 高速译码方案[J].微计算机

信息.2009,6-2:p243-245

[2]王新梅,肖国镇.纠错码-原理与方法[M].西安电子科技大学出

版社.1991

[3]张宗橙. 编码理论-算法、结构和应用[M].人民邮电出版社.2009

[4]刘少阳,邹永.(2,1,7)卷积编码及其维特比译码算法的软件实

会因为存储量太大而难以实用化。根据维特比译码截断定理,译

图 1 (2,1,7)卷积编码状态转移示意图 2.1 卷积编码

码深度一般为 5~10 倍的 m.

3 Viterbi 译码的软 件实现

卷 积 码 是 Elise 于 1955 年 提 出 的 一 种 按 比 特 编 码 的 技 术,