Viterbi译码的MATLAB仿真研究

Matlab设计卷积编码和Viterbi已实现_read me

1、卷积编码和Viterbi解码的原理参见tutorial,代码编写都是基于该文档进行

网址:

或者附带的pdf文件

2、Convolutional Encoding采用Matlab自带的编码程序;可以在Matlab安装目

录下的通信工具箱中找到

3、测试程序testV对比了uncoded system & (2,1,2)卷积码经维特比解码后误码率

和信噪比曲线图,也可以采用别的卷积编码生成矩阵

4、由于无法压缩上传,故把代码放在一个word文档中,可将其中各子程序分

别复制出来保存为M。

注意有可能某些注释在doc文件中换行了,需要修改为注释

5、代码很少用matlab内部函数和工具箱,除某些参考网上设计外其余皆为自己

编写并测试通过,可修改其内容实现其他功能。

基于C54XDSP的viterbi译码技术

1 引言卷积码的概率码最早始于1961年由Wozencraft提出的序列译码,这是第一个实用的概率译码方法,1963年Fano对序列译码进行改进,提出Fano算法,从而推动了序列译码的实际应用。

1967年Viterbi提出了另一种概率译码算法:Viterbi算法,它是一种最大似然译码算法。

在码的约束比较小时,它比序列译码算法效率更高、速度更快,译码器也较简单。

因而自Viterbi算法提出以来,无论在理论上还是实践上都得到了极其迅速的发展,并广泛应用于各种数据传输系统,特别是卫星通信系统中。

1.1 卷积码的发展卷积码是深度空间通信系统和无线通信系统中常用的一种编码。

卷积码与分组码不同,它的本码组的校验元不仅与本组的信息元有关,而且还与以前各时刻输入至编码器的信息组有关。

在编码过程中,卷积码充分利用了各码字间的相关性,而且它的信息元和校验元也比分组码小,在与分组码同样的码率R和设备复杂性条件下,无论从理论上还是从实践上都证明卷积码的性能至少不比分组码差;而且卷积码在实现最佳译码也较分组码容易。

所以从信道编码定理来看,卷积码是一种非常有前途的码类。

在IS-95.CDMA的无线数字蜂窝标滩中都采用了卷积码;在第三代无线通信系统的蜂窝结构中所采用的Turbo码,也是源自卷积码。

卷积码是由伊利亚斯(P.Elias)发明的一种非分组码。

通常它更适用于前向纠错,因为对于许多实际情况它的性能优于分组码,而且运算简单。

卷积码是一种线性树码,由于该码的输出序列是输入序列和编码器的冲击响应的离散时间卷积,故名卷积码。

其一般结构包括:一个由N段组成的输入移位寄存器,每段k个,共Nk个移位寄存器、一组n个模2和相加器,一个由n级组成的输出移位寄存器。

对应于每段k个比特的输入序列,输出n个比特。

卷积码常记为(n,k,N-1),当k等于1时,N-1就是寄存器的个数。

卷积编码器是由记忆的,即一组信息码元的校验码元不但取决于本组信息元,而且还与前m=N-1组信息码元有关。

通信系统中Viterbi译码的Matlab仿真与实现

在现代通信 中, 信源 、 信宿和信道是组成通信系统 的最基本单元。其中信源是产生信息的源 , 信宿是信息 的 目的地, 信道则是传送载荷信息的信号所通 过的通 道, 信源和信宿之间是通过信道连接的¨ J 。 。通常从两 方 面来衡 量通信 系统的性 能指标 : 数量 和质 量 。一 般数

摘

要

数 字通信 作为一种前向纠错编码技 术卷积码起 着重要的作用 。相应地 ,信 息接 收端对卷积码 的译码 实现

也提 出了更高的要 求。文 中提 出的卷积码译码 Ma a 真方案 ,旨在用 Vt b 译码 实现对卷积码 译码的功能。仿 真结 tb仿 l i ri e 果表 明,维特 比是 一种 良好 的译码方式 。

量 指标用 有效性度 量 , 而质量 指标 用可靠 性度 量 。前者 主要取决 于信源 的统计特 I 而后 者主要 取决 于信 道 的 生, 统 计特性 。在信道 中传输数 字信 号 , 一般 要求信 源 端把 信息 转换成 电信号 , 用尽量低 速率 的二进 制数 字 信号 并

长度为 k的一个个分组 , 在某一 时刻 的编码输 出不 仅取 决于本 时刻的分组 而且 取 决于本 时刻 以前 的 ( N一1 个 ) 分组 , 这种距 离性决定 了卷积码潜在 的纠错能力 ] 。 下面 以参数 ( ,, ) 2 17 的卷 积码 为 例说 明卷 积 码编

a 叶技22 第2卷 3 0年 5 第 期 1

卷积码编码和维特比译码的原理、性能与仿真分析

卷积码编码和维特比译码的原理、性能与仿真分析1.引言卷积码的编码器是由一个有k位输入、n位输出,且具有m位移位寄存器构成的有限状态的有记忆系统,通常称它为时序网络。

编码器的整体约束长度为v,是所有k个移位寄存器的长度之和。

具有这样的编码器的卷积码称作[n,k,v]卷积码。

对于一个(n,1,v)编码器,约束长度v等于存储级数m.卷积码是由k个信息比特编码成n(n>k)比特的码组,编码出的n比特码组值不仅与当前码字中的k个信息比特值有关,而且与其前面v个码组中的v*k个信息比特值有关。

卷积码有三种译码方式:序列译码、门限译码和概率译码。

其中,概率译码根据最大似然译码原理在所有可能路径中求取与接收路径最相似的一条路径,具有最佳的纠错性能,维特比译码是概率译码中极重要的一种方式。

序列译码和门限译码则不一定能找出与接收路径最相似的一条路径。

不同于维特比译码,门限译码与序列译码所需的计算量是可变的且对于给定信息分组的最终判决仅仅基于(m+1)个接收分组,而不是基于整个接收序列。

与维特比译码所使用的对数似然量度不同,序列译码所使用的量度为Fano量度。

在接收序列受扰严重的情况下,序列译码的计算量大于维特比译码所需的固定计算量,虽然序列译码要求的平均计算次数通常小于维特比译码。

在采用并行处理的情况下,维特比译码的速度会优于序列译码。

在同样码率和存储级数的条件下,门限译码的性能比维特比译码低大约3dB.维特比译码的数据输出方式有硬判决及软判决两种方式,本文选取生成多项式为561,753的(2,1,8)卷积码对硬判决的性能进行分析,并依据维特比译码的原理以及卷积码的特性,对卷积码编码和维特比译码过程在加性高斯白噪声(AWGN)信道下进行仿真,并且根据仿真结果对维特比译码(硬判决)的结果进行分析。

由于卷积码的生成可以看做一个马尔科夫过程,因此,不同状态间的转移概率对描述这个过程有极关键的作用。

本文则基于MATLAB对不同状态间的转移概率进行求解,从而更准确地分析维特比译码的性能。

卷积编码与解码的MATLAB实现及性能分析

积编码与解码的MATLAB实现及性能分析摘要本课程设计主要解决通信系统中卷积编码与解码技术在Matlab中实现以及对其性能进行分析。

用贝努利二进制序列产生器作为信号源,产生基带信号,对其中的卷积进行编码,调制解调,然后采用Viterbi译码输出,最后计算误码率,对其性能进行分析。

关键词卷积码;卷积编码器;Viterbi译码器;BSK调制与解调;约束长度。

目录1引言 (4)1.1课程设计的目的 (4)1.2 课程设计的基本任务和要求 (4)1.2.1本次课程设计的基本任务 (4)1.2.2课程设计中的要求 (5)1.3设计平台 (5)2设计原理 (5)2.1卷积码的基本概念 (5)2.2卷积码的编码 (5)2.2.1卷积编码 (5)2.2.2卷积码的树状图 (6)2.2.3卷积码的网格图 (7)2.2.4卷积码的状态图 (8)2.3卷积码的解码 (8)3卷积码的仿真与性能分析 (9)3.1 卷积码的仿真 (9)3.1.1卷积码的设计框图 (9)3.1.2Simulink仿真模块的参数设置 (9)3.2 卷积码的波形输出 (15)3.2.1输入信号波形 (15)3.2.2输入信号与解码输出波形 (16)3.3卷积码的性能分析 (17)4出现的问题及解决方法 (19)5 结束语 (19)6参考文献 (20)1 引言本课程设计主要解决基于Matlab的Simulink下的模块对卷积编码与解码进行仿。

通过仿真可以更清楚的认识到卷积码的编码与解码的各个环节,并对仿真结果进行分析。

得出Viterbi译码的误码率性能和约束长度的关系。

1.1课程设计目的卷积码,又称连环码,是由伊莱亚斯(P.elias)于1955年提出来的一种非分组码[4]。

卷积码是一种向前纠错控制编码。

它将连续的信息比特序列映射为连续的编码器输出符号。

这种映射是高度结构化的,使得卷积码的译码方法与分组码译码所采用的方法完全不同。

可以验证的是在同样复杂度情况下,卷积码的编码增益要大于分组码的编码增益。

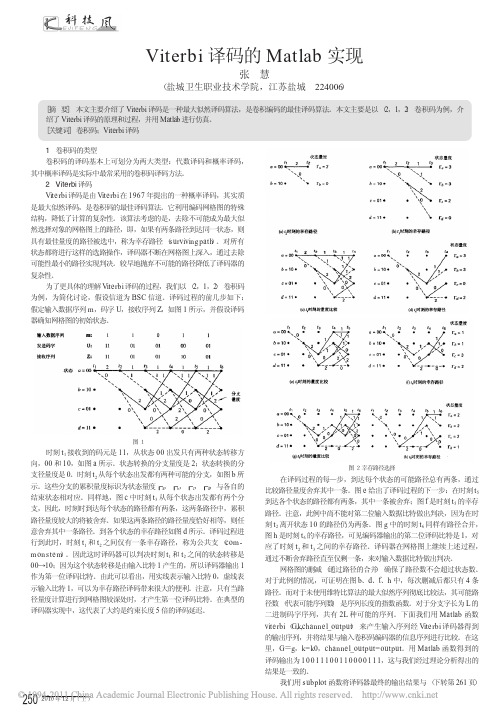

Viterbi译码的Matlab实现

2010年12月(上)Viterbi 译码的Matlab 实现张慧(盐城卫生职业技术学院,江苏盐城224006)[摘要]本文主要介绍了Viterbi 译码是一种最大似然译码算法,是卷积编码的最佳译码算法。

本文主要是以(2,1,2)卷积码为例,介绍了Viterbi 译码的原理和过程,并用Matlab 进行仿真。

[关键词]卷积码;Viterbi 译码1卷积码的类型卷积码的译码基本上可划分为两大类型:代数译码和概率译码,其中概率译码是实际中最常采用的卷积码译码方法。

2Viterbi 译码Viterbi 译码是由Viterbi 在1967年提出的一种概率译码,其实质是最大似然译码,是卷积码的最佳译码算法。

它利用编码网格图的特殊结构,降低了计算的复杂性。

该算法考虑的是,去除不可能成为最大似然选择对象的网格图上的路径,即,如果有两条路径到达同一状态,则具有最佳量度的路径被选中,称为幸存路径(surviving path )。

对所有状态都将进行这样的选路操作,译码器不断在网格图上深入,通过去除可能性最小的路径实现判决。

较早地抛弃不可能的路径降低了译码器的复杂性。

为了更具体的理解Viterbi 译码的过程,我们以(2,1,2)卷积码为例,为简化讨论,假设信道为BSC 信道。

译码过程的前几步如下:假定输入数据序列m ,码字U ,接收序列Z ,如图1所示,并假设译码器确知网格图的初始状态。

图1时刻t 1接收到的码元是11,从状态00出发只有两种状态转移方向,00和10,如图a 所示。

状态转换的分支量度是2;状态转换的分支径量度是0。

时刻t 2从每个状态出发都有两种可能的分支,如图b 所示。

这些分支的累积量度标识为状态量度┎a ,┎b ,┎c ,┎d ,与各自的结束状态相对应。

同样地,图c 中时刻t 3从每个状态出发都有两个分支,因此,时刻时到达每个状态的路径都有两条,这两条路径中,累积路径量度较大的将被舍弃。

如果这两条路径的路径量度恰好相等,则任意舍弃其中一条路径。

matlab卷积编码与viterbi译码的实现

matlab卷积编码与viterbi译码的实现MATLAB中viterbi译码算法讨论⼤家可以再评论区交流!!!MATLAB中实现viterbi译码的函数为:convenc其中:code = convenc(msg,trellis)vitdec其中:vitdec(code,trellis,tblen,opmode,dectype)code卷积编码,trellis⽹格表,tblen回溯长度,opmode:cont、term、trunc,dectype:unquant、hard、soft;本⼈最近在做⼀个关于viterbi译码算法,最终在FPGA中实现,在FPGA中最终的实现⽅案为xillinx IP核实现。

在此之前⽤MATLAB进⾏仿真验证。

matlab程序:Tre = poly2trellis(7,[133 171]);通过poly2trellis⽣成逻辑关系图,如下图所⽰。

逻辑关系图%卷积编码:msg = [0 1 0 1 1 0 1 0 1 1 1 1 0 0 1 1 0 0 1 0 1 0 0 1];code = convenc(msg,Tre);%code = [0,0,1,1,0,1,0,0,0,1,1,0,0,1,0,1,1,0,0,0,1,0,0,0,1,0,1,0,0,1,1,1,1,1,1,1,0,0,1,1,0,1,0,1,1,1,1,0];%这是通过convenc函数⽣成的卷积码%vitdec译码:%在vitdec译码过程中采⽤硬判决,通过不同的tblen和opmode来找出其中关系。

%(1) opmode = conttblen = 12;msg_dat = vitdec(code,Tre,tblen,'cont','hard');%msg_dat =[ 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 ];%通过了解到cont模式中,vitdec译码会有延迟,延迟的长度为tblen长度,所以在此对vitdec进⾏修改code_temp = [code,zeros(1,24)];msg_temp = vitdec(code_temp ,T,12,'cont','hard')msg_dat = msg_temp(13:end);%msg_dat = [ 0 1 0 1 1 0 1 0 1 1 1 1 0 0 1 1 0 0 1 0 1 0 0 1];%此时vitdec译码出来的数据和信源⼀样tblen = 18;code_temp = [code,zeros(1,24)];msg_temp = vitdec(code_temp ,T,12,'cont','hard')msg_dat = msg_temp(13:end);%msg_dat = [ 0 0 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 0 0 1 1 0 0];%此时vitdec译码出来的数据和信源在后⾯最后⼀位不⼀样%(2) opmode = termtblen = 12;msg_dat = vitdec(code,Tre,tblen,'term','hard');%msg_dat = [0 1 0 1 1 0 1 0 1 1 1 1 0 0 1 1 1 0 0 0 0 0 0 0];%此时vitdec译码出来的数据和信源⼀样前16位和信源⼀样后⾯的就出错了tblen = 18;msg_dat = vitdec(code,Tre,tblen,'term','hard');%msg_dat = [0 1 0 1 1 0 1 0 1 1 1 1 0 0 1 1 1 0 0 0 0 0 0 0];%此时vitdec译码出来的数据和信源⼀样前16位和信源⼀样后⾯的就出错了%(3)opmode = trunctblen = 12;msg_dat = vitdec(code,Tre,tblen,'trunc','hard');%msg_dat = [ 0 1 0 1 1 0 1 0 1 1 1 1 0 0 1 1 0 0 1 0 1 0 0 1];%此时vitdec译码出来的数据和信源⼀样tblen = 18;msg_dat = vitdec(code,Tre,tblen,'trunc','hard');%msg_dat = [ 0 1 0 1 1 0 1 0 1 1 1 1 0 0 1 1 0 0 1 0 1 0 0 1];%此时vitdec译码出来的数据和信源⼀样总结:以上通过⽐较tblen和opmode模式的不同对产⽣的结果,其中cont和trunc的模式总结起来就是cont有tblen延迟,但是trunc没有。

通信原理维特比解码matlab

通信原理维特比解码Matlab实现维特比解码(Viterbi decoding)是一种广泛应用于通信系统的算法,尤其在卷积码的解码中。

以下是一个基于Matlab的维特比解码实现的简要指南,主要包含初始化参数、构建状态网格、计算路径概率、更新最佳路径、计算最终解码结果、输出解码数据、性能评估和可视化结果等步骤。

1.初始化参数2.在开始维特比解码之前,需要设置一些参数,如卷积码的生成多项式、约束长度、编码比特率等。

这些参数将用于构建状态网格和计算路径概率。

3.构建状态网格4.状态网格是用于表示卷积码状态转移的图。

在Matlab中,可以使用二维数组来表示状态网格。

每个状态由一个二元组表示,例如 (00,01)、(00,10)、(01,00) 等。

5.计算路径概率6.在构建了状态网格之后,需要计算每个状态到接收序列的路径概率。

这可以通过使用动态规划的方法来完成。

在Matlab中,可以使用递归函数来计算路径概率。

7.更新最佳路径8.在计算了所有路径概率之后,需要更新最佳路径。

最佳路径是指具有最大概率的路径。

在Matlab中,可以使用动态规划的思想来更新最佳路径。

9.计算最终解码结果10.一旦找到了最佳路径,就可以根据该路径计算出原始的未编码数据。

在Matlab中,可以使用一个递归函数来解码最佳路径并输出原始数据。

11.输出解码数据12.最后,将解码后的数据输出到控制台或保存到文件中。

在Matlab中,可以使用fprintf函数将数据写入文件,或者使用disp函数将数据输出到控制台。

13.性能评估14.为了评估维特比解码的性能,可以使用一些性能指标,如误码率(BER)和误帧率(FER)。

在Matlab中,可以使用循环和条件语句来计算这些性能指标。

15.可视化结果16.最后,可以将维特比解码的过程进行可视化,以更直观地了解解码性能。

在Matlab中,可以使用plot函数来绘制状态网格和最佳路径等图示。

第9章Viterbi译码及其实现

第9章Viterbi译码及其实现Viterbi译码是一种使用动态规划算法来解码卷积码的方法,它通过寻找最有可能的路径来恢复被编码的数据。

在这篇文章中,我们将介绍Viterbi译码的基本原理以及如何实现它。

1. Viterbi译码原理:Viterbi译码是一种基于有向无环图(DAG)的动态规划算法。

它的基本思想是在每一个时刻,选取最有可能的路径来解码出当前的数据。

具体来说,它会使用一个状态转移图来表示每个时刻的状态以及状态之间的转移。

每个状态表示接收到的一串码元,其中可能包含错误。

在Viterbi译码中,我们需要确定的是在给定的时刻,以及所有之前的时刻,哪个状态是最有可能接收到当前的码元。

为了实现这一点,我们需要每个时刻的状态转移图以及每个状态接收到正确码元的概率。

通过比较不同路径的概率,我们可以选择最有可能的路径。

2. Viterbi译码实现:Viterbi译码可以通过以下步骤实现:1)初始化:在初始时刻,我们首先需要将所有状态的概率初始化为1,并将每个状态的前一个状态设置为初始状态。

这样做是为了确保在选择路径时考虑所有可能的路径。

2)递推计算:从初始时刻开始,我们根据每个状态接收到的码元和切换到下一个状态的概率,更新每个状态的概率以及前一个状态。

具体来说,我们可以使用以下公式进行计算:当前状态概率=当前状态接收到的码元概率*前一个状态概率*切换到当前状态的概率3)路径选择:一旦计算出所有状态的概率,我们可以比较不同路径的概率,选择最有可能的路径。

具体来说,我们可以从最后一个时刻的状态开始,根据每个状态的概率选择前一个状态,直到回到初始状态。

4)结果恢复:一旦选择了最有可能的路径,我们可以根据这条路径中每个状态接收到的码元恢复原始数据。

通过以上步骤,我们可以使用Viterbi译码来解码卷积码并恢复原始数据。

总结:Viterbi译码是一种有效的卷积码译码方法,它使用了动态规划算法来选择最有可能的路径。

卷积码编译码matlab仿真

一、概述卷积码是一种常用的编码技术,用于提高数字通信系统的可靠性和抗干扰能力。

而编码的解码过程则需要运用编译码技术,以恢复原始数据。

Matlab作为一种强大的工程仿真软件,可以用来对卷积码编译码进行仿真分析,帮助工程师们更好地理解和优化卷积码系统,提高通信系统的性能。

二、卷积码原理1. 卷积码的概念卷积码是一种线性块码,它采用移位寄存器和模2加法器进行编码,通过引入冗余比特来提高信号的可靠性。

卷积码的编码过程可以简单描述为:将输入信息数据与特定的生成多项式进行卷积运算,得到编码后的输出数据。

2. 卷积码的特点卷积码具有较高的编码效率和能够很好地控制码长、纠错能力等特性,因此在实际通信系统中得到广泛应用。

三、编译码原理1. Viterbi算法卷积码的译码过程通常采用Viterbi算法,它是一种最大似然译码算法,通过计算最小距离路径的方式来进行译码。

Viterbi算法能够有效地对卷积码进行解码,提高译码的准确性。

2. 编译码的实现在Matlab中,编译码的实现通常是通过编写一定的程序来模拟Viterbi算法的译码过程。

通过仿真分析,可以评估不同的编码方案对通信系统性能的影响。

四、Matlab仿真环境1. Matlab的特点Matlab作为一种强大的仿真软件,具有丰富的工具和函数库,能够方便地进行数字通信系统设计与仿真分析。

Matlab提供了直观的图形界面和强大的数据处理能力,可用于展示仿真结果和进行数据分析。

2. 使用Matlab进行卷积码编译码仿真在Matlab环境中,可以编写程序来实现卷积码的编码和Viterbi算法的译码过程。

通过调用Matlab中的工具函数和绘图函数,可以直观地展示通信系统的性能指标,并对比不同编码方式的性能差异。

五、仿真实例分析1. 卷积码编码仿真我们可以编写Matlab程序,实现对卷积码的编码过程。

通过模拟不同的编码率和约束长度,可以观察到编码后的效果,并评估编码的性能。

MATLAB实现卷积码编译码

本科生毕业论文(设计)题目:MATLAB实现卷积码编译码专业代码:作者姓名:学号:单位:指导教师:年月日目录前言----------------------------------------------------- 1 1. 纠错码基本理论---------------------------------------- 21.1纠错码基本理论 ----------------------------------------------- 21.1.1纠错码概念 ------------------------------------------------- 21.1.2基本原理和性能参数 ----------------------------------------- 21.2几种常用的纠错码 --------------------------------------------- 62. 卷积码的基本理论-------------------------------------- 82.1卷积码介绍 --------------------------------------------------- 82.1.1卷积码的差错控制原理----------------------------------- 82.2卷积码编码原理 ---------------------------------------------- 102.2.1卷积码解析表示法-------------------------------------- 102.2.2卷积码图形表示法-------------------------------------- 112.3卷积码译码原理---------------------------------------------- 152.3.1卷积码三种译码方式------------------------------------ 152.3.2V ITERBI译码原理---------------------------------------- 163. 卷积码编译码及MATLAB仿真---------------------------- 183.1M ATLAB概述-------------------------------------------------- 183.1.1M ATLAB的特点------------------------------------------ 193.1.2M ATLAB工具箱和内容------------------------------------ 193.2卷积码编码及仿真 -------------------------------------------- 203.2.1编码程序 ---------------------------------------------- 203.3信道传输过程仿真-------------------------------------------- 213.4维特比译码程序及仿真 ---------------------------------------- 223.4.1维特比译码算法解析------------------------------------ 233.4.2V ITERBI译码程序--------------------------------------- 253.4.3 VITERBI译码MATLAB仿真----------------------------------- 283.4.4信噪比对卷积码译码性能的影响 -------------------------- 283.4.5码率对卷积码译码性能的影响 ---------------------------- 303.4.6约束长度对卷积码误码性能的影响------------------------ 313.4.7回溯长度对卷积码误码性能的影响 ------------------------ 323.4.8判决方式对卷积码误码性能的影响------------------------ 324. 结论及展望------------------------------------------ 344.1结论-------------------------------------------------------- 344.2展望 -------------------------------------------------------- 355. 结束语----------------------------------------------- 36参考文献------------------------------------------------ 37致谢---------------------------------------------------- 38附录---------------------------------------------------- 39摘要在数字通信系统中,通常采用差错控制编码来提高系统的可靠性。

Matlab的卷积码译码器的设计与仿真

Matlab的卷积码译码器的设计与仿真540802 112008111郭林《基于Matlab的卷积码译码器的设计与仿真》第1页共17页Matlab**本课程设计主要解决对一个输入信号进行卷积码编码,以及维特比(Viterbi)译码输出,并通过Matlab软件进行设计与仿真,并进行误码率分析。

程序设计与仿真均采用Matlab R2007a(7.4),最后仿真详单与理论分析一致。

卷积码编码器;卷积码译码器;Matlab;设计与仿真1本课程设计主要解决对一个信号进行信道编解码,采用卷积码编码,维特比(Viterbi)译码输出,并通过Matlab软件进行设计与仿真。

卷积码的译码有两种方法——软判决和硬判决,此课程设计采用硬判决的维特比译码。

1.1卷积码是一种向前纠错控制编码。

它将连续的信息比特序列映射为连续的编码器输出符号。

这种映射是高度结构化的,使得卷积码的译码方法与分组码译码所采用的方法完全不同。

可以验证的是在同样复杂度情况下,卷积码的编码增益要大于分组码的编码增益。

对于某个特定的应用,采用分组编码还是采用卷积编码哪一种更好则取决于这一应用的具体情况和进行比较时可用的技术。

本课程设计便是通过Matlab,构造了一个卷积码编码后,通过产生加性高斯白噪声的信道,再进行译码的过程,译码后计算误码率,并进行分析。

郭林《基于Matlab的卷积码译码器的设计与仿真》第2页共17页 1.2 2卷积码,又称连环码,是由伊莱亚斯(P.elias)于1955年提出来的一种非分组码。

卷积编码的最佳译码准则为:在给定已知编码结构、信道特性和接收序列的情况下,译码器将把与已经发送的序列最相似的序列作为传送的码字序列的估值。

对于二进制对称信道,最相似传送序列就是在汉明距离上与接收序列最近的序列。

卷积码的译码方法有两大类:一类是大数逻辑译码,又称门限译码(硬判决,编者注);另一种是概率译码(软判决,编者注),概率译码又分为维特比译码和序列译码两种。

matlab维特比译码

维特比(Viterbi)译码是一种用于解码卷积码的算法,常用于通信和数据存储系统。

在MATLAB中实现维特比译码主要涉及以下步骤:定义模型参数:首先,你需要定义卷积码的生成矩阵和转移概率。

初始化路径:为每个可能的起始状态初始化一个路径。

递归计算:对于每个时间步,根据转移概率和接收信号,递归地计算每条路径的概率。

选择最佳路径:在每个时间步,选择具有最大概率的路径作为当前状态。

生成输出:根据最佳路径,生成输出序列。

终止条件:当达到终止状态或达到最大迭代次数时,停止计算。

下面是一个简单的MATLAB代码示例,演示了如何实现维特比译码:matlabfunction [decoded, decoded_path] = viterbi_decoder(received, G, num_states, init_state_prob) % received: 接收信号% G: 生成矩阵% num_states: 状态数% init_state_prob: 初始状态概率num_time_steps = length(received);transition_prob = zeros(num_states, num_states); % 转移概率矩阵% 初始化路径和概率矩阵path = zeros(num_time_steps, num_states);path(:, 1) = init_state_prob;path(:, 1) = path(:, 1) .* ones(size(path(:, 1))); % 设置初始路径prob = zeros(num_time_steps, 1); % 概率矩阵prob(1) = path(1,:) .* log2(init_state_prob); % 初始化概率矩阵% 递归计算for t = 2:num_time_stepsfor i = 1:num_statesfor j = 1:num_statestransition_prob(i,j) = G(:,j) * received(t) .* path(t-1,i); % 计算转移概率endend[~, max_state] = max(prob(t-1) + log2(transition_prob)); % 选择最佳状态path(t,:) = zeros(1, num_states); % 重置路径矩阵path(t, max_state) = 1; % 设置当前路径为最佳状态prob(t) = max_state + log2(prob(t-1) + log2(transition_prob)); % 更新概率矩阵end% 选择最佳路径和生成输出[~, max_time] = max(prob); % 选择具有最大概率的时间步作为终止状态decoded = path(:, max_time); % 生成输出序列end请注意,这只是一个基本的示例,可能需要根据您的具体应用和需求进行调整。

维特比译码的仿真与实现

卷积码的码率越高 ,约束长度越大 ,所需维特比 译码的回溯长度也越长 。我们仍然就上面提出的那 个系统进行 Matlab 仿真 ,在回溯深度为 24 ,48 ,96 时分别观察其误码率曲线 (如图 2) 。可以看出回溯 深度对系统误码率的影响没有判决方式那么严重 ,但 是在误码率为 10 - 3时回溯深度为 24 的情况下所需信 噪比比 48 的情况下大约013 dB左右 ,这也是不可忽 略的 。但是回溯深度为 96 或者更长时相对于回溯深

了广泛地应用 。 本文首先使用 Matlab 分析了在无线高斯信道

中 ,对于维特比译码采用硬判决 、2 比特 、3 比特 、4 比特及 5 比特时的系统性能进行分析比较 ,同时也 分析了在回溯深度分别为 24 、48 和 96 时的系统性 能 ,得出结论 :在 3 比特软判决及回溯深度为 48 时 , 系统的性能达到最佳 。基于这些结论 ,用 Q1900 芯 片来实现卷积编码和维特比译码 ,其性能与仿真结 论一致 。

1 引 言

在无线通信系统中 ,为克服数据传输错误 ,需要 进行差错控制编码 。卷积编码是一种很好的纠错编 码方法 。它充分利用了各组之间的相关性 ,增加的 监督元不仅与本组的信息元有关 ,而且与前面若干 组的信息数字发生关系 ,这就是卷积码的基本想法 。 由于每个校验数字与更多的信息数字有关 ,无论从 理论上还是实际上均已证明其性能优于分组码 。与 卷积码相应的维特比译码算法是加性高斯白噪声 (additive white gaussian noise ,AW GN) 信道下卷积 码的最优译码算法 ,在数据通信和卫星通信中得到

第9章 Viterbi译码及其实现

“黑色经典”系列之《DSP嵌入式系统开发典型案例》第9章Viterbi译码及其实现华清远见<ARM开发培训班>培训教材在通信系统中,信息传输的可靠性和有效性是相当重要的。

信息在传输时是经由信道(Channel)传输。

当其在信道传输过程中会受到各种干扰,使得传输信息掺杂各种错误序列在其中。

因此,在通信系统中,良好的纠错码可以有效地应用在信息传输过程中,以降低信息的误码率。

信息在传输时,先由信源发出消息,如语言、图像、文字等,消息进入通信系统后,经由信源编码器编码成信息序列1。

编码过程中,为了使传输有效,还加上一些与传输信息无关的冗余度。

接着信息序列1经过信道编码器编码成信息序列2,序列2是将信息序列1加入了更多的冗余数据(Redundancy Data),以抵抗信道中的各种干扰。

数字信号一般不适合直接在信道上传输,所以调制器是将数字信号转变成模拟信号,使其在信道中传输。

而信道中难免会受到噪声干扰,使信道的输出序列不同于信道的输入序列。

解调器将信道的输出序列由原来的模拟信号转化成数字信号,既是接收序列3,信息序列中因噪声干扰会掺杂一些错误的码元在其中。

信道译码器利用序列中的冗余码元去纠正错误,并且根据信道译码器的结果,产生接近于信息序列1的接收序列1。

整个译码过程是根据信道编码的结果和噪声在信道中的特性所得到的。

理想的结果是所有的错误都被更正回来,即接收序列等同于发送序列。

9.1 Viterbi译码概述在众多的纠错码中,卷积码(Convolutional Code)是一种在实际中得到广泛应用、性能很好的纠错码。

卷积码是不同于分组码的另一种码,它虽然也是把k个信息比特编成n个比特,但k和n都很小,延时小,特别适宜于以串行形式传输信息。

与分组码不同,卷积码中编码后的n个码元不但与当前段的众个信息码元有关,而且与前面(N−1)段的信息有关,编码过程中相互关联的码元为Nn个。

在编码器复杂程度相同的情况下,卷积码的性能优于分组码。

基于Matlab编译码器的仿真与设计

摘要摘要本课程设计主要解决信源编码和信道编码中的卷积码的数字调制,信源输出的模拟信号要转换成数字信号,就需要对信源信道进行编码译码操作,并通过Simulink软件进行设计与仿真,进行误码率分析。

卷积码是一种性能优越的信道编码。

它的编码器和译码器都比较容易实现,同时它具有较强的纠错能力。

随着纠错编码理论研究的不断深入,卷积码的实际应用越来越广泛。

本文简明地介绍了卷积码的编码原理和译码原理。

并在SIMULINK模块设计中,完成了对卷积码的编码和译码以及误比特统计整个过程的模块仿真。

最后,通过在仿真过程中分别改变卷积码的重要参数来加深理解卷积码的这些参数对卷积码的误码性能的影响。

经过仿真和实测,并对测试结果作了分析。

得出了以下三个结论:(1)当改变卷积码的码率时,系统的误码性能也将随之发生变化。

(2)对于码率一定的卷积码,当约束长度N 发生变化时,系统的误码性能也会随之发生变化。

(3)回溯长度也会不同程度上地影响误码性能。

关键词:编译码器;simulink;设计与仿真卷积码;码率ABSTRACTABSTRACTThis course is designed to solve source coding and channel coding convolutional codes in the digital modulation, the source output analog signals into digital signals to be converted to the need for the source and channel coding and decoding operations, and through the Simulink software design and simulation, and the bit error rate analysis. Convolutional code is a superior performance of channel coding. Its encoder and decoder are relatively easy to implement, and it has a strong error correction capability. Error-correcting coding theory research with the deepening of the practical application of convolutional codes more widely. This concise introduction to the principles of convolutional coding and decoding principles. SIMULINK module in the design, completed the coding and decoding convolutional code and bit error statistics of the whole process simulation module. Finally, changes in the simulation process of convolutional codes, respectively, to deepen our understanding of the important parameters of these parameters on convolutional codes convolutional codes error performance. The simulation and measurement, and test results are analyzed. Reached the following three conclusions:(1) When the change rate convolutional code, the system error performance will subsequently change.(2) For a certain rate convolutional codes, when the constraint length N changes, the system BER performance also will be changed.(3) back length will be affected to varying degrees, error performance. Keywords: codec; simulink;design and simulation of convolutional code目录第1章引言 (1)1.1 课题背景 (1)1.2 国内外研究现状 (1)1.3 本课题的意义 (1)1.4 本课题的研究方法 (2)第2章 MATLAB组件介绍及通信系统概述 (3)2.1 MATLAB与通信仿真的发展现状及应用 (3)2.2 通信系统概述与组成 (3)2.3 通信仿真 (4)2.4 Simulink仿真及工作原理 (6)第3章信源编码 (8)3.1 A律μ律编码特性 (8)3.1.1 A律编码 (8)3.1.2 μ律编码 (8)3.1.3 A律13折线 (9)3.2 A律、μ律的特性比较 (11)第4章信道编码及译码 (15)4.1 卷积码的概念介绍 (15)4.2 卷积码的编码过程介绍 (15)4.3 卷积码译码过程的概述 (16)4.4 卷积码的最大似然译码 (19)4.5 输入与同步单元 (21)第5章卷积码的仿真 (22)5.1 Simulink仿真模块的参数设置以及重要参数的意义 (22)5.2 简化维特比译码器的仿真 (26)第6章卷积码译码器的误码率分析 (28)6.1信噪比与误码率的关系 (28)6.2.不同回溯长度对卷积码性能的影响 (29)6.3 不同码率对卷积码误码性能的响 (31)6.4 不同约束长度对卷积码的误码性能影响 (32)第7章结论 (35)参考文献 (36)致谢 (37)第1章引言第1章引言1.1 课题背景随着现代通信的发展,高速信息传输和高可靠性传输成为信息传输的两个主要方面,而可靠性尤其重要。

通信系统中Viterbi译码的Matlab仿真与实现

通信系统中Viterbi译码的Matlab仿真与实现门兰宁;葛持恒【期刊名称】《电子科技》【年(卷),期】2012(025)003【摘要】数字通信作为一种前向纠错编码技术卷积码起着重要的作用。

相应地,信息接收端对卷积码的译码实现也提出了更高的要求。

文中提出的卷积码译码Matlab仿真方案,旨在用Viterbi译码实现对卷积码译码的功能。

仿真结果表明,维特比是一种良好的译码方式。

%The digital communication system plays an important role as a forward error correction technology convolutional code.And the message receiver has a higher requirement on the decoding of the convolutional code.This article comes up with a simulation scheme of convolutional code's decoding with Matlab,and realizes the convolutional decoding with Viterbi Decoding.The simulation indicates that viterbi decoding is a perfect means for convolutional code's decoding,and it provides a good reference for technical applications.【总页数】3页(P35-37)【作者】门兰宁;葛持恒【作者单位】西安电子科技大学电子工程学院,陕西西安710071;西安电子科技大学电子工程学院,陕西西安710071【正文语种】中文【中图分类】TN919.32【相关文献】1.TETRA数字集群通信系统中Viterbi译码的FPGA设计与实现 [J], 吴菲2.电力线通信系统中卷积码和Viterbi译码的FPGA设计实现 [J], 杨沛3.AMR系统中Viterbi译码的仿真与实现 [J], 王宇翔4.应用于通信系统中的高性能Viterbi译码器实现 [J], 黄昊;秦水介5.应用于LTE通信系统中专用Viterbi译码器实现 [J], 黄昊;因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

BUPT卷积码编码及Viterbi译码班级:07114学号:070422姓名:吴希龙指导老师:彭岳星邮箱:FusionBupt@1. 序言卷积码最早于1955年由Elias 提出,稍后,1957年Wozencraft 提出了一种有效地译码方法即序列译码。

1963年Massey 提出了一种性能稍差但是比较实用的门限译码方法,使得卷积码开始走向实用化。

而后1967年Viterbi 提出了最大似然译码算法,它对存储级数较小的卷积码很容易实现,被称作Viterbi 译码算法,广泛的应用于现代通信中。

2. 卷积码编码及译码原理2.1 卷积码编码原理卷积码是一种性能优越的信道编码,它的编码器和解码器都比较易于实现,同时还具有较强的纠错能力,这使得它的使用越来越广泛。

卷积码一般表示为(n,k,K)的形式,即将k 各信息比特编码为n 个比特的码组,K 为编码约束长度,说明编码过程中相互约束的码段个数。

卷积码编码后的n 各码元不经与当前组的k 个信息比特有关,还与前K-1个输入组的信息比特有关。

编码过程中相互关联的码元有K*n 个。

R=k/n 是编码效率。

编码效率和约束长度是衡量卷积码的两个重要参数。

典型的卷积码一般选n,k 较小,但K 值可取较大(>10),以获得简单而高性能的卷积码。

卷积码的编码描述方式有很多种:冲激响应描述法、生成矩阵描述法、多项式乘积描述法、状态图描述,树图描述,网格图描述等。

2.1.1 卷积码解析表示法卷积码的解析表示发大致可以分为离散卷积法,生成矩阵法,码多项式法。

下面以离散卷积为例进行说明。

卷积码的编码器一般比较简单,为一个具有k 个输入端,n 个输出端,m 级移位寄存器的有限状态有记忆系统。

下图所示为(2,1,7)卷积码的编码器。

若输入序列为u =(u 0u 1u 2u 3……),则对应两个码字序列c ①=(c 0①c 1①c 2①c 3①……)和c ②=(c 0②c 1②c 2②c 3②……)相应的编码方程可写为c ①=u ∗g ①,c ②=u ∗g ②,c=(c ①,c ②)。

“∗” 符号表示卷积运算,g ①,g ②表示编码器的两个冲激响应,即编码器的输出可以由输入序列和编码器的两个冲击响应卷积而得到,故称为卷积码。

这里的冲激响应指:当输入为[1 0 0 0 0 … … ]序列时,所观察到的两个输出序列值。

由于上图K 值为7,故冲激响应至多可持续到第7位,可写为g ①=[1 1 1 1 0 0 1],g ②=[1 0 1 1 0 1 1]然后将两个输出端的码字序列合并为一个码字序列为c =(c 0①c 0②c 1①c 1②c 2①c 2②……)若输入信息序列为[1 1 0 1]; 则c ①=[1 0 0 1 0 1 0 1 0 1],c ②=[1 1 1 1 1 0 1 1 1 1]c =[1 1 0 1 0 1 1 1 0 1 1 0 0 1 1 1 0 1 1 1]。

下图所示为(2,1,3)卷积码的编码器,也是本次课程设计所研究的卷积码编码器,由于其生成冲激响应分别为[1 1 1]和[1 0 1],故被称为(7,5)码。

2.1.2 卷积码图形表示法除了用解析法描述卷积码的编码外,还可以使用比较形象的图形法来表示卷积码。

比较常用的有状态图法,网格图法和树图法。

下面简介状态图法和网格图法。

状态图法:由于卷积码编码器在下一时刻的输出取决于编码器的当前状态和下一时刻的输入,而编码器当前状态取决于编码器当前各移位寄存器的存储内容。

称编码器当前各移位寄存器存储内容(0或)为编码器在该时刻的状态(此状态代表记忆以前的输入信息)。

随着信息序列的不断输入,编码器不断从一个状态转移到另外一个状态,并且输出相应的编码序列。

编码器的总可能状态数为2mk 个。

对(7,5)码的编码器来说,n=2,k=1,K=3,m=2。

共有四个可能状态,其状态图如下:图中四个方块表示状态,状态间的连线与箭头表示转移方向,连线上的数字表示是状态发生转移的到来比特,斜杠后的数字由一个状态到另一个状态转移时的输出码字。

如当前状态为11,输入信息为0,则转移到01状态并输出01码字,若输入信息为1,则依然为11状态并输出10码字。

网格图法:网格图可以描述卷积码的状态随时间推移而转移的情况。

该图纵坐标表示所有状态,横坐标表示时间。

网格图在卷积码的概率译码,特别是Viterbi译码中非常重要,它综合了状态图法直观简单和树图法时序关系清晰的特点。

如下图图中实线表示输入0时所走分支,虚线表示输入1时所走分支,编码时只需从起始状态开始依次选择路线并读出输出即可。

假设从a状态开始,输入为[1 0 1 1],则可由图中读出输出为[11 10 10 01]。

2.2 卷积码译码原理卷积码的译码方式主要有三种:1).1963年Massey提出的门限译码,这是一种基于码代数结构的代数译码,类似于分组码中的大数逻辑译码。

2).1963年有Fano改进的序列译码,这是基于码的树状图结构的一种准最佳概率译码。

3).1967年Viterbi提出的Viterbi算法,基于码的网格图基础上的最大似然译码算法,是一种最佳概率译码。

其中,代数译码,利用编码本身的代数结构进行译码,不考虑信道本身的统计特性。

该方法的硬件实现简单,但性能较差,其中具有典型意义的是门限译码。

另一类是概率译码,这种译码通常建立在最大似然准则的基础上。

由于计算是用到了信道的统计特性.因而提高了译码性能,但这种性能的提高是以增加硬件的复杂度为代价的。

常用的概率译码方法有维特比译码和序列译码。

维特比译码具有最佳性能,但硬件实现复杂;门限译码性能最差,但硬件简单;序列译码在性能和硬件方面介于维特比译码和门限译码之间。

2.2.1 Viterbi译码卷积码概率译码的基本思路是:以接收码流为基础,逐个计算它与其他所有可能出现的、连续的网格图路径的距离,选出其中可能性最大的一条作为译码估值输出。

概率最大在大多数场合可解释为距离最小,这种最小距离译码体现的正是最大似然的准则。

卷积码的最大似然译码与分组码的最大似然译码在原理上是一样的,但实现方法上略有不同。

主要区别在于:分组码是孤立地求解单个码组的相似度,而卷积码是求码字序列之间的相似度。

基于网格图搜索的译码是实现最大似然判决的重要方法和途径。

用格图描述时,由于路径的汇聚消除了树状图中的多余度,译码过程中只需考虑整个路径集合中那些使似然函数最大的路径。

如果在某一点上发现某条路径已不可能获得最大对数似然函数,就放弃这条路径,然后在剩下的“幸存”路径中重新选择路径。

这样一直进行到最后第L级(L为发送序列的长度)。

由于这种方法较早地丢弃了那些不可能的路径,从而减轻了译码的工作量,Viterbi译码正是基于这种想法。

对于(n, k, K )卷积码,其网格图中共2kL种状态。

由网格图的前K-1条连续支路构成的路径互不相交,即最初2k_1条路径各不相同,当接收到第K条支路时,每条路径都有2条支路延伸到第K级上,而第K级上的每两条支路又都汇聚在一个节点上。

在Viterbi 译码算法中,把汇聚在每个节点上的两条路径的对数似然函数累加值进行比较,然后把具有较大对数似然函数累加值的路径保存下来,而丢弃另一条路径,经挑选后第K级只留下2K 条幸存路径。

选出的路径同它们的对数似然函数的累加值将一起被存储起来。

由于每个节点引出两条支路,因此以后各级中路径的延伸都增大一倍,但比较它们的似然函数累加值后,丢弃一半,结果留存下来的路径总数保持常数。

由此可见,上述译码过程中的基本操作是,“加-比-选”,即每级求出对数似然函数的累加值,然后两两比较后作出选择。

有时会出现两条路径的对数似然函数累加值相等的情形,在这种情况下可以任意选择其中一条作为“幸存”路径。

卷积码的编码器从全零状态出发,最后又回到全零状态时所输出的码序列,称为结尾卷积码。

因此,当序列发送完毕后,要在网格图的终结处加上(K-1)个己知的信息作为结束信息。

在结束信息到来时,由于每一状态中只有与已知发送信息相符的那条支路被延伸,因而在每级比较后,幸存路径减少一半。

因此,在接收到(K-1)个己知信息后,在整个网格图中就只有唯一的一条幸存路径保留下来,这就是译码所得的路径。

也就是说,在己知接收到的序列的情况下,这条译码路径和发送序列是最相似的。

3.MATLAB仿真在本次课程设计中,我们对整个通信过程进行了仿真,其过程如下:下面将分别对每一部分进行仿真3.1卷积码编码仿真在程序设计中,我们没有采用MATLAB自带的编码函数而是采用了自己的编码函数codec,其参数m为输入信息序列,g1,g2为两个输出端口的冲激响应序列。

function cod=codec(m,g1,g2)%g1,g2为两输出端口的冲激响应序列。

m1=conv(m,g1);m2=conv(m,g2);l=length(m1);for i=1:l;cod([2*i-1])=rem(m1([i]),2);cod([2*i])=rem(m2([i]),2);end下为试运行编码结果,g1=[1 1 1],g2=[1 0 1]。

clear allg1=[1 1 1];g2=[1 0 1];msg=[1 1 0 1];cod=codec(msg,g1,g2)输出为:cod =110101001011符合预期结果。

3.2信道传输过程仿真为了方便起见,我们采用了BPSK调制,为了了解整个通信系统,我们对BPSK的调制过程作了研究,用一个简短的程序对BPSK的全过程进行了观察。

function [bpsk_output]=bpsk_1(bpsk_input);%g=[1 0 1 1 1 0 0 1];基带信号g=bpsk_input;f=100; %载波频率t=0:2*pi/99:2*pi;cp=[];sp=[];mod=[];mod1=[];bit=[];for n=1:length(g);if g(n)==0;die=-ones(1,100); %Modulantese=ones(1,100); %endc=sin(f*t);cp=[cp die];mod=[mod c];bit=[bit se];endbpsk=cp.*mod;subplot(2,1,1);plot(bit,'LineWidth',1.5);grid on ;title('Binary Signal');axis([0 100*length(g) -2.5 2.5]);bpsk_output=bpsk;subplot(2,1,2);plot(bpsk,'LineWidth',1.5);grid on ;title('BPSK modulation');axis([0 100*length(g) -2.5 2.5]);观察到如下波形上图很好的符合了BPSK 的调制特性。