Z-Turn Board U-Boot启动流程 zynq

zynq的启动方式

Zynq-7000AP SOC器件有效利用了片上CPU来帮忙配置。

在没有外部JTAG的情况下,处理系统(PS)与可编程逻辑(PL)都必须依靠PS来完成芯片的初始化配置。

ZYNQ的两种启动模式:从BootROM主动启动,从JTAG被动启动。

ZYNQ的启动配置分多级进行的。

配置至少需要两步,但通常按如下三个阶段进行:阶段0:该阶段简称为BootROM,控制着整个芯片的初始化过程。

放在BootROM中的代码是固化的,不可修改的,处理器核在上电或者热启动时自动执行这部分代码。

阶段1:该阶段的启动加载器(FSBL)也可以由用户代码控制。

阶段2:这阶段通常可以是用户的PS端的设计代码,当然也可以是第二阶段的启动加载器(SSBL),这个阶段可以完全由用户控制,是可选的。

ZYNQ外部启动条件:1、电源要求:在阶段0 BootROM状态时,PS与PL的电源要求如表所示:在阶段1 FSBL时,PS与PL都是必须上电的,因为PL将在这个阶段进行配置,而PS将负责配置的过程。

2、时钟要求:必须满足时钟3、复位要求:主要有两个外部复位源将影响BootROM的执行。

(电源复位信号,系统复位信号)4、启动引脚设置:需要配置好引脚才能正确启动平台。

BootROM1、BootROM的作用:上电复位以后,PS端即开始进行配置。

在不使用JTAG的情况下,ARM将在片上的BootROM中开始执行代码。

BootROM中的代码对NAND、NOR、Quad-SPI、SD与PCAP的基本外设控制器进行初始化,使得ARM核可以访问、使用这些外设。

而DDR等其他外设将在阶段1或者之后进行初始化。

BootROM中的代码还负责加载阶段1的启动镜像。

PS的启动源是由外部模式引脚的高低电平来选择的,也就是指BootROM将根据外部配置引脚的设置来从不同的外部存储中加载阶段1的启动镜像,当然也支持在线性Flash 上直接运行。

需要注意的是PL的配置并不在BootROM中完成,BootROM只为配置PL做好准备。

u-boot简单使用手册

u-boot简单使⽤⼿册(转⾃)1.u-boot 简介-----------------------------------------------------------------1.u-boot2.它有两种模式引导模式(⽤于引导OS)下载模式(⽤于开发,在u-boot启动按任意键)进⼊控制台。

在控制台执⾏ boot 命令,则进⼊引导模式去引导OS。

2.u-boot 控制台常⽤命令--------------------------------------------------------------------help 显⽰帮助命令boot ⽤引导常数来引导OS。

bootm 从内存引导OS。

.bootp/tftpboot 从TFTP/BOOTP引导OSgo 从某⼀个地址开始直接运⾏程序mtdparts 管理flash上的分区ping 简单发送⼀个ICMP包测试。

printenv 打印环境变量setenv 设置环境变量saveenv 把内存的环境变量存到flash上的param分区.usbslave 从USB下载⽂件 (PC机要运⾏dnw)version 显⽰u-boot 版本4. 设置环境变量printenv 打印环境变量bootargs=noinitrd root=/dev/mtdblock2 init=/linuxrc console=ttySAC0bootcmd=nboot 0x32000000 kernel; bootm 0x32000000bootdelay=0baudrate=115200ethaddr=0a:1b:2c:3d:4e:5fipaddr=192.168.1.6serverip=192.168.1.8netmask=255.255.255.0stdin=serialstdout=serialstderr=serialmtdids=nand0=nandflash0mtdparts=mtdparts=nandflash0:256k@0(bios),128k(params),128k(toc),512k(eboot),1024k(log)partition=nand0,0mtddevnum=0mtddevname=biosEnvironment size: 453/131068 bytes经常修改是 bootargs ( 启动参数)ipaddr (开发板IP地址)serverip( 默认tftp/NFS/...下载主机)setenv 命令只是改变内存的环境变量值,如果不调⽤saveenv,下次的设置仍然是旧的配置。

ZYNQ ZC702 之UDP组播实现

Hale Waihona Puke 选择 Finish。 3、主要函数 (1)、main.c /*****

11

main.c * 功能: LWIP UDP 组播 * 状态: PC 端多客户端 和多服务器端 均测试成功 * 时间: 2017‐11‐11 * 作者: 李俊辉 * ******/

#include <stdio.h> #include "xparameters.h" #include "netif/xadapter.h" #include "platform.h" #include "platform_config.h" #if defined (__arm__) || defined(__aarch64__)

13

int start_application(); int transfer_data(); /* missing declaration in lwIP */ void lwip_init(); #if LWIP_DHCP==1 extern volatile int dhcp_timoutcntr; err_t dhcp_start(struct netif *netif); #endif extern volatile int TcpFastTmrFlag; extern volatile int TcpSlowTmrFlag; extern volatile int udp_Flag; volatile int udp_revflag = 0; static struct netif server_netif;

if (ERR_OK != err) {

printf("LWIP_IGMP err = %d \n", err); return ; } #endif g_udppcb = (struct udp_pcb*)udp_new(); udp_bind(g_udppcb,IP_ADDR_ANY, UDP_MULTICAST_LOCAL_PORT );

Z-turnBoardXC7Z010XC7Z020用户指导文档

Z-turnBoardXC7Z010XC7Z020用户指导文档Z-turn Board 产品用户手册版本V1.12014年12月16日版本记录目录目录 (1)第1章产品概述 (1)1.1 产品简介 (1)1.2 产品预览 (1)第2章SoC介绍 (2)2.1 SoC特性 (2)2.1 SoC BANK (3)第3章硬件资源介绍 (5) 3.1 开发板硬件资源 (5) 第4章接口说明 (7)4.1 板上接口说明 (7)3.1.1 用户接口 (7)4.2 扩展接口定义 (8)第5章硬件说明 (11) 5.1 电源 (11)5.2 引导模式 (11)5.3 DDR (11)5.4 存储 (12)5.4.1 NAND Flash (12) 5.4.2 SPI Flash (12)5.4.3 Micro SD卡 (13) 5.5 USB (13)5.5.1 USB OTG (13) 5.5.2 USB调试串口 (14) 5.6 以太网 (14)5.7 自定义逻辑外设 (15) 5.7.1 GPIO (15)5.7.2 I2C (16)5.7.3 HDMI (16)第6章软件资源介绍 (17) 6.1 Linux软件资源 (17)6.2 编程逻辑资源 (18)第7章快速使用指南 (19)7.1 烧写固件到开发板 (19)7.2 启动开发板 (19)第6章机械参数 (21)附录一售后服务与技术支持 (22)第1章产品概述1.1 产品简介Z-turn Board是深圳市米尔科技有限公司推出的一款以Xilinx Zynq-7010(兼容7020)作为主处理器的嵌入式开发板。

Z-turn Board采用Xilinx最新的基于28nm工艺流程的Zynq-7000 All Programmable SoC平台,将ARM处理器和FPGA架构紧密集成。

该产品拥有双核ARM Cortex-A9 MPCore的高性能,低功耗特性,在设计中能更好的满足各种工业需要。

ZYNQ7000开发平台用户手册说明书

文档版本控制目录文档版本控制 (2)一、开发板简介 (6)二、AC7Z020核心板 (8)(一)简介 (8)(二)ZYNQ芯片 (9)(三)DDR3 DRAM (11)(四)QSPI Flash (14)(五)时钟配置 (16)(六)电源 (17)(七)结构图 (18)(八)连接器管脚定义 (19)三、扩展板 (23)(一)简介 (23)(二)CAN通信接口 (24)(三)485通信接口 (24)(四)千兆以太网接口 (25)(五)USB2.0 Host接口 (27)(六)USB转串口 (28)(七)AD输入接口 (29)(八)HDMI输出接口 (30)(九)MIPI摄像头接口(仅AX7Z020使用) (32)(十)SD卡槽 (33)(十一)EEPROM (34)(十二)实时时钟 (34)(十三)温度传感器 (35)(十四)JTAG接口 (36)(十五)用户LED灯 (36)(十六)用户按键 (37)(十七)扩展口 (38)(十八)供电电源 (40)(十九)底板结构图 (41)芯驿电子科技(上海)有限公司 基于XILINX ZYNQ7000开发平台的开发板(型号: AX7Z020B )2022款正式发布了,为了让您对此开发平台可以快速了解,我们编写了此用户手册。

这款ZYNQ7000 FPGA 开发平台采用核心板加扩展板的模式,方便用户对核心板的二次开发利用。

核心板使用XILINX 的Zynq7000 SOC 芯片的解决方案,它采用ARM+FPGA SOC 技术将双核ARM Cortex-A9 和FPGA 可编程逻辑集成在一颗芯片上。

另外核心板上含有2片共512MB 高速DDR3 SDRAM 芯片和1片256Mb 的QSPI FLASH 芯片。

在底板设计上我们为用户扩展了丰富的外围接口,比如2路CAN 通信接口,2路485通信接口,2路XADC 输入接口, 1路千兆以太网接口,1路USB2.0 HOST 接口,1路HDMI输出接口,Uart 通信接口,SD 卡座,40针扩展接口等等。

uboot启动流程分析

uboot启动流程分析Uboot启动流程分析。

Uboot是一种常用的嵌入式系统启动加载程序,它的启动流程对于嵌入式系统的正常运行至关重要。

本文将对Uboot启动流程进行分析,以便更好地理解其工作原理。

首先,Uboot的启动流程可以分为以下几个步骤,Reset、初始化、设备初始化、加载内核。

接下来我们将逐一进行详细的分析。

Reset阶段是整个启动流程的起点,当系统上电或者复位时,CPU会跳转到Uboot的入口地址开始执行。

在这个阶段,Uboot会进行一些基本的硬件初始化工作,包括设置栈指针、初始化CPU寄存器等。

接着是初始化阶段,Uboot会进行一系列的初始化工作,包括初始化串口、初始化内存控制器、初始化时钟等。

这些初始化工作是为了确保系统能够正常地运行,并为后续的工作做好准备。

设备初始化阶段是Uboot启动流程中的一个重要环节,它包括对外设的初始化和检测。

在这个阶段,Uboot会初始化各种外设,如网卡、存储设备等,并对其进行检测,以确保它们能够正常工作。

最后一个阶段是加载内核,Uboot会从存储设备中加载操作系统的内核镜像到内存中,并跳转到内核的入口地址开始执行。

在这个过程中,Uboot会进行一些必要的设置,如传递启动参数给内核,并最终将控制权交给内核。

总的来说,Uboot的启动流程是一个非常重要的过程,它涉及到系统的硬件初始化、外设的初始化和内核的加载等工作。

只有当这些工作都顺利完成时,系统才能够正常地启动运行。

因此,对Uboot启动流程的深入理解对于嵌入式系统的开发和调试具有重要意义。

通过本文对Uboot启动流程的分析,相信读者对Uboot的工作原理有了更清晰的认识。

希望本文能够对大家有所帮助,谢谢阅读!。

zedboard启动流程新

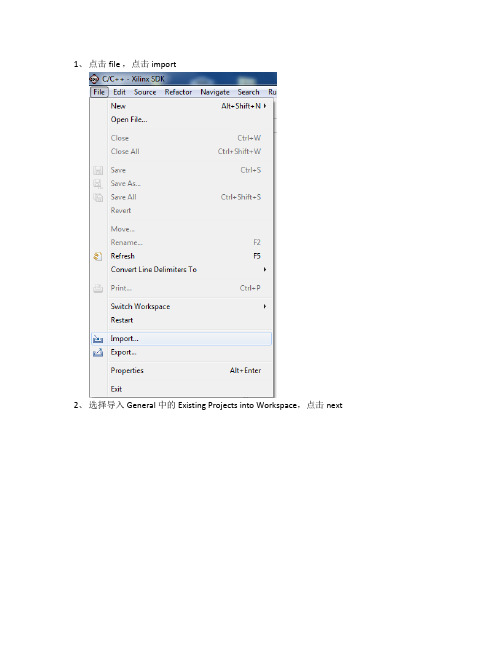

1、点击file ,点击import2、选择导入General 中的Existing Projects into Workspace,点击next3、点击Browse4、选中解压出的NJ-cpu1-src,点击OK5、弹出界面如下图,点击Finish6、在Project Explorer可看到如下界面:7:点击展开app_cpu1,继续点击展开src,双击app_cpu1.c8、此时界面如下:9、点击Xilinx Tools ,点击Creat Zynq Boot Image10、点击browse,选择BIF文件保存位置,取名为zrobot.bif11、一次添加amp_fsbl.elf、system.bit、u-boot.elf、app_cpu1.elf。

前3个文件直接使用提供的,第4个替换成自己编译的文件。

点击add后弹窗如下:12、点击Browse,选中NJ-cpu1-targets中的amp_fsbl.elf,点击Open13、点击OK14、继续点击add,点击Browse,选中NJ-cpu1-targets中的system.bit,点击Open15、点击OK16、继续点击add,点击Browse,选中NJ-cpu1-targets中的u-boot.elf,点击Open17、点击OK18、继续点击add,点击Browse,选中NJ-cpu1-targets中的app_cpu1.elf,点击Open19、点击OK20、create image界面最终如下,可以看到添加的四个文件。

必须按照此顺序修改输出文件名,讲output.bin修改成BOOT.bin21、点击Create Image,Console窗口输出结果如下:下图是SD卡中必要的文件,其中init2.sh是由init.sh文件重命名的。

如果你需要由SD自启动需将此文件修改成init.sh文件名,如果你需要Linux单步调试,则需要将其修改成init2.sh,或者其他名称。

uboot启动流程

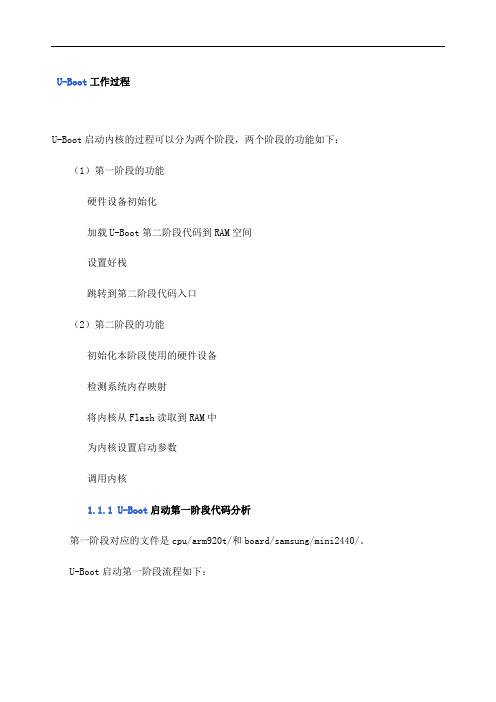

U-Boot工作过程U-Boot启动内核的过程可以分为两个阶段,两个阶段的功能如下:(1)第一阶段的功能硬件设备初始化加载U-Boot第二阶段代码到RAM空间设置好栈跳转到第二阶段代码入口(2)第二阶段的功能初始化本阶段使用的硬件设备检测系统内存映射将内核从Flash读取到RAM中为内核设置启动参数调用内核1.1.1 U-Boot启动第一阶段代码分析第一阶段对应的文件是cpu/arm920t/和board/samsung/mini2440/。

U-Boot启动第一阶段流程如下:图 U-Boot启动第一阶段流程根据cpu/arm920t/中指定的连接方式:ENTRY(_start)SECTIONS{. = 0x00000000;. = ALIGN(4);.text :{cpu/arm920t/ (.text)board/samsung/mini2440/ (.text)board/samsung/mini2440/ (.text)*(.text)}… …}第一个链接的是cpu/arm920t/,因此的入口代码在cpu/arm920t/中,其源代码在cpu/arm920t/中。

下面我们来分析cpu/arm920t/的执行。

1. 硬件设备初始化(1)设置异常向量cpu/arm920t/开头有如下的代码:.globl _start_start: b start_code /* 复位*/ldr pc, _undefined_instruction /*未定义指令向量 */ldr pc, _software_interrupt /* 软件中断向量 */ldr pc, _prefetch_abort /* 预取指令异常向量 */ldr pc, _data_abort /* 数据操作异常向量 */ldr pc, _not_used /* 未使用 */ldr pc, _irq /* irq中断向量 */ldr pc, _fiq /* fiq中断向量 */ /* 中断向量表入口地址 */_undefined_instruction: .word undefined_instruction_software_interrupt: .word software_interrupt_prefetch_abort: .word prefetch_abort_data_abort: .word data_abort_not_used: .word not_used_irq: .word irq_fiq: .word fiq.balignl 16,0xdeadbeef以上代码设置了ARM异常向量表,各个异常向量介绍如下:表 ARM异常向量表在cpu/arm920t/中还有这些异常对应的异常处理程序。

详细解读Zynq的三种启动方式(JTAG,SD,QSPI)

详细解读Zynq的三种启动方式(JTAG,SD,QSPI)本文介绍zynq上三种方式启动文件的生成和注意事项,包括只用片上RAM (OCM)和使用DDR3两种情况。

JTAG方式JTAG方式是调试中最常用的方式,在SDK中在Project Explorer窗口工程上右键-Debug As-Debug ConfiguraTIons可以看到以下窗口首次打开左边窗口中Xilinx C/C++ applicaTIon(GDB)下没有子项,这时双击Xilinx C/C++ applicaTIon(GDB)即可新建一个调试;这时右边窗口会自动填充如上图,若没有则手动填入;在右边ApplicaTIon窗口指定要下载调试的.elf文件;在右边STDIO Connection可以指定标准输入输出串口,即printf打印串口,若这里选择开发板上uart的com口,则调试时printf的信息打印到调试时Console窗口,同时也可从Console窗口输入数据,以此将数据通过串口发送到开发板上以上设置完成后点击Debug即可开始调试;若以上在Project Explorer窗口工程上右键-Run As-Run Configurations;配置与此类似,最后点击run即可开始运行,只是不是调试而是直接上板运行。

只用OCM只用OCM指不使用DDR3的方式,与使用DDR3的方式略有不同。

这里不用FSBL来加载PL部分的.bit文件和第二阶段启动程序(裸机程序),而直接用BootROM加载裸机程序到OCM,即将裸机程序当做FSBL来运行,当然还要以下处理才可以:包含进头文件:#include ps7_init.h在裸机程序main函数开始处调用:ps7_init()从design_1_wrapper_hw_platform_1目录复制ps7_init.c和ps7_init.h文件到裸机程序所在的src目录中注意:这里样调用ps7_init()只适用于只用OCM的情况,经测试打开DDR3后再这样调用会在ps7_init()中初始化失败,调试发现在初始化PLL时失败(原因未知)。

uboot 代码运行流程

uboot 代码运行流程U-Boot代码运行流程U-Boot(Universal Bootloader)是一个开源的引导加载程序,广泛应用于嵌入式系统中。

它负责在系统上电后初始化硬件并加载操作系统内核,是系统启动的重要一环。

下面将从U-Boot代码的运行流程方面进行介绍。

1. 启动阶段当系统上电后,处理器会从预定义的存储器地址开始运行代码。

U-Boot的启动代码通常存放在ROM中,处理器会从ROM的起始地址开始执行。

启动代码负责初始化处理器和一些外设,然后跳转到U-Boot的入口点。

2. 入口点U-Boot的入口点是指U-Boot的main()函数。

在启动代码的最后,会调用main()函数,从而进入U-Boot的主循环。

U-Boot的主循环负责处理用户输入的命令,并根据命令执行相应的操作。

3. 硬件初始化在main()函数中,首先会进行硬件的初始化工作。

这包括初始化串口、初始化存储器控制器、初始化网络接口等。

硬件初始化的目的是为了确保系统能够正常运行,并为后续的操作做好准备。

4. 系统启动硬件初始化完成后,U-Boot会尝试从存储设备(如闪存、SD卡)中加载操作系统内核镜像。

U-Boot会根据预定义的启动命令(例如bootcmd)来确定从哪个设备加载内核镜像,并执行相应的加载操作。

加载完成后,U-Boot会将控制权交给操作系统内核,进入操作系统的启动阶段。

5. 用户交互一般情况下,U-Boot会在系统启动后进入命令行界面,等待用户输入命令。

用户可以通过串口、网络等方式与U-Boot进行交互,执行各种操作,例如烧写固件、修改配置等。

U-Boot提供了丰富的命令集,可以满足不同的需求。

6. 系统重启当用户输入重启命令或系统发生异常时,U-Boot会执行系统重启操作。

重启操作包括重新初始化硬件、重新加载内核镜像等步骤,以重新启动系统。

U-Boot会将控制权交给重新加载的内核,然后进入内核的启动流程。

总结:U-Boot代码的运行流程包括启动阶段、入口点、硬件初始化、系统启动、用户交互和系统重启等几个关键步骤。

bootloader启动过程详细说明

bootloader启动过程详细说明今天早上看了⼀上午的bootloader简单源码,终于捋顺了bootloader的执⾏过程,之前只是知道bootloader代码会先被irom中的代码拷贝到iram中⼀部分,然后执⾏这部分代码,会把整个bootloader代码拷贝到sdram中,最终在sdram执⾏剩下的代码,⽽这段代码会把kernel拷贝到sdram的某个地址,最终引导起来整个内核。

但是我今天早上看代码的时候看到⼀个问题,我所有的代码都是⾃⼰动⼿实现的,只要⼀步⼀步按照顺序来,不就可以实现么?为什么还要拷贝来拷贝去的。

感觉直接按照跳转的⽅式,跳转值进⾏指令的跳转就⾏,但是想过之后,我意识到⾃⼰真是⽆知了。

⽐如说在irom中执⾏的时候,会有⼀次跳转到iram中某⼀个地址,当然pc是肯定可以直接跳转到指定的任何⼀个地址,但是在这个地址中没有存放指令码,这时候,肯定是⼀个有去⽆回的过程,不仅这样,这个pc跳到这⾥后,就会很迷茫,前不着村,后不着店的,不知道⾃⼰的所去所从,就会死到这⾥。

只有先把代码拷贝到将要跳转的地址中,pc指针才会顺着跳转后的指令继续执⾏,也就是说每⼀个指令都要负责⼈,确保执⾏完这个指令后,⼀定要有另⼀个指令去接纳pc。

这样pc才会⼀直活在我的代码中。

下边我就再把我更进⼀步了解到的bootloader执⾏过程再重新叙述⼀下:我使⽤的是s5pv210芯⽚、K9K8G08U0A型号的nand flash第⼀步:cpu启动起来后,先来到0x00000000这个地址处(也就是irom的地址),此时会看到有⼀段代码(这是irom中固定的代码)在这⾥,这段代码会找到bootloader的第⼀段代码(以下就称为BL1)存放的地址,由于BL1存放在nand flash中,不⽀持⽚上执⾏,所以irom会把这段代码拷贝到iram中,但是在拷贝之前,irom会先把iram的起始4个地址分别写上⼀定的内容(不过通常只写0x00地址为BL1所占空间的⼤⼩(⼀般是8k),⽽其他三个地址全写为0),把BL1这段代码拷贝到iram后,irom的使命就快要完成了,irom的最后⼀个任务就是把pc指针指向放BL1的那块地址的起始位置,然后就按照这个地址的指令开始执⾏。

[uboot](第五章)uboot流程——uboot启动流程

uboot流程——uboot启动流程](https://img.taocdn.com/s3/m/3e1805d6d05abe23482fb4daa58da0116c171ff6.png)

[uboot](第五章)uboot流程——uboot启动流程/ooonebook/article/details/53070065以下例⼦都以project X项⽬tiny210(s5pv210平台,armv7)为例[uboot] uboot流程系列:建议先看《[project X] tiny210(s5pv210)上电启动流程(BL0-BL2)》,根据例⼦了解⼀下上电之后的BL0\BL1\BL2阶段,以及各个阶段的运⾏位置,功能。

建议可以和《[uboot] (番外篇)global_data介绍》和《[uboot] (番外篇)uboot relocation介绍》结合起来看。

=================================================================================⼀、uboot说明1、uboot要做的事情CPU初始刚上电的状态。

需要⼩⼼的设置好很多状态,包括cpu状态、中断状态、MMU状态等等。

其次,就是要根据硬件资源进⾏板级的初始化,代码重定向等等。

最后,就是进⼊命令⾏状态,等待处理命令。

在armv7架构的uboot,主要需要做如下事情arch级的初始化关闭中断,设置svc模式禁⽤MMU、TLB关键寄存器的设置,包括时钟、看门狗的寄存器板级的初始化堆栈环境的设置代码重定向之前的板级初始化,包括串⼝、定时器、环境变量、I2C\SPI等等的初始化进⾏代码重定向代码重定向之后的板级初始化,包括板级代码中定义的初始化操作、emmc、nand flash、⽹络、中断等等的初始化。

进⼊命令⾏状态,等待终端输⼊命令以及对命令进⾏处理上述⼯作,也就是uboot流程的核⼼。

2、疑问在前⾯的⽂章中虽然已经说明了,在spl的阶段中已经对arch级进⾏了初始化了,为什么uboot⾥⾯还要对arch再初始化⼀遍?回答:spl对于启动uboot来说并不是必须的,在某些情况下,上电之后uboot可能在ROM上或者flash上开始执⾏⽽并没有使⽤spl。

从SD卡启动ZYNQ(裸机)

从SD卡启动ZYNQ(裸机)从SD卡中启动ZYNQ7020中的linux系统(裸机)看了⼀整的⽂档,就为了从SD卡中启动ZYNQ中的系统,⽹上的资料⼤同⼩异,主要还是⽣成BOOT.bin⽂件(现在先是进⾏裸机的运⾏)。

这个⽂档打算从以下⼏个⽅⾯进⾏说明:⼀、现在将⽹上的⽣成的BOOT.bin⽂件的流程做⼀个总结(或者说是copy过来)⾸先讲⼀下BOOT.bin⽂件的构成:BOOT.bin⽂件=PL部分.bit+FSBL.elf+PS部分.elf⽂件。

(design.bit⽂件就是⽣成的⽐特流⽂件;FSBL.elf⽂件是在Vivado的SDK中⽣成的,下⾯有这部分的介绍;⼯程的.elf⽂件就是在SDK中运⾏程序时建⽴的⽂件)由于上⾯⽤到了FSBL.elf⽂件,所以这⾥要讲解⼀下如何⽣成FSBL.elf⽂件。

打开SDK软件,在菜单栏中依次选择“File——New——Application Project”,出现下⾯的界⾯:,并写⼊FSBL,在Hardware Platform中选择如何圈中的选项(很重要)!再在点击Next,出现如下界⾯,选择zynq FSBL,点击finish,等待编译(⾃动编译)完成即可。

⾄此,FSBL.elf⽂件就已经⽣成完毕了。

将三个⽂件拷贝到⼀个独⽴的⽂件下⾯,为制作BOOT.bin做准备⼯作。

现在制作BOOT.bin所需的⽂件都已经准备完毕了,接下来就来讲解如何利⽤SDK软件来⽣成BOOT.bin⽂件。

步骤如下:依次执⾏xilinx tools---creat biit image,之后出现如下界⾯:在output BIF file path中选择⽣成⽂件的⽬录(这个⽬录可以任意)。

第⼆步,点击add将三个⽂件添加进来。

点击add之后出现如下界⾯,需要注意两点:第⼀点是:三个⽂件的添加顺序必须是FSBL.elf、PL部分.bit、PS部分.elf。

第⼆点是:在添加三个⽂件时FSBL.elf⽂件在下图中的Partitiontype选择bootloader,其余两个⽂件选择datafile。

z-turn开发笔记

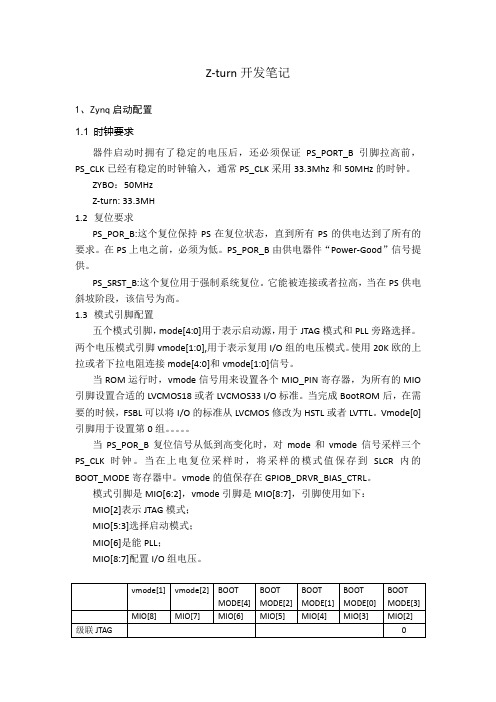

Z-turn开发笔记1、Zynq启动配置1.1 时钟要求器件启动时拥有了稳定的电压后,还必须保证PS_PORT_B引脚拉高前,PS_CLK已经有稳定的时钟输入,通常PS_CLK采用33.3Mhz和50MHz的时钟。

ZYBO:50MHzZ-turn: 33.3MH1.2复位要求PS_POR_B:这个复位保持PS在复位状态,直到所有PS的供电达到了所有的要求。

在PS上电之前,必须为低。

PS_POR_B由供电器件“Power-Good”信号提供。

PS_SRST_B:这个复位用于强制系统复位。

它能被连接或者拉高,当在PS供电斜坡阶段,该信号为高。

1.3模式引脚配置五个模式引脚,mode[4:0]用于表示启动源,用于JTAG模式和PLL旁路选择。

两个电压模式引脚vmode[1:0],用于表示复用I/O组的电压模式。

使用20K欧的上拉或者下拉电阻连接mode[4:0]和vmode[1:0]信号。

当ROM运行时,vmode信号用来设置各个MIO_PIN寄存器,为所有的MIO 引脚设置合适的LVCMOS18或者LVCMOS33 I/O标准。

当完成BootROM后,在需要的时候,FSBL可以将I/O的标准从LVCMOS修改为HSTL或者LVTTL。

Vmode[0]引脚用于设置第0组。

当PS_POR_B复位信号从低到高变化时,对mode和vmode信号采样三个PS_CLK时钟。

当在上电复位采样时,将采样的模式值保存到SLCR内的BOOT_MODE寄存器中。

vmode的值保存在GPIOB_DRVR_BIAS_CTRL。

模式引脚是MIO[6:2],vmode引脚是MIO[8:7],引脚使用如下:MIO[2]表示JTAG模式;MIO[5:3]选择启动模式;MIO[6]是能PLL;MIO[8:7]配置I/O组电压。

Boot Interface OptionsThe PS supports boot from Quad-SPI, NAND, and NOR devices. Boot devices do not impact system level dynamic power as the boot process only occurs once at device power up. Lower voltage 1.8V devices are of lower static power than higher 3.3V devices.启动选择:1.8V启动优于3.3V启动。

uboot启动流程

uboot启动流程U-Boot是一款开源的嵌入式引导加载程序(bootloader),主要用于嵌入式系统的引导启动。

它是一个跨平台的引导加载程序,可以在不同的处理器架构和操作系统上运行。

下面将介绍U-Boot的启动流程。

U-Boot启动流程主要包括三个阶段:启动ROM代码、启动SPL(Secondary Program Loader)和启动U-Boot。

首先,当嵌入式设备上电后,处理器会首先执行固定在芯片内部的启动ROM代码。

这些代码主要完成一些基本的硬件初始化工作,例如设置栈指针、初始化外设等。

然后,启动ROM 代码会从预定义的启动设备(例如闪存、SD卡等)中加载SPL。

接下来,SPL(Secondary Program Loader)被加载到内存中执行。

SPL是一个较小的引导加载程序,主要作用是完成一些必要的初始化和硬件配置。

SPL会初始化内存控制器、外设等,并加载U-Boot镜像到内存中。

最后,U-Boot被加载到内存中执行。

U-Boot是一个功能强大的引导加载程序,拥有丰富的命令和功能。

它可以根据不同的系统配置进行配置和扩展,并提供了丰富的调试和测试功能。

U-Boot的启动流程主要可以分为以下几个步骤:1. CPU初始化:U-Boot开始执行后,首先进行CPU的初始化工作,包括设置栈指针、cache的初始化等。

2. 设备初始化:接下来,U-Boot会初始化外设设备,例如串口、网络接口等。

这些设备的初始化是为了后续的调试和配置工作做准备。

3. 系统环境的初始化:U-Boot会读取存储在非易失性存储设备(例如NAND闪存、SD卡等)中的环境变量,根据这些变量进行系统的初始化配置。

4. 设备驱动的加载:U-Boot会加载并初始化必要的设备驱动程序,以便后续的硬件操作可以正常进行。

5. 启动命令的执行:U-Boot会根据配置文件中的设置,执行预定义的启动命令。

这些命令可以是启动操作系统、加载应用程序等。

uboot学习之uboot启动流程简述

uboot学习之uboot启动流程简述⼀、uboot启动分为了三个阶段BL0、BL1、BL2;BL0表⽰上电后运⾏ROM中固化的⼀段程序,其中ROM中的程序是⼚家写进去的,所以具体功能可能根据⼚家芯⽚⽽有所不同。

功能如下:1. 初始化系统时钟、特殊设备的控制器、启动设备、看门狗、堆栈、SRAM等硬件;2. 验证B1镜像,并且加载BL1镜像到SRAM中,然后跳转到BL1镜像的地址上。

BL0需要将BL1加载到对应的RAM上,这就涉及到它的启动模式,详细如下:1.OneNand Boot模式要了解OneNAND先得了解NOR Flash和NAND Flash。

与NOR Flash相⽐,NAND Flash的读数据速度稍慢,但是擦写速度快得多,并且在容量、使⽤寿命、成本上也占有较⼤优势。

NOR Flash的编程简单,⽽NAND Flash的编程较为复杂(因为它的flash管理需要特殊的接⼝)。

NAND Flash⼀般⽤于存储数据,⽽NOR Flash⼀般⽤于存储启动代码。

NOR Flash带有SRAM接⼝,有⾜够的地址引脚来寻址,可以很容易地存取其内容的每⼀字节(有限的地址引脚是限制其容量的因素之⼀)。

NAND Flash使⽤复杂的I/O⼝来串⾏地存取数据,各个产品或⼚商的⽅法可能各不相同。

为了弥补NAND Flash的不⾜,三星公司在NAND Flash芯⽚内集成了⼀个RAM接⼝,命名为OneNAND Flash,这类Flash拥有与NOR Flash相同的简单接⼝,⽽且不受地址引脚的限制,即容量与地址引脚⽆关。

其实OneNAND 其实就是采⽤了NOR的接⼝,NAND的架构,是两者的性能得到了综合。

这就有了X-LOADER的产⽣,以前我们接触到的都是BOOTLOADER,其实这个X-LOADER也起到初始化的作⽤,因为我们的BOOTLOADER是放在NAND的架构下的,⽽CPU却是从NOR的接⼝下读取BOOTLOADER到SDRAM中的,所以现在要做⼀个⼯作就是要如何将BOOTLOADER在OneNAND的架构下从NAND复制到SDRAM中,这就是X-LOADER的功能了,它不仅初始化OneNAND,并且把U-BOOT从NAND的架构下复制到BufferRam中,再复制到SDRAM中。

zynq硬件设计流程

zynq硬件设计流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor. I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!Zynq 是赛灵思公司(Xilinx)推出的一款集成了 ARM 处理器和 FPGA (现场可编程门阵列)的片上系统(SoC)。

ZYNQMPSoc的启动过程

ZYNQMPSoc的启动过程ZYNQ启动是由ARM引导FPGA,以及用户程序的加载。

预配置阶段Pre-configuration stage1. 通过上电复位(POR),将PMU(平台管理单元/Platform Management Unit)从复位状态唤醒,提供如下操作:o复位低压域LPD寄存器o复位全电源域FPD寄存器o复位PMU的RAMo复位PMU处理器的TLB内存o检查LPD、AUX、专用IO等区域电压o复位CSU、LPD、FPD的内存区2.执行PMU ROM中的预启动代码,以执行复位操作(包括配置安全单元CSU)复位),该阶段结束的标志是CSU复位的释放。

预启动代码进行的初始化操作:•初始化PS Sysmon单元和启动所需要的PLL•清除PMU RAM 和 CSU RAM区域•验证PLL锁•利用PS Sysmon验证LPD、AUX、I/O的范围•清除低压域(LPD)和全电源域(FPD)配置阶段Configuration stageCSU复位后,初始化OC-RAM,将FBSL加载到OC-RAM(on-chip RAM),CSU加载PMU用户固件(PMU FW:firmware)到PMU RAM,若没有则不加载。

在ZYNQ上运行程序的时候,Boot Rom直接固化在硬件中,开发者无法修改。

FSBL(first stage boot loader)是第一阶段的加载程序,经过这个阶段,后面系统才能够运行裸奔程序或者是引导操作系统的u-boot。

用户可以选择用cortex-a53制作启动的FSBL文件,也可以选择用cortex-r5来制作启动的FSBL文件。

处理器开始执行FSBL代码。

FSBL(first-stage boot loader)的作用如下: 1.初始化PS端配置,如:MIO、PLL、DDR、QSPI、SD等。

2.加载PL端程序,即:加载bitstream 3.搬运用户程序到DDR,并跳转执行。

Zynq7000从零开始之一

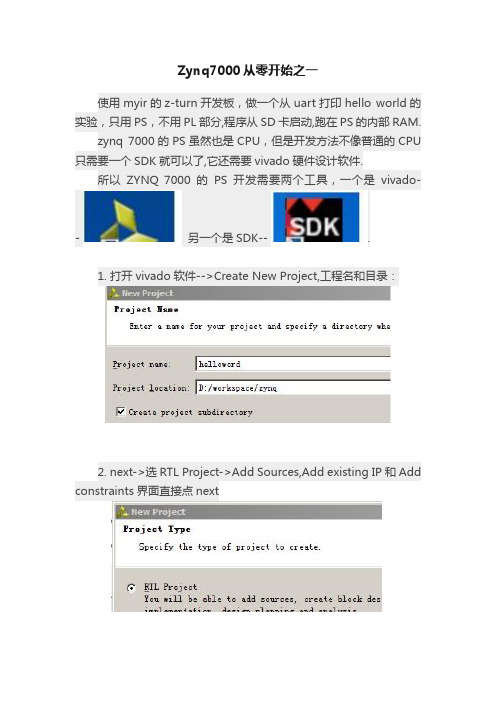

Zynq7000从零开始之一使用myir的z-turn开发板,做一个从uart打印hello world的实验,只用PS,不用PL部分,程序从SD卡启动,跑在PS的内部RAM.zynq 7000的PS虽然也是CPU,但是开发方法不像普通的CPU 只需要一个SDK就可以了,它还需要vivado硬件设计软件.所以ZYNQ 7000的PS开发需要两个工具,一个是vivado-- 另一个是SDK-- .1. 打开vivado软件-->Create New Project,工程名和目录:2. next->选RTL Project->Add Sources,Add existing IP和Add constraints界面直接点next3. New Parts界面4. 添加IP,在Flow Navigator的IP Integrator下点Create Block DesignCreate Block Design如下,点OK在Diagram界面点击Add IP双击ZYNQ7 Processing System,添加CPU5. 设置CPU在Diagram界面点击Run Block Automation,不做修改,点Finish就可以。

在Diagram界面双击进入设置界面,我们把所有的接口去掉,只留下FIXED_IO.1> PS-PL Configuration->General->Enable Clock Resets->去掉FCLK_RESET0_N2> PS-PL Configuration->GP Master AXI Interface->去掉 MAXI GP0 interface3> Clock Configuration->PL Fabric Clocks->去掉FCLK_CLK04> DDR Congiguration->去掉Enable DDR5> 设置SD和UART引脚MIO Configuration->Bank1 IO Voltage选LVCMOS 1.8V.MIO Configuration->IO Peripherals->选上SD 0, SD 0的引脚配置:MIO Configuration->IO Peripherals->选上UART 1, UARRT 1的引脚配置:6. 点击OK返回Diagram界面, 把DDR接口删掉,配置之后的界面7. 生成设计文件右击system项->Generate Output Products->直接点Generate, 之后会提示文件生成成功.右击system项->Create HDL Wrapper选下面一项,点OK注意:如果重新修改了CPU配置,上面两个步骤一定要重新实行。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Z-Turn Board使用Xilinx的Zynq 7000系列芯片,即Zynq-7000 Extensible Processing Platform,是一个可扩展处理平台,简单说就是有个FPGA做外设的A9双核处理器。

所以,它的启动流程自然也和FPGA完全不同,而与传统的ARM处理器类似。

Zynq7000支持多种设备启动,包括Jtag、NAND、parallel NOR、Serial NOR (Quad-SPI)以及SD 卡。

按手册说明除了Jtag之外的启动方式均支持安全启动,使用AES、SHA256加密后的启动代码(不过在勘误里说到,当前硅片版本的无法正常使用secure configuration功能,所以俺就不介绍它鸟)

还是按照时间顺序来介绍下具体流程吧

1、在器件上电运行后,处理器自动开始Stage-0 Boot,也就是执行片内BootROM中的代码。

2、BootROM会初始化CPU和一些外设,以便读取下一个启动阶段所需的程序代码:FSBL (First Stage Bootloader)。

不过这又有一个问题了,之前说到,Zynq支持多种启动设备,BootROM怎么知道从哪个启动设备里去加载FSBL?这就得靠几个特殊的MIO引脚来选择了,具体见下图。

BootROM会去读取MIO[2..8],从而确定启动设备,将选定设备的头192Kbyte内容,也就是FSBL,复制到OCM中,并将控制器交给FSBL。

3、FSBL启动时可以使用整块256Kb的OCM,当FSBL开始运行后,器件就正式由咱自己控制了。

Xilinx提供了一份FSBL代码,如果没什么特殊要求,可以直接使用。

按照手册说明,FSBL应该完成以下几件事。

使用XPS提供的代码,继续初始化PS(ARM)。

将bitstream写入PL(配置FPGA),不过这一步也可以以后再做。

将接下来启动用的Second Stage Bootloader(SSBL,一般就是U-Boot一类的东西),或者裸奔程序,复制到内存中

跳到SSBL运行去

4、接下来的步骤就没啥特别了,U-boot开始运行,初始化好Linux启动环境,然后开始运行Linux系统。

双核处理器, Board, 程序, 加密, 上电。