Xilinx-XADC的使用中文介绍doc资料

xadc wizard用法 -回复

xadc wizard用法-回复XADC(Xilinx Analog-to-Digital Converter)是一种用于将模拟信号转换为数字信号的硬件模块,广泛应用于Xilinx的FPGA(现场可编程门阵列)中。

XADC Wizard是一个方便易用的工具,用于配置和生成XADC 模块的Verilog或VHDL代码。

本文将一步一步介绍如何使用XADC Wizard来配置和使用XADC模块。

第一步:打开Xilinx Vivado软件并创建工程首先,打开Xilinx Vivado软件,并创建一个新工程。

选择一个合适的名称和文件夹路径,并选择相应的FPGA设备。

第二步:添加XADC模块在工程创建完成后,打开生成的Block Design并打开“Design Sources”面板。

右键单击并选择“Add IP”,在搜索框中输入“XADC”,然后选择“XADC Wizard”并单击“Add”。

第三步:配置XADC模块在弹出的XADC Wizard界面中,可以配置各种参数来满足特定的需求。

首先,选择XADC模块的采样率和分辨率。

采样率决定了模块对输入信号进行采样的频率,而分辨率决定了模块对模拟信号进行数字化的精度。

接下来,可以选择是否启用内部温度传感器和电压检测器。

这些传感器可以提供FPGA芯片的温度和电压信息,以便进行实时监测和控制。

另外,还可以配置模块的输出方式和电压范围。

XADC模块可以将转换后的数字信号输出到FPGA内部的寄存器或片上存储器中,并且可以选择输出的电压范围,如0V到1V或是-1V到1V等。

最后,还可以选择是否生成模块的配置和测试代码,并且可以自定义模块的名称和文件路径。

第四步:生成XADC模块在完成对XADC模块的配置后,单击“Finish”按钮,XADC Wizard将自动生成需要的Verilog或VHDL代码,并将其添加到工程中。

第五步:使用XADC模块生成的代码中包含了对XADC模块的初始化和配置,以及对模块进行数据转换和读取的相关操作。

xadc核例化教程

xadc核例化教程7系列的XADCIP核包括两个12位的模数转换器,转换速率可以达到1MSPS(每秒一百万次采样)。

它带有片上温度和电压传感器,可以测量芯片工作时的温度和供电电压。

用户可以设置报警阈值,用来检测温度过高或者供电电压异常等事件。

除此之外,通过XADCIP 核内部的模拟多路复用器,它支持最多17路外部模拟输入信号的测量,且支持单极、双极和差分等信号类型。

为没有在设计中直接例化XADC模块,故XADCIP核工作在一种预先定义好的模式即缺省模式,此模式下XADCIP核专用于监视芯片上的供电电压和芯片温度。

以上是对XADCIP核的简介。

教程:1、首先建立一个空白的工程,然后点击IPCatalog;2、输入XADC找到我们要的IP核,并且双击他;3、在Basic界面进行配置,使能AXI4Stream,在仿真波形选择上,我们选sin波,频率10k,2个周期;把警报信号都关了;4、这里我们选择通道VP/VN,然后点击确定,再点击弹窗里的Generate,我们的IP核就配置好了;5、点击IPSource,展开INSTANTIATIONTemplate,双击.veo文件,可以看到官方给出的当前配置下的例化案例;6、右键IP核,点击OpenIPExampleDesign,点击OK,然后等待;7、我们可以看到仿真文件xadc_wiz_0_tb已经生成,双击可以打开查看;8、点击RUNsimulation,以及runbehavioralsimulation,可以看到我们的仿真结果,但是是不完整的;9、先点击中间的箭头,再点击zoomfit按键,可以看到完整的仿真结果,找到m_axis_tdata[15:0]信号,右键,waveformstyle,Analog,这条数据就是我们的仿真下的AD采集数据,两个周期且频率为10K的SIN波。

XilinxXADC的使用中文介绍.docx

Zynq 器件 XADC的使用 ( 原创 )1.前言赛灵思的7 系列 FPGA和 Zynq 器件创造性地在片上集成了模数转换器和相关的片上传感器(内置温度传感器和功耗传感器),这是相比赛灵思前一代产品来新增加的特性,可在系统设计中免去外置的ADC器件,有力地提高了系统的集成度。

本文就这一新模块的使用进行简单介绍,希望对大家有所帮助,当然如有不当之处还请高手指正,以免误导大家,欢迎大家补充。

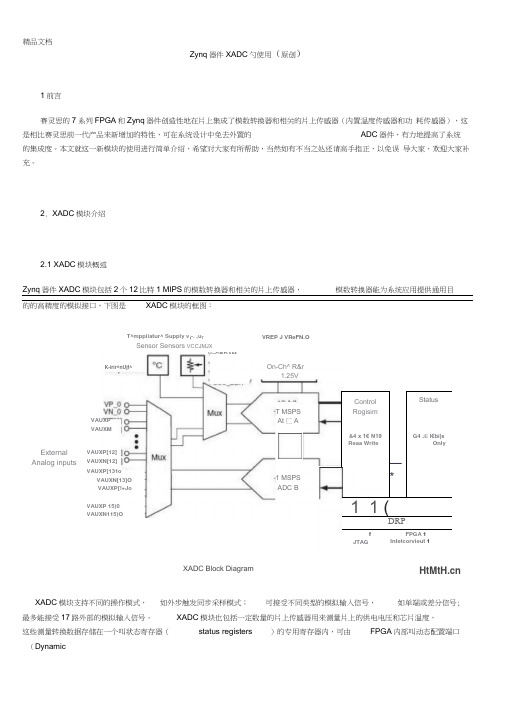

2. XADC模块介绍2.1 XADC 模块概述Zynq 器件 XADC模块包括2 个 12 比特 1 MIPS的模数转换器和相关的片上传感器,模数转换器能为系统应用提供通用目的的高精度的模拟接口,下图是XADC模块的框图:XADC模块支持不同的操作模式,如外步触发同步采样模式;可接受不同类型的模拟输入信号,如单端或差分信号;最多能接受 17 路外部的模拟输入信号。

XADC模块也包括一定数量的片上传感器用来测量片上的供电电压和芯片温度,这些测量转换数据存储在一个叫状态寄存器(status registers)的专用寄存器内,可由FPGA内部叫动态配置端口(DynamicReconfiguration Port (DRP))的16 位的同步读写端口访问。

ADC转换数据也可以由JTAG TAP访问,这种情况下并不需要去直接例化 XADC模块,因为这是一个已经存在于 FPGAJTAG结构的专用接口,此时因为没有在设计中直接例化XADC模块, XADC模块就工作在一种预先定义好的模式叫缺省模式,缺省模式下 XADC模块专用于监视芯片上的供电电压和芯片温度。

XADC模块的操作模式是由用户通过 DRP或 JTAG接口写控制寄存器来选择的,控制寄存器的初始值有可能在设计中例化 XADC模块时的块属性( block attributes )指定。

2.2 XADC 模块管脚需求所有的 XADC模块专用管脚都位于bank0,所以都加有_0的后缀。

xadc原理

xadc原理XADC是Xilinx公司推出的一种高性能、高灵活性的模数转换器(ADC)和数字模拟转换器(DAC),被广泛用于FPGA芯片中。

它的主要功能是将模拟信号转换为数字信号或将数字信号转换为模拟信号。

XADC具有很高的分辨率和采样率,支持各种输入和输出模式,并可以灵活地配置进行数据处理和滤波等操作。

在XADC的设计中,核心部分是一个多通道ADC和DAC组成的数据转换器。

它可以通过编程方式控制转换的精度和速度,以满足不同应用的需要。

XADC采用了16位的转换精度,其采样率可以达到1 MSPS (百万样本每秒)。

XADC的输入通道由模拟输入引脚和内部硬件构成。

模拟输入引脚是FPGA芯片上固定的引脚,用于接收外部模拟信号。

内部硬件通道由芯片内部的参数感测器等电路构成,可以测量基准电压、温度、电源电压等内部参数。

XADC还可以通过多路复用器选择不同的输入通道进行转换。

XADC的输出可以通过AXI总线和配置界面进行读取。

AXI总线是一种高性能的总线架构,可以实现与其他外设的高速数据传输。

配置界面则是FPGA芯片的一部分,用于配置和控制XADC的工作方式。

用户可以通过配置界面选择转换模式、采样率、参考电压等参数。

在使用XADC时,需要对其进行初始化和配置。

首先,需要对XADC 进行电源管理和时钟控制,使其正常工作。

其次,需要进行模拟引脚和内部硬件通道的配置,以确定输入信号源。

然后,需要配置转换精度和采样率,以满足具体应用的需求。

最后,可以通过AXI总线和配置界面读取和处理转换后的数据。

总结起来,XADC是一种高性能、高灵活性的ADC和DAC,可以将模拟信号转换为数字信号或将数字信号转换为模拟信号。

它具有很高的分辨率和采样率,并支持各种输入和输出模式。

XADC可以通过编程方式配置和控制,以满足不同应用的需求。

因此,在FPGA芯片中广泛应用于数据采集、信号处理、仪器仪表等领域。

xadc wizard用法 -回复

xadc wizard用法-回复xadc(Xilinx Analog-to-Digital Converter)是一种用于在Xilinx FPGA(Field-Programmable Gate Array)平台上进行模拟到数字转换的IP核。

它提供了一种以可编程方式将模拟信号转换为数字信号的方法。

在本文中,我们将详细介绍xadc wizard的用法。

我们将逐步回答以下问题:1. 什么是xadc wizard?2. 如何使用xadc wizard?3. 如何配置和使用xadc核?4. 如何读取xadc核的输出值?5. 如何优化xadc的性能?6. xadc核的应用场景有哪些?现在让我们一步一步回答这些问题,深入了解xadc wizard的用法。

1. 什么是xadc wizard?xadc wizard是一种在Xilinx Vivado(Xilinx FPGA设计工具)中提供的可视化配置工具。

它用于生成和配置xadc核。

通过xadc wizard,我们可以根据特定的需求对核进行配置,并将其集成到我们的FPGA设计中。

2. 如何使用xadc wizard?首先,在Vivado工程中打开“IP Catalog”选项卡。

然后,搜索并选择“xadc wizard”IP核。

接下来,双击该核,在弹出的对话框中选择“开户工具”选项。

3. 如何配置和使用xadc核?在xadc wizard工具中,我们可以配置xadc核的各种参数,包括采样率、输入电压范围、转换精度等。

一旦配置完成,我们可以生成和导出IP。

然后将IP核添加到Vivado设计中。

4. 如何读取xadc核的输出值?一旦将xadc核添加到设计中,我们可以使用Xilinx提供的API(应用程序接口)来读取其输出值。

这些API包括对于控制和配置xadc核的函数,以及读取转换数据的函数。

我们可以在Vivado的SDK(软件开发工具)中编写C代码来访问这些API,并将xadc核的输出值存储在FPGA片上存储器中或发送到外部系统。

xadc ip核调用例程 -回复

xadc ip核调用例程-回复XADC IP核调用例程IP核(Intellectual Property core)是一种可重复使用的集成电路设计,可以被嵌入到FPGA(Field Programmable Gate Array)中,以实现特定的功能。

Xilinx公司的XADC IP核是一种用于模拟/数字转换器(ADC)的IP核,它使得FPGA可以接收模拟输入信号并将其转换为数字信号进行处理。

在本篇文章中,我们将一步一步地介绍XADC IP核的调用例程。

第一步:创建工程和添加IP核在使用XADC IP核之前,我们首先需要创建一个Vivado工程。

打开Vivado设计套件并在“Welcome to Vivado”对话框中选择“Create Project”。

接下来,我们需要指定项目的名称和存储位置,并选择我们所使用的FPGA设备。

完成这些设置后,点击“Next”。

在第二个对话框中,我们需要选择项目的类型。

选择“RTL Project”并点击“Next”。

在接下来的对话框中,我们需要选择“Default Part”或手动指定所使用的FPGA型号,并选择我们所需要的语言(VHDL或Verilog)。

完成这些设置后,点击“Next”。

最后,在“Default Project Directory”对话框中选择项目文件夹的位置,并点击“Finish”完成工程的创建。

现在,我们需要为我们的工程添加XADC IP核。

在Vivado主界面的左侧面板中,选择“IP”选项卡,并点击“Create IP”。

在“Create and Package New IP”对话框中,选择“Create a new AXI4 peripheral”并点击“Next”。

在接下来的对话框中,我们需要指定IP核的名称和存储位置。

完成这些设置后,点击“Next”。

在第三个对话框中,我们需要选择IP核的参数。

在下拉菜单中选择“XADC”(或“XADC_WIZ”),并点击“Finish”完成IP核的添加。

xadc wizard用法

XADC(Xilinx Analog-inx FPGA器件中的模数 转换器。XADC Wizard是Xilinx Vivado设计套件中的一个工具,用于配置和生成XADC的IP 核。以下是使用XADC Wizard的基本步骤:

xadc wizard用法

5. 点击"Next"继续,然后根据需要配置XADC的参数,例如采样率、通道数、电压范围等。 6. 配置完成后,点击"Next"继续,然后可以选择是否添加其他的IP核或连接到其他的模块。 7. 点击"Finish"完成配置,并将XADC Wizard生成的IP核添加到Block Design中。 8. 连接其他的模块或信号到XADC IP核的输入和输出端口。 9. 生成Bitstream,并将其下载到目标FPGA器件中进行验证和测试。

1. 打开Vivado设计套件,并创建一个新的项目。 2. 在设计界面中,点击左侧的"IP Integrator"选项卡,然后点击右侧的"Create Block Design"按钮,创建一个新的Block Design。 3. 在Block Design中,右键点击设计界面的空白处,选择"Add IP"。 4. 在弹出的对话框中,搜索并选择"XADC Wizard"。

通过XADC Wizard生成的IP核可以方便地在FPGA设计中使用XADC模块,实现模拟信号的采 样和转换功能。根据具体的需求,可以在XADC Wizard中配置不同的参数,以适应不同的应用场 景。

Xilinx-XADC的使用中文介绍doc资料

Zynq 器件XADC 勺使用(原创)1前言赛灵思的7系列FPGA 和Zynq 器件创造性地在片上集成了模数转换器和相关的片上传感器(内置温度传感器和功 耗传感器),这是相比赛灵思前一代产品来新增加的特性,可在系统设计中免去外置的ADC 器件,有力地提高了系统的集成度。

本文就这一新模块的使用进行简单介绍,希望对大家有所帮助,当然如有不当之处还请高手指正,以免误 导大家,欢迎大家补充。

2. XADC 模块介绍2.1 XADC 模块概述Zynq 器件XADC 模块包括2个12比特1 MIPS 的模数转换器和相关的片上传感器,模数转换器能为系统应用提供通用目的的高精度的模拟接口,下图是XADC 模块的框图:XADC Block DiagramXADC 模块支持不同的操作模式,如外步触发同步采样模式;可接受不同类型的模拟输入信号,如单端或差分信号;最多能接受17路外部的模拟输入信号。

XADC 模块也包括一定数量的片上传感器用来测量片上的供电电压和芯片温度,这些测量转换数据存储在一个叫状态寄存器( status registers)的专用寄存器内,可由FPGA 内部叫动态配置端口(Dynamic精品文档External Analog inputsT^mppiiatur^ Supply v (-. ,u T Sensor Sensors VCCJMJXVcCBRAMV QCPNT ,1JVgWJK 门; Vcco DOR ltlVAUXP[12] VAUXN[12] VAUXP[131oVAUXN[13]O VAUXP[!+Jo Control RogisimStatus&4 x 1€ N19G4 JE l€bi|sReaa Write —*Only1 1 (DRPJTAGf FPGA 1 Intetcorvieut 1T MSPS At 匚A1 MSPS ADC BVAUXP VAUXMVAUXP 15)0 VAUXN115)OOn-Ch^ R&r1.25VVREP J VReFN.OK-irir^nUjf^精品文档Reconfiguration Port (DRP))的16位的同步读写端口访问。

Xilinx-XADC的使用中文介绍

Zynq器件XADC的使用(原创)1.前言赛灵思的7系列FPGA和Zynq器件创造性地在片上集成了模数转换器和相关的片上传感器(内置温度传感器和功耗传感器),这是相比赛灵思前一代产品来新增加的特性,可在系统设计中免去外置的ADC器件,有力地提高了系统的集成度。

本文就这一新模块的使用进行简单介绍,希望对大家有所帮助,当然如有不当之处还请高手指正,以免误导大家,欢迎大家补充。

2.XADC模块介绍2.1 XADC模块概述Zynq器件XADC模块包括2个12比特1 MIPS的模数转换器和相关的片上传感器,模数转换器能为系统应用提供通用目的的高精度的模拟接口,下图是XADC模块的框图:XADC模块支持不同的操作模式,如外步触发同步采样模式;可接受不同类型的模拟输入信号,如单端或差分信号;最多能接受17路外部的模拟输入信号。

XADC模块也包括一定数量的片上传感器用来测量片上的供电电压和芯片温度,这些测量转换数据存储在一个叫状态寄存器(status registers)的专用寄存器内,可由FPGA内部叫动态配置端口(DynamicReconfiguration Port (DRP))的16位的同步读写端口访问。

ADC转换数据也可以由JTAG TAP访问,这种情况下并不需要去直接例化XADC模块,因为这是一个已经存在于FPGA JTAG结构的专用接口,此时因为没有在设计中直接例化XADC模块,XADC模块就工作在一种预先定义好的模式叫缺省模式,缺省模式下XADC模块专用于监视芯片上的供电电压和芯片温度。

XADC模块的操作模式是由用户通过DRP或JTAG接口写控制寄存器来选择的,控制寄存器的初始值有可能在设计中例化XADC模块时的块属性(block attributes)指定。

2.2 XADC模块管脚需求所有的XADC模块专用管脚都位于bank0, 所以都加有_0的后缀。

下图表示了XADC的基本输入输出需求:这有两种推荐配置:图中左边XADC由Vccaux(1.8V)供电,并且用一个外部的1.25V参考源。

xadc原理

xadc原理XADC(Xilinx Analog-to-Digital Converter)是赛灵思(Xilinx)公司提供的一种集成在FPGA芯片中的模拟数字转换器。

它是一种多功能的IP(Intellectual Property)核,用于采集和转换模拟信号为数字信号,使FPGA能够处理模拟信号。

xadc原理基于FPGA的片上资源,其中包括了一系列的片上硬件模块,如模拟输入多路复用器、模拟前端电路、模数转换器(ADC)、温度传感器等。

它们共同构成了xadc的工作原理。

模拟输入多路复用器用于选择不同的模拟信号源,如温度传感器、电压传感器等。

通过选择不同的模拟信号源,xadc可以采集不同的模拟信号。

模拟前端电路主要负责对采集到的模拟信号进行增益调整、滤波和放大。

增益调整可以根据不同的应用需求来调整信号的幅值范围,以适应不同的工作环境。

滤波可以去除模拟信号中的杂散噪声,提高信号的质量。

放大可以将信号增大到合适的幅值范围,以便后续的模数转换器能够正确地进行数字化处理。

然后,模数转换器(ADC)是xadc的核心部分,它将模拟信号转换为数字信号,以便FPGA可以对其进行数字处理。

ADC的工作原理是将模拟信号按照一定的时间间隔进行采样,并将每个采样点的电压值转换为一个对应的数字值。

这个过程需要使用到ADC的量化器和采样时钟。

量化器将连续的模拟信号离散化为一系列的数字值,采样时钟则提供了一个时间基准,用于确定每个采样点的时刻。

xadc还集成了一个温度传感器,用于测量FPGA芯片的温度。

温度传感器的原理是根据温度对材料的电性能参数的影响,通过测量这些参数的变化来间接测量温度。

温度传感器可以通过xadc进行读取,并将温度值转换为数字信号。

xadc原理是基于FPGA的片上资源,通过模拟输入多路复用器选择模拟信号源,经过模拟前端电路调整信号的幅值范围、滤波和放大,然后通过模数转换器将模拟信号转换为数字信号,最后通过温度传感器测量FPGA芯片的温度。

Xilinx 7系列FPGA内置ADC XADC获取模拟信号

Xilinx 7系列FPGA内置ADC XADC获取模拟信号

Xilinx 7系列FPGA全系内置了一个ADC,称呼为XADC。

这个XADC,内部是两个1mbps的ADC,可以采集模拟信号转为数字信号送给FPGA内部使用。

XADC内部可以直接获取芯片结温和FPGA的若干供电电压(7系列不包括VCCO),用于监控FPGA内部状况。

同时提供了17对差分管脚,其中一对专用的模拟差分输入,16对复用的模拟差分输入,不使用的时候可以作为普通的User I/O。

关于XADC具体的结构,功能和各个参数的含义,请参考相关文档。

这里不做详细描述。

另外有两点需要注意。

1.关于参考电压的设置,会影响误差范围及采样值的计算公式。

2.模拟差分输入对模拟信号幅值有要求,需要外边模拟电路进行一定程度的转换。

假设现在需要用XADC来获取几个模拟信号的信息,那么应该如何操作呢。

下面解释一种个人偏爱设置方式。

注意红框中的几点:

1.使用DRP端口获取数字信号,这样控制似乎更简单一些。

2.使用连续采样模式,ADC一直工作在数据采集模式,采集后就可以进行输出。

3.使用Channel Sequencer模式,由于只有两个XADC而需要采样的数据过多,所以让XADC依次陆续进行采样。

4.设置好DRP端口的时钟频率。

IP设置第二页,主要是设置Calibration、平均值和外部MUX。

这几个可以暂时跳过,等熟悉XADC的使用后在进行深入了解。

第三页设置告警参数,可以不用。

如果需要的话,可以设置一下,便于使用。

xadc 负值 -回复

xadc 负值-回复【xadc 负值】作为一种先进的模拟数字转换器,XADC(Xilinx Analog-to-Digital Converter)在嵌入式系统中发挥着至关重要的作用。

然而,有时候我们会遇到一些问题,比如xadc产生负值的情况。

在本文中,我将一步一步地回答关于xadc负值的问题,帮助读者更好地理解和解决这个问题。

第一步:了解XADC和负值的概念XADC是一种内置在Xilinx FPGA芯片中的模拟数字转换器。

它可以测量模拟信号并将其转换为数字信号,供FPGA进行处理。

而负值则表示测量到的模拟信号低于原点或参考电压的数值。

第二步:确定问题的来源当xadc产生负值时,我们首先需要确定该问题真正的来源。

可能的原因包括但不限于测量到的模拟信号本身低于原点或参考电压,xadc配置错误,或者是某种硬件问题。

第三步:验证模拟信号为了验证模拟信号本身是否低于原点或参考电压,我们可以使用示波器测量模拟信号的振幅和偏移量。

如果模拟信号确实低于原点或参考电压,那么负值就是合理的。

第四步:检查xadc配置如果我们排除了模拟信号本身的问题,那么我们应该检查xadc的配置是否正确。

可以通过查看FPGA设计中的xadc实例的代码或者使用Xilinx Vivado等工具来验证配置是否符合预期。

第五步:查看参考电压和偏移校准在一些情况下,xadc可能需要参考电压和偏移校准。

如果这些校准没有正确进行,可能会导致xadc产生负值。

检查xadc的参考电压和偏移校准是否正确是解决这个问题的一种方法。

第六步:检查硬件连接如果以上步骤都没有解决问题,那么最后一步就是检查硬件连接。

确认模拟信号的输入端是否正确连接到xadc,并检查是否存在接地或干扰问题。

第七步:使用滤波器在一些情况下,我们可能会遇到模拟信号中的噪音或干扰导致xadc产生负值的问题。

在这种情况下,我们可以尝试使用滤波器来去除噪音或干扰,从而解决xadc产生负值的问题。

Zynq片内XADC应用笔记

Zynq片内XADC应用笔记Zynq片内XADC应用笔记Hello,panda 应用笔记简要描述Xilinx Zynq XADC的相关资源及若干种应用。

参考文档:◆ug480:7Series_XADC.pdf;◆xapp795:driving-xadc.pdf◆xapp554:xadc-layout-guidelines.pdf◆xapp1203:post-proc-ip-zynq-xadc.pdf◆xapp1183:zynq-xadc-axi.pdf◆xapp1182:zynq_axi_xadc_mon.pdf◆xapp1172:zynq_ps_xadc.pdf◆pg019:axi_xadc.pdf◆pg091:xadc-wiz.pdf◆ug953:vivado-7series-libraries.pdf◆ug585:Zynq-7000-TRM.pdf1XADC概述XADC是位于Zynq系列器件Pakage正中心位置的12bit 1MSPS,内置温度传感器,可实时监测片内结温,各路电压数据并可输出告警信号。

图1是XADC原语结构。

图1 XADC原语结构由图1可以看出,XADC模拟输入包括专用模拟输入VP/VN和16组复用模拟信号输入VAUX(15:0);XADC转换结果可以通过动态重配接口(DRP)或者JTAG 接口输出;告警信号可通过ALM(7:0)输出,并有专用的温度告警信号OT。

因此,控制XADC和获得结果数据最终方式必然是通过DRP或JTAG接口,无论它外面作了何种接口的封装,但最终都要转换为DRP 或JTAG实现和XADC 直接相连。

应用笔记仅讨论对XADC的控制和读取结果编程的内容,其他内容请参照:①用户手册:UG480;②前端模拟驱动电路设计:xapp795;③PCB Layout设计:xapp554。

2XADC访问XADC访问路径结构如图2所示,用户可以通过PL-JTAG、PS-XADC和AXI-GP Master接口访问XADC,前面两个在PL逻辑中无需调用XADC原语即可直接访问,后者需要调用XADC IP核。

概述xadc的主要参数

概述xadc的主要参数XADC(Xilinx Analog-to-Digital Converter)是一种集成在Xilinx FPGA(Field-Programmable Gate Array)器件中的模拟-数字转换器,用于将外部模拟信号转换为数字信号以供FPGA进行处理。

XADC具有多个主要参数,包括分辨率、采样速率、输入范围、精度、通道数和功耗等。

分辨率是指XADC可以将模拟信号转换为数字值的精确度。

XADC通常具有12位或14位的分辨率,表示可以将模拟信号转换为4096或16384个离散的数字值。

较高的分辨率可以提供更精确的模拟信号转换,但也会增加计算和存储开销。

采样速率是指XADC对模拟信号进行采样的速度。

XADC通常具有可调节的采样速率,可以根据需要进行配置。

较高的采样速率可以提供更高的信号采样精度,但也会增加功耗和数据处理的要求。

输入范围是指XADC能够接受的模拟信号的电压范围。

XADC通常具有可配置的输入范围,可以根据需要选择不同的范围。

常见的输入范围包括0-1V、0-3.3V和0-5V等。

选择合适的输入范围可以确保模拟信号在转换过程中不会超出范围,从而避免失真和损坏。

精度是指XADC转换的数字值与模拟信号实际值之间的误差。

XADC 通常具有指定的精度,用于描述其数字转换的准确程度。

精度通常以百分比或位数表示,例如0.1%或±1LSB(最低有效位)。

较高的精度可以提供更准确的数字转换结果,但也会增加硬件和算法的复杂性。

通道数是指XADC可以同时转换的模拟信号通道数量。

XADC通常具有多个输入通道,可以同时采集多个模拟信号。

通道数取决于具体的XADC型号和配置,通常可以从1个到16个不等。

较多的通道数可以提高数据采集的效率和多样性,但也会增加硬件资源和功耗。

功耗是指XADC在工作过程中消耗的电能。

XADC通常具有指定的功耗参数,用于描述其工作电流或功率消耗。

功耗取决于XADC的工作模式、采样速率以及其他配置参数。

概述xadc的主要参数

概述xadc的主要参数XADC的主要参数XADC(Xilinx Analog-to-Digital Converter)是Xilinx FPGA中的模拟数字转换器,用于将模拟信号转换为数字信号,以便FPGA进行处理。

XADC具有许多重要的参数,下面将对其主要参数进行概述。

1. 采样率(Sample Rate):采样率是指XADC每秒对模拟输入信号进行采样的次数。

采样率越高,能够更精确地还原原始模拟信号。

XADC的采样率通常在几百kHz到几MHz之间,可以根据具体应用需求进行设置。

2. 分辨率(Resolution):分辨率是指XADC将模拟信号转换为数字信号时的精度。

它表示XADC可以将模拟信号分成多少个不同的数字级别。

一般来说,分辨率越高,XADC能够更准确地转换模拟信号。

XADC的分辨率通常是12位或16位。

3. 输入电压范围(Input Voltage Range):输入电压范围是指XADC可以接受的模拟输入信号的电压范围。

不同的XADC具有不同的输入电压范围,常见的范围包括0V到1V、0V到3.3V等。

在使用XADC时,应根据实际应用需求选择合适的输入电压范围。

4. 参考电压(Reference Voltage):参考电压是指XADC在进行模拟数字转换时使用的基准电压。

XADC通常需要一个稳定的参考电压来确保转换的准确性。

常见的参考电压为1V或3.3V,可以通过外部引脚或内部电压参考源提供。

5. 工作温度范围(Operating Temperature Range):工作温度范围是指XADC能够正常工作的温度范围。

XADC通常具有较广的工作温度范围,可以在-40℃到+125℃的环境温度下正常工作。

6. 功耗(Power Consumption):功耗是指XADC在工作过程中消耗的功率。

XADC通常具有较低的功耗,以确保在嵌入式系统中节省能源。

7. 接口类型(Interface Type):接口类型是指XADC与FPGA之间的连接方式。

XCMB说明

XC2S200 Main Board User’s Manuals This menu contains the user's guide to the FPGA Main Board of the XC2S00 FPGA Integrated System Design System from the Zeppe Tech. Inc. For the use the peripheral module, please refer to the related application notes. For more use of IDS, refer to the user's menu.In This DocumentThis document contains the following sections:• Features• Before Using this Main Board• Functional Descriptionso FPGAo Clocko AVR ISP Porto Host Interface Porto Misc.FeaturesXilinx Spartan XC2S200 ( 200,000 gates ) FPGA, 含284 I/O Pins, 具無限次燒錄週期透過RS232快速電路下載及ISP ( In System Programming )燒錄, 並具資料壓縮, 可同時燒錄多組電路, 並可做動態電路切換2048K bits電路架構EEPROM, 可重覆燒寫10萬次PLL頻率合成器提供3組獨立的高頻clocks ( 800KHz ~ 90MHz ), 及1組低相差1/M 頻率clocks2組可程式低頻clocks ( 0.5Hz ~ 100 K Hz ), 具單步及多步功能提供AVR RISC系列微處理器的ISP燒錄功能提供3個偵錯模式的Debugging Port, 多至128 bits Input pattern feeds / 128 bits output probes; 或memory access模式Before Using this Main Board實驗器附2個電源轉換器(adaptor):一為Digital Power 5V / 4A, 此為FPGA主板所使用, 插在FPGA主板下方另一個體積較小的電源為Analog Power 7.5V / 900mA, 為使用特定Analog Devices (AD/DA, CMOS Image Sensor, VGA) 時, 插在模主上, 之Analog電源供應 ( 這些Devices 的 Digital電源有些仍是由前述Digital 5V/4A Power供應 ) , 不使用這些Devices時, 則不必插上FPGA主板所使用的Power為前述Digital 5V/4A Power, 其正極在中心; 若需使用其他電源, 務必先確認規格是否一致請確認FPGA之I/O 排針, 並無互相或與其他電源接點短路; 此外, 由於實驗器為裸板, 務必注意不可有金屬物或水掉落其上插上電源後, 請檢視板上元件溫度是否過高, 如果溫度過高, 請立即拔除電源, 檢查是否有任何異常, 或與本公司聯絡若欲使用自行擴充之介面, 請於FPGA I/O Pin 與周邊Devices之間, 串上33 Ohm 限流電阻, 以免誤將FPGA I/O Pad 損毀Functional DescriptionsFPGA 主板提供四類功能 :FPGAXilinx Spartan XC2S200FG456, 284 I/Os, 200k Gates, Logic Cells, Kbit Block RAMFPGA Configuration DownloadConfiguration EEPROM Programming & LoadingClock4 Programmable Hi-Frequency Clock CKA-CKD ( 800KHz~90MHz )2 Programmable Lo-Frequency Clock CKE-CKF ( 0.5Hz~100KHz )AVR ISPIn System Programming for AVR Micro-ProcessorsHost InterfaceFeeds Input Pattern & Grabs Output Patterns, each up to 128 nodesMemory Mode Access or Host Emulation by IDSI. FPGA1. Xilinx Spartan II XC2S200FG456 FPGA 位於主板中間, 其284個I/O pins連接至J10-J32, 再由這些Connectors接至週邊模組2. Spartan II 為SRAM Based FPGA, 其電路Configuration 儲存在FPGA內的SRAM Cells; Power On時Configuration 由外部載入此SRAM, 載入完成後,FPGA便以此Configuration運作; 而Power Off時, 此儲存在FPGA內SRAM的Configuration亦即消失3. 此實驗器有2種載入Configuration方式: LoadConfig: 直接由PC端IDS軟體載入FPGA內的SRAM; AddConfig: 由PC端IDS軟體燒錄至EEPROM, 之後(例如Power On時), 再由EEPROM載入至FPGA內(ActConfig )FPGA4. IDS 有關FPGA Configuration 的功能鍵如下圖示:5. 在Forth 內, FPGA Configuration 的指令(Words)如下: Configuration Forth WordsWordStackDescriptionRemarkLOADCONF $addr --Download the configuration file withname at $addrADDCONF $addr -- Add the configuration file withname at $add to EEPROMDELCONF n -- Delete the n-th configuration in theEEPROMACTCONF n -- Activate the n-th configuration inthe EEPROMSETACT n -- Set or disable the n-th configurationin the EEPROM as power-up configurationDIRROM --Display all configuration in EEPROMActConfigConfigROMLoadConfig6. FPGA 主板Layout圖7. XC2S200FG456 FPGA的Pin-Out 圖: 白色圓圈為可使用的I/O, 或Clock Pins.填滿的圓圈為電源及特殊Pin. Pin Number 是以垂直的英文字母和水平的數字組合而成, 例如最左上角的Pin為A1; 最右下角的Pin為AB228. FPGA 主板I/O Pin NumberJ10J11J22J235V GK2 E11F11 B10A10 C10E10 A9D10 D9B9 E9C9 B8A8 D8C8 GK0X GND3V3VD11B3F12E12GND GNDGND GNDB12C12D12A133V3VGND GK5B13E13D13C13A14B14C14E14D14A15A16B15C15D15E15D16GK1Y5VJ12J13J24J25 5V GK1XA7E8C7B7C6D7B6D6E7C5A5D5 E6B5 A3B1 GK4GND3V3VA4B4C1D2GND GNDGND GNDC21D21D20C223V3VGND GK0YC16E16A17C17B17D17A18B18C18A19B19C19A20H18D22E21GK35VJ14J15J26J275V GK2 E1 E2 F1 F2 F5 G1 G5 H1 J1 J2 J3 J4 K1 K4 L4 L3 GK0 GND3V 3VE3 E4F3 F4G3 G4H2 H5H3 H4J5 K2K3 K5L5GND GNDGND GNDE22 F18F21 F22G20 G21H20 H21J18 J20K18 K19K22 L17L203V 3VGND GK5E20 G18F19 F20G19 H19H22 J19J21 J22K20 K21L18 L21L22 M17GK1 5VJ34J35GK0X GK0GK1X GK1GK1GK1Y GK0GK0Y J16J17J28J295V GK1 L6L1 M5M6 M1M3 N1P1 P2P3 R1R2 T4T5 V2U4 GK4GND3V3VM4N4N3N2N5P4P5T1R4R5T3T2U1U2V1GND GNDGND GNDM19N19M20P18P19N21N22P21P22U19U20T21T22U21U223V3VGND GK0M18M22N20N18P20R19R18T20R22R21T19V20V19T18V22V21GK35VJ18J19J30J315V GK2 V9V3 V7W6 W1Y6 W2W7 Y7W8 W9Y8 Y9V10 W10Y10 GK0X GND3V3VV4W3V8W5GND GNDGND GNDAA20AA22AA19AB203V3VGND GK5W21W22Y21W18AA18AB19AB18Y17Y18AB17V17AA17W16W17AB16Y16GK1Y5VJ20J21J32J33 5V GK1XV11W11U11AB10Y1AB9Y2AB3AA4AB4AA5AB5 AA6AB6 AA7AB11 GK4GND3V3VAA8AB8AA9AA10GND GNDGND GNDU12V12Y12AA123V3VGND GK0YY15V16AA15W15Y14AB15AB14AA14Y13W14AB13AA13W13V15V13V14GK35V9. J5設定的說明: J5為Configuration方式設定, 目前只提供單一原設定的此種方式,若使用者需要其他Configuration的方式, 可將原設定的Jumper取下, 在相關的Pin 輸入對應的Configuration訊號(例如使用Download Cable)clk d0 sta donecclk cdt csta cdntck tdi tms tdoJ5Pin Type功能說明clk in FPGA configuration clock inputd0 in FPGA configuration data inputsta out FPGA configuration status outputdonedone out FPGAconfigurationcclk out Configuration clock outputcdt out Configuration data outputcsta in Configuration status inputcdn in Configuration done inputtck in FPGA JTAG clock inputtdi in FPGA JTAG data inputtms in FPGA JTAG mode selecttdo out FPGA JTAG data outputJ5 Default SettingII. CLOCK1. FPGA主板與各個週邊模組共用6個global nets, 即gck0-gck5; 另外主板上有6個Programmable clock sources, 即cka-ckf; J6就是用來設定cka-ckf如何分別驅動gck0-gck5的方式, 而gck0-gck3分別又接至FPGA的Dedicated Clock/Input: (gck0->W12), (gck1->C11), (gck2->A11), (gck3->Y11), gck4及gck5未接至FPGAcke gck2 cka gck1 ckd gck5gck4 ckc gck0 ckb gck3 ckfgck2 gck3gck5 gck4J6Clock Source的Select jumper區Pin Type功能說明cka,ckb,ckc out Programmable high frequency clock sourcesckd out 10Mhz clock sourcecke,ckf out Programmable low frequency clock sourcesgck0 in FPGA clock pin W12/System global netgck1 in FPGA clock pin C11/System global netgck2 in FPGA clock pin A11/System global netgck3 in FPGA clock pin Y11/System global netgck4 in System global netgck5 in System global netJ6 Default Setting2. Clock的指定a. 此實驗器有3組獨立可程式的高頻clock sources—分別為CKA, CKB,CKC, 其頻率為800KHz~90MHz; 另外1組CKD, 在此版本為目前頻率為10MHzb. 實驗器另有2組可單步, 多步低頻的clock, 分別為CKE和CKF, CKE的clock頻率為1Hz~100KHz, CKF的clock頻率為0.1Hz~100KHz; 低頻的clock可作為debug之用; CKE和CKF 頻率設定的單位為: 每秒toggle(0->1或1->0)次數, 因此, 實際的clock週期頻率為f*1/2.c. 在PACE Pin Assignment Editor中, Xilinx FPGA XC2S200FG456有4個Ports是FPGA專門用來作為clock的Input, 分別是W12, C11, A11, Y11 ,System Main Clock必須設定在這4個Ports的其中之一d. 實驗器主板的J6為Clock Source的Select jumper區, 例如, 將jumper short在cke與gck2上, 接著在進行Pin Assignment的時候, 將clock指定到A11;如此, cke(drives)->gck2(drives)->A11 of FPGA; 然後輸入Forth指令20 ckef, 意思就是設定cke,以20Hz的頻率toggle (10Hz的clock頻率), drives gck2及A11e. 經由Jumper的Short, clock輸入的Port就有許多不同的組合與選擇, 例如 :cka可驅動gck0, gck1或 gck2; 下表列出每個clock source ckn所能驅動的gck listgck0(W12)gck1(C11) gck2(A11) gck3(Y11) gck4 gck5cka v v vckb v v vckc v v vckd v v vcke v vckf v v3. J34, J35設定的說明: 為使Global clock net gck0及gck1能運載較高的頻率,其default的fan out只有module1,4兩個memory modules, 以減少fan out load.若欲使gck0,1 驅動module0,2 及 module3,5,則須分別設定J34, J35gck0x gck0gck1x gck1gck1gck1y gck0gck0y J34J35Pin Type功能說明gck0 out Clock source from clock generator via J6gck0x in Clock driving input to module 0,2gck1 out Clock source from clock generator via J6gck1x in Clock driving input to module 0,2Pin Type功能說明gck0 out Clock source from clock generator via J6gck0y in Clock driving input to module 3,5gck1 out Clock source from clock generator via J6gck1y in Clock driving input to module 3,5J34 Default Setting J35 Default Settingv 直接連接驅動; * 經由J34或J35設定連接驅動; 空白為無法連接驅動Module0 Module1 Module2 Module3 Module4 Module5 gck0 * v * * v *gck1 * v * * v *gck2 v v vgck3 v v vgck4 v v vgck5 v v v4. Clock頻率的設定a. 此實驗器有3組獨立可程式的高頻clock sources—分別為CKA, CKB,CKC, 其頻率為800KHz~90MHz; 另外1組CKD, 在此版本為目前頻率為10MHzb. 實驗器另有2組可單步, 多步低頻的clock, 分別為CKE和CKF, CKE的clock頻率為1Hz~100KHz, CKF的clock頻率為0.1Hz~100KHz; 低頻的clock可作為debug之用; CKE和CKF 頻率設定的單位為: 每秒toggle(0->1或1->0)次數, 因此, 實際的clock週期頻率為f*1/2.c. Clock 頻率設定的FORTH Words如下:CKAF f -- Set frequency of clock A in the unit of KHzCKBF f -- Set frequency of clock B in the unit of KHzCKCF f -- Set frequency of clock C in the unit of KHzCKEF f -- Set frequency of clock E in the unit of 1/2Hz, 0:stopsCKENF n f -- Toggle clock E n steps at the frequency of f *1/2HzCKEN n -- Toggle clock E n steps at the previous frequencyCKFF f -- Set frequency of clock F in the unit of 1/2Hz, 0:stopsCKFNF n f -- Toggle clock F n steps at the frequency of f *1/2HzCKEN n -- Toggle clock F n steps at the previous frequency5. Clock其他注意事項a. gck0和gck1除了驅動FPGA本身即Module 1和Module 4, 雖然可藉由J34和J35再額外驅動其他的4個Modules, 但是如果Loading過大, 有可能造成clock的波形不佳, 違反某些chips對clock的準位或transition time的requirements, 解決方法如下 :b. 不使用的Module, 其clock選擇的Jumper可以保持空接, 以減少clock的Loading; 或拔除J34, J35的Jumpersc. 當gck0或gck1所需驅動的Loading較大時, 可分散clock的driving source,例如 : 某個設計需要由同一個clock 同時驅動FPGA, 2個SDRAM Module, VGA Module 及Image Sensor Module, 可採取此方式 : CKA->gck0->(FPGA, left SDRAM, right SDRAM); CKD->gck3->VGA; CKC->gck2-> Image Sensor . Jumper 設定如下圖; 並設定:25000 ckaf 2500 ckbf 2500 ckcfd. 當CKA, CKB, CKC, 設定的頻率相同時, 其相位會一致(在Update 的新版IDS), 而Loading 相近時, Clocks 間的Skew 即不大. CKD 則一直與CKA 同頻同相.III. AVR ISP Port1. J2為AVR Processor ISP(In system programming) 的輸出連接器, 透過所附的cable,連接至AVR模組或其他AVR板子, 則可使用IDS進行該AVR processor 的ISP燒錄miso v5vmsck mosimrst gndmssJ2Pin Type功能說明v5v pwr Digital power 5V supply by main boardgnd pwr Digital power groundmiso in AVR ISP misomsck out AVR ISP msckmrst out AVR ISP mrstmosi out AVR ISP mosimss inout slave select for AVR SPI host interfaceIV. Host Interface Port1. J1為Host Interface Port, 其多項功能, 請參考Application Note: Host InterfacePort.hp1 hp3 hp5 hp7 hp9 hp11 hp13 hp15hp0 hp2 hp4 hp6 hp8 hp10 hp12 hp14J1Pin Type功能說明hp[15:0] inout Host port interfaceV. MISC.1. Short J3 可令整個主板進行Reset動作gndrstJ3Pin Type功能說明reset rst inSystemgnd pwr Digital power ground。

xadc 负值 -回复

xadc 负值-回复xadc是一种电子元件中的一个模块,它是一种数据转换器,可以将模拟信号转换为数字信号。

在一些特殊的情况下,xadc可能会产生负值,意味着模拟信号的电压低于其参考电压或者超出了其输入电压范围。

本文将详细介绍xadc负值的原因、影响以及解决办法。

首先,让我们更深入地了解什么是xadc。

xadc是Xilinx FPGA(Field Programmable Gate Array,现场可编程门阵列)系列芯片中的一个模块,它通常用于在FPGA中实现模拟信号的采集和转换。

xadc可以将模拟信号转换为数字信号,并通过FPGA的逻辑电路进行处理。

这使得FPGA 可以处理与外部世界更接近的模拟信号,例如温度、湿度、电压等。

然而,有时xadc可能会产生负值的输出。

这种情况通常发生在输入信号电压低于xadc的参考电压时,或者超出了其输入电压范围。

这可能是因为电路设计问题、传感器故障或者电源问题等原因导致的。

对于这种负值输出,可能会产生一系列的问题和影响。

首先,这可能会导致FPGA逻辑电路的错误判断。

如果输入信号被错误地转换为负值,那么FPGA中的逻辑电路可能会基于错误的数值进行计算和决策,从而导致系统错误。

其次,对于一些特定的应用场景,负值的出现可能会破坏系统的正常工作。

例如,在一些传感器应用中,如果温度或湿度的信号被错误地转换为负值,可能会导致错误的数据处理和判断。

最后,负值输出还可能影响到整个系统的可靠性和稳定性。

如果FPGA逻辑电路无法正确处理负值,可能会导致系统的性能下降或者丧失系统的功能。

针对xadc负值的问题,我们可以采取一些解决办法。

首先,我们可以通过检查电路设计和传感器连接来解决这个问题。

确保信号传输过程中没有电源杂散或者数值翻转的问题,以及传感器与xadc之间的连接正确可靠。

其次,我们可以考虑调整参考电压或者输入电压范围,使其适应实际应用场景。

通过合理的设置参考电压和输入电压范围,可以有效地避免负值输出的问题。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Zynq器件XADC的使用(原创)

1.前言

赛灵思的7系列FPGA和Zynq器件创造性地在片上集成了模数转换器和相关的片上传感器(内置温度传感器和功耗传感器),这是相比赛灵思前一代产品来新增加的特性,可在系统设计中免去外置的ADC器件,有力地提高了系统的集成度。

本文就这一新模块的使用进行简单介绍,希望对大家有所帮助,当然如有不当之处还请高手指正,以免误导大家,欢迎大家补充。

2.XADC模块介绍

2.1 XADC模块概述

Zynq器件XADC模块包括2个12比特1 MIPS的模数转换器和相关的片上传感器,模数转换器能为系统应用提供通用目的的高精度的模拟接口,下图是XADC模块的框图:

XADC模块支持不同的操作模式,如外步触发同步采样模式;可接受不同类型的模拟输入信号,如单端或差分信号;最多能接受17路外部的模拟输入信号。

XADC模块也包括一定数量的片上传感器用来测量片上的供电电压和芯片温度,这些测量转换数据存储在一个叫状态寄存器(status registers)的专用寄存器内,可由FPGA内部叫动态配置端口(Dynamic

Reconfiguration Port (DRP))的16位的同步读写端口访问。

ADC转换数据也可以由JTAG TAP访问,这种情况下并不需要去直接例化XADC模块,因为这是一个已经存在于FPGA JTAG结构的专用接口,此时因为没有在设计中直接例化XADC模块,XADC模块就工作在一种预先定义好的模式叫缺省模式,缺省模式下XADC模块专用于监视芯片上的供电电压和芯片温度。

XADC模块的操作模式是由用户通过DRP或JTAG接口写控制寄存器来选择的,控制寄存器的初始值有可能在设计中例化XADC模块时的块属性(block attributes)指定。

2.2 XADC模块管脚需求

所有的XADC模块专用管脚都位于bank0, 所以都加有_0的后缀。

下图表示了XADC的基本输入输出需求:

这有两种推荐配置:图中左边XADC由Vccaux(1.8V)供电,并且用一个外部的1.25V参考源。

用外部参考源在精度和热飘移方面可以获得更好的性能,一个磁珠用隔离模拟地和数字地,这可避免较常用的模拟和数字电路共地而把噪声带入模拟电路的缺点;图中右边XADC是用片内的参考源,这时VREFP脚必须按图中所示连接到地。

下表列出了XADC相关的引脚和连接:

注:XADC模块有一专用的支持差分输入的模拟通道输入引脚(VP/VN),另外还最多有16个辅助的模拟通道输入引脚(ADxP or ADxN,x为0到15),Kintex-7不支持辅助通道6,7,13,14,15。

Zynq-7000 AP SoC器件由于封装不通可能不会支持所有的辅助通道,具体要查询封装文件。

3.基本使用方法

3.1 XADC模块的操作模式

最基本的操作模式叫缺省模式,缺省模式下XADC模块专用于监视芯片上的供电电压和芯片温度,这时XADC模块并不需要用户对其进行配置。

另外一个为同步采样模式,按预定的步骤顺序采样两个外部的模拟输入信号,并把采样结果存储在状态寄存器内。

单通道模式,在这种模式下,用户必须通过写控制寄存器40H的CH4到CH0比特来选择一个要采样的通道。

另外控制寄存器40H的BU(analog input mode)和ACQ(settling time)两个参数也必须设置。

独立ADC模式,在这种模式下,ADC A是固定用来实现一个类似于缺省模式的“监控模式”,报警输出功能是有效的,用户必须设置正确的报警门限;ADC B只能用来测量外部的模拟输入。

Single Pass模式,在这种模式下,按用户选择的采样顺序序列顺序采样一遍后停止ADC。

采样顺序序列是由用户写序列通道选择寄存器48H和49H来设定的。

Continuous Sequence连续序列模式,这种模式和Single Pass模式很相似,区别是采样完一遍后系统自动重新开始序列采样,故为连续采样。

模式选择是由控制寄存器41H的SEQ3到SEQ0比特决定,具体如下图示:

3.2 XADC primitive

XADC模块的使用方法,一是直接用FPGA JTAG专用接口访问,这时XADC模块工作在缺省模式;二是在设计中例化XADC 模块,这是可以通过FPGA逻辑或ZYNQ器件的PS到ADC模块的专用接口访问。

例化XADC模块有两种基本形式:一是ISE和PlanAhead环境下LogiCOREIP核的形式调用,二是EDK环境下对LogiCOREIP核的调用。

这两种调用方法相信对使用过XILINX产品的朋友来说操作界面与步骤都很熟悉,这里就不赘述了,主要是想说明下XADC模块原语,以期对这模块有个基本的了解。

下图是XADC模块的输入与输出端口的示意图:

各引脚功能描述如下:

XADC可配置的属性如下图示(等效于配置相应的寄存器):

4.PCB要点

模数转换器所能获得的精度和PCB设计关系很大,因为模数转换器是敏感的部件,它的模拟接口容易受到噪声的影响,下面就PCB设计时要注意的地方做一简单介绍。

1). 典型应用中VREFP 和VREFN外接1.25V参考电压,电压精度为± 0.2%,并且在PCB上要尽可能的靠近VREFP 和VREFN引脚,并且按电源IC要求使用合适的去耦电容。

2). 如果使用片内的参考电压,VREFP 和VREFN引脚要通过一磁珠连到模拟地,以去除高频干扰。

上面两种情况的电源连接情况如下图示:

注意隔离数字电源和模拟电源的磁珠应使噪声对模拟电源供应的波动小于1 LSB (250 uV),这在用12比特测量时可以最小化噪声对精度的影响。

作为一个通用原则,模拟地和数字地要分开,以减少噪声从地平面耦合过来的影响。

3). 尽量在每个引脚放一个100nF的去耦电容,PCB上尽量靠近引脚。

4). 外接1.25V参考电压接VREFP 和VREFN引脚时,PCB上应该用紧密耦合的差分对形式布线,它们应该走线在同一层,使用最小间隔,可以用模拟电源和模拟地来隔离保护它。

5). 外部模拟输入引脚采用差分输入形式可以有效地去除共模噪声,两个差分输入应该按紧密耦合的差分对形式布线,使用最小间隔,推荐在输入端应该放置抗混叠滤波器,这个抗混叠滤波器应该尽可能地靠近FPGA。

5.参考文献:

以上介绍抛砖引玉挂一漏万地,详细的说明还需要大家认真阅读XILINX官方出的原始文档,下面列出这些主要的参考文献供大家进一步学习研究:

[1].Xilinx UG480: 7 Series FPGAs and Zynq-7000 AllProgrammable SoC XADC Dual 12-Bit 1 MSPS

Analog-to-Digital Converter User Guide

[2].Xilinx UG772: LogiCORE IP XADC Wizard User Guide

[3].Xilinx PG019: LogiCORE IP AXI XADC (v1.00.a) Product Guide

[4]. Xilinx UG585:Zynq-7000 All ProgrammableSoC Technical Reference Manual

[5].Xilinx XAPP554: XADC Layout Guidelines。