Chapter4 模拟集成电路设计

《模拟集成电路设计》教学大纲

《模拟集成电路设计》课程教学大纲一、课程基本信息1、课程编码:2、课程名称(中/英文):模拟集成电路设计/ Design of Analog integrated Circuits3、学时/学分:56学时/3.5学分4、先修课程:电路基础、信号与系统、半导体物理与器件、微电子制造工艺5、开课单位:微电子学院6、开课学期(春/秋/春、秋):秋7、课程类别:专业核心课程8、课程简介(中/英文):本课程为微电子专业的必修课,专业核心课程,是集成电路设计方向最核心的专业课程之一。

本课程主要介绍典型模拟CMOS集成电路的工作原理、设计方法和设计流程、仿真分析方法,以及模拟CMOS集成电路的最新研发动态。

通过该课程的学习,将为学生今后从事集成电路设计奠定坚实的理论基础。

9、教材及教学参考书:教材:《模拟集成电路设计》,魏廷存,等编著教学参考书:1)《模拟CMOS集成电路设计》(第2版).2)《CMOS模拟集成电路设计》二、课程教学目标本课程为微电子专业的必修课,专业核心课程,是集成电路设计方向最核心的专业课程之一。

通过该课程的学习,将为学生今后从事集成电路设计奠定坚实的理论基础。

本课程主要介绍典型模拟CMOS集成电路的工作原理、设计方法和设计流程、仿真分析方法,以及模拟CMOS模拟集成电路的最新研发动态。

主要内容有:1)模拟CMOS集成电路的发展历史及趋势、功能及应用领域、设计流程以及仿真分析方法;2)CMOS元器件的工作原理及其各种等效数学模型(低频、高频、噪声等);3)针对典型模拟电路模块,包括电流镜、各种单级放大器、运算放大器、比较器、基准电压与电流产生电路、时钟信号产生电路、ADC与DAC电路等,重点介绍其工作原理、性能分析(直流/交流/瞬态/噪声/鲁棒性等特性分析)和仿真方法以及电路设计方法;4)介绍模拟CMOS集成电路设计领域的最新研究成果,包括低功耗、低噪声、低电压模拟CMOS集成电路设计技术。

模拟集成电路设计经典教材

1、 CMOS analog circuit design by P .E.ALLEN评定:理论性 90 实用性 70 编写100精彩内容:运放的设计流程、比较器、开关电容这本书在国内非常流行, 中文版也翻译的很好, 是很多人的入门教材。

建议大家读影印版, 因为 ic 领域的绝大部分文献是以英文写成的。

如果你只能读中文版,你的学习资料将非常有限。

笔者对这本书的评价并不高,认为该书理论有余,认为该书理论有余,实用性实用性不足,在内容的安排上也有不妥的地方,比如没有安排专门的章节讲述反馈, 在小信号的计算方面也没有巧方法。

本书最精彩的部分应该就是运放的设计流程了。

这是领域里非常重要的问题,像 Allen 教授这样将设计流程一步一步表述出来在其他书里 是没有的。

这正体现了 Allen 教授的治学风格:苛求理论的完整性系统性。

但是,作为一项工程技术,最关键的是要解决问题,是能够拿 出一套实用的经济的保险的方案。

所以,读者会发现,看完最后一章关于 ADC/DAC 的内容,似乎是面面俱到,几种结构的 ADC 都提到 了,但是当读者想要根据需求选择并设计一种 ADC/DAC 时,却无从下手。

书中关于比较器的内容也很精彩,器的内容也很精彩,也体现了也体现了 Allen 教授求全的风格。

教授求全的风格。

不过,不过,正好其它教科书里对比较器的系统讲述较少,该书正好弥补了 这一缺陷。

Allen 教授是开关电容电路和滤波器电路的专家。

书中的相关章节很适合作为开关电容电路的入门教材。

该书的排版、图表等书籍编写方面的工作也做的很好。

像 Allen 这样的理论派教授不管在那所大学里,大概都会很快的获得晋升吧。

另外, Allen 教授的学生 Rincon Moca 教授写的关于 LDO 的书非常详尽,值得一读。

2、 CMOS Circuit Design Layout and Simulation CMOS Mixed-Signal Circuit Design byR.J.Baker评定:理论性 80 实用性 100 编写 80精彩内容:数据转换器的建模和测量、hspice网表 这本书的风格和 Allen 的书刚好相反:理论的系统性不强,但是极为实用,甚至给出大量的电路仿真网表和 hspice 仿真图线。

模拟集成电路设计

模拟集成电路设计模拟集成电路设计是指将电子元件和电路设计应用于模拟信号的电子设计技术。

相比数字电路设计,模拟集成电路设计非常复杂,因为它以复杂的方式处理模拟信号,并且有大量的设计和实现参数,例如电源电压、输入信号电平、输出信号电平和传输函数,等等。

模拟集成电路设计的发展形式改变了电子元件与电路设计应用的历史。

模拟集成电路设计自从20世纪60年代起就开始了,有一些电子元件模型和电路技术已经形成。

此后,各种电子元件和电路技术又不断发展,使得现代模拟集成电路设计技术获得了跨越性的发展。

模拟集成电路设计通常包括多种电子元件和电路技术,例如放大器、滤波器、衰减器、可调电容器、电阻器、电感器、二极管、直流电源等。

模拟集成电路设计中的多种元件和电路技术十分复杂,需要有很强的电子技术和理论基础。

模拟集成电路设计的主要目的是实现对模拟信号进行处理,并将输入信号转换成输出信号,使信号得到有效处理。

这种设计可以解决复杂的信号处理问题,例如模拟音频信号处理、数字音频处理、数字图像处理、生物医学信号处理等。

模拟集成电路设计的常用设计工具可以分为两类,即硬件设计工具和软件设计工具。

硬件设计工具包括电路板布线工具、仿真工具和示波器等,它们用于评估电路组件的正确性和性能,并实现电路原理图设计。

软件设计工具包括模拟电路模拟器、状态器件仿真器和模拟示波器等,他们可以进行精细的模拟电路设计和分析。

综上所述,模拟集成电路设计的发展为电子元件与电路设计应用带来了极大的发展,为电子界的设计提供了有效的技术支持。

模拟集成电路设计技术仍然在不断发展,届时电子元件与电路设计应用能力将会进一步提升,可以更好地适应不断变化的电子应用环境。

模拟集成电路设计

一电路原理模拟电路广泛地包含电压基准和电流基准,这种基准是直流量,与电源盒工艺参数的关系很小,但与温度的关系式确定的。

在本章中,我们讨论在coms 技术中基准产生的设计,着重于公认的带隙技术。

首先我们研究与电源无关的偏执电路和启动问题。

接着,阐述与温度无关的基准,研究诸如失调电压的影响等问题。

最后,我们给出常数m G 偏置电路。

带隙基准利用得到的正负温度西数的电压,我们现在可以设计出一个令人呢满意的零温度系数的基准。

我们有12ln REF BE T V V V n =∂+∂,这里ln T V n 是两个工作在不同电流密度下的双极性晶体管的基极和发射极电压之差,我们如何选择呢,因为在室温下,然而,所以我们可以令,选择,使得,也就是,表明零温度系数的基准为现在让我们来设计一个完成和想家的电路,首先,如图,假设基极电流可以忽略,晶体管是由n 个并列的晶体管单元组成,而是一个晶体管单元。

假设我们用某种方法强制相等,那么,即,就可以作为与温度无关的基准。

上述电路需要作两处修改,首先,假如一种电路,保证,其次,适当增大项。

这里,放大器以为输入,驱动和的上端,使得店和店稳定在近似相等的电压。

基准电压可以再放大器输出端。

格局对图的分析,我们有,得到流过右边之路的电流为,一次输出电压为。

为了而得到零温度洗漱,必须使。

考虑到与CMOS 工艺的兼容性,我们用pnp 晶体管实现图中的电路。

带隙基准根据式子ref T V =V +ln BE V n 产生的电压被称为带隙基准,我们将输出电压写为因此得到,将此式子置为零,并用代替,我们有,如果由此式子得到,我们得到,这样额定零温度系数的电压基准就由一些基本数字给出,硅的带隙基准,迁移率的温度指数m,和热电势,因为,当T 趋于零时,所以这里使用带隙这个术语。

电源影响和启动问题在电路中,只要运放的开环增益足够高,输出电压就相对独立于电源电压,但是,如果x V 和y V 均等于零,运放的输入差动就可能会关断,所以电路可能要启动机制,我们可以增加与图所示的相似的启动技术,以保证运放在上电时能正常工作。

模拟cmos集成电路设计拉扎维第4章差分放大器ppt课件

16

差分放大器

优点

抗干扰能力强,高线性度等 和单端电路相比,差分电路规模加倍

与获得的性能提高相比,这个不算做缺点

西电微电子学院-董刚-模拟集成电路设计

17

本讲

差分放大器简介 简单差分放大器 基本差分对放大器

大信号差分特性 大信号共模特性 小信号差分特性 小信号共模特性

MOS管做负载的基本差分对放大器 差分放大器的应用-Gilbert单元

西电微电子学院-董刚-模拟集成电路设计

12

本讲

差分放大器简介 简单差分放大器 基本差分对放大器

大信号差分特性 大信号共模特性 小信号差分特性 小信号共模特性

MOS管做负载的基本差分对放大器 差分放大器的应用-Gilbert单元

西电微电子学院-董刚-模拟集成电路设计

13

差分放大器简介

AIC中非常重要的电路模块 对两个信号的差值进行放大

(V X V )Y Vin 2引起的 = g m RDVin 2

西电微电子学院-董刚-模拟集成电路设计

36

小信号差分特性-用叠加法求全差分时的 差模增益

(VX V ) = Y Vin1引起的 gm RDVin1 (VX VY )Vin 2引起的 = gm RDVin2

(VX V ) = Y Vin1和Vin2共同引起的 gmRD (Vin1 Vin2 )

Rout

=

g

1 m+ g

mb

西电微电子学院-董刚-模拟集成电路设计

10

上一章

共栅级

Rin小,Rout大

Av = gm(1+ )RD

Rin = 1/[gm (1+ )]

Rin =

RD + rO

模拟集成电路设计与分析

模拟集成电路设计与分析随着科技的不断进步,集成电路在现代电子产品中扮演着至关重要的角色。

特别是模拟集成电路,它们被广泛应用于各种电子设备中,为我们提供了更多功能和便利。

本文将介绍模拟集成电路的设计与分析过程,帮助读者了解这个领域的基本原理和实践技巧。

一、模拟集成电路设计1. 模拟电路特点模拟电路是以连续的信号为基础,通过模拟元器件实现信号的放大、滤波、调节等功能。

与数字电路相比,模拟电路更注重信号的精确度和连续性。

2. 模拟集成电路概述模拟集成电路是将各种模拟元器件(如电阻、电容、二极管、晶体管等)集成在一个芯片上,以实现更高级的功能。

它可以减小电路的体积、降低功耗,并提高信号的稳定性和抗干扰能力。

3. 模拟集成电路设计流程(1)需求分析:了解客户需求,明确电路功能和性能要求。

(2)电路拓扑设计:选择适合的电路结构,分析电路的工作原理,确定核心元器件。

(3)元器件选择:根据电路需求,选择合适的模拟元器件,并进行参数模拟。

(4)版图设计:将电路元器件进行布局,优化版图,确保电路的稳定性和可靠性。

(5)电路仿真与验证:使用电路仿真软件对设计的电路进行验证,发现并解决潜在问题。

(6)样品制作与调试:生产样品芯片,并进行实验验证和调试。

(7)量产与测试:将电路交由工厂进行批量生产,并进行质量测试和性能验证。

二、模拟集成电路分析1. 电路分析方法(1)DC分析:分析电路在直流工作状态下的电压、电流等参数。

(2)AC分析:分析电路在交流工作状态下的频率响应、增益、相位等。

(3)时域分析:分析电路中信号的波形变化和响应时间。

(4)频域分析:分析电路中信号的谱分布和频率特性。

2. 电路性能指标(1)增益:电路输出信号与输入信号之比,用于衡量电路的放大能力。

(2)带宽:电路能够工作的频率范围,通常指的是放大器的3dB带宽。

(3)失真:电路输出信号与输入信号之间的差异,失真越小表示电路工作越稳定。

(4)噪声:电路在工作过程中产生的无用信号,影响信号的清晰度和准确性。

扎维模拟CMOS集成电路设计第四章习题

I SS 1103 0.72V 4 0.383510 50 W p Cox L 3

Vout max 3 0.72 2.28V Vout , swing 2Vout max Vout min 22.28 0.673 3.214 V

Chapter 4 习题

4.11

Cox

0 ox

tox

8.851014 F / cm 3.9 7 2 3 . 835 10 F / cm 9 109 m

cm2 F 4 A nCox 350 3.835107 1 . 34225 10 V s cm2 V2 cm2 F 4 A pCox 100 3.835107 0 . 3835 10 V s cm2 V2

b. VDD 0.8V时,M 3截止,Vout 0, AV 0 VDD 0.8V时,M 3导通,M1工作在线性区,VDD ,Vout , AV 当VDD 上升到一定值时,M1进入饱和区。

VinCM 1.2V时,满足M1工作在饱和区的最小电 源电压为 VDD min VinCM VTH 1 VGS 3 1.2 0.7 1.607 2.107V

2 I D1 VGS 1 Vod 1 VTH 1 0.7 W nCox L 1 2 0.25103 0.7 0.893 V 4 1.3422510 100

VinCM min VodSS VGS 1 0.273 0.893 1.166 V

a. VinCMmin VodSS VGS1 VinCMmax VDD VGS3 VTH1

模拟集成电路设计

读书笔记

01 思维导图

03 精彩摘录 05 目录分析

目录

02 内容摘要 04 阅读感受 06 作者简介

思维导图

关键字分析思维导图

集成电路

集成电路

通过

读者

深入

大家

理论

设计

设计

模拟 能够

掌握

内容摘要

《模拟集成电路设计》是一本全面介绍模拟集成电路设计的著作,涵盖了从基础知识到高级设计 技术的各个方面。本书首先介绍了模拟集成电路的基本概念和设计流程,然后详细阐述了各种模 拟电路元件的设计和特性,包括电阻、电容、电感、二极管、晶体管等。接下来,本书深入探讨 了模拟集成电路的设计技巧,包括反馈设计、频率响应优化、噪声抑制等。本书还涵盖了模拟集 成电路的版图设计和测试方法,为读者提供了全面的设计工具。

本书的一大亮点是它的理论与实践相结合的方法。它不仅提供了大量的理论分析,还通过实例演 示了如何将理论应用到实际设计中。这种方法使得读者能够更好地理解并掌握模拟集成电路设计 的精髓。

《模拟集成电路设计》是一本非常优秀的教材,无论是对初学者还是对有一定经验的工程师来说, 都是一本极有价值的参考书籍。本书不仅介绍了模拟集成电路的基本知识和技术,还通过实例和 案例分析,使读者能够深入了解并掌握模拟集成电路设计的关键技术和实际应用。

书中另一句引人注目的话是:“在所有的电子系统中,模拟电路是心脏。” 这句话强调了模拟集成电路在电子系统中的核心地位。无论是信号的输入、放大、 处理,还是最后的输出,都离不开模拟集成电路的强大功能。

还有一句令人印象深刻的话:“模拟集成电路设计的挑战在于平衡性能、功 耗和成本。”这是对模拟集成电路设计复杂性的最好诠释。设计师需要在满足性 能要求的还要考虑功耗和成本的问题,这需要他们具备深厚的专业知识和丰富的 实践经验。

模拟集成电路设计

模拟集成电路设计模拟集成电路设计是一门非常重要的课程,它涉及到广泛的知识和技术,对学生们的未来发展很有帮助。

在当今这个电子信息化社会里,模拟集成电路设计与制造已成为我们社会发展的重要组成部分,成为当下科技发展的重要领域之一。

模拟集成电路设计涉及到多项技术,其中包括电路分析,电路设计,半导体材料,专用器件设计,电子功能分析,数字逻辑电路,多媒体技术等。

同时,还要考虑电路的反馈机制,控制系统结构以及模拟集成电路设计的数字技术。

模拟集成电路设计的主要内容包括:电路分析、电路设计、电子功能分析、布线等。

电路分析是模拟集成电路设计的基础,掌握电路分析常用的分析方法和新技术,是有效分析电路结构和性能的前提条件。

电路设计是模拟集成电路设计的核心,要掌握电子元器件、特性、技术参数,以及电路选择、设计和测试等基本知识。

电子功能分析主要是通过模拟电路、数字电路、控制系统等来进行系统分析,需要深入的理论知识,但也有很多实际上的应用。

模拟集成电路设计的布线是把电路从方案概念上转换成具体的装配布局,它要求在具体引脚位置把电路各元件接在一起,同时也要考虑抗干扰能力。

模拟集成电路设计为学生提供了对实际应用有用的技能,并增强了他们的专业实践能力,为他们的将来发展提供了有利条件,培养具备多项先进技术的人才,具备创新精神。

模拟集成电路设计的重要性可以从多方面来考虑,它不仅能够培养学生的独立思考能力、实践能力,还能够提高学生的创新意识,帮助学生们在技术领域丰富自己的知识,为未来社会发展做一些准备,更好地去面对未来发展的挑战。

总之,模拟集成电路设计是一门重要且有益的课程,它不但能够提高学生在技术上的能力,还能够帮助学生建立自己的创新意识,培养具有创新精神的人才,为未来的发展做好准备。

如果学生能够把这门课程学习好,他们将会更好地受益于自己在科技发展中获得的知识,有助于他们在未来实现自己的梦想。

《模拟集成电路设计》教学大纲

模拟集成电路设计课程教学大纲一、课程的基本信息适应对象:电子科学与技术专业本科课程代码:25E01015学时分配:64=48理论+16实践赋予学分:4先修课程:电路分析、半导体物理、模拟电子技术、信号与系统后续课程:集成电路原理与应用、集成电路工艺原理二、课程性质与任务本课程是电子科学与技术专业本科生必修的一门重要的专业课程。

通过本课程的学习,使学生掌握模拟集成电路分析与设计的基本方法,并能借助辅助设计工具对简单模拟集成电路进行仿真设计。

三、教学目的与要求通过本课程的教学,引导和帮助学生实现简单的模拟集成电路分析与设计。

本课程要求掌握模拟集成电路的分析、设计与仿真方法,内容包括集成电路器件模型、工艺与布局、镜像电流源和单级放大电路基础、噪声分析与模型分析、基本运算放大器设计、比较器、采样保持与带隙基准。

四、教学内容与安排(一)理论教学内容与安排绪论(2学时)教学内容:1、模拟集成电路设计方法、工具与流程2、模拟集成电路的工艺技术3、模拟集成电路的发展教学要求:1、本章重点了解模拟集成电路设计方法、工具与流程。

第一章集成电路器件和模型(8学时)教学内容:1、半导体和pn结2、mos晶体管3、高级mos模型4、双极结晶体管5、器件模型总结6、spice模型参数教学要求:1、本章难点在于高级mos模型的掌握;2、本章重点在于掌握spice模型参数。

第二章工艺和布局(4学时)教学内容:1、工艺和布局2、cmos工艺3、双极工艺4、cmos布局和设计准则5、模拟布局考虑教学要求:1、本章难点在于模拟布局考虑;2、本章重点在于了解cmos工艺。

第三章镜像电流源和单级放大电路基础(8学时)教学内容:1、简单cmos镜像电流源2、共源放大器3、源极跟随器或共漏放大器4、共栅放大器5、源极退化镜像电流源6、高输出阻抗镜像电流源7、共射共基增益级8、mos差动对和增益级9、双极镜像电流源10、双极增益级11、频率响应教学要求:1、本章难点在于掌握用小信号模型分析电流镜与放大器;2、本章重点在于掌握电流镜原理、COMS单管放大。

模拟集成电路设计知识点总结

模拟集成电路设计知识点总结《模拟集成电路设计知识点总结》嘿,大家好呀!今天咱就来唠唠模拟集成电路设计这个“高大上”又有点神秘的玩意儿。

说起这模拟集成电路设计啊,那可真是像搭积木一样,不过这积木可不普通,每一块都得放得恰到好处。

它就像是在创建一个微小的电路世界,各种元件相互配合,才能奏出美妙的“电流之歌”。

首先,什么是重要的呢?那肯定是器件模型啊!就像是给每个小零件都贴上一个“身份标签”,让咱知道它们的脾气和特点。

要是弄不清这个,那电路就可能变成一个“小调皮”,不听使唤咯!然后呢,还有放大器这个大主角。

它就像是电路世界里的大力士,能把小小的信号变得强大起来。

不过可要小心哦,调得不好可能就变成“软脚虾”啦。

反馈也是不能不提的。

这可真是个神奇的东西,就像是给电路加了个“自动驾驶”模式,让它能自动调整到最佳状态。

但是搞不好的话,嘿嘿,那就等着电路“晕车”吧。

在设计过程中,那可真是要眼观六路、耳听八方啊。

一会儿算电流,一会儿算电压,稍不注意就会犯迷糊。

不过没关系,咱就当是在和这些小玩意儿玩捉迷藏,多找找总能找对的。

还有啊,布线就像是在给电路画地图,得让电流能顺顺利利地跑起来,可不能让它们迷路啦。

有时候为了走好这几根线,真是绞尽脑汁,感觉头发都掉了几根。

总之,模拟集成电路设计就像是一个趣味十足但又充满挑战的游戏。

有时候会被它折磨得死去活来,但当看到自己设计的电路听话地工作时,那成就感简直爆棚!就好像自己是这个微小世界的造物主一样。

所以啊,朋友们,要是你们也对这个神秘的领域感兴趣,那就大胆地来尝试吧!别怕犯错,就把它当成一场有趣的冒险。

只要咱坚持不懈,总有一天能在这个小小的电路世界里闯出一片大大的天!哈哈,加油吧!。

模拟集成电路的设计4z24页PPT

1

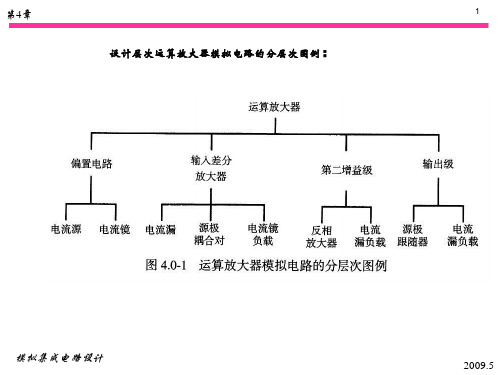

设计层次运算放大器模拟电路的分层1

4.1 MOS开关

目的: 研究与CMOS集成电路兼容的开关特性

模拟集成电路设计

2009.5

§4-1: MOS开关

一、开关模型

● 理想开关 导通时短路,关断时开路

● 实际开关

模拟集成电路设计

41

实际开关 2009.5

情况2, U=5V/10ns=5X108<2.66X109 属慢跃变, Verror=10.95mV

说明:不要期望从误差公式得到关于电荷馈通量的精确答案。 相反,它们只是帮助了解各种电路元件和端口的条件的影响, 以便在设计技术中最大限度地减少不必要的行为。

2009.5

41

§4-1: MOS开关

5.解决电荷注入的方案

2009.5

§4-1: MOS开关 4.近似电荷注入的分析表达式 假设珊极电压从VH到VL变化 所以: 定义: 又:

电荷注入引起的误差:

其中,U是vG(t)的斜率

(1 )慢跃变时

(2 )快跃变时

41

2009.5

41

§4-1: MOS开关 P98 例4.1-1 电荷馈通误差的计算

情况1: U=5V/0.2ns=25X109>2.66X109 属快跃变,Verror=19.7mV

(1)使用最小尺寸的开关,以减少重叠电容;增加CL ; (2)使用虚拟补偿晶体管;

● 需要一个互补时钟; ● 完全消除是困难的,实际上可能会在其他方面产生问题。

(3)使用互补开关;

2009.5

第1节

41

4.2 MOS二极管、有源电阻

模拟集成电路设计

2009.5

41

§4-1: MOS开关

模拟集成电路设计流程.ppt

Spectre: 由Cadence开发的电路仿真器,在SPICE的基础 上进行了改进,使得计算的速度更快,收敛性能更好。

方法一

安装并运行exeed软件, 使用putty软件(缘网下 载),在Host name处填 工作站地址,端口默认, 协议(protocol)选SSH, 如图所示,然后点击 Open。

2020/5/9

共88页

7

1、键入用户名和密码, 在提示符处键入: source/opt/demo/cds. env(回车)

2020/5/9

共88页

32

Calculator的使用

Calculator是 一个重要的数 据处理工具, 可以用来仿真 电源抑制比, 相位裕度,共

模抑制比

2020/5/9

共88页

33

其它有关的菜单项(3)

Results菜单

2020/5/9

共88页

34

模拟结果的显示以及处理

在模拟有了结果之后, 如果设定的output有 plot属性的话,系统 会自动调出waveform 窗口,并显示outputs 的波形,如左图

2020/5/9

共88页

9

二、建立可进行SPECTRE模拟 的单元文件

主窗口分为信息窗口 CIW、命令行以及主 菜单。信息窗口会给 出一些系统信息(如 出错信息,程序运行 情况等)。在命令行 中可以输入某些命令。

主菜单包括:

1、File菜单 2、Tools菜单 3、Options菜单

2020/5/9

模拟集成电路设计软件使用教程.

模拟集成电路设计软件实验教程2006年4月目录实验一自上而下(Top-Down)的电路设计 (3)Lab 1.1 启动软件 (3)Lab 1.2 自上而下的系统级仿真 (3)Lab 1.3 电路图输入 (7)Lab 1.4 模块的创建 (10)Lab 1.5 电源的创建 (12)Lab 1.6 建立运放测试电路 (14)实验二使用Spectre Direct进行模拟仿真 (17)Lab 2.1 运行仿真 (17)Lab 2.2 使用激励模板 (28)Lab 2.3 波形窗的使用 (32)Lab 2.4 保存仿真状态 (36)Lab 2.5 将仿真结果注释在电路图窗口 (37)实验一自上而下(Top-Down)的电路设计Lab 1.1 启动软件实验目的:掌握如何启动模拟电路设计环境.实验步骤:1.进入Linux界面后,点击鼠标右键,选中New Terminal,则会弹出一个交互终端.2.进入教程所在目录后,输入命令cd Artist446 (注意:cd后必须有空格;命令行大小写敏感)3.在同一个交互终端内,输入命令icms &,在屏幕底部会出现一个命令交互窗(Command Interpreter Window,CIW).如果出现What’s New窗口,可使用File-Close命令关闭.Lab 1.2 自上而下的系统级仿真实验目的:掌握如何对含AHDL模块的模块级设计进行仿真.实验步骤:1.在CIW中选择Tool-Library Manager,会弹出库管理器(Library Manager).2.在库管理器中,用鼠标左键选中training,则cell中会显示出training库中所有的cell;在training的所有cell中用左键选中peakTestv;用鼠标中键(或右键)打开(open)view 中的schematic.将会出现如下图所示的测试电路:3.将鼠标置于图中peakDetectv模块上,当该模块四周出现一高亮黄色虚线框时,点击左键选中该模块,则模块四周线框变为白色实线框.4.选择Design-Hierarchy-Descend Edit,弹出Descend对话框,将View Name设置为schematic,然后点击OK.则出现peakDetectv模块的电路图:阻和nmos器件,所有其余的器件都是用Verilog-A(一种模拟HDL语言)编写的.使用Verilog-A语言支持自上而下的设计方法.5.选中peakDetectv电路图中的Ampv模块,Design-Hierachy-Descend Edit,在Descend对话框中将View Name设置为veriloga,点击OK.将出现文本编辑窗,可对窗内的文本进行编辑.退出该编辑窗可敲击键盘左上角的Esc键,然后在文本编辑窗中输入:q!,回车即可.6.在电路图窗口选择Tool-Analog Environment,弹出模拟设计环境仿真(AnalogDesign Environment Simulation)窗口,同时可再次弹出peakTestv电路图.7.在该仿真窗口中选择Setup-Simulator/Directory/Host;在随后出现的ChoosingSimulator对话框中,将仿真器(Simulator)设置为spectre,点击OK.8.在该仿真窗口中选择Setup-Model Libraries,弹出模型库建立(Models Library Setup)对话框;如图,在该对话框的Model Library File中如图输入后,点击Add,然后OK.9.在该仿真窗口中,点击Choose Analysest图标,弹出Choosing Analyses框;如图所示,选择tran和Enabled,截止时间写入390u;然后点击OK10.如步骤4所示,打开peakDetectv的电路图,并在仿真窗口中选择Outputs-To BePlotted-Select On Schematic.按照电路图窗口底部的命令行提示,左键选中图中与标有vinput,vcap和vcontrol的管脚相连的连线,这些被选中的连线会以特殊的颜色显现出来.11.将鼠标置于电路图窗口中,点击Esc键.注意在仿真窗口输出部分的更新信息是否如下图所示:信号vcontrol的名字是I54/vcontrol.12.在仿真窗口中选择Simulation-Netlist and Run开始仿真,或者可以点击右侧Netlist and Run图标,仿真成功后会自动输出如下曲线:13.退出仿真窗口,选择Session-Quit.14.退出电路图窗口,选择Windou-Close;在弹出的Save Change框中点击No.15.在被仿真环境激活的窗口中,选择File-Close Window,退出仿真环境.Lab 1.3 电路图输入实验目的:掌握如何创建一个库,如何创建一个双极CMOS(Bi-CMOS)运算放大器.实验步骤:1.在CIW窗口中,选择File-New-Library;在弹出的New Library框中,确认Directory下的路径被设置为~/Artist446(~可以被扩展为绝对路径),并选择Don’t need a techfile,如图所示:2.点击OK.并在库管理器窗口中确认mylib库已经列入其中.3.在CIW或库管理器中选择File-New-Cellview,如下图所示建立新文件:4.点击OK.弹出一个空白的电路编辑窗口,用于下面步骤中放大器设计图的输入5.在该电路编辑窗口中,点击左侧的Instance图标,弹出添加器件(AddInstance)对话框.确认框中的View Name设置为symbol.按照下面表格输入欲添加器件的器件参数,并点击左键将器件置于图中适宜位置.或可使用框中Browse键添加器件.Library Name Cell Name PROPERTIES/COMMENTSanalogLib pnp For Q2,Q3,Q4:Model Name=trpnp(no quotes) analogLib npn For Q0,Q1:Model Name=trnpn(no quotes) analogLib pmos4 For M1:Model Name=trpmos(no quotes)Length=8u,Width=iPar("l")*16analogLib pmos4 For M3:Model Name=trpmos(no quotes)Length=iPar("w")/16,Width=128uanalogLib nmos4 For M2,M5:Model Name=trnmos,Width=100u,Length=10uanalogLib res Resistance=2.5KanalogLib cap Capacitance=CAP(Design Variable)analogLib vdd,vss如果参数值设置错误,可采用Edit-Properties-Objects进行修改;如果器件放置位置不当,可采用Edit-Move命令加以调整.6.器件放置完毕后,点击器件添加对话框中的Cancel键,或鼠标置于电路图窗口中时敲击Esc键.7.点击电路图窗口的添加管脚图标,弹出添加管脚(Add Pin)对话框;严格按照顺序依次输入管脚名称(各名称间需留有空格),Direction设置为input,Usage设置为schematic,如下图所示:用左键将管脚置于图中合适位置(可使用右键调整管脚方向).8.点击细连线图标,并用左键完成器件间连线.点击命令选项图标或F3调整连线参数(建议将Draw Mode设置为route,将Route Method设置为full);连线完毕后,将鼠标箭头置于电路图中,敲击Esc键即可退出连线模式.9.点击添加连线名称图标,在添加连线名称对话框中依次输入连线名称vdd!gnode(之间需留有空格),用左键在电路图中添加连线名称.vdd!添加到M1和M2基极连线上,gnode添加到M5和M2的栅极连线上(注:标有!代表为全局变量).将鼠标箭头置于电路图中,敲击Esc键即可退出添加连线名称模式.10.最终可得电路图如下图所示:11.点击左侧检查并存图图标.观察CIW的输出区域(如下图所示)表明无错误,并已正确存图.Lab 1.4 模块的创建实验目的:掌握如何为一个双极CMOS(Bi-CMOS)运算放大器创建模块.实验步骤:1.在运放的电路图中选择Design-Create Cellview-From Cellview,弹出CellviewFrom Cellview对话框.激活对话框中的Edit Options选项后,可对模块的外观进行调整.2.确认From View Name设置为schematic,To View Name设置为symbol,Tool/DataType设置为Composer-Symbol.如下图所示:3.点击OK.弹出模块生成(Symbol Generation)对话框,并在该框内进行管脚规格的调整.如下图所示:4.点击OK.一个新的窗口内会自动生成一个放大器模块,如图:(图a)观察CIW输出框,可知一个模拟器件描述格式(analog Component Description,CDF)已经生成.可进一步将上图中的模拟器件外观调整为如下图中所示:(图b)5.左键选中图a中绿色矩形框,点击删除图标;选择Add-Shape-Polygon,按照电路图底部的提示,在图中画上三角形外观.如果对所画线条不满意,可使用Backspace键删除刚画出的最后一条线.画完最后一笔时,双击鼠标左键即可完成画图.6.点击电路图窗口中的移动(Move)图标,并将inp管脚移至图b中所示位置.再用类似方法移动inm和iref管脚.7.用Edit-Rotate命令,按照电路图底部的提示旋转iref标签,并用Move移动到合适的位置.8.左键选定标签cdsParam(3)并删除.9.左键选中整个红色矩形框,并删除.10.点击Selection Box图标,或选择Add-Selection Box.在Add Selection Box对话框中点击Automatic,则自动添加生成一个红色选择框.11.选择伸展(Stretch)图标,调整iref管脚的长度以适合新的选择框.可能需要再次移动iref和cdsTerm(“iref”)标签.12.利用shift键,同时选中cdsParam(1)和cdsParam(2)标签,并将它们移到图b中所示的位置.13.将cdsName()标签移到图b所示位置.14.可选择Add-Note-Note Text在电路图中添加必要的说明文档.Lab 1.5 电源的创建实验目的:掌握如何创建一个电源来为电路供电实验步骤:1.在CIW或库管理器中选择File-New-Cellview,建立如下对话框:2.点击OK.弹出一个空白电路图编辑窗用于输入电源设计电路.3.在电路图编辑窗中,选择Design-Create Cellview-From Cellview,在弹出的Cellview From Cellview框中点击OK;弹出”模块生成选项”(Symbol Generation Options)框. 如下图所示,在Top Pins后填入VDD VSS后点击OK.4.注意观察CIW输出信息表明一个模拟CDF已经生成.同时弹出的窗口中显示出生成的电源模块.如下图:5.将上图调整为如下图所示,并在编辑完成后保存(Save)模块;选择Window-Close退出电路图编辑窗即可.Lab 1.6 建立运放测试电路实验目的:用双极CMOS(Bi-COMS)运算放大器建立一个运放测试电路实验步骤:1.在CIW或库管理器中选择File-New-Cellview,弹出”创建新文件”(Creat New File)框,并在进行如下设置后点击OK:2.在弹出的空白电路编辑窗中将建立一个增益为3的运放,具体器件参数见下表: Library Name Cell Name PROPERTIES/COMMENTSmylib amplifiermylib supply VDD=5,VSS=-5analogLib vsin For V2:AC Magnitude=1,Amplitude=50m,Frequency=1M,Offset voltage=0analogLib idc For 14:DC current=500uanalogLib res For R1:Resistance=20KanalogLib res For R0:Resistance=10KanalogLib vdd,vss得到如下电路图后保存::实验二用Spectre Direct进行模拟仿真Lab 2.1 运行仿真实验目的:对运放测试电路进行仿真实验步骤:1.在运放测试电路的电路编辑窗中选择Tools-Analog Environment,弹出模拟电路设计环境仿真窗(Analog Circuit Design Environment Simulation)2.在仿真窗中选择Setup-Simulator/Directory/Host,确认弹出框中Simulator后设置为spectre后,点击OK.3.选择Setup-Simulation Files, 确认弹出框中的Include Path后设置为./Model,如下图所示:可以加入更多的路径,只要在各路径之间插入空格即可.4.在仿真窗口中,选择Setup-Model Libraries,弹出模型库建立(Model LibrarySetup)菜单;在该菜单中如下图所示,在Model Library File中输入myModels.scs5.点击Add,则刚刚输入的路径转移到上面的框中.若想查看这个模型文件的文件内容,则选中该文件,并点击Edit File.如下图所示:弹出文件内容如下:使用”Esc : q! 回车”或File-Close均可退出该文件编辑窗.在Simulation Files Setup框中点击OK,完成模型库的建立.6.在仿真窗中,点击选择分析图标,弹出”选择分析”(Choosing Analyses)框.7.为进行瞬态分析(Transient Analysis)进行如下设置,如下图:1.在Analysis后选择tran;2.在Stop Time后设置为3u;3.选中Enabled;4.点击Apply.8.为进行交流分析(AC Analysis)进行如下设置,如下图:a.在Analysis后选择ac;b.在Sweep Variable下选择Frequency;c.在Sweep Range下选中Start-Stop,并将扫频范围设置为100-200M;d.将Sweep Type设置为Logarithmic,选中Points Per Decade后,设置参数为20;e.选中Enabled;f.点击Apply.9.为进行直流分析(DC Analysis)进行如下设置,如下图:a.在Analysis部分选择dc;b.在DC Analysis部分,激活Save DC Operating Point;c.激活Enabled;10.在Choosing Analyses框中点击OK,完成设置.11.在仿真窗中点击编辑变量(Edit Variables)图标,弹出编辑设计变量(Editing Design Variables)框.12.点击该框底部的Copy From键,软件会自动对整个电路设计进行扫描,把找到的所有变量都列在Table of Design Variables下;(如下图所示)13.在运放设计电路图中找到CAP变量a.左键选中Teble of Design Variables中的CAP变量后,点击Find(如上图所示)发现图中的运放已被高亮矩形框选中;b.选择Design-Hierarchy-Descend Editc.在弹出框中将View Name设置为schematic,然后点击OK;则弹出运放的电路图结构;d.再次点击上图中的Find,会看到图中的电容器件已被矩形高亮框选中,即已经在图中找到CAP变量;e.Design-Hierarchy-Return命令,返回到上层运放测试电路图14.设置CAP变量的值:如上图所示,选中CAP变量,在Value后输入0.8p;然后点击Change(注意Teble of Design Variables中的参量更新)15.点击框底部的Copy to,将刚刚设置的值写回电路图中;保存,将该值存在电路图中;16.点击上图框中的OK或Cancel;在运放测试电路中点击Check and Save,保存设置;17.在仿真窗中选择Outputs-Save All,弹出保存选项(Save Option)框;确认”选择保存输出信号”(Select signals to output(save))为allpub后,点击OK.如下图所示:18.在仿真窗口中通过Outputs-To Be Saved-Select On Schematic,选择保存特定终端的电流值.注意运放测试电路图窗口底端的提示.19.在电路图中点击20K反馈电阻两端,电阻两端被椭圆圈出,表明通过该处的电流值将被保存下来20.鼠标位于电路图窗中时,敲击Esc,退出选择状态.21.选择Outputs-To Be Plotted-Select On Schematic,按照电路图窗口底部的提示选中标有vin和out的结点.22.鼠标位于电路图窗中时,敲击Esc,退出选择状态.注意仿真窗口中的输出部分的信息更新,如下图所示:23.在仿真窗中,选择Simulation-Netlist-Create.弹出一个显示分层网表的窗口.注意你输入的所有变量和仿真设置在网表中是如何描述的.如果在生成网表的过程中遇到错误,可查看CIW中的输出信息,检查输入的所有数据是否正确.24.若对电路图加以改动,则要重新生成新的网表Simulation-Netlist-Recreate.25.选择File-Close Window关闭网表窗口.26.在仿真窗中选择Simulation-Run,或点击窗口右侧的运行(Run)图标开始仿真.(可以选择Simulation-Netlist and Run或点击Netlist and Run图标,生成网表并仿真)当仿真开始时,在CIW窗口中有信息出现,同时,弹出一个独立的Spectre输出窗口,如下图:可通过File-Close Window关闭这个窗口.27.当仿真结束后,瞬态响应图和交流分析图自动弹出:28.在仿真窗中选择Session-Save State,弹出保存状态(Saving State)框;将Save As设置为state1,并且确认在What to Save后的所有选项均已被选中.29.点击OK,仿真器的状态被保存下来.30.如下图所示,用control键同时选中ac和dc,选择Analyses-Disable.可发现ac和dc后面变为”no”,而tran后仍为”yes”31.双击上图中tran所在行,弹出选择分析(Choosing Analyses)框;点击框底部的Options,弹出瞬态选项(Transient Options)框.将TIME STEP PARAMETERS下的maxstep设置为100p32.点击Apply.33.选择Simulation-Run或点击Run图标,开始仿真.在Spectre的输出窗口中,当看到第一个仿真时间点时点击波形输出图标或选择Result-Plot Outputs-Transient,输出当时的图像;再次点击波形输出图标,观察更新后的输出图像.仿真结束后,波形窗中显示出3u的仿真数据,如下图:注意:当仿真结束后,要将设置的最大步长100p删除,点击Apply或OK.点击Cancel 关闭Choosing Analyses框.34.在仿真窗中选择Session-Load State;在弹出的Loading State窗中State Name后选择state1;使What to Load下的Waveform Setup失效;点击OK.35.在运放测试电路图编辑窗中,选择Design-Probe-Remove All,删除所有可能残留的标记仿真结果的彩色探针.36.File-Close Window关闭仿真输出窗口.37.保留仿真窗口,波形窗口和所有其他的设计窗口不变.Lab 2.2 使用激励模板实验目的:使用图形激励模板为运放测试电路提供激励实验步骤:1.将运放测试电路的左侧部分调整为如图所示,并检查并保存会看到一条警告信息出现在电路图检查框(Schematic Check box)中.注意电路编辑窗中的闪烁标志,这些标志提示未连接的终端.暂时忽略警告信息,点击Close关闭该窗口.2.设置输入激励.在仿真窗中,选择Setup-Stimuli,弹出建立模拟激励(Setup Analog Stimuli)框.确认框中的Stimulus Type设置为Inputs,并按照下图进行参量设置:3.设置全局激励.设置Stimulus Type为Global Sources; 分别设置vdd和vss为直流5v,-5v;设置完毕后点击OK.如下图:4.在仿真窗中选择Simulation-Netlist-Recreate.生成网表.选择File-Close Window关闭网表.5.选择Simulation-Run或开始仿真,仿真结束后自动弹出波形窗口:6.将电路图复原到原状态时,若不关闭刚刚创建的激励,则它将和原电路图中的电源并列而出错.所以,选择Setup-Stimuli,在弹出的窗口中将所有的激励输入改为OFF,点击Apply和OK.7.将电路图恢复为如图所示,并点击检查并保存:8.在运放测试电路编辑窗中选择Design-Probe-Remove All,删除所有可能残留的标记仿真结果的彩色探针.9.在运放测试电路编辑窗中选择Simulation-Netlist-Recreat,弹出网表.选择网表窗中的File-Close Window关闭该网表.10.选择Simulation-Run或点击,仿真结束后出现波形如下:如果出现错误信息,检查是否由于某些图形激励仍然处于激活状态(ON).11.关闭仿真输出窗,保留仿真窗,波形窗和所有其他设计窗口.Lab 2.3 波形窗的使用实验目的:研究波形窗的特点及使用实验步骤:1.左键点击子窗口1的数字1,使之高亮显示,再选择Axis-Strips;同样方法对子窗口2进行处理,得到图形如下:2.选择Trace-Delta Cursor调出测量标尺,并注意观察波形图下方的数字显示:3.左键双击子窗口右上角的数字,调出图形属性(Graph Attributes);在此框中可进行图形标题和子标题的设置,对坐标系外观进行调整等操作.4.双击Y轴图标(V)或Axes-Eidt,调出Y轴属性框,可对Y轴属性进行编辑;同理,可双击X轴图标freq(HZ)或Axes-Eidt,调出X轴属性框,可X轴属性进行编辑.5.直接输出增益和相位曲线:a.在仿真窗口中,选择Result-Direct Plot-AC Magnitude & Phaseb.按照运放测试电路编辑窗底部的提示,选择图中标有out的结点,保持鼠标置于电路编辑窗中,敲击Esc,弹出增益和相位曲线波形.6.保存仿真结果:在仿真窗中,选择Result-Save;在弹出的保存结果(Save Result)框中仅做如下改动即可点击OK:仿真结果保存在名为original.CAP的目录下.7.更新设计变量并再次仿真:a.双击仿真窗口中Design Variables中的CAP,在弹出的编辑设计变量(EditingDesign Variables)框中将值改为0.4pb.点击Apply & Run SimulationCAP的值更新后,在不生成网表的情况下仿真,因此速度会有所提高.c.点击编辑设计变量(Editing Design Variables)框中的Cancel.d.在仿真窗中,选择Result-Save,进行如图更新设置后点击OK8.载入以前仿真的结果并比较a.在仿真窗口中选择Result-Selectb.在结果选择(Select Result)窗中,左键双击original.CAP CAP=0.8pF或选中该项后点击OK仿真窗的底部信息表明original.CAP目录中的数据已经载入到仿真环境中了Lab 2.4 保存仿真状态实验目的:掌握如何保存并恢复一个设计和仿真窗口的状态实验步骤:1.在CIW窗口中,选择Option-Save Defaults.2.如图设置Save Defaults内容后,点击OK:3.在Cadence软件运行过程中载入一个默认文件,可在CIW中输入envLoadFile(“~/.cdsenv”)4.在CIW窗口中,选择Option-Save Session.在弹出的Save Session框中不做任何改动,点击OK即可将系统状态保存在特定文件中了.5.恢复系统状态:a.在CIW中,选择File-Exit退出设计状态.b.在交互界面中输入cd ~/Artist446c.再在同一个交互界面中输入icms –restore cdsSession.save &可发现CIW,设计窗,仿真窗和波形窗都复原到屏幕上原来的位置.6.在恢复的环境中运行仿真:选择Simulation-Run或Run开始仿真;CIW中的结果报告表明仿真成功,瞬态和交流响应的波形以自动弹出.7.将所有的仿真窗和运放测试电路窗口保持不变.Lab 2.5 将仿真结果注释在电路图窗口实验目的:掌握如何将仿真结果注释在电路图窗口实验步骤:1.从顶层运放测试电路进入运放内部电路,在仿真窗中选择Results-Annotate-DC Operating Points,则所有的静态工作点都注释在每一个器件的旁边,如下图:2.将静态工作点输出到一个独立的窗口中:a.在仿真窗中,选择Result-Print-DC Operating Point;b.按照电路窗底部的提示选中npn输出晶体管,则结果显示窗中输出所选晶体管的静态工作点c.选中图中电阻,观察结果输出窗口中的变化d.注意该结果输出窗口中菜单条中的三个命令:Window,Expressions和Info;使用这些命令可以保存数据,打印数据,重定数据格式并打印,重命名.e.选择Window-Close关闭结果输出窗口.f.鼠标置于电路图窗口中,敲击Esc直到在工具提示行中不再有信息出现3.返回电路顶层运放测试电路;在Save Change对话框中点击No.。

模拟集成电路设计

模拟集成电路设计

模拟集成电路设计是当今科技发展的必备技能,它是将模拟电路元件、电路模拟设备和电路分析工具,结合起来组成一个完整的模拟电路设计系统。

如今,模拟集成电路设计是许多电子产品开发及其应用活动的基础而被广泛应用于不同领域,为电子技术的发展起到了重要作用。

模拟集成电路设计的基本流程主要分为以下几个方面:

第一,电路设计。

包括设计电路拓扑、进行电路分析、仿真设计、选择元件、建模仿真、分析结果验证等步骤。

第二,仿真环境的准备。

仿真环境的准备是仿真的基础,其目的是在模拟环境中搭建相应的仿真模型,以便可以将模拟电路仿真出来。

第三,电路参数测试。

这一步是设计过程中最关键的一个步骤,要根据电路设计结果,测试电路内部参数,如时间延迟、静态失真等,了解电路工作状态;

第四,验证及优化。

完成上述步骤后,进行模拟电路验证,确保各参数符合要求,确保电路工作稳定,如果不符合要求,可以进行相应的优化,以获得满意的设计结果。

模拟集成电路设计不仅需要有基础的电路知识,更需要具备一定的分析能力和分析工具。

此外,还要对现有元件、模拟工具、数据库等进行熟悉,具备良好的产品开发流程,才能让模拟设计更有效率。

同时,模拟集成电路设计系统日益复杂,需要不断学习新的设备、工具和技术,以确保设计的有效性和可靠性。

总的来说,模拟集成电路设计在电子设备的各个阶段开发中都起到了重要的作用,不仅是设计人员应拥有的重要技能,更是未来电子产品发展的基石。

因此,应该积极探索新技术,不断完善模拟设计方法,以满足电子技术的日益发展。

模拟集成电路设计教学大纲

模拟集成电路设计教学大纲目录一、课程开设目的和要求2二、教学中应注意的问题2三、课程内容及学时分配2第一章模拟电路设计绪论2第二章MOS器件物理基础2第三章单级放大器3第四章差动放大器3第五章无源与有源电流镜3第六章放大器的频率特性3第八章反馈3第九章运算放大器3高级专题3四、授课学时分配4五、实践环节安排4六、教材及参考书目5课程名称:模拟集成电路设计课程编号:055515英文名称:Analog IC design课程性质:独立设课课程属性:专业限选课应开学期:第5学期学时学分:课程总学时___48,其中实验学时一-一8。

课程总学分--3学生类别:本科生适用专业:电子科学与技术专业的学生。

先修课程:电路、模拟电子技术、半导体物理、固体物理、集成电路版图设计等课程。

一、教学目的和要求CMOS模拟集成电路设计课程是电子科学与技术专业(微电子方向)的主干课程,在教学过程中可以培养学生对在先修课程中所学到的有关知识和技能的综合运用能力和CMOS模拟集成电路分析、设计能力,掌握微电子技术人员所需的基本理论和技能,为学生进一步学习硕士有关专业课程和日后从事集成电路设计工作打下基础。

二、教学中应注意的问题1、教学过程中应强调基本概念的理解,着重注意引导和培养学生的电路分析能力和设计能力2、注重使用集成电路设计工具对电路进行分析仿真设计的训练。

3、重视学生的计算能力培养。

三、教学内容第一章模拟电路设计绪论本课程讨论模拟CMOS集成电路的分析与设计,既着重基本原理,也着重于学生需要掌握的现代工业中新的范例。

掌握研究模拟电路的重要性、研究模拟集成电路以及CMOS模拟集成电路的重要性,掌握电路设计的一般概念。

第二章MOS器件物理基础重点与难点:重点在于MOS的I/V特性以及二级效应。

难点在于小信号模型和SPICE模型。

掌握MOSFET的符号和结构,MOS的I/V特性以及二级效应,掌握MOS 器件的版图、电容、小信号模型和SPICE模型,会用这些模型分析MOS电路。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

5

6

4.1.3 second order low-pass H(s) with real poles

Here, w0 is the resonant or pole frequency and Q the quality factor, K the DC gain of H(s).

Equating yields

3

4.1.2 First order circuits

It is a first-order low-pass transfer function. It arises naturally when a resistance and capacitance are combined. It is often used as a simple model of more complex circuits, such as OpAmp.

t

Chapter 4 Figure 10

Chapter 4 Figure 09

11

4.2. Frequency response of elementary circuits

Small-signal analysis is implicitly assumed as only linear circuits can have well-defined frequency response. The procedure for small-signal analysis remains the same as that in Chapter 3 for single-stage amplifiers, however parasitic capacitance are now included.

18

Miller effect applied to CS amplifier

Miller effect allows one to quickly estimate the 3dB bandwidth in many cases.

Chapter 4 Figure 14

Chapter 4 Figure 18

12

4.2.1 High frequency small-signal model

Chapter 4 Figure 11

Chapter 4 Figure 12

13

4.2.2 Common-source amplfier

Note: assumed that Q1, Q2 are in active mode.

19

4.2.4 Zero-value time constant method

Except Miller effect, the most common and powerful technique for frequency response analysis of complex circuits is the zero-value time constant analysis method. It is very powerful in estimating a circuit’s 3dB bandwidth with minimal complication and also in determine which nodes are most important.

Generally, the approach is to calculate a time-constant for each capacitor in the circuit by assuming all other capacitors are zero, then sum all time constants to estimate the 3dB bandwidth. Detailed procedure:

Then, need to make sure that all transistors are in active region

23

Design example 4.12 (page 178)

Chapter 4 Figure 13

In this example, the load capacitance is very large and source resistance is small, so C2 may become a major limitation of thee plot

Chapter 4 Figure 04

9

4.1.5 Second-order low-pass H(s) with complex poles

Recall

Subt. In

10

4.1.5 Second-order low-pass H(s) with complex poles

Today’s topic: frequency response

Chapter 4

1

Small-signal analysis applies when transistors can be adequately characterized by their operating points and small linear changes about the points. The use of this technique has led to application of frequency-domain techniques to the analysis of the linear equivalent circuits derived from small-signal models. The transfer function of analog circuits to be discussed can be written in rational form with real-valued coefficients, that is as a ratio of polynomials in Laplace Transform variable s,

20

Example 4.9 (page 174)

Chapter 4 Figure 14

The same as obtained previously

21

Design example 4.11 (page 177)

Chapter 4 Figure 13

In this example, the load capacitance is modest and source resistance is high, so Cgd1 may become a major limitation of the bandwidth. This means that W1 should be small. So, given a current, Veff1 has to be relatively large: choose Veff1 to be 0.3V Then suppose L1<<L2 so that rds2>>rds1 so R2=rds1 and A0=-gm1rds1

22

Design example 4.11 (page 177)

Then solve L1 to be Then note that increasing drain current of Q1 while keeping Veff1=0.3V will increase gm1 and reduce rds1 roughly in proportion, which results in about the same gain, but a smaller R2 is achieved which increase 3db bandwidth. So, bandwidth is maximized by maximizing the drain current of Q1.

Then, we can compute the required gate width

To ensure L2>>L1, we can take L2=3L1=0.72μm Then, we can arbitrarily and conveniently set W2=3W1 Finally, Q3 is sized to provide the desired current mirror ratio

1. The step response in this case has sinusoidal term whose envelope exponentially decays with a time constant equal to the inverse of real parts of poles, 1/wr=2Q/w0. 2. A system with high Q factor will have oscillation and ringing for some time. The oscillation frequency is determined by the imaginary parts of the poles. 3. In summary, when Q<0.5, the poles are real-valued and there is no overshoot. The borderline case Q=0.5 is called maximally-damped response. When Q>0,5, there are overshoot and ringing.

24

Design example 4.12 (page 178)

rds=2rds1

Chapter 4 Figure 13

25

Comments

The above two design examples illustrate the manual analysis to provide an initial design solution, which thereafter needs to be refined iteratively using simulation. A number of challenges here: 1. there is no guarantee that the initial solution is valid or good; 2. the refinement may take many many iterations until a good design is achieved; 3. at each iteration, what are not working or good in the circuit, what parameters to modify, and how to modify them requires in depth understanding of analog circuits. What about those cases when it is hard to decide which capacitance dominates? Experience counts here, after you had many designs and were aware of the biasing conditions, capacitance conditions?