高速PCI总线接口卡的开发

pci-e 标准

pci-e 标准PCI-Express(Peripheral Component Interconnect Express)标准PCI Express(Peripheral Component Interconnect Express)是一种高速串行接口标准,用于计算机内部的外部设备连接。

它是一种用于连接扩展卡的总线,通常被用于图形卡、网络卡、声卡等设备的连接。

本文将介绍PCI-E标准的背景、工作原理和应用领域。

一、背景在早期计算机系统中,使用的是PCI(Peripheral Component Interconnect)标准。

然而,随着计算机性能的提升和需求的增加,PCI标准逐渐无法满足高性能设备的需求。

因此,PCI-SIG(PCI Special Interest Group)组织开发了PCI Express标准,以提供更高的数据传输速率和更好的可扩展性。

二、工作原理PCI Express采用串行数据传输方式,相比于并行传输方式,具有更高的速度和可靠性。

它使用一对差分信号线进行通信,其中一个线对应发送数据,另一个线对应接收数据。

通过使用差分信号,可以减少传输过程中的干扰和信号损失。

PCI Express的数据传输速率通常以“x”倍数来表示,比如PCI-E x1、PCI-E x4等。

每个PCI Express通道能够提供一定宽度的数据传输,通常为一个数据轴(lane),数据轴可以传输一个或多个数据字节。

数据轴的数量越多,数据传输速度越快。

PCI-E还引入了数据包和虚拟通道的概念。

数据包是数据传输的基本单位,包括有用数据和控制信息。

虚拟通道可以将传输数据进行分组,以提高并发性和可扩展性。

三、应用领域PCI Express标准已经成为现代计算机系统中设备连接的主要标准之一。

以下是PCI Express在不同应用领域的应用情况:1. 图形卡:PCI Express x16接口被广泛用于连接高性能显卡,以满足对图形处理性能的需求。

基于PCI Express总线的高速数据传输卡设计.

基于PCI Express总线的高速数据传输卡设计地面测控系统由上位机软件、工业控制计算机、地面控制台及相应电缆网组成。

在系统联试前它可以和采编器、存储器构成闭环反馈,对采编器、存储器实施自检。

地面控制台在上位机软件的控制下,真实模拟机上接口信号,为采编器提供不同的数字量信号,并对回收后的存储器进行数据的读取分析。

以前地面测试系统中的上位机软件系统和地面控制台之间的通信是由USB接口来完成的,传输速率较低。

为了解决大容量数据高速读取的瓶颈问题,采用P地面测控系统由上位机软件、工业控制计算机、地面控制台及相应电缆网组成。

在系统联试前它可以和采编器、存储器构成闭环反馈,对采编器、存储器实施自检。

地面控制台在上位机软件的控制下,真实模拟机上接口信号,为采编器提供不同的数字量信号,并对回收后的存储器进行数据的读取分析。

以前地面测试系统中的上位机软件系统和地面控制台之间的通信是由USB接口来完成的,传输速率较低。

为了解决大容量数据高速读取的瓶颈问题,采用PCI Express总线来读取数据。

PCI Express 采用了目前业内流行的点对点串行连接, 每个设备都有自己的专用连接, 不需要向整个总线请求带宽, 而且可以把数据传输率提高到一个很高的频率, 达到 USB 所不能提供的高带宽。

本文设计并实现的数据传输卡基于PCI Express总线,提高了系统的读写速度,满足了目前大容量高速实时传输记录的要求。

1 系统结构地面控制台是模拟机上信号源功能,信号源由上位机生成,然后下载到地面控制台的RAM中。

为了正确地发送信号源数据需要对下载的信号源数据进行自检,即将地面控制台RAM中的数据读入上位机来验证控制台中信号源是否正确。

本系统通过PCI Express传输卡实现了信号源自检功能。

如图1所示,上位机通过PCI Express接口将信号源的数据下载到FIFO1存储器当中,同时将相应的控制命令发送给FPGA。

FPGA检测到相应控制命令后,开始读取FIFO1中的数据,并将该数据经过串并转换写到地面控制台RAM中。

基于FPGA结构高速PCIe总线传输系统设计与实现

参考内容

基本内容

在现代计算机系统中,快速、高效的数据传输是至关重要的。直接内存访问 (DMA)是一种可实现这一目标的技术,其允许特定设备直接从内存中读取或 写入数据,而无需通过CPU进行干预。如今,基于FPGA(现场可编程门阵列) 的PCIe(Peripheral Component Interconnect Express)总线接口的DMA 传输设计已被广泛应用于高速、高效率的数据传输。

二、基于FPGA的PCIe总线接口的 DMA传输设计

基于FPGA的PCIe总线接口的DMA传输设计主要涉及两个关键部分:FPGA和DMA 控制器。

1、FPGA

在DMA传输设计中,FPGA被用作PCIe总线接口的实现。FPGA接收来自PCIe总线 的数据,并将其存储在内部RAM中。此外,FPGA还负责管理数据的传输过程, 包括数据的打包、解包、校验以及错误检测等。

系统设计:

基于FPGA结构高速PCIe总线传输系统的设计主要分为硬件设计和软件设计两 个部分。首先,硬件设计方面采用了高性能的FPGA芯片和相应的接口电路,以 确保数据传输的速度和稳定性。同时,为了提高系统的可靠性,采用了冗余设 计和故障检测技术。

其次,软件设计方面,通过对PCIe总线协议的研究和分析,采用了符合协议规 范的驱动程序和数据传输算法,以保证数据传输的正确性和实时性。此外,为 了提高系统的可维护性和可扩展性,采用了模块化和分层的设计方法。

系统测试与评估

为验证本次演示所设计高速数据采集系统的性能,我们进行了相应的测试。测 试结果表明,该系统的数据传输速度可达1000 MB/s,数据采集精度为12 bits,采样率可达1 GS/s,能够满足大多数高速数据采集应用的需求。评估 结果表明,本次演示所设计的高速数据采集系统在性能和稳定性方面具有一定 的优势。

高速电机控制领域的PCI总线的数据采集卡设计

地实 现 , 又要 考 虑 其 适 宜 的 价 格 。

21 P 总线 接 口芯 片 P 9 5 CI CIO 2和 H 9 L 6串行 E P OM T 3 C4 E R

P 95 CI0 2是 一 种 专 用 的 P 总 线 接 口芯 片 ,它 实 现 了 P CI CI 规范 所 有 的硬 件 接 口信 号 和 配置 空间 寄存 器 ,能 够 减 少 开 发 的 时 间 和成 本 ,并 获得 较好 的数 据 传 输 性 能 ,并 且 该 芯 片 功 能 强 大 , 户接 口简 单 。 用 P 95 CI 2的工 作 模 式 有 复用 模 式 、 复 用 模 式 、 A 接 口模 0 非 I S 式 , 文 的数 据 采 集 卡 采 用 了 非 复 用 模 式 , 模 式 下 主要 的管 脚 该 该

引线 信 号 如 图 2所 示 。

/ 、、

采 集 卡 的 基本 结构 如 图 1所 示 , 用 P ) O 2作 为 接 口芯 使 L( 5 9

片实 现 与 P 总 线 的 连 接 , 块 E P OM 对 9 5 CI 一 E R 0 2进 行 初 始 化

益霹

兽

。

掰

’ R

维普资讯

高 速 电 机控 制 领 域 的 P 总线 的数 据 采 集 卡设 计 CI

高速电机控制领域的 P C 总线的数据采集卡设计 I

De in o CI sg f P Daa Ac ust n t q iio Ca d i i r n App ia in o gh l t f Hi -Sp e Mo o n r c o ed t r Co t o

i prs t l t s e ened at as .

vivado最简单的pcie例程 -回复

vivado最简单的pcie例程-回复开发工具Vivado为FPGA设计师提供了丰富的功能和工具,可以简化设计流程并提高开发效率。

其中,PCIE(Peripheral Component Interconnect Express)是一种高速串行总线接口,被广泛应用于计算机领域。

在使用Vivado进行FPGA开发时,涉及到PCIE的例程也是一种常见的设计需求。

下面将一步一步回答关于Vivado最简单的PCIE例程的问题,帮助读者了解并掌握相关知识。

一、什么是PCIE接口和PCIE例程?PCIE(Peripheral Component Interconnect Express)接口是一种高速串行总线技术,用于连接计算机内部各种设备和外部扩展卡。

通过PCIE 接口,计算机可以高速传输数据,并与其他设备进行通信。

在FPGA开发中,我们通常需要使用PCIE例程来实现与PCIE接口的通信,以实现特定的功能。

二、Vivado中如何创建一个PCIE例程?1. 打开Vivado软件,并创建一个新的工程。

2. 在“项目导航器”窗口中,右键单击“源文件”文件夹,选择“添加源文件”。

3. 在弹出的窗口中,选择“添加或创建源文件”选项,并点击“下一步”。

4. 在接下来的窗口中,选择“创建一个新的源文件”选项,并点击“下一步”。

5. 在新的源文件窗口中,选择“带有IP的设计”选项,并点击“下一步”。

6. 在IP选项窗口中,选择“PCI Express”并点击“下一步”。

7. 在创建PCI Express窗口中,选择需要的IP核,并点击“下一步”。

8. 在IP配置窗口中,按需求进行相关配置,并点击“下一步”。

9. 完成配置后,点击“下一步”并“下一步”以接受默认配置,然后点击“完成”。

10. 在源文件列表中,可以看到新建的PCIE例程文件。

三、Vivado中如何配置PCIE例程?1. 双击打开PCIE例程文件,进入IP核的配置界面。

基于PCIe总线的高速数据采集卡设计与实现

design,hardware

interface and software program of the

quisition card transfer

state

analyzed and discussed mainly,and the implementation method of high—speed DMA data

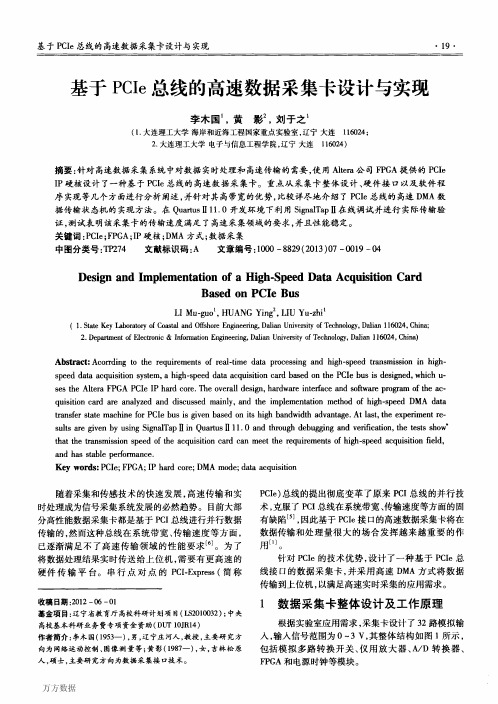

模拟输入信号1 模拟输入信号2

需要进行灵活的配置,并且PCIe高带宽优势明显。 本设计使用Ahera公司Cyclone IV GX系列的FP— GA芯片EP4CGX30CF23C8。该芯片集成了PCIe IP 硬核模块,实现×4通道的PCIe接口。IP核采用分层 结构,即分别为物理层、数据链路层、传输层和用户应

1

收稿日期:2012—06—01 基金项目:辽宁省教育厅高校科研计划项目(LS2010032);中央 高校基本科研业务费专项资金资助(DUT 10JRl4) 作者简介:李木国(1953一),男,辽宁庄河人,教授,主要研究方 向为网络运动控制、图像测量等;黄影(1987一),女,吉林松原 人,硕士,主要研究方向为数据采集接口技术。

3.2

… ~一

32-bit中断服务0x2为允许PCIe产生中断;0x3为DMA 寄存器 传输结束中断

。如8誓盏甚鬻输寄存器每传送一个双字地址自删Ⅱ4

~~

。.

32一bit

DMA传输每传送一个双字自动减4,直到减为0,

MB

字节寄存器DMA传送一次最多为2

… …~

32-bit

DMA传输OxOl:DMA读操作(Pc机到FPGA端); Oxl00:DMA写操作(FPGA端到Pc机)

发挥PCIe高带宽的优势,在FPGA内部开辟了深度为 128 KB的FIFO缓存空间用于缓存A/D采集的数据, 上位机获得数据时可以通过DMA方式传输。 本文所设计的采集卡的关键技术集中在PCIe的 DMA实现上,本节将讨论PCIe传输时数据包的TLP 结构以及基于FPGA实现的PCIe的DMA写操作核心 状态机的设计与实现。

pci卡开发大概是个什么流程

pci卡开发大概是个什么流程?

我来少讲几句吧。

一般,PCI总线开发采用两种方式,一是采用CPLD来设计控制接口。

由于PCI总线协议复杂,设计PCI控制接口难度较大,对于产品不大又有时限的工程项目来说,成本巨大,不划算。

二是采用通用PCI接口芯片,它能实现PCI规范所要求的所有硬件接口信号和配置空间寄存器,能够减少开发时间和成本,并能获得较好的数据传输性能。

采用后者,一般按如下几个步骤来:

1、PCI接口模式的选择。

根据应用项目的要求来确定是用PCI主控还是从控,由此,选定协议芯片。

从控方式的芯片有:PLX的PCI9052,TI的PCI2031,AMCC的AMCC5920等芯片;主控方式有PLX的PCI9054,CYPRESS的CY7C09449PV-AC,TI的PCI1251,AMCC5933等。

2、根据所选协议芯片及相应接口设计PCI卡硬件;

3、设计电路板,若用PCI开发工具则只需用双层板设计应用电路。

若无开发工具。

则要用四层板。

4、在有开发工具(如S5933的开发板可以支持开发S5933和S5922)情况下,根据应用定义属于自己应用系统的PCI配置数据。

在无开发工具的情况下按如下顺序:

1)焊接好电路板;

2)确认系统能识别PCI卡,若不能则检查原因知道修好为止或重做PCB板;

3)在线烧写PCI配置数据,并引导系统复位,观察系统是否采用新设计。

5、编写驱动程序及应用程序并调试软硬件。

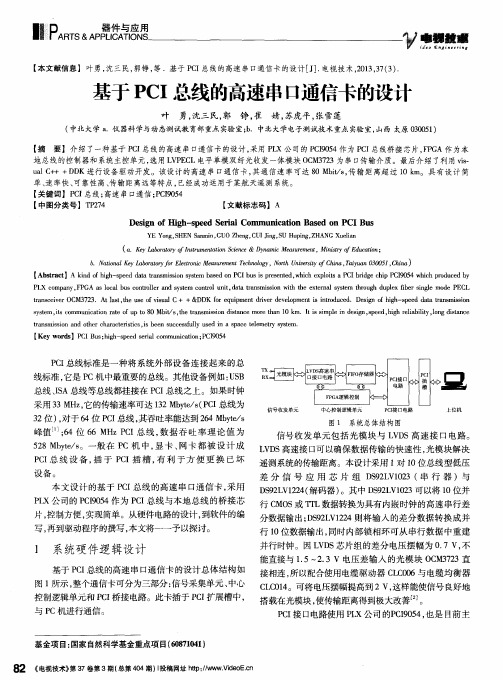

基于PCI总线的高速串口通信卡的设计

b . N a t i o n a l K e y L a b o r a t o yf r o r E l e c t r o n i c M e a s u r e en m t T e c h n o l o g y , N o r t h U n i v e r s i t y fC o h i n a , T a i y u a n 0 3 0 0 5 1 , c h i a) n 【 A b s t r a c t 】A k i n d o f h i g h — s p e e d d a t a t r a n s m i s s i o n s y s t e m b a s e d o n P C I b u s i s p r e s e n t e d , w h i c h e x p l o i t s a P C I b i r d g e c h i p P C I 9 0 5 4 w h i c h p r o d u c e d b y

s y s t e m, i t s c o mmu n i c a t i o n r a t e o f u p t o 8 0 Mb i t /s , t h e t r a n s mi s s i o n d i s t a n c e mo r e t h a n 1 0 k m.I t i s s i mp l e i n d e s i g n, s p e e d, h i g h r e l i a b i l i t y, l o n g d i s t nc a e

PL X c o mp n y, a F P GA a s l o c a l b u s c o n t r o l l e r a n d s y s t e m c o n t r o l u n i t , d a t a t r a n s mi s s i o n wi t h t h e e x t e r n a l s y s t e m t h r o u g h d u p l e x ib f e r s i ng l e mo d e P EC L t r a n s c e i v e r 0C M3 7 2 3.At l a s t . t h e u s e o f v i s u a l C + + &DDK f o r e q u i p me n t d r i v e r d e v e l o p me n t i s i n t r o d u c e d . De s i g n o f h i g h -s p e e d d a t a t r a n s mi s s i o n

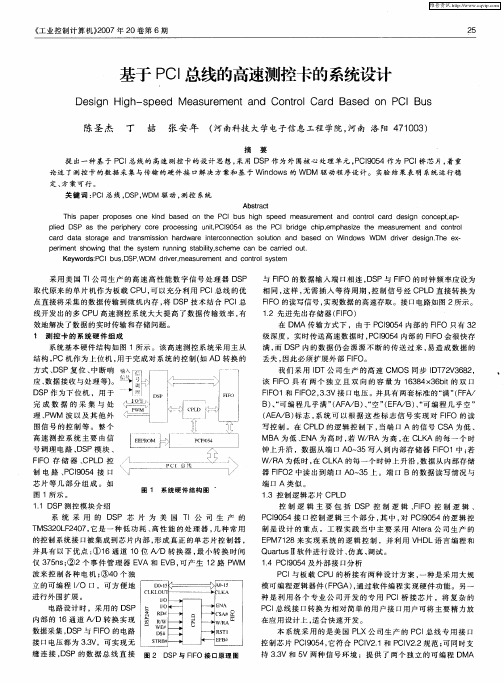

基于PCI总线的高速测控卡的系统设计

陈 圣 杰 丁 拮 张 安 年

( 河南科技大学电子信息工程 学院, 河南 洛阳 4 1 0 的 高 速 测 控 卡 的 设 计 思 想 , 用 DS Cl 采 P作 为 外 围核 心 处 理 单 元 , ClO 4作 为 P l 芯 片 , 重 P 95 C桥 着 论 述 了测控 卡 的 数据 采 集 与传 输 的硬 件 接 口解 决 方案 和基 于 Wid ws的 WD 驱 动 程 序 设 计 。 实验 结果 表 明 系统 运行 稳 no M

图 1所 示 。

图 1 系统硬件结构图 ‘

EE ROM P 、 pC ) 4 I 5

在 D MA 传 输 方 式 下 , 由 于 P 9 5 C10 4内部 的 FF 只 有 3 I O 2

级 深 度 ,实 时 传 送 高 速 数 据 时 , Cl 5 P 9 4内 部 的 FF 会 很 快 存 0 IO 满 , DS 内 的 数 据 仍 会 源 源 不 断 的 传 送 过 来 , 造 成 数 据 的 而 P 易 丢失 , 因此 必须 扩展 外 部 FF IO。 我 们 采 用 IT公 司 生 产 的高 速 CMOS 同 步 IT 2 3 8 , D D 7 V 6 2

采 用 美 国 T 公 司 生 产 的高 速 高 性 能 数 字 信 号 处 理 器 D P l S

与 FF 的数 据输 入 端 口相 连 , S IO D P与 FF 的 时 钟 频 率 应 设 为 I O

相 同 , 样 , 需插入等待 周期 , 制信号 经 C L 这 无 控 P D直 接转 换 为 FF 的读 写 信 号 , 现数 据 的高 速存 取 。接 口电路 如 图 2所 示 。 I O 实 1 先进先出存储器 (I . 2 FF O)

PCIExpress总线实验开发板软件设计与研究

PCI Express 总线实验开发板软件设计与研究王 丽,周 强,于守谦(北京航空航天大学自动化与电气工程学院,北京 100191)摘 要:作为新一代高速串行总线,PCI Ex pr ess 总线在高速数据采集等领域有着非常广阔的应用前景。

为了使学生更系统、深入地理解和掌握P CI Express 总线驱动程序和应用程序及其开发技术,设计开发了PCI Ex press 总线实验开发板在W indo ws 环境下的设备驱动程序和用户级应用程序。

同时,以高速LV DS(low voltage differentia l sig naling)的采集为例,深入研究了P CI Ex pr ess 总线相关的中断和DM A (direct memo ry access)传输技术。

实测结果表明,在D M A 传输方式下,数据传输速率可稳定达到132M B/s,相比传统的PCI 总线系统有大幅度提升。

该驱动程序和应用软件可广泛用于计算机相关专业本科高年级或研究生阶段的计算机接口技术实验课程教学中。

关键词:PCI Ex press 总线;DM A;驱动程序中图分类号:T P336 文献标志码:A 文章编号:1002 4956(2010)11 0345 05A software design based on PCI Express development boardWang Li,Zhou Q iang,Yu Sho uqian(Scho ol of A utomatio n Science and Electr ical Engineering ,Beijing U niver sityof A ero nautics and A stro nautics,Beijing 100191,China)Abstract:As a new generation o f hig h speed serial bus,PCI Ex pr ess bus has a ver y br oad application pro spects in t he ar eas o f high speed data acquisitio n.In o rder to make students understand and master the P CI Ex press bus dr iver and applicatio n development techno lo gy mor e sy st emat ically and tho roug hly,the device dr iver s and user level applicat ions of the PCI Ex pr ess bus test boar d under W indo ws envir onment are designed and dev el o ped.M eanwhile,taking hig h speed LV DS signal acquisition as an ex ample,tw o related t echnolo g ies of the PCI Express bus,inter rupt and D M A t ransfer a re researched.Ex per imental r esult s show t hat in the DM A transfer mode,the dat a transfer rat e can be stable t o 132M B/s,compared to the traditio na l P CI bus system,the P CI Ex press bus system is impr oved sig nificantly.T he dr iver and applicatio n so ftwa re can be used in teaching of Computer Interface T echno log y fo r com puter r elated senio r underg raduates o r postg raduat es.Key words:PCI Express bus;DM A;driv er收稿日期:2010 08 09作者简介:王丽(1985 ),女,山西晋中市人,硕士,主要从事计算机测试、半实物仿真方面的科研工作通信作者:周强(1972 ),男,北京市人,博士,副教授,主要从事计算机测试技术、计算机总线接口技术方面的教学、实验和科研.随着计算机技术的飞速发展,多媒体数据传输、高速数据采集、实时信息显示等领域对计算机总线速率提出了越来越高的要求。

计算机PCI总线设备开发流程

,

<AD[ 1 : 3 3 :0 C B 3 :] / 卧 : 0#

PAR

<AD[ 3 : q 6 :0 : ( / El : 4 C B :] 7

PAR

6 4

是 以某种 形式 的物理 量 存 在于 计 算 机之 外 , 就 涉及 这 到计算 机如何 与外 部进 行数 据交换 的问题 。通 常的计 算 机 与 外 部 进 行 数 据 交 换 的 接 口有 RS 2 2串 口 , 一3 US B接 口和 P I C 总线 , 以 P I 又 C 总线 的数 据传 输 率最 高。 工作频 率 3 MHz 数 据宽 度 3 位 的 P I 3 , 2 C 总线设 备

(

GNT#

CLK #

REQ #

TD Tn 0 T

TCK TM S TRS # T

RST #

能力, 目前 已广 泛应 用 于 数 据采 集 、 像采 集 、 图 虚拟 仪

器 和嵌入 式系 统等领 域 。

图 1 P I 号 线 C 信

如 图 1 示 , C 协 议 规 定 了近 百 根 的 信 号线 , 所 PI 但 在实 现工 程应 用 中并非 每根信 号 线都 要用 到 。如 作 者 所 开发 的 P I 线从 设 备 只使 用 了其 中的 4 信 C 总 9根 号线( 不含 电源 线和地 线 ) 。

维普资讯

计 算 机 P I 线 设 备 开 发 流 程 C 总

文章 编 号 :0 35 5 (0 6 1 —0 60 10 —8 0 2 0 )00 3—3

计 算 机 P I总 线 设 备 开 发 流 程 C

The De i n Pr c du e o m pu e s g o e r f Co t r PCI BU v c S De i e

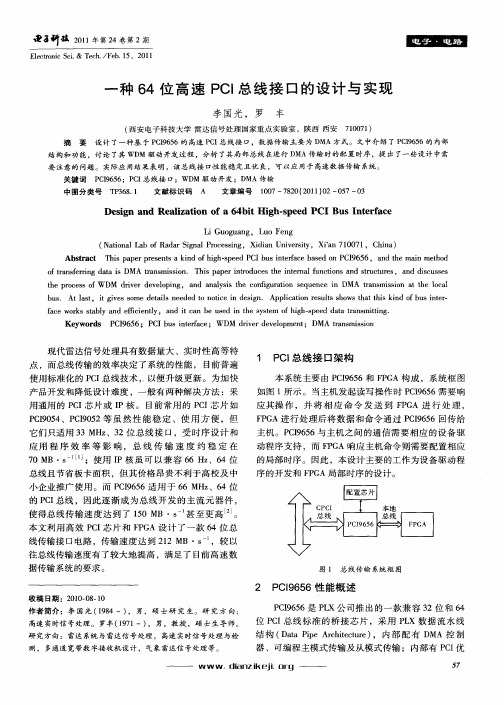

一种64位高速PCI总线接口的设计与实现

摘

要

设 计 了一 种 基 于 P I6 6的 高 速 P I 线 接 口 ,数 据 传 输 主 要 为 D C9 5 C总 MA 方 式 。文 中介 绍 了 P I6 6的 内部 C9 5

结 构 和 功 能 .讨 论 了其 WD 驱 动 开 发 过 程 ,分 析 了其局 部 总 线 在 进 行 D M MA传 输 时 的 配 置 时 序 ,提 出 了一 些 设 计 中 需 要 注 意 的 问题 。 实 际 应 用 结 果 表 明 ,该 总 线接 口性 能 稳 定 且 优 良 , 可 以应 用 于 高 速 数 据 传 输 系统 。

应其 操 作 ,并 将 相 应 命 令 发 送 到 F G 进 行 处 理 , PA FG P A进 行 处理 后 将 数 据 和命 令 通 过 P I66回传 给 C95

应 用 程 序 效 率 等 影 响 ,总 线 传 输 速 度 约 稳 定 在 7 0MB・ ¨ ;使 用 I 虽 可 以 兼 容 6 z 4位 s P核 6H 、6

现 代雷 达信 号处 理具 有数 据量 大 、实 时性 高等 特 点 ,而 总线 传输 的效 率决 定 了系 统 的性能 , 目前 普 遍

使 用标 准化 的 P I C 总线技 术 , 以便 升 级更 新 。为 加 快 。

1 P 总 线 接 口 架构 Cl

本 系统 主要 由 P I6 6和 F G C9 5 P A构 成 ,系 统 框 图 如 图 1所示 。当主机 发起 读 写操 作 时 P I6 6需 要 响 C9 5

高速数据处理系统中的PCI总线接口设计

4 ・ 9

维普资讯

・

计算机与 自动化技术 ・

电 子 工 蠢 师

20 0 7年 7月

C m at C 热交 换 ; 有 2个 独 立 的可 编 程 D A控 o pc P I 具 M

别表 示 3 i数据 线 由高至低 8位有 效 。 2bt

一

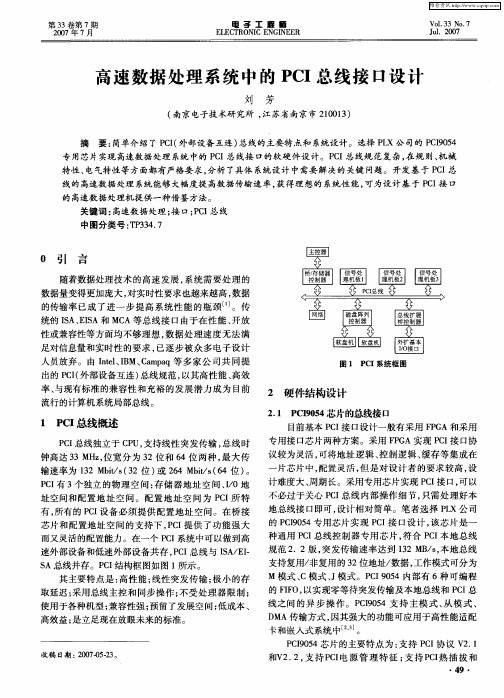

1 PI C 总线概 述

PI C 总线独立 于 C U, P 支持 线性 突发传 输 , 线 时 总

钟高达 3 H , 3M z位宽分为 3 2位和 6 4位两种 , 最大传 输速率为 12 M i s 3 3 b / (2位 ) 24 M i s 6 t 或 6 b / (4位) t 。 P I 3个 独立 的 物理 空 间 : C有 存储 器 地 址 空 间 、 0地 I /

刘 芳

( 南京 电子技 术研 究所 , 苏省 南京 市 2 0 1 ) 江 10 3

摘

要: 简单 介 绍 了 P I 外部设备 互连 ) C( 总线的主要 特 点和 系统设 计 。选择 PX公 司的 P I04 L C95

专用芯 片 实现 高速数据 处理 系统 中的 P I 线接 口的软 硬 件设 计 。P I总线规 范 复 杂 , 规 则 、 械 C总 C 在 机 特性 、 电气特性等 方 面都 有 严格要 求 , 分析 了具体 系统 设计 中需要 解 决 的关键 问题 。 开发 基 于 P I总 C 线的 高速数 据 处理 系统 能 够大幅度 提 高数据 传输速 率 , 获得 理 想 的 系统性 能 , 为设计 基 于 P I 口 可 C接

.

PI C 总线

的传输率 已成 了进一步提高系统性能 的瓶颈 。传 J

统韵 IA、 IA和 MC S ES A等 总线 接 口 由于在 性 能 、 放 开

pcie学习计划

pcie学习计划一、入门阶段1. 了解PCIe的基本概念和原理在入门阶段,首先要对PCIe(Peripheral Component Interconnect Express)的基本概念和原理进行了解。

PCIe是一种用于连接扩展卡和主板的高速接口标准,它是PCI总线的后继者,在传输速度、带宽和功耗方面都有了显著的提升。

了解PCIe的发展历程、工作原理和技术特点,对后续的学习和应用都有很大的帮助。

2. 学习PCIe的物理层和数据链路层PCIe接口包括物理层和数据链路层两个部分,这两个部分是理解PCIe技术的关键。

在学习物理层时,要掌握信号传输的基本原理、组成部分和接口规范;在学习数据链路层时,要了解数据传输的机制、连接管理和控制流程。

对PCIe接口的物理层和数据链路层有深入的理解,有助于后续的应用和故障排除。

3. 学习PCIe的架构和规范PCIe接口有多个版本和规范,每个版本都有其特定的架构和规范。

在入门阶段,要学习PCIe的各个版本的架构和规范,包括连接类型、带宽规格、电气特性等。

对PCIe的各个版本的架构和规范有全面的了解,有助于选择合适的接口版本和了解其应用场景。

4. 学习PCIe的设备驱动开发PCIe接口的设备驱动开发是PCIe学习的重要内容之一。

在入门阶段,要学习PCIe设备驱动的基本概念、开发流程和调试技巧。

了解设备驱动的开发原理和方法,对后续的应用和系统优化都有很大的帮助。

二、进阶阶段1. 深入学习PCIe的协议和传输层PCIe接口的协议和传输层是PCIe学习的进阶内容,包括数据传输协议、报文格式、序列管理和错误控制等。

在进阶阶段,要深入学习PCIe接口的协议和传输层,包括数据包的格式、传输流程和错误检测与纠正等。

对PCIe接口的协议和传输层有深入的了解,有助于应用和系统性能的提升。

2. 学习PCIe的性能优化和调试技巧PCIe接口的性能优化和调试技巧是PCIe学习的重要内容之一。

在进阶阶段,要学习PCIe 接口的性能优化技巧,包括传输速度、带宽利用和延迟控制等。

基于PCIe总线的高速数据采集卡设计与实现

・l 9・

基于 P C I e 总线的高速数据采集卡设 计与实现

李 木国 , 黄 影 ,刘于之

1 1 6 0 2 4 ; ( 1 . 大连理工大学 海岸和近海工程 国家重点实验室 , 辽宁 大连 2 . 大连理工 大学 电子与信息工程学院 , 辽 宁 大连 1 1 6 0 2 4 )

s u i t s a r e g i v e n b y u s i n g S i g n a l T a p H i n Q u a r t u s Ⅱ1 1 . 0 a n d t h r o u g h d e b u g g i n g a n d v e r i i f c a t i o n 。 t h e t e s t s s h o w "

Ab s t r a c t : Ac o r r d i n g t o t h e r e q u i r e me n t s o f r e a l - ・ t i me d a t a p r o c e s s i n g a n d h i g h- - s p e e d t r a n s mi s s i o n i n h i g h - — s p e e d d a t a a c q u i s i t i o n s y s t e m, a h i g h— s pe e d d a t a a c q u i s i t i o n c a r d b a s e d o n t h e PCI e bu s i s d e s i g ne d, wh i c h U—

L I Mu — g u o , HUANG Yi n g , L I U Yu — z h i (1 . S t a t e K e y L a b o r a t o r y o f C o a s t a l a n d O f f s h o r e E n g i n e e i r n g , D l a i a n U n i v e r s i t y o f T e c h n o l o g y , D a l i a n 1 1 6 0 2 4 , C h i n e r a F P GA P C I e I P h a r d c o r e . T h e o v e r a l l d e s i g n , h a r d w a r e i n t e r f a c e a n d s o t f wa re p r o g r a m o f t h e a c — q u i s i t i o n c a r d a r e a n a l y z e d a n d d i s c u s s e d ma i n l y , a n d t h e i mp l e me n t a t i o n me t h o d o f h i g h — s p e e d DMA d a t a

PCIe接口高速数据传输卡的驱动程序开发

PCIe接口高速数据传输卡的驱动程序开发

杨阿锋;吴帅;刘凯;徐欣

【期刊名称】《中国测试》

【年(卷),期】2008(034)002

【摘要】结合自行开发的PCI Express接口高速数据传输卡,讨论了一般PCI Express设备驱动程序编写时所面临的主要问题和解决方案,重点从驱动程序、硬件接口以及应用程序等几个方面进行分析阐述,并比较详尽的介绍了使用WinDriver开发具有简单数据传输和DMA传输功能的驱动程序的有效方法.【总页数】3页(P67-68,115)

【作者】杨阿锋;吴帅;刘凯;徐欣

【作者单位】国防科技大学电子科学与工程学院,湖南长沙,410073;国防科技大学电子科学与工程学院,湖南长沙,410073;国防科技大学电子科学与工程学院,湖南长沙,410073;国防科技大学电子科学与工程学院,湖南长沙,410073

【正文语种】中文

【中图分类】TP334.7;TP311

【相关文献】

1.基于PCIE驱动程序的数据传输卡DMA传输 [J], 李晃;巩峰;陈彦化

2.基于WinDriver的PCIe 1553B总线接口卡驱动设计与实现 [J], 闫海明;史岩;常于敏;杨北亚

3.一种PCI总线高速数据传输卡WDM驱动程序开发 [J], 胡修林;刘可

4.Linux下的PCIE同步时钟卡的设备驱动程序开发 [J], 杨兵见;魏丰;陈永志

5.基于PCIE接口的高速数据传输系统设计 [J], 张彪;宋红军;刘霖;胡骁;李洋

因版权原因,仅展示原文概要,查看原文内容请购买。

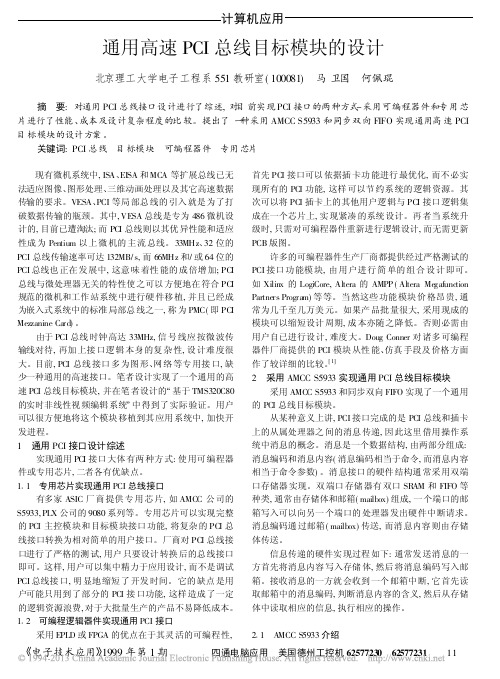

通用高速PCI总线目标模块的设计

通用高速PCI总线目标模块的设计北京理工大学电子工程系551教研室(100081)马卫国何佩琨摘要:对通用PCI总线接口设计进行了综述,对目前实现PCI接口的两种方式-采用可编程器件和专用芯片进行了性能、成本及设计复杂程度的比较。

提出了一种采用AMCC S5933和同步双向FIFO实现通用高速PCI 目标模块的设计方案。

关键词:PCI总线目标模块可编程器件专用芯片现有微机系统中,ISA、EI SA和MCA等扩展总线已无法适应图像、图形处理、三维动画处理以及其它高速数据传输的要求。

VESA、PCI等局部总线的引入就是为了打破数据传输的瓶颈。

其中,VESA总线是专为486微机设计的,目前已遭淘汰;而PCI总线则以其优异性能和适应性成为Pentium以上微机的主流总线。

33MHz、32位的PCI总线传输速率可达132MB/s,而66MHz和/或64位的PCI总线也正在发展中,这意味着性能的成倍增加;PCI 总线与微处理器无关的特性使之可以方便地在符合PCI 规范的微机和工作站系统中进行硬件移植,并且已经成为嵌入式系统中的标准局部总线之一,称为PMC(即PCI Mezzanine Ca rd)。

由于PCI总线时钟高达33MHz,信号线应按微波传输线对待,再加上接口逻辑本身的复杂性,设计难度很大。

目前,PCI总线接口多为图形、网络等专用接口,缺少一种通用的高速接口。

笔者设计实现了一个通用的高速PCI总线目标模块,并在笔者设计的/基于TMS320C80的实时非线性视频编辑系统0中得到了实际验证。

用户可以很方便地将这个模块移植到其应用系统中,加快开发进程。

1通用PCI接口设计综述实现通用PCI接口大体有两种方式:使用可编程器件或专用芯片,二者各有优缺点。

111专用芯片实现通用PCI总线接口有多家ASIC厂商提供专用芯片,如AMCC公司的S5933,PLX公司的9080系列等。

专用芯片可以实现完整的PCI主控模块和目标模块接口功能,将复杂的PCI总线接口转换为相对简单的用户接口。

PCI板卡的开发板卡

PLX9052 PCI板卡的开发第一章概述由于PC机的发展,PCI总线已成为工业和商业PC机的主流。

因此学习开发基于PCI 总线的技术是许多工程技术人员以及大专院校的当务之急。

§1第一节PCI总线简介PCI总线与早期的ISA总线有极大的不同,它与ISA总线技术也无任何连贯性。

下面我们就将PCI总线与ISA总线作一些对比来简单的介绍PCI总线,让大家对PCI总线有一个比较全面的初步了解。

ISA总线由如下几个部份组成:数据总线:D0~D15;地址总线:A0~A23;控制总线:MEMW、MEMR、IOW、IOR、IRQ3~7,9~12,14,15、IOCHCK、IOCHRDY、RESET、SYSCLK、DACK0~3、DACK5~7、AEN、REFRESH、T/C、SBHE、MASTER、DRQ0~3、DRQ5~7等;电源:±12V、±5V、GND。

PCI总线由如下几个部份组成:地址/数据复用总线:AD0~31;系统引脚:CLK、RST#;控制总线:C/BE[3:0]#、PAR、FRAME#、IRDY#、TRDY#、STOP#、LOCK#、IDSEL、 DEVSEL#;仲裁引脚(仅主控):REQ#、GNT#;错误状态引脚:PERR#>SERR#;中断:INTA#、INTB#、INTC#、INTD#(一般仅用INTA#);JTAG边界扫描信号:TD1、TD0、TDK、TMS、TRST#;电源:±12V、VCC、GND。

从以上的列表可看出PCI总线和ISA总线的不同,ISA总线的地址与数据是独立的,而PCI总线的地址与数据是复用的。

因此它不可能像ISA总线那样将应用电路的地址线与其直接连接。

但是,如果应用电路的地址与数据总线也是复用的,那是不是就可以直接连接呢?答案是否定的。

这是因为PCI总线实现即插即用(PNP),使用了一种软地址分配的方法,即特定的PCI总线上设备的地址,不是设备设计时确定的,而是系统通过软件来分配的。

PCIE接口的设计与应用培训

PCIE接口的设计与应用培训简介PCI Express(简称PCIE)是一种计算机总线技术,广泛用于计算机的扩展卡和主板之间的高速数据传输。

在现代计算机系统中,PCIE接口已成为一种重要的技术标准。

本文档将介绍PCIE接口的设计原理和应用开发,以帮助读者更好地了解PCIE接口的工作方式和使用方法。

PCIE接口的基本原理PCIE接口采用了串行总线的方式,相比传统的并行总线具有更高的带宽和更快的数据传输速度。

它采用了差分信号传输和包络调制的技术,可以在较短的时间内传输更多的数据。

PCIE接口的主要特点包括以下几点:•高带宽:PCIE接口支持多通道传输,每个通道的带宽都可以达到几GB/s。

•低延迟:PCIE接口采用了点对点的通信模式,减少了数据传输的延迟。

•热插拔支持:PCIE接口可以在计算机运行的过程中插入或拔出设备,而无需重新启动系统。

•可扩展性:PCIE接口支持多种不同大小和功能的插槽,可以连接不同类型的设备。

PCIE接口的设计流程PCIE接口的设计流程包括硬件设计和软件开发两个方面。

硬件设计主要涉及PCIE接口的物理层设计和协议设计,而软件开发则涉及PCIE接口的驱动程序和应用程序开发。

以下是PCIE接口设计的基本流程:1.硬件设计:–确定PCIE接口的连线方式:根据设计需求选择适合的PCIE 接口类型,如PCIE x1、PCIE x4等,并确定接口的连接方式,如插槽式设计或直插式设计。

–进行连线布局:根据选定的PCIE接口类型和连接方式,在硬件电路板上进行连线布局,并保证信号的稳定性和可靠性。

–完成物理层设计:根据PCIE接口的规范和标准,设计PCIE 接口的物理层电路,包括差分信号线、时钟信号线等。

–实施协议设计:设计PCIE接口的协议层,包括数据传输协议、握手协议等。

确保PCIE接口的正常通信和数据传输。

2.软件开发:–编写PCIE接口驱动程序:根据操作系统的要求,编写PCIE 接口的驱动程序,用于管理和控制PCIE接口的硬件设备。

pcie规范

pcie规范PCIe(Peripheral Component Interconnect Express)是一种高速串行总线规范,用于在计算机系统中连接各种外部设备和扩展卡。

PCIe是一种基于总线结构的互联技术,它提供了更高的带宽和更快的数据传输速度,以满足现代计算需求日益增长的需求。

本文将详细介绍PCIe规范,包括其历史、特点、工作原理以及应用领域。

PCIe的历史可以追溯到1992年,当时英特尔、IBM和康柏就开始开发PCI(Peripheral Component Interconnect)总线规范,用于取代传统的ISA和VLB总线。

PCI总线规范在1993年发布,迅速成为标准计算机接口,并在20世纪90年代普及开来。

然而,随着计算机性能的不断提升和多媒体、网络等应用的广泛应用,PCI总线的带宽和性能已经无法满足需求。

为了提供更高的带宽和更快的数据传输速度,PCI-SIG(PCI Special Interest Group)于2004年发布了PCI Express规范,即PCIe 1.0版本。

PCIe采用了全新的串行总线结构,以替代传统的并行总线。

相较于PCI总线,PCIe具有更高的数据传输速度、更低的延迟、更高的带宽和更好的可伸缩性。

PCIe的特点主要体现在以下几个方面:1. 高速传输:PCIe提供了多个版本,每个版本都有不同的数据传输速率。

当前最常见的PCIe 3.0版本,具有每条通道8 Gbps的传输速度,每条通道相当于一个全双工的高速通道。

2. 可伸缩性:PCIe采用点对点连接的拓扑结构,每个设备都有一个独立的通道,与其他设备无冲突。

这种可伸缩性使得PCIe可以支持大量的设备以及更复杂的系统架构。

3. 低延迟:由于PCIe采用了串行传输,相较于并行总线具有更低的延迟,能够更快地处理数据。

4. 热插拔支持:PCIe支持热插拔特性,即可以在计算机运行时插入或拔出设备,而不需要重启计算机。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PCI9052的PCI总线直接与金手指连接,局部总线与DSP之间的数据传输在双端口RAM中实现。双端口RAM采用两片CYPRESS公司的双端口RAM芯片CY7C131,组成16位存储转接电路。PCI9052和CY7C131供电电压均为5V,而TMS320LF2407供电电压为3.3V,所以接口电平不匹配,需要加总线电平转换电路,这里选用16位总线传送接收器74FCT164245来实现。PCI9052的控制信号和TMS320LF2407的控制信号之间的逻辑转换用一片ALTERA公司的PFGA芯片EPM7032LC44来实现。 TMS320LF2407的外围电路可以根据需要扩展。由于TMS320LF2407内部自带32K字的FLASH程序存储器,程序调试程序调试完毕后可以烧写进去,但程序调试过程中需要频繁修改程序,所以可扩展一片存储器,调试程序时当作程序存储器用,程序调试完毕后再作为数据存储器用,这样既方便又实用。TMS320LF2407有一个串行通信接口和一个16位并行通信接口,串口可以做成RS485、RS232、RS422、SDI总线接口等,并行通信接口可以做成16位并行输入输出接口。1.4 电路板制作 (1)在连线上只要将对应的引脚连在总线上就可以了。由于信号用的是反射波信号,所以驱动的信号只用了要求电压的一半,另一半靠反射来提升,所以对信号线的长度有要求:CLK信号线的长度为2500mil±100mil。如果长度不够可以画蛇行线,另外,CLK信号线要用地线屏蔽。 (2)PCI总线规范要求布四层线,也可以只布两层线。布两层线时,走线难度增大,要做好电源退耦。每个Vcc引脚必须有退耦电容,且容量的平均值至少为0.01μF,从引脚根部到电容器焊盘的走线长度不大于250mil,线宽至少为20mil,多个引脚可以并用一个电容,并且参与共用的引脚数不受限制,但必须满足以上条件。 (3)PCI总线信号PRSNT1#和PRSNT2#中必须有一个接地。如果都不接地,系统找不到开发板。它们接地有两个用途,其一,用来表明槽位上实际存在一块板;其二,提供该板对电源要求的有关信息。表1给出了PRSNT#引脚的设置情况。

(4)对于不实现JTAG边界扫描的板子,必须把引脚TDI和TDO连接起来,以使扫描链不至于断开。 (5)PCI连接器上的3.3V引脚(即使实际使用中未提供电流)在母板上必须连到一起,最好连到一个3.3V的电源平面上。而且,对3.3V引脚应提供一个交流回路,这时对地去耦应符合高频信号技术的要求。为此,应在3.3V平面上均匀排列12个高速电容,容量为0.01μF。 (6)为了稳定性,局部总线除了少数有特殊要求外,所有的信号线都应加上拉电阻(5kΩ~10kΩ)或下拉电阻(一般选150Ω)。 (7)为防止干扰,局部总线时钟也应对地屏蔽。 (8)串行EEPROM提供PCI总线和局部总线的部分重要配置信息,EEPROM一定要选支持串行传输方式的,如NM93CS46或者与之兼容的存储器。NM93C46不支持串行读写,所以不能选取。NM93CS46的CS、SK、SDI、SDO和PE端都要接10kΩ的上拉电阻,而PRE端要接150Ω的下拉电阻。EEPROM的配置至关重要,EEPROM配置不正确可能导致操作系统无法运行。系统启动时自动检测EEPROM的开始48位是否全为“1”,若全为“1”,则载入PCI9052的默认配置;否则则装载EEPROM中的内容,为板卡分配资源。串行EEPROM可以通过PCI总线直接写入,也可以用编程器直接烧写。1.5 程序调试1.5.1 FPGA程序的开发 可编程器件的设计软件设计软件种类很多,各大器件厂家及一些软件公司都开发了一些设计软件。软件的设计根据逻辑功能的描述方法可分为语言描述设计和原理图描述设计两大类。常见的如DATA I/O公司的ABEL语言、四通公司ASIC事业部开发的针对GAL器件的FM(Fast MAP)软件等属于语言描述类设计软件;而DATA I/O 公司的Synario软件、Orcad公司的PLD等软件属于电路图描述或电路图描述与语言描述相结合设计的软件。 本设计中FPGA的编程只涉及到信号逻辑转换,所以只需选用语言描述类设计软件,这里选用DATA I/O公司的ABEL语言描述设计软件。程序调试结束后用编程器写入FPGA芯片即可。1.5.2 DSP程序开发 TI公司提供了DSP专用仿真器和仿真开发系统,C2000系列的开发系统最新版本为CCS2.2。对于不同的仿真器,只要安装驱动程序即可使用该开发系统进行仿真。仿真器选用最新款的带USB接口的ICETEK-51000USBV2.0仿真器。由于该仿真器使用USB接口,所以不需外接供电电源,实用又方便。 由于硬件设计时扩展了可转换的存储器,进行仿真时把存储器接成程序存储器,程序可以直接转载到扩展的存储器中进行调试,免去了往FLASH中烧写的麻烦,程序调试完毕后再固化到FLASH中。2 PCI总线接口卡的软件驱动开发 PCI卡的硬件调试需要结合软件程序的调试来完成。PCI卡的驱动程序开发有多种途径,驱动开发工具也有多种选择。2.1 驱动开发工具的选取 (1)DDK(Driver Device Kit) 许多VMM服务都使用寄存器的调用方式,使用起来不是很方便,没有深厚的汇编语言及硬件基础很难在短时间内开发出设备驱动程序。Microsoft公司提供了设备驱动程序工具箱(DDK),它是基于汇编语言的编程方式的,DDK的优点是可以开发核心态的真正意义上的驱动程序,开发出来的驱动程序效率是最高的。 (2)DS(Driver Studio) DS是一个驱动程序集成开发包,其中包括了DriverAgent、VtoolsD、DriverWorks、SoftICE Driver Edition、BoundsChecker Driver Edition、DriverWorkbenc、FieldAgent for Drivers等。几种常见的DS驱动开发工具介绍如下: ·DriverAgent为Win32应用程序提供了访问硬件的接口。 ·VtoolsD支持Windows95和Windows98的驱动程序开发(VxD)。VtoolsD包括代码生成器、实时接口库和可以作为开发一类驱动程序的例子程序。 ·DriverWorks包括为Window NT和Win32 Driver Model(WDM)开发驱动程序的完整的开发框架,同时也支持Windows98和Windows2000下驱动程序的开发。DriverWorks包含一个复杂的代码生成工具(Driver Wizard),其中含有支持C++下编程的类库和例子程序。 (3)WinDriver WinDriver是KRF-Tech公司的一套PCI驱动程序开发包。它改变了传统驱动程序开发的方法和思路,极大地简化了驱动程序的编制;同时又没有牺牲驱动程序的性能,是一套高效、快捷的PCI驱动程序开发软件包,特别适合专业硬件人员使用。 利用WinDriver开发驱动程序不需要熟悉操作系统的内核,整个驱动程序中的所有函数都是工作在用户态下的,通过与WinDriver的.Vxd或者.Sys文件交互可达到驱动硬件的目的。由于是一个用户态程序,效率的高低也就成了人们选择WinDriver时关心的问题。大量实践数据表明,WinDriver并没有通过牺牲系统性能来换取驱动程序的快速开发。本设计中选用WinDriver来开发驱动程序。2.2 WinDriver开发驱动程序 在WinDriver的体系结构中,WinDriver Kernel处于中心位置,它提供的用户态库函数(API)实际就是对WinDriver Kernel中实现的功能进行调用。几乎所有用户同硬件的交互都是通过WinDriver Kernel来实现的,这样就极大地解放了开发人员。用户的主要任务就是利用WinDriver提供的用户动态函数库(API函数库)在用户态实现自己的驱动程序代码,完成硬件驱动的功能。 基于WinDriver的设备驱动程序主要分为驱动程序和应用程序两部分。利用DriverWizard生成.inf驱动程序,安装该驱动程序后,系统就根据EEPROM中的配置信息给板卡分配资源,接下来就可以进行应用程序的开发了。利用DriverWizard生成应用程序框架后,用户把生成的框架整理到自己的程序中,再添加实际应用中需要的功能就完成了软件的开发。 PCI总线是计算机总线的枢纽,其速度是一般总线望尘莫及的,其应用也十分广泛。利用本文介绍的方法开发出的板卡可以运用于各种高速数据传输场合中,如雷达系统仿真控制、工业总线控制、高速数据采集、图像采集等。本设计在对芯片的选型时本着经济实用的原则,开发出的板卡性价比较高。

高速PCI总线接口卡的开发

摘 要: 从系统的角度介绍高速PCI总线接口卡开发的整个过程,其中包括硬件电路的设计制作和软件驱动的开发。介绍一些从实际设计过程中得出的应该注意的细节等。 关键词: PCI总线 PCI9052 TMS320LF2407 双端口RAM

PCI总线技术已经应用于形形色色的微机接口中。现在声卡、网卡甚至有些显卡都是基于PCI总线技术的,一些高速数据传输系统中也需要用到PCI总线技术。PCI总线技术的出现是为了解决由于微机总线的低速度和微处理器的高速度而造成的数据传输瓶颈问题,PCI局部总线局部总线是在ISA总线和CPU总线之间增加的一级总线。由于独立于CPU的结构,该总线增加了一种独特的中间缓冲器的设计,从而与CPU及时钟频率无关,用户可以将一些高速外设直接挂到CPU总线上,使之与其相匹配。PCI局部总线使得PC系列微机结构也随之升级为现在的基于PCI总线的三级总线结构。线接口卡的开发

PCI局部总线最显著的特征是速度快。ISA总线的传输速率传输速率为5MB/s,EISA总线的传输速率为33MB/s,PCI1.0标准定义的总线传输速率为132MB/s,PCI2.0标准定义的总线传输速率为264MB/s,PCI2.1和PCI2.2标准定义的总线传输速率为512MB/s。而新一代PCI-X技术则在原有PCI总线技术的基础上增加了许多新的技术特征,利用PCI-X技术可以为千兆以太网卡、基于Ultra SCSI320的磁盘阵列控制器等高数据吞吐量的设备提供足够的带宽。1999年PCISIG(PCI特别兴趣小组)发布的PCI-X1.0标准最高可提供1GB/s的传输速率,而2003年推出的PCI-X2.0标准则最高可提供4.3GB/s的传输速率。 目前,PCI总线接口电路的选择主要有两种方案。一种是选用可编程逻辑器件(PLD)。使用PLD,用户可以灵活地开发出适合自己需要的具有特定功能的芯片,但PCI总线协议比较复杂,设计PCI控制接口难度较大,对于一般的工程项目来说,成本较大。现在有许多生产可编程逻辑器件的厂商都提供经过严格测试的PCI接口功能模块,用户只需进行组合即可。另一种是选用PCI专用芯片组(又称桥接电路),通过专用芯片来实现完整的PCI主控模块和目标模块的功能,将复杂的PCI总线接口转换为相对简单的用户接口,用户只需设计转换后的总线接口。本设计中选用PCI总线专用接口芯片接口芯片来开发接口卡。1.1 接口芯片介绍 PCI总线接口电路又分为主控设备和目标设备。主控设备可以控制总线,驱动地址、数据和控制信号;目标设备不能启动总线操作,只能依赖于主控设备从其中读取数据或向其传送数据。主控设备芯片价格比较高,目标设备芯片价格则比较便宜,而且目标设备芯片比较简单、易于操作。 目前两大PCI专用接口芯片生产商是AMCC公司和PLX公司。AMCC公司的PCI接口芯片有S5920、S5933、S5935等。S5920是目标设备芯片;S5933既可以设置为主控设备芯片,又可以设置为目标设备芯片;S5935是S5933的改进版,同样既可以设置为主控设备芯片,也可以设置为目标设备芯片。PLX公司在PCI接口芯片的设计生产中首屈一指,其目标设备芯片产品主要有PCI9030、PCI9052和PCI9050,PCI9050和PCI9052可以运用于ISA卡转接PCI的设计中,PCI9030是专门为嵌入式系统设计的;主控设备芯片产品主要有PCI9054、PCI9080和PCI9060,PCI9060是最早的32位主控设备芯片,PCI9080是PCI9060的后继产品,而PCI9054则是一种性价比很高的芯片,其性能比PCI9080、PCI9052更优越。 由于主控设备芯片比较复杂,而且价格昂贵,所以对处理速度和传输速度要求不是特别高的场合应尽量选用目标设备芯片。本设计中选用PLX公司的PCI9052目标设备芯片来设计PCI接口电路。1.2 PCI9052介绍 PCI9052是PLX公司继PCI9050之后推出的低成本、低功耗、32位PCI总线接口芯片,利用它可以使局部总线快速转换到PCI总线上。 PCI9052芯片的设计符合PCI2.1规范。它支持低成本从属适配器,其局部总线可根据需要配置成复用或非复用模式的8、16或32位的局部总线。PCI总线侧的时钟频率范围为0~33MHz,局部总线与PCI总线的时钟相互独立,局部总线的时钟频率范围为0~40MHz,两种总线的异步运行方便了高低速设备的相互兼容。PCI9052芯片内部有一个64字节的写FIFO和一个32字节的读FIFO,通过读写FIFO,可实现高性能的突发式数据传输,也可以进行连续的单周期操作。1.3 硬件设计 由于PCI9052属于目标设备芯片,只能依赖于主控设备从其中读取数据或向其传送数据,所以需要一个微处理器对通过PCI9052从PCI总线发送到局部总线的命令作出处理响应,或者把用户想要传送的数据以中断的方式通知PCI总线来读取。本设计中微处理器选用TI公司的C2000系列的16位DSP芯片TMS320LF2407。 TMS320LF2407是TI公司推出的定点DSP处理器,是一款性价比较高的芯片。它采用高性能静态CMOS技术,供电电压为3.3 V,指令周期可达25 ns,片内有高达32K字的FLASH程序存储器、1.5K字的数据/程序RAM、544字双口RAM(DARAM)和2K字的单口RAM(SARAM),可以分别扩展64K字外部程序存储器、64K字外部数据存储器和64K字I/O寻址空间;片内还集成了包括CAN控制器在内的多个外围模块及存储器,可以运用于电机及逆变电路的控制中;10位16通道的A/D转换器最小转换时间为500ns;内部自带看门狗定时器模块(WDT)和16位的串行外设接口模块(SPI)。另外,该芯片有高达40个可单独编程或复用的通用输入/输出引脚、一个串行通信接口(SCI)、一个并口和5个外部中断。目前投入市场试用的C2000系列的32位DSP芯片TMS320C2812采用的是150MHz的时钟速率,其指令周期只为6.7ns,存储器可以扩展到1M,速度更快,功能更强大。 PCI接口卡硬件总体设计。图中,DB代表数据总线,AB代表地址总线,CB代表控制总线。