24C08芯片手册

任务:24C08的使用

项目五基于I2C总线协议的存储操作与应用设计任务要求:24C08的使用1.仿真图proteus2程序原代码#include "iom16v.h" //ICC AVR环境下的ATmega16库函数定义了所有的寄存器及其位的标号#include "macros.h"#define TWI_Status_Start 0x08#define TWI_Status_ReStart 0x10#define TWI_Status_MTSlaACK 0x18#define TWI_Status_MTDataACK 0x28#define TWI_Status_MRSlaACK 0x40#define TWI_Status_MRDataNOACK 0x58#define TWI_Status_MRDataACK 0x50#define TWIAddr_24C08_Wr 0xA0 //写命令#define TWIAddr_24C08_Rd 0xA1 //读命令#define TWI_Work_Start() (TWCR=(1<<TWINT)|(1<<TWSTA)|(1<<TWEN))#define TWI_Work_Stop() (TWCR=(1<<TWINT)|(1<<TWSTO)|(1<<TWEN))#define TWI_Work_Wait() {while(!(TWCR&(1<<TWINT)));}#define TWI_Work_TestAck() (TWCR&0xF8)#define TWI_Work_SetAck() (TWCR|=(1<<TWEA))#define TWI_Work_SentNoAck() (TWCR&=~(1<<TWEA))#define TWI_Work_Twi() (TWCR=(1<<TWINT)|(1<<TWEN))#define TWI_Work_WriteByte(x) {TWDR=(x);TWCR=(1<<TWINT)|(1<<TWEN);}#define LCM_RS_1 PORTB|=(1<<0)#define LCM_RS_0 PORTB&=(~(1<<0))#define LCM_RW_1 PORTB|=(1<<1)#define LCM_RW_0 PORTB&=(~(1<<1))#define LCM_E_1 PORTB|=(1<<2)#define LCM_E_0 PORTB&=(~(1<<2))/******************************************************************************函数功能:延时1us(4M晶振,0.25微秒的指令执行周期)入口参数:无函数说明:4*0.25=1(微秒)******************************************************************************/void Delay_1_us(void){NOP();NOP();NOP();NOP();}/************************************************************************************* *函数功能:延时若干微秒入口参数:n_us************************************************************************************** */void Delay_n_us(unsigned int n_us){unsigned int cnt_i;for(cnt_i=0;cnt_i<n_us;cnt_i++){Delay_1_us();}}/************************************************************************************* *函数功能:延时1ms(4M晶振,0.25微秒的指令执行周期)入口参数:无函数说明:(3×cnt_j+2)×cnt_i=(3×33+2)×40*0.25=1010(微秒),可以近似认为是1毫秒************************************************************************************** */void Delay_1_ms(void){unsigned char cnt_i,cnt_j;for(cnt_i=0;cnt_i<40;cnt_i++){for(cnt_j=0;cnt_j<33;cnt_j++){}}}/************************************************************************************* *函数功能:延时若干毫秒入口参数:n_ms************************************************************************************** */void Delay_n_ms(unsigned int n_ms){unsigned int cnt_i;for(cnt_i=0;cnt_i<n_ms;cnt_i++){Delay_1_ms();}}/************************************************************************************* *函数功能:读取忙标志和AC的值入口参数:无************************************************************************************** */unsigned char LCM_Re_BAC(){unsigned char status;//LCM_Dat为输入DDRA=0x00;//选择命令通道LCM_RS_0;//选择读操作LCM_RW_1;//使能线置1LCM_E_1;//等待信号线稳定Delay_n_us(1);//读入status=PINA;//使能线置0LCM_E_0;return status;}/************************************************************************************* *函数功能:写入命令入口参数:命令代码************************************************************************************** */void LCM_Wr_CMD(unsigned char cmd_dat){//判忙while(LCM_Re_BAC()>=0x80);//LCM_Dat为输出DDRA=0xFF;//选择命令通道LCM_RS_0;//选择写操作LCM_RW_0;//使能线置1LCM_E_1;//设置命令数据PORTA=cmd_dat;//等待信号线稳定Delay_n_us(1);//送命令数据LCM_E_0;}/************************************************************************************* *函数功能:写入数据入口参数:数据代码************************************************************************************** */void LCM_Wr_DAT(unsigned char dis_dat){//判忙while(LCM_Re_BAC()>=0x80);//LCM_Dat为输出DDRA=0xFF;//选择数据通道LCM_RS_1;//选择写操作LCM_RW_0;//使能线置1LCM_E_1;//设置数据数据PORTA=dis_dat;//等待信号线稳定Delay_n_us(1);//送数据数据LCM_E_0;Delay_n_us(40);}/************************************************************************************* *函数功能:初始化入口参数:无************************************************************************************** */void LCM_1602_Init(void){LCM_Wr_CMD(0x38); //显示模式设置:16×2显示,5×7点阵,8位数据接口Delay_n_ms(5); //延时5msLCM_Wr_CMD(0x38);Delay_n_ms(5);LCM_Wr_CMD(0x38);Delay_n_ms(5);LCM_Wr_CMD(0x0f); //显示模式设置:显示开,有光标,光标闪烁Delay_n_ms(5);LCM_Wr_CMD(0x06); //显示模式设置:光标右移,字符不移Delay_n_ms(5);LCM_Wr_CMD(0x01); //清屏幕指令,将以前的显示内容清除Delay_n_ms(5);}/************************************************************************************* *函数功能:读取独立式键盘键值入口参数:无************************************************************************************** */unsigned char Get_Key_Val(){unsigned char key_val;key_val=PIND;switch(key_val){case 0xfe:key_val=1;break;case 0xfd:key_val=2;break;case 0xfb:key_val=3;break;case 0xf7:key_val=4;break;case 0x7f:key_val=8;break;case 0xbf:key_val=7;break;case 0xdf:key_val=6;break;case 0xef:key_val=5;break;default:key_val=0;break;}while(PIND==0xFF);return key_val;}unsigned char TWI_Device_Write(unsigned char wdata,unsigned char address){TWI_Work_Start();TWI_Work_Wait();if(TWSR&0xf8!=TWI_Status_Start) return 1;TWI_Work_WriteByte(TWIAddr_24C08_Wr);TWI_Work_Wait();if(TWSR&0xf8!=TWI_Status_MTSlaACK) return 1;TWI_Work_WriteByte(address);TWI_Work_Wait();if( TWSR&0xf8!=TWI_Status_MTDataACK) return 1;TWI_Work_WriteByte(wdata);TWI_Work_Wait();if( TWSR&0xf8!=TWI_Status_MTDataACK) return 1;TWI_Work_Stop();Delay_n_ms(1);}unsigned char TWI_Device_Read(unsigned char address){unsigned char rtndata;TWI_Work_Start();TWI_Work_Wait();if(TWSR&0xf8!=TWI_Status_Start) return 0;TWI_Work_WriteByte(TWIAddr_24C08_Wr);TWI_Work_Wait();if(TWSR&0xf8!=TWI_Status_MTSlaACK) return 0;TWI_Work_WriteByte(address);TWI_Work_Wait();if(TWSR&0xf8!=TWI_Status_MTDataACK) return 0;TWI_Work_Start();TWI_Work_Wait();if(TWSR&0xf8!=TWI_Status_ReStart) return 0;TWI_Work_WriteByte(TWIAddr_24C08_Rd);TWI_Work_Wait();if(TWSR&0xf8!=TWI_Status_MRSlaACK) return 0;TWI_Work_Twi();TWI_Work_Wait();if(TWSR&0xf8!=TWI_Status_MRDataNOACK) return 0;rtndata=TWDR;TWI_Work_Stop();return rtndata;}/************************************************************************************* *主函数************************************************************************************** */void main(void){unsigned char data[11]={'0','1','2','3','4','5','6','7','8','9','k'};unsigned char x,keyn;unsigned char j;TWBR=64;TWSR=00;DDRB=0xFF;PORTB=0XFF;DDRA=0XFF;PORTA=0XFF;DDRD=0XFF;PORTD=0XFF;LCM_1602_Init();Delay_n_ms(10);while(1){keyn=Get_Key_Val();TWI_Device_Write(keyn,keyn);Delay_n_ms(1);x=TWI_Device_Read(keyn);LCM_Wr_CMD(0x80);LCM_Wr_DAT(data[x]);}}3.Protel图。

掉电存储模块产品使用手册

ATMEL08掉电存储模块简要说明:一、尺寸:全长30mm宽15mm高10mm二、主芯片:ATMEL24C08芯片三、工作电压:直流5V四、特点:电路简单实用,接线简单。

电路支持:ATMEL24C02\ ATMEL24C04\ ATMEL24C08\ ATMEL24C16\ ATMEL24C32.适用场合:单片机学习、电子竞赛、产品开发、毕业设计。

【标注说明】【参考原理图】【PCB尺寸图】【测试程序】#include <reg52.H>#include <stdio.h>#include <absacc.h>unsigned char code table[]={ 0xc0,0xf9,0xa4,0xb0,0x99,0x92,0x82,0xf8,0x80,0x90,0x40}; signed char sec=1; //定义计数值,每过1 秒,sec加1unsigned int tcnt; //定时中断次数unsigned char jd=0;unsigned char gd=0;bit write=0; //写24C08 的标志;sbit gewei=P2^6; //个位选通定义sbit shiwei=P2^5; //十位选通定义sbit baiwei=P2^7; //百位选通定义sbit qianwei=P2^4; //千位选通定义sbit P10=P1^0;sbit P11=P1^1;sbit P12=P1^2;sbit P13=P1^3;sbit P14=P1^4;sbit P15=P1^5;sbit P16=P1^6;sbit P17=P1^7;sbit P30=P3^0;sbit P31=P3^1;sbit P32=P3^2;sbit P35=P3^5;sbit jia=P2^0;sbit jian=P2^1;sbit res=P2^2;/////////24C08 读写驱动程序//////////////////// sbit scl=P3^3; // 24c08 SCLsbit sda=P3^4; // 24c08 SDAvoid delay1(unsigned char x){ unsigned int i;for(i=0;i<x;i++);;}void flash(){ ; ; }void x24c08_init() //24c08 初始化子程序{scl=1; flash(); sda=1; flash();}void start() //启动(I方C)总线{sda=1; flash(); scl=1; flash(); sda=0; flash(); scl=0; flash();} void stop() //停止(I方C)总线{sda=0; flash(); scl=1; flash(); sda=1; flash();}void writex(unsigned char j) //写一个字节{ unsigned char i,temp;temp=j;for (i=0;i<8;i++){temp=temp<<1; scl=0; flash(); sda=CY; flash(); scl=1; flash();} scl=0; flash(); sda=1; flash();}unsigned char readx() //读一个字节{unsigned char i,j,k=0;scl=0; flash(); sda=1;for (i=0;i<8;i++){flash(); scl=1; flash();if (sda==1) j=1;else j=0;k=(k<<1)|j;scl=0;}flash(); return(k);}void clock() //(I方C)线时钟{unsigned char i=0;scl=1; flash();while ((sda==1)&&(i<255))i++;scl=0; flash();}////////从24c02 的地址address 中读取一个字节数据/////unsigned char x24c08_read(unsigned char address){unsigned char i;start(); writex(0xa0);clock(); writex(address);clock(); start();writex(0xa1); clock();i=readx(); stop();delay1(10);return(i);}//////向24c02 的address 地址中写入一字节数据info///// void x24c08_write(unsigned char address,unsigned char info){EA=0;start(); writex(0xa0);clock(); writex(address);clock(); writex(info);clock(); stop();EA=1;delay1(50);}/////////////24C08 读写驱动程序完///////////////////// void Delay(unsigned int tc) //延时程序{while( tc != 0 ){unsigned int i;for(i=0; i<100; i++);tc--;}}void LED() //LED显示函数{qianwei=0; P0=0xc0; Delay(3); qianwei=1; baiwei=0; P0=0xc0; Delay(3); baiwei=1; shiwei=0; P0=table[sec/10]; Delay(3); shiwei=1; gewei=0; P0=table[sec%10]; Delay(3); gewei=1;}void t0(void) interrupt 1 using 0 //定时中断服务函数{TH0=(65536-50000)/256; //对TH0 TL0 赋值TL0=(65536-50000)%256; //重装计数初值tcnt++; //每过250ust tcnt 加一if(tcnt==1) //计满20次(1 秒)时{tcnt=0; //重新再计write=1; //1 秒写一次24C08}}void main(void){TMOD=0x01; //定时器工作在方式1ET0=1; EA=1;x24c08_init(); //初始化24C08sec=x24c08_read(2);//读出保存的数据赋于secTH0=(65536-50000)/256; //对TH0 TL0 赋值TL0=(65536-50000)%256; //使定时器0.05 秒中断一次TR0=1; //开始计时*/while(1){if(jia==0){Delay(8); while(!jia){LED();}; {sec++;if(sec==36){sec=0;}} } if(jian==0){ Delay(8); while(!jian){LED();};{sec--;if(sec<0){sec=35;}} }if(res==0){sec=0;}switch(sec){case 0:P1=0X81;P30=1;P31=1;P32=1;P35=1;break;case 1:P1=0X82;P30=1;P31=1;P32=1;P35=1;break;case 2:P1=0X84;P30=1;P31=1;P32=1;P35=1;break;case 3:P1=0X88;P30=1;P31=1;P32=1;P35=1;break;case 4:P1=0X90;P30=1;P31=1;P32=1;P35=1;break;case 5:P1=0XA0;P30=1;P31=1;P32=1;P35=1;break;case 6:P1=0X41;P30=1;P31=1;P32=1;P35=1;break;case 7:P1=0X42;P30=1;P31=1;P32=1;P35=1;break;case 8:P1=0X44;P30=1;P31=1;P32=1;P35=1;break;case 9:P1=0X48;P30=1;P31=1;P32=1;P35=1;break;case 10:P1=0X50;P30=1;P31=1;P32=1;P35=1;break;case 11:P1=0X60;P30=1;P31=1;P32=1;P35=1;break;case 12:P1=0XC1;P30=0;P31=1;P32=1;P35=1;break;case 13:P1=0XC2;P30=0;P31=1;P32=1;P35=1;break;case 14:P1=0XC4;P30=0;P31=1;P32=1;P35=1;break;case 15:P1=0XC8;P30=0;P31=1;P32=1;P35=1;break;case 16:P1=0XD0;P30=0;P31=1;P32=1;P35=1;break;case 17:P1=0XE0;P30=0;P31=1;P32=1;P35=1;break;case 18:P1=0XC1;P30=1;P31=0;P32=1;P35=1;break;case 19:P1=0XC2;P30=1;P31=0;P32=1;P35=1;break; case 20:P1=0XC4;P30=1;P31=0;P32=1;P35=1;break; case 21:P1=0XC8;P30=1;P31=0;P32=1;P35=1;break; case 22:P1=0XD0;P30=1;P31=0;P32=1;P35=1;break; case 23:P1=0XE0;P30=1;P31=0;P32=1;P35=1;break;case 24:P1=0XC1;P30=1;P31=1;P32=0;P35=1;break; case 25:P1=0XC2;P30=1;P31=1;P32=0;P35=1;break; case 26:P1=0XC4;P30=1;P31=1;P32=0;P35=1;break; case 27:P1=0XC8;P30=1;P31=1;P32=0;P35=1;break; case 28:P1=0XD0;P30=1;P31=1;P32=0;P35=1;break; case 29:P1=0XE0;P30=1;P31=1;P32=0;P35=1;break;case 30:P1=0XC1;P30=1;P31=1;P32=1;P35=0;break; case 31:P1=0XC2;P30=1;P31=1;P32=1;P35=0;break; case 32:P1=0XC4;P30=1;P31=1;P32=1;P35=0;break; case 33:P1=0XC8;P30=1;P31=1;P32=1;P35=0;break; case 34:P1=0XD0;P30=1;P31=1;P32=1;P35=0;break; case 35:P1=0XE0;P30=1;P31=1;P32=1;P35=0;break; default:break;}LED();if(write==1) //判断计时器是否计时一秒{write=0; //清零x24c08_write(2,sec); //在24c08 的地址2 中写入数据sec}}}【实物展示】。

I2C总线24C08(PDF档)

应答信号时序

写操作 • 写操作分为字节写和页面写两种操作,

•

在字节写模式下 主器件发送起始命令和从器件地址信息 R/W位置零 给从器件 在从器件产生 •应答信号后 主器件发送16的字节地址 主器件在收到从器件的另一个应答信号后 再发送数据到被寻址的存 储单元 再次应答 并在主器件产生停止信号后 •开始内部数据的擦写 在内部擦写过程中 从器件不再应答主器件的任何请求

I2C总线的传送格式

I2C总线的传送格式为主从式,对系统中的某一器件来说有 四种工作方式:主发送方式、从发送方式、主接收方式、从接 收方式。 只讲主发送从接收(单片机发送 24C08接收)

主器件产生开始信号以后,发送的第一个字节为控制字节。前 七位为从器件的地址片选信号。最低位为数据传送方向位(高 电平表示读从器件,低电平表示写从器件),然后发送一个选 择从器件片内地址的字节,来决定开始读写数据的起始地址。 接着再发送数据字节,可以是单字节数据,也可以是一组数据, 由主器件来决定。从器件每接收到一个字节以后,都要返回一 个应答信号(ASK=0)。主器件在应答时钟周期高电平期间释 放SDA线,转由从器件控制,从器件在这个时钟周期的高电平 期间必须拉低SDA线,并使之为稳定的低电平,作为有效的应 答信号。

K0110K0101850380055(K24C08)-规格书

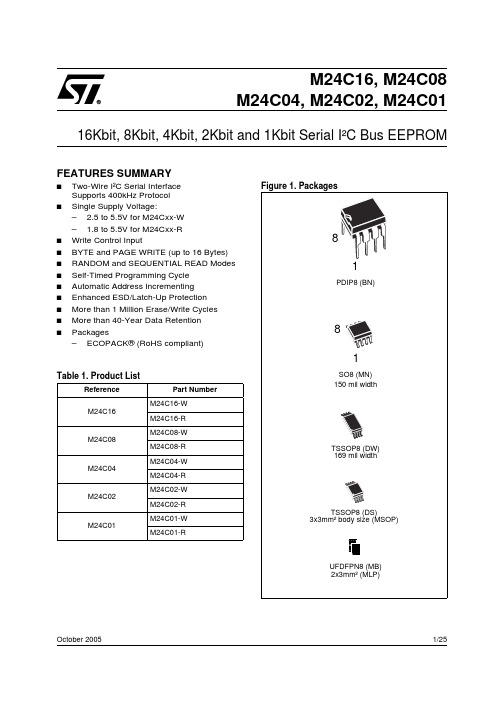

Table 1: Pin Configuration

Pin Designation Type Name and Functions

A0 - A2 SDA SCL WP GND VCC NC

I

Address Inputs Serial Data Serial Clock Input Write Protect Ground Power Supply No Connect

At VCC At GND

Normal Read / Write Operations

Memory Organization

K24C02, 2K SERIAL EEPROM: Internally organized with 32 pages of 8 bytes each, the 2K requires an 8-bit data word address for random word addressing. K24C04, 4K SERIAL EEPROM: Internally organized with 32 pages of 16 bytes each, the 4K requires a 9-bit data word address for random word addressing. K24C08, 8K SERIAL EEPROM: Internally organized with 64 pages of 16 bytes each, the 8K requires a 10-bit data word address for random word addressing. K24C16, 16K SERIAL EEPROM: Internally organized with 128 pages of 16 bytes each, the 16K requires an 11-bit data word address for random word addressing.

NM24C08中文资料

Pin Names

A2 VSS SDA SCL NC VCC Device Address Input Ground Serial Data I/O Serial Clock Input No Connection Power Supply

Dual-in-Line Package (N), SO Package (M8) and TSSOP Package (MT8)

NOTE: Pins designated as "NC" are typically unbonded pins. However some of them are bonded for special testing purposes. Hence if a signal is applied to these pins, care should be taken that the voltage applied on these pins does not exceed the VCC applied to the device. This will ensure proper operation.

Connection Diagrams

Dual-in-Line Package (N), SO Package (M8) and TSSOP Package (MT8)

NC NC A2 VSS 1 2 8 7 VCC NC SCL SDA

DS500071-2

NM24C08

3 4 6 5

See Package Number N08E, M08A and MTC08

2

NM24C08/09 Rev. G

元器件交易网

NM24C08/09 – 8K-Bit Standard 2-Wire Bus Interface Serial EEPROM

K24c08

图5:写字节

第7页

K24C08

图6:写页面

图7:读当前地址

图8:自由读

第8页

K24C08

图9:连续读

电气特性

极限参数 直流供电压………………………-0.3V~+6.5V 输入/输出电压……………………GND-0.3V ~Vcc+0.3V 工作环境温度……………………-40℃ ~+85℃ 存储温度……………………………………-65℃ to +150℃ 备注 如果外加条件超过“极限额定参数”的额定值,将会对芯片造成永久性的破坏。这些仅是外加条件的极 限额定参数,本说明书中正常工作条件下的功能和性能参数并不适用于这些极限条件或其它任何超过本 说明书标明的正常工作条件外的情况。长时间牌极限条件下,将影响器件的可靠性。

页写: 8K器件能实现16字节页写。 页写操作与字节写操作的启动方式基本相同,不同的是,在时钟送入第一组数据并得到EEPROM应答后,主控 器件不是发出停止命令,而是继续发送其余十五组数据,每收到一组数据EEPROM都会返回应答信号。主控器 件必须以停止命令来结束页写操作(参见图6)。 每接收一组数据,数据地址的低四位会在内部自动递加。数据地址的高几位不会变化,保持存储器的页地址 不变,当内部产生的数据地址达到页边界时,数据地址将会翻转,接下来的数据的写入地址将被置为同一页 的最小地址。如果有超过16组数据被送入EEPROM,数据地址将回到最先写入的地址,先前写入的数据将被覆 盖。

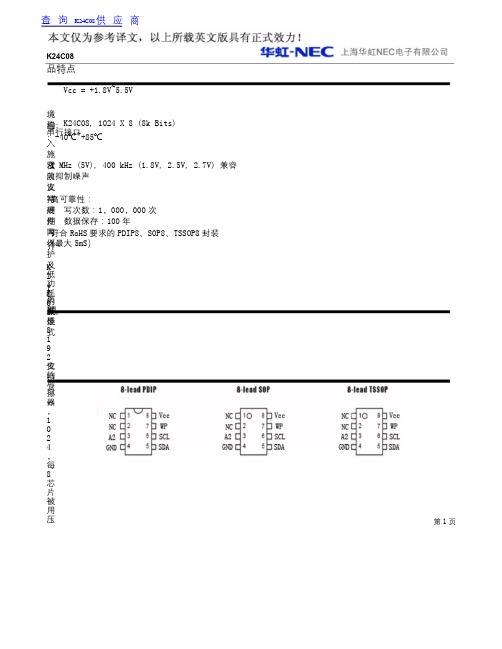

查询K24C08供应商

K24C08

产品特点

工作电压: Vcc = +1.8V~5.5V 工作环境温度范围: -40℃~+85℃ 内部结构: K24C08, 1024 X 8 (8k Bits) 两线串行接口 输入引脚经施密特触发器滤波抑制噪声 双向数据传输协议 1 MHz (5V), 400 kHz (1.8V, 2.5V, 2.7V) 兼容 支持硬件写保护 16字节页写模式 支持分区页写 写周期内部定时(最大5mS) 高可靠性: 写次数:1,000,000次 数据保存:100年 符合RoHS要求的PDIP8、SOP8、TSSOP8封装

IS24C08中文资料

IS24C01IS24C02IS24C04IS24C08IS24C16ISSI®Copyright © 2002 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.1K-bit/2K-bit/4K-bit/8K-bit/16K-bit 2-WIRE SERIAL CMOS EEPROMAPRIL 2002DESCRIPTIONThe IS24CXX (refers to IS24C01, IS24C02, IS24C04,IS24C08, IS24C16) family is a low-cost and low voltage 2-wire Serial EEPROM. It is fabricated using ISSI’s advanced CMOS EEPROM technology and provides a low power and low voltage operation. The IS24CXX family features a write protection feature, and is available in 8-pin DIP and 8-pin SOIC packages.The IS24C01 is a 1K-bit EEPROM; IS24C02 is a 2K-bit EEPROM; IS24C04 is a 4K-bit EEPROM; IS24C08 is a 8K-bit EEPROM; IS24C16 is a 16K-bit EEPROM.The IS24C01 and IS24C02 are available in 8-pin MSOP package. The IS24C01, IS24C02, IS24C04, and IS24C08are available in 8-Pin TSSOP package.Automotive data is preliminary.FEATURES•Low Power CMOS Technology–Standby Current less than 8 µA (5.5V)–Read Current (typical) less than 1 mA (5.5V)–Write Current (typical) less than 3 mA (5.5V)•Flexible Voltage Operation–Vcc = 1.8V to 5.5V for –2 version –Vcc = 2.5V to 5.5V for –3 version •400 KHz (I 2C Protocol) Compatibility •Hardware Data Protection–Write Protect Pin •Sequential Read Feature•Filtered Inputs for Noise Suppression •8-pin PDIP and 8-pin SOIC packages •8-pin TSSOP (1K,2K, 4K & 8K only)•8-pin MSOP (1K,2K only)•Self time write cycle with auto clear 5 ms @ 2.5V •Organization:–IS24C01128x8(one block of 128 bytes)–IS24C02256x8(one block of 256 bytes)–IS24C04512x8(two blocks of 256 bytes)–IS24C081024x8(four blocks of 256 bytes)–IS24C162048x8(eight blocks of 256 bytes)•Page Write Buffer•Two-Wire Serial Interface–Bi-directional data transfer protocol •High Reliability–Endurance: 1,000,000 Cycles –Data Retention: 100 Years•Commercial, Industrial and Automotive tempera-ture ranges元器件交易网元器件交易网IS24C01IS24C02IS24C04IS24C08 IS24C16ISSI®FUNCTIONAL BLOCK DIAGRAM2Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.DIS24C01IS24C02IS24C04IS24C08 IS24C16ISSI®PIN DESCRIPTIONSA0-A2Address InputsSDA Serial Address/Data I/O SCL Serial Clock Input WP Write Protect Input Vcc Power Supply GNDGroundSCLThis input clock pin is used to synchronize the data transfer to and from the device.SDAThe SDA is a Bi-directional pin used to transfer addresses and data into and out of the device. The SDA pin is an open drain output and can be wire-Ored with other open drain or open collector outputs.The SDA bus requires a pullup resistor to Vcc.A0, A1, A2The A0, A1 and A2 are the device address inputs. The IS24C01 and IS24C02 use the A0, A1, and A2 for hardware addressing and a total of 8 devices may be used on a single bus system.PIN CONFIGURATION8-Pin DIP and SOIC8 Pin TSSOP (1K, 2K, 4K and 8K)8-Pin MSOP (1K, 2K)12348765A0A1A2GNDVCC WP SCL SDAThe IS24C04 uses A1 and A2 pins for hardwire addressing and a total of four devices may be addressed on a single bus system.The A0 pin is not used by IS24C04. This pin can be left floating or tied to GND or Vcc.The IS24C08 only use A2 input for hardwire addressing and a total of two devices may be addressed on a single bus system.The A0 and A1 pins are not used by IS24C08. They may be left floating or tied to either GND or Vcc.These pins are not used by IS24C16. A0 and A1 may be left floating or tied to either GND or Vcc. A2 should be tied to either GND or Vcc.WPWP is the Write Protect pin. On the 24C01, 24C02, IS24C04and 24C08, if the WP pin is tied to V CC the entire array becomes Write Protected (Read only). On the 24C16, if the WP pin is tied to Vcc the upper half array becomes Write Protected (Read only). When WP is tied to GND or left floating normal read/write operations are allowed to the device.元器件交易网IS24C01IS24C02IS24C04IS24C08 IS24C16ISSI®DEVICE OPERATIONThe IS24CXX family features a serial communication and supports a bi-directional 2-wire bus transmission protocol. 2-WIRE BUSThe two-wire bus is defined as a Serial Data line(SDA), and a Serial Clock Line (SCL). The protocol defines any device that sends data onto the SDA bus as a transmitter, and the receiving devices as a receiver. The bus is controlled by MASTER device which generates the SCL, controls the bus access and generates the STOP and START conditions. The IS24CXX is the SLAVE device on the bus.THE BUS PROTOCOL:--Data transfer may be initiated only when the bus is not busy--During a data transfer, the data line must remain stable whenever the clock line is high. Any changes in the data line while the clock line is high will be interpreted as a START or STOP condition.The state of the data line represents valid data when after a START condition, the data line is stable for the duration of the HIGH period of the clock signal. The data on the line must be changed during the LOW period of the clock signal. There is one clock pulse per bit of data. Each data transfer is initiated with a START condition and terminated with a STOP condition.START CONDITIONThe START condition precedes all commands to the devices and is defined as a HIGH to LOW transition of SDA when SCL is HIGH. The IS24CXX monitors the SDA and SCL lines and will not respond until the START condition is met.STOP CONDITIONThe STOP condition is defined as a LOW to HIGH transition of SDA when SCL is HIGH. All operations must end with a STOP condition.ACKNOWLEDGEAfter a successful data transfer, each receiving device is required to generate an acknowledge. The Acknowledging device pulls down the SDA line.DEVICE ADDRESSINGThe MASTER begins a transmission by sending a START condition. The MASTER then sends the address of the particular slave devices it is requesting. The SLAVE address is 8 bytes.The four most significant bytes of the address are fixed as 1010 for the IS24CXX.For the IS24C16, the bytes(B2, B1 and B0) are used for memory page addressing (the IS24C16 is organized as eight blocks of 256 bytes).For the IS24C04 out of the next three bytes, B0 is for Memory Page Addressing (the IS24C04 is organized as two blocks of 256 bytes) and A2 and A1 bytes are used as device address bytes and must compare to its hard-wire inputs pins (A2 and A1). Up to four IS24C04's may be individually addressed by the system. The page addressing bytes for IS24Cxx should be considered the most significant bytes of the data word address which follows.For the IS24C08 out of the next three bytes, B1 and B0 are for memory page addressing (the IS24C08 is organized as four blocks of 256 bytes) and the A2 bit is used as device address bit and must compare to its hard-wired input pin (A2). Up to two IS24C08 may be individually addressed by the system. The page addressing bytes for IS24CXX should be considered the most significant bytes of the data word address which follows.For the IS24C01 and IS24C02, the A0, A1, and A2 are used as device address bytes and must compare to its hard-wired input pins (A0, A1, and A2) Up to Eight IS24C01 and/ or IS24C02's may be individually addressed by the system. The last bit of the slave address specifies whether a Read or Write operation is to be performed. When this bit is set to 1, a Read operation is selected, and when set to 0, a Write operation is selected.After the MASTER sends a START condition and the SLAVE address byte, the IS24CXX monitors the bus and responds with an Acknowledge (on the SDA line) when its address matches the transmitted slave address. The IS24CXX pulls down the SDA line during the ninth clock cycle, signaling that it received the eight bytes of data. The IS24CXX then performs a Read or Write operation depending on the state of the R/W bit.WRITE OPERATIONBYTE WRITEIn the Byte Write mode, the Master device sends the START condition and the slave address information(with the R/W set to Zero) to the Slave device. After the Slave generates an acknowledge, the Master sends the byte address that is to be written into the address pointer of the IS24CXX. After receiving another acknowledge from the Slave, the Master device transmits the data byte to be written into the address memory location. The IS24CXX acknowledges once more and the Master generates the STOP condition, at which time the device begins its internal programming cycle. While this internal cycle is in progress, the device will not respond to any request from the Master device.元器件交易网4Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.DIS24C01IS24C02IS24C04IS24C08 IS24C16ISSI®condition and the IS24CXX discontinues transmission. If 'n' is the last byte of the memory, then the data from location '0' will be transmitted. (Refer to Current Address Read Diagram.)RANDOM ADDRESS READSelective READ operations allow the Master device to select at random any memory location for a READ operation.The Master device first performs a 'dummy' write operation by sending the START condition, slave address and word address of the location it wishes to read. After the IS24CXX acknowledge the word address, the Master device resends the START condition and the slave address, this time with the R/W bit set to one. The IS24CXX then responds with its acknowledge and sends the data requested. The master device does not send an acknowledge but will generate a STOP condition. (Refer to Random Address Read Diagram.)SEQUENTIAL READSequential Reads can be initiated as either a Current Address Read or Random Address Read. After the IS24CXX sends initial byte sequence, the master device now responds with an ACKnowledge indicating it requires additional data from the IS24CXX. The IS24CXX continues to output data for each ACKnowledge received. The master device terminates the sequential READ operation by pulling SDA HIGH (no ACKnowledge) indicating the last data word to be read, followed by a STOP condition.The data output is sequential, with the data from address n followed by the data from address n+1, ... etc.The address counter increments by one automatically,allowing the entire memory contents to be serially read during sequential read operation. When the memory address boundary (127 for IS24C01; 255 for IS24C02; 511 for IS24C04; 1023 for IS24C08; 2047 for IS24C16) is reached,the address counter “rolls over” to address 0, and the IS24CXX continues to output data for each ACKnowledge received. (Refer to Sequential Read Operation Starting with a Random Address READ Diagram.)PAGE WRITEThe IS24CXX is capable of page-WRITE (8-byte for 24C01/02 and 16-byte for 24C04/08/16) operation. A page-WRITE is initiated in the same manner as a byte write, but instead of terminating the internal write cycle after the first data word is transferred, the master device can transmit up to N more bytes (N=7 for 24C01/02 and N=15 for 24C04/08/16). After the receipt of each data word, the IS24CXX responds immediately with an ACKnowledge on SDA line, and the three lower (24C01/24C02) or four lower (24C04/24C08/24C16) order data word address bits are internally incremented by one, while the higher order bits of the data word address remain constant. If the master device should transmit more than N+1 (N=7 for 24C01/02 and N=15 for 24C04/08/16) words, prior to issuing the STOP condition,the address counter will “roll over,” and the previously written data will be overwritten. Once all N+1 (N=7 for 24C01/02 and N=15 for 24C04/08/16) bytes are received and the STOP condition has been sent by the Master, the internal programming cycle begins. At this point, all received data is written to the IS24CXX in a single write cycle. All inputs are disabled until completion of the internal WRITE cycle.ACKNOWLEDGE POLLINGThe disabling of the inputs can be used to take advantage of the typical write cycle time. Once the stop condition is issued to indicate the end of the host's write operation, the IS24CXX initiates the internal write cycle. ACK polling can be initiated immediately. This involves issuing the start condition followed by the slave address for a write operation.If the IS24CXX is still busy with the write operation, no ACK will be returned. If the IS24CXX has completed the write operation, an ACK will be returned and the host can then proceed with the next read or write operation.READ OPERATIONREAD operations are initiated in the same manner as WRITE operations, except that the read/write bit of the slave address is set to “1”. There are three READ operation options: current address read, random address read and sequential read.CURRENT ADDRESS READThe IS24CXX contains an internal address counter which maintains the address of the last byte accessed, incremented by one. For example, if the previous operation is either a read or write operation addressed to the address location n,the internal address counter would increment to address location n+1. When the IS24CXX receives the Device Addressing Byte with a READ operation (read/write bit set to “1”), it will respond an ACKnowledge and transmit the 8-bit data word stored at address location n+1. The master will not acknowledge the transfer but does generate a STOP元器件交易网元器件交易网IS24C01IS24C02IS24C04IS24C08 IS24C16ISSI®TYPICAL SYSTEM BUS CONFIGURATIONSTART AND STOP CONDITIONS6Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.D元器件交易网IS24C01IS24C02IS24C04IS24C08 IS24C16ISSI®DATA VALIDITY PROTOCOL元器件交易网IS24C01IS24C02IS24C04IS24C08 IS24C16ISSI®PAGE WRITE8Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.D元器件交易网IS24C01IS24C02IS24C04IS24C08 IS24C16ISSI®SEQUENTIAL READ元器件交易网IS24C01IS24C02IS24C04IS24C08 IS24C16ISSI®ABSOLUTE MAXIMUM RATINGS(1)Symbol Parameter Value UnitV S Supply Voltage0.5 to +6.25VV P Voltage on Any Pin–0.5 to Vcc + 0.5VT BIAS Temperature Under Bias–40 to +85°CT STG Storage Temperature–65 to +150°CI OUT Output Current5mANotes:1.Stress greater than those listed under ABSOLUTE MAXIMUM RATINGS may causepermanent damage to the device. This is a stress rating only and functional operation of thedevice at these or any other conditions above those indicated in the operational sections ofthis specification is not implied. Exposure to absolute maximum rating conditions forextended periods may affect reliability.OPERATING RANGE(IS24C01-2, IS24C02-2, IS24C04-2 IS24C08-2, & IS24C16-2)Range Ambient Temperature V CCCommercial0°C to +70°C 1.8V to 5.5VIndustrial–40°C to +85°C 1.8V to 5.5VOPERATING RANGE(IS24C01-3, IS24C02-3, IS24C04-3, IS24C08-3, & IS24C16-3)Range Ambient Temperature V CCCommercial0°C to +70°C 2.5V to 5.5VIndustrial–40°C to +85°C 2.5V to 5.5VAutomotive–40°C to +125°C 2.7V to 5.5VNote: Automotive data is preliminary.OPERATING RANGE(IS24C01-5, IS24C02-5, IS24C04-5 IS24C08-5, & IS24C16-5)Range Ambient Temperature V CCAuromotive–40°C to +125°C 4.5V to 5.5VNote: Automotive data is preliminary.10Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.DDC ELECTRICAL CHARACTERISTICSSymbol Parameter Test Conditions Min.Max.Unit V OL1Output LOW Voltage V CC = 1.8V, I OL = 0.15 mA—0.2V V OL2Output LOW Voltage V CC = 2.5V, I OL = 1.0 mA—0.4V V IH Input HIGH Voltage V CC X 0.7V CC + 0.5V V IL Input LOW Voltage–1.0V CC X 0.3VI LI Input Leakage Current V IN = V CC max.—3µAI LO Output Leakage Current—3µA Notes: V IL min and V IH max are reference only and are not tested.POWER SUPPLY CHARACTERISTICSSymbol Parameter Test Conditions Min.Max.UnitI CC1Vcc Operating Current READ at 100 KHz (Vcc = 5V)— 1.0mAI CC2Vcc Operating Current WRITE at 100 KHz (Vcc = 5V)— 3.0mAI SB1Standby Current Vcc = 1.8V— 4.0µAI SB2Standby Current Vcc = 5.5V—8.0µACAPACITANCE(1,2)Symbol Parameter Conditions Max.UnitC IN Input Capacitance V IN = 0V6pFC OUT Output Capacitance V OUT = 0V8pFNotes:1.Tested initially and after any design or process changes that may affect these parameters.2.Test conditions: T A = 25°C, f = 1 MHz, Vcc = 5.0V.12Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.D AC ELECTRICAL CHARACTERISTICS (Over Operating Range)Automotive (T A = –40°C to +125°C) 2.7V-5.5V 4.5V-5.5V Symbol Parameter Test ConditionsMin.Max.Min.Max.Unit f SCL SCL Clock Frequency 01000400KHz T Noise Suppression Time (1)—100—50ns t LOW Clock LOW Period 4.7— 1.2—µs t HIGH Clock HIGH Period4—0.6—µs t BUF Bus Free Time Before New Transmission 4.7— 1.2—µs t SU:STA Start Condition Setup Time 4.7—0.6—µs t SU:STO Stop Condition Setup Time 4.7—0.6—µs t HD:STA Start Condition Hold Time 4—0.6—µs t HD:STO Stop Condition Hold Time 4—0.6—µs t SU:DAT Data In Setup Time 200—100—ns t HD:DAT Data In Hold Time 0—0—ns t DH Data Out Hold Time SCL LOW to SDA Data Out Change 100—50—ns t AA Clock to Output SCL LOW to SDA Data Out Valid0.1 4.50.10.9µs t R SCL and SDA Rise Time(1)—1000—300ns t F SCL and SDA Fall Time (1)—300—300ns t WRWrite Cycle Time—10—10msNote:1. This parameter is characterized but not 100% tested.2. Automotive data is preliminary.AC ELECTRICAL CHARACTERISTICS (Over Operating Rnage)Commercial (T A = 0°C to +70°C) Industrial (T A = –40°C to +85°C) 1.8V-5.5V 2.5V-5.5V Symbol Parameter Test ConditionsMin.Max.Min.Max.Unit f SCL SCL Clock Frequency 01000400KHz T Noise Suppression Time (1)—100—50ns t LOW Clock LOW Period 4.7— 1.2—µs t HIGH Clock HIGH Period4—0.6—µs t BUF Bus Free Time Before New Transmission (1) 4.7— 1.2—µs t SU:STA Start Condition Setup Time 4.7—0.6—µs t SU:STO Stop Condition Setup Time 4.7—0.6—µs t HD:STA Start Condition Hold Time 4—0.6—µs t HD:STO Stop Condition Hold Time 4—0.6—µs t SU:DAT Data In Setup Time 200—100—ns t HD:DAT Data In Hold Time 0—0—ns t DH Data Out Hold Time SCL LOW to SDA Data Out Change 100—50—ns t AA Clock to Output SCL LOW to SDA Data Out Valid 0.1 4.50.10.9µs t R SCL and SDA Rise Time (1)—1000—300ns t F SCL and SDA Fall Time (1)—300—300ns t WRWrite Cycle Time—10—5msNote:1. This parameter is characterized but not 100% tested.AC WAVEFORMS BUS TIMINGWRITE CYCLE TIMINGORDERING INFORMATIONCommercial Range: 0°C to +70°CVol tageFrequency Range Part Number Package100 KHz 1.8V IS24C01-2P300-mil Plastic DIPto 5.5V IS24C01-2G Small Outline (JEDEC STD)IS24C01-2S MSOPIS24C01-2Z TSSOP100 KHz 1.8V IS24C02-2P300-mil Plastic DIPto 5.5V IS24C02-2G Small Outline (JEDEC STD)IS24C02-2S MSOPIS24C02-2Z TSSOP100 KHz 1.8V IS24C04-2P300-mil Plastic DIPto 5.5V IS24C04-2G Small Outline (JEDEC STD)IS24C04-2Z TSSOP100 KHz 1.8V IS24C08-2P300-mil Plastic DIPto 5.5V IS24C08-2G Small Outline (JEDEC STD)IS24C08-2Z TSSOP100 KHz 1.8V IS24C16-2P300-mil Plastic DIPto 5.5V IS24C16-2G Small Outline (JEDEC STD)400 KHz 2.5V IS24C01-3P300-mil Plastic DIPto 5.5V IS24C01-3G Small Outline (JEDEC STD)IS24C01-3S MSOPIS24C01-3Z TSSOP400 KHz 2.5V IS24C02-3P300-mil Plastic DIPto 5.5V IS24C02-3G Small Outline (JEDEC STD)IS24C02-3S MSOPIS24C02-3Z TSSOP400 KHz 2.5V IS24C04-3P300-mil Plastic DIPto 5.5V IS24C04-3G Small Outline (JEDEC STD)IS24C04-3Z TSSOP400 KHz 2.5V IS24C08-3P300-mil Plastic DIPto 5.5V IS24C08-3G Small Outline (JEDEC STD)IS24C08-3Z TSSOP400 KHz 2.5V IS24C16-3P300-mil Plastic DIPto 5.5V IS24C16-3G Small Outline (JEDEC STD)14Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.DORDERING INFORMATIONIndustrial Range: –40°C to +85°CVoltageFrequency Range Part Number Package100 KHz 1.8V IS24C01-2PI300-mil Plastic DIPto 5.5V IS24C01-2GI Small Outline (JEDEC STD)IS24C01-2SI MSOPIS24C01-2ZI TSSOP100 KHz 1.8V IS24C02-2PI300-mil Plastic DIPto 5.5V IS24C02-2GI Small Outline (JEDEC STD)IS24C02-2SI MSOPIS24C02-2ZI TSSOP100 KHz 1.8V IS24C04-2PI300-mil Plastic DIPto 5.5V IS24C04-2GI Small Outline (JEDEC STD)IS24C04-2ZI TSSOP100 KHz 1.8V IS24C08-2PI300-mil Plastic DIPto 5.5V IS24C08-2GI Small Outline (JEDEC STD)IS24C08-2ZI TSSOP100 KHz 1.8V IS24C16-2PI300-mil Plastic DIPto 5.5V IS24C16-2GI Small Outline (JEDEC STD) 400 KHz 2.5V IS24C01-3PI300-mil Plastic DIPto 5.5V IS24C01-3GI Small Outline (JEDEC STD)IS24C01-3SI MSOPIS24C01-3ZI TSSOP400 KHz 2.5V IS24C02-3PI300-mil Plastic DIPto 5.5V IS24C02-3GI Small Outline (JEDEC STD)IS24C02-3SI MSOPIS24C02-3ZI TSSOP400 KHz 2.5V IS24C04-3PI300-mil Plastic DIPto 5.5V IS24C04-3GI Small Outline (JEDEC STD)IS24C04-3ZI TSSOP400 KHz 2.5V IS24C08-3PI300-mil Plastic DIPto 5.5V IS24C08-3GI Small Outline (JEDEC STD)IS24C08-3ZI TSSOP400 KHz 2.5V IS24C16-3PI300-mil Plastic DIPto 5.5V IS24C16-3GI Small Outline (JEDEC STD)ORDERING INFORMATIONAutomotive Range: –40°C to +125°CVoltageFrequency Range Part Number Package100 KHz 2.7V IS24C01-3PA300-mil Plastic DIPto 5.5V IS24C01-3GA Small Outline (JEDEC STD)IS24C01-3SA MSOPIS24C01-3ZA TSSOP100 KHz 2.7V IS24C02-3PA300-mil Plastic DIPto 5.5V IS24C02-3GA Small Outline (JEDEC STD)IS24C02-3SA MSOPIS24C02-3ZA TSSOP100 KHz 2.7V IS24C04-3PA300-mil Plastic DIPto 5.5V IS24C04-3GA Small Outline (JEDEC STD)IS24C04-3ZA TSSOP100 KHz 2.7V IS24C08-3PA300-mil Plastic DIPto 5.5V IS24C08-3GA Small Outline (JEDEC STD)IS24C08-3ZA TSSOP100 KHz 2.7V IS24C16-3PA300-mil Plastic DIPto 5.5V IS24C16-3GA Small Outline (JEDEC STD)400 KHz 4.5V IS24C01-5PA300-mil Plastic DIPto 5.5V IS24C01-5GA Small Outline (JEDEC STD)IS24C01-5SA MSOPIS24C01-5ZA TSSOP400 KHz 4.5V IS24C02-5PA300-mil Plastic DIPto 5.5V IS24C02-5GA Small Outline (JEDEC STD)IS24C02-5SA MSOPIS24C02-5ZA TSSOP400 KHz 4.5V IS24C04-5PA300-mil Plastic DIPto 5.5V IS24C04-5GA Small Outline (JEDEC STD)IS24C04-5ZA TSSOP400 KHz 4.5V IS24C08-5PA300-mil Plastic DIPto 5.5V IS24C08-5GA Small Outline (JEDEC STD)IS24C08-5ZA TSSOP400 KHz 4.5V IS24C16-5PA300-mil Plastic DIPto 5.5V IS24C16-5GA Small Outline (JEDEC STD)Note: Automotive data is preliminary.16Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.D。

I2C总线24C08(PDF档)

I2C总线接口 EEPROM存储器

目前,市场上I2C总线接口器件有多种,例如A/D转换器、D/A转换 器(PCF8591)、时钟芯片和存储器(24C08)等。这里以典型的I2C 总线接口的存储器为例进行介绍。 I2C总线接口EEPROM存储器是一种采用I2C总线接口的串行总线存 储器,这类存储器具有体积小、引脚少、功耗低、工作电压范围宽等 特点。目前,Atmel、MicroChip、National等公司均提供各种型号的 I2C总线接口的串行EEPROM存储器。在单片机系统中使用较多的 EEPROM存储器是24系列串行EEPROM。其具有型号多、容量大、 支持I2C总线协议、占用单片机I/O端口少,芯片扩展方便、读写简单 等优点。

读操作 读操作有三种基本操作:当前地址读、随机读和顺序读。 下图给出的是顺序读的时序图。应当注意的是,为了结束读操 作,主机必须在第9个周期间发出停止条件或者在第9个时钟周 期内保持SDA为高电平,然后发出停止条件。

I2C协议起始信号时序

起始信号用于开始I2C总线通信。其中,起始信号是在时钟线SCL为高电平 期间,数据SDA上高电平向低电平变化的下降沿信号。起始信号出现以后, 才可以进行后续的I2C总线寻址或数据传输等

I2C总线数据操作

在I2C总线上,数据是伴随着时钟脉冲,一位一位地传送的,数据位 由低到高传送,每位数据占一个时钟脉冲。I2C总线上的在时钟线 SCL高电平期间,数据线SDA的状态就表示要传送的数据,高电平为 数据1,低电平为数据0。在数据传送时,SDA上数据的改变在时钟线 为低电平时完成,而SCL为高电平时,SDA必须保持稳定,否则SDA 上的变化会被当作起始或终止信号而致使数据传输停止。

I2C总线工作原理

存储器24C08的串口读取与写入程序

l p 嚣工

图1 16 2010 V01...10

万方数据

一¨¨lf…. —————————————i沥洒一DN制作天地嬲 F'乏口JE亡Ts潮

实际电路构成。图2是24C08A的引脚图和外

方的时钟将不可能做到绝对的统一。总是会有一定差

观图。

异,主要包括中心频率的差异与时钟频率的漂移。电

子振荡器的频率虽然非常非常稳定,但是随环境气温

可以提高程序执行的效率。在连续读取模式下。

不会得到响应.包括单片机发出的标准总线起动

单片机完整读到每一字节数据后必须做出应答,

信号。具体实现方法就是使SDA线维持高电平。

由24C08识别后.控制内部地址存储器自动加

使单片机得不到应答进入等待状态,直至24C08

1,下一地址所储存的数据就会自动移位输出。

大的功能就是起到直观显示编缉24C08数据

动同步。这样的做法,将把双方时钟差异限定在十个

的作用。单片机依然使用比较常见的51系列

时钟周期之内。只要双方时钟误差保持在5%以内。

中的89S51。将编制好的读写程序写入内部

数据传输基本上不会出错。付出的代价是传输速率降

便好了。在电脑一方,需要一种功能全面的 串口调试软件配合,这里使用PORTTEST这 种串口调试工具。单片机与电脑之间的联机 通讯通过RS232串1:3完成。RS232接口芯片 采用MAX3232,MAX3232的最大数据传输率 低于1 Mbps,而24C08的总线最高时钟频率 400KHZ,所以双方的传输速率还是很相称的。 这里采用RS232通讯方式中最简单的发送、接 收、地端三线传输的方式。

循环移位。先期发出的数据将被复写,直至收到

取到两字节数据后,内部相应地址储存的数据将

24C08

DS21081D-page 12© 1996 Microchip Technology Inc.Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. No repre-sentation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip’s products as critical components in life support systems is not autho-rized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights. The Microchip logo and name are registered trademarks of Microchip Technology Inc. All rights reserved. All other trademarks mentioned herein are the property of their respective companies.W ORLDWIDE S ALES & S ERVICEASIA/PACIFIC China Microchip Technology Unit 406 of Shanghai Golden Bridge Bldg.2077 Yan’an Road West, Hongiao District Shanghai, Peoples Republic of China Tel: 86 21 6275 5700 Fax: 011 86 21 6275 5060 Hong Kong Microchip Technology RM 3801B, Tower Two Metroplaza 223 Hing Fong Road Kwai Fong, N.T. Hong Kong Tel: 852 2 401 1200 Fax: 852 2 401 3431India Microchip Technology No. 6, Legacy, Convent Road Bangalore 560 025 India Tel: 91 80 526 3148 Fax: 91 80 559 9840Korea Microchip Technology 168-1, Youngbo Bldg. 3 Floor Samsung-Dong, Kangnam-Ku,Seoul, Korea Tel: 82 2 554 7200 Fax: 82 2 558 5934Singapore Microchip Technology 200 Middle Road #10-03 Prime Centre Singapore 188980Tel: 65 334 8870 Fax: 65 334 8850Taiwan, R.O.C Microchip Technology 10F-1C 207Tung Hua North Road Taipei, Taiwan, ROC Tel: 886 2 717 7175 Fax: 886 2 545 0139EUROPE United Kingdom Arizona Microchip Technology Ltd.Unit 6, The Courtyard Meadow Bank, Furlong Road Bourne End, Buckinghamshire SL8 5AJ Tel: 44 1628 850303 Fax: 44 1628 850178France Arizona Microchip Technology SARL Zone Industrielle de la Bonde 2 Rue du Buisson aux Fraises 91300 Massy - France Tel: 33 1 69 53 63 20 Fax: 33 1 69 30 90 79Germany Arizona Microchip Technology GmbH Gustav-Heinemann-Ring 125D-81739 Muenchen, Germany Tel: 49 89 627 144 0 Fax: 49 89 627 144 44Italy Arizona Microchip Technology SRL Centro Direzionale Colleone Pas Taurus 1Viale Colleoni 120041 Agrate Brianza Milan Italy Tel: 39 39 6899939 Fax: 39 39 689 9883JAPAN Microchip Technology Intl. Inc.Benex S-1 6F 3-18-20, Shin Yokohama Kohoku-Ku, Yokohama Kanagawa 222 Japan Tel: 81 45 471 6166 Fax: 81 45 471 61229/3/96AMERICASCorporate OfficeMicrochip Technology Inc.2355 West Chandler Blvd.Chandler, AZ 85224-6199Tel: 602 786-7200 Fax: 602 786-7277Technical Support: 602 786-7627Web: AtlantaMicrochip Technology Inc.500 Sugar Mill Road, Suite 200BAtlanta, GA 30350Tel: 770 640-0034 Fax: 770 640-0307BostonMicrochip Technology Inc.5 Mount Royal AvenueMarlborough, MA 01752Tel: 508 480-9990 Fax: 508 480-8575ChicagoMicrochip Technology Inc.333 Pierce Road, Suite 180Itasca, IL 60143Tel: 708 285-0071 Fax: 708 285-0075DallasMicrochip Technology Inc.14651 Dallas Parkway, Suite 816Dallas, TX 75240-8809Tel: 972 991-7177 Fax: 972 991-8588DaytonMicrochip Technology Inc.Suite 150Two Prestige PlaceMiamisburg, OH 45342Tel: 513 291-1654 Fax: 513 291-9175Los AngelesMicrochip Technology Inc.18201 Von Karman, Suite 1090Irvine, CA 92612Tel: 714 263-1888 Fax: 714 263-1338New YorkMicrochip Technmgy Inc.150 Motor Parkway, Suite 416Hauppauge, NY 11788Tel: 516 273-5305 Fax: 516 273-5335San JoseMicrochip Technology Inc.2107 North First Street, Suite 590San Jose, CA 95131Tel: 408 436-7950 Fax: 408 436-7955TorontoMicrochip Technology Inc.5925 Airport Road, Suite 200Mississauga, Ontario L4V 1W1, CanadaTel: 905 405-6279Fax: 905 405-6253All rights reserved. © 1996, Microchip Technology Incorporated, USA. 9/96Printed on recycled paper.。

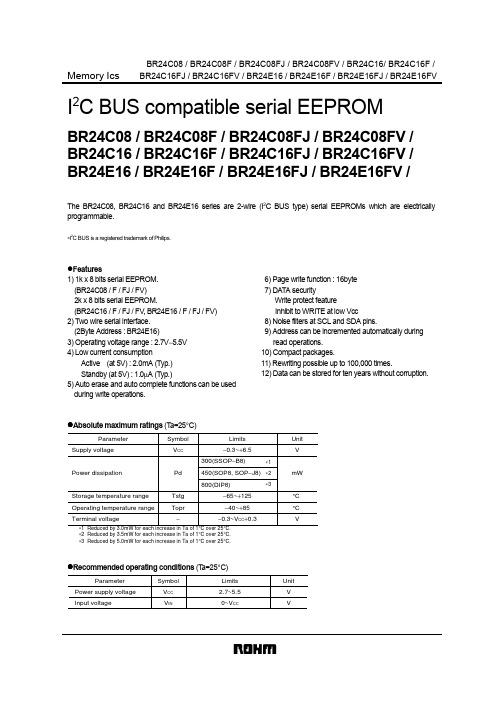

BR24C08中文资料

∗3

Storage temperature range

Tstg

−65~+125

°C

Operating temperature range

Topr

−40~+85

°C

Terminal voltage

−

−0.3~VCC+0.3

V

∗1 Reduced by 3.0mW for each increase in Ta of 1°C over 25°C. ∗2 Reduced by 3.5mW for each increase in Ta of 1°C over 25°C. ∗3 Reduced by 5.0mW for each increase in Ta of 1°C over 25°C.

VIL

−

−

0.3VCC

V

VOL

−

−

0.4

V

ILI

−1

−

1

µA

ILO

−1

−

1

µA

ICC

−

−

3.0

mA

andby current

ISB

−

−

3.0

µA

This product is not designed for protection against radioactive rays.

Conditions − −

tWR

−

−

10

−

−

10

ms

Noise erase valid time (SDA/SCL pins)

tI

−

− 0.05 −

− 0.1

µs

元器件交易网

TC24C08两线EEPROM存储芯片

TC24C08A The TC24C04A/08A/16A series are 4,096/8,192/16,384 bits of serial Electrical Erasable and TC24C04A/08A/16A: V page1Two-Wire Serial EEPROM4K, 8K and 16K (8-bit wide)FEATURES❑Low voltage and low power operations:CC = 1.8V to 5.5V❑ Maximum Standby current < 1µA (typically 0.02µA and 0.06µA @ 1.8V and 5.5V respectively). ❑ 16 bytes page write mode.❑ Partial page write operation allowed.❑ Internally organized: 512 x 8 (4K), 1024 x 8 (8K), 2048 x 8 (16K). ❑ Standard 2-wire bi-directional serial interface. ❑ Schmitt trigger, filtered inputs for noise protection. ❑ Self-timed Write Cycle (5ms maximum).❑ 1 MHz (5V), 400 kHz (1.8V, 2.5V, 2.7V) Compatibility. ❑ Automatic erase before write operation.❑ Write protect pin for hardware data protection.❑ High reliability: typically 1, 000,000 cycles endurance. ❑ 100 years data retention.❑ Industrial temperature range (-40o C to 85o C).❑Standard 8-lead DIP/SOP/MSOP/TSSOP/DFN and 5-lead SOT-23/TSOT-23 Pb-free packages.DESCRIPTIONProgrammable Read Only Memory, commonly known as EEPROM. They are organized as 512/1,024/2,048 words of 8 bits (1 byte) each. The devices are fabricated with proprietary advanced CMOS process for low power and low voltage applications. These devices are available in standard 8-lead DIP, 8-lead SOP, 8-lead TSSOP, 8-lead DFN, 8-lead MSOP, and 5-lead SOT-23/TSOT-23 packages. A standard 2-wire serial interface is used to address all read and write functions. Our extended V CC range (1.8V to 5.5V) devices enables wide spectrum of applications.PIN CONFIGURATIONPin Name Pin Function A2, A1, A0 Device Address Inputs SDA Serial Data Input / Open Drain Output SCL Serial Clock Input WP Write Protect NC No-ConnectTC24C08A TC24C04A/08A/16AAll these packaging types come in conventional or Pb-free certified.VCC W P SCL SDAA2A1A0G 8L DIP 8L SOP 8L TSSOP W P VCCG ND5L SOT-23SCL 8L DFN8L M SOP 5L TSO T-23ABSOLUTE MAXIMUM RATINGSIndustrial operating temperature: -40℃ to 85℃ Storage temperature:-50℃ to 125℃Input voltage on any pin relative to ground: -0.3V to V CC + 0.3V Maximum voltage: 8VESD protection on all pins: >2000V* Stresses exceed those listed under “Absolute Maximum Rating” may cause permanent damage to the device. Functional operation of the device at conditions beyond those listed in the specification is not guaranteed. Prolonged exposure to extreme conditions may affect device reliability or functionality . page1TC24C08A A0 pin as no-connect. TC24C08A has both A0 and A1 pins as no-connect. For TC24C16A, all device . TC24C04A has The TC24C04A/08A/16A devices have a WP pin to protect the whole EEPROM array from programming.PIN DESCRIPTIONS(A) SERIAL CLOCK (SCL)The rising edge of this SCL input is to latch data into the EEPROM device while the falling edge of this clock is to clock data out of the EEPROM device. (B) DEVICE / CHIP SELECT ADDRESSES (A2, A1, A0)These are the chip select input signals for the serial EEPROM devices. Typically, these signals are hardwired to either V IH or V IL . If left unconnected, they are internally recognized as V IL address pins (A0-A2) are no-connect. (C) SERIAL DATA LINE (SDA)SDA data line is a bi-directional signal for the serial devices. It is an open drain output signal and can be wired-OR with other open-drain output devices. (D) WRITE PROTECT (WP)Programming operations are allowed if WP pin is left un-connected or input to V IL . Conversely all programming functions are disabled if WP pin is connected to V IH or V CC. Read operations is not affected by the WP pin’s input level.Table A page1random word addressing to TC24C04A/08A/16A will require 9/10/11 bits data word addresses respectively.The TC24C04A/08A/16A devices have 32/64/128 pages respectively. Since each page has 16 bytes,TC24C16A(None)TC24C08A A2, A1, TC24C04A A2, A1 A0Device Chip Select/DeviceAddress Pins UsedNo-Connect Pins Max number of similardevices on the samebus4A0 2 A2, A1, A01MEMORY ORGANIZATIONDEVICE OPERATION(A) SERIAL CLOCK AND DATA TRANSITIONSThe SDA pin is typically pulled to high by an external resistor. Data is allowed to change only when Serial clock SCL is at V IL . Any SDA signal transition may interpret as either a START or STOP condition as described below. (B) START CONDITIONWith SCL V IH , a SDA transition from high to low is interpreted as a START condition. All valid commands must begin with a START condition. page1(C) STOP CONDITIONWith SCL V IH , a SDA transition from low to high is interpreted as a STOP condition. All valid read or write commands end with a STOP condition. The device goes into the STANDBY mode if it is after a read command. A STOP condition after page or byte write command will trigger the chip into the STANDBY mode after the self-timed internal programming finish. (D) ACKNOWLEDGEThe 2-wire protocol transmits address and data to and from the EEPROM in 8 bit words. The EEPROM acknowledges the data or address by outputting a "0" after receiving each word. The ACKNOWLEDGE signal occurs on the 9th serial clock after each word. (E) STANDBY MODEThe EEPROM goes into low power STANDBY mode after a fresh power up, after receiving a STOP bit in read mode, or after completing a self-time internal programming operation.Figure 1: Timing diagram for START and STOP conditionsFigure 2: Timing diagram for output ACKNOWLEDGESCLSDASTART ConditionSTOP ConditionData Data Valid TransitionSCLData inData out START ConditionACK page1TC24C04A/08A/16A are organized to have 16 bytes per TC24C16A does not use any device address bit. Only one TC24C16A device can be used on the on 2-wire ) device address bit. Only two TC24C08A devices can be wired-OR on the ) device address bits. Only four TC24C04A devices can be wired-OR on TC24C08A uses only A2 (5TC24C04A uses A2 (5DEVICE ADDRESSINGThe 2-wire serial bus protocol mandates an 8 bits device address word after a START bit condition to invoke valid read or write command. The first four most significant bits of the device address must be 1010, which is common to all serial EEPROM devices. The next three bits are device address bits. These three device address bits (5th , 6th and 7th ) are to match with the external chip select/address pin states. If a match is made, the EEPROM device outputs an ACKNOWLEDGE signal after the 8th read/write bit, otherwise the chip will go into STANDBY mode. However, matching may not be needed for some or all device address bits (5th , 6th and 7th ) as noted below. The last or 8th bit is a read/write command bit. If the 8th bit is at V IH then the chip goes into read mode. If a “0” is detected, the device enters programming mode.th ) and A1 (6th the same 2-wire bus. Their corresponding chip select address pins A2 and A1 must be hard wired and coded from 00 (b) to 11 (b). Chip select address pin A0 is not used.th same 2-wire bus. Their corresponding chip select address pin A2 must be hard-wired and coded from 0 (b) to 1 (b). Chip select address pins A1 and A0 are not used.bus. Chip Select address pins A2, A1, and A0 are not used.WRITE OPERATIONS(A) BYTE WRITEA byte write operation starts when a micro-controller sends a START bit condition, follows by a proper EEPROM device address and then a write command. If the device address bits match the chip select address, the EEPROM device will acknowledge at the 9th clock cycle. The micro-controller will then send the rest of the lower 8 bits word address. At the 18th cycle, the EEPROM will acknowledge the 8-bit address word. The micro-controller will then transmit the 8 bit data. Following an ACKNOWLDEGE signal from the EEPROM at the 27th clock cycle, the micro-controller will issue a STOP bit. After receiving the STOP bit, the EEPROM will go into a self-timed programming mode during which all external inputs will be disabled. After a programming time of T WC , the byte programming will finish and the EEPROM device will return to the STANDBY mode. (B) PAGE WRITEA page write is similar to a byte write with the exception that one to sixteen bytes can be programmed along the same page or memory row. All memory row or page.With the same write command as the byte write, the micro-controller does not issue a STOP bit after sending the 1st byte data and receiving the ACKNOWLEDGE signal from the EEPROM on the 27th clock cycle. Instead it sends out a second 8-bit data word, with the EEPROM acknowledging at the 36th cycle. This data sending and EEPROM acknowledging cycle repeats until the micro-controller sends a STOP bit after the n 9th clock cycle. After which the EEPROM device will go into a self-timed partial or full page programming mode. After the page programming completes after a time of T WC , the devices will return to the STANDBY mode. page1The least significant 4 bits of the word address (column address) increments internally by one afterreceiving each data word. The rest of the word address bits (row address) do not change internally, butpointing to a specific memory row or page to be programmed. The first page write data word can be ofany column address. Up to 16 data words can be loaded into a page. If more then 16 data words areloaded, the 17th data word will be loaded to the 1st data word column address. The 18th data word willbe loaded to the 2nd data word column address and so on. In other word, data word address (columnaddress) will “roll” over the previously loaded data.(C) ACKNOWLEDGE POLLINGACKNOWLEDGE polling may be used to poll the programming status during a self-timed internalprogramming. By issuing a valid read or write address command, the EEPROM will not acknowledge atthe 9th clock cycle if the device is still in the self-timed programming mode. However, if the programmingcompletes and the chip has returned to the STANDBY mode, the device will return a validACKNOWLEDGE signal at the 9th clock cycle.READ OPERATIONSThe read command is similar to the write command except the 8th read/write bit in address word is set to “1”.The three read operation modes are described as follows:(A) CURRENT ADDRESS READThe EEPROM internal address word counter maintains the last read or write address plus one if thepower supply to the device has not been cut off. To initiate a current address read operation, the micro-controller issues a START bit and a valid device address word with the read/write bit (8th) set to “1”. TheEEPROM will response with an ACKNOWLEDGE signal on the 9th serial clock cycle. An 8-bit data wordwill then be serially clocked out. The internal address word counter will then automatically increase byone. For current address read the micro-controller will not issue an ACKNOWLEDGE signal on the 18thclock cycle. The micro-controller issues a valid STOP bit after the 18th clock cycle to terminate the readoperation. The device then returns to STANDBY mode.(B) SEQUENTIAL READThe sequential read is very similar to current address read. The micro-controller issues a START bitand a valid device address word with read/write bit (8th) set to “1”. The EEPROM will response with anACKNOWLEDGE signal on the 9th serial clock cycle. An 8-bit data word will then be serially clocked out.Meanwhile the internally address word counter will then automatically increase by one. Unlike currentaddress read, the micro-controller sends an ACKNOWLEDGE signal on the 18th clock cycle signalingthe EEPROM device that it wants another byte of data. Upon receiving the ACKNOWLEDGE signal, theEEPROM will serially clocked out an 8-bit data word based on the incremented internal address counter.If the micro-controller needs another data, it sends out an ACKNOWLEDGE signal on the 27th clockcycle. Another 8-bit data word will then be serially clocked out. This sequential read continues as longas the micro-controller sends an ACKNOWLEDGE signal after receiving a new data word. When theinternal address counter reaches its maximum valid address, it rolls over to the beginning of the memoryarray address. Similar to current address read, the micro-controller can terminate the sequential read bynot acknowledging the last data word received, but sending a STOP bit afterwards instead.(C) RANDOM READRandom read is a two-steps process. The first step is to initialize the internal address counter with atarget read address using a “dummy write” instruction. The second step is a current address read.To initialize the internal address counter with a target read address, the micro-controller issues a STARTbit first, follows by a valid device address with the read/write bit (8th) set to “0”. The EEPROM will thenacknowledge. The micro-controller will then send the address word. Again the EEPROM willacknowledge. Instead of sending a valid written data to the EEPROM, the micro-controller performs a current address read page1TC24C08A F MDCo nf i de nt i a linstruction to read the data. Note that once a START bit is issued, the EEPROM will reset the internal programming process and continue to execute the new instruction - which is to read the current address. page1Figure 8: SCL and SDA Bus TimingAC CHARACTERISTICS1.8 V2.5-5.0 V Symbol ParameterMin Max Min Max Unit f SCL Clock frequency, SCL 400 1000 kHz t LOW Clock pulse width low 1.20.7µst HIGH Clock pulse width high0.4 0.3 µst I Noise suppression time (1) 180 120 ns t AA Clock low to data out valid 0.3 0.9 0.2 0.7 µs t BUF Time the bus must be free before a new transmission can start (1)1.3 0.5 µs t HD.STA START hold time 0.6 0.25 µs t SU.STA START set-up time 0.6 0.25 µs t HD.DAT Data in hold time 0 0 µs t SU.DAT Data in set-up time 100100nst R Input rise time (1)0.3 0.3 µs t F Input fall time (1) 300 100 nst SU.STO STOP set-up time 0.6 0.25 µs t DH Date out hold time 50 50 ns WRWrite cycle time55msEndurance(1)25o C, Page Mode, 3.3V1,000,000Write CyclesNotes: 1. This Parameter is expected by characterization but are not fully screened by test.2. AC Measurement conditions: R L (Connects to Vcc): 1.3K ΩInput Pulse Voltages: 0.3Vcc to 0.7VccInput and output timing reference Voltages: 0.5Vcc page1DC CHARACTERISTICSSymbol Parameter TestConditions MinTypicalMaxUnitsV CC124C A supplyV CC1.8 5.5 VI CC Supply read current V CC@ 5.0V SCL = 400 kHz 0.5 1.0 mA I CC Supply write current V CC@ 5.0V SCL = 400 kHz 2.0 3.0 mA I SB1 Supplycurrent V CC@ 1.8V, V IN = V CC or V SS 1.0 µA I SB2 Supplycurrent V CC@ 2.5V, V IN = V CC or V SS 1.0 µA I SB3 Supplycurrent V CC@ 5.0V, V IN = V CC or V SS0.06 1.0 µAI IL Input leakagecurrentV IN = V CC or V SS 3.0 µAI LO Output leakagecurrentV IN = V CC or V SS 3.0 µAV IL Input low level -0.6 V CC x0.3 V V IH Input high level V CC x0.7V CC+0.5 V V OL1 Outputlowlevel V CC@ 1.8V, I OL = 0.15 mA 0.2 V V OL2 Outputlowlevel V CC@ 3.0V, I OL = 2.1 mA 0.4 V page1Tape and Reel TC24C08A-USG-TTube TC24C08A-USG-B Tape and Reel TC24C08A-USR-TTube TC24C08A-USR-B Green Tube TC24C08A-UDG-B RoHS Tube TC24C08A-UDR-B Green Tape and Reel TC24C04A-UNG-TRoHS Tape and Reel TC24C04A-UNR-T Green Tape and Reel TC24C04A-UPG-T RoHS Tape and Reel TC24C04A-UPR-T Green Tape and Reel TC24C04A-ULG-T RoHS Tape and Reel TC24C04A-ULR-T Tape and Reel TC24C04A-UTG-T Tube TC24C04A-UTG-BTape and Reel TC24C04A-UTR-TTube TC24C04A-UTR-B Tape and Reel TC24C04A-UMG-TTube TC24C04A-UMG-B Tape and Reel TC24C04A-UMR-TTube TC24C04A-UMR-B Tape and Reel TC24C04A-USG-TTube TC24C04A-USG-B Tape and Reel TC24C04A-USR-TTube TC24C04A-USR-B Green Tube TC24C04A-UDG-B RoHSTube TC24C04A-UDR-BORDERING INFORMATION:Density PackageTemperatureRangeVcc HSF Packaging Ordering CodeDIP8 -40℃-85℃ 1.8V-5.5VRoHSSOP8 -40℃-85℃ 1.8V-5.5VGreen RoHSMSOP8 -40℃-85℃ 1.8V-5.5VGreenRoHSTSSOP8 -40℃-85℃ 1.8V-5.5VGreenSOT23-5 -40℃-85℃ 1.8V-5.5V TSOT23-5 -40℃-85℃ 1.8V-5.5V 4kbitsDFN8 -40℃-85℃ 1.8V-5.5V DIP8 -40℃-85℃ 1.8V-5.5VRoHS8kbitsSOP8 -40℃-85℃ 1.8V-5.5VGreenD: DIP8 S: SOP8 M: MSOP8 T: TSSOP8 L: SOT23-5 P: TSOT23-5 N: DFN8Packaging B: TubeT: Tape and Reel HSF R: RoHS G: GreenU: page1Tube TC24C16A-UTG-B Tape and Reel TC24C16A-UTG-T RoHS Tape and Reel TC24C16A-ULR-T Green Tape and Reel TC24C16A-ULG-T Tube TC24C08A-UMR-B GreenTape and Reel TC24C16A-UNG-TRoHS Tape and Reel TC24C16A-UNR-T Green Tape and Reel TC24C16A-UPG-T RoHS Tape and Reel TC24C16A-UPR-T Tape and Reel TC24C16A-UTR-TTube TC24C16A-UTR-B Tape and Reel TC24C16A-UMG-TTube TC24C16A-UMG-B Tape and Reel TC24C16A-UMR-TTube TC24C16A-UMR-B Tape and Reel TC24C16A-USG-TTube TC24C16A-USG-B Tape and Reel TC24C16A-USR-TTube TC24C16A-USR-B Green Tube TC24C16A-UDG-B RoHS Tube TC24C16A-UDR-B Green Tape and Reel TC24C08A-UNG-TRoHS Tape and Reel TC24C08A-UNR-T Green Tape and Reel TC24C08A-UPG-T RoHS Tape and Reel TC24C08A-UPR-T Green Tape and Reel TC24C08A-ULG-T RoHSTape and Reel TC24C08A-ULR-T Tape and Reel TC24C08A-UTG-T Tube TC24C08A-UTG-B Tape and Reel TC24C08A-UTR-TTube TC24C08A-UTR-B Tape and Reel TC24C08A-UMG-TTube TC24C08A-UMG-B Tape and Reel TC24C08A-UMR-TDensity PackageTemperatureRangeVcc HSF Packaging Ordering CodeRoHSMSOP8 -40℃-85℃ 1.8V-5.5VGreen RoHSTSSOP8 -40℃-85℃ 1.8V-5.5VGreen SOT23-5 -40℃-85℃ 1.8V-5.5V TSOT23-5 -40℃-85℃ 1.8V-5.5V 8kbitsDFN8 -40℃-85℃ 1.8V-5.5V DIP8 -40℃-85℃ 1.8V-5.5VRoHSSOP8 -40℃-85℃ 1.8V-5.5VGreen RoHSMSOP8 -40℃-85℃ 1.8V-5.5VGreenRoHSTSSOP8 -40℃-85℃ 1.8V-5.5VGreenSOT23-5 -40℃-85℃ 1.8V-5.5V TSOT23-5 -40℃-85℃ 1.8V-5.5V 16kbitsDFN8 -40℃-85℃ 1.8V-5.5V page1DIP8 PACKAGE OUTLINEDIMENSIONSDimensions In Millimeters Dimensions In InchesSymbolMin Max Min MaxA 3.710 4.310 0.146 0.170A1 0.510 0.020A2 3.200 3.600 0.126 0.142B 0.380 0.570 0.015 0.0221.524(BSC) 0.060(BSC)B1C 0.204 0.360 0.008 0.014D 9.000 9.400 0.354 0.370E 6.200 6.600 0.244 0.260E1 7.320 7.920 0.288 0.312(BSC) 0.100(BSC)e 2.540L 3.000 3.600 0.118 0.142E2 8.400 9.000 0.331 0.354 page1SOP8 PACKAGE OUTLINE DIMENSIONSDimensions In Millimeters Dimensions In InchesSymbolMin Max Min MaxA 1.350 1.750 0.053 0.069A1 0.100 0.250 0.004 0.010A2 1.350 1.550 0.053 0.061b 0.330 0.510 0.013 0.020c 0.170 0.250 0.006 0.010D 4.700 5.100 0.185 0.200E 3.800 4.000 0.150 0.157E1 5.800 6.200 0.228 0.244(BSC)(BSC) 0.050e 1.270L 0.400 1.270 0.016 0.050θ0° 8° 0° 8° page1MSOP8 PACKAGE OUTLINE DIMENSIONSDimensions In Millimeters Dimensions In InchesSymbolMin Max Min MaxA 0.820 1.100 0.320 0.043A1 0.020 0.150 0.001 0.006A2 0.750 0.950 0.030 0.037b 0.250 0.380 0.010 0.015c 0.090 0.230 0.004 0.009D 2.900 3.100 0.114 0.122e 0.65 (BSC) 0.026 (BSC)E 2.900 3.100 0.114 0.122E1 4.750 5.050 0.187 0.199L 0.400 0.800 0.016 0.031θ0° 6° 0° 6° page1TSSOP8 PACKAGE OUTLINEDIMENSIONSDimensions In Millimeters Dimensions In InchesSymbolMin Max Min MaxD 2.900 3.100 0.114 0.122E 4.300 4.500 0.169 0.177b 0.190 0.300 0.007 0.012c 0.090 0.200 0.004 0.008E1 6.250 6.550 0.246 0.258A 1.100 0.043A2 0.800 1.000 0.031 0.039A1 0.020 0.150 0.001 0.006e 0.65 (BSC) 0.026 (BSC)L 0.500 0.700 0.020 0.028H 0.25 (TYP) 0.01 (TYP)θ 1° 7° 1° 7° page1SOT-23-5 PACKAGE OUTLINE DIMENSIONSDimensions In Millimeters Dimensions In InchesSymbolMin Max Min MaxA 1.050 1.250 0.041 0.049A1 0.000 0.100 0.000 0.004A2 1.050 1.150 0.041 0.045b 0.300 0.500 0.012 0.020c 0.100 0.200 0.004 0.008D 2.820 3.020 0.111 0.119E 1.500 1.700 0.059 0.067E1 2.650 2.950 0.104 0.116e 0.95 (BSC) 0.037 (BSC)e1 1.800 2.000 0.071 0.079L 0.300 0.600 0.012 0.024θ 0° 8° 0° 6°TSOT-23-5 PACKAGE OUTLINE DIMENSIONSDimensions In Millimeters Dimensions In InchesSymbolMin Max Min MaxA 0.700 0.900 0.028 0.035A1 0.000 0.100 0.000 0.004A2 0.700 0.800 0.028 0.031b 0.350 0.500 0.014 0.020c 0.080 0.200 0.003 0.008D 2.820 3.020 0.111 0.119E 1.600 1.700 0.063 0.067E1 2.650 2.950 0.104 0.116e 0.95 (BSC) 0.037 (BSC)e1 1.90 (BSC) 0.075 (BSC)L 0.300 0.600 0.012 0.024θ 0° 8° 0° 8° page1DFN8 PACKAGE OUTLINE DIMENSIONSDimensions In MillimetersSymbolMin Nom Max0.75 0.80A 0.700.02 0.05A1 -0.25 0.03b 0.180.20 0.25c 0.182.00 2.10D 1.90D2 1.50REFe 0.50BSCNd 1.50BSC3.10E 2.903.00E2 1.60REF0.40 0.50L 0.300.25 0.30h 0.20 page1。

X24C08S8-2.7资料