HYS 72V32220GU中文资料

HYS72V4200GU-10中文资料

• • • • •

•

Programmed Latencies :

Product Speed -8 -8B -10 PC100 PC100 PC66 CL 2 3 2 tRCD 2 2 2 tRP 2 3 2

100 Mhz 4M x 64 1 bank SDRAM module 100 MHz 4M x 72 1 bank SDRAM module 100 Mhz 8M x 64 2 bank SDRAM module 100 MHz 8M x 72 2 bank SDRAM module 100 Mhz 4M x 64 1 bank SDRAM module 100 Mhz 8M x 64 2 bank SDRAM module 66 Mhz 4M x 64 1 bank SDRAM module 66 MHz 4M x 72 1 bank SDRAM module 66 Mhz 8M x 64 2 bank SDRAM module 66 MHz 8M x 72 2 bank SDRAM module

• • • • • • •

Semiconductor Gr交易网

HYS64(72)V4200/8220GU SDRAM-Modules

The HYS64(72)V4200 and HYB64(72)V8220 are an industry standard 168-pin 8-byte Dual in-line Memory Module (DIMM) which are organised as 4M x 64, 4M x 72 in an one bank and 8M x 64, 8M x72 in two banks high speed memory arrays designed with 64Mbit Synchronous DRAMs (SDRAMs Die Rev.B) for non-parity and ECC application. The DIMMs use -8 and -8B speed sort 4M x 16 SDRAM devices in TSOP54 packages to meet the PC100 requirements and -10 parts for 66 MHz bus speed applications. Decoupling capacitors are mounted on the PC board. The PC board design is according to INTEL’s module specification. The DIMMs have a serial presence detect, implemented with a serial E2PROM using the two pin I2C protocol. The first 128 bytes are utilized by the DIMM manufacturer and the second 128 bytes are available to the end user. All SIEMENS 168-pin DIMMs provide a high performance, flexible 8-byte interface in a 133,35 mm long footprint, with t.d.b. height.

HYS72V64300GR-75-C2中文资料

3.3V 168-pin Registered SDRAM Modules PC133128MByte Module PC133256MByte module PC133512MByte Module PC1331GByte Module PC1332GByte ModuleDescriptionThe HYS 72Vxx3xxGR-7and -7.5are industry standard 168-pin 8-byte Dual in-line Memory Modules (DIMMs)organized as 16M ×72,32M x 72,64M ×72,128M ×72and 256M x 72high speed memory arrays designed with Synchronous DRAMs (SDRAMs)for ECC applications.All control and address signals are registered on-DIMM and the design incorporates a PLL circuit for the Clock e of an on-board register reduces capacitive loading on the input signals but are delayed by one cycle in arriving at the SDRAM devices.Decoupling capacitors are mounted on the PC board.The DIMMs use a serial presence detects scheme implemented via a serial E 2PROM using the 2-pin I 2C protocol.The first 128bytes are utilized by the DIMM manufacturer and the second 128bytes are available to the end user.All Infineon 168-pin DIMMs provide a high performance,flexible 8-byte interface in a 133.35mm long footprint.•168-pin Registered 8Byte Dual-In-Line SDRAM Module for PC and Server main memory applications •One bank 16M ×72,32M x 72,64M ×72and 128M x 72,two bank 128M ×72and 256M x 72organization •Optimized for ECC applications with very low input capacitances •JEDEC standard Synchronous DRAMs(SDRAM)Programmable CAS Latency,Burst Length and Wrap Sequence (Sequential &Interleave)•Single +3.3V (±0.3V)power supply •Auto Refresh (CBR)and Self Refresh •Programmable Latency,Burst Length,and Wrap Sequence (Sequential &Interleave)•All inputs and outputs are LVTTL compatible •Serial Presence Detect with E 2PROM •Utilizes SDRAMs in TSOPII-54packages with registers and PLL.•Card Size:133.35mm ×38.10/43.18mm with Gold contact pads and max.4.00/6.80mm thickness (JEDEC MO-161)•These modules all fully compatible with the current industry standard PC133and PC100specifications•Performance:speed grade-7-7.5Unitf CK Clock Frequency (max.)@CL =3133133MHz t CK Clock Cycle Time (min.)@CL =37.57.5ns t AC Clock Access Time (min.)@CL=3 5.4 5.4ns f CK Clock Frequency (max.)@CL =2133100MHz t CK Clock Cycle Time (min.)@CL =27.510ns t ACClock Access Time (min.)@CL=25.46nsOrdering Information.Partnumber1)ComplianceCode2)Description SDRAMTechnologyPC133-333:HYS72V16300GR-7.5-CHYS72V16300GR-7.5-EPC133R-333-542-B2one bank128MB Reg.DIMM64MBit(x4)HYS72V16301GR-7.5-C2PC133R-333-542-B2one bank128MB Reg.DIMM128MBit(x8) HYS72V32301GR-7.5-C2PC133R-333-542-B2one bank256MB Reg.DIMM128Mbit(x4) HYS72V32300GR-7.5-C2HYS72V32300GR-7.5-DPC133R-333-542-AA one bank256MB Reg.DIMM256Mbit(x8)HYS72V64300GR-7.5-C2HYS72V64300GR-7.5-DPC133R-333-542-B2one bank512MB Reg.DIMM256MBit(x4)HYS72V128320/1GR-7.5-C2 HYS72V128320/1GR-7.5-D PC133R-333-542-B2two banks1GByte Reg.DIMM256MBit(x4,stacked)3)HYS72V128300GR-7.5-A PC133R-333-542-B2one bank1GByte Reg.DIMM512MBit(x4) HYS72V256320/1GR-7.5-A PC133R-333-542-B2two banks2GByte Reg.DIMM512MBit(x4,stacked)3) PC133-222:HYS72V16300GR-7-E PC133R-222-542-B2one bank128MB Reg.DIMM64MBit(x4) HYS72V16301GR-7-C2PC133R-222-542-B2one bank128MB Reg.DIMM128MBit(x8) HYS72V32301GR-7-C2PC133R-222-542-B2one bank256MB Reg.DIMM128Mbit(x4) HYS72V32300GR-7-D PC133R-222-542-AA one bank256MB Reg.DIMM256Mbit(x8) HYS72V64300GR-7-D PC133R-222-542-B2one bank512MB Reg.DIMM256MBit(x4) HYS72V128320/1GR-7-D PC133R-222-542-B2two banks1GByte Reg.DIMM256MBit(x4,stacked)3) HYS72V128300GR-7-A PC133R-222-542-B2one bank1GByte Reg.DIMM512MBit(x4) HYS72V256320/1GR-7-A PC133R-222-542-B2two banks2GByte Reg.DIMM512MBit(x4,stacked)3) Notes:1.)All part numbers end with a place code,designating the die revision of the components used on theRegistered DIMM module.Consult factory for current revision.Example:HYS64V32300GR-7.5-D, indicating Rev.D dies are used for256Mbit SDRAM components.2.)The Compliance Code is printed on the modules labels and describes speed sort of the modules,latencies,access time from clock,SPD revision and Raw Card version acording to the actual JEDEC standard.3.)Modules with stacked components are available in two version,with components stacked using asoldering stacking technique(f.e.HYS72V128320GR-7.5)and an welding technique developed by INFINEON Technologies(f.e.HYS72V128321GR-7.5)Pin Definitions and FunctionsA0-A11,A12Address Inputs(A12is used for256Mbit based modules only)DQMB0-DQMB7Data MaskBA0,BA1Bank Selects CS0-CS3Chip SelectDQ0-DQ63Data Input/Output REGE*)Register Enable“H”or N.C=registered mode“L”=buffered modeCB0-CB7Check Bits VDDPower(+3.3V)RAS Row Address Strobe VSSGroundCAS Column Address Strobe SCL Clock for Presence Detect WE Read/Write Input SDA Serial Data OutCKE0Clock Enable N.C.No ConnectionCLK0-CLK3Clock Input––Note:*)To confirm to this specification,motherboards must pull this pin to high state or no connect. Address FormatDensity Organization MemoryBanks SDRAMs#ofSDRAMs#of row/bank/columns bitsRefresh Period Interval128MB16M×72116M×41812/2/104k64ms15.6µs 128MB16M×72116M x8912/2/104k64ms15.6µs 256MB32M x72132M x41812/2/114k64ms15.6µs 256MB32M x72132M x8913/2/108k64ms7.8µs 512MB64M×72164M×41813/2/118k64ms7.8µs 1GB128M×72264M×43613/2/118k64ms7.8µs 1GB128M×721128M×41813/2/128k64ms7.8µs 2GB256M×722128M×43613/2/128k64ms7.8µsPin ConfigurationBlock Diagram:One Bank16M x72,32M x72,64M x72and128M x72SDRAM DIMM Modules HYS72V16300GR,HYS72V32301GR,HYS72V64300GR and HYS72V128320GRusing x4organized SDRAMsHYS72V16301&HYS72V32300GR using x8organized SDRAMsBlock Diagram:Two Bank128M x72and256M x72SDRAM DIMM ModulesHYS72V128320GR and HYS72V256320GR Using Stacked x4Organized SDRAMsAbsolute Maximum RatingsDC CharacteristicsTA=0to70°C1);V SS=0V;V DD=3.3V±0.3V CapacitanceT A =0to70°C1);V DD=3.3V±0.3V,f=1MHzParameter Symbol Limit Values Unitmin.max.Input/Output voltage relative to V SS V IN,V OUT–1.0 4.6VPower supply voltage on VDD VDD–1.0 4.6VStorage temperature range T STG-55+150o C Power dissipation(per SDRAM component)P D–1W Data out current(short circuit)I OS–50mA Permanent device damage may occur if“Absolute Maximum Ratings”are exceeded.Functional operation should be restricted to recommended operation conditions.Exposure to higher than recommended voltage for extended periods of time affect device reliabilityParameter Symbol Limit Values Unitmin.max.Input High Voltage V IH 2.0V DD+0.3V Input Low Voltage V IL–0.50.8V Output High Voltage(I OUT=–4.0mA)V OH 2.4–V Output Low Voltage(I OUT=4.0mA)V OL–0.4VInput Leakage Current,any input(0V<V IN<3.6V,all other inputs=0V)II(L)–1010µAOutput Leakage Current(DQ is disabled,0V<VOUT <VDD)IO(L)–1010µAParameter Symbol Limit Values UnitOne Bank Modules Two Bank ModulesInput Capacitance(all inputs except CLK and CKE)CIN1020pFInput Capacitance(CLK)C CLK3030pF Input Capacitance(CKE)C CKE1730pF Input/Output Capacitance(DQ0-DQ63,CB0-CB7)C IO1017pF Input Capacitance(SCL,SA0-2)C SC88pF Input/Output Capacitance(SDA)C SD88pFOperating Currents per SDRAM Component T=0to70°C1),V=3.3V±0.3VAC Characteristics(SDRAM Device Specification)4),5) T=0to70°C1);V=0V;V=3.3V±0.3V,t=1nsRefresh CycleRefresh Period64&128MBit SDRAM Based Modules 256&512MBit SDRAM Based Modulest REF ––15.67.8––15.67.8µs µs –Self Refresh Exit Time t SREX1–1–CLK6)Read Cycle Data Out Hold Timet OH 3–3–ns –Data Out to Low Impedance Time t LZ 0–0–ns 7)Data Out to High Impedance Time t HZ 3737ns 7)DQM Data Out Disable Latency t DQZ–2–2CLK–Write CycleData Input to Precharge (write recovery)t WR 2–2–CLK –DQM Write Mask Latencyt DQW––CLK–AC Characteristics (SDRAM Device Specification)(cont’d)4),5)T A =0to 70°C 1);V SS =0V;V DD =3.3V ±0.3V,t T =1ns ParameterSymbolLimit ValuesUnitNote-7PC133-222-7.5PC133-333min.max.min.max.Notes1.The registered DIMM modules are designed to operate under system operating conditionsbetween0-55deg C ambient,maximum sustained bandwidth and0LFM airflow.Operating at higher ambient temperatures needs sufficient air flow to limit the case temperature of the SDRAM components do not exceed85o C.2.These parameters depend on the cycle rate.All values are measured at133MHz operationfrequency.Input signals are changed once during tck excepts for Icc6and for standby currents when tck=infinity.3.These parameters are measured with continous data stream during read access and all DQtoggling.CL=3and BL=4is assumed and the data-out current is excluded.4.An initial pause of100µs is required after power-up.Then a Precharge All Banks command mustbe given followed by eight Auto Refresh(CBR)cycles before the Mode Register Set Operation can begin.Also the on-DIMM PLL must be given enough clock cycles to stabilize(t STAB)before any operation can be guaranteed.5.AC timing tests have V IL=0.8V and V IH=2.0V with the timing referenced to the1.4V crossoverpoint.The transition time is measured between V IH and V IL.All AC measurements assume t=1ns with the AC output load circuit shown.Specified t AC and t OH parameters are measured Twith a50pF only,without any resistive termination and with a input signal of1V/ns edge rate between0.8V and2.0V.6.Self Refresh Exit is a synchronous operation and begins on the second positive clock edge afterCKE returns high.Self Refresh Exit is not complete until a time period equal to t RC is satisfied after the Self Refresh Exit command is registered.7.Referenced to the time at which the output achieves the open circuit condition,not to outputvoltage levels.Serial Presence DetectA serial presence detect storage device-E2PROM34C02-is assembled onto the module. Information about the module configuration,speed,etc.is written into the E2PROM device during module production using a serial presence detect protocol(I2C synchronous2-wire bus).The first 128bytes are utilized by the DIMM manufacturer and the second128bytes are available to the enduser.SPD-Table for-7.5Registered DIMM ModulesSPD-Table for-7.5Registered DIMM Modules(cont’d)SPD-Table for-7Registered DIMM ModulesPackage Outlines for Raw Card AAPackage Outlines for Raw Card BPackage Outlines for Raw Card B(with stacked components)Functional DescriptionAll these PC133168-pin Registered DIMMs conform to a compatible set of timing and operation characteristics intended to comply with the133MHz standards.The Registered DIMMs achieve high speed data transfer rate up to133MHz,when in“registered mode”.The“registered mode”is achieved when the REGE input signal is in“high”state or the pin is not connected.Operation in “buffered mode”(REGE=“low”)needs careful system design to compensate all input signals for the extra delay time of the register components when in“buffered mode”.“Buffered mode”is limited to 66Mhz maximum operation frequency.Registered Mode:All control and address signals are synchronized with the positive edge of externally supplied clocks and are registered on-DIMM and hence delayed by one clock cycle in arriving at the SDRAM devices.The use of the on-board register reduces the capacitive loading of the DIMM on input control and address signals.The SDRAM device data lines(DQ)are connected directly to the DIMM tabs through10Ohm series resistors.All the following timing diagrams and explanations show DIMM operation at the tabs,not SDRAM operation.The picture below depicts an overview of the effect of the Registered Mode on the data outputs (DQs)for a Read operation.Without the registers,the data is delayed according to the device CAS latency,in the case two clocks.With the register,the data is delayed according to the device CAS latency plus an additional clock cycle.This is known as the DIMM CAS latency,and in this example is four three.The data path can be thought of as a pipeline in which the register effectively lengthens the pipe by one clock cycle.In case of a Burst Write Command the data-in is delayed one clock due the op-DIMM pipeline register also.Therefore,data for the first Burst Write cycle must be applied on the DQ pins on the next clock cycle after the Write command is issued.the remaining data inputs must be supplied oneach subsequent rising clock edge until the burst length is completed.When the burst has finished, any additional data supplied to the DQ pins will be ignored.Registered DIMM Burst Write Operation(BL=4)。

PQ3220开关电源磁芯规格书

2008 Sep 01

6

≈0 ≈0 ≈0 ≈0 ≈0

TYPE NUMBER

PQ32/20-3C81-E315 PQ32/20-3C81-A400 PQ32/20-3C81-A630 PQ32/20-3C81-A1000 PQ32/20-3C81-A1600 PQ32/20-3C81 PQ32/20-3C90-E315 PQ32/20-3C90-A400 PQ32/20-3C90-A630 PQ32/20-3C90-A1000 PQ32/20-3C90-A1600 PQ32/20-3C90 PQ32/20-3C91 PQ32/20-3C94 PQ32/20-3C95 PQ32/20-3C96

SPECIFICATION

Polyethylene terephtalate (PET), glass-reinforced, flame retardant in accordance with “UL 94V-0” ; UL file number E41938 copper-tin alloy (CuSn), tin (Sn) plated 180 °C, “IEC 60085”, class H “IEC 6068-2-20” , Part 2, Test Tb, method 1B, 350 °C, 3.5 s “IEC 60068-2-20”, Part 2, Test Ta, method 1

2008 Sep 01

2

Ferroxcube

PQ cores and accessories

PQ32/20

GRADE 3F3

AL (nH)

315 ±3% 400 ±3% 630 ±3% 1000 ±3% 1600 ±5% 6000 ±25%

GU320a控制系统说明书

轮胎吊发电机组补充使用说明书G320a控制系统上海中集内燃发电设备有限公司地址:上海市青浦区华新镇华志路1295弄118号(近嘉松中路) 上海市华新工业园区邮编: 201708 •电话:(021)69790728 传真:(021)69791384公司网址:1.概述:GU320A发电机组智能控制屏,采用背包式结构,安装方便,高性能的专用控制器,可修改发电机的控制程序和保护参数,集测量、控制、保护、三遥等众多功能为一体。

完全满足发电机组使用及不同类型的发电机组自动控制要求。

----高性能的的发电机组专用控制器----双路启动线路----双路仪表显示2.控制屏的外形结构与原理:外形图及电气原理图详见对应图纸。

3.控制屏面板:GU320A 控制器一只手动启动钥匙一只4.控制屏操作控制屏有两种操作,手动钥匙启动和控制器操作。

4.1 手动钥匙启动:1.检查柴油机机油、冷却水位是否正常。

2.检查蓄电池连接,注意:正、负极不能接反。

3.合上屏内所有塑壳开关。

4.将手动钥匙转向右一档,接通电源,再次转向右二档,启动马达工作,发动机开始点火,启动一成功,立即松手动钥匙,手动钥匙自动复位。

5.观察液晶显示器显示所有参数(电压、功率、油压、水温等)。

6.将手动钥匙转向左边(STOP位),机组停机(电调机组),将手动钥匙转向左边(STOP位),待机组完全停机后松开,钥匙自动复位(机械调速)。

4.2 控制器操作:1.检查柴油机机油、冷却水位是否正常。

2.检查蓄电池连接,注意:正、负极不能接反。

3.合上屏内所有塑壳开关。

4.将控制器模式放到自动模式,“AUTO”:自动模式5. 遥控开机开关合上,机组自动起动。

遥控开机开关断开,机组自动停机。

等待下次起动。

(详细见控制器操作说明)4.3 控制器操作说明控制器有六个按钮:“AUTO”、“MAN”、“TEST”、“START”、“STOP/RESET”、“L.TEST/MUTE”“AUTO”:自动模式“MAN”:手动模式“TEST”:测试模式“START”:启动“STOP/RESET”:停机“L.TEST/MUTE”:试灯及消音控制器有三种控制方式:自动操作模式、手动操作模式、测试操作模式。

72v32ah石墨烯电池尺寸

72v32ah石墨烯电池尺寸72V32AH石墨烯电池尺寸随着电动汽车的普及和发展,电池作为电动汽车的重要组成部分,也在不断创新和改进。

石墨烯电池作为一种新型电池,具有高能量密度、长寿命、快速充电等优势,备受关注。

在石墨烯电池中,72V32AH是一种常见的规格,接下来我们将重点介绍其尺寸特点。

我们需要了解72V32AH的含义。

其中,72V表示电池的电压为72伏特,32AH表示电池的容量为32安时。

电池容量是衡量电池储存能量能力的重要指标,表示电池在特定电压下能提供的电能量。

具体到32AH的容量,可以理解为电池在一小时内以1安的电流放电时,能够持续放电32小时。

对于石墨烯电池的尺寸,一般是根据电池的电压和容量来确定的。

由于石墨烯电池较为新颖,其尺寸规格可能因不同厂家而有所差异。

但一般来说,72V32AH石墨烯电池的尺寸相对较大。

其大尺寸主要是为了满足高能量密度和长寿命的要求,同时也考虑到了电池内部结构和散热等因素。

具体到尺寸方面,72V32AH石墨烯电池的一般尺寸为长宽高分别为约400mm x 200mm x 200mm。

这样的尺寸设计可以容纳更多的电池单体,并提供足够的空间用于电池内部的电解液、保护装置、连接器等组件。

同时,较大的尺寸也有助于散热,提高电池的安全性和稳定性。

在实际应用中,72V32AH石墨烯电池的尺寸也会因应用场景和需求而有所不同。

例如,在一些电动汽车中,由于空间的限制,可能需要更小尺寸的电池来适应车辆结构。

因此,厂家会根据用户的需求进行定制,提供符合要求的电池尺寸。

石墨烯电池的尺寸设计也会考虑电池的重量。

由于石墨烯电池具有高能量密度的特点,相对于传统电池来说,可以在相同容量下减少电池的重量。

这也是石墨烯电池在电动汽车领域得到广泛应用的原因之一。

72V32AH石墨烯电池是一种常见的电池规格,其尺寸相对较大,一般为约400mm x 200mm x 200mm。

这样的尺寸设计可以满足高能量密度和长寿命的要求,同时也考虑了电池内部结构和散热等因素。

MAX3222EEUP中文资料

Battery-Powered Equipment Cell Phones Cell-Phone Data Cables Notebook, Subnotebook, and Palmtop Computers

Applications

Printers Smart Phones xDSL Modems

_______________Ordering Information

PART

TEMP RANGE

PINPACKAGE

PKG CODE

MAX3222ECTP MAX3222ECUP

0°C to +70°C 0°C to +70°C

20 Thin QFNEP** (5mm x 5mm) 20 TSSOP

♦ For Low-Voltage or Data Cable Applications MAX3380E/MAX3381E: +2.35V to +5.5V, 1µA, 2Tx/2Rx, RS-232 Transceivers with ±15kV ESD-Protected I/O and Logic Pins

MAX3222EEPN -40°C to +85°C 18 Plastic DIP —

MAX3232ECAE 0°C to +70°C 16 SSOP

—

MAX3232ECWE 0°C to +70°C 16 Wide SO —

MAX3232ECPE 0°C to +70°C 16 Plastic DIP —

A proprietary low-dropout transmitter output stage delivers true RS-232 performance from a +3.0V to +5.5V power supply, using an internal dual charge pump. The charge pump requires only four small 0.1µF capacitors for operation from a +3.3V supply. Each device guarantees operation at data rates of 250kbps while maintaining RS-232 output levels. The MAX3237E guarantees operation at 250kbps in the normal operating mode and 1Mbps in the MegaBaud™ operating mode, while maintaining RS-232compliant output levels.

NCV33272ADR2中文资料

1

October, 2006 − Rev. 11

Publication Order Number: MC33272A/D

元器件交易网 MC33272A, MC33274A, NCV33272A, NCV33274A

PIN CONNECTIONS

DUAL CASE 626/751

−

Power Supply Rejection VCC/VEE = +15 V/ −15 V, +5.0 V/ −15 V, +15 V/ −5.0 V

14, 15

PSR

80

105

−

Output Short Circuit Current (VID = 1.0 V, Output to Ground)

元器件交易网

MC33272A, MC33274A, NCV33272A, NCV33274A

Single Supply, High Slew Rate, Low Input Offset Voltage Operational Amplifiers

The MC33272/74 series of monolithic operational amplifiers are

TA

NCV33272A, NCV33274A

Note 2

mW

−40 to +85

°C

−40 to +125

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability. 1. Either or both input voltages should not exceed VCC or VEE. 2. Power dissipation must be considered to ensure maximum junction temperature (TJ) is not exceeded (see Figure 2).

Y3系列三相异步电机产品资料

Y3系列三相异步电动机一、产品简介Y3系列三相异步电动机(以下简称Y3电机)是一般用途的全封闭自扇冷鼠笼型三相异步电动机。

该系列电机的基本防护等级为IP55,绝缘等级为F级,电机温升按B级考核;等级和安装尺寸符合IEC标准。

该系列电机采用冷轧硅钢片作为导磁材料,符合国家产业政策,是Y 、Y2系列电动机的升级换代产品。

同时,满足了GB18613-2002《中小型三相异步电动机能效限定值及节能评价值》的能效限定值的要求。

该系列电机主要适用于不含易燃、易爆或腐蚀气体的一般场所和无特殊要求的机械上。

二、产品特点Y3电机具有设计新颖、结构紧凑,造型美观、效率和转矩高、起动性能好、节能、噪声低、振动小、运行安全可靠、使用维护方便等特点;但功率因数较低,调速也较困难。

大容量低转速的动力机常用同步电动机,同步电动机不但功率因数高,而且其转速与负载大小无关,只决定于电网频率,工作较稳定。

在要求宽范围调速的场合多用直流电动机,但它有换向器,结构复杂,价格昂贵,维护困难,不适于恶劣环境。

三、用途Y3电机广泛应用于机床、风机、水泵、压缩机和交通运输、农业、食品加工等各类机械电力传动。

四、使用条件在下列使用条件下,Y3电机应能正常运行:1、海拔不超过1000m;2、环境空气最高温度随季节而变化,但不超过400C;3、环境空气最低温度为-150C;4、最湿月月平均最高相对湿度为90%,同时该月月平均最低温度不高于25℃;五、工作原理当电动机的三相定子绕组(各相差120度电角度),通入三相对称交流电后,将产生一个旋转磁场,该旋转磁场切割转子绕组,从而在转子绕组中产生感应电流(转子绕组是闭合通路),载流的转子导体在定子旋转磁场作用下将产生电磁力,从而在电机转轴上形成电磁转矩,驱动电动机旋转,并且电机旋转方向与旋转磁场方向相同。

三相异步电动机转子的转速低于旋转磁场的转速,转子绕组因与磁场间存在着相对运动而感生电动势和电流,并与磁场相互作用产生电磁转矩,实现能量变换。

HYS72D32000GR-8-A资料

2.5V 184-pin Registered DDR-I SDRAM Modules 256MB,512MB &1GByte Modules PC1600&PC2100DescriptionThe HYS 72Dxx0x0GR are industry standard 184-pin 8-byte Dual in-line Memory Modules (DIMMs)organized as 32M ×72(256MB),64M ×72(512MB)and 128M ×72(1GB).The memory array is designed with Double Data Rate Synchronous DRAMs for ECC applications.All control and address signals are re-driven on the DIMM using register devices and a PLL for the clock distribution.This reduces capacitive loading to the system bus,but adds one cycle to the SDRAM timing.A variety of decoupling capacitors are mounted on the PC board.The DIMMs feature serial presence detect based on a serial E 2PROM device using the 2-pin I 2C protocol.The first 128bytes are programmed with configuration data and the second 128bytes are available to the customer.•184-pin Registered 8-Byte Dual-In-Line DDR-I SDRAM Module for PC and Server main memory applications •One bank 32M ×72,64M x 72,and two bank 64M x 72,128M ×72organization •JEDEC standard Double Data RateSynchronous DRAMs (DDR-I SDRAM)with a single +2.5V (±0.2V)power supply •Built with 256Mbit DDR-I SDRAMs in 66-Lead TSOPII package •Programmable Latency,Burst Length,and Wrap Sequence (Sequential &Interleave)•Auto Refresh (CBR)and Self Refresh •All inputs and outputs SSTL_2compatible •Re-drive for all input signals using register and PLL devices.•Serial Presence Detect with E 2PROM •Jedec standard MO-206form factor:133.35mm (nom.)×43.18mm (nom.)×4.00mm (max.)(6,80mm max.with stacked components)•Jedec standard reference layout:Raw Cards A,B and C •Gold plated contacts•Performance:-7-8UnitComponent Speed Grade DDR266A DDR200Module Speed GradePC2100PC1600f CK Clock Frequency (max.)@CL =2.5143125MHz f CKClock Frequency (max.)@CL =2133100MHzOrdering InformationType Compliance Code Description SDRAMTechnologyPC2100(CL=2):HYS72D32000GR-7-A PC2100R-20330-A1one bank256MB Reg.DIMM256MBit(x8) HYS72D64000GR-7-A PC2100R-20330-B1one bank512MB Reg.DIMM256Mbit(x4) HYS72D64020GR-7-A PC2100R-20330-A1two banks512MB Reg.DIMM256MBit(x8) HYS72D128020GR-7-A PC2100R-20330-C1two banks1GByte Reg.DIMM256MBit(x4)(stacked)PC1600(CL=2):HYS72D32000GR-8-A PC1600R-20220-A1one bank256MB Reg.DIMM256MBit(x8) HYS72D64000GR-8-A PC1600R-20220-B1one bank512MB Reg.DIMM256Mbit(x4) HYS72D64020GR-8-A PC1600R-20220-A1two banks512MB Reg.DIMM256MBit(x8) HYS72D128020GR-8-A PC1600R-20220-C1two banks1GByte Reg.DIMM256MBit(x4)(stacked)Note:All part numbers end with a place code(not shown),designating the silicon-die revision.Reference information available on request.Example:HYS72D32000GR-8-A,indicating Rev.A die are used for SDRAM componentsThe Compliance Code is printed on the module labels and describes the speed sort fe.“PC2100R”,the latencies(f.e.“20330”means CAS latency=2,trcd latency=3and trp latency=3)and the Raw Card used for this module.Pin Definitions and FunctionsA0-A11,A12Address Inputs(A12for256Mb&512Mb based modules)VDDPower(+2.5V)BA0,BA1Bank Selects VSSGroundD Q0-D Q63Data Input/Output VDD QI/O Driver power supplyCB0-CB7Check Bits(x72organization only)VDDIDVDD Indentification flagRAS Row Address Strobe VDDSPDEEPROM power supplyCAS Column Address Strobe VREFI/O reference supply WE Read/Write Input SCL Serial bus clockCKE0,CKE1Clock Enable SDA Serial bus data lineD Q S0-D Q S8SDRAM low data strobes SA0-SA2slave address select CK0,CK0Differential Clock Input NC no connectDM0-DM8D Q S9-D Q S17SDRAM low data mask/high data strobesDU don’t useCS0-CS1Chip Selects RESET Reset pin(forces registerinputs low)*)*)for detailed description of the Power Up and Power Management on DDR Registered DIMMs see the Application Note at the end of this datasheetAddress FormatDensity Organization MemoryBanks SDRAMs#ofSDRAMs#of row/bank/columns bitsRefresh Period Interval256MB32M x72132M x8913/2/108k64ms7.8µs 512MB64M×72164M×41813/2/118k64ms7.8µs 512MB64M x72232M x81813/2/108k64ms7.8µs 1GB128M×72264M×43613/2/118k64ms7.8µsPin ConfigurationBlock Diagram:One Bank32Mb x72DDR-I SDRAM DIMM Module HYS72D32000GR using x8organized SDRAMs on Raw Card Version ABlock Diagram:Two Bank64Mb x72DDR-I SDRAM DIMM Modules HYS72D64020GR Using x8Organized SDRAMs on Raw Card Version ABlock Diagram:One Bank64Mb x72DDR-I SDRAM DIMM Modules HYS72D64000GR Using x4Organized SDRAMs on Raw Card Version BBlock Diagram:Two Bank128Mb x72DDR-I SDRAM DIMM Modules HYS72D128020GR using x4Organized SDRAMs on Raw Card Version CAbsolute Maximum RatingsParameter Symbol Limit Values Unitmin.max.Input/Output voltage relative to VSS VIN,VOUT–0.5 3.6VPower supply voltage on VDD /VDD Qto VSSVDD,VDD Q–0.5 3.6VStorage temperature range TSTG-55+150o CPower dissipation(per SDRAM component)PD–1WData out current(short circuit)IOS–50mA Permanent device damage may occur if“Absolute Maximum Ratings”are exceeded.Functional operation should be restricted to recommended operation conditions.Exposure to higher than recommended voltage for extended periods of time affect device reliabilitySupply Voltage LevelsParameter Symbol Limit Values Unit Notesmin.nom.max.Device Supply Voltage VDD2.3 2.5 2.7V-Output Supply Voltage VDD Q2.3 2.5 2.7V1)Input Reference Voltage VREF 0.49x VDD Q0.5x VDD Q0.51x VDD QV2)Termination Voltage VTT VREF–0.04VREFVREF+0.04V3)EEPROM supply voltage VDDSPD2.3 2.53.6V1Under all conditions,VDD Q must be less than or equal to VDD2Peak to peak AC noise on VREF may not exceed±2%VREF(DC).V REF is also expected to track noise variations in VDD Q.3VTT of the transmitting device must track VREFof the receiving device.DC Operating Conditions(SSTL_2Inputs)(V DD Q=2.5V,T A=70°C,Voltage Referenced to V SS)Parameter Symbol Limit Values Unit Notesmin.max.DC Input Logic High VIH(DC)VREF+0.15VDD Q+0.3V1)DC Input Logic Low VIL(DC)–0.30VREF–0.15V–Input Leakage Current IIL–55µA1)Output Leakage Current IOL–55µA2)1)The relationship between the VDD Q of the driving device and the VREFof the receiving device is whatdetermines noise margins.However,in the case of VIH(max)(input overdrive),it is the VDD Qof the receivingdevice that is referenced.In the case where a device is implemented such that it supports SSTL_2inputs buthas no SSTL_2outputs(such as a translator),and therefore no VDD Q supply voltage connection,inputs musttolerate input overdrive to3.0V(High corner VDD Q +300mV).2)For any pin under test input of0V≤VIN≤V DD Q+0.3V.Values are shown per DDR-SDRAM component.Operating,Standby and Refresh Currents(PC1600)Operating,Standby and Refresh Currents(PC2100)Electrical Characteristics&AC Timing for DDR-I components (for reference only)(0°C≤ TA ≤ 70 °C; VDD Q=2.5V± 0.2V;VDD=2.5V± 0.2V)Electrical Characteristics&AC Timing for DDR-I components (for reference only)(0°C≤ TA ≤ 70 °C; VDD Q=2.5V± 0.2V;VDD=2.5V± 0.2V)SPD CodesPackage Outlines Raw Card A(one memory bank)Package Outlines Raw Card A(two memory banks)Package Outlines Raw Card BPackage Outlines Raw Card CAPPLICATION NOTE:Power Up and Power Management on DDR Registered DIMMs(according to JEDEC ballot JC-42.5Item1173)184-pin Double Data Rate(DDR)Registered DIMMs include two new features to facilitate controlled power-up and to minimize power consumption during low power mode.One feature is externally controlled via a system-generated RESET signal;the second is based on module detection of the input clocks.These enhancements permit the modules to power up with SDRAM outputs in a High-Z state(eliminating risk of high current dissipa-tions and/or dotted I/Os),and result in the powering-down of module support devices(registers and Phase-Locked Loop)when the memory is in Self-Refresh mode.The new RESET pin controls power dissipation on the module’s registers and ensures that CKE and other SDRAM inputs are maintained at a valid‘low’level during power-up and self refresh.When RESET is at a low level,all the register outputs are forced to a low level,and all differential register input receivers are powered down,resulting in very low register power consumption.The pin,located on DIMM tab#10,is driven from the system as an asynchronous signal according to the attached ing this function also permits the system and DIMM clocks to be stopped during memory Self Refresh operation,while ensuring that the SDRAMs stay in Self Refresh mode.The function for RESET is as follows:As described in the table above,a low on the input ensures that the Clock Enable(CKE)signal(s)are maintained low at the SDRAM pins(CKE being one of the'Q'signals at the register output).Holding CKE low maintains a high impedance state on the SDRAM D Q,D Q S and DM outputs—where they will remain until acti-vated by a valid‘read’cycle.CKE low also maintains SDRAMs in Self Refresh mode when applicable.The DDR PLL devices automatically detect clock activity above20MHz.When an input clock frequency of20MHz or greater is detected,the PLL begins operation and initiates clock frequency lock(the minimum operat-ing frequency at which all specifications will be met is95MHz).If the clock input frequency drops below20MHz (actual detect frequency will vary by vendor),the PLL VCO(Voltage Controlled Oscillator)is stopped,outputs aremade High-Z,and the differential inputs are powered down—resulting in a total PLL current consumption of less e of this low power PLL function makes the use of the PLL RESET(or G pin)unnecessary,and it is tied inactive on the DIMM.This application note describes the required and optional system sequences associated with the DDR Regis-tered DIMM''function.It is important to note that all references to CKE refer to both CKE0and CKE1for a2-bank DIMM.Because applies to all DIMM register devices,it is therefore not possible to uniquely control CKE to one physical DIMM bank through the use of the RESET pin.Power-Up Sequence with RESET—Required1.The system sets RESET at a valid low level.This is the preferred default state during power-up.This input condition forces all register outputs to a low state independent of the condition on the register inputs(data and clock),ensuring that CKE is at a stable low-level at the DDR SDRAMs.2.The power supplies should be initialized according to the JEDEC-approved initialization sequence for DDR SDRAMs.3.Stabilization of Clocks to the SDRAMThe system must drive clocks to the application frequency(PLL operation is not assured until the input clock reaches20MHz).Stability of clocks at the SDRAMs will be affected by all applicable system clock devices, and time must be allotted to permit all clock devices to settle.Once a stable clock is received at the DIMM PLL,the required PLL stabilization time(assuming power to the DIMM is stable)is100microseconds.Whena stable clock is present at the SDRAM input(driven from the PLL),the DDR SDRAM requires200µsec priorto SDRAM operation.4.The system applies valid logic levels to the data inputs of the register(address and controls at the DIMM con-nector).CKE must be maintained low and all other inputs should be driven to a known state.In general these com-mands can be determined by the system designer.One option is to apply an SDRAM‘NOP’command(with CKE low),as this is the first command defined by the JEDEC initialization sequence(ideally this would be a ‘NOP Deselect’command).A second option is to apply low levels on all of the register inputs to be consistent with the state of the register outputs.5.The system switches RESET to a logic‘high’level.The SDRAM is now functional and prepared to receive commands.Since the RESET signal is asynchronous, setting the RESET timing in relation to a specific clock edge is not required(during this period,register inputs must remain stable).6.The system must maintain stable register inputs until normal register operation is attained.The registers have an activation time that allows their clock receivers,data input receivers,and output drivers sufficient time to be turned on and become stable.During this time the system must maintain the valid logic levels described in step5.It is also a functional requirement that the registers maintain a low state at the CKE outputs to guarantee that the DDR SDRAMs continue to receive a low level on CKE.Register activation time (t(ACT)),from asynchronous switching of RESET from low to high until the registers are stable and ready to accept an input signal,is specified in the register and DIMM do-umentation.7.The system can begin the JEDEC-defined DDR SDRAM power-up sequence(according to the JEDEC-pproved initialization sequence).Self Refresh Entry(RESET low,clocks powered off)—OptionalSelf Refresh can be used to retain data in DDR SDRAM DIMMs even if the rest of the system is powered down and the clocks are off.This mode allows the DDR SDRAMs on the DIMM to retain data without external clocking. Self Refresh mode is an ideal time to utilize the RESET pin,as this can reduce register power consumption low deactivates register CK and CK,data input receivers,and data output drivers).1.The system applies Self Refresh entry command.(CKE→Low,CS→Low,RAS → Low,CAS→Low,WE→High)Note:The commands reach the DDR SDRAM one clock later due to the additional register pipelining on a Registered DIMM.After this command is issued to the SDRAM,all of the address and control and clock input conditions to the SDRAM are Don’t Cares—with the exception of CKE.2.The system sets RESET at a valid low level.This input condition forces all register outputs to a low state,independent of the condition on the registerm inputs(data and clock),and ensures that CKE,and all other control and address signals,are a stable low-level at the DDR SDRAMs.Since the RESET signal is asynchronous,setting the RESET timing in relation toa specific clock edge is not required.3.The system turns off clock inputs to the DIMM.(Optional)a.In order to reduce DIMM PLL current,the clock inputs to the DIMM are turned off,resulting in High-Z clockinputs to both the SDRAMs and the registers.This must be done after the RESET deactivate time of the reg-ister(t(INACT)).The deactivate time defines the time in which the clocks and the control and address sig-nals must maintain valid levels after RESET low has been applied and is specified in the register and DIMM documentation.b.The system may release DIMM address and control inputs to High-Z.This can be done after the RESET deactivate time of the register.The deactivate time defines the time in which the clocks and the control and the address signals must maintain valid levels after RESET low has been applied.It is highly recommended that CKE continue to remain low during this operation.4.The DIMM is in lowest power Self Refresh mode.Self Refresh Exit(RESET low,clocks powered off)—Optional1.Stabilization of Clocks to the SDRAM.The system must drive clocks to the application frequency(PLL operation is not assured until the input clock reaches~20MHz).Stability of clocks at the SDRAMs will be affected by all applicable system clock devices, and time must be allotted to permit all clock devices to settle.Once a stable clock is received at the DIMM PLL,the required PLL stabilization time(assuming power to the DIMM is stable)is100microseconds.2.The system applies valid logic levels to the data inputs of the register(address and controls at the DIMM con-nector).CKE must be maintained low and all other inputs should be driven to a known state.In general these com-mands can be determined by the system designer.One option is to apply an SDRAM‘NOP’command(with CKE low),as this is the first command defined by the JEDEC Self Refresh Exit sequence(ideally this would be a‘NOP Deselect’command).A second option is to apply low levels on all of the register inputs,to be con-sistent with the state of the register outputs.3.The system switches to a logic‘high’level.The SDRAM is now functional and prepared to receive commands.Since the RESET signal is asynchronous, timing relationship to a specific clock edge is not required(during this period,register inputs must remain stable).4.The system must maintain stable register inputs until normal register operation is attained.The registers have an activation time that allows the clock receivers,input receivers,and output drivers suffi-cient time to be turned on and become stable.During this time the system must maintain the valid logic levels described in Step2.It is also a functional requirement that the registers maintain a low state at the CKE out-puts to guarantee that the DDR SDRAMs continue to receive a low level on CKE.Register activation time(t (ACT)),from asynchronous switching of RESET from low to high until the registers are stable and ready to accept an input signal,is specified in the register and DIMM do-umentation.5.System can begin the JEDEC-defined DDR SDRAM Self Refresh Exit Procedure.Self Refresh Entry(RESET low,clocks running)—OptionalAlthough keeping the clocks running increases power consumption from the on-DIMM PLL during self refresh, this is an alternate operating mode for these DIMMs.1.System enters Self Refresh entry command.(CKE→Low,CS→Low,RAS→Low,CAS→Low,WE→High)Note:The commands reach the DDR SDRAM one clock later due to the additional register pipelining on a Registered DIMM.After this command is issued to the SDRAM,all of the address and control and clock input conditions to the SDRAM are Don’t Cares—with the exception of CKE.2.The system sets RESET at a valid low level.This input condition forces all register outputs to a low state,independent of the condition on the data and clock register inputs,and ensures that CKE is a stable low-level at the DDR SDRAMs.3.The system may release DIMM address and control inputs to High-Z.This can be done after the RESET deactivate time of the register(t(INACT)).The deactivate time describes the time in which the clocks and the control and the address signals must maintain valid levels afterlow has been applied.It is highly recommended that CKE continue to remain low during the operation.4.The DIMM is in a low power,Self Refresh mode.Self Refresh Exit(RESET low,clocks running)—Optional1.The system applies valid logic levels to the data inputs of the register(address and controls at the DIMM con-nector).CKE must be maintained low and all other inputs should be driven to a known state.In general these com-mands can be determined by the system designer.One option is to apply an SDRAM‘NOP’command(with CKE low),as this is the first command defined by the Self Refresh Exit sequence(ideally this would be a ‘NOP Deselect’command).A second option is to apply low levels on all of the register inputs to be consistent with the state of the register outputs.2.The system switches to a logic'high'level.The SDRAM is now functional and prepared to receive commands.Since the signal is asynchronous, it does not need to be tied to a particular clock edge(during this period,register inputs must continue to remain stable).3.The system must maintain stable register inputs until normal register operation is attained.The registers have an activation time that allows the clock receivers,input receivers,and output drivers suffi-cient time to be turned on and become stable.During this time the system must maintain the valid logic levels described in Step1.It is also a functional requirement that the registers maintain a low state at the CKE out-puts in order to guarantee that the DDR SDRAMs continue to receive a low level on CKE.This activation time,from asynchronous switching of from low to high,until the registers are stable and ready to accept an input signal,is t(ACT)as specified in the register and DIMM documentation.4.The system can begin JEDEC defined DDR SDRAM Self Refresh Exit Procedure.Self Refresh Entry/Exit(RESET high,clocks running)—OptionalAs this sequence does not involve the use of the RESET function,the JEDEC standard SDRAM specification explains in detail the method for entering and exiting Self Refresh for this case.Self Refresh Entry(RESET high,clocks powered off)—Not PermissibleIn order to maintain a valid low level on the register output,it is required that either the clocks be running and the system drive a low level on CKE,or the clocks are powered off and RESET is asserted low according to thesequence defined in this application not e.In the case where remains high and the clocks are powered off,the PLL drives a High-Z clock input into the register clock input.Without the low level on RESET an unknown DIMM state will result.。

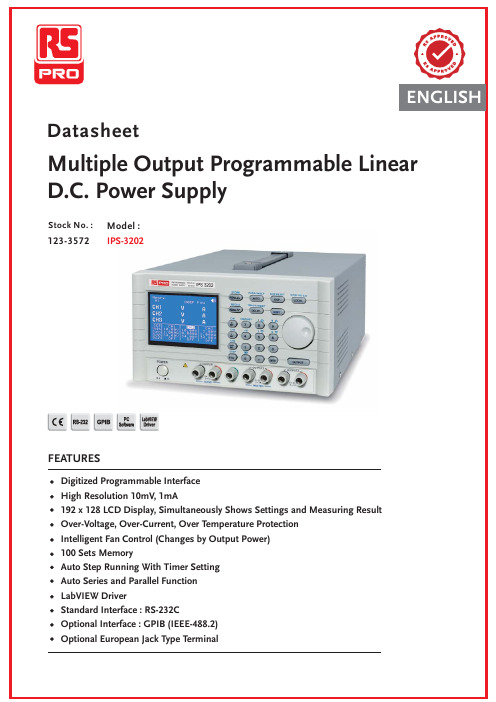

IPS-3202 三通道可编程直流电源技术数据手册说明书

READBACK RESOLUTION

Voltage

10mV(20mV, rating voltage >36V)

Current

1mA(2mA, rating current >3.0A)

READBACK ACCURACY(25 5 C)

Voltage

< 0.05%+10mV(+20mV, rating voltage >36V)

RESPONSE TIME

Voltage Up (10%~90%) Voltage Down (90%~10%)

< 100mS < 100mS ( 10% Байду номын сангаасating load)

DRIFT

Voltage Current

< 100ppm+10mV(+20mV, rating voltage >36V) < 150ppm+10mA

European Type Jack Terminal

Rear Panel

SPECIFICATIONS

OUTPUT

Voltage Current OVP

0~32Vx2, 0~6Vx1 0~2Ax2, 0~5Ax1 0~33Vx2, 0~7Vx1

LOAD REGULATION

Voltage Current

Load Effect

Voltage < 3mV(< 5mV, rating current>3.0A); Current< 6mA

Source Effect

Voltage < 3mV;Current < 6mA

MEMORY

THS3202中文资料

−50 −60 HD − Hormonic Distortion − dB −70 −80 −90 −100 3rd Harmonic −110 −120 0 2 4 6 8 10 12 VO − Output Voltage − Vpp G=5 RL = 500 Ω VCC = 15 V Rf = 420 Ω f = 10 MHz 50 48 46 44 OIP 3 − dBc 42 40 38 36 34 32 30 28 26 10 60

16.5 V ±VS ±3 V 175 mA

See Dissipation Rating Table

Continuous power dissipation TJ (3)

150°C 125°C −40°C to 85°C −65°C to 150°C 300°C 3000 V 1500 V 200 V

Copyright 2002 − 2004, Texas Instruments Incorporated

元器件交易网

THS3202

SLOS242D − SEPTEMBER 2002 − REVISED JANUARY 2004

ABSOLUTE MAXIMUM RATINGS

OIP3 vs FREQUENCY

Test Instrument Measurement Limit VCC = ±7.5 V VCC = ±7 V VCC = ±6 V

TEST CIRCUIT FOR IMD3 / OIP3

Output Power Spectrum Analyzer

2nd Harmonic

Maximum junction temperature, continuous operation, long term reliability TJ (4) Operating free-air temperature range, TA Storage temperature range, Tstg Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds

AQY214S中文资料

Footprint

Approx. 70%

2. Tape and reel

The device comes standard in a tape and reel (1,000 pcs./reel) to facilitate automatic insertion machines.

3. Controls low-level analog signals PhotoMOS relays feature extremely low closed-circuit offset voltage to enable control of low-level analog signals without distortion. 4. Low-level off state leakage current In contrast to the SSR with an off state leakage current of several milliamperes, the PhotoMOS relay features a very small off state leakage current of typ. 100 pA (AQY214S) even with the rated load voltage of 400 V.

3.0

2.5

2.0

1.5

AQY212S

威盛智能表说明书

照需量周期进行需量测量,当第一个需量周期完成后,按滑差间隔开始最大需量记录。在一个不完

整的需量周期内,不做最大需量的记录。

(3)功率方向改变时,需量中间单元清零。跨费率时段时,需量中间单元不清零,保证总最大

需量计量的连续性。下面几种情况需量中间单元清零:1电表总清零;2通讯命令清最大需量时;3按键

手动清最大需量时;4功率方向改变时;5跨月结算时。

MODBUS代码 DL/T645代码 数据内容

1.2 产品特点

本仪表采用了高精度采样计量单元和高速 MCU 数据处理单元,可实现高精度宽范围准确计量

和快速数据分析;采用段码式多行宽视角液晶显示屏,显示内容很丰富;液晶配备白色背光,可满

足黑暗环境下查阅数据的要求;采用非易失存储器存储各类数据,可长时间保存数据且掉电不丢失;

采用高精度带温补功能的时钟芯片,在工作温度范围内有效保证了时钟的准确性;支持双通信端口

位号

功能

位值与功能对应关系

缺省值

Bit 7

保留

0

Bit 6

保留

0

Bit 5

需量同步模式

1: 分钟同步 0: 时钟同步

1

Bit 4

极值结算方式

1:按日结; 0:按月结

0

Bit 3

保留

0

Bit 2

保留

0

Bit 1

保留

0

Bit 0

保留Leabharlann 0拟 制:刘展未 尹凌 2013-01-28 审 核: 工 艺: 标准化: 批 准:

GB/T17215.301-2007 多功能电能表 特殊要求

GB/T17215.322-2008 静止式有功电能表(0.2S级和 0.5S级)

HEAG HYP2120 微机变压器(三圈)差动保护装置 说明书

HYP2120微机变压器(三圈)差动保护装置使用说明书®ZHEJIANG HUAYI ELECTRIC POWER AUTOMATIONCO.,L TD目前公司推出的HYP2000系列主要产品有:HYS-8000 后台监控系统HYP2110 微机变压器(双圈)差动保护监控装置HYP2120 微机变压器(三圈)差动保护监控装置HYP2130 微机变压器后备保护监控装置HYP2140 微机厂(所)用变压器保护监控装置HYP2150 微机变压器非电量保护监控装置HYP2210 微机电容器保护监控装置HYP2310 微机PT监控(切换)装置HYP2410 微机异步电动机保护监控装置HYP2420 微机同步电动机保护监控装置HYP2510 微机进线备自投保护监控装置HYP2520 微机母联备自投保护监控装置HYP2610 微机线路保护监控装置HYP2620 微机线路保护监控装置(带高周带方向) HYP2680 微机中央信号监控装置HYP2690 通讯管理机HYP2691 通讯管理机(微型版)HYP2710 微机发电机差动保护监控装置HYP2720 微机发电机后备保护监控装置HYP2730 微机发电机转子接地保护监控装置目录1概述 (4)1.1适用范围 (4)1.2装置主要特点 (4)1.3装置基本功能 (4)1.4保护主要功能: (6)1.5测控主要功能: (6)1.6装置外形尺寸和安装尺寸 (7)2技术条件 (7)2.1环境条件 (7)2.2额定参数 (8)2.3电气绝缘性能 (8)2.4机械性能 (8)2.6安全性能 (9)2.7过载能力 (9)2.8功率消耗 (9)2.9技术参数 (9)3工作原理和结构特性 (10)3.1装置总体结构 (10)3.2装置对外接线说明 (11)3.3 保护原理框图 (14)3.4保护逻辑说明 (15)3.5装置定值范围及说明 (16)4用户手册 (18)4.1 人机交换 (18)4.2 运行人员注意事项及要求 (20)4.3 检修及维护 (20)4.4 常见问题答疑 (20)4.5常规故障检修方法 (21)5 订货须知 (22)1概述1.1适用范围HYP2120适用于 6.6~110KV 电压等级的变压器,采集变压器高中低三侧9个电流量,因而既适用于三圈变压器,又适用于双圈变压器的完全差动保护。

Belden 22 AWG 7x30 TC 洗炼铜电缆说明书

For more Informationplease call1-800-Belden1General Description:22 AWG stranded (7x30) tinned copper conductors, semi-rigid PVC insulation, twisted pairs, overallBeldfoil® (100% coverage) + tinned copper braid shield (65% coverage), PVC jacket.Physical Characteristics (Overall)ConductorAWG:# Pairs AWG Stranding Conductor Material7227x30TC - Tinned CopperTotal Number of Conductors:14InsulationInsulation Material:Insulation Material Wall Thickness (mm)S-R PVC - Semi-Rigid Polyvinyl Chloride0.279Outer ShieldOuter Shield Material:Layer #Outer Shield Trade Name Type Outer Shield Material Coverage (%)1Beldfoil®Tape Aluminum Foil-Polyester Tape1002Braid TC - Tinned Copper65Outer JacketOuter Jacket Material:Outer Jacket Material Nom. Wall Thickness (mm)PVC - Polyvinyl Chloride0.889Overall CableOverall Nominal Diameter:8.839 mmPairPair Color Code Chart:Number Color1Black & Red2Black & White3Black & Green4Black & Blue5Black & Yellow6Black & Brown7Black & OrangeMechanical Characteristics (Overall)Operating Temperature Range:-30°C To +80°CUL Temperature Rating:80°C (UL AWM Style 2464)Bulk Cable Weight:114.591 Kg/KmMin. Bend Radius/Minor Axis:88.900 mmC = CRATE REEL PUT-UP.Revision Number: 2 Revision Date: 08-22-2012© 2019 Belden, IncAll Rights Reserved.Although Belden makes every reasonable effort to ensure their accuracy at the time of this publication, information and specifications described herein are subject to error or omission and to change without notice, and the listing of such information and specifications does not ensure product availability.Belden provides the information and specifications herein on an "AS IS" basis, with no representations or warranties, whether express, statutory or implied. In no event will Belden be liable for any damages (including consequential, indirect, incidental, special, punitive, or exemplary damages) whatsoever, even if Belden has been advised of the possibility of such damages, whether in an action under contract, negligence or any other theory, arising out of or in connection with the use, or inability to use, the information or specifications described herein. All sales of Belden products are subject to Belden's standard terms and conditions of sale.Belden believes this product to be in compliance with EU RoHS (Directive 2002/95/EC, 27-Jan-2003). Material manufactured prior to the compliance date may be in stock at Belden facilities and in our Distributor’s inventory. The information provided in this Product Disclosure, and the identification of materials listed as reportable or restricted within the Product Disclosure, is correct to the best of Belden’s knowledge, information, and belief at the date of its publication. The information provided in this Product Disclosure is designed only as a general guidefor the safe handling, storage, and any other operation of the product itself or the one that it becomes a part of. This Product Disclosure is not to be considered a warranty or quality specification. Regulatory information is for guidance purposes only. Product users are responsible for determining the applicability of legislation and regulations based on their individual usage of the product.Belden declares this product to be in compliance with EU LVD (Low Voltage Directive 2014/35/EU).。

Sanwa Power System 电源系统说明书

Advanced ParametersDaily UseMaintenance & RepairExplanations for ProtectionsTroubleshooting & Warning Tones• Start-up Protection:The ESC will shut down the motor if it fails to start the motor normally within 2 seconds by increasing the throttle input. In this case, you need to move thethrottle stick back to the bottom position and restart the motor. (Possible causes of this problem: poor connection/ disconnection between the ESC and motor wires, propellers are blocked, and etc.)• Motor Lock-up Protection:The ESC will cut off its output to the motor immediately and won’t try to restart the motor when it detects the motor is locked up.In this condition, you need to pull the throttle stick to the bottom position first and then push it upward to clear the error and restart the ESC to resume the output. • Over-current Protection:The ESC will cut off its output immediately when the peak current gets close to 300A. It only restarts after you power it off and then back on. • Throttle Signal Loss Protection:When the ESC detects loss of signal for over 0.25 second, it will cut off the outputimmediately to avoid an even greater loss which may be caused by the continuous high-speed rotation of propellers. The ESC will resume the corresponding output after normal signals are received.1. How to Change the Light ColorUnscrew the two M3*8 screws for fastening the light cover with a screw driver, slide the DIP switches accordingly (as shown below) to change the light color (it’s Green by default), mount the cover back after setting.2. How to Replace a Propeller • Unscrew the two M4 *13.5 screws for fastening the blades with a screw driver and change the blade(s). If you also want to change the propeller adapter, then you need to unscrew the four M3*8 screws for fixing the adapter with another screw driver and change the whole set of propeller.• When mounting the propeller, you need to mount the bottom cover (of the propeller adapter) on the motor first, then blades, spacers and the top cover (of the propeller adapter), and then fix them with screws. Please note that the blades can rotate freely after fastening them with M4 screws, and ensure that you will also apply some glue to the screws after fastening the propeller adapter to the motor with M3 screws.Please contact Hobbywing for after-sales service timely when the power system is damaged. You can replace the damaged part(s) with the replacements (included in the product box) on condition that the coming operation won’t affect the performance of the power system, you’ve contacted and confirmed with the customer service representative; it’s forbidden to replace the damaged part(s) with other parts you configure. Please contact Hobbywing for repair timely when serious damage occurs.。

华盛源新产品简介2013.12.23

HSY华盛源机电

致力成为电力电子散热行业领导者

铜管水冷散热器

名称

应用: 管铜水冷散热是散热器家族的新秀,其安全性和稳 定性经严格试验得到了可靠的验证,现广泛应用于 汽车,煤矿、风力发电及各种电子设备等。 优点: 1、外观精美,水路排布灵活; 2、密封性、散热能力强; 3、铜质水道更耐压、防震、加工周期短,安全性 高。 3、散热效率很高。

HSY华盛源机电

HSY华盛源机电

致力成为电力电子散热行业领导者

HSY华盛源机电

致力成为电力电子散热行业领导者

Diagram 高标准的生产管理 新项目新设备

公司不断创新,开发适合市场需要,适销对路的新产品,我们公司和上海航天合作引进高 端设备、高端技术,保持着华盛源始终处于行业领跑位置。

HSY华盛源机电

致力成为电力电子散热行业领导者

关注客户,共创辉煌, 规范标准,共赢未来。

:铜管水冷ቤተ መጻሕፍቲ ባይዱ热器

HSY华盛源机电

致力成为电力电子散热行业领导者

摩擦焊水冷散热器

名称

应用: 摩擦焊水冷散热是散热器家族的高端产品,其安全 性和稳定性经严格试验得到了可靠的验证,现广泛 应用于大功率散热器,如汽车,煤矿、风力发电及 各种电子设备等。 优点: 1、较普通水冷散热器,体积更加减小,材料用量 小;水道分布复杂、多样化; 2、密封性、散热能力更强,减小了密封故障及延 长使用寿命; 3、安全性高、散热效率很高。

2、改善超大型材材料成本单价高、交期长; 3、解决材料制作过程中产生的变形、尺寸不稳定; 4、解决制作大型产品变形大平面度差,散热板加工 时产生偏差; 5、解决大型散片散热器叶齿与基板间的间隙及强度 不足,解决材料硬度不足,其强度较整体型材散 热器强度高。 6、用于大型散热器; 7、用于无法成型之型材散热器; 8、用于强度要求较高散热器。 9、有效减少散热不均。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3.3V 16M × 64/72-Bit 1 Bank SDRAM Module 3.3V 32M × 64/72-Bit 2 Bank SDRAM Module 168-Pin Unbuffered DIMM ModulesThe HYS 64(72)V16300GU and HYS 64(72)V32220GU are industry-standard 168-pin 8-byte Dual In-line Memory Modules (DIMMs) which are organized as 16M ×64, 16M ×72 in 1 bank and 32M ×64 and 32M ×72 in two banks of high-speed memory arrays designed with 128Mbit Synchronous DRAMs (SDRAMs) for non-parity and ECC applications. The DIMMs use -7.5 speed sorted 16M ×8 SDRAM devices in TSOP54 packages to meet the PC133-333 requirements and use -8 components for the standard PC100-222 applications. Decoupling capacitors are mounted on the PC board. The PC board design is in accordance with I NTEL’s PC SDRAM Rev. 1.0 Module Specification. The DIMMs have Serial Presence Detect, implemented with a serial E 2PROM using the two-pin I 2C protocol. The first 128bytes are utilized by the DIMM manufacturer and the second 128bytes are available to the end user. All INFINEON 168-pin DIMMs provide a high performance,flexible 8-byte interface in a 133.35mm long footprint, with 1.25“ (31.75mm) height.•168-Pin unbuffered 8-Byte Dual-In-Line SDRAM Modules for PC main memory applications •PC100 and PC133 versions• 1 bank 16M ×64, 16M ×72 and 2bank 32M ×64, 32M ×72 organzation •Optimized for byte-write non-parity (x64) or ECC (x72) applications •JEDEC standard Synchronous DRAMs (SDRAM)•Fully PC board layout compatible to INTEL’s Rev. 1.0 Module Specification •SDRAM Performance:•Programmed Latencies: •Single +3.3V(±0.3V) Power Supply •and Wrap Sequence(Sequential and Interleave)•Auto-Refresh (CBR) and Self-Refresh •Decoupling capacitors mounted on substrate •All inputs and outputs are LVTTL compatible •Serial Presence Detect with E 2PROM•Utilizes 16M ×8 SDRAMs in TSOPII-54 packages with 4096refresh cycles every 64ms •133.35mm ×31.75mm ×4,00mm card size with gold-contact pads-7.5-8Unit PC133PC100f CK ClockFrequency (max.)133100MHzt AC Clock Access Time5.46nsProduct Speed CL t RCDt RP-7.5PC133333-8PC100222Note:All part numbers end with a place code, designating the die revision. Consult factory forcurrent revision. Example: HYS 64V16300GU-8-C, indicates that Rev.C dies are used for SDRAM components.Ordering Information TypeCodePackageDescriptionsModule Height128MByte DIMMs HYS 64V16300GU-7.5-C PC133-333-520L-DIM-168-33133Mhz 16M ×641bank SDRAM module 1.25“HYS 72V16300GU-7.5-C PC133-333-520L-DIM-168-33133Mhz 16M ×721bank SDRAM module 1.25“HYS 64V16300GU-8-C PC100-222-620L-DIM-168-33100MHz 16M ×641bank SDRAM module 1.25“HYS 72V16300GU-8-C PC100-222-620L-DIM-168-33100MHz 16M ×721bank SDRAM module1.25“256MByte DIMMs HYS 64V32220GU-7.5-C PC133-333-520L-DIM-168-30133MHz 32M ×642bank SDRAM module 1.25“HYS 72V32220GU-7.5-C PC133-333-520L-DIM-168-30133Mhz 32M ×722bank SDRAM module 1.25“HYS 64V32220GU-8-C PC100-222-620L-DIM-168-30100MHz 32M ×642bank SDRAM module 1.25“HYS 72V32220GU-8-CPC100-222-620L-DIM-168-30100Mhz 32M ×722bank SDRAM module1.25“Pin Definitions and FunctionsA0-A11Address Inputs WE Read/Write Input V SS GroundBA0, BA1Bank Selects CKE0, CKE1Clock Enable SCL Clock for SPD DQ0 - DQ63Data Input/Output CLK0 - CLK3Clock Input SDA Serial Data Out CB0-CB7Check Bits(x72 modules only)DQMB0 - DQMB7Data Mask N.C.No Connection RAS Row Address Strobe CS0 - CS3Chip Select––CAS Column AddressStrobe VDDPower (+3.3V)––Address FormatPart Number Rows Columns Bank Select Refresh Period Interval 16M×64HYS64V16300GU121024k64ms15,6µs 16M×72HYS72V16300GU121024k64ms15,6µs 32M×64HYS64V32220GU121024k64ms15,6µs 32M×72HYS72V32220GU121024k64ms15,6µsPin ConfigurationPIN#Symbol PIN#Symbol PIN#Symbol PIN#Symbol1V SS43V SS85V SS127V SS2DQ044DU86DQ32128CKE03DQ145CS287DQ33129CS34DQ246DQMB288DQ34130DQMB65DQ347DQMB389DQ35131DQMB76V DD48DU90V DD132N.C.7DQ449V DD91DQ36133V DD8DQ550N.C.92DQ37134N.C.9DQ651N.C.93DQ38135N.C.10DQ752N.C. (CB2)94DQ39136CB611DQ853N.C. (CB3)95DQ40137CB712V SS54V SS96V SS138V SS13DQ955DQ1697DQ41139DQ4814DQ1056DQ1798DQ42140DQ4915DQ1157DQ1899DQ43141DQ5016DQ1258DQ19100DQ44142DQ51Pin Configuration (cont’d)PIN#Symbol PIN#Symbol PIN#Symbol PIN#Symbol 17DQ1359V DD101DQ45143V DD18V DD60DQ20102V DD144DQ52 19DQ1461N.C.103DQ46145N.C.20DQ1562DU104DQ47146DU21N.C. (CB0)63CKE1105N.C. (CB4)147N.C.22N.C. (CB1)64V SS106N.C. (CB5)148V SS23V SS65DQ21107V SS149DQ53 24N.C.66DQ22108N.C.150DQ54 25N.C.67DQ23109N.C.151DQ55 26V DD68V SS110V DD152V SS27WE69DQ24111CAS153DQ56 28DQMB070DQ25112DQMB4154DQ57 29DQMB171DQ26113DQMB5155DQ58 30CS072DQ27114CS1156DQ59 31DU73V DD115RAS157V DD32V SS74DQ28116V SS158DQ60 33A075DQ29117A1159DQ61 34A276DQ30118A3160DQ62 35A477DQ31119A5161DQ63 36A678V SS120A7162V SS37A879CLK2121A9163CLK3 38A1080N.C.122BA0164N.C.39BA181WP123A11165SA040V DD82SDA124V DD166SA141V DD83SCL125CLK1167SA242CLK084V DD126N.C.168V DD Note:Pin names in parentheses are for the x72 ECC versions; example: Pin 106 = (CB5).Block Diagram for 16M×64/72 SDRAM DIMM Modules (HYS64/72V16300GU)Block Diagram for 32M×64/72 SDRAM DIMM Modules (HYS64/72V32220GU)DC CharacteristicsTA=0 to 70°C; V SS=0V; V DD,V DDQ=3.3V±0.3VParameter Symbol Limit Values Unitmin.max.Input High Voltage V I H 2.0V DD+0.3V Input Low Voltage V IL–0.50.8V Output High Voltage (I OUT=–4.0mA)V OH 2.4–V Output Low Voltage (I OUT=4.0 mA)V OL–0.4VInput Leakage Current, any input(0V<V IN<3.6V, all other inputs=0V)II(L)–4040µAOutput Leakage Current(DQ is disabled, 0V<V OUT<V DD)IO(L)–4040µACapacitanceTA=0 to 70°C; V DD=3.3V±0.3V, f=1MHzParameter Symbol Limit Values Unitmax. 16M×64max.16M×72max.32M×64max.32M×72Input Capacitance(A0 to A11, BA0, BA1, RAS, CAS, WE)CI16572105144pFInput Capacitance (CS0 - CS3)C CS32403543 pF Input Capacitance (CLK0 - CLK3)C CLK38404245pF Input Capacitance (CKE0, CKE1)C CKE65726572pF Input Capacitance (DQMB0 - DQMB7)C I413132020pFInput/Output Capacitance (DQ0 - DQ63, CB0 - CB7)CIO10101717pFInput Capacitance (SCL, SA0-2)C SC8888pF Input/Output Capacitance C SD8888pFOperating Currents per SDRAM Component 1)T A =0 to 70o C, V DD =3.3V±0.3V(Recommended Operating Conditions unless otherwise noted)Parameter TestCondition Symbol-7.5-8Unit Notemax.Operating CurrenttRC=t RCMIN., t CK=t CKMIN.Outputs open, Burst Length=4, CL=3All banks operated in random access,all banks operated in ping-pong mannerto maximize gapless data access–I CC1160150mA1)Precharge Standby Currentin Power Down ModeCS=V IH (min.), CKE≤V IL(MAX)tCK=min.I CC2P 1.5 1.5mA1)Precharge Stand-by Current in Non-Power Down Mode CS=V IH (MIN.), CKE≥V IH(MIN)tCK=min.I CC2N4035mA1)No Operating CurrenttCK=min., CS=V IH(MIN), active state (max. 4banks)CKE≥V IH(MIN.)I CC3N5045mA1) CKE≤V IL(MAX.)I CC3P1010mA1)Burst Operating CurrenttCK=min.,Read command cycling–I CC410090mA1), 2)Auto-Refresh CurrenttCK=min.,Auto-Refresh command cycling–I CC5230210mA1)Self-Refresh CurrentSelf-Refresh Mode, CKE=0.2V–I CC6 1.5 1.5mA1)AC Characteristics3), 4)TA=0 to 70°C; V SS=0V; V DD=3.3V±0.3V, t T=1nsParameter Symbol Limit Values Unit Note-7.5 PC133-333-8PC100-222min.max.min.max. Clock and Access TimeClock Cycle TimeCAS Latency=3CAS Latency=2tCK7.510––1010––nsns–System FrequencyCAS Latency=3CAS Latency=2fCK––133100––100100MHzMHz–Clock Access TimeCAS Latency=3CAS Latency=2tAC––5.46––66nsns4), 5)Clock High Pulse Width t CH 2.5–3–ns6) Clock Low Pulse Width t CL 2.5–3–ns6)Setup & Hold ParametersInput Setup Time t IS 1.5–2–ns7) Input Hold Time t IH0.8–1–ns7) Power Down Mode Entry Time t SB–1–1CLK8) Power Down Mode Exit Setup Time t PDE1–1–CLK9) Mode Register Setup Time t RSC2–2–CLK Transition Time (rise and fall)t T1–1–ns–Common ParametersRAS to CAS Delay t RCD20–20–ns–Precharge Time t RP20–20–ns–Active Command Period t RAS45100k50100k ns–Cycle Time t RC67.5–70–ns–Bank-to-Bank Delay Time t RRD15–16–ns–CAS to CAS Delay Time (same bank)t CCD1–1–CLK–Refresh CycleRefresh Period (4096cycles)t REF –64–64ms Self-Refresh Exit Time t SREX1–1–CLK10)Read Cycle Data Out Hold Time t OH 3–3–ns 4)Data Out to Low Impedance t LZ 0–0–ns –Data Out to High Impedance t HZ 3738ns 11DQM Data Out Disable Latency t DQZ–2–2CLK–Write CycleData Input to Precharge (write recovery)t WR 2–2–CLK –DQM Write Mask Latencyt DQW––CLK–AC Characteristics (cont’d) 3), 4)T A =0 to 70°C; V SS =0V; V DD =3.3V ±0.3V, t T =1ns ParameterSymbolLimit ValuesUnitNote-7.5PC133-333-8PC100-222min.max.min.max.Notes1.These parameters depend on the cycle rate. These values are measured at 133MHz for -7.5modules and at 100Mhz for -8 modules. Input signals are changed once during t CK, except for Iand for standby currents when t CK=infinity. All values are shown per memory component.CC62.These parameters are measured with continuous data stream during read access and all DQtoggling. CL=3 and BL=4 assumed and the V DDQ current is excluded.3.All AC characteristics are shown on SDRAM component level.An initial pause of 100µs is required after power-up, then a Precharge All Banks command must be given followed by eight Auto-Refresh (CBR) cycles before the Mode Register Set Operation can begin.4.AC timing tests have V IL=0.4V and V IH=2.4V with the timing referenced to the 1.4V crossoverpoint. The transition time is measured between V IH and V IL. All AC measurements assume t=1ns with the AC output load circuit show. Specified t AC and t OH parameters are measured Twith a 50pF only, without any resistive termination and with a input signal of 1V/ns edge rate between 0.8V and 2.0V.5.If clock rising time is longer than 1ns, a time (t T/2–0.5)ns must be added to this parameter.6.Rated at 1.4V7.If t T is longer than 1ns, a time (t T–1)ns has to be added to this parameter.8.Anytime the Refresh Period has been exceeded, a minimum of two Auto-Refresh (CBR)commands must be given to “wake-up” the device.9.Timing is asynchronous. If setup time is not met by rising edge of the clock then the CKE signalis assumed latched on the next cycle.10.Self-Refresh Exit is a synchronous operation and begins on the second positive clock edge afterCKE returns high. Self-Refresh Exit is not complete until a time period equal to t RC is satisfied after the Self Refresh Exit command is registered.11.This is referenced to the time at which the output achieves the open circuit condition, not tooutput voltage levels.A Serial Presence Detect storage device—E2PROM—is assembled onto the module. Information about the module configuration, speed, etc. is written into the E2PROM device during moduleproduction using a Serial Presence Detect protocol (I2C synchronous 2-wire bus).SPD-Table for PC133 Modules:Byte#Description SPD EntryValueHex16Mx64 -7.516Mx72-7.532Mx64-7.532Mx72-7.50Number of SPD bytes128801T otal bytes in Serial PD256082Memory Type SDRAM043Number of Row Addresses(without BS bits)120C4Number of Column Addres-ses100A5Number of DIMM Banks 1 / 201026Module Data Width64 / 7240484048 7Module Data Width (cont’d)0008Module Interface Levels LVTTL019SDRAM Cycle Time at CL=37.5 ns7510SDRAM Access time fromClock at CL=35.4 ns5411Dimm Config none / ECC00020002 12Refresh Rate/Type Self-Refresh,15.6ms8013SDRAM w idth, P rimary x80814Error Checking SDRAM datawidthn/a / x80008000815Minimum clock delay forback-to-back random columnaddress tccd= 1 CLK0116Burst Length supported1, 2, 4 & 8 0F 17Number of SDRAM banks404 18Supported CAS Latencies CAS latency = 2& 306 19CS Latencies CS latency = 001 20WE Latencies Write latency = 00121SDRAM DIMM module attributes non buffered/nonreg.0022SDRAM Device Attributes:GeneralVcc tol +/- 10%0E23Min. Clock Cycle Time atCAS Latency = 210.0 ns A024 Max. data access time fromClock for CL=26.0 ns6025 Minimum Clock Cycle Timeat CL = 1not supported FF26Maximum Data Access Timefrom Clock at CL=1not supported FF27Minimum Row PrechargeTime20 ns1428Minimum Row Active to RowActive delay tRRD15 ns0FByte#Description SPD EntryValueHex16Mx64 -7.516Mx72-7.532Mx64-7.532Mx72-7.529Minimum RAS to CAS delaytRCD20 ns1430Minimum RAS pulse widthtRAS45 ns2D31Module Bank Density (perbank)128 MByte2032SDRAM input setup time 1.5 ns1533SDRAM input hold time0.8 ns0834SDRAM data input hold time 1.5 ns1535SDRAM data input setuptime0.8 ns0862-61Superset information (may beused in future)FF62SPD Revision Revision 1.21263Checksum for bytes 0 - 6213251426 64-125Manufacturers information XX XX XX XX 126Frequency Specification64127Support Details AF FF128+Unused storage locations FFSPD-Table for PC100 Modules:Byte#Description SPD EntryValueHex16Mx64-816Mx72-832Mx64-832Mx72-80Number of SPD bytes128801T otal bytes in Serial PD256082Memory Type SDRAM043Number of Row Addresses(without BS bits)120C4Number of Column Addres-ses100A5Number of DIMM Banks 1 / 201026Module Data Width64 / 7240484048 7Module Data Width (cont’d)0008Module Interface Levels LVTTL019SDRAM Cycle Time at CL=310.0 ns A010SDRAM Access time fromClock at CL=36.0 ns6011Dimm Config none / ECC00020002 12Refresh Rate/Type Self-Refresh,15.6ms8013SDRAM w idth, P rimary x80814Error Checking SDRAM datawidthn/a / x80008000815Minimum clock delay forback-to-back random columnaddress tccd= 1 CLK0116Burst Length supported1, 2, 4 & 8 0F 17Number of SDRAM banks404 18Supported CAS Latencies CAS latency = 2& 306 19CS Latencies CS latency = 001 20WE Latencies Write latency = 00121SDRAM DIMM module attributes non buffered/nonreg.0022SDRAM Device Attributes:GeneralVcc tol +/- 10%0E23Min. Clock Cycle Time atCAS Latency = 210.0 ns A024 Max. data access time fromClock for CL=26.0 ns6025 Minimum Clock Cycle Timeat CL = 1not supported FF26Maximum Data Access Timefrom Clock at CL=1not supported FF27Minimum Row PrechargeTime20 ns1428Minimum Row Active to RowActive delay tRRD16 ns10Byte#Description SPD EntryValueHex16Mx64-816Mx72-832Mx64-832Mx72-829Minimum RAS to CAS delaytRCD20 ns1430Minimum RAS pulse widthtRAS45 ns2D31Module Bank Density (perbank)128 MByte2032SDRAM input setup time 2 ns2033SDRAM input hold time 1 ns1034SDRAM data input hold time 2 ns2035SDRAM data input setuptime1 ns1062-61Superset information (may beused in future)FF62SPD Revision Revision 1.21263Checksum for bytes 0 - 6271837284 64-125Manufacturers information XX XX XX XX 126Frequency Specification100 MHz64127Support Details AF FF128+Unused storage locations FFPackage OutlinesSorts of PackingPackage outlines for tubes, trays etc. are contained in ourData Book “Package Information”.Dimensions in mmSorts of PackingPackage outlines for tubes, trays etc. are contained in ourData Book “Package Information”.Dimensions in mm。