2.5-12 micron spectrophotometry and imaging of the CfA sample

micronmtfdkba512tfh参数

micronmtfdkba512tfh参数Micron MTFDKBA512TFH 是一款 Micron Technology 公司生产的SATA 接口的固态硬盘(SSD)产品。

下面将介绍该产品的一些主要参数。

容量:Micron MTFDKBA512TFH 固态硬盘的总容量为 512GB(千兆字节),可以满足大多数用户的存储需求。

接口:该固态硬盘采用了SATAIII接口标准(6Gb/s),与主板或扩展卡的SATA插槽兼容。

尺寸:Micron MTFDKBA512TFH 固态硬盘的尺寸为 2.5 英寸,符合标准的硬盘尺寸,适用于大多数笔记本电脑和台式机。

读写速度:该固态硬盘具有出色的读写速度,能够提供更快的数据传输和载入速度。

具体的性能参数可能因不同的使用场景而有所差异。

耐用性:Micron MTFDKBA512TFH 采用固态技术,不包含任何机械部件,因此具有较长的寿命和更高的抗震性能。

此外,它还具有抗磁性,能够更好地保护数据的安全性。

功耗:固态硬盘比传统的机械硬盘具有更低的功耗,可以帮助延长笔记本电脑或台式机的电池寿命。

支持TRIM:Micron MTFDKBA512TFH 固态硬盘支持 TRIM 功能,可以通过操作系统轻松管理和优化固态硬盘的性能。

随机读写性能:该固态硬盘拥有优秀的随机读写性能,可以有效处理大量小文件的读写操作,提高文件传输速度和系统运行效率。

数据安全性:该固态硬盘支持硬件加密和数据保护功能,可以帮助用户保护存储在固态硬盘上的敏感数据。

兼容性:Micron MTFDKBA512TFH 固态硬盘兼容大多数操作系统,如Windows、Mac OS和Linux等。

它可以与现有的硬件设备连接和使用,无需进行额外的配置。

总结:Micron MTFDKBA512TFH 固态硬盘是一款高性能、高稳定性并具备较大存储容量的产品。

无论是用于日常办公、高速数据传输还是游戏娱乐,该固态硬盘都能提供出色的性能和用户体验。

MEMORY存储芯片N25Q128A11BSF40G中文规格书

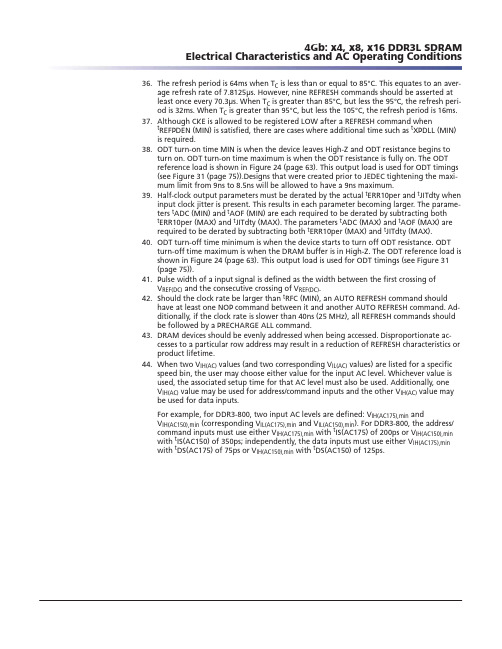

36.The refresh period is 64ms when T C is less than or equal to 85°C. This equates to an aver-age refresh rate of 7.8125μs. However, nine REFRESH commands should be asserted atleast once every 70.3μs. When T C is greater than 85°C, but less the 95°C, the refresh peri-od is 32ms. When T C is greater than 95°C, but less the 105°C, the refresh period is 16ms.37.Although CKE is allowed to be registered LOW after a REFRESH command whent REFPDEN (MIN) is satisfied, there are cases where additional time such as t XPDLL (MIN)is required.38.ODT turn-on time MIN is when the device leaves High-Z and ODT resistance begins toturn on. ODT turn-on time maximum is when the ODT resistance is fully on. The ODTreference load is shown in Figure 24 (page 63). This output load is used for ODT timings(see Figure 31 (page 75)).Designs that were created prior to JEDEC tightening the maxi-mum limit from 9ns to 8.5ns will be allowed to have a 9ns maximum.39.Half-clock output parameters must be derated by the actual t ERR10per and t JITdty wheninput clock jitter is present. This results in each parameter becoming larger. The parame-ters t ADC (MIN) and t AOF (MIN) are each required to be derated by subtracting botht ERR10per (MAX) and t JITdty (MAX). The parameters t ADC (MAX) and t AOF (MAX) arerequired to be derated by subtracting both t ERR10per (MAX) and t JITdty (MAX).40.ODT turn-off time minimum is when the device starts to turn off ODT resistance. ODTturn-off time maximum is when the DRAM buffer is in High-Z. The ODT reference load isshown in Figure 24 (page 63). This output load is used for ODT timings (see Figure 31(page 75)).41.Pulse width of a input signal is defined as the width between the first crossing ofV REF(DC) and the consecutive crossing of V REF(DC).42.Should the clock rate be larger than t RFC (MIN), an AUTO REFRESH command shouldhave at least one NOP command between it and another AUTO REFRESH command. Ad-ditionally, if the clock rate is slower than 40ns (25 MHz), all REFRESH commands shouldbe followed by a PRECHARGE ALL command.43.DRAM devices should be evenly addressed when being accessed. Disproportionate ac-cesses to a particular row address may result in a reduction of REFRESH characteristics orproduct lifetime.44.When two V IH(AC) values (and two corresponding V IL(AC) values) are listed for a specificspeed bin, the user may choose either value for the input AC level. Whichever value isused, the associated setup time for that AC level must also be used. Additionally, oneV IH(AC) value may be used for address/command inputs and the other V IH(AC) value maybe used for data inputs.For example, for DDR3-800, two input AC levels are defined: V IH(AC175),min andV IH(AC150),min (corresponding V IL(AC175),min and V IL(AC150),min ). For DDR3-800, the address/command inputs must use either V IH(AC175),min with t IS(AC175) of 200ps or V IH(AC150),minwith t IS(AC150) of 350ps; independently, the data inputs must use either V IH(AC175),minwith t DS(AC175) of 75ps or V IH(AC150),min with t DS(AC150) of 125ps.4Gb: x4, x8, x16 DDR3L SDRAM Electrical Characteristics and AC Operating ConditionsVoltage Initialization/ChangeIf the SDRAM is powered up and initialized for the 1.35V operating voltage range, volt-age can be increased to the 1.5V operating range provided the following conditions aremet (See Figure 51 (page 139)):•Just prior to increasing the 1.35V operating voltages, no further commands are issued,other than NOPs or COMMAND INHIBITs, and all banks are in the precharge state.•The 1.5V operating voltages are stable prior to issuing new commands, other thanNOPs or COMMAND INHIBITs.•The DLL is reset and relocked after the 1.5V operating voltages are stable and prior toany READ command.•The ZQ calibration is performed. t ZQinit must be satisfied after the 1.5V operatingvoltages are stable and prior to any READ command.If the SDRAM is powered up and initialized for the 1.5V operating voltage range, voltagecan be reduced to the 1.35V operation range provided the following conditions are met(See Figure 51 (page 139)) :•Just prior to reducing the 1.5V operating voltages, no further commands are issued,other than NOPs or COMMAND INHIBITs, and all banks are in the precharge state.•The 1.35V operating voltages are stable prior to issuing new commands, other thanNOPs or COMMAND INHIBITs.•The DLL is reset and relocked after the 1.35V operating voltages are stable and prior toany READ command.•The ZQ calibration is performed. t ZQinit must be satisfied after the 1.35V operatingvoltages are stable and prior to any READ command.4Gb: x4, x8, x16 DDR3L SDRAM Voltage Initialization/Change。

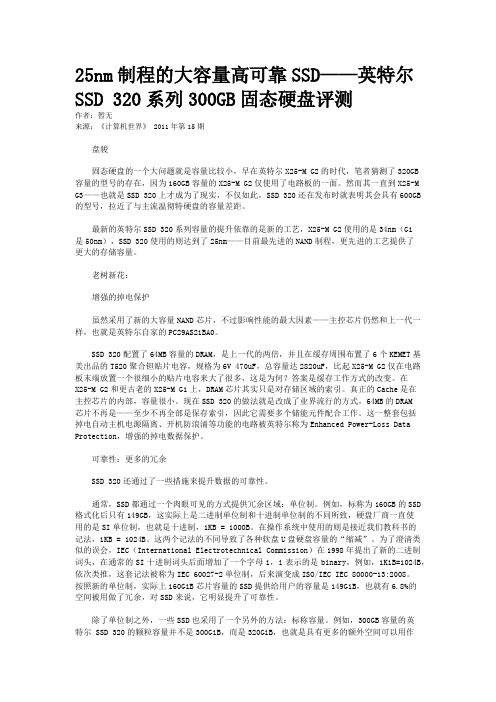

25nm制程的大容量高可靠SSD——英特尔SSD 320系列300GB固态硬盘评测

25nm制程的大容量高可靠SSD——英特尔SSD 320系列300GB固态硬盘评测作者:暂无来源:《计算机世界》 2011年第15期盘骏固态硬盘的一个大问题就是容量比较小,早在英特尔X25-M G2的时代,笔者猜测了320GB容量的型号的存在,因为160GB容量的X25-M G2仅使用了电路板的一面。

然而其一直到X25-M G3——也就是SSD 320上才成为了现实,不仅如此,SSD 320还在发布时就表明其会具有600GB 的型号,拉近了与主流温彻特硬盘的容量差距。

最新的英特尔SSD 320系列容量的提升依靠的是新的工艺,X25-M G2使用的是34nm(G1是50nm),SSD 320使用的则达到了25nm——目前最先进的NAND制程,更先进的工艺提供了更大的存储容量。

老树新花:增强的掉电保护虽然采用了新的大容量NAND芯片,不过影响性能的最大因素——主控芯片仍然和上一代一样,也就是英特尔自家的PC29AS21BA0。

SSD 320配置了64MB容量的DRAM,是上一代的两倍,并且在缓存周围布置了6个KEMET基美出品的T520聚合钽贴片电容,规格为6V 470uF,总容量达2820uF,比起X25-M G2仅在电路板末端放置一个很细小的贴片电容来大了很多,这是为何?答案是缓存工作方式的改变。

在X25-M G2和更古老的X25-M G1上,DRAM芯片其实只是对存储区域的索引。

真正的Cache是在主控芯片的内部,容量很小。

现在SSD 320的做法就是改成了业界流行的方式,64MB的DRAM芯片不再是——至少不再全部是保存索引,因此它需要多个储能元件配合工作。

这一整套包括掉电自动主机电源隔离、开机防浪涌等功能的电路被英特尔称为Enhanced Power-Loss Data Protection,增强的掉电数据保护。

可靠性:更多的冗余SSD 320还通过了一些措施来提升数据的可靠性。

通常,SSD都通过一个肉眼可见的方式提供冗余区域:单位制。

Micron 产品数据手册说明书

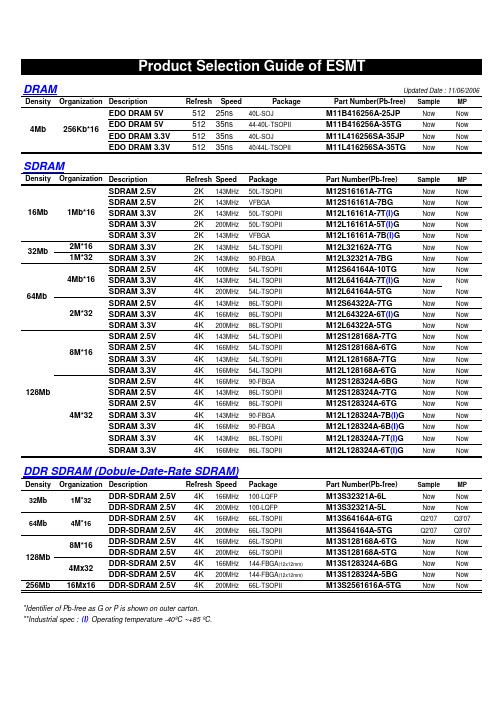

DRAMUpdated Date : 11/06/2006DensityOrganization DescriptionRefreshSpeedPackagePart Number(Pb-free)Sample MP EDO DRAM 5V 51225ns 40L-SOJ M11B416256A-25JP Now Now EDO DRAM 5V 51235ns 44-40L-TSOPII M11B416256A-35TG Now Now EDO DRAM 3.3V 51235ns 40L-SOJ M11L416256SA-35JP Now Now EDO DRAM 3.3V 51235ns 40/44L-TSOPIIM11L416256SA-35TGNowNowSDRAMDensityOrganization DescriptionRefresh SpeedPackagePart Number(Pb-free)Sample MP SDRAM 2.5V 2K 143MHz 50L-TSOPII M12S16161A-7TG Now Now SDRAM 2.5V 2K 143MHz VFBGA M12S16161A-7BG Now Now SDRAM 3.3V 2K 143MHz 50L-TSOPII M12L16161A-7T (I)G Now Now SDRAM 3.3V 2K 200MHz 50L-TSOPII M12L16161A-5T (I)G Now Now SDRAM 3.3V 2K 143MHz VFBGA M12L16161A-7B (I)G Now Now 2M*16SDRAM 3.3V 2K 143MHz 54L-TSOPII M12L32162A-7TG Now Now 1M*32SDRAM 3.3V 2K 143MHz 90-FBGA M12L32321A-7BG Now Now SDRAM 2.5V 4K 100MHz 54L-TSOPII M12S64164A-10TG Now Now SDRAM 3.3V 4K 143MHz 54L-TSOPII M12L64164A-7T (I)G Now Now SDRAM 3.3V 4K 200MHz 54L-TSOPII M12L64164A-5TG Now Now SDRAM 2.5V 4K 143MHz 86L-TSOPII M12S64322A-7TG Now Now SDRAM 3.3V 4K 166MHz 86L-TSOPII M12L64322A-6T (I)G Now Now SDRAM 3.3V 4K 200MHz 86L-TSOPII M12L64322A-5TG Now Now SDRAM 2.5V 4K 143MHz 54L-TSOPII M12S128168A-7TG Now Now SDRAM 2.5V 4K 166MHz 54L-TSOPII M12S128168A-6TG Now Now SDRAM 3.3V 4K 143MHz 54L-TSOPII M12L128168A-7TG Now Now SDRAM 3.3V 4K 166MHz 54L-TSOPII M12L128168A-6TG Now Now SDRAM 2.5V 4K 166MHz 90-FBGA M12S128324A-6BG Now Now SDRAM 2.5V 4K 143MHz 86L-TSOPII M12S128324A-7TG Now Now SDRAM 2.5V 4K 166MHz 86L-TSOPII M12S128324A-6TG Now Now SDRAM 3.3V 4K 143MHz 90-FBGA M12L128324A-7B (I)G Now Now SDRAM 3.3V 4K 166MHz 90-FBGA M12L128324A-6B (I)G Now Now SDRAM 3.3V 4K 143MHz 86L-TSOPII M12L128324A-7T (I)G Now Now SDRAM 3.3V4K166MHz86L-TSOPIIM12L128324A-6T (I)GNowNowDDR SDRAM (Dobule-Date-Rate SDRAM)Density Organization DescriptionRefresh SpeedPackagePart Number(Pb-free)Sample MP DDR-SDRAM 2.5V 4K 166MHz 100-LQFP M13S32321A-6L Now Now DDR-SDRAM 2.5V 4K 200MHz 100-LQFP M13S32321A-5L Now Now DDR-SDRAM 2.5V 4K 166MHz 66L-TSOPII M13S64164A-6TG Q2'07Q3'07DDR-SDRAM 2.5V 4K 200MHz 66L-TSOPII M13S64164A-5TG Q2'07Q3'07DDR-SDRAM 2.5V 4K 166MHz 66L-TSOPII M13S128168A-6TG Now Now DDR-SDRAM 2.5V 4K 200MHz 66L-TSOPII M13S128168A-5TG Now Now DDR-SDRAM 2.5V 4K 166MHz 144-FBGA (12x12mm)M13S128324A-6BG Now Now DDR-SDRAM 2.5V 4K 200MHz 144-FBGA (12x12mm)M13S128324A-5BG Now Now 256Mb16Mx16DDR-SDRAM 2.5V 4K200MHz66L-TSOPIIM13S2561616A-5TGNowNow*Identifier of Pb-free as G or P is shown on outer carton.**Industrial spec : (I) Operating temperature -40ºC ~+85 ºC.2M*3264Mb4Mb*1632Mb4Mb 256Kb*161Mb*1616Mb 128Mb8M*164Mx324M*32128Mb8M*1632Mb 64Mb1M*324M*16Mobile SDRAMDensityOrganizationDescriptionRefresh Speed Package & MCPPart Number(Pb-free)Sample MP Mobile SDRAM 2.5V4K 100MHz 50L-TSOPII M52S16161A-10T (I)G Now Now Mobile SDRAM 2.5V 4K 125MHz 50L-TSOPII M52S16161A-8T (I)G Now Now Mobile SDRAM 1.8V4K 100MHz50L-TSOPIIM52D16161A-10T (I)G Now Now Mobile SDRAM 2.5V 4K 100MHz 54L-TSOPII M52S32162A-10T (I)G Now Now Mobile SDRAM 2.5V 4K 100MHz 54-FBGA M52S32162A-10B (I)G Now Now Mobile SDRAM 2.5V 4K 133MHz 54L-TSOPII M52S32162A-7.5T (I)G Now Now Mobile SDRAM 2.5V 4K 133MHz 54-FBGA M52S32162A-7.5B (I)G Now Now Mobile SDRAM 1.8V 4K 100MHz 54L-TSOPII M52D32162A-10T (I)G Now Now Mobile SDRAM 1.8V 4K 100MHz 54-FBGA M52D32162A-10B (I)G Now Now Mobile SDRAM 1.8V 4K 100MHz 54L-TSOPII M52D32162A-7.5T (I)G Now Now Mobile SDRAM 1.8V 4K 133MHz 54-FBGA M52D32162A-7.5B (I)G Now Now Mobile SDRAM 2.5V 4K 100MHz 90-FBGA M52S32321A-10B (I)G Now Now Mobile SDRAM 2.5V 4K 133MHz 90-FBGA M52S32321A-7.5B (I)G Now Now Mobile SDRAM 1.8V 4K 100MHz 90-FBGA M52D32321A-10B (I)G Now Now Mobile SDRAM 1.8V 4K 133MHz 90-FBGA M52D32321A-7.5B (I)G Now Now Mobile SDRAM 2.5V 4K 100MHz 54L-TSOPII M52S64164A-10T (I)G Q2 '07Q3 '07Mobile SDRAM 2.5V 4K 100MHz 54-FBGA M52S64164A-10B (I)G Q2 '07Q3 '07Mobile SDRAM 2.5V 4K 133MHz 54L-TSOPII M52S64164A-7.5T (I)G Q2 '07Q3 '07Mobile SDRAM 2.5V 4K 133MHz 54-FBGA M52S64164A-7.5B (I)G Q2 '07Q3 '07Mobile SDRAM 1.8V 4K 100MHz 54L-TSOPII M52D64164A-10T (I)G Q2 '07Q3 '07Mobile SDRAM 1.8V 4K 100MHz 54-FBGA M52D64164A-10B (I)G Q2 '07Q3 '07Mobile SDRAM 1.8V 4K 100MHz 54L-TSOPII M52D64164A-7.5T (I)G Q2 '07Q3 '07Mobile SDRAM 1.8V 4K 133MHz 54-FBGA M52D64164A-7.5B (I)G Q2 '07Q3 '07Mobile SDRAM 2.5V 4K 100MHz 86L-TSOPII M52S64322A-10T (I)G Q2 '07Q3 '07Mobile SDRAM 2.5V 4K 100MHz 90-FBGA M52S64322A-10B (I)G Q2 '07Q3 '07Mobile SDRAM 2.5V 4K 133MHz 86L-TSOPII M52S64322A-7.5T (I)G Q2 '07Q3 '07Mobile SDRAM 2.5V 4K 133MHz 90-FBGA M52S64322A-7.5B (I)G Q2 '07Q3 '07Mobile SDRAM 1.8V 4K 100MHz 86L-TSOPII M52D64322A-10T (I)G Q2 '07Q3 '07Mobile SDRAM 1.8V 4K 100MHz 90-FBGA M52D64322A-10B (I)G Q2 '07Q3 '07Mobile SDRAM 1.8V 4K 100MHz 86L-TSOPII M52D64322A-7.5T (I)G Q2 '07Q3 '07Mobile SDRAM 1.8V4K133MHz 90-FBGAM52D64322A-7.5B (I)GQ2 '07Q3 '07*Identifier of Pb-free as G or P is shown on outer carton.**Industrial spec : (I) Operating temperature -40ºC ~+85 ºC.64Mb4Mx162Mx32(1)All Mobile functions are included : PASR,TCSR,DS,Deep power down mode.(2)Max. Icc6 : Self-refresh current with full bank in 70 ºC .1Mx16Max. Icc6= 75uA (1.8V)16Mb32Mb2Mx161Mx32。

药物分析专业英语

(dissolution) vessel 溶出杯(FTIR) 傅里叶变换红外光谱仪13C-NMR spectrum,13CNMR 碳-13核磁共振谱1ength basis 长度基准1H-NMR 氢谱2D-NMR 二维核磁共振谱:2D-NMR3D-spectrochromatogram 三维光谱-波谱图Aa stream of nitrogen 氮气流a wide temperature range 宽的温度范围absolute detector response 检测器绝对响应(值)absolute entropy 绝对熵absolute error 绝对误差absolute reaction rate theory 绝对反应速率理论absolute temperature scale 绝对温标absorbance 吸光度,而不是吸收率(absorptance)。

当我们忽略反射光强时,透射率(T)与吸光度(A)满足如下关系式:A=lg(1/T)。

absorbance noise, absorbing noise 吸光度噪音。

也称光谱的稳定性,是指在确定的波长范围内对样品进行多次扫描,得到光谱的均方差。

吸光度噪音是体现仪器稳定性的重要指标。

将样品信号强度与吸光度噪音相比可计算出信噪比。

absorbed water 吸附水absorptance 吸收率absorptant 吸收剂absorption band 吸收带absorption cell 吸收池absorption curve 吸收光谱曲线/光吸收曲线absorption tube 吸收管abundance 丰度。

即具有某质荷比离子的数量accelerated solvent extraction(ASE) 加速溶剂萃取accelerated testing 加速试验accelerating decomposition 加速破坏acceptance limit,acceptance criterion 验收限度,合格标准accidental error 随机误差accuracy 准确度。

石油英语词汇(U)

石油英语词汇(U)石油英语词汇(U)石油英语词汇(U)u trap 虹吸管u u形u-antenna u型天线u-bend u形弯头u-bolt u形螺栓u-clamp u形夹子u-form tube u形管u-iron 槽铁u-joint 万向节u-leather ring u形皮圈u-nut u形螺母u-pipe u形管u-symmetric matrices u对称阵u-th-pb dating 铀钍铅年龄测定u-tube heat exchanger u形管换热器u-type manometer u形压力计u.f. 脲醛u.p.o 无失真输出功率u.s. 如上所述u.s. 在上面提及之处u.s.a.e.c. 美国原子能委员会u.s.mesh series 美国筛制u.s.standard sieve designation 美国标准筛标记u.s.standard sieve series 美国标准筛制u.v.r. 低电压继电器uadi 干谷ub 单总线缓冲器ubbelodhe viscosimeter 尤比洛得粘度计ubho 组装式翼片扩眼器ubiquitous element 遍在性元素ubiquity 普遍性uc 稠度单位uc 在建造中uca 超声波水泥分析仪ucl 控制上限ud 单总线显示udc 上死点udc 通用十进制分类法udometer 雨量器udw 用户定义字ueje 上射流器uet 地下爆炸试验ufo 不明飞行物ug 尺寸不足ug 地下ugandite 暗橄白榴岩ugm 最大地面增益ugrandite 铬钙铁榴石类uhe 特别恶劣的环境uhf 超高频uhmw polyethylene 超高分子量聚乙烯uhv 超高压uintahite 硬沥青uintaite 硬沥青ujt 单结晶体管uk 联合王国ukooa 英国海上作业者协会ukrainite 少英二长岩ul 负载不足ul 上下ul 上限ul 无限的ulatisian 乌拉蒂斯阶ulcc 超大型油轮ulcer 溃疡;腐败的根源ulexite 钠硼解石ulf 超低频ulfe 最终地层评价uliginous =uliginose 淤泥的ullage bob 储罐空高测量锤ullage gage 储罐空高检尺ullage gaging 储罐空高测量ullage reference-point 储罐空高计量基准点ullage rule 量油尺ullage tape 储罐空高计量卷尺ullage 容器内液面以上的空间ullaging 测空高量油ullmanite 锑硫镍矿ulmain 无结构镜煤ulmal 铝锰硅合金ulmic acid 棕腐酸ulmification 泥炭化ulmin 棕腐质ulminite 腐木质体ulmipollenites] 榆粉属ulmite 腐殖颗粒;腐殖砂漆ulmoideipites] 肋榆粉属ulrichodina] 乌氏牙形石属uls 极限状态ulsane 乌散烷ulsel 超长电极距电测井ulsterian 乌尔斯特统ult. 上月ult. 最终的;极限的ultimate analysis 元素分析ultimate bearing capacity 极限承载能力ultimate bending strength 极限抗弯强度ultimate capacity 最终产量ultimate composition 元素组成ultimate compression strength 极限抗压强度ultimate cost 最终费用ultimate cumulative recovery 最终累积产量ultimate demand 最终需要ultimate design 极限设计ultimate elongation 极限伸长ultimate life 最终寿命ultimate limit state 极限状态ultimate load 极限载荷ultimate oil produced 最终采出油量ultimate oxygen demand 极限需氧量ultimate principle 基本原理ultimate production 最终开采量ultimate range 最大距离ultimate recoverable reserves 最终可采储量ultimate recovery factor 最终采收率ultimate recovery 最终采收率ultimate resistance 极限电阻ultimate resources 总资源储量ultimate separation 极限分离ultimate spacing pattern 最大井距布井法ultimate strain 极限应变ultimate strength 极限强度ultimate stress 极限应力ultimate system 基本系统ultimate temperature rise 极限温升ultimate temperature 极限温度ultimate tensile strength 极限抗拉强度ultimate tension 极限拉力ultimate value 极限值ultimate wetting-phase saturation 最终润湿相饱和度ultimate 最终的;极限的;极端的;总的ultimatum 最后结论;基本原理ultor 高压最后阳极ultra deep well 超深井ultra filtration membrane 超滤膜ultra large crude carrier 超大型油轮ultra rays 宇宙线ultra selective cracking 超选择性裂解ultra- 超ultra-abyssal 超深海的ultra-acid rock 超酸性岩石ultra-acidic 超酸性的ultra-acoustics 超声学ultra-albanite 超沥青ultra-clean chamber 超净间ultra-clean 超净的ultra-deep exploration 超深勘探ultra-deep 超深的ultra-high purity 超高纯度ultra-high strength steel 超高强度钢ultra-high-draft 超大牵伸ultra-high-speed spinning 超高速纺ultra-low density polyethylene 超低密度聚乙烯ultra-pure zinc anode 超纯锌阳极ultra-sensitive pressure gauge 高灵敏度压力计ultra-slim hole rig 超小井眼钻机ultra-sonic defect detector 超声波探伤仪ultra-sonic depth finder 超声波测深仪ultra-violet absorber 紫外线吸收剂ultra-violet absorption spectrometry 紫外线吸收光谱法ultra-violet absorption spectrum 紫外线吸收光谱ultra-violet analysis 紫外分析ultra-violet resistance 耐紫外性ultrabasic complex 超基性杂岩体ultrabasic rock 超基性岩ultrabasic 超基性的ultracentrifugal method 超离心法ultracentrifugation 超速离心分离ultracentrifuge 超速离心机ultradeep dive 超深潜水ultraduralumin 超硬铝ultrafiche 超微卡片ultrafilter 超滤器ultrafiltration 超过滤ultrafine fiber 超细纤维ultraharmonics 超高频谐波ultrahigh frequency 超高频ultrahigh voltage transformer oil 超高压变压器油ultrajet 高效能射孔器ultralinear 超线性ultralong 超长的ultralong-spaced electric log 超长电极距测井ultralow frequency 超低频ultralow-frequency oscillator 超低频振荡器ultralumin 超硬铝ultraluminescence 紫外荧光ultramafic rock 超镁铁岩ultramafite 超镁铁岩ultramarine 群青;深蓝色ultrametamorphism 超变质作用ultramicro method 超微量法ultramicro 超微的ultramicro-analysis 超微量分析ultramicro-determination 超微量测定ultramicro-earthquake 超微地震ultramicrobalance 超微量天平ultramicrochemistry 超微量化学ultramicrofiche =ultraficheultramicrofossil 超微化石ultramicrometer 超测微计ultramicron 超微粒子ultramicropaleontology 超微古生物学ultramicropore 超微孔隙ultramicroscope 超显微镜ultramicroscopic 超显微的;超微型的ultramicrospectrophotometer 超显微分光光度计ultramicrospectrophotometry 超显微分光光度测定法ultramicrostructure 超微结构ultramicrotechnique 超微技术ultramicrotome 超薄切片机ultramicrowave 超微波ultramodern 最新的ultramylonite 超糜棱岩ultraoptimeter 超光测仪ultrapaleontology 超微古生物学ultraperm 超导磁铁镍钼铜合金ultraperminvar 超永磁合金ultraphotometer 超光度计ultraplankton 超微浮游生物ultraporcelain 超高频瓷ultrapurification 超提纯ultrapurity 超纯度ultrared heating 红外线加热ultrared ray 红外线ultrasensitive amino acid analyzer 超灵敏氨基酸分析仪ultrashort wave 超短波ultrasonator 超声振荡器ultrasonic atomizer 超声雾化器ultrasonic bias 超声偏移ultrasonic casing inspection tool 超声套管检查测井仪ultrasonic cement analyzer 超声水泥分析器ultrasonic cleaner 超声波清洗槽ultrasonic cleaning 超声波清洗ultrasonic converter 超声波变换器ultrasonic defectoscope 超声探伤器ultrasonic degradation 超声降解ultrasonic delay line 超声波延迟线ultrasonic detector 超声波检测器ultrasonic electrostatic sprayer 超声波静电喷涂机ultrasonic examination 超声检验ultrasonic extraction 超声萃取ultrasonic extractor 超声萃取器ultrasonic flaw detection 超声波裂纹探测ultrasonic flow meter 超声波流量计ultrasonic frequency 超声频率ultrasonic gage 超声波测量计ultrasonic generator 超声波发生器ultrasonic imager 超声波成象仪ultrasonic inspection 超声波检查ultrasonic investigation 超声波测试ultrasonic leak detection 超声检漏ultrasonic luminescence 超声波发光ultrasonic machining 超声波加工ultrasonic modulator 超声波调制器ultrasonic monitor 超声波监测器ultrasonic particle monitor 超声波机械杂质监测仪ultrasonic probe 超声波探头ultrasonic pulse 超声波脉冲ultrasonic radar 超声雷达ultrasonic ranging 超声波测距ultrasonic seismic scattering tomography 超声地震散射层析成象法ultrasonic seismology 超声波地震学ultrasonic sensor 超声波传感器ultrasonic soldering 超声波焊接ultrasonic spot welding 超声波点焊ultrasonic testing 超声波检验ultrasonic thickness gage 超声波测厚计ultrasonic thickness test 超声波测厚ultrasonic thicknessmeter 超声波测厚计ultrasonic transducer 超声换能器ultrasonic transmitter 超声波发射器ultrasonic wave field 超声波场ultrasonic wave 超声波ultrasonic 超声的ultrasonics 超声学ultrasonography 超声波探测术ultrasound tomography 超声层析成象法ultrasound 超声ultraspeed 超高速度ultrastability 超高稳定性ultrastable y-type zeolite 超稳y型沸石ultrastructure 超微结构ultrathermometer 限外温度计ultrathick complexed gel 超稠多元胶ultrathin film 超薄薄膜ultrathin section 超薄片ultratrace element 超痕量元量ultratrace 超痕量ultraudion 反馈电路;检波器电路ultraviolet absorbent 紫外线吸收剂ultraviolet absorption 紫外线吸收ultraviolet band 紫外区ultraviolet detector 紫外线检测器ultraviolet flame detection 紫外线火焰检测ultraviolet generator 紫外线发生器ultraviolet lamp 紫外线灯ultraviolet light absorber 紫外线吸收剂ultraviolet light 紫外线ultraviolet microscope 紫外线显微镜ultraviolet monitor 紫外监测器ultraviolet photoelectron spectroscopy 紫外光电子能谱学ultraviolet photography 紫外线摄影术ultraviolet protecting agent 紫外线防护剂ultraviolet radiation 紫外线辐射ultraviolet ray 紫外线ultraviolet recorder 紫外线记录器ultraviolet region 紫外区ultraviolet remote sensing 紫外遥感ultraviolet screening agent 紫外线屏蔽剂ultraviolet spectral analysis 紫外光谱分析ultraviolet spectrogram 紫外线光谱图ultraviolet spectrograph 紫外光谱仪ultraviolet spectrometer 紫外分光计ultraviolet spectrometry 紫外光谱测定法ultraviolet spectrophotometer 紫外分光光度计ultraviolet spectrophotometry 紫外分光光度测定法ultraviolet spectroscopy 紫外线光谱法ultraviolet spectrum 紫外光谱ultraviolet transmittance 紫外线透射率ultraviolet tube 紫外光灯管ultraviolet 紫外线ultraviolet-visible detector 紫外可见光检测器ultraviolet-visible pectrophotometer 紫外可见分光光度计umbella] 伞轮藻属umber 赭土umbilic 脐点umbilical cable 控制电缆umbilical line 集成管束umbilical 脐带umbilically-controlled 管缆控制的umbrella antenna 伞状天线umbrella roof 伞形顶umbrella 伞;综合的umc 水下管汇中心umformer 直流变压器;变流机umpire analysis 仲裁分析umpire 公断人umpolarization 退极化umptekite 碱闪正长岩un 联合国un- 不unabr. 没有删节的unaccelerated aging 自然老化unacceptable product 不合格品unacceptable 不能接受的unadvisable 不适宜的unaffected 未受影响的unaided eye 肉眼unakite 绿帘花岗岩unallowable instruction digit 非法字符unaltered 未改变的unambiguous interpretation 明确的解释unambiguous 单值的unanimity 一致unanimous agreement 一致同意unanimous approval 一致通过unanimous resolution 一致决定unanimous 一致的unarmored cable 非铠装电缆unary operation 一元操作unary operator 一元算子unassociated gas 非伴生气unassorted 未分选的unatextisporites] 单缝联囊粉属unattended operation 自动操作unattended pumper 自动抽油井unattended station 无人管理站unattended 无人管理的unaudited voucher 未审核凭单unauthorized 未经认可的unavailability 不能利用unavailable energy 无用能unavoidable 不可避免的unbaffled 无屏蔽的unbalance load 不平衡负载unbalance 不平衡unbalanced bridge 不平衡电桥unbalanced circuit 不对称回路unbalanced drill collar 偏重钻铤unbalanced load 不平衡载荷unbalanced pressure 不平衡压力unbalanced seal 非平衡密封unbalanced 不平衡的unbalancedness 不平衡性unballast 卸压舱水unbedded 不成层的unbend 弄直unbiased confidence interval 无偏置信区间unbiased critical region 无偏临界区域unbiased error 无偏误差unbiased estimate 无偏估计unbiased importance sampling 无偏重要性抽样unbiased statistics 无偏统计unbiased 不偏的;未加偏压的unbiasedness 无偏性unblanking 增辉;开启;开锁unblended 未掺合的unblind 截断符号unboarded derrick 无遮挡井架unbonded casing 未胶结套管unbonded coating 未粘合绝缘层unbonded 非粘合的unbound electron 自由电子unbound molecule 无束缚分子unbounded fracture 无边界裂缝unbounded function 无界函数unbounded reservoir 不封闭储集层unbounded solution 无界解unbranched-chain hydrocarbon 无支链烃unbroken rock 未破碎岩石unbuffered 无缓冲的unbuilding 破坏;去磁;剥磁损失;自励损失unburnt 不完全燃烧的unc thread 统一标准粗牙螺纹unc 统一标准粗牙螺纹uncapped 无管帽的uncased crossing 不加套管的穿越uncased hole 裸眼井uncased wellbore 裸眼井筒uncased 无套管的uncemented fault 未胶结断层uncemented rock 未胶结岩石uncemented 未胶结的uncentered interference figures 偏心干涉图uncentralized screen 未扶正筛管uncertain interpretation 不确定性解释uncertain region 不确定范围uncertainty analysis 不确定性分析uncertainty principle 测不准原理uncertainty 不确定性unchangeability 不变性uncharacteristic 无特征的uncharged structure 未充填结构uncharged 不带电的uncharted 图上未注明的unchecked construction 盲目建设unchecked 未经核对的unchuck 拆下卡盘uncitral 联合国国际贸易法律委员会unclamp 卸开卡子unclamped elevator 开式吊卡unclamped 未制动的unclasping 放松unclassified 解除保密的unclosed 开着的uncoated cast-iron pipe 裸铸铁管uncoated sample 未涂层样品uncoated 不加涂层的uncoaxiality 不同轴性uncoil 松开uncoiler 展卷机uncol 通用计算机语言uncollectable accounts 呆帐uncollectible notes 坏票uncolored 无色的;未着色的uncombined carbon 游离碳uncombined 未结合的;游离的uncommercial 无工业价值的uncompacted gravel 充填不密实的砾石uncompacted sand 未压实的砂层uncompaction 欠压实uncompatibility 不相容性uncompensated amplifier 无补偿放大器uncompensated drainage 无赔偿的石油流失uncompensated 未补偿的uncompleted anticline 不完整背斜uncompressible 不可压缩的unconcern 漠不关心uncondensible 不能冷凝的unconditional acceptance 无条件承兑unconditional branch instruction 无条件转移指令unconditional branch 无条件转移unconditional contract 无条件合约unconditional convergence 无条件收敛unconditional delivery 无条件交货unconditional expected payoff criterion 无条件支付期望值准则unconditional jump 无条件转移unconditional order 无条件定货unconditional stability 无条件稳定unconditional transfer 无条件转移unconfined 无约束的unconfirmed credit 未确认信用证unconfirmed letter of credit 非保兑信用证unconformability of dip 角度不整合unconformability of lap 海侵不整合unconformability 不整合unconformable contact 不整合接触面unconformable stratification 不整合层理unconformable surface 不整合面unconformable 不整合的unconformity bounded stratigraphic unit 不整合围限地层单位unconformity by erosion 侵蚀不整合unconformity interface 不整合界面unconformity surface 不整合面unconformity trap 不整合圈闭unconformity 不一致uncongealable dynamite 耐冻的黄色炸药uncongealable 不冻结的unconsolidated core 松散岩心unconsolidated formation 疏松地层unconsolidated rubble 非固结碎石层unconsolidated sand 非胶结砂岩unconsolidated surface layer 未固结表层unconsolidated 未固结的unconsolidation 松散unconstrained minimization 无约束极小化unconstrained optimization 无约束优化unconstrained problem 无约束问题unconstrained 无约束的uncontaminated zone 未污染带uncontaminated 未污染的uncontinuity 不连续性uncontinuous change 非连续性变化uncontrollable 不可控制的uncontrolled flow 敞喷uncontrolled sidetrack 未受控制侧钻unconventional gas reservoir 非常规气藏unconventional gas resources 非常规天然气资源unconvertible hydrocarbon 未能转化的烃uncorked 未加塞的uncorrelated variables 不相关变量uncorrelated 不相关的uncouple 解开uncover 无盖uncovered canal 明渠uncovered map 除去冲积土的地质图uncracking 展开uncrosslinked gel 非交联凝胶uncrystalline 非晶质的uncrystallized 未结晶的unctuosity 油性;油腻;润滑性unctuous 油性的uncured phenolic resin 未凝固的酚醛树脂uncurtailed production 不限制开采uncut diamond 未加工的金刚石unda 浪蚀环境undamaged formation face 未受污染的地层面undamaged perforation 无污染射孔undamaged well 未污染井undamaged 未损坏的undamped geophone 无阻尼检波器undamped oscillation 无阻尼振动undamped pendulum 无阻尼摆undamped wave 无阻尼波undark 夜明涂料;使明亮undated check 未注日期支票undated deposit 不定期存款undathem facies 浅海岩相undation 波动;起伏;大波状褶皱undaturbidite 浪成浊积岩undecane 十一烷undecanoic acid 十一烷酸undecene 十一碳烯undecimal 十一进制的undecyl 十一基undecylene 十一碳烯undefined 未定义的;未定界的;不明确的undeformed 未变形的undegraded material 未降解物质undepleted 未衰竭的undepreciated balance 未提折旧余额undepreciated cost 未提折旧成本under construction 在建造中under control 受控under drive gear 减速传动齿轮under gauge 尺寸小于标准under production 生产不足under- 下under-balanced drilling 欠平衡钻井under-capitalization 投资不足under-compensation 欠补偿under-current relay 低电流继电器under-damped motion 欠阻尼运动under-river pipeline crossing 河床下管线穿越under-stream period 工作期under-travel 减距行程under-utilization 利用不足underaction 辅助动作;反应不足;不够灵活underbalance 欠平衡underbalanced perforating 欠平衡射孔underbead crack 焊道下裂纹underbunching 电子欠集聚underburden 下伏岩层undercapacity 非饱和量undercarriage 底架undercharge 非饱和充电;缺荷underclay 底粘土undercoat 底涂层undercommutation 迟后换向;欠整流undercompacted formation 欠压实地层undercompacted 欠压实的undercompaction 欠压实underconsolidation 不充分固结undercooling 过冷undercoupling 欠耦合undercritical conditions 亚临界条件undercrossing 管道水下穿越undercuring 欠处理;欠硫化;欠熟undercurrent 潜流undercut bolt 下凹螺栓undercut drilling tool 底切式钻井工具undercut slot 梯形割缝undercut 下部凹陷;淘底undercutting 底切;掏槽;钻杆接头下端面磨蚀underdamping 弱衰减underdeterminant 子行列式underdetermined equation 欠定方程underdeveloped countries 不发达国家underdeveloped reservoir 未充分开发的油藏underdeveloped 未充分发育的underdevelopment 显象不足;发展不充分underdraft 轧件下弯underdrain 暗沟;聚水系统;地下排水管underdrainage 地下排水underestimate 低估underestimation 估计不足underexcitation 欠励磁underexposure 曝光不足;照射不足underfeature 小起伏地形underfeed 下部进料underfilm corrosion 膜下腐蚀underfire 自下燃烧;欠火的underfloor 地板下面underflow 潜流underfold 次生小型褶皱underframe 底架underfrequency 频率过低;低于额定频率undergage 尺寸不足undergauge bit 缩径钻头undergauge hole 小于钻头的井眼undergo 受underground blast 地下爆炸underground blowout 地下井喷underground cable 地下电缆underground cavern 地下洞穴underground combustion 地下燃烧underground conduit 地下管道underground corrosion 地下腐蚀underground detonation 地下爆炸underground drain 地下排水管underground explosion 地下爆炸underground filling installation 地下装油设施underground flooding 地下注水underground folding 深带褶皱underground gas-holder 地下储气罐underground gasification 地下气化underground heated line 地下加热管线underground image reconstruction 地下图象重建underground liquefied petroleum gas storage 地下液化石油气库;液化石油气地下储存underground loss 地下损耗underground natural gas storage 地下储气库underground nuclear explosion 地下核爆炸underground oil storage 地下油库;地下储油underground petrol tank 地下油罐underground pipeline 地下管道underground pressure 岩层压力underground property 地下财产underground reservoir 地下储集层;地下库underground seismic survey 地下地震测量underground seismics 地下地震学underground storage pool 地下油气库;地下储存用的采竭油层underground storage 地下储存;地下油气库underground structure 地下构造underground tank 地下储罐underground temperature gradient 地温梯度underground water level 地下水面underground water sealed oil storage in rock caverns 地下水封石洞油库underground water supply 地下水供给underground water surface 地下水面underground water table 地下水位underground water 地下水underground work 地下作业underground works 地下工程underground 地下的underguard 下部保护物underheated 加热不足的underlay 倾斜;下伏层;下伏的underlayer 下层underlie 横在…的下面;构造…的基础;下层;倾斜余角;延伸矿体underlife 欠提underlimb 平卧褶皱的下翼underline 底线;插图说明;在…下划线;强调underload 欠载underloading 负荷不够underlying asthenosphere 下伏软流圈underlying bed 下伏层;底层underlying bedrock 下伏基岩underlying block 下伏断块underlying formation 下伏地层underlying unconformity 下伏不整合underlying 在下面的undermass 下伏岩体undermigration 偏移不足undermine 底切undermixing 混合不足undermodulated 调制不足的underneath 下部underpan 底盘underpass 地道;高桥下通道;下穿交叉道underplate 基础;基座;底板underpower 功率不足underpressing 压制不够underpressure 低压力;真空计压力underpressured reservoir 欠压储集层underpriced 作价低估underpriming 注油不足underproof 不合格的underpunch 下部孔;低位穿孔underquenching 淬火不足underrate 低估underream 管下扩眼underreamed zone 管下扩眼井段underreamer cutter 管下扩眼器刀刃underreamer 管下扩眼器underreaming bit 套管下扩眼钻头underreaming fluid 扩眼液underreinforced 加固不足的underrelaxation 低松弛underriding 俯冲underrun 在下面通过;低于估计的产量undersampling 采样过疏undersaturated condition 欠饱和状态undersaturated oil 欠饱和原油undersaturated reservoir 欠饱和油藏undersaturated 欠饱和的undersaturation 欠饱和undersea delta 海下三角洲undersea detection 水下探测undersea ranging 水下测距undersea vehicle 潜水器undersea 海面下的undersealing 底封underseam 底部煤层undersell 廉价出售underset 与海面流向或风向相反的潜流;逆流;下部矿脉;支撑undershoot 跨越放炮underside welding 仰焊underside 下面;内面;下侧undersigned 签字人;在下面签名的undersize core 小于标准尺寸的岩心undersize 尺寸过小undersized coupling 薄壁管箍undersized grain 尺寸过小的颗粒undersized slot concept 选择偏小割缝尺寸的设计概念underslung 悬挂的underspeed 速度不足understable 欠稳定的understanding 了解understeer 转向不足;对驾驶盘反应迟钝understressed sand 疏松砂岩understressing 应力不足understructure 下层结构undersupplied products 短线产品undersupply 供给不足undersurface filling 液面下灌注undersurface loading 液面下灌装underswing 负脉冲信号;幅度不足undertake 承担undertaker 承办人;计划者;企业家undertaking 任务;计划;事业;企业;保证;承担underthrust fault 俯冲断层underthrust mass 俯冲体underthrust plate 俯冲板块underthrust 俯冲断层underthrusting 俯冲undertighten 不够紧密undertonging 上扣不足undertow mark 底流痕undertow 底流undervaluation 评价过低undervalue 低估undervoltage relay 欠压继电器undervoltage trip 欠压跳闸undervoltage 欠压underwater acoustic communication apparatus 水声通信机underwater acoustic positioning system 水声定位系统underwater acoustic transducer 水声换能器underwater acoustics 水声学underwater blast 水下爆炸underwater cable 水下电缆underwater camera 水下照相机underwater coating compound 水下涂料underwater communication 水下通信underwater compass 水下罗盘underwater completion 水下完井underwater coring 水下取心underwater coupling 水下联接underwater crossing 水下穿越underwater current 潜流underwater cutting blowpipe 水下切割割炬underwater drilling 水下钻井underwater emission 水下发射underwater exploration 水下勘探underwater explosion charge 水下炸药underwater gas shielded arc welding 水下气体保护焊underwater gathering line 水下集油管道underwater gravimeter 水下重力仪underwater gyro compass system 水下陀螺罗经系统underwater hammer 水下打桩机underwater house 水下工作舱underwater hyperbaric welding habitat 水下高压焊接舱underwater inclinometer system 水下倾斜仪系统underwater laser radar 水下激光雷达underwater laser surveying system 水下激光测量系统underwater laser 水下激光器underwater listening device 水下监听装置underwater listening post 水下监听站underwater manned submersible 水下载人潜水器underwater navigation 水下导航underwater noise 水下噪声underwater observations 水下观测underwater penetration 入水深度underwater pile driver 水下打桩机underwater pipeline 水下管道underwater plow 水下开沟犁underwater position fixing technique 水下定位技术underwater prospecting 水下勘探underwater robot 水下遥控机械装置underwater safety valve 水下安全阀underwater sampling 水下取样underwater seismic survey 水下地震勘探underwater sensor 水下传感器underwater separator 水下分离器underwater ship 潜水船underwater shock 水下冲击underwater signal 水下信号underwater sound telephone 水下声能电话underwater sound 水声underwater source 水下震源underwater speech communication 水下语言通信underwater surveillance 水下监听underwater survey 水下测量underwater telemetry 水下遥测技术underwater television 水下电视underwater tracking system 水下跟踪系统underwater trench 水下管沟underwater tv 水下电视underwater vehicle 潜水器underwater visibility 水下能见度underwater wave 水下波underwater welding 水下焊接underwater well 水下井underwater wellhead 水下井口装置underwater 水中的underway 正在进行underweight 重量不足的;不足的重量underwork 附属性工作;支持结构underwrite 写在下面underwriter 保证人undesirable 不符合要求的undesired signal 干扰信号undetectable 探测不到的undetected 未检测到的undeterminable 不可测定的undetermined coefficient 待定系数undetermined 未定的undeveloped field 未开发油气田undeveloped proved reserves 未开发的证实储量undeveloped region 未开发区undeveloped 未开发的undiluted 未稀释的undiminished 等幅的undiscovered possible reserves 待发现可能储量undiscovered potential recovery 待发现潜在可采量undiscovered resources 待发现资源undissolved residue 不溶残渣undissolved 未溶解的undissolving 不溶的undistorted 无畸变的undistributed earnings 未分配盈利undistributed profit 未分配利润undisturbed flow 未扰动的流动undisturbed formation 原状地层undisturbed sample 未扰动的样品undisturbed soil 未扰动土undisturbed zone 原状地层undisturbed 未扰动的undivided interest farmout 不可分割权益转租undivided interest 不可分割权益undivided-interest pipeline 合资管线undo 放松;拆开;使恢复原状;取消undock 出坞undomed salt 非盐丘的盐undp 联合国开发计划署undrained 水系不发育的undrawn yarn 未拉伸丝undrillable 不能钻的undrilled 未钻的undrinkable water 非饮用水undue wear 过度的磨损undue 过度的undulate fold 波状褶皱undulate 波动;波状的undulating anticline 波状背斜undulating current 波动电流undulating horizon 波状层undulating monocline 波状单斜层undulating quantity 波动值undulating 起伏的undulation 波状;波浪形地面;波动undulatisporites] 波缝孢属undulator 波纹机;波纹印码机undulatory motion 波状运动undulatory 波动的unearned profit 分外利润;非营业利润unearthed 未接地的;采掘出的uneconomic 不经济的unef thread 统一标准特细牙螺纹unemployed capital 游资unemployment 失业unep 联合国环境规划署unequal angle 不等边角钢unequal 不平均的uneven distribution 不均匀分布uneven grain 不均匀颗粒uneven heating 不均匀加热uneven injection 不均匀注入uneven load 不均匀载荷uneven settlement 不均匀沉陷uneven surface 粗糙面uneven wear 不均匀磨损uneven 不平的unevenbanded 不均匀条带状unevenness of twisting 捻度斑unevenness 不均匀性unexpected expenses 不可预见费unexpected pay 不可预见费用unexpected shutdown 意外停输unexpected 想不到的unexpl 未爆炸的unexpl 未解释的unexpl 未勘探的unexplained 未解释的unexploited 未开采的unexplored region 未勘探地区unexplored 未勘探的unf thread 统一标准细牙螺纹unfair competition 不公平竞争unfair price 不合理价格unfamiliar feature 未知要素unfasten 解开unfathomable 深不可测的unfaulted crust 未断裂地壳unfaulted downwarp 非断裂下挠unfaulted syncline 无断层向斜unfaulted 无断层的unfavorable area 不利地区unfavorable balance 逆差unfavorable trade balance 对外贸易逆差unfavorable 不利的unfilled bitumen 纯沥青unfiltered 未过滤的unfinished bolt 粗制螺栓unfired process area 无火加工区unfired 不烧的unflowing well 非自喷井unfoamed crosslinked gel 不发泡交联凝胶unfolded 未褶皱的unfolding 消褶皱作用unforeseeable 不可预见的unforeseen 未预见到的unformed 未成熟的;未成形的unfortunate 不幸的unfossiliferous 不含化石的unfreezing 解卡unfused 未熔化的ungaite 奥长英安岩ungated noise 非选通噪声ungated 闭塞的ungelled 未成胶的unglazed crucible 素烧坩埚ungrounded 不接地的unguent 润滑油;软膏unheated line 不加热管线unhec 联合国人类环境会议unhindered 不受阻碍的unhydrated 未水合的uni- 单uni-dimensional displacement 一维驱替uniaxial compressive strength 单轴抗压强度uniaxial orientation 单轴取向uniaxial stress 单向应力uniaxial 单轴的uniaxially-stretched film 单轴向拉伸薄膜unibody 单片式汽车车身;单片式车身汽车unibolt coupling 带锥形台肩的单螺栓管子联接件unibus 单总线unicellular algae 单细胞藻类unicellular plastic 单孔塑料unichoke 互感扼流圈unicircuit 集成电路unicity 单一性uniclinal fold 单斜褶皱uniclinal structure 单斜构造uniclinal 单斜的unicline 单斜unicontrol 单向控制unidentifiable 无法鉴别的unidimensional linear flow 一维线性流动unidirected discharge 单向放电unidirectional bus 单向总线unidirectional conductivity 单向传导率unidirectional current 单向电流unidirectional nonwoven fabric 单向无纺织物unidirectional orientation 单向定向unidirectional perforating 单向射孔unidirectional prover 单向标准体积管unidirectional shooting 单向放炮unidirectional spread 单边排列unidirectional twist 单向捻unidirectional 同一方向的unido 联合国工业发展组织unidyne 灯丝屏极同一电源式双栅极管unifet 单极场效应晶体管unification 统一unified budget 综合预算unified miniature screw thread 统一标准小直径螺纹unified purchase and sale 统购统销unified screw thread 统一标准螺纹unified state allocation 国家统一调配uniflow engine 单流机uniflow 单流uniflux 单向流动unifluxor 匀磁线uniform acceleration 匀加速度uniform asymptotic formula 均匀渐近公式uniform bed 均质层uniform bound 一致界uniform circular motion 匀速圆周运动uniform coating 均匀涂层uniform compression 均匀压缩uniform contact 均匀接触uniform convergence 一致收敛uniform corrosion 均匀腐蚀uniform cross section 等截面uniform cross-section jacket 等截面导管架uniform decompression 均匀减压uniform dielectric 均匀介质uniform distribution 均匀分布uniform fluid 均匀流体uniform formation 均质地层uniform grid 均匀网格uniform intergranular porosity 均匀粒间孔隙度uniform internal diameter 等内径uniform load 均布载荷uniform magnetic field 均匀磁场uniform magnetization 均匀磁化uniform mix 均匀混合物uniform motion 均匀运动uniform permeability interval 均匀渗透性层段uniform plane state 均一平面状态uniform price 统一价格uniform sandstone 均质砂岩uniform settling 均匀沉降uniform spheres 均匀球粒uniform stability 一致稳定性uniform stream 匀流uniform strength 均匀强度uniform temperature 均匀温度uniform thickness 等厚uniform variable motion 匀变速运动uniform wear 均匀磨损uniform wettability 均匀润湿性uniform 均匀的uniform-flux fracture 流量均布型裂缝uniforma price 单一价格uniformitarian 均变论者uniformitarianism 均变论;推今及古原理uniformity coefficient 均匀度uniformity of texture 结构的均质性uniformity ratio 均匀系数uniformity 均匀性uniformization 均匀化;单值化uniformly accelerated motion 匀加速运动uniformly distributed load 均布载荷uniformly retarded motion 匀减速运动unifunction pipeline 单功能流水线uniguide 单向管unijunction transistor 单结晶体管unijunction 单结unilateral contract 单方承担义务的合同unilateral fault 单向扩展断层unilateral faulting 单侧断裂unilateral import quota 单边进口限额。

MT25QU512ABB8ESF-0SIT

Signal Assignments – Package Code: SFFigure 6: 16-Pin, Plastic Small Outline – SO16 (Top View)12345678161514131211109C DQ0V SSW#/DQ2DQ3/HOLD#V CC RESET#DNU DNU DNU DNU DNU DNU DNU C DQ0V SSW#/DQ2DNU DNU DNU DNU C DQ0V SSW#/DQ2DNU DNU DNU DNU S#DQ1DQ3/HOLD#V CC DNU DNU DNU DNU S#DQ1DQ3/RESET#V CCDNUDNUDNUDNU S#DQ18MT25QXXXXXXX 3EXX-XXXXMT25QXXXXXXX 1EXX-XXXXNotes: 1.RESET# or HOLD# signals can share Pin 1 with DQ3, depending on the selected device(see Part Numbering Ordering Information). When using single and dual I/O commandson these parts, DQ3 must be driven high by the host, or an external pull-up resistor mustbe placed on the PCB, in order to avoid allowing the HOLD# or RESET# input to float.2.Pin 3 = RESET# or DNU, depending on the part number. This signal has an internal pull-up resistor and may be left unconnected if not used.Signal Assignments – Package Code: W9Figure 7: 8-Pin, W-PDFN (Top View)12348765S#DQ1W#/DQ2V1MT25QXXXXXXX 3EXX-XXXXS#DQ1W#/DQ2V V CC DQ3/HOLD#C DQ0V CC DQ3/RESET#C DQ0Notes: 1.RESET# or HOLD# signals can share Pin 7 with DQ3, depending on the selected device(see Part Numbering Ordering Information). When using single and dual I/O commands on these parts, DQ3 must be driven high by the host, or an external pull-up resistor mustbe placed on the PCB, in order to avoid allowing the HOLD# or RESET# input to float.2.On the underside of the W-PDFN package, there is an exposed central pad that is pulledinternally to V SS . It can be left floating or can be connected to V SS . It must not be con-nected to any other voltage or signal line on the PCB.3.MT25QXXXXXXX8EXX-XXXX not available on 8 pin package512Mb, 1.8V Multiple I/O Serial Flash Memory Signal Assignments – Package Code: SF09005aef864f8d6dmt25q-qlkt-u512-abb-0.pdf - Rev. F 1/18 EN 14Micron Technology, Inc. reserves the right to change products or specifications without notice.© 2013 Micron Technology, Inc. All rights reserved.Table 1: Signal Descriptions (Continued)512Mb, 1.8V Multiple I/O Serial Flash Memory Signal Descriptions09005aef864f8d6dmt25q-qlkt-u512-abb-0.pdf - Rev. F 1/18 EN 16Micron Technology, Inc. reserves the right to change products or specifications without notice.© 2013 Micron Technology, Inc. All rights reserved.Package Dimensions – Package Code: SFFigure 10: 16-Pin SOP2 – 300 mil Body Width0.23 MIN/0.32 MAX 0.40 MIN/1.27 MAXNotes: 1.All dimensions are in millimeters.2.See Part Number Ordering Information for complete package names and details.512Mb, 1.8V Multiple I/O Serial Flash Memory Package Dimensions – Package Code: SF09005aef864f8d6dmt25q-qlkt-u512-abb-0.pdf - Rev. F 1/18 EN 19Micron Technology, Inc. reserves the right to change products or specifications without notice.© 2013 Micron Technology, Inc. All rights reserved.。

技嘉GA-Z270X-Gaming SOC主板使用手册说明书

Dec. 30, 2016Motherboard GA-Z270X-Gaming SOC目录清点配件 (6)选购配件 (6)GA-Z270X-Gaming SOC主板配置图 (7)第一章硬件安装 (9)1-1 安装前的注意事项 (9)1-2 产品规格 (10)1-3 安装中央处理器及散热风扇 (14)1-3-1 安装中央处理器(CPU) (14)1-3-2 安装散热风扇 (16)1-4 安装内存条 (17)1-4-1 双通道内存技术 (17)1-4-2 安装内存条 (18)1-5 安装扩展卡 (19)1-6 构建AMD CrossFire™/NVIDIA® SLI™系统 (20)1-7 后方设备插座介绍 (21)1-8 内建灯号、按钮及切换器 (23)1-9 更换音频放大器 (25)1-10 插座及跳线介绍 (26)第二章 BIOS 程序设置 (41)2-1 开机画面 (42)2-2 BIOS设定程序主画面 (43)2-3 M.I.T. (频率/电压控制) (45)2-4 System (系统信息) (57)2-5 BIOS (BIOS功能设定) (58)2-6 Peripherals (集成外设) (61)2-7 Chipset (芯片组设定) (64)2-8 Power (省电功能设定) (65)2-9 Save & Exit (储存设定值并结束设定程序) (67)第三章构建磁盘阵列 (69)3-1 设定SATA控制器模式 (69)3-2 安装SATA RAID/AHCI驱动程序及操作系统 (83)3-3 启动Intel® Optane™技术 (86)第四章驱动程序安装 (87)4-1 Drivers & Software (驱动程序及应用软件) (87)4-2 Application Software (软件应用程序) (88)4-3 Information (信息清单) (88)- 4 -第五章独特功能介绍 (89)5-1 BIOS更新方法介绍 (89)5-1-1 如何使用Q-Flash更新BIOS (89)5-1-2 如何使用@BIOS更新BIOS (92)5-2 APP Center (93)5-2-1 3D OSD (94)5-2-2 AutoGreen (95)5-2-3 BIOS Setup (96)5-2-4 Color Temperature (97)5-2-5 Cloud Station (98)5-2-6 EasyTune (103)5-2-7 Easy RAID (104)5-2-8 Fast Boot (107)5-2-9 Game Boost (108)5-2-10 Platform Power Management (109)5-2-11 RGB Fusion (110)5-2-12 Smart TimeLock (111)5-2-13 Smart Keyboard (112)5-2-14 Smart Backup (113)5-2-15 System Information Viewer (115)5-2-16 USB Blocker (116)5-2-17 USB DAC-UP 2 (117)5-2-18 V-Tuner (118)第六章附录 (119)6-1 音频输入/输出设定介绍 (119)6-1-1 2 / 4 / 5.1 / 7.1声道介绍 (119)6-1-2 S/PDIF输出设定 (121)6-1-3 麦克风录音设定 (122)6-1-4 语音录音机使用介绍 (124)6-2 疑难排解 (125)6-2-1 问题集 (125)6-2-2 故障排除 (126)6-3 除错灯号代码说明 (128)管理声明 (132)技嘉主板售后服务及质量保证卡 (134)技嘉科技全球服务网 (135)- 5 -清点配件5GA-Z270X-Gaming SOC主板- 1片5驱动程序光盘- 1片5使用手册- 1本5硬件安装指南- 1张5SATA排线- 4条5后方I/O设备挡板铁片- 1个5G Connector- 1个5后方I/O设备防尘盖- 1包5GC-SLI2P连接器- 1个上述附带配件仅供参考,实际配件请以实物为准,技嘉科技保留修改的权利。

2800系列使用手册

UV-2802S

0.5、1、2、4nm

≤0.15%T 在 220nm,340 nm 处 0-200%T,-0.3-2.80A, 0-9999C(0-9999F) ±0.5%T RS-232C 串口,Centronics 并口配 Hp,Epson 兼容激光,喷墨打印机 550×400×270 580×400×280 16kg 约 21kg

23仪器外观uv2800见图21图22样品室盖键盘液晶显示屏拉杆图21散热风扇电源插座打印口液晶对比度调节旋钮电源开关110v220v转换开关rs232串行通uv28022802s见图23图24图25液晶对比度调节旋钮液晶显示屏样品室盖拉杆键盘图23电源指示灯打印口电源开关rs232串行通讯口图24电源插座散热风扇散热孔110v220v转换开关换灯口盖板观察孔图2524仪器安装将仪器放置于水平平台上仪器应避免阳光直射远离电磁发射装置和大功率电气装置使用环境不能有尘埃腐蚀性气体和振动

UV-2800/2802/2802S 型

紫外可见分光光度计 用户使用手册

尤尼柯(上海)仪器有限公司

目 录 第一章 概述………………………………………………………………………………… 1. 1 原理……………………………………………………………………………………… 1. 2 用途……………………………………………………………………………………… 1. 3 特点……………………………………………………………………………………… 第二章 主要技术指标……………………………………………………………………… 2. 1 技术指标………………………………………………………………………………… 2. 2 随机附件………………………………………………………………………………… 2. 3 仪器外观………………………………………………………………………………… 2. 4 仪器安装………………………………………………………………………………… 第三章 仪器的基本操作…………………………………………………………………… 3. 1 显示屏和按键…………………………………………………………………………… 3. 2 仪器上电………………………………………………………………………………… 3. 3 仪器的基本操作………………………………………………………………………… 3. 3. 1 调空白………………………………………………………………………………… 3. 3. 2 设置波长……………………………………………………………………………… 3. 3. 3 调出, 存储, 打印实验结果………………………………………………………… 3. 4 试验前的准备…………………………………………………………………………… 第四章 光度计模式………………………………………………………………………… 4. 1 测试方法描述…………………………………………………………………………… 4. 1. 1 吸光度模式…………………………………………………………………………… 4. 1. 2 透过率模式…………………………………………………………………………… 4. 1. 3 含量 (浓度) 模式……………………………………………………………………… 4. 2 打印实验报告…………………………………………………………………………… 第五章 定量测量…………………………………………………………………………… 5. 1 测量方法描述…………………………………………………………………………… 5. 1. 1 选择浓度单位………………………………………………………………………… 5. 1. 2 选择校正方法………………………………………………………………………… 5. 1. 3 选择曲线拟合方法…………………………………………………………………… 5. 1. 4 直接输入标准曲线…………………………………………………………………… 5. 1. 5 建立标准曲线………………………………………………………………………… 5. 1. 6 定量测量……………………………………………………………………………… 第六章 光谱扫描…………………………………………………………………………… 6. 1 参数设置………………………………………………………………………………… 6. 2 扫描模式选择…………………………………………………………………………… 6. 3 建立基线………………………………………………………………………………… 6. 4 扫描样品………………………………………………………………………………… 6. 5 图谱处理………………………………………………………………………………… 6. 5. 1 改变标尺……………………………………………………………………………… 6. 5. 2 峰谷查寻……………………………………………………………………………… 6. 5. 3 存储, 调入, 打印扫描曲线………………………………………………………… 第七章 动力学测量………………………………………………………………………… 7. 1 参数设置………………………………………………………………………………… 1 1 1 1 2 2 2 3 5 5 5 6 8 8 9 10 12 12 12 13 13 13 15 15 15 15 16 16 16 17 19 21 21 21 22 22 23 23 23 24 26 26

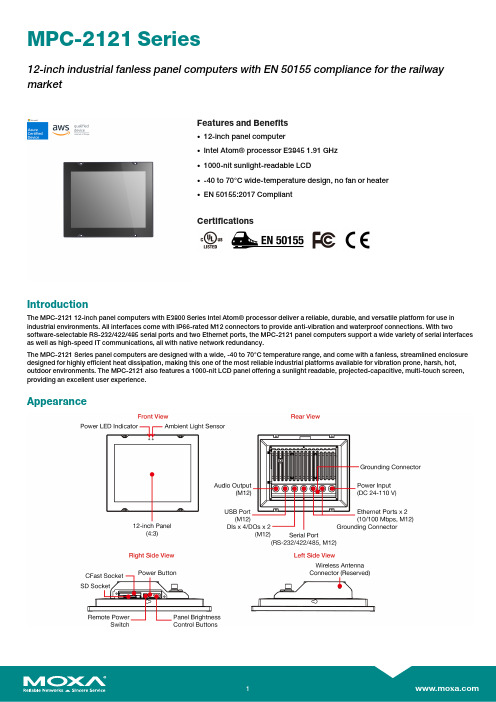

莫加 MPC-2121 系列 12英寸无风扇车辆面板计算机商品介绍说明书

MPC-2121Series12-inch industrial fanless panel computers with EN50155compliance for the railway marketFeatures and Benefits•12-inch panel computer•Intel Atom®processor E38451.91GHz•1000-nit sunlight-readable LCD•-40to70°C wide-temperature design,no fan or heater•EN50155:2017CompliantCertificationsIntroductionThe MPC-212112-inch panel computers with E3800Series Intel Atom®processor deliver a reliable,durable,and versatile platform for use in industrial environments.All interfaces come with IP66-rated M12connectors to provide anti-vibration and waterproof connections.With two software-selectable RS-232/422/485serial ports and two Ethernet ports,the MPC-2121panel computers support a wide variety of serial interfaces as well as high-speed IT communications,all with native network redundancy.The MPC-2121Series panel computers are designed with a wide,-40to70°C temperature range,and come with a fanless,streamlined enclosure designed for highly efficient heat dissipation,making this one of the most reliable industrial platforms available for vibration prone,harsh,hot, outdoor environments.The MPC-2121also features a1000-nit LCD panel offering a sunlight readable,projected-capacitive,multi-touch screen, providing an excellent user experience.AppearanceSpecificationsComputerCPU Intel Atom®Processor E3845(2M Cache,1.91GHz)Graphics Controller Intel®HD GraphicsSystem Memory Pre-installed4(8GB Max.)GB DDR3LSystem Memory Slot SODIMM DDR3/DDR3L slot x1Pre-installed OS MPC-2121-E4-LB-CT-T-W7E/MPC-2101-E4-CT-T-W7E:Windows Embedded Standard7(WS7P)64-bit pre-installedMPC-2121-E4-LB-CT-T-LX/MPC-2121-E4-CT-T-LX:Linux9pre-installedSupported OS Windows10Pro64-bitWindows10Embedded IoT Ent2019LTSC64-bitWindows10Embedded IoT Ent2016LTSBWindows7Pro for Embedded SystemsWindows Embedded Standard7(WS7P)64-bitLinux Debian9Expansion Slots Mini PCIeStorage Slot CFast slot x1SD slots x1,SD3.0(SDHC/SDXC)socketStorage Pre-installed MPC-2121-E4-LB-CT-T-W7E/MPC-2121-E4-CT-T-W7E:32GB CFast CardMPC-2121-E4-LB-CT-T-LX/MPC-2121-E4-CT-T-LX:32GB CFast CardComputer InterfaceEthernet Ports Auto-sensing10/100Mbps ports(M12D-coded4P)x2Serial Ports RS-232/422/485ports x1(M12A-code12P)USB2.0USB2.0hosts x1(M12A-coded5P)Digital Input DIs x4(M12A-code)Digital Output DOs x2(M12A-code)LED IndicatorsSystem Power x1DisplayActive Display Area245.76(H)x184.32(V)mmAspect Ratio4:3Contrast Ratio1000:1Light Intensity(Brightness)500/1000cd/m2Max.No.of Colors16.2M(8-bit/color)Panel Size12-inch viewable imagePixel Pitch(RGB)0.240(H)x0.240(V)mmPixels1024x768Response Time5ms(gray to gray)Viewing Angles176°/176°Touch FunctionTouch Type Capacitive Touch(PCAP)Touch Support Points4pointsGlove Support YesSerial InterfaceBaudrate50bps to115.2kbpsData Bits5,6,7,8Flow Control RTS/CTS,XON/XOFFParity None,Even,Odd,Space,MarkStop Bits1,1.5,2Serial SignalsRS-232TxD,RxD,RTS,CTS,DTR,DSR,DCD,GND RS-422Tx+,Tx-,Rx+,Rx-,GNDRS-485-2w Data+,Data-,GNDRS-485-4w Tx+,Tx-,Rx+,Rx-,GNDPower ParametersInput Voltage24to110VDCPhysical CharacteristicsHousing MetalIP Rating IP66Dimensions297x238x59mm(11.69x9.37x2.32in) Weight2850g(6.28lb)Environmental LimitsOperating Temperature-40to70°C(-40to158°F)Storage Temperature(package included)-40to70°C(-40to158°F)Ambient Relative Humidity5to95%(non-condensing)Standards and CertificationsEMI CISPR32,FCC Part15B Class AEMS IEC61000-4-2ESD:Contact:6kV;Air:8kVIEC61000-4-3RS:80MHz to1GHz:20V/mIEC61000-4-4EFT:Power:2kV;Signal:2kVIEC61000-4-5Surge:Power:2kV;Signal:1kVIEC61000-4-6CS:10VIEC61000-4-8PFMFMechanical Protection Rating IEC60529,IP codeShock EN50155standardVibration EN50155standardEMC EN55032/35Safety IEC60950-1,IEC62368-1,UL62368-1 DeclarationGreen Product RoHS,CRoHS,WEEEWarrantyWarranty Period LCD:1yearSystem:3yearsDetails See /warrantyPackage ContentsDevice1x MPC-2121Series computerInstallation Kit6x screw,for panel-mounting1x M12-Phone jack power cable1x M12-Type A USB cable1x terminal block,2-pin(for remote power input) Documentation1x quick installation guide1x warranty cardDimensionsOrdering Information2.0MPC-2121-E4-LB-CT-T-W7E 12"(4:3)500nitsE3845Quadcore4GBW7E(64-bit)2(M12)1(M12)1(M12)4/2(M12)24to110VDCIP66-40to70°CMPC-2121-E4-CT-T-W7E12"(4:3)1,000nitsE3845Quadcore4GBW7E(64-bit)2(M12)1(M12)1(M12)4/2(M12)24to110VDCIP66-40to70°CMPC-2121-E4-LB-CT-T-LX 12"(4:3)500nitsE3845Quadcore4GB Debian92(M12)1(M12)1(M12)4/2(M12)24to110VDCIP66-40to70°CMPC-2121-E4-CT-T-LX12"(4:3)1,000nitsE3845Quadcore4GB Debian92(M12)1(M12)1(M12)4/2(M12)24to110VDCIP66-40to70°CMPC-2121-E4-LB-CT-T 12"(4:3)500nitsE3845Quadcore4GB–2(M12)1(M12)1(M12)4/2(M12)24to110VDCIP66-40to70°CMPC-2121-E4-CT-T12"(4:3)1,000nitsE3845Quadcore4GB–2(M12)1(M12)1(M12)4/2(M12)24to110VDCIP66-40to70°C©Moxa Inc.All rights reserved.Updated Jun28,2021.This document and any portion thereof may not be reproduced or used in any manner whatsoever without the express written permission of Moxa Inc.Product specifications subject to change without notice.Visit our website for the most up-to-date product information.。

EJ闪烁体

荧光片和双闪烁体

EJ-440 ....................................................................... 36 EJ-442 ....................................................................... 37 EJ-444 ....................................................................... 38

掺杂闪烁体

EJ-254 ....................................................................... 30 EJ-256 ....................................................................... 32 EJ-331 & EJ-335....................................................... 33 EJ-339 & EJ-339A.................................................... 34 EJ-351 ....................................................................... 35

液体闪烁体

EJ-301....................................................................... 16 EJ-305....................................................................... 17 EJ-309....................................................................... 18 EJ-313....................................................................... 19 EJ-315....................................................................... 20 EJ-321....................................................................... 21 EJ-399-04 ................................................................. 22 EJ-399-08 ................................................................. 23 EJ-399-05D1............................................................. 24 EJ-399-05D2............................................................. 25

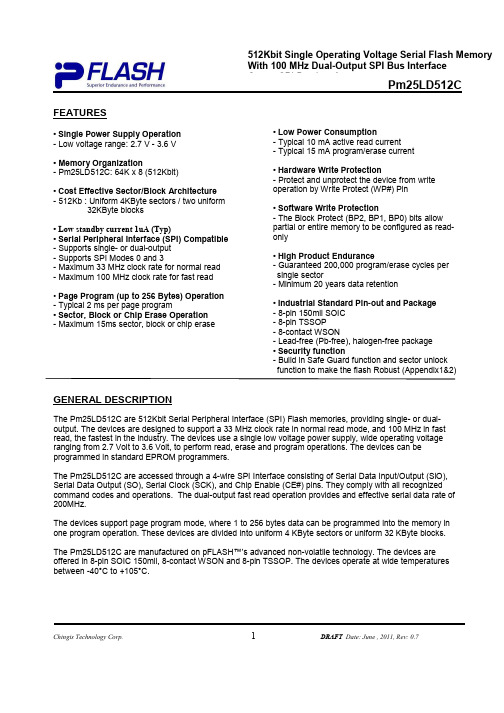

Pm25LD512C datasheet v0.7

Pm25LD512CChingis Technology Corp.1DRAFT Date: June , 2011, Rev: 0.7FEATURES• Single Power Supply Operation - Low voltage range: 2.7 V - 3.6 V• Memory Organization- Pm25LD512C: 64K x 8 (512Kbit)• Cost Effective Sector/Block Architecture - 512Kb : Uniform 4KByte sectors / two uniform32KByte blocks• Low standby current 1uA (Typ)• Serial Peripheral Interface (SPI) Compatible - Supports single- or dual-output - Supports SPI Modes 0 and 3- Maximum 33 MHz clock rate for normal read - Maximum 100 MHz clock rate for fast read• Page Program (up to 256 Bytes) Operation - Typical 2 ms per page program• Sector, Block or Chip Erase Operation - Maximum 15ms sector, block or chip erase• Low Power Consumption- Typical 10 mA active read current - Typical 15 mA program/erase current• Hardware Write Protection- Protect and unprotect the device from write operation by Write Protect (WP#) Pin• Software Write Protection- The Block Protect (BP2, BP1, BP0) bits allow partial or entire memory to be configured as read-only• High Product Endurance- Guaranteed 200,000 program/erase cycles per single sector- Minimum 20 years data retention• Industrial Standard Pin-out and Package - 8-pin 150mil SOIC - 8-pin TSSOP - 8-contact WSON- Lead-free (Pb-free), halogen-free package • Security function- Build in Safe Guard function and sector unlock function to make the flash Robust (Appendix1&2)GENERAL DESCRIPTIONThe Pm25LD512C are 512Kbit Serial Peripheral Interface (SPI) Flash memories, providing single- or dual-output. The devices are designed to support a 33 MHz clock rate in normal read mode, and 100 MHz in fast read, the fastest in the industry. The devices use a single low voltage power supply, wide operating voltage ranging from 2.7 Volt to 3.6 Volt, to perform read, erase and program operations. The devices can be programmed in standard EPROM programmers.The Pm25LD512C are accessed through a 4-wire SPI Interface consisting of Serial Data Input/Output (SlO), Serial Data Output (SO), Serial Clock (SCK), and Chip Enable (CE#) pins. They comply with all recognized command codes and operations. The dual-output fast read operation provides and effective serial data rate of 200MHz.The devices support page program mode, where 1 to 256 bytes data can be programmed into the memory in one program operation. These devices are divided into uniform 4 KByte sectors or uniform 32 KByte blocks.The Pm25LD512C are manufactured on pFLASH™’s advanced non-volatile technology. The devices are offered in 8-pin SOIC 150mil, 8-contact WSON and 8-pin TSSOP. The devices operate at wide temperatures between -40°C to +105°C.512Kbit Single Operating Voltage Serial Flash Memory With 100 MHz Dual-Output SPI Bus Interface Output SPI Bus InterfacePm25LD512CChingis Technology Corp.2Date: April, 2011, Rev: 0.6PRODUCT ORDERING INFORMATIONPacking Type R = Tape & Reel Blank = TubeEnvironmental AttributeE = Lead-free (Pb-free) and Halogen- free packageTemperature RangeC = Commercial Grade (-40°C to +105°C)Package TypeS = 8-pin SOIC 150mil (8S) K = 8-contact WSON (8K) D = 8-pin TSSOP (8D)pFlash Device Number Pm25LD512CPart Number Operating Frequency (MHz) PackageTemperature RangePm25LD512C-SCE 1008S150mil SOICPm25LD512C-KCE 1008K WSON (Back Side Metal) Pm25LD512C-DCE1008D TSSOPCommercial Grade (-40o C to +105o C)Pm25LD512CChingis Technology Corp.3Date: April, 2011, Rev: 0.6CONNECTION DIAGRAMSHOLD#SCK SISO GNDWP#CE#PIN DESCRIPTIONSSYMBOL TYPE DESCRIPTIONCE#INPUT Chip Enable: CE# low activates the devices internal circuitries for device operation. CE# high deselects the devices and switches intostandby mode to reduce the power consumption. When a device is not selected, data will not be accepted via the serial input pin (Sl), and the serial output pin (SO) will remain in a high impedance state.SCK INPUT Serial Data ClockSIO INPUT/OUTPUT Serial Data Input/Output SO OUTPUTSerial Data Output GND Ground Vcc Device Power Supply WP#INPUT Write Protect: A hardware program/erase protection for all or part of amemory array. When the WP# pin is low, memory array write-protection depends on the setting of BP2, BP1 and BP0 bits in the Status Register. When the WP# is high, the devices are not write-protected.HOLD#INPUT Hold: Pause serial communication by the master device without resettingthe serial sequence.CE# SOHOLD#SCKSIOSIOVcc 8-Pin SOIC8-Contact WSON8-Pin TSSOPPm25LD512CChingis Technology Corp.4Date: April, 2011, Rev: 0.6BLOCK DIAGRAMSIOPm25LD512CChingis Technology Corp.5Date: April, 2011, Rev: 0.6SPI MODES DESCRIPTIONMultiple Pm25LD512C devices can be connected on the SPI serial bus and controlled by a SPI Master, i.e. microcontroller, as shown in Figure 1. The devices support either of two SPI modes:Mode 0 (0, 0) Mode 3 (1, 1)The difference between these two modes is the clock polarity when the SPI master is in Stand-by mode: the serial clock remains at “0” (SCK = 0) for Mode 0 and the clock remains at “1” (SCK = 1) for Mode 3. Please refer to Figure 2. For both modes, the input data is latched on the rising edge of Serial Clock (SCK), and the output data is available from the falling edge of SCK.Figure 1. Connection Diagram among SPI Master and SPI Slaves (Memory Devices)Figure 2. SPI Modes SupportedMSbMSbSCKSCKSOSIOInput mode Mode 0 (0, 0) Mode 3 (1, 1)Pm25LD512CChingis Technology Corp.6Date: April, 2011, Rev: 0.6SYSTEM CONFIGURATIONThe Pm25LD512C devices are designed to interface directly with the synchronous Serial Peripheral Interface (SPI) of the Motorola MC68HCxx series of microcontrollers or any SPI interface-equipped system controllers. The devices have two superset features that can be enabled through specific software instructions and the Configuration Register:Table 1. Block/Sector Addresses of Pm25LD512CMemory Density Block No. Block Size (KBytes) Sector No. SectorSize (KBytes)Address RangeSector 0 4 000000h - 000FFFh Sector 1 4 001000h - 001FFFh: : :Block 0 32 Sector 7 4 007000h - 007FFFh Sector 8 4 008000h - 008FFFh Sector 17 4 009000h - 009FFFh : : :512KbitBlock 1 32Sector 15 4 00F000h - 00FFFFhPm25LD512CChingis Technology Corp.7Date: April, 2011, Rev: 0.6REGISTERS (CONTINUED)STATUS REGISTERRefer to Tables 5 and 6 for Status Register Format and Status Register Bit Definitions.The BP0, BP1, BP2, and SRWD are non-volatile memory cells that can be written by a Write Status Register (WRSR) instruction. The default value of the BP2, BP1, BP0 were set to “0” and SRWD bits was set to “0” at factory. Once a “0” or “1”is written, it will not be changed by device power-up or power-down, and can only be altered by the next WRSR instruction. The Status Register can be read by the Read StatusRegister (RDSR). Refer to Table 10 for Instruction Set.The function of Status Register bits are described as follows:WIP bit : The Write In Progress (WIP) bit is read-only, and can be used to detect the progress or completion of a program or erase operation. When the WIP bit is “0”, the device is ready for a write status register, program or erase operation. When the WIP bit is “1”, the device is busy.WEL bit : The Write Enable Latch (WEL) bit indicates the status of the internal write enable latch. When the WEL is “0”, the write enable latch is disabled, and all write operations, including write status register, page program, sector erase, block and chip erase operations are inhibited. When the WEL bit is “1”, write operations are allowed. The WEL bit is set by a Write Enable (WREN) instruction. Each write register, program and erase instruction must be preceded by a WREN instruction. The WEL bit can be reset by a WriteDisable (WRDI) instruction. It will automatically be the reset after the completion of a write instruction.BP2, BP1, BP0 bits : The Block Protection (BP2, BP1, BP0) bits are used to define the portion of the memory area to be protected. Refer to Tables 7, 8 and 9 for the Block Write Protection bit settings. When a defined combination of BP2, BP1 and BP0 bits are set, the corresponding memory area is protected. Any program or erase operation to that area will be inhibited. Note: a Chip Erase (CHIP_ER) instruction is executedsuccessfully only if all the Block Protection Bits are set as “0”s.SRWD bit : The Status Register Write Disable (SRWD) bit operates in conjunction with the Write Protection (WP#) signal to provide a Hardware Protection Mode. When the SRWD is set to “0”, the Status Register is not write-protected. When the SRWD is set to “1” and the WP# is pulled low (V IL ), the volatile bits of Status Register (SRWD, BP2, BP1, BP0) become read-only, and a WRSR instruction will be ignored. If the SRWD is set to “1” and WP# is pulled high (V IH ), the Status Register can be changed by a WRSR instruction.Table 5. Status Register FormatBit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 SRWD1ReservedBP2BP1 BP0 WEL WIP Default (flash bit) 0 0Pm25LD512CChingis Technology Corp.8Date: April, 2011, Rev: 0.6REGISTERS (CONTINUED)Table 6. Status Register Bit Definition BitNameDefinitionRead- /Write Non-Volatile bit Bit 0 WIP Write In Progress Bit:"0" indicates the device is ready"1" indicates a write cycle is in progress and the device is busy R No Bit 1 WEL Write Enable Latch:"0" indicates the device is not write enabled (default)"1" indicates the device is write enabledR/W No Bit 2 BP0 Bit 3 BP1 Bit 4 BP2 Block Protection Bit: (See Table 7 and Table 8 for details) "0" indicates the specific blocks are not write-protected (default) "1" indicates the specific blocks are write-protected R/W Yes Bits 5 - 6 N/A Reserved: Always "0"sN/A Bit 7 SRWD Status Register Write Disable: (See Table 9 for details)"0" indicates the Status Register is not write-protected (default)"1" indicates the Status Register is write-protectedR/WYesTable 8. Block Write Protect Bits for Pm25LD512CStatus Register Bits Protected Memory AreaBP2 BP1 BP0 512Kbit Not used 0 0 None Not used 0 1 None Not used 1 0 NoneNot used 11All blocks: 000000h - 00FFFFhPm25LD512CChingis Technology Corp.9Date: April, 2011, Rev: 0.6REGISTERS (CONTINUED)PROTECTION MODEThe Pm25LD512C have two types of write-protection mechanisms: hardware and software. These are used to prevent irrelevant operation in a possibly noisy environment and protect the data integrity.HARDWARE WRITE-PROTECTIONThe devices provide two hardware write-protection features:a. When inputting a program, erase or write status register instruction, the number of clock pulse ischecked to determine whether it is a multiple of eight before the executing. Any incomplete instruction command sequence will be ignored.b. The Write Protection (WP#) pin provides ahardware write protection method for BP2, BP1, BP0 and SRWD in the Status Register. Refer to the STATUS REGISTER description.c. Write inhibit is 2.1V, all write sequence will beignored when Vcc drop to 2.1V and lowerSOFTWARE WRITE PROTECTIONThe Pm25LD512C also provides two software write protection features:a. Before the execution of any program, erase or write status register instruction, the Write Enable Latch (WEL) bit must be enabled by executing a Write Enable (WREN) instruction. If the WEL bit is not enabled first, the program, erase or write register instruction will be ignored.b. The Block Protection (BP2, BP1, BP0) bits allow part or the whole memory area to be write-protected. Table 9. Hardware Write Protection on Status RegisterSRWD WP#Status Register 0Low Writable 1 Low Protected 0 High Writable 1HighWritablePm25LD512CChingis Technology Corp.10Date: April, 2011, Rev: 0.6DEVICE OPERATIONThe Pm25LD512C utilize an 8-bit instruction register. Refer to Table 10 Instruction Set for details of theInstructions and Instruction Codes. All instructions,addresses, and data are shifted in with the mostsignificant bit (MSB) first on Serial Data Input (SI). The input data on SI is latched on the rising edge of Serial Clock (SCK) after Chip Enable (CE#) is driven low (V IL ). Every instruction sequence starts with a one-byte instruction code and is followed by address bytes, databytes, or both address bytes and data bytes, depending on the type of instruction. CE# must be driven high (V IH ) after the last bit of the instruction sequence has been shifted in.The timing for each instruction is illustrated in the following operational descriptions.Table 10. Instruction SetInstruction NameHexCodeOperationCommand Cycle Maximum FrequencyRDIDABh Read Manufacturer and Product ID4 Bytes 100 MHz JEDEC ID READ 9Fh Read Manufacturer and Product ID by JEDEC ID Command1 Byte 100 MHz RDMDID 90h Read Manufacturer and Device ID 4 Bytes 100 MHz WREN 06h Write Enable 1 Byte 100 MHz WRDI 04h Write Disable1 Byte 100 MHz RDSR 05h Read Status Register 1 Byte 100 MHz WRSR 01h Write Status Register2 Bytes 100 MHz READ03h Read Data Bytes from Memory at Normal Read Mode 4 Bytes 33 MHz FAST_READ 0Bh Read Data Bytes from Memory at Fast Read Mode 5 Bytes 100 MHz FRDO3Bh Fast Read Dual Output5 Bytes 100 MHz PAGE_ PROG 02h Page Program Data Bytes Into Memory 4 Bytes + 256B 100 MHz SECTOR_ER D7h/20h Sector Erase 4 Bytes 100 MHz BLOCK_ER D8h Block Erase 4 Bytes 100 MHz CHIP_ERC7h/60hChip Erase1 Byte100 MHzHOLD OPERATIONHOLD# is used in conjunction with CE# to select the Pm25LD512C. When the devices are selected and a serial sequence is underway, HOLD# can be used to pause the serial communication with the master device without resetting the serial sequence.To pause, HOLD# is brought low while the SCK signal is low. To resume serial communication, HOLD# is brought high while the SCK signal is low (SCK may still toggle during HOLD). Inputs to Sl will be ignored while SO is in the high impedance state.Pm25LD512CChingis Technology Corp.11Date: April, 2011, Rev: 0.6DEVICE OPERATION (CONTINUED)RDID COMMAND (READ PRODUCT IDENTIFICATION) OPERATIONThe Read Product Identification (RDID) instruction is for reading out the old style of 8-bit Electronic Signature, whose values are shown as table of ID Definitions. This is not same as RDID or JEDEC ID instruction. It’s not recommended to use for newdesign. For new design, please use RDID or JEDEC ID instruction.The RDES instruction code is followed by three dummy bytes, each bit being latched-in on SI during the rising edge of SCK. Then the Device ID is shifted out on SO with the MSB first, each bit been shifted out during the falling edge of SCK. The RDES instruction is ended byCE# goes high. The Device ID outputs repeatedly if continuously send the additional clock cycles on SCK while CE# is at low.Table 11. Product IdentificationProduct Identification Data First Byte 9DhManufacturer ID Second Byte7Fh Device ID: Device ID 1 Device ID 2Pm25LD512C 05h 20hFigure 3. Read Product Identification SequenceSCKCE#SI SOPm25LD512CChingis Technology Corp.12Date: April, 2011, Rev: 0.6DEVICE OPERATION (CONTINUED)JEDEC ID READ COMMAND (READ PRODUCT IDENTIFICATION BY JEDEC ID) OPERATIONThe JEDEC ID READ instruction allows the user to read the manufacturer and product ID of devices. Refer to Table 11 Product Identification for pFlash Manufacturer ID and Device ID. After the JEDEC ID READ command is input, the second Manufacturer ID (7Fh) is shifted out on SO with the MSB first, followed by the first Manufacturer ID (9Dh) and the Device ID (20h), each bit shifted out during the falling edge of SCK. If CE# stays low after the last bit of the Device ID is shifted out, the Manufacturer ID and Device ID will loop until CE# is pulled high.Figure 4. Read Product Identification by JEDEC ID READ SequenceSCKCE#SISOPm25LD512CChingis Technology Corp.13Date: April, 2011, Rev: 0.6DEVICE OPERATION (CONTINUED)RDMDID COMMAND (READ DEVICE MANUFACTURER AND DEVICE ID) OPERATIONThe RDMDID instruction allows the user to read the manufacturer and product ID of devices. Refer to Table 11 Product Identification for pFlash Manufacturer ID and Device ID. The RDMDID command is input, followed by a 24-bit address pointing to an ID table. The table contains the first Manufacturer ID (9Dh) andthe Device ID (20h), and is shifted out on SO with the MSB first, each bit shifted out during the falling edge of SCK. If CE# stays low after the last bit of the Device ID is shifted out, the Manufacturer ID and Device ID will loop until CE# is pulled high.Figure 5. Read Product Identification by RDMDID READ SequencePm25LD512CChingis Technology Corp. 14 Date: April, 2011, Rev: 0.6Pm25LD512CChingis Technology Corp.15Date: April, 2011, Rev: 0.6DEVICE OPERATION (CONTINUED)WRITE ENABLE OPERATIONThe Write Enable (WREN) instruction is used to set the Write Enable Latch (WEL) bit. The WEL bit of the Pm25LD512C is reset to the write –protected state after power-up. The WEL bit must be write enabled before any write operation, including sector, block erase, chip erase, page program and write status register operations. The WEL bit will be reset to the write-protect state automatically upon completion of a write operation. The WREN instruction is required before any above operation is executed.Figure 6. Write Enable SequenceWRDI COMMAND (WRITE DISABLE) OPERATIONThe Write Disable (WRDI) instruction resets the WEL bit and disables all write instructions. The WRDI instruction is not required after the execution of a write instruction, since the WEL bit is automatically reset.Figure 7. Write Disable SequenceSIOSIOPm25LD512CChingis Technology Corp.Date: April, 2011, Rev: 0.6DEVICE OPERATION (CONTINUED)RDSR COMMAND (READ STATUS REGISTER) OPERATIONThe Read Status Register (RDSR) instruction provides access to the Status Register. During the execution of a program, erase or write status register operation, all other instructions will be ignored except the RDSR instruction, which can be used to check the progress or completion of an operation by reading the WIP bit of Status Register.Figure 8. Read Status Register SequenceWRSR COMMAND (WRITE STATUS REGISTER) OPERATIONThe Write Status Register (WRSR) instruction allows the user to enable or disable the block protection and status register write protection features by writing “0”s or “1” s into the volatile BP2, BP1, BP0 and SRWD bits.Figure 9. Write Status Register SequenceDEVICE OPERATION (CONTINUED)SIOSIOPm25LD512CChingis Technology Corp.17Date: April, 2011, Rev: 0.6READ COMMAND (READ DATA) OPERATIONThe Read Data (READ) instruction is used to read memory data of a Pm25LD512C under normal mode running up to 33 MHz.The READ instruction code is transmitted via the Sl line, followed by three address bytes (A23 - A0) of the first memory location to be read. A total of 24 address bits are shifted in, but only A MS (most significantaddress) - A0 are decoded. The remaining bits (A23 – A MS ) are ignored. The first byte addressed can be at any memory location. Upon completion, any data on the Sl will be ignored. Refer to Table 12 for the related Address Key.The first byte data (D7 - D0) addressed is then shifted out on the SO line, MSb first. A single byte of data, or up to the whole memory array, can be read out in one READ instruction. The address is automaticallyincremented after each byte of data is shifted out. The read operation can be terminated at any time by driving CE# high (V IH ) after the data comes out. When the highest address of the devices is reached, the address counter will roll over to the 000000h address, allowing the entire memory to be read in one continuous READ instruction.Table 12. Address KeyAddress Pm25LD512CA N (A MS – A 0) A15 - A0 Don't Care BitsA23 – A16Figure 12. Read Data SequenceSIOPm25LD512CChingis Technology Corp.18Date: April, 2011, Rev: 0.6DEVICE OPERATION (CONTINUED)FAST_READ COMMAND (FAST READ DATA) OPERATIONThe FAST_READ instruction is used to read memory data at up to a 100 MHz clock. The FAST_READ instruction code is followed by three address bytes (A23 - A0) and a dummy byte (8 clocks), transmitted via the SI line, with each bit latched-in during the rising edge of SCK. Then the first data byte addressed is shifted out on the SO line, with each bit shifted out at a maximum frequency f CT , during the falling edge of SCK. The first byte addressed can be at any memory location. The address is automatically incremented after each byte of data is shifted out. When the highest address is reached, the address counter will roll over to the 000000h address, allowing the entire memory to be read with a single FAST_READ instruction. The FAST_READ instruction is terminated by driving CE# high (V IH ).Figure 13. Fast Read Data SequenceSIOSIOPm25LD512CChingis Technology Corp.19Date: April, 2011, Rev: 0.6DEVICE OPERATION (CONTINUED)FRDO COMMAND (FAST READ DUAL OUTPUT) OPERATIONThe FRDO instruction is used to read memory data on two output pins each at up to a 100 MHz clock. The FRDO instruction code is followed by threeaddress bytes (A23 - A0) and a dummy byte (8 clocks), transmitted via the SI line, with each bit latched-in during the rising edge of SCK. Then the first data byte addressed is shifted out on the SO and SIO lines, with each pair of bits shifted out at a maximum frequency f CT , during the falling edge of SCK. The first bit (MSb) is output on SO, while simultaneously the second bit is output on SIO.The first byte addressed can be at any memory location. The address is automatically incremented after each byte of data is shifted out. When the highest address is reached, the address counter will roll over to the 000000h address, allowing the entire memory to be read with a single FRDO instruction. FRDO instruction is terminated by driving CE# high (V IH).Figure 14. Fast Read Dual-Output Sequence123456789101128293031...INSTRUCTION = 0011 1011b (23)22213213 - BYTE ADDRESSCE#SCKSIOSO HIGH IMPEDANCE3233343536373839404142434445464748765432107654321076CE#SCKSIOSOHIGH IMPEDANCEDATA OUT 1DATA OUT 2Pm25LD512CChingis Technology Corp.20Date: April, 2011, Rev: 0.6DEVICE OPERATION (CONTINUED)PAGE_PROG COMMAND (PAGE PROGRAM) OPERATIONThe Page Program (PAGE_PROG) instruction allows up to 256 bytes data to be programmed into memory in a single operation. The destination of the memory to be programmed must be outside the protected memoryarea set by the Block Protection (BP2, BP1, BP0) bits. A PAGE_PROG instruction which attempts to program into a page that is write-protected will be ignored.Before the execution of PAGE_PROG instruction, the Write Enable Latch (WEL) must be enabled through a Write Enable (WREN) instruction.The PAGE_PROG instruction code, three addressbytes and program data (1 to 256 bytes) are input via the Sl line. Program operation will start immediately after the CE# is brought high, otherwise thePAGE_PROG instruction will not be executed. Theinternal control logic automatically handles the programming voltages and timing. During a program operation, all instructions will be ignored except the RDSR instruction. The progress or completion of theprogram operation can be determined by reading the WIP bit in Status Register via a RDSR instruction. If the WIP bit is “1”, the program operation is still in progress. If WIP bit is “0”, the program operation hascompleted.If more than 256 bytes data are sent to a device, theaddress counter rolls over within the same page, the previously latched data are discarded, and the last 256 bytes data are kept to be programmed into the page. The starting byte can be anywhere within the page.When the end of the page is reached, the address will wrap around to the beginning of the same page. If the data to be programmed are less than a full page, the data of all other bytes on the same page will remainunchanged. Note: A program operation can alter “1”s into “0”s, but an erase operation is required to change “0”s back to “1”s. A byte cannot be reprogrammed without firsterasing the whole sector or block.Figure 15. Page Program SequenceSIOPm25LD512CChingis Technology Corp.21Date: April, 2011, Rev: 0.6DEVICE OPERATION (CONTINUED)ERASE OPERATIONThe memory array of the Pm25LD512C is organized into uniform 4 KByte sectors or 32KByte uniform blocks (a block consists of sixteen adjacent sectors).Before a byte can be reprogrammed, the sector or block that contains the byte must be erased (erasing sets bits to “1”). In order to erase the devices, there are three erase instructions available: Sector Erase(SECTOR_ER), Block Erase (BLOCK_ER) and Chip Erase (CHIP_ER). A sector erase operation allows any individual sector to be erased without affecting the data in other sectors. A block erase operation erases any individual block. A chip erase operation erases the whole memory array of a device. A sector erase, block erase or chip erase operation can be executed prior to any programming operation.SECTOR_ER COMMAND (SECTOR ERASE) OPERATIONA SECTOR_ER instruction erases a 4 KByte sector Before the execution of a SECTOR_ER instruction, the Write Enable Latch (WEL) must be set via a Write Enable (WREN) instruction. The WEL bit is reset automatically after the completion of sector an erase operation.A SECTOR_ER instruction is entered, after CE# ispulled low to select the device and stays low during the entire instruction sequence The SECTOR_ERinstruction code, and three address bytes are input via SI. Erase operation will start immediately after CE# is pulled high. The internal control logic automatically handles the erase voltage and timing. Refer to Figure 14 for Sector Erase Sequence.During an erase operation, all instruction will be ignored except the Read Status Register (RDSR) instruction. The progress or completion of the eraseoperation can be determined by reading the WIP bit in the Status Register using a RDSR instruction. If the WIP bit is “1”, the erase operation is still in progress. If the WIP bit is “0”, the erase operation has been completed.BLOCK_ER COMMAND (BLOCK ERASE) OPERATIONA Block Erase (BLOCK_ER) instruction erases a 32 KByte block of the Pm25LD512C. Before the execution of a BLOCK_ER instruction, the Write Enable Latch (WEL) must be set via a Write Enable (WREN)instruction. The WEL is reset automatically after the completion of a block erase operation.The BLOCK_ER instruction code and three address bytes are input via SI. Erase operation will startimmediately after the CE# is pulled high, otherwise the BLOCK_ER instruction will not be executed. The internal control logic automatically handles the erase voltage and timing. Refer to Figure 15 for Block Erase Sequence.CHIP_ER COMMAND (CHIP ERASE) OPERATIONA Chip Erase (CHIP_ER) instruction erases the entire memory array of a Pm25LD512C. Before the execution of CHIP_ER instruction, the Write Enable Latch (WEL) must be set via a Write Enable (WREN) instruction. The WEL is reset automatically after completion of a chip erase operation.The CHIP_ER instruction code is input via the SI. Erase operation will start immediately after CE# ispulled high, otherwise the CHIP_ER instruction will not be executed. The internal control logic automatically handles the erase voltage and timing. Refer to Figure 16 for Chip Erase Sequence.。

MEMORY存储芯片N25Q512A13GSF40中文规格书