康华光数电第五版PPT课件

康华光数电第五版PPT课件

3.6.1 各种门电路之间的接口问题

在数字电路或系统的设计中,往往将TTL和CMOS两种器件

混合使用,以满足工作速度或者功耗指标的要求。由于每种 器件的电压和电流参数各不相同,因而在这两种器件连接时

,要满足驱动器件和负载器件以下两个条件:

1) 驱动器件的输出电压必须处在负载器件所要求的输入电压范

围,包括高、低电压值(属于电压兼容性的问题)。

A B A B & ≥1 & L

A B A B

& ≥1 & L

A B A B

& & & L

A B

&

L = A B

逻辑门等效符号强调低电平有效

D0 D1 D2 D3 D4 D5 D6 D7

AL

IC

Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7

EN

AL RE = L

L=0

AL = 0 RE = 1

2. 正负逻辑等效变换

某电路输入与输出电平表 A L L H H B L H L H L H H H L

A 0 0 1 1

B 0 1 0 1

采用负逻辑

___或非门

L

0 0 0

A

1 1 0

B

1 0 1

正逻辑 负逻辑 与非 或非 与 或 非 非

0

0

1

3.5.2 基本逻辑门电路的等效符号及其应用

(4)采用推拉式输出级以提高开关速度和带负载能力 a)带负载能力

当O=0.2V时 当输出为低电平时,T4截止, T3饱和导通,其饱和电流全 部用来驱动负载

当O=3.6V时 T3截止,T4组成的电压跟随 器的输出电阻很小,输出高 电平稳定,带负载能力也较 强。 b)输出级对提高开关速度的作用 输出端接负载电容CL时, O由低到高电平跳变的瞬间, CL充电,其时间常数很小使 输出波形上升沿陡直。而当 O由高变低后, CL很快放电, 输出波形的下降沿也很好。

康华光《数字电子技术》第五版 课件 第03章 逻辑门电路01

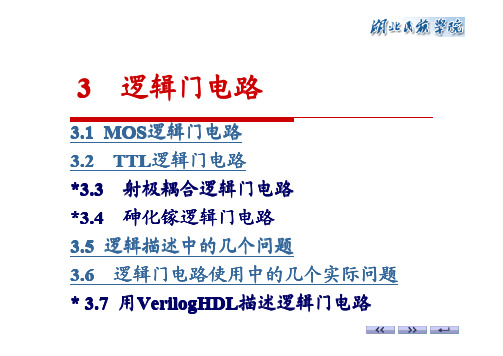

逻辑门电路3 逻辑门电路3.1 MOS逻辑门电路3.2TTL逻辑门电路*3.3 射极耦合逻辑门电路射极耦合逻辑门电路*3.4 砷化镓逻辑门电路砷化镓逻辑门电路3.5逻辑描述中的几个问题逻辑门电路使用中的几个实际问题3.6 逻辑门电路使用中的几个实际问题*3.7用VerilogHDL描述逻辑门电路3.逻辑门电路教学基本要求:1、了解半导体器件的开关特性。

2、熟练掌握基本逻辑门(与、或、与非、或非、异或门)、三态门、OD门(OC门)和传输门的逻辑功能。

3、学会门电路逻辑功能分析方法。

4、掌握逻辑门的主要参数及在应用中的接口问题。

3.1 MOS逻辑门数字集成电路简介3.1.1 数字集成电路简介3.1.2 逻辑门的一般特性逻辑门的一般特性及其等效电路3.1.3MOS开关开关及其等效电路3.1.4CMOS反相器3.1.5CMOS逻辑门电路门电路3.1.6CMOS漏极开路门和三态输出漏极开路门和三态输出门电路3.1.7CMOS传输门3.1.8CMOS逻辑门电路的技术参数1 、逻辑门逻辑门::实现基本逻辑运算和复合逻辑运算的单元电路。

2、 逻辑门电路的分类二极管门电路三极管门电路TTL 门电路MOS 门电路PMOS 门CMOS 门逻辑门电路分立门电路集成门电路NMOS 门3.1.1 数字集成电路简介数字集成电路简介1.CMOS 集成电路集成电路::广泛应用于超大规模、甚大规模集成电路4000系列74HC 74HCT 74VHC 74VHCT 速度慢与TTL 不兼容抗干扰功耗低74LVC 74VAUC 速度加快与TTL 兼容负载能力强抗干扰功耗低速度两倍于74HC 与TTL 兼容负载能力强抗干扰功耗低低(超低超低))电压速度更加快与TTL 兼容负载能力强抗干扰功耗低74系列74LS 系列74AS 系列74ALS2.TTL 集成电路集成电路::广泛应用于中大规模集成电路3.1.1 数字集成电路简介3.1.2 逻辑门电路的一般特性1. 1. 输入和输出的高、低电平输入和输出的高、低电平 v O v I 驱动门G 1负载门G 2 11输出高电平的下限值 V OH(min OH(min))输入低电平的上限值输入低电平的上限值V IL(max IL(max))输入高电平的下限值输入高电平的下限值 V IL(min IL(min))输出低电平的上限值 V OH(max OH(max))输出高电平+V DD DDV OH OH((min )V OLOL((max max)) 0G 1门v O 范围v O输出低电平输入高电平V IH IH((min ) V IL IL((max max)) +V DD DD 0G 2门v I 范围输入低电平v IV NH —当前级门输出高电平的最小值时值时允许负向噪声电压的最大值允许负向噪声电压的最大值允许负向噪声电压的最大值。

电子技术基础(数字部分 第五版 康华光)华中科大课件第四章节

A0 A0 1 A1 A1 1

& Y1 Y1 & Y2 Y2 & Y3 Y3

7

4.4.2 译码器/数据分配器 (b) 74HC138(74LS138)集成译码器

E3

Y0

E2

Y1

E1

Y2

74HC138 Y3

Y4

A0

Y5

A1

Y6

A2

Y7

示意框图

A0 1 A1 2 A2 3

E1 4

E2 5 E3 6

Y7 7 GND 8

译码器的应用

1、已知下图所示电路的输入 信号的波形试画出译码器输E

出的波形。

A

+5V

E3

Y0

E

E2

Y1

E1

Y2

74HC138 Y3

Y4

A B C

A0 A1 A2

Y5 Y6 Y7

B

Y0 C

Y1 Y0

Y2 Y1

Y3 Y4

Y5

Y2 Y3

Y6 Y4

Y7 Y5

Y6

Y7 12

4.4.2 译码器/数据分配器

3、用译码器实现逻辑函数。 当E3 =1 ,E2 = E1 = 0时

&

Y6

&

&

Y7

8个译码 输出端

9

4.4.2 译码器/数据分配器

74HC138集成译码器功能表

输

入

输

出

E3 E 2 E 1 A2 A1 A0 Y 0 Y 1 Y 2 Y 3 Y 4 Y 5 Y 6 Y 7

×H××××HHHHHHHH ×XH×××HHHHHHHH L×××××HHHHHHHH HL L L L L LHHHHHHH HL L L LHHLHHHHHH HL L LHLHHLHHHHH HL L LHHHHHLHHHH HL LHL LHHHHLHHH HL LHLHHHHHHLHH HL LHHLHHHHHHLH HL LHHHHHHHHHHL

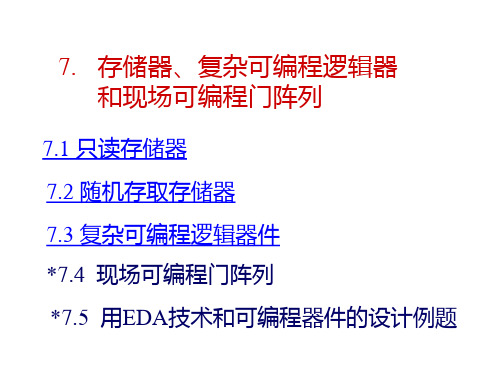

康华光,数字电路,(第五版),第七章 ,PPT课件

7.1 只读存储器 7.2 随机存取存储器 7.3 复杂可编程逻辑器件 *7.4 现场可编程门阵列 *7.5 用EDA技术和可编程器件的设计例题

教学基本要求:

• 掌握半导体存储器字、位、存储容量、地址、等基 本概念。 • 掌握RAM、ROM的工作原理及典型应用。 • 了解存储器的存储单元的组成及工作原理。 • 了解 CPLD 、 FPGA 的结构及实现逻辑功能的编程 原理。

A5 A6

列地址译码器

A7

Y0 A4 A3 A2 A1 A0

行 地 址 译 码 器 X0 X1 · · · X31

Y1

··· ··· ···

Y7

···

7.1 .1 ROM的 定义与基本结构

只读存储器,工作时内容只能读出,不能随时写入,所以 称为只读存储器。(Read-Only Memory) ROM的分类

存储的数据必须有电源供应才能保存, 一旦掉电, 数据全部丢失。 ROM(只读存储器):在正常工作状态只能读出信息。

断电后信息不会丢失,常用于存放固定信息(如程序、常数等)。

几个基本概念: 字长(位数):表示一个信息多位二进制码称为一个字, 字的位数称为字长。 字数:字的总量。 字数=2n (n为存储器外部地址线的线数) 地址:每个字的编号。 存储容量(M)=字数×位数 存储容量(M):存储二值信息的总量。

概

述

半导体存贮器能存放大量二值信息的半导体器件。 存储器的主要性能指标 存储数据量大——存储容量大 取快速度——存储时间短 可编程逻辑器件是一种通用器件,其逻辑功能是由用户 通过对器件的编程来设定的。它具有集成度高、结构灵 活、处理速度快、可靠性高等优点。

7.1 只读存储器 7.1 .1 ROM的 定义与基本结构

数字电路第五版(康华光)5__锁存器和触发器共58页PPT

31、园日涉以成趣,门虽设而常关。 32、鼓腹无所思。朝起暮归眠。 33、倾壶绝余沥,窥灶不见烟。

34、春秋满四泽,夏云多奇峰,秋月 扬明辉 ,冬岭 秀孤松 。 35、丈夫志四海,我愿不知老。

41、学问是异常珍贵的东西,从任何源泉吸 收都不可耻。——阿卜·日·法拉兹

42、只有在人群中间,才能认识自 己。——德国

43、重复别人所说的话,只需要教育; 而要挑战别人所说的话,则需要头脑。—— 玛丽·佩蒂博恩·普尔

44、卓越的人一大优点是:在不利与艰 难的遭遇里百折不饶。——贝多芬

45、自己的饭量自己知ห้องสมุดไป่ตู้。——苏联

模电第四章3(第五版)——康华光.ppt

.

Re

. r be Ib

Re

Rcb

+5V

+ . Rc + Vo . _

Vo _

极性错

3

Vi1 + _ + _ Vi2

Vo

+ . Vi _

Re

Rc

+ . Vo _

3

4

16

第三章 三极管及放大电路基础 例:Vo的波形出现下列三种情况。说明各是什么失真?应调节什么 参数才能使失真改善?如果电路改为 PNP 管电路,这三种情况各是 vo 什么失真? v i

T

vs

vBE

vCE v o

RL

4kΩ

共射极放大电路

ib

vce Rc RL vo

ic i b

rbe Rc RL vo

vi

Rb

交流等效电路

微变等效电路

12

放大电路如图所示。已知BJT的 ß =40, Rb=300k , Rc=2k, VCC= +12V,求: (1)放大电路的Q点。 (2)Av、Ri、Ro (3) 若RL开路,Av如何变化

ib 0

Ro = Rc

β ib 0

9

4.3.2 小信号模型分析法

第三章 三极管及放大电路基础

3. 小信号模型分析法的适用范围 放大电路的输入信号幅度较小,BJT工作在其V-T特性 曲线的线性范围(即放大区)内。H参数的值是在静态工作 点上求得的。所以,放大电路的动态性能与静态工作点参数 值的大小及稳定性密切相关。 优点: 分析放大电路的动态性能指标(Av 、Ri和Ro等)非常方便, 且适用于频率较高时的分析。 缺点: 在BJT与放大电路的小信号等效电路中,电压、电流等 电量及BJT的H参数均是针对变化量(交流量)而言的,不能用 来分析计算静态工作点。

电子技术基础数字部分第五版(康华光)5 锁存器和触发器59页PPT

5、虽然权力是一头固执的熊,可是金 子可以 拉着它领的就越加自命不凡。——邓拓 12、越是无能的人,越喜欢挑剔别人的错儿。——爱尔兰 13、知人者智,自知者明。胜人者有力,自胜者强。——老子 14、意志坚强的人能把世界放在手中像泥块一样任意揉捏。——歌德 15、最具挑战性的挑战莫过于提升自我。——迈克尔·F·斯特利

电子技术基础数字部分第五版(康华光)5 锁存器和触发器

1、合法而稳定的权力在使用得当时很 少遇到 抵抗。 ——塞 ·约翰 逊 2、权力会使人渐渐失去温厚善良的美 德。— —伯克

3、最大限度地行使权力总是令人反感 ;权力 不易确 定之处 始终存 在着危 险。— —塞·约翰逊 4、权力会奴化一切。——塔西佗

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3.6.1 各种门电路之间的接口问题

在数字电路或系统的设计中,往往将TTL和CMOS两种器件

混合使用,以满足工作速度或者功耗指标的要求。由于每种 器件的电压和电流参数各不相同,因而在这两种器件连接时

,要满足驱动器件和负载器件以下两个条件:

1) 驱动器件的输出电压必须处在负载器件所要求的输入电压范

围,包括高、低电压值(属于电压兼容性的问题)。

高阻

高电平

使能

L = AB

L=Z

与非逻辑 高阻状态

A B CS

逻辑符号 &

EN L

3.2.6 BiCMOS门电路

特点:功耗低、速度快、驱动力强 工作原理: I为高电平: MN、M1和T2导通,MP、M2和T1

截止,输出O为低电平。

M1的导通, 迅速拉走T1的基区存储 电荷; M2截止, MN的输出电流全部

2. TTL或非门

若A、B均为低电平: T2A和T2B均将截止, T3截止。 T4和D饱和,

输出为高电平。

若A、B中有一个为高电平:

T2A或T2B将饱和,

T3饱和,T4截止, 输出为低电平。 逻辑表达式

L = A B

3.2.5 集电极开路门和三态门电路

1.集电极开路门电路

VCC(5V) Rb1 4kΩ Rc2 1.6kΩ Rc4 130Ω T4 A B C Re2 1kΩ VCC(5V) Rb1 4kΩ Rc2 1.6kΩ Rc4 130Ω T4 A B C Re2 1kΩ T3 T1 T2 D T3 T1 T2 D

1

…

1

灌电流情况

74HC00: IOL(max)=4mA 74系列反相器: IIL(max)=1.6mA 74LS门: IIL(max)=0.4mA 总的输入电流IIL(total)=1.6mA+60.4mA=4mA 拉电流情况 74HC00: IOH(max)=4mA 74系列反相器: IIH(max)=0.04mA 74LS门: IIH(max)=0.02mA 总的输入电流 IIH(total)=0.04mA+60.02mA=0.16mA 驱动电路能为负载电路提供足够的驱动电流 CMOS门 74系列 & 1 74LS系列 1

2)驱动器件必须对负载器件提供足够大的拉电流和灌电流(属 于门电路的扇出数问题);

负载器件所要求的输入电压

1 驱动门

vO

vI

1

负载门

VOH(min)

v I

≥ VIH(min)

v O

VOH (min) VIH (min)

V IL (max ) V OL (max )

VOL(max) ≤ VIL(max)

(4)采用推拉式输出级以提高开关速度和带负载能力 a)带负载能力

当O=0.2V时 当输出为低电平时,T4截止, T3饱和导通,其饱和电流全 部用来驱动负载

当O=3.6V时 T3截止,T4组成的电压跟随 器的输出电阻很小,输出高 电平稳定,带负载能力也较 强。 b)输出级对提高开关速度的作用 输出端接负载电容CL时, O由低到高电平跳变的瞬间, CL充电,其时间常数很小使 输出波形上升沿陡直。而当 O由高变低后, CL很快放电, 输出波形的下降沿也很好。

作为T2管的驱动电流, M1 、 M2加快

输出状态的转换

I为低电平:

MP、M2和T1导通,MN、M1和T2

截止,输出O为高电平。

M1截止,MP的输出 电流全部作为T1的驱动电流。 T2基区的存储电荷通过M2而消散。 M1 、 M2加快输出状态的转换电 路的开关速度可得到改善

3.5 逻辑描述中的几个问题

& &

L

2. 三态与非门(TSL )

当CS= 3.6V时

三态与非门真值表 CS 数据输入端 输出端L 1 1 1 0

A

0 0 1 1

B

0 1 0 1

1

0

当CS= 0.2V时 真值表

CS

数据输入端

A 0 0 1 1 B 0 1 0 1

输出端L

1 1 1 0

1

0

×

×

____ CS =1 CS = 0

& 1 G1 G2

L

RE

控制电路 end

如RE、AL都要求高电平有效,EN低电平有效

AL RE & G2

L

如RE、AL都要求低电平有效,EN高电平有效

AL

RE

& G2

L

如RE、AL都要求高电平有效,EN高电平有效

A L RE & G2 L

3.6 逻辑门电路使用中的几个实际问题

3.6.1 各种门电路之间的接口问题 3.6.2 门电路带负载时的接口问题

3.2.4 TTL逻辑门电路

1. TTL与非门电路 多发射极BJT

b

b e e

T1

c

e e

c

A B

&

L= A B

TTL与非门电路的工作原理 • 当全部输入端为高电平时:

输出低电平 任一输入端为低电平时: 输出高电平

TTL与非门各级工作状态

I T1 T2 T4 放大 截止 T5 截止 饱和 O 高 电 平 低 (0.2V 3.6V) 输入有低电平 输入全为高电 深饱和 倒置使用的放大 截止 饱和 (0.2V) 平 (3.6V) 状态

3.5.1 正负逻辑问题 3.5.2 基本逻辑门的等效符号及其应用

3.5 逻辑描述中的几个问题

3.5.1 正负逻辑问题

1. 正负逻辑的规定 正逻辑体制:将高电平用逻辑1表示,低电平用逻辑0表示 负逻辑体制:将高电平用逻辑0表示,低电平用逻辑1表示

1

正逻辑

0

负逻辑

0

1

采用正逻辑

___与非门

L 1 1 1 0

1、)VOH(min)

≥

VIH(min)

2、)VOL(max) 3、) IOH(max)

4、)IOL(max)

≤ ≥

≥

VIL(max) IIH(total)

IIL(total)

2、 CMOS门驱动TTL门 CMOS门(4000系列): VOH(min)=4.9V TTL门(74系列): 输出、输入电压 VOH(min) ≥ VIH(min) VOL(max) ≤ VIL(max) 带拉电流负载 IOH(max) ≥ IIH(total) VOL(max) =0.1V IOL(max)=0.51mA IOH(max)=-0.51mA VIH(min) = 2V VIL(max )= 0.8V IIH(max)=20A IIL(max)=-0.4mA,

逻辑真值表

输入A 0 1 输出L 1 0

逻辑表达式 L = A

输入 低电平 高电平 T1 T2 饱和 截止 倒置工作 饱和 T3 截止 饱和 D4 导通 截止

T4 导通 截止

输出 高电平 低电平

(3 )采用输入级以提高工作速度 当TTL反相器I由3.6V变0.2V的瞬间 •T2、T3管的状态变化滞 后于T1管,仍处于导通 状态。 •T1管Je正偏、Jc反偏, T1工作在放大状态。 T1管射极电流(1+1 ) iB1很快地从T2的基区抽 走多余的存储电荷,从而 加速了输出由低电平到 高电平的转换。

2. 正负逻辑等效变换

某电路输入与输出电平表 A L L H H B L H L H L H H H L

A 0 0 1 1

B 0 1 0 1

采用负逻辑

___或非门

L

0 0 0

A

1 1 0

B

1 0 1

正逻辑 负逻辑 与非 或非 与 或 非 非

0

0

1

3.5.2 基本逻辑门电路的等效符号及其应用

1 vI 1 限流电阻 继电器

如果负载所需的电流比较大,则需要在数字电路的输出 端与负载之间接入一个功率驱动器件。

A B A B & ≥1 & L

A B A B

& ≥1 & L

A B A B

& & & L

A B

&

L = A B

逻辑门等效符号强调低电平有效

D0 D1 D2 D3 D4 D5 D6 D7

AL

IC

Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7

EN

AL RE = L

L=0

AL = 0 RE = 1

vOH

输出为低电平 的逻辑门输出 级的损坏

vOL

a) 集电极开路与非门电路 b) 使用时的外电路连接

VCC VCC RR b1b1 RR c2c2

Rc4 T4

C) 逻辑功能 L=AB OC门输出端连接实现线与

VDD RP

VCC

AA BB

TT 11

TT 22 TT 33 RR e2 e2

D

LL

A B C D

( 5 1.6 0.1 )V R= = 825Ω 4mA

2. 机电性负载接口 用各种数字电路来控制机电性系统的功能,而机电系统所需 的工作电压和工作电流比较大。要使这些机电系统正常工作, 必须扩大驱动电路的输出电流以提高带负载能力,而且必要时 要实现电平转移。 如果负载所需的电流不特别大,可以将两个反相器并联 作为驱动电路,并联后总的最大负载电流略小于单个门最 大负载电流的两倍。

3.6.2 门电路带负载时的接口电路

1. 用门电路直接驱动显示器件 门电路的输入为低电平,输出为高电平时,LED发光

vI 1 LED R

V OH V F R= ID

当输入信号为高电平,输出为低电平时,LED发光

VCC

V CC V F VOL R= ID

vI