用CPLD实现单片机与ISA总线接口的并行通信

单片机与cpld接口设计说明

摘要分析了基于FPGA/CPLD的EDA技术的特点与由其构成数字系统的优越性,并将它与单片机系统进行了比较,指出EDA技术克服了单片机本身难以克服的缺陷,将成为今后电子系统设计的主流。

针对可编程ASIC和MCS51单片机的特点,对两者之间的接口方式进行了分析。

用VerilogHDL给出了几个实用的接口参考程序。

VHDL的英文全名是Very-High-Speed Integrated Circuit HardwareDescription Language,诞生于1982年。

1987年底,VHDL被IEEE和美国国防部确认为标准硬件描述语言。

自IEEE公布了VHDL的标准版本,IEEE-1076(简称87版)之后,各EDA公司相继推出了自己的VHDL设计环境,或宣布自己的设计工具可以和VHDL接口。

此后VHDL 在电子设计领域得到了广泛的接受,并逐步取代了原有的非标准的硬件描述语言。

8051工作频率为11.0592MHZ CPLD(EPM7128SLC15)的工作频率为16.0000MHZ(有源晶振)进行接口连接,CPLD作为高速的地址缓存口,能够将数据地址部分进行暂时存储和译码,减少了多余的器件而使得设计布局更加合理。

关键词:EDA;CPLD/FPGA;单片机;VHDLABSTRACTBased on the analysis of the FPGA / CPLD of EDA technologies and the characteristics of a digital system by the superiority,And SCM system with a relatively,EDA that the SCM technology to overcome the deficiencies in itself difficult to overcome, the future will become the mainstream of electronic system design.MCS51 for programmable ASIC and the characteristics of SCM, the interface between the way the analysis.VHDL the English full name is Very-High-Speed Integrated Circuit HardwareDescription Language, was born in 1982. By the end of 1987, VHDL by the IEEE and the U.S. Department of Defense confirmed as the standard hardware description language. Since the publication of the IEEE VHDL version of the standard, IEEE-1076 (short version 87), the EDA companies have launched their own VHDL design environment, or to declare their own design tools and VHDL interface. Since then VHDL in the field of electronic design has been widely accepted and gradually replace the original non-standard hardware description language.8051 operating frequency of 11.0592 MHZ CPLD (EPM7128SLC15) the operating frequency of 16.0000 MHZ (Active crystal) interface connector, CPLD's address as a high-speed cache I can address some of the data for temporary storage and decoding, a decrease of Redundant device design and make distribution more reasonable.Keyword:EDA;SCM;CPLD/FPGA;VHDL;目录1 选题背景11.1 关于FPGA/CPLD和EDA技术11.2FPGA/CPLD与单片机21.2.1 单片机的学习效率较低21.2.2单片机本身的速度相对FPGA/CPLD来显得太慢22 硬件描述42.1单片机42.1.1单片机的特点42.1.2单片机的应用42.1.3单片机的基本组成42.1.4 MCS-51 的寻址方式52.1.5指令52.1.6计数初值的计算62.1.8串行口工作方式与帧格式72.2 FPGA/CPLD82.2.1 CPLD/FPGA特点82.2.2 CPLD102.2.3 FPGA112.2.4 VHDL语言描述132.3单片机与复杂可编程CPLD 器件的接口设计352.3.1总线方式353.3.2 独立方式372.3.3基于总线结构的接口设计382.3.4 实际电路连接392.3.5 地址锁存,译码与统一编址402.3.6 LCD 总线接口设计422.3.7 数码管接口设计433 软件程序设计463.1 软件程序简介463.1.1 Quartus II 图形用户界面的基本设计流程463.1.2 其它 EDA 工具与 Quartus II 软件配合使用时的基本设计流程473.1.3 cpld 与8051的总线接口方式设计流程图483.1.4 cpld 与8051的总线接口VHDL源码493.1.5 仿真步骤与其结果63结论67致68参考文献69附录691 选题背景目前,单片机在我国电子系统的设计中已得到广泛的应用,使我国的电子系统智能化水平在广度和深度上发生了质的飞跃。

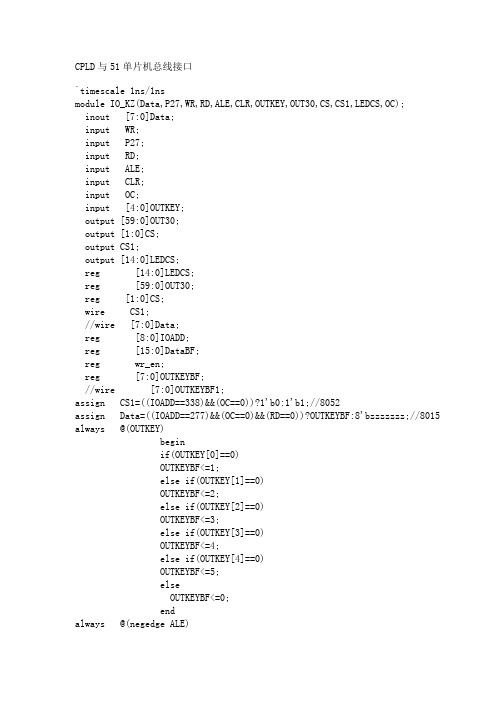

CPLD与51单片机总线接口

CPLD与51单片机总线接口`timescale 1ns/1nsmodule IO_KZ(Data,P27,WR,RD,ALE,CLR,OUTKEY,OUT30,CS,CS1,LEDCS,OC); inout [7:0]Data;input WR;input P27;input RD;input ALE;input CLR;input OC;input [4:0]OUTKEY;output [59:0]OUT30;output [1:0]CS;output CS1;output [14:0]LEDCS;reg [14:0]LEDCS;reg [59:0]OUT30;reg [1:0]CS;wire CS1;//wire [7:0]Data;reg [8:0]IOADD;reg [15:0]DataBF;reg wr_en;reg [7:0]OUTKEYBF;//wire [7:0]OUTKEYBF1;assign CS1=((IOADD==338)&&(OC==0))?1'b0:1'b1;//8052assign Data=((IOADD==277)&&(OC==0)&&(RD==0))?OUTKEYBF:8'bzzzzzzz;//8 015always @(OUTKEY)beginif(OUTKEY[0]==0)OUTKEYBF<=1;else if(OUTKEY[1]==0)OUTKEYBF<=2;else if(OUTKEY[2]==0)OUTKEYBF<=3;else if(OUTKEY[3]==0)OUTKEYBF<=4;else if(OUTKEY[4]==0)OUTKEYBF<=5;elseOUTKEYBF<=0;endalways @(negedge ALE)beginIOADD<={P27,Data};//ALE下降延读地址endalways @(IOADD or WR) //WR下降延写数据beginif((IOADD>256)&&(IOADD<337)&&(IOADD!=277))wr_en<=WR;elsebeginwr_en<=1;endendalways @(negedge wr_en or posedge OC or posedge WR) //WR下降延写数据beginif(OC)beginCS=2'b00;LEDCS=15'b00000_0000_0000_00;endelse if(WR)beginCS=2'b00;endelsebegincase(IOADD)261: begin CS=2'b01; end//8005262: begin CS=2'b10;LEDCS=15'b00000_0000_00 00_01;end//8006263: begin CS=2'b10;LEDCS=15'b00000_0000_00 00_10;end//8007264: begin CS=2'b10;LEDCS=15'b00000_0000_0001_00;e nd//8008265: begin CS=2'b10;LEDCS=15'b00000_0000_0010_00;e nd//8009266: begin CS=2'b10;LEDCS=15'b00000_0000_0100_00;e nd//800A267: begin CS=2'b10;LEDCS=15'b00000_0000_1000_00;e nd//800B268: begin CS=2'b10;LEDCS=15'b00000_0001_0000_00;end//800C269: begin CS=2'b10;LEDCS=15'b00000_0010_0000_00;e nd//800D270: begin CS=2'b10;LEDCS=15'b00000_0100_0000_00;e nd//800E271: begin CS=2'b10;LEDCS=15'b00000_1000_0000_00;e nd//800F272: begin CS=2'b10;LEDCS=15'b00001_0000_0000_00;e nd//8010273: begin CS=2'b10;LEDCS=15'b00010_0000_0000_00;e nd//8011274: begin CS=2'b10;LEDCS=15'b00100_0000_0000_00;e nd//8012275: begin CS=2'b10;LEDCS=15'b01000_0000_0000_00;e nd//8013276: begin CS=2'b10;LEDCS=15'b10000_0000_00 00_00;end//8014endcaseendendalways @(negedge wr_en or posedge CLR or posedge OC ) //WR下降延写数据beginif(OC)beginDataBF=0;OUT30[59:0]=60'hfffffffffffffff;endelse if(CLR)beginDataBF=0;OUT30[59:0]=60'hfffffffffffffff;endelsebeginif(Data[0])DataBF[1:0]=2'b10;elseDataBF[1:0]=2'b01; if(Data[1])DataBF[3:2]=2'b10;elseDataBF[3:2]=2'b01;if(Data[2])DataBF[5:4]=2'b10;elseDataBF[5:4]=2'b01;if(Data[3])DataBF[7:6]=2'b10;elseDataBF[7:6]=2'b01;if(Data[4])DataBF[9:8]=2'b10;elseDataBF[9:8]=2'b01;if(Data[5])DataBF[11:10]=2'b10;elseDataBF[11:10]=2'b01;if(Data[6])DataBF[13:12]=2'b10;elseDataBF[13:12]=2'b01;if(Data[7])DataBF[15:14]=2'b10;elseDataBF[15:14]=2'b01;case(IOADD)257: begin OUT30[15:0] =DataBF;end//8001258: begin OUT30[31:16]=DataBF;end//8002259: begin OUT30[47:32]=DataBF;end//8003 260: begin OUT30[59:48]=DataBF;end//8004endcasecase(IOADD)278: begin OUT30[1:0]=2'b10;end//8016279: begin OUT30[1:0]=2'b01;end//8017280: begin OUT30[3:2]=2'b10;end//8018281: begin OUT30[3:2]=2'b01;end//8019282: begin OUT30[5:4]=2'b10;end//801A283: begin OUT30[5:4]=2'b01;end//801B284: begin OUT30[7:6]=2'b10;end//801C285: begin OUT30[7:6]=2'b01;end//801D287: begin OUT30[9:8]=2'b01;end//802F endcasecase(IOADD)288: begin OUT30[11:10]=2'b10;end//8020 289: begin OUT30[11:10]=2'b01;end//8021 290: begin OUT30[13:12]=2'b10;end//8022 291: begin OUT30[13:12]=2'b01;end//8023 292: begin OUT30[15:14]=2'b10;end//8024 293: begin OUT30[15:14]=2'b01;end//8025 294: begin OUT30[17:16]=2'b10;end//8026 295: begin OUT30[17:16]=2'b01;end//8027 296: begin OUT30[19:18]=2'b10;end//8028 297: begin OUT30[19:18]=2'b01;end//8029 endcasecase(IOADD)298: begin OUT30[21:20]=2'b10;end//802A 299: begin OUT30[21:20]=2'b01;end//802B 300: begin OUT30[23:22]=2'b10;end//802C 301: begin OUT30[23:22]=2'b01;end//802D 302: begin OUT30[25:24]=2'b10;end//802E 303: begin OUT30[25:24]=2'b01;end//802F 304: begin OUT30[27:26]=2'b10;end//8030 305: begin OUT30[27:26]=2'b01;end//8031 306: begin OUT30[29:28]=2'b10;end//8032 307: begin OUT30[29:28]=2'b01;end//8033 endcasecase(IOADD)308: begin OUT30[31:30]=2'b10;end//8034 309: begin OUT30[31:30]=2'b01;end//8035 310: begin OUT30[33:32]=2'b10;end//8036 311: begin OUT30[33:32]=2'b01;end//8037 312: begin OUT30[35:34]=2'b10;end//8038 313: begin OUT30[35:34]=2'b01;end//8039 314: begin OUT30[37:36]=2'b10;end//803A 315: begin OUT30[37:36]=2'b01;end//803B 316: begin OUT30[39:38]=2'b10;end//803C 317: begin OUT30[39:38]=2'b01;end//803D endcasecase(IOADD)318: begin OUT30[41:40]=2'b10;end//803E 319: begin OUT30[41:40]=2'b01;end//803F 320: begin OUT30[43:42]=2'b10;end//8040 321: begin OUT30[43:42]=2'b01;end//8041323: begin OUT30[45:44]=2'b01;end//8043 324: begin OUT30[47:46]=2'b10;end//8044 325: begin OUT30[47:46]=2'b01;end//8045 326: begin OUT30[49:48]=2'b10;end//8046 327: begin OUT30[49:48]=2'b01;end//8047 endcasecase(IOADD)328: begin OUT30[51:50]=2'b10;end//8048 329: begin OUT30[51:50]=2'b01;end//8049 330: begin OUT30[53:52]=2'b10;end//804A 331: begin OUT30[53:52]=2'b01;end//804B 332: begin OUT30[55:54]=2'b10;end//804C 333: begin OUT30[55:54]=2'b01;end//804D 334: begin OUT30[57:56]=2'b10;end//804E 335: begin OUT30[57:56]=2'b01;end//804F 336: begin OUT30[59:58]=2'b10;end//8050 337: begin OUT30[59:58]=2'b01;end//8051 endcaseendendendmodule。

基于单片机与CPLD的无线控制系统

基于单片机与CPLD的无线控制系统摘要:介绍一种基于单片机与CPLD结合的传感器网络节点的无线控制系统。

节点中单片机对无线命令进行译码,并对外围子模块进行控制,CPLD扩展控制系统的并行I/O端口、SPI串行接口等,从而根据系统需要可扩展无线传感网络节点的外围功能模块。

采用单片机与CPLD模块化设计方法,降低了设计成本,方便电路的多次改进,为传感器网络节点在不同场合的应用提供了一种通用的方法。

0引言自单片机引入我国以来,相关产品的普及促使单片机的应用设计日益广泛。

传统的单片机控制系统由单片机以及外围扩展芯片组成,但是这些外,围芯片一般具有接线重复性高、体积大等缺点。

可编程逻辑宏单元或逻辑块之间的相互连线在同一封装内,受外界干扰影响小,电磁兼容(EMC)性能好。

对设计者来说,CPLD器件最大的优点在于可现场编程,改变逻辑关系时,无需更改外部线路板,只需用图形语言程序或硬件描述语言程序来改变电路,生成下载编辑软件,通过下载电缆输入CPLD器件即可,非常方便,特别有利于新品试制,大大缩短了开发周期。

使用CPLD和单片机结合构成其外围电路可以减少系统芯片数量,缩小系统体积,提高系统可靠性。

1控制系统该系统是一个无线传感器网络节点的控制系统,它用于控制无线模块接收主站发送过来的信息,单片机读取这些数据并译码后,根据译码结果控制各功能子模块,如无线模块控制、温度采集控制、电源管理控制、时间统一信号控制等功能,共需要28个输出控制I/O口,13个输入控制I/O口,扩展I/O端口分配8个。

各外围模块通过SPI串行标准接口的扩展与单片机和CPLD进行通信,并完成数据传输控制功能。

各外围模块只需接受MCU的控制命令,即可独立完成外围模块各自的功能:无线模块的收发、数据采集A/D转换、时间统一记录、电源管理等。

同时预留单片机通过USART的串口输出,另外,还需要此系统具有很好的扩展性,通过扩展外围模块来增加节点不同的功能。

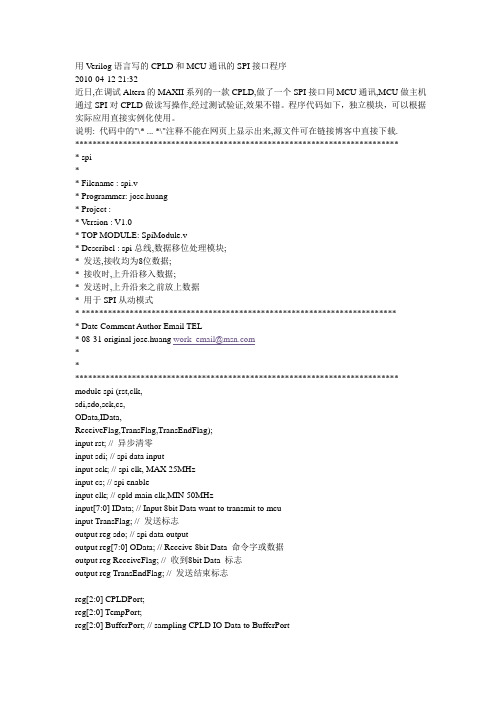

用Verilog语言写的CPLD和MCU通讯的SPI接口程序

用Verilog语言写的CPLD和MCU通讯的SPI接口程序2010-04-12 21:32近日,在调试Altera的MAXII系列的一款CPLD,做了一个SPI接口同MCU通讯,MCU做主机通过SPI对CPLD做读写操作,经过测试验证,效果不错。

程序代码如下,独立模块,可以根据实际应用直接实例化使用。

说明: 代码中的"\* ... *\"注释不能在网页上显示出来,源文件可在链接博客中直接下载.*************************************************************************** spi** Filename : spi.v* Programmer: jose.huang* Project :* Version : V1.0* TOP MODULE: SpiModule.v* Describel : spi总线,数据移位处理模块;* 发送,接收均为8位数据;* 接收时,上升沿移入数据;* 发送时,上升沿来之前放上数据* 用于SPI从动模式* ************************************************************************* Date Comment Author Email TEL* 08-31 original jose.huang work_email@* ------- ----*************************************************************************** module spi (rst,clk,sdi,sdo,sck,cs,OData,IData,ReceiveFlag,TransFlag,TransEndFlag);input rst; // 异步清零input sdi; // spi data inputinput sck; // spi clk, MAX 25MHzinput cs; // spi enableinput clk; // cpld main clk,MIN 50MHzinput[7:0] IData; // Input 8bit Data want to transmit to mcuinput TransFlag; // 发送标志output reg sdo; // spi data outputoutput reg[7:0] OData; // Receive 8bit Data 命令字或数据output reg ReceiveFlag; // 收到8bit Data 标志output reg TransEndFlag; // 发送结束标志reg[2:0] CPLDPort;reg[2:0] TempPort;reg[2:0] BufferPort; // sampling CPLD IO Data to BufferPortreg[7:0] samplnum;always@(posedge clk)beginCPLDPort[0] <= sdi;CPLDPort[1] <= sck;CPLDPort[2] <= cs;endalways@(posedge clk or negedge rst)beginif(!rst) // 异步清零beginsamplnum <= 8'b0;endelse if(TempPort == CPLDPort)beginsamplnum <= samplnum + 1'b1;endelsebeginsamplnum <= 8'b0;TempPort <= CPLDPort;endendalways@(posedge clk or negedge rst)beginif(!rst) // 异步清零beginBufferPort[0] <= 1'b0; //CPLDPort[0] <= sdi; BufferPort[1] <= 1'b0; //CPLDPort[1] <= sck; BufferPort[2] <= 1'b1; //CPLDPort[2] <= cs;endelsebeginif(samplnum > 10) // set by cpld main clk and spi clk beginBufferPort <= TempPort;endelse BufferPort <= BufferPort;endendwire wsdi;wire wsck;wire wcs;assign wsdi = BufferPort[0]; //CPLDPort[0] <= sdi; assign wsck = BufferPort[1]; //CPLDPort[1] <= sck; assign wcs = BufferPort[2]; //CPLDPort[2] <= cs;// 计数reg[7:0] ShiftCounter;reg[7:0] ClrFlagCounter;reg Bwsck;always@(posedge clk or negedge rst or posedge wcs) beginif(!rst) // 异步清零beginShiftCounter <= 8'b0;ReceiveFlag <= 1'b0;TransEndFlag <= 1'b0; // shift状态清接收标志Bwsck <= 1'b0;endelse if(wcs) // 结束异步清零beginShiftCounter <= 8'b0;Bwsck <= 1'b0;if(ClrFlagCounter == 10)beginReceiveFlag <= 1'b0; // SPI操作结束清接收标志TransEndFlag <= 1'b0; // shift状态清接收标志endelse ClrFlagCounter <= ClrFlagCounter + 1'b1;endelsebeginBwsck <= wsck;ClrFlagCounter <= 8'b0;if(wsck && (!Bwsck)) // 上升沿处理beginif(ShiftCounter == 7)beginShiftCounter <= 8'b0;if(!TransFlag) // receive data from mcu ReceiveFlag <= 1'b1; // 收到8bit dataelseTransEndFlag <= 1'b1; // 发送完成endelsebeginShiftCounter <= ShiftCounter + 1'b1;ReceiveFlag <= 1'b0; // shift状态清接收标志TransEndFlag <= 1'b0; // shift状态清接收标志endendendend// 移位always@(posedge clk or negedge rst or posedge wcs) beginif(!rst)sdo <= 1'b0;else if(wcs)sdo <= 1'b0;else if(wsck && (!Bwsck)) //上升沿处理beginif(!TransFlag) // receive data from mcubeginOData <= {OData[6:0],wsdi};endelse // transmit data to mcubeginsdo <= IData[7-ShiftCounter];endendendendmodule波形图。

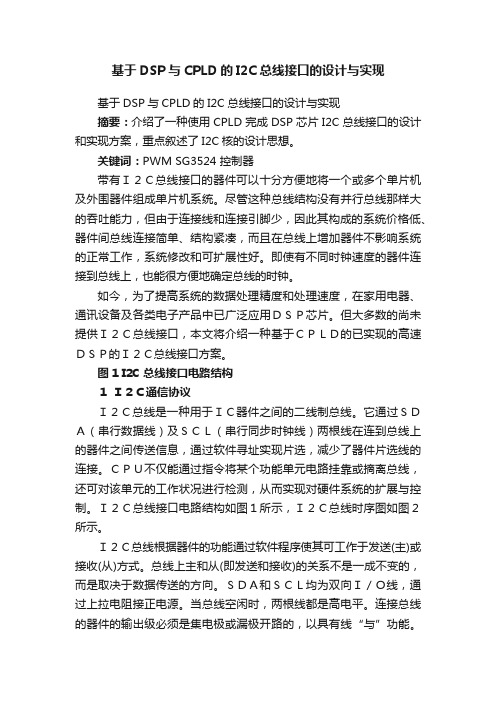

基于DSP与CPLD的I2C总线接口的设计与实现

基于DSP与CPLD的I2C总线接口的设计与实现基于DSP与CPLD的I2C总线接口的设计与实现摘要:介绍了一种使用CPLD完成DSP芯片I2C总线接口的设计和实现方案,重点叙述了I2C核的设计思想。

关键词:PWM SG3524 控制器带有I2C总线接口的器件可以十分方便地将一个或多个单片机及外围器件组成单片机系统。

尽管这种总线结构没有并行总线那样大的吞吐能力,但由于连接线和连接引脚少,因此其构成的系统价格低、器件间总线连接简单、结构紧凑,而且在总线上增加器件不影响系统的正常工作,系统修改和可扩展性好。

即使有不同时钟速度的器件连接到总线上,也能很方便地确定总线的时钟。

如今,为了提高系统的数据处理精度和处理速度,在家用电器、通讯设备及各类电子产品中已广泛应用DSP芯片。

但大多数的尚未提供I2C总线接口,本文将介绍一种基于CPLD的已实现的高速DSP的I2C总线接口方案。

图1 I2C总线接口电路结构1I2C通信协议I2C总线是一种用于IC器件之间的二线制总线。

它通过SDA(串行数据线)及SCL(串行同步时钟线)两根线在连到总线上的器件之间传送信息,通过软件寻址实现片选,减少了器件片选线的连接。

CPU不仅能通过指令将某个功能单元电路挂靠或摘离总线,还可对该单元的工作状况进行检测,从而实现对硬件系统的扩展与控制。

I2C总线接口电路结构如图1所示,I2C总线时序图如图2所示。

I2C总线根据器件的功能通过软件程序使其可工作于发送(主)或接收(从)方式。

总线上主和从(即发送和接收)的关系不是一成不变的,而是取决于数据传送的方向。

SDA和SCL均为双向I/O线,通过上拉电阻接正电源。

当总线空闲时,两根线都是高电平。

连接总线的器件的输出级必须是集电极或漏极开路的,以具有线“与”功能。

I2C总线的数据传送速率在标准工作方式下为100kbit/s,在快速方式下,最高传送速率可达400kbit/s。

在数据传送过程中,必须确认数据传送的开始和结束信号(也称启动和停止信号)。

用CPLD实现单片机与ISA总线接口的并行通信

用CPLD实现单片机与ISA总线接口的并行通信用CPLD实现单片机与ISA总线接口的并行通信摘要:介绍了用ALTERA公司MAX7000系列CPLD芯片实现单片机与PC104ISA总线接口之间的关行通信。

给出了系统设计方法及程序源代码。

关键词:CPLD ISA总线并行通信CPLD(Complex Programmable Logic Device)是一种复杂的用户可编程逻辑器件,由于采用连续连接结构,易于预测延时,从而使电路仿真更加准确。

CPLD是标准的大规模集成电路产品,可用于各种数字逻辑系统的设计。

近年来,由于采用先进的集成工艺和大指量生产,CPLD器件成本不断下降,集成密度、速度和性能大幅度提高,一个芯片就可以实现一个复杂的数字电路系统;再加上使用方便的开发工具,使用CPLD器件可以极大地缩短产品开发周期,给设计修改带来很大方便[1]。

本文以ALTERA公司的MAX7000系列为例,实现MCS51单片机与PC104ISA总线接口的并行通信。

采用这种通信方式,数据传输准确高速,在12MHz晶振的MCS51单片机控制的数据采集系统中,可以满足与PC104 ISA总线接口实时通信的要求,通信速率达200Kbps。

1 系统总体设计方案用CPLD实现单片机与PC104ISA总线接口的并行通信,由于PC104主要完成其它方面的数据采集工作,只是在空闲时才能接收单片机送来的数据,所以要求双方通信的实时性很强,但数据量不是很大。

因此在系统设计中,单片机用中断方式接收数据,PC104采用查询方式接收数据。

系统设计方案如图1所示。

在单片机部分,D[0..7]是数据总线,A[0..15]是地址总线,RD和WR分别是读写信号线,INT0是单片机的外部中断,当单片机的外部中断信号有效时,单片机接收数据。

在CPLD部分,用一片MAX7000系列中的PM7128 ESLC84来实现,用来完成MCS51与PC104ISA总线接口之间的数据传输、状态查询及延时等待。

一种基于CPLD的单片机与PCI接口设计解决方案

一种基于CPLD的单片机与PCI接口设计解决方案0 引言8 位单片机在嵌入式系统中应用广泛,然而让它直接与PCI 总线设备打交道却有其固有缺陷。

8 位单片机只有16 位地址线,8 位数据端口,而PCI 总线2.0 规范中,除了有32 位地址数据复用AD[3~0]外,还有FRAME、IRDY、TRDY等重要的信号线。

让单片机有限的I/O 端口来直接控制如此众多的信号线是不可能的。

一种可行的方案就是利用CPLD 作为沟通单片机与PCI 设备间的桥梁, 充分利用CPLD 中I/O 资源丰富、用户可自定制逻辑的优势,来帮助单片机完成与PCI 设备间的通信任务。

1 PCI 接口设计原理1.1 PCI 总线协议简介这里只讨论PCI 总线2.0 协议,其它协议仅仅是在2.0 的基础上作了一些扩展,仅就单片机与PCI 设备间的通信来说,意义不大。

PCI 总线是高性能局部总线,工作频率0~33MHz,可同时支持多组外围设备。

在这里,我们只关心单片机与一个PCI 设备间通信的情况,而且是以单片机与CPLD 一方作为主控方,另一方作为PCI 从设备。

这样做的目的是为了简化问题,降低系统造价。

PCI 总线上信号线虽然多,但并不是每个信号都要用到。

实际上PCI 设备也并不会支持所有的信号线,比如错误报告信号PERR 与SERR 在网卡中就不支持。

我们可以针对具体的应用选择支持其中部分信号线,还有一些信号线可以直接连电源或接地。

下面简单介绍一下常用信号线的功能。

AD[31~0]:地址数据多路复用信号。

在FRAME 有效的第一个周期为地址,在IRDY 与TRDY 同时有效的时候为数据。

C/BE[3~0]:总线命令与字节使能控制信号。

在地址中传输的是总线命。

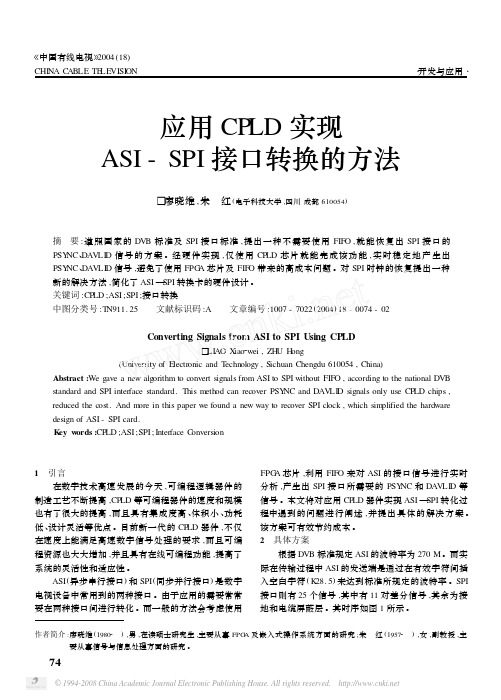

应用CPLD实现ASI_SPI接口转换的方法

应用CP LD 实现ASI -SPI 接口转换的方法□廖晓维,朱 红(电子科技大学,四川成都610054)摘 要:遵照国家的DVB 标准及SPI 接口标准,提出一种不需要使用FIFO ,就能恢复出SPI 接口的PSY NC 、DAV LI D 信号的方案。

经硬件实现,仅使用CP LD 芯片就能完成该功能,实时稳定地产生出PSY NC 、DAV LI D 信号,避免了使用FPG A 芯片及FIFO 带来的高成本问题。

对SPI 时钟的恢复提出一种新的解决方法,简化了ASI —SPI 转换卡的硬件设计。

关键词:CP LD ;ASI ;SPI ;接口转换中图分类号:T N911.25 文献标识码:A 文章编号:1007-7022(2004)18-0074-02Converting Signals from ASI to SPI Using CP LD□LI AO X iao 2wei ,ZH U H ong(University of Electronic and T echnology ,Sichuan Chengdu 610054,China )Abstract :We gave a new alg orithm to convert signals from ASI to SPI without FIFO ,according to the national DVB standard and SPI interface standard.This method can recover PSY NC and DAV LI D signals only use CP LD chips ,reduced the cost.And m ore in this paper we found a new way to recover SPI clock ,which sim plified the hardware design of ASI -SPI card.K ey w ords :CP LD ;ASI ;SPI ;Interface C onversion1 引言在数字技术高速发展的今天,可编程逻辑器件的制造工艺不断提高,CP LD 等可编程器件的速度和规模也有了很大的提高,而且具有集成度高、体积小、功耗低、设计灵活等优点。

关于单片机脉冲信号源的CPLD实现方法

关于单片机脉冲信号源的CPLD实现方法单片机产生的脉冲信号源由于是靠软件实现的,所以输出频率及步进受单片机时钟频率、指令数和指令执行周期的限制。

文中介绍了一种以CPLD为核心的脉冲信号源,脉冲信号源的参数(频率、占空比)由工控机通过I/O 板卡设置,设定的参数由数码管显示,这种脉冲信号源与其它脉冲信号发生电路相比具有输出频率高、步进小(通过选用高速CPLD 可提高频率及缩小步进)、精度高、参数调节方便、易于修改等优点。

1 系统组成及工作原理脉冲信号源电路核心采用一片可编程逻辑器件EPM7128SLC84—10,它属于Ahera 公司MAX7000 系列产品,MAX7000 系列产品是高密度、高性能的CMOS EPLD,是工业界速度最快的可编程逻辑器件系列,它是在Ahera 公司的第二代MAX 结构基础上采用先进的CMOS EEPROM 技术制造的。

MAX7000 系列产品包括MAX7000E、MAX7000S、MAX7000A,集成度为600~5 000 可用门,有32~256 个宏单元和36—155 个用户I/0 引脚。

这些基于EEPROM 的器件能够组合传输延迟快至5.0 ns,16 位频率为178 MHz。

此外,它们的输入寄存器的建立时间非常短,能够提供多个系统时钟且有可编程的速度/功率控制。

MAX7000S 是MAX7000 系列的增强型,具有高密度,是通过工业标准4 引脚JTAG 接口实现在线可编程的,在线编程电压为5V。

EPM7128SLC84—10 有128 个逻辑宏单元,2 500 个门电路,8 个逻辑阵列块,68 个L/O 管脚,速度等级为一6(传输延迟6 ns),最高时钟频率为147.1 MHz。

整个信号产生及数码显示控制电路(不包括驱动)集成在一片中。

脉冲信号源电路由时钟源、锁存器、计数器、控制电路、驱动电路以及数码管动态扫描显示电路组成,电路框图,如图l 所示。

时钟电路采用80 MHz 有源晶振,它为系统提供时钟信号;锁存器1 及锁存器2 用于保存频率及占空比数据,为16 位计数器提供预置值,锁存器位数为8 位,设定的数据通过工控机输入,由于计数器位数为16 位,故需分两次打人数据;计数器1 及计数器2 作为定时器,按锁存器1、2 设定的值计时,两个计数器交替工作,即一个计数器工作而另一个计数器不工作。

单片机与CPLD通信

SPI驱动数码管

SPI的定义:

SPI 是英文Serial Peripheral Interface的缩写,中文意思是串行外围设 备接口,SPI是Motorola公司推出的一种同步串行通讯方式,是一种四线同 步总线,因其硬件功能很强,与SPI有关的软件就相当简单,使CPU有更多 的时间处理其他事务。

void wr_byte(unsigned char d) { unsigned char i; for(i=0;i<8;i++) { SPI_DI = d&0x01; //发送最低位 SPI_CK = 0; _nop_(); SPI_CK = 1; //移位寄存器移位 _nop_(); d = d >>1; //数据移位 } }

void main() { write_data(0,1); write_data(1,2); write_data(2,3); write_data(3,4); write_data(4,5); write_data(5,6); write_data(6,7); write_data(7,8); while(1);

谢谢观赏

WPS Office

Make Presentation much more fun

总线驱动数码管

#include <reg52.h> #include <absacc.h> #define DA0 XBYTE[0xff00]//定义总线读写地址 #define DA1 XBYTE[0xff01] #define DA2 XBYTE[0xff02] #define DA3 XBYTE[0xff03] #define DA4 XBYTE[0xff04] #define DA5 XBYTE[0xff05] #define DA6 XBYTE[0xff06] #define DA7 XBYTE[0xff07] void main() { while(1) { DA7 = 0xE0; //7 DA6 = 0xBE; //6 DA5 = 0xB6; //5 DA4 = 0xFE; //8 DA3 = 0x66; //4 DA2 = 0xf2; //3 DA1 = 0xDA; //2 DA0 = 0x60; //1 } }

单片机与CPLD接口及数码管驱动设计

#include "STC89C51RC.H" //STC 单 片 机 头 文 件,

相当与一般 51 单片机的 reg51.h

#include <absacc.h> // 单片机 C 语言绝对地址宏

定义头文件,例如对 XBYTE 的定义

// 根据显示缓冲寄存器 CLK 始终编制信号 YC、 YD、YE、YF 确 定 地 址 为 0xffec、0xffed、0xffee、 0xffef

时钟

2Bit 计数器

译 码

图10 CPLD驱动的数码管扫描电路原理框图 根 据 以 上 显 示 原 理, 电 路 如 图 11 所 示, 在

Max+plusII 环 境 中 直 接 调 用 8D 数 据 锁 存 器 74273b 做显示缓冲器,数据输入端口接单片机 P0 口,CLR 接 VCC(也可以接 MCU 的某个 IO 实现清零),CLK 由 WR 与译码地址 YC ~ YF 相或,数据选择器 led_ sel、 计 数 器 counter、2-4 译 码 器 decode2_4 均 由 Max+plusII 集成 LPM(参数可配置)模块配置向导直 接生成。显示缓冲器输出给 4 选 1 数据选择器由 led_ sel 控制分时送显,时钟由 MCU ALE 信号由 div_clk 分 频后给计数 counter,计数器输出接数据选择器得到 数码管段码 DISP[7..0],计数器输出经过 2-4 译码器 decode2_4 译码得 SEG[4..1],SEG[4..1] 依次译码为 8、 4、2、1(共阳极数码管决定),保证每时间段只有一

图3 地址锁存仿真时序图

基于CPLD与单片机的双向通信控制器设计

基于CPLD与单片机的双向通信控制器设计来源:无线测温 单片机 CPLD 控制系统在传统的控制系统中,人们常常采用单片机作为控制核心。

但这种方法硬件连线复杂,可靠性差,且单片机的端口数目、内部定时器和中断源的个数都有限,在实际应用中往往需要外加扩展芯片。

这无疑对系统的设计带来诸多不便。

现在有很多系统采用可编程逻辑器件CPLD作为控制核心。

它与传统设计相比较,不仅简化了接口和控制,提高了系统的整体性能及工作可靠性,也为系统集成创造了条件。

但可编程逻辑器件的D触发器资源非常有限,而且可编程逻辑器件在控制时序方面不如单片机那样方便,很多不熟悉的应用者往往感到应用起来非常的困难。

利用可编程逻辑器件和单片机构成的双向通信控制器克服了两者的缺点,且把二者的长处最大限度地发挥出来。

1 CPLD与单片机AT89C51双向串行通信原理1.1 单片机到可编程逻辑器件的串行通信单片机到CPLD的串行通信接口电路是利用VHDL语言在CPLD中设计一个串行输入并行输出的八位移位寄存器,其端口与单片机的P1.4~P1.7相连,如图1所示。

CS为单片机选信号,当其为低时使能八位寄存器;当DCLOCK信号的上升沿到达clk端口时,八位移位寄存器就会将单片机输出到cxin的一位数据移入;当单片机A寄存器中的八位数据欲传送给CPLD时,就在P1.6连续产生八次上升沿,单片机便顺次地将A中的数据移到cxin,八次后A中的数据段就会出现在CPLD的cxout中。

其VHDL源程序如下:entity cuanxing isport (clk,cxin,cs:in std_logic;cxout:out std_logic_vector(7 downto 0));end;architecture rtl of cuanxing issignal shift:std_logic_vector(7 downto 0) ;八位暂存变量并行输出beginprocess(clk)beginif(cs=‘0’)thenshift <=(others=>‘0’);若未被选中,输出全零elsif(clk‘event and clk=’1‘)then ;若上升沿到达clk时,被选中。

cpld和单片机接口

工程实例2:

——远距离数据采集监测系统

随着现代工业的发展,远距离数据采集监测已成为日益重 要的检测技术,广泛应用于工农业等需要同时监控温度、湿度 和压力等场合。

设计思路:

为了提高系统的智能性、可靠性和实用性,可采用双CPU的 方法,即在数据采集的远端和本地都采用单片机控制,远端完 数据的采集、 数据的接收、 成数据的采集、抽样和发送 数据的采集 抽样和发送,本地完成数据的接收、处理,同 数据的接收 处理, 时采用一片CPLD作为键盘、显示器及打印机的接口扩展。

程序实现: 1)单片机部分

#define CPLD ADDRESS 0x0000 #include <absacc. h> main() { unsigned charA DDRESSIndex; //CPLD某个功能部件的地址 unsigned char DATA_READ,DATA_WRITE; XBYTE [CPLD_ADDRESS+ADDRESSIndex]=DATA_WRITE;//单片机向 CPLD写数据 DATA_READ=XBYTE[CPLD_ADDRESS+ADDRESSIndex]; // 单片机从 CPLD读数据 }

附:总线接口模块设计Verilog 参考程序:

接口定义:

module interface(mcu_p0,mcu_p2_7,mcu_ale,mcu_wr,mcu_rd,creg1,creg2); inout[7:0] mcu_p0;//8位数据总线 input mcu_p2_7;//地址总线 input mcu_ale,mcu_rd,mcu_wr;//控制总线 input creg1;//连接内部控制寄存器,用于单片机从CPLD读取信号 output creg2; //连接内部控制寄存器,用于单片机将信号写入CPLD reg dph;//内部变量,用于锁存高位地址 reg[7:0] dpl;//内部变量,用于锁存低位地址 ……

采用复杂可编程逻辑器件与ISA总线相结合实现数据采集系统设计

采用复杂可编程逻辑器件与ISA总线相结合实现数据采集系统设计数据采集是工业测量和控制系统中的重要部分。

它是测控现场的模拟信号源与上位机之间的接口,其任务是采集现场连续变化的被测信号。

系统应将所采集的模拟数据信号尽可能真实、不失真地显示给控制人员。

随着计算机技术和EDA技术的发展,由于复杂可编程逻辑器件(CPLD)具有高集成度、小体积、低成本、低功耗以及高稳定性等诸多优点而广泛使用到诸如传统工业控制等各个领域。

基于ISA的接口电路,其布线要求远没有PCI或USB接口板高。

由于它能够提供16位I/O操作,对I/O的直接读写可以完全不考虑复杂的驱动程序和应用程序,因而在ISA 总线上开发接口电路目前仍是首先考虑的方法。

因此,这里提出一种基于CPLD和ISA总线的数据采集系统设计。

1 系统硬件设计数据采集系统的硬件电路主要包括:CPLD逻辑控制电路、8254定时器电路、A/D转换电路。

该系统硬件设计框图如图1所示。

1.1 CPLD逻辑控制电路该系统使用XC9572作为主控器件。

XC9572是一款高性能可编程逻辑器件,内含4个36 v 18功能模块,具有l 600个可用系统门。

ISA总线上的地址、控制指令和数据被送进CPLD,经处理后送到相应电路中。

由A/D转换电路得到的数据也返回到CPLD进行处理,并经ISA总线送至计算机中。

图2为数据采集系统的逻辑控制电路,Ul是数据缓冲器74HC245,由lSA总线的读/写信号(IOR/IOW)和板卡选择信号(BSEL)决定数据的流向。

比较器74LS688和XFl组成板卡选择信号发生电路。

通过在XFl上的跳线可确定采集系统板的基地址。

该系统基地址设置为280H。

ISA总线上的读写信号,经缓冲器的数据信号(LADO~LAD7),地址信号(A0~A3)均与。

基于CPLD的单片机之间的通信接口设计

本 设计 利用 MA X+pu Ⅱ开发 软件 , 通信 控制 ls 在

板 上用 E 1 0芯 片设计 了一个 三 通道 F F 存 储器 P K3 IO

阵列 , 过复 用方 式 分别 与 通 信控 制 板 和 有线 传输 板 通 上 C8 5 F 2 0 1 0 0单 片机 的 总线 系统 连 接 , 通 信控 制板 使

可 以通 过单 片机 总线 与 3 有线 传输 板进 行高 速数据 块

输 出端 口

通 信 , 两 块 E 1 0芯 片可 与 6块 有 线 传输 板 进行 用 P K3 高速 数据通 信 。

2 F F 存 储 器 阵列 的设 计 IO

本设 计 采用 了 自下 向上 的 层 次化 设 计 方法 , 底 在 层 设计 中 , 图形 编辑 输 入 法 设 计 双 向 F F 存 储 器 用 IO 模块 、 语 言 描述 输人 法 设计 了与 有 线传 输 板 接 口的 用 单 路 逻 辑 端 口和 与 通 信 控 制 板 上 C 0 1 0 0单 片 机 8 5F 2

旭

000) 3 0 6

厦 f 31 0 ,. 方 自动 控 制 技 术 研 究 所 , 原 - 6052 北 I 太

摘 要 : 绍 了 AL E 介 T RA 公 司 C L 器 件 E I 0芯 片 的特 点 , 用 M AX+p u P D P K3 利 lsⅡ开 发 软 件 在 E 1 0芯 片 上 设 计 了 一 个 P K3

接 口的多路 逻辑端 口等 3个 功能模 块 ; 在顶 层设计 中 ,

表 2 L M— I O D P F F — C存 储 器 读 写 操 作 逻 辑

直 接调 用 了 3 双 向 F F 存 储器模 块 、 个 单路 逻辑 个 IO 3 端 口和 一 个 多路 逻 辑 端 口, 过 逻 辑 组 合 组成 一 个 3 通 通 道 双 向 F F 存 储 器 阵列 , 现 了一个 C 0 1 0 0 IO 实 85F 2 单 片机 系统 与其 他 3个 C8 5 F 2 0 1 0 0单 片 机 系 统 之 间 的 总线 接 口, 于通 信 控制 板 与 3块有 线 传输 板 之 间 用 的实 时通 信 。

基于CPLD的单片机接口设计

基于CPLD的单片机接口设计作者:田开坤徐海霞来源:《现代电子技术》2008年第02期摘要:现在分离元件在很多电路设计中还在普遍使用,完成逻辑转换、地址译码、数据锁存等任务,在PLD技术相当成熟的今天,采用PLD代替传统分离元器件,将会极大地减小PCB尺寸,节约成本。

对CPLD器件和开发工具进行研究,提出一种单片机与CPLD总线接口方案。

运用该方案设计单片机系统实现A/D,D/A,LCD等多种外设的接口,电路简洁,并给出CPLD电路设计方案,总体电路原理图和关键程序代码。

关键词:CPLD;分离元件;PLD;EDA中图分类号:TP331.1 文献标识码:B 文章编号:1004-373X(2008)02-034-03Design of Single Chip Computer Interface Based on CPLDTIAN Kaikun,XU Haixia(Electrician and Electronics Experiment Center,Hubei NormalUniversity,Huangshi,435002,China)Abstract:Many circuit design still use separative components in nowadays,completes the logic to transform,the address decoding,the data lock saves and so on.Today the PLD technology has become more and more mature,using the PLD technology instead of tradational separative components not only reduce the PCB size,but also save the cost.This paper researches CPLD devices and the reference tools,proposes a bus interface between single chip computer and CPLD.The single chip computer system contain A/D,D/A,LCD and something else,adopting this way,making the circuit more easy and clear.This paper also gives CPLD circuit design scheme,circuit theory graphic and the main program code.Keywords:CPLD;separative components;PLD;EDA1 引言随着PLD(可编程器件)技术的成熟,应用越来越广泛。

单片机并行通信接口设计与实现方法

单片机并行通信接口设计与实现方法摘要:本文主要介绍了单片机并行通信接口的设计与实现方法。

首先简要介绍了单片机的基本概念和工作原理,然后详细分析了并行通信接口的设计要求和实现步骤,包括硬件设计和软件编程。

接着,本文提出了一种基于单片机的并行通信接口设计方案,并通过具体实例进行演示。

最后,对并行通信接口的优势和应用进行了总结和展望。

一、引言单片机作为一种微处理器,具有体积小、功率低、成本低等优点,被广泛应用于各种控制系统中。

在很多应用场景中,单片机需要与其他设备进行通信,因此通信接口的设计和实现显得尤为重要。

本文主要聚焦于单片机并行通信接口的设计与实现方法。

二、单片机基本概念和工作原理单片机是一种集成电路,主要由中央处理器、存储器和输入输出设备组成。

它通过执行预先编写的程序实现各种功能。

单片机的工作原理可以大致分为四个步骤:取指令、译码指令、执行指令和写回结果。

三、并行通信接口的设计要求并行通信接口是指同时传送多个二进制信息位的通信接口。

在设计并行通信接口时,需要考虑以下几个方面的要求:1. 数据传输速率要满足实际需求;2. 数据传输的可靠性要得到保证;3. 接口设计要简单、易于实现;4. 对外部设备的兼容性要好。

四、并行通信接口的实现步骤实现并行通信接口主要包括硬件设计和软件编程两个方面。

1. 硬件设计:硬件设计主要涉及以下几个方面:1.1 电平转换:由于单片机的工作电平与其他设备的工作电平可能不一致,因此需要进行电平转换;1.2 时钟同步:单片机与外部设备之间的通信需要一个共同的时钟信号来同步数据传输;1.3 数据传输线路:并行通信需要多条数据传输线路,传输的数据位数取决于实际需求;1.4 控制信号:控制信号用于控制数据的传输方向、时序等。

2. 软件编程:软件编程主要涉及以下几个方面:2.1 初始化:设置并行通信接口所需的控制寄存器等;2.2 数据传输:根据实际需求,编写相应的数据传输函数;2.3 异常处理:处理并行通信过程中的异常情况,保证通信的可靠性。

怎样使用CPLD实现DSP芯片与背板VME总线之间的高速数据传输连接

怎样使用CPLD实现DSP芯片与背板VME总线之间的高速数据传输连接1 引言CPLD是一种用户可以根据自行需要而自己能够设计构造其逻辑功能的数字集成电路系统,实现了硬件设计的软件化。

CPLD具有丰富的可编程I/O引脚,具有在系统可编程(In System programmability)、使用方便灵活的的特点;近年来,CPLD器件成本不断下降,集成密度、速度和性能大幅度提高,一个芯片就可以实现一个复杂的数字电路系统;再加上使用方便的开发工具,使用CPLD器件可以极大地缩短产品开发周期,给设计、修改带来很大方便。

CPLD成为一种可优化硬件电路设计且具竞争力的产品。

ALTERA 公司不仅提供大规模的CPLD 和FPGA 器件,同时也提供一套十分有特色的综合工具MAXPLU S- II,设计者既可以使用原理图输入,也可以使用文本输入方式,更可以二者混合输入。

从编译、综合、布线到仿真、下载一气呵成,十分方便。

TMS320C6713是TI公司在TMS320C6711的基础上推出的新一代浮点DSP芯片,它可以在255MHz的时钟频率下实现1800MIPS/1350MFLOPS的定点和浮点运算,极大程度上满足了高速数据采集与实时控制系统对信号处理速度的要求。

作为下位机使用时,它可通过主机口HPI与各种不同类型的上位机连接。

本文将给出如何使用ALTERA 公司的CPLD 器件EPM7128AE-144实现DSP的HPI口和背板的VME总线之间的连接方法。

2 TMS320C6713的HPI2.1 TMS320C6713HPI口的接口信号TMS320C6713的HPI口是一个16位宽的并行端口。

上位机掌管该端口的主控权,可通过HPI直接访问TMS320C6713的存储空间和外围设备。

表1总结了TMS320C6713HPI的接口信号的基本特征。

下面对它们的具体工作方式进行说明。

(1)HD[15-0]可以看作数据地址的共用总线,通过HD[15-0]传送的数据包括控制。

I2C总线通讯接口器件的CPLD实现

I2C总线通讯接口器件的CPLD实现I2C(IIC)总线是PHILIPS公司开发的一种简单、双向、二线制、同步串行总线串行总线。

它只需两根线(串行时钟线和串行数据线)即可在连接于总线上的器件之间传送信息。

该总线是高性能串行总线,具备多主机系统所需要的裁决和高低速设备同步等功能,应用极为广泛。

目前市场上虽然有专用IIC总线接口芯片,但是地址可选范围小、性能指标固定、功能单一、使用不方便。

根据IIC总线的电气特性及其通讯协议,采用ALTERA公司的FLEX10K 系列CPLD器件EPF10K10LC84-3可以方便地实现I2C(IIC)总线的通讯接口,且具有高速、易调试、可以灵活地实现地在线配置等优点,同时大大地减少了系统的开发周期。

1 IIC总线的数据传输规范I2C(IIC)总线主从机之间的一次数据传送称为一帧,由启动信号、地址码地址码、若干数据字节、应答位以及停止信号等组成。

通讯启动时,主动发送一个启动信号(当SCL线上是高电平时,SDA线上产生一个下降沿)、从机的地址码(8位)和读写信号;通讯停止时,主机发送一个停止信号(当SCL线上是高电平时,SDA线上产生一个上升沿)。

在数据传送过程中,当SCL线上是高电平时,必须保证SDA线上的数据稳定;传送一个字节的数据,必须由接收机发一个应答信号。

总线的传输码速率为100kbps (标准)~400kbps(高速)。

采用+5V电源供电时,输入电平规定为:VILmax=1.5V,VIHmin=3V;采用宽电源电压时,电平规定为:VILmax=1.5VDD,VIHmin=3VDD。

IIC总线的通讯过程。

2 ISP的逻辑实现基于IIC总线的数据传输规范,为完成IIC总线的数据发送与接收,采用ISP器件实现通讯接口的逻辑功能框图。

通过频选、控制、可控时钟可获得100kHz、200kHz、300kHz、400kHz 的时钟频率。

器件退出总线竞争总线竞争后,时钟线置高电平。

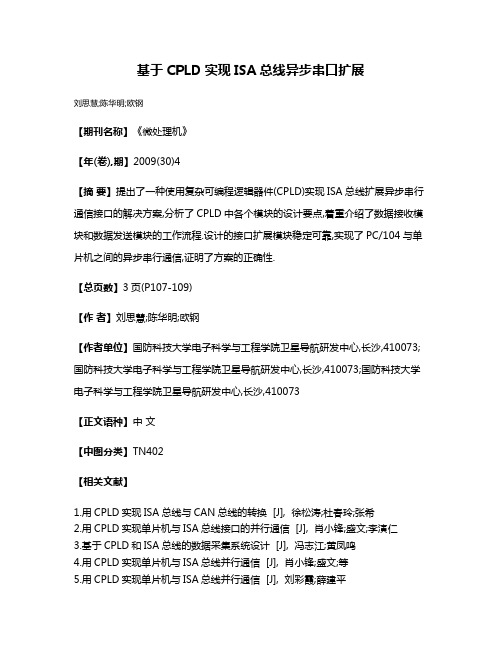

基于CPLD实现ISA总线异步串口扩展

基于CPLD实现ISA总线异步串口扩展

刘思慧;陈华明;欧钢

【期刊名称】《微处理机》

【年(卷),期】2009(30)4

【摘要】提出了一种使用复杂可编程逻辑器件(CPLD)实现ISA总线扩展异步串行通信接口的解决方案,分析了CPLD中各个模块的设计要点,着重介绍了数据接收模块和数据发送模块的工作流程.设计的接口扩展模块稳定可靠,实现了PC/104与单片机之间的异步串行通信,证明了方案的正确性.

【总页数】3页(P107-109)

【作者】刘思慧;陈华明;欧钢

【作者单位】国防科技大学电子科学与工程学院卫星导航研发中心,长沙,410073;国防科技大学电子科学与工程学院卫星导航研发中心,长沙,410073;国防科技大学电子科学与工程学院卫星导航研发中心,长沙,410073

【正文语种】中文

【中图分类】TN402

【相关文献】

1.用CPLD实现ISA总线与CAN总线的转换 [J], 徐松涛;杜春玲;张希

2.用CPLD实现单片机与ISA总线接口的并行通信 [J], 肖小锋;盛文;李演仁

3.基于CPLD和ISA总线的数据采集系统设计 [J], 冯志江;黄凤鸣

4.用CPLD实现单片机与ISA总线并行通信 [J], 肖小锋;盛文;等

5.用CPLD实现单片机与ISA总线并行通信 [J], 刘彩霞;薛建平

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

! 系统总体设计方案

用 "45’ 实 现 单 片 机 与 4"%-61#, 总 线 接 口 的 并 行 通 信 " 由 于 4"%-6 主 要 完 成 其 它 方 面 的 数 据 采 集 工 作 " 只是在空闲时才能接收单片机送来的数据"所以要求双 方通信的实时性很强"但数据量不是很大 # 因此在系统 设 计 中 " 单 片 机 用 中 断 方 式 接 收 数 据 " 4"%-6 采 用 查 询 方式接收数据# 系统设计方案如图 % 所示#

"45’ 器 件 成 本 不 断 下 降 " 集 成 密 度 $ 速 度 和 性 能 大 幅 度

提高" 一个芯片就可以实现一个复杂的数字电路系统% 再 加 上 使 用 方 便 的 开 发 工 具 " 使 用 "45’ 器 件 可 以 极 大 地缩短产品开发周期"给设计修改带来很大方便

L %.

# 本

文 以 ,53:/, 公 司 的 !,M*--- 系 列 为 例 " 实 现 !"#$% 单 片 机 与 4"%-61#, 总 线 接 口 的 并 行 通 信 # 采 用 这 种 通 信 方 式 " 数 据 传 输 准 确 高 速 " 在 %N!;O 晶 振 的 !"#$% 单 片 机 控 制 的 数 据 采 集 系 统 中 " 可 以 满 足 与 4"%-6 1#, 总 线 接 口 实 时 通 信 的 要 求 " 通 信 速 率 达 N--=G@P #

55&E $

! 通信软件设计

90&4" 是 基 于 <$7 总 线 的 # 在 系 统 软 件 设 计 中 要 防 止 地 址 冲 突 $ 90&4" 中 使 用 74 c7Z 地 址 位 来 表 示 < , 端 口 地 址 # 即 可 有 &45" 个 口 地 址 # 前 A&5 个 供 系 统 板 使 用 # 后 A&5 个 供 扩 充 插 槽 使 用 # 当 7Z_ 4 时 表 示 为 系 统 板 上 的 口 地 址 % 当 7Z _& 时 表 示 扩 充 插 槽 接 口 卡 上 的 口 地 址 35+ $ 因 为 本 设 计 中 采 用 保 留 的 口 地 址 554E 和 55&E # 保证不会发生地址冲突$

集成电路应用

用 ,-./ 实现单片机与 +0$ 总线接口的并行通信

武 汉 空 军 雷 达 学 院 二 系 新 装 备 维 修 教 研 室 ! 6U--%- " 肖 小 锋 盛 文 李 演 仁

要 ! 介 绍 了 用 ,53:/, 公 司 !,M*--- 系 列 "45’ 芯 片 实 现 单 片 机 与 4"%-61#, 总 线 接 口 之 间的并行通信! 给出了系统设计方法及程序源代码! 关 键 词 ! "45’ 摘

&8& &85 &8% &8" 90$;7;. </; 4

辑’状态机 和 真 值 表 #地 址 译 码 部 分 采 用 文 本 输 入方式充分体现了文本输入方式的优点$ 文本 输入内容如下&

$?C’.$<6/ 7LLJINN Y 9073Z==)+ [</9?;\ [</9?;\ [</9?;\ [</9?;\ [</9?;\ [-?;9?;\ [-?;9?;\ [-?;9?;\ [-?;9?;\ [-?;9?;\ [-?;9?;\ [-?;9?;\ [-?;9?;\

#3,3: 变 为 低 电 平 " 单 片 机 通 过 判 断 此 信 号 为 低 电 平 来

!"

集成电路应用

’34==!+ !"#$ %!" ! & " ’()**!+ 234**!+ , -./ 0#1 !" #$ %!" ! 5 " ’34**!+ 234**!+ , -./ 0#1 90’ 3 4 = = ! +

" 基 于 #$%&’()*++ 的 硬 件 实 现

,53:/, 公 司 的 "45’ 开 发 工 具 !,M S@ATP11 " 支 持

多种输入方式"给设计开发提供了极大的方便"因此本 系 统 采 用 !,M S@ATP11 进 行 设 计 # 系 统 的 主 体 部 分 用 原 理图输入方式"由于库中提供了现成的芯片"所以使用 很方便# 原理图输入部分如图 N 和图 U 所示# 图 N 主要 完 成 单 片 机 与 1#, 接 口 通 信 中 的 数 据 传 输 和 握 手 判 断 # 在图 N 中"各信号说明如下&

是 一 种 模 块 化 的 高 级 语 言 # 完 全 集 成 于 >7WX

>0?@: $;7;. 9:/ 90:’ 90@: ’ 0#1 9:/ >0?:’ ’ 0#1 2 2

!" #$ 5"" , &6 &7& &75 &7% &7"

QGUN << 系 统 中 # 特 别 适 合 于 描 述 复 杂 的 组 合 逻

’#8D0#: 信 号 有 效 ! 低 电 平 " # <-0E:’8 信 号

变 为 高 电 平 # 90&)" 可 以 读 写 数 据 $ 地 址 译 码 部 分 采 用 文 本 输 入 方 式 # 用 7#F ;.:7 公 司 的 硬 件 设 计 开 发 语 言 7E’# ! 7GHIJK

EKJLMKJI ’INOJPQHPRS #KSTUKTIV 实 现 $ 7E’#

当 !"R0/ 信 号 有 效 时 " 单 片 机 把 数 据 锁 存 于

*65#U*6 ! % ’ 中 " 此 时 4"#3,3: 变 为 高 电 平 % 4"%-6 用 #3,3: 信 号 选 通 *65#N66 来 判 断 数 据 位 4"’- 是 否 为 高

电 平 " 如 果 为 高 " 说 明 单 片 机 送 来 了 数 据 " 则 使 4"/’ 有 效 " 从 数 据 锁 存 器 *65#U*6 ! % ’ 中 取 走 数 据 " 此 时 4"V

$8$0#1 <$7 接 口 的 系 统 时 钟 信 号 $ 在 >0$ A& 与 90&)" 进 行 通 信 的 过 程 中 # ’#8D’ 信

号 一 直 有 效 ! 高 电 平 " # 在 信 号 $8$0#1 的 作 用 下 # 每 A 个 时 钟 周 期 ’.#78 信 号 有 效 一 次 # 即 为 高 电 平 $ 此 时

要 在 90&)" 的 <-0E:’8 处 插 入 等 待 周 期 $ 如 图 % 所 示 # 各信号说明如下&

<-0E:’8 ’#8D’ ’#8D01 ’#8D0#: ’.#78

用 来 使 <$7 接 口 等 待 A 个 时 钟 周 期 % 延时输入信号% 延时等待时钟信号% 等待清除信号 #为开始下一次送数周 期做准备% 延时 A 个时钟周期后的输出信号#作 为 ’#8D0#: 信 号 的 输 入 %

’#8 D’ ’#8D01

C 7

<-0E:’8

图 % 延时电路

90@: >0?:’ >0?@: V C.6</

判 定 90&)" 已 取 走 了 数 据 # 此 时 可 以 发 下 一 个 数 据 $ 当 90@: 信 号 有 效 时 # 90&)" 把 数 据 锁 存 于

!"#$%!" ! 5 " 中 # 此 时 </;) 变 为 低 电 平 % 单 片 机 产 生 外 部 中 断 # 使 >0?:’ 信 号 有 效 # 从 数 据 锁 存 器 !"#$%!%" ! 5 "

单片机的 Q 位双向数据总线%

1#, 接 口 的 Q 位 双 向 数 据 总 线 % 1#, 接 口 的 读 有 效 信 号 % 1#, 接 口 的 写 有 效 信 号 % 1#, 接 口 的 查 询 选 通 信 号 " 用 来 判 断 单

片机已写数据或读走数据% 单 片 机 用 此 查 询 1#, 接 口 已 取 走 数 据 % 单片机的读有效信号% 单片机的写有效信号% 单片机的外部中断信号#

1#, 总 线

并行通信

:#5"Q6 来 实 现 " 用 来 完 成 !"#$% 与 4"%-61#, 总 线 接

口之间的数据传输$状态查询及延时等待# 在 4"%-6 1#, 部 分 " 只 用 到 4"%-6 的 Q 位 数 据 总 线

ቤተ መጻሕፍቲ ባይዱ

"45’ ! ">?@ABC 4D>EDF??FGAB 5>EHI ’BJHIBK 是 一 种 复

/’ 0/ 123 -

延时等待 图 % 系统设计方案

在 单 片 机 部 分 " ’ L -))*. 是 数 据 总 线 " , L -))%$. 是 地 址 总 线 " /’ 和 0/ 分 别 是 读 写 信 号 线 " 123- 是 单 片 机 的 外部中断"当单片机的外部中断信号有效时"单片机接 收数据# 在 "45’ 部 分 " 用 一 片 !,M*--- 系 列 中 的 4!*%NQ