dsp第四章

《DSP系统设计及应用》第四章

22

4.4 指令简介

4.4.1 内存寻址方式 C3x系列支持 组寻址方式。 系列支持4 ‘C3x系列支持4组寻址方式。每种寻址方式又支持两种或两种以上 的寻址类型。 的寻址类型。 (1)通用指令寻址方式 指令中包括2个操作数(1 ,1目的 通用指令寻址方式: (1源 目的) (1)通用指令寻址方式:指令中包括2个操作数(1源,1目的) 寄存器寻址:操作数是CPU的寄存器。 CPU的寄存器 寄存器寻址:操作数是CPU的寄存器。 立即数寻址:操作数是16位或24位的立即数。 16位或24位的立即数 立即数寻址:操作数是16位或24位的立即数。 直接寻址:操作数是24位地址指向的内容, 24位地址是由 24位地址指向的内容 位地址是由8 直接寻址:操作数是24位地址指向的内容,这24位地址是由8位的数 据页指针和16位的操作数连接而成。 16位的操作数连接而成 据页指针和16位的操作数连接而成。 间接寻址:通过一个辅助寄存器指示出操作数的地址。 间接寻址:通过一个辅助寄存器指示出操作数的地址。 (2)三操作数指令寻址方式 指令中包括3个操作数(2 ,1目的 三操作数指令寻址方式: (2源 目的) (2)三操作数指令寻址方式:指令中包括3个操作数(2源,1目的) 。 寄存器寻址:同通用指令寻址方式中的寄存器寻址。 寄存器寻址:同通用指令寻址方式中的寄存器寻址。 间接寻址:同通用指令寻址方式中的间接寻址。 间接寻址:同通用指令寻址方式中的间接寻址。 (3)并行指令寻址方式 两条指令并行绝对地址的寻址方式。 并行指令寻址方式: (3)并行指令寻址方式:两条指令并行绝对地址的寻址方式。 寄存器寻址:操作数是增强精度寄存器。 寄存器寻址:操作数是增强精度寄存器。 间接寻址:同通用指令寻址方式中的间接寻址。 间接寻址:同通用指令寻址方式中的间接寻址。 (4)分枝指令寻址方式 根据操作数特定位不同值执行不同操作。 分枝指令寻址方式: (4)分枝指令寻址方式:根据操作数特定位不同值执行不同操作。 寄存器寻址。同通用指令寻址方式中的寄存器寻址。 寄存器寻址。同通用指令寻址方式中的寄存器寻址。 程序记数器相对寻址:在程序计数器指针的基础上加上16位或32 16位或32位 程序记数器相对寻址:在程序计数器指针的基础上加上16位或32位 的偏移量。 的偏移量。

第四章 DSP开发环境

CCS简介 简功能: 包含如下基本功能

1.可视化代码编辑界面。可编写C、汇编、.H文件、.cmd文件等。 可视化代码编辑界面。可编写C 汇编、.H文件、.cmd文件等。 文件 文件等 集成代码生成工具。如汇编器、 编译器、链接器等。 2.集成代码生成工具。如汇编器、C编译器、链接器等。 基本调试工具。跟踪、查看程序执行、存储器、寄存器等。 3.基本调试工具。跟踪、查看程序执行、存储器、寄存器等。 断点工具。 4.断点工具。 探针工具。用于算法仿真、数据监视等。 5.探针工具。用于算法仿真、数据监视等。 分析工具。评估代码执行的时钟数。 6.分析工具。评估代码执行的时钟数。 数据的图形显示工具。如绘制时域/频域波形、眼图、星座图等。 7.数据的图形显示工具。如绘制时域/频域波形、眼图、星座图等。 GEL工具 用户可以自行修改控制面板、菜单,方便直观修改变量,配置参数等。 工具。 8.GEL工具。用户可以自行修改控制面板、菜单,方便直观修改变量,配置参数等。 支持RTDX 实时数据交换)技术。可以在不中断系统运行的情况下,实现DSP RTDX( DSP与其 9.支持RTDX(实时数据交换)技术。可以在不中断系统运行的情况下,实现DSP与其 他应用程序的数据交换。 他应用程序的数据交换。 10.开放式Plug in技术 支持第三方的ActiveX插件( Plug- 技术, ActiveX插件 10.开放式Plug-in技术,支持第三方的ActiveX插件(一种支持软件组件网络交互的 工具),支持包括软仿真在内的各种仿真器(只需安装驱动)。 ),支持包括软仿真在内的各种仿真器 工具),支持包括软仿真在内的各种仿真器(只需安装驱动)。 11.提供DSP/BIOS工具。增强了对代码的实时分析、运行调度、资源管理的能力,减 11.提供DSP/BIOS工具。增强了对代码的实时分析、运行调度、资源管理的能力, DSP/BIOS工具 少了用户对硬件熟悉程度的依赖。 少了用户对硬件熟悉程度的依赖。 12.支持多DSP调试。 DSP调试 12.支持多DSP调试。

DSP第四章 TMS320C20X系列的寻址方式及汇编指令

LT *0+

执行指令前: ARP=1, (AR1)=100H,(AR0)=3 执行操作: 用AR1所指的数据存储器100H内 容装载暂时寄存器; 执行指令后: ARP=1,(AR1)=103H

⑤减去索引量

方法

举例

指令使用AR内容作

LT *0-

为数据存储器地址,

执行指令后AR内容 执行指令前:

自动减去ARO的内容。 ARP=1, (AR1)=100H,(AR0)=3

执行操作:

用AR1所指的数据存储器100H内

容装载暂时寄存器;

执行指令后:

ARP=1,(AR1)=FEH

⑥加上索引量,反向进位

方法

举例

指令使用AR内容作为 数据存储器地址,执 行指令后AR内容自动 加上AR0的内容,该 加法采用反向进位方 法。 注:主要用于FFT算 法

LT *BR0+

把AR0加到辅助寄存器中时,地址以位倒序的方 式产生,即进位是从左向右,而不是从右向左进位。

LTP ind [,ARn]

MAC MAC pma , dma

乘且累加

MAC pma, ind [ , ARn]

MACD MACD pma, dma

乘且累加,并将被寻址数据移至下一单元

MACD pma, ind [, ARn]

MPY MPY dma

MPY ind [, ARn]

MPYA/MPYS

累加前次乘积,再将TREG与被寻址数相乘

PAC PAC

PREG转入累加器ACC

SPH

存储PREG高16位,直接或间接寻址

SPL

存储PREG低16位,直接或间接寻址

例1:MAC

0FF00H,02H ;DP=6,地址300H~37FH,PM=0, CNF=1

DSP第4章快速付里叶变换FFT.

第四章快速付里叶变换(FFT) Fast Fourier Transforming第一节引言、快速付里叶变换FFT •有限反序列通过离散傅里叶变换(DFT)将其频域离散化成有限K序列•但其计算量太大(与N 的平方成正比),很难实时地处理问题,因此引出了快速傅里叶变换(FFT)・•FFT并不是一种新的变换形式,它只是DFT的一种快速算法•并且根据对序列分解与选取方法的不同而产生了FFT的多种算法.•FFT在离散傅里叶反变换、线性卷积和线性相关等方面也有重耍应用・。

二、FFT产生故事当时加文(Garwin)在自已的研究中极需要一个计算付里叶变换的快速方法。

他注意到图基(J.W.Turkey)iE 在写有关付里叶变换的文章,因此详细询问了图基关于计算付里叶变换的技术知识。

图基概括地対加文介绍了一种方法,它实质上就是后来的著名的库利(Cooley J.W)图基算法。

在加文的迫切要求下,库利很快设计出一个计算机程序o 1965年库利-图基在v计算数学〉、Mathematic of Computation 杂志上发表了著乞的“机器计算付里级数的一种算法”文章,提出一种快速计算DFT的方法和计算机程序-揭开了FFT发展史上的第一页,促使FFT算法产牛原因还有1967年至1968年间FFT的数字硬件制成,电子数字计算机的条件,使DFT的运算大简化了。

、本章主要内容•1 •立接计算DFT算法存在的问题及改进途径。

•2•多种DFT算法(时间抽取算法DIT算法,频率抽取算法DIF算法,线性调频Z变换即CZT 法)• 3.FFT的应用直接计算DFT算法存在的问题及改进逐径\直接计算DFT计算量•问题提出:设有限长序列x(n),非零值长度为N,计算对x(n)进行一次DFT 运算,共需多大的运算工作量?1 •比较DFT与IDFT之间的运算量N—1x(n) DFT > X 伙)=工上=0,1,…N -1n=0N-\X伙)u)n > x(n) = Y X伙)A2 = 0,1,・・・ N -1 k=0其中x(n)为复数,W严之G"也为复数所以DFT与IDFT二者计算量相同。

数字信号处理DSP第4章

k 0,1, , N 1

2

13

4.2 按时间抽取(DIT)的基2–FFT算法

将系数统一为 WNk 2 WN2k ,则可得

x[0]

N 4点

x[4]

DFT

G[0]

X [0]

G[1]

X [1]

x[2]

N 4点

WN0

x[6]

DFT

WN2

G[2]

1 G[3]

1

X [2] X [3]

x[1]

N 4点

X m1[i] WNr X m1[ j] , X m1[i] WNr X m1[ j]

m 1, 2 ,

每一个蝶形需要一次复数乘法和两次复数加法。

17

4.2 按时间抽取(DIT)的基2–FFT算法

N点的DIT-FFT计算量为

复数乘法:

1

N 2

log2

N

N 2

复数加法:

2

N 2

log2

N

N

例: 如果每次复数乘法需要100us,每次复数加法需要20us,来 计算N=1024点DFT,则需要

12

4.2 按时间抽取(DIT)的基2–FFT算法

同理

( N 4)1

( N 4)1

G[k] DFT[g[r]]

g[2l]WN2lk2

g[2l 1]WN(22l1)k

l 0

l 0

( N 4)1

( N 4)1

g[2l]WNlk 4 WNk 2

g[2l 1]WNlk 4 ,

l 0

l 0

k 0,1,

(3) WN0 WN4 WN8 WN12 WN16 WN20 WN24 WN28

或 WN4i i 0,1, 2, 3, 4, 5, 6, 7 (dm 1)

DSP教程4.TMS320C55x的指令系统

例4-12,@bitoffset用于对寄存器位的寻址。

(1)BSET @0,AC3

;CPU将AC3的位0置为1

例4-13,*ARn用于对寄存器位的寻址,设AR0=0。

(1)BSET *AR0,AC3

;CPU将AC3的位0置为1

11

4.1.7 I/O空间的寻址

Baddr Bitin BitOut

BORROW

CARRY

符号 Cmem cond CSR Cycles dst Dx kx Kx lx Lx

含义 系数间接寻址操作数 条件表述 单指令重复计数寄存器 指令执行的周期数 目的操作数:累加器,或辅助寄存器的低16位,或临时寄存器 X位长的数据地址

X位长的无符号常数

表4-5 循环寻址

指针 线性/循环 寻址配置位 支持主数据页 缓冲区首地址寄 缓冲区大小寄存 存器 器

AR0

AR1 AR2 AR3 AR4 AR5 AR6 AR7 CDP

ST2_55(0)=AR0LC

ST2_55(1)=AR1LC ST2_55(2)=AR2LC ST2_55(3)=AR3LC ST2_55(4)=AR4LC ST2_55(5)=AR5LC ST2_55(6)=AR6LC ST2_55(7)=AR7LC ST2_55(8)=CDPLC

符号 【】 40 含义 可选的项 若选择该项,则该指令执行时M40=1 累计器溢出状态位:ACOV0~ACOV3 累计器AC0~AC3 辅助寄存器:AR0~AR7 寄存器位地址 移进的位:TC2或CARRY 移出的位:TC2或CARRY CARRY位的补 进位位

16

ACOVx Acx,Acy,Acz, ACw ARx,ARy

DSP第四章6概论

1、变换原理 使数字滤波器的频率响应

与模拟滤波器的频率响应相似。

冲激响应不变法、阶跃响应不变法:时域模仿逼近 缺点是产生频率响应的混叠失真

:[,]

1

:

T

,

T

tg 1T 2

z es1T

tg 1T 2

sin 1T 2

cos 1T 2

j 1T

j 1T

e 2 e 2

2 j j 1T

c tg 1T 2

s

c

1 1

z z

1 1

z cs cs

2、变换常数c的选择

1)低频处有较确切的对应关系: 1

1

c

tg

1T 2

c

1T 2

c 2 T

2)某一特定频率严格相对应: c c

c

c tg

1cT 2

c tg c

2

c

cctg

Байду номын сангаас

c

2

特定频率处频率响应严格相等,可以较准确地 控制截止频率位置

4、优缺点

优点:避免了频率响应的混迭现象

c tg

2 s 平面与 z 平面为单值变换

0 0 0 0

缺点:除了零频率附近, 与 之间严重非线性

1)线性相位模拟滤波器 非线性相位数字滤波器

2)要求模拟滤波器的幅频响应为分段常数型,不 然会产生畸变

分段常数型模拟滤波器 经变换后仍为分段常数 型数字滤波器,但临界 频率点产生畸变

j 1T

e 2 e 2

2

j 1T

j 1T

s1T

s1T

s

j

e2

j 1T

e 2

j 1T

DSP原理及应用第四章

9

常用的汇编命令:

汇编命令 .title .end 作 用 .title "example.asm" 放在汇编语言源程序的最后 .text段是源程序正文。经汇编后,紧随.text后的是可执 行程序代码 有两种数据形式:.int和.word Table: .word 1,2,3,4 .word 8,6,4,2 表示在程序存储器标号为table开始的8个单元中存放初 始化数据1、2、3、4、8、6、4和2 .bss x,4表示在数据存储器中空出4个存储单元存放变 量x1,x2,x3和x4 .sect " vectors "定义向量表,紧随其后的是复位向量 和中断向量,名为vectors STACK .usect "STACK",10H在数据存储器中留出16 个单元作为堆栈区,名为STACK .def 举 例 紧跟其后的是用双引号括起的源程序名 结束汇编命令,汇编程序将忽略此后的任何源 语句,所以它应是程序的最后语句 紧跟其后的是汇编语言程序正文

分段的优点:在目标文件中将放置程 序、数据、变量的代码分开,便于在链 接时作为一个单独的部分分配存储器。 由于大多数系统都有好几种形式的存储 器,通过对各个段重新定位,可以使目 目标文件中的段与目标存 标存储器得到更为有效的利用。 储器之间的关系

17

2.外部符号的概念

外部符号 在一个模块中定义,可在另 一个模块中引用的符号。

25

段命令应用举例

汇编语言源程序: .data coeff .word 044h,055h,066h .bss buffer,8 prt .word 0456h .text add: LD 0Dh,A aloop:SUB #1,A BC aloop,AGEQ .data ivals .word 0CCh,0DDh,0EEh

DSP第四章

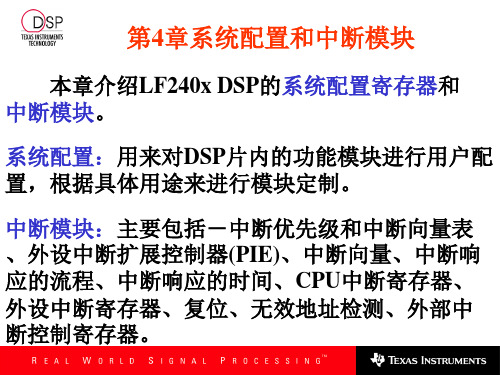

位8:保留 位7:ADC CLKEN,ADC模块时钟使能控制位 0-禁止ADC模块时钟(节能) 1-使能ADC模块时钟,且正常运行 位6:SCICLKEN,SCI模块时钟使能控制位 0-禁止SCI模块时钟(节能) 1-使能SCI模块时钟,且正常运行

位5:SPICLKEN, SPI模块时钟使能控制位 0-禁止SPI模块时钟(节能) 1-使能SPI模块时钟,且正常运行 位4:CANCLKEN, CAN模块时钟使能控制位 0-禁止CAN模块时钟(节能) 1-使能CAN模块时钟,且正常运行 位3:EVBCLKEN, EVB模块时钟使能控制位 0-禁止EVB模块时钟(节能) 1-使能EVB模块时钟,且正常运行

如这些引脚作I/O使用,则不使用输入时钟限定电路

位5:WD保护位,该位可用来禁止WD工作。该位 是-个只能清除的位,复位后=1。通过向该位写 1对其清0。

0-保护WD,防止WD被软件禁止。 1-复位时的默认值,能够通过软件禁止WD工作 位4:XMIF HI-Z。该位控制外部存储器接口信号 (XMIF)。 0-所有XMIF信号为正常驱动模式(非高阻态)。 1-所有XMIF信号处于高阻态。

外设中断请求寄存器和外设中断应答寄存器 都属于外设中断扩展模块用来向CPU产生INT1INT6中断请求的内部寄存器。这些寄存器用于测 试目的,编程时可以忽略。用户只能对其读。 1.外设中断向量寄存器(PIVR) 外设中断向量寄存器(PIVR)映射在数据存储 器空间中的地址为701Eh,该寄存器的16位V15- V0,为最近一次被应答的外设中断的地址向量。

中断请求(PIRQ)标志位一直保持到中断应答自动 清除或用软件将其清除。 在高层次中断,或逻辑运算的多个外设中断请求 INTn产生一个到CPU的中断请求,它是2个CPU时 钟脉冲宽的低电平脉冲。 当多个外设同时发出中断请求时,CPU总是响应 优先级高的中断请求。 注意:外设中断请求标志位是在CPU响应中断时 自动清除,即在高层次中断时清0,而不是在低层 次中断时,清0。

DSP_第四-八章演示文档

4. 不同滤波器对信号的作用

4.2 差分方程流图 1.二阶非递归滤波器节的级联 2.流图方程 3.级联流图的方程 4.递归差分方程 例题:求出下图所示流图的滤波器差分方程

例:写出下图所示脉冲响应的滤波器差分方程

5.4 数字图像滤波

1. 数字图像及其灰度 2. 数字图像的滤波 ห้องสมุดไป่ตู้. 低通滤波的文字

第六章 z变换 6.1 常用z变换表 z变换的性质 1.举例 5.3 滑动平均滤波器

1. 举例

5.4 数字图像滤波 1. 数字图像及其灰度 2. 数字图像的滤波 3. 低通滤波的文字

第七章 傅立叶变换与滤波器形状 7.3.2 幅度相应和相位相应 1. 脉冲通过梳状滤波器 2. ‘hello’通过梳状滤波器 例:把数字信号x[n]=0.5cos(pi/4*n)加到如下数字滤波器上,求输出信号。

例:数字频率为1.5弧度的余弦波通过滤波器,在此频率下,滤波器增益为21dB,相位差为86度,如果输入幅度为20,相位为12度,则输出幅度和相 位是多少。 对于n=10和n=20求出y[n]的值。

推断滤波器形状:H(z)=1/(z-0.45)

第八章 数字信号频谱 8.1 频谱的意义 1. 正弦波合成方波 2. 非周期数字信号 3. 非周期数字信号及其频谱

z 2 z cos() z 2 2 z cos 1

z sin( ) z 2 z cos 1

2

z 2 z cos() z 2 2 z cos 2

z sin() z 2 z cos 2

2

z变换的性质 性质 时间反转 线形 时移 序列 g[-n] ag[n]+bh[n] g[n-m]

DSP原理与应第四章.ppt

1.HPI与主机的连接

HCNTL0、

主机控制信号,与主机地址线

HCN或TL控1:制线连接,用来选择主机所要寻址的寄

存器。

HCNTL0 HCNTL1

功能说明

0

0

主机可以读/写HPIC寄存器。

主机可以读/写HPID寄存器。

0

1

每读1次,HPIA事后增1;

每写1次,HPIA事先增1。

1

0

主机可以读/写HPIA寄存器。 这个寄存器指向HPI存储器。

可以访问HPI RAM,而’C54x则配置为最小功耗

。 2021年2月25日

DSP原理及应用

4

第4章 TMS320C54x的片内外设、接口及应用

4.1 ’C54x的主机接口

HPI口可以支持主设备与’C54x之间的高速 数据传送。

在SAM工作方式时,若HPI每5个CLKOUT周 期传送一个字节,则主机的运行频率可达(fd×n)/5 。 f在d—H—OM’方C5式4x时的,C主LK机O可UT以频获率得;更高的速度。 即每5n—0n—s寻主址机一每个进字行节一(次即外16部0寻M址bp的s)周,期且数与,通 常 ’nC是543x(的或时4)钟。速度无关。

1.HPI与主机的连接

HPI与主机连接的信号名称和功能:

HD0~HD 双向并行三态数据总线,与主机数据总

7:

线相连。

当不传送数据(HDSx或HCS=1)或EMU1/OFF=0(切 断所有输出)时,HD7~HD0均处于高阻状态。

HCS: 片选信号,与主机地址线或控制线相连。

作为HPI的使能输入端,在每次寻址期间必须 为低电平,而两次寻址之间也可以停留在低电平。

第4章 TMS320C54x片内外设、接口及应用

DSP的开发环境第四章

TI DSP有那些开发工具?

TI公司为TMS320系统的集成与调试 所提供的工具包括:

软仿真器(Simulator)-------软件仿真器 DSP入门套件(DSK,DSP Starter Kit) 标准评估模块(EVM) 扩展开发系统XDS(eXtended Development System)---------硬件仿真器需软件配合使用 集成开发软件CCS(Code Composer Stdio)

归档器允许用户将一组文件归入一 个档案文件(库)。例如,将若干 个宏归入一个宏库,汇编器将搜索 这个库,并调用源文件中使用的宏。 也可以用归档器将一组目标文件收 入一个目标文件库,连接器将连接 库内的成员,并解决外部引用

DSP的开发环境第四章

交叉引用列表器 (Cross-Reference Lister)

连接器(Linker)

连接器的基本任务是将目标文件 连接在一起,产生可执行模块。连 接器可以接受的输入文件包括汇编 器产生的COFF目标文件、命令文件、 库文件、以及已部分连接好了的文 件。它所产生的可执行COFF目标模 块可以装入各种开发工具,或由 TMS320器件来执行

DSP的开发环境第四章

归档器(Archiver)

DSP的开发环境第四章

通用优化

优化转移/简化控制流 分析程序的转移情况,重新安排操作 顺序,消去转移或多余的条件

在循环中总是计算同样值的表达式, 移到循环外面

DSP的开发环境第四章

通用优化

优化循环相关变量,例如:

为数组元素设置下标的代码改为指 针增量的代码; 用计数器控制的循环写成块循环, 或使用高效的增/减量转移指令

DSP的开发环境第四章

软仿真器的性能在主机上执行 Nhomakorabea户的DSP程序

DSP教程 第四章_中断管理和复位

▲ STANDBY模式:如果在LPMCRl寄存器中被选中,所有信号(包括

XNMI)都能够将处理器从STANDBY模式唤醒,用户必须选择具体哪个信号唤醒 处理器。在唤醒处理器之前,要通过OSCCLK确认被选定的信号:OSCCLK的周 期数在LPMCR0寄存器当中确定。

D9

R/W-0

D8

R/W-0

CANRX SCIRXB SCIRXA C6TRIPC5TRIPC4TRIPC3TRIPC2TRIP

D7 D6

R/W-0

D5

R/W-0

D4

R/W-0

D3

R/W-0

D2

R/W-0

D1

R/W-0

D0

R/W-0

C1TRIP

R/W-0

T4CTRIP T3CTRIP T2CTRIP T1CTRIP

WDINT XNMI XINT1

低功耗方式控制1寄存器LPMCR1

第4章 中断管理和复位

七、片内外设的中断扩展

▲ PIE:外设中断扩展模块(the Peripheral Interrupt Expansion block)把许

多中断源多路复用成一个较小的中断输入集。

▲ 功能:PIE模块支持96个不同的中断,这些中断分成12个组,每个组有8个

第4章 中断管理和复位

三、非屏蔽中断

C28x非屏蔽中断包括: ▲ 软中断INTR和TRAP指令 ▲ 硬件中断NMI ▲ 非法指令陷阱 ▲ 硬件复位中断RS

INTR指令

可以通过INTR指令用标号INTl~INTl4、DLOGINT、 RTOSINT和NMI来对指令进行初始化。 ▲ INTl~INTl4、DLOGINT和RTOSINT。 ▲ NMI——一个非屏蔽中断,引脚上的硬件请求和用INTR指令引起的软

dsp第四章

MAC [R] Xmem,Ymem,src[,dst] ; src or[dst]=(Xmem)*(Ymem)+ (src), T=(Xmem) MAC #1k, src[,dst] ; dst=(T)*1k+(src)

MAC Smem, #1k,src[,dst]

; dst=(Smem)*1k+(src), T=(Smem)

(2)减法指令是将累加器的内容或另一个数据存储单元的内容与 一个16比特的值相减,并把结果放进累加器。 SUB Smem,src ;src=(src)-(Smem) SUB Smem,TS,src ;src=(src)-(Smem)<<TS SUB Smem,16,src[,dst] ;src or[,dst]=(src)-(Smem)<<16 SUB Smem [,SHIFT],src[,dst] ;src or[,dst]=(src)-(Smem)<<SHIFT SUB Xmem,SHFT,src ;src=(src)-(Xmem)<<SHFT SUB Xmem,Ymem,dst ;dst=(Xmem)<<16-(Ymem)<<16 SUB #1k [,SHFT],src[,dst] ;src or[,dst]=(src)-1k<<SHFT SUB #1k,16,src[,dst] ;src or[,dst]=(src)-1k<<16 SUB src[,SHIFT] [,dst] ; dst=(dst)-(src)<<SHIFT SUB src,ASM[,dst] ; src or[,dst]=(dst)-(src)<<ASM SUBB Smem,src ;src-Smem-C SUBC Smem,src ;if (src-Smem<<15)>=0 ;src= (src-Smem<<15) <<1+1 Else src=src<<! SUBS Smem,src ;src=src-uns(Smem)

DSP第4章

34

X (k )

nk x ( n ) W N n 0

N 1

N / 2 1

n 0

nk x ( n )W N

n N / 2

N 1

nk x ( n )W N

k X1 (k ) X 3 (k ) WN / 2 X 4 (k ) N k 0,1,..., 1 N k 4 X 1 (k 4 ) X 3 (k ) WN / 2 X 4 (k )

15

同理:

k X 2 (k ) X 5 (k ) WN N / 2 X 6 (k ) k 0,1,..., 1 N 4 k X ( k ) X ( k ) W X ( k ) 2 5 N /2 6 4

nk N

把长序列DFT 短序列DFT,从而减少其运算量。

FFT算法分类:

• 时间抽选法 DIT: Decimation-In-Time • 频率抽选法 DIF: Decimation-In-Frequency

8

二 、按时间抽选的基-2FFT算法

1、算法原理

N为2的整数幂的FFT算法称基-2FFT算法。 将序列x(n)按n的奇偶分成两组:

X 3 (k )

N / 4 1

l 0

lk lk x3 ( l )W N x ( l ) W 3 N /4 /4 l 0

1

k 0,1

0 X 3 (0) x3 (0)W20 W20 x3 (1) x(0) W N x(4) 0 1 0 X (1) x (0) W W x (1) x (0) W 3 2 2 3 N x (4) 3

第四章学习目标

第十一讲

dsp5000指导书 第四章

第4章定时器及硬件中断4.1定时器硬件结构原理TMS320VC5509 DSPs有两个独立20-bit的软件可编程通用减数计数定时器,可用于产生周期中断给CPU或给DMA控制器发送周期同步事件或给外部设备提供周期信号,也可以用于外部事件计数。

20-bit的通用定时器是减数计数器,它由两部分组成:4位预分频计数器(PSC)和16位主计数器(TIM),定时器结构框图如图4-1所示。

4-1通用定时器结构框图预分频计数器PSC由输入时钟驱动,可以是内部CPU时钟或外部时钟(当FUNC=11b时使用外部时钟,从TIN/TOUT引脚输入,当FUNC为其它值时使用内部CPU时钟),每输入一个时钟PSC减1。

每当PSC减到0,主计数器TIM减1,每当TIM 减到0,定时器给CPU发出一个中断请求TINT,一个同步事件TEVT给DMA控制器和一个输出到定时器引脚(如果FUNC=01b)。

定时器输出速率为:)1()1++=PRD TDDR TINT (输入时钟频率频率 式中: )1()1(++PRD TDDR >4预分频寄存器PRSC 由两部分组成:预分频周期寄存器TDDR 和预分频器PSC ,如图4-2所示;预分频器PSC 减到0时,当再有一个输入时钟输入时,预分频器PSC 从预分频周期寄存器TDDR 重新装载预分频器PSC ,当定时器设定为自动装载模式时(ARB=1)。

周期寄存器PRD 和计数器TIM 都为16位寄存器。

计数器TIM 减到0时, TIM 从PRD 重新装载,当定时器设定为自动装载模式时(ARB=1)。

定时器控制寄存器TCR 如图4-3所示,使用它的特定位可以实现对定时器进行配置、启动、停止、装载和重新装载等,表4-1是对定时器控制寄存器TCR 每位进行说明。

R=读 W=写 -n=复位值图4-3 定时器控制寄存器TCR定时器引脚功能模式合法转换如图4-4所示,FUNC 位的某些改变会产生一个错误并反映在ERRTIM 位,FUNC = 01b 到 FUNC = 00b 或 11b ,FUNC = 10b 到 FUNC = 00b 或 11b ,FUNC = 11b 到任意值都会产生一个错误,当ERRTIM = 1,复位DSP 并重新初始化定时器。

DSP原理及应用第四章

4.3.3 链接器对段的处理 链接器有2条伪指令支持上述任务:

● MEMORY伪指令——用来定义目标系统的存储 器配置空间,包括对存储器各部分命名,以及规定 它们的起始地址和长度。 ● SECTIONS伪指令——用来指定链接器将输入 段组合成输出段方式,以及输出段在存储器中的位 置,也可用于指定子段。 若未使用伪指令,则链接器将使用目标处理器 默认的方法将段放入存储空间。

DSP应用技术

第4章汇编语言程序开发工具

第4章 汇编语言程序开发工具

内容提要

可编程DSP芯片开发需要一套完整的软、硬件开 发工具。通常可分成代码生成工具和代码调试工具两 大类。 代码生成工具是指将高级语言或汇编语言编写的 DSP程序转换成可执行的DSP芯片目标代码的工具程 序,主要包括汇编器、链接器和C编译器以及一些辅 助工具程序等。 代码调试工具包括C/汇编语言源码调试器、仿真 器等。 本章主要介绍代码生成工具,包括’C54x软件开 发流程、汇编语言程序的编写、编辑、汇编和链接过 程、COFF段的一般概念、汇编器和链接器处理段的 方法以、程序的重定位及CCS等。

制作:段荣行 X

5

第4章 汇编语言程序开发工具

1. ’C54x应用软件开发流程

宏源文件 C源文件

开发过程的目的是产生一个可以由’C54x目标系 统执行的模块。

存档器 汇编 源文件 C编译器 宏库 汇编器 汇编 源文件 存档器 COFF 目标文件 建库工具

目标 文件库

链接器

运行时 支持库

调试工具 可执行的 COFF文件 HEX代码 转换工具

4.2 汇编语言程序的编辑、汇编和链接过程

. cmd 链接命 令文件

.asm 源文件 .obj 目标文件 .out 输出文件

DSP课件第四章-2资料

退出

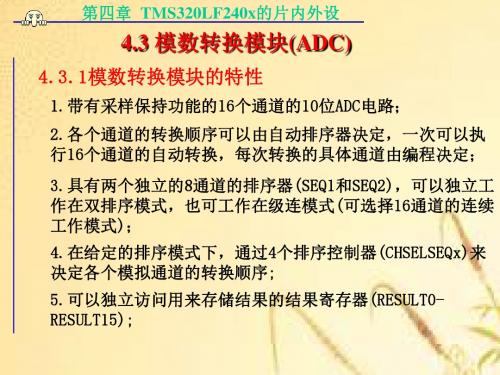

第四章 TMS320LF240x的片内外设 当触发源有效时,按照通道号在CHSELSEQx中的排列顺序, 依次对其进行A/D转换,直到转换完所设置的全部通道数目为 止。 当A/D转换正在进行时,新来的有效触发信号将被挂起,等 待当前转换结束后再启动新的转换。如果在新来的触发信号之 前已经有触发信号被挂起,则后到的触发信号会被丢弃。 1.连续转换方式 当ADC控制寄存器1(ADCTRL1)的CONTRUN位为1时,就设置 成连续转换方式。 当触发信号触发转换时,排序器就根据设置的顺序对所选 的通道进行转换。当最后一个通道转换完后,申请中断。如果 这时CONTRUN位仍为1,则排序器重新指向要转换的第一个通道, 自动进入新一轮的转换。因此用户必须想办法保证将前一轮的 转换结果及时取走,以避免被覆盖。 退出

退出

第四章 TMS320LF240x的片内外设

2.ADC控制寄存器2(ADCTRL2) :地址为70A1h

15 EVB SOC SEQ 7 14 RST SEQ1/ STRT CAL 6 RST SEQ2 13 SOC SEQ1 5 SOC SEQ2 12 SEQ1 BSY 4 11 INT ENA SEQ1(mode1) 3 10 INT ENA SEQ1(mode0 ) 2 INT ENA SEQ2(mode0 ) 9 INT FLAG SEQ1 1 8 EVA SOC SEQ1 0

退出

第四章 TMS320LF240x的片内外设 8通道的双排序和16通道的单排序的工作方式极为相似,为 描述方便,下表列出了SEQ1、SEQ2、SEQ的区别。

特性参数 转换触发源 最多可选择通道 数 触发转换优先级 SEQ1 EVA、软件、外引 脚 8 高 SEQ2 EVB、软件 8 低 SEQ EVA、EVB、软件、 外引脚 16 无

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2812的中断系统

• 清除T1PINT标志位: EvaRegs.EVAIFRA.bit.T1PINT = 1; • 中断屏蔽位使能 : EvaRegs.EVAIMRA.bit.T1PINT = 1;

16

2812的中断系统

(2)PIE级中断控制 ) 级中断控制

• 当外设产生中断事件,相关中断标志位置位,中 断使能位使能之后,外设就会把中断请求提交PIE 模块。PIE模块将96个外设和外部引脚的中断进 行了分组,每8个中断为1组,一共是12组,分别 是PIE1-PIE12。每个组的中断被多路汇集进入1 个CPU中断。

13

2812的中断系统

• 我们用具体的T1PINT来进行进一步的说明。当定时器T1 的计数器寄存器T1CNT计数到和T1周期寄存器T1PINT的 值匹配时(相等时),就产生了一个T1PINT事件,即T1 的周期中断。这时候,事件管理器EVA的中断标志寄存器 A(EVAIFRA)中的第7位T1PINT FLAG被置为1,这时 候如果EVA的中断屏蔽寄存器A(EVAIMRA)中的第7位 T1PINT的使能位是1,则EVA就会向PIE发出中断请求, 当然,如果该位的值是0,也就是该中断未被使能(被屏 蔽),则EVA不会向PIE发出中断请求,而且EVAIFRA中 T1PINT FLAG位将一直保持为1,除非通过程序将其清除。 需要注意的是,不管在什么情况下,外设寄存器中的中断 标志位都必须手工清除。

5

2812的中断系统

• 2812内部具有很多外设,每个外设又可以产生一 个或者多个中断请求,对于2812的CPU而言,它 没有足够的能力去同时处理所有外设的中断请求。 • 2812的CPU为了能够及时有效的处理好各个外设 的中断请求,特别设计了一个专门处理外设中断 的扩展模块(the Peripheral Interrupt Expansion block),叫做外设中断控制器PIE,它能够对各 种中断请求源(例如来自于外设或者其他外部引 脚的请求)做出判断以及相应的决策。

7

2812的中断系统

8

2812的中断系统

• ,黄色部分表示已经使用的中断,来看看 事件管理器EVA中定时器T1的周期中断 T1PINT在图中的哪里?我们可以看到 T1PINT在行号为INT2,列号为INTx.4的位 置,也就是说T1INT对应于INT2,是INT2 中的第四个中断。这样,我们就可以找到 所有外设中断的所属分组情况以及在该组 中的位置。

22

2812的中断系统

(3)CPU级 中断 和前面两级类似的,CPU也有标志寄存 器IFR和使能寄存器IER。当某一个外设中 断请求通过PIE发送到CPU时,CPU级中与 INTx相关的中断标志位就会被置位。

23

2812的中断系统

例如,T1的周期中断T1PINT的请求到 达CPU这边时,与其相关的INT2的标志位 就会被置位。这时候,该标志位就会被所 存在IFR中,这时候,CPU不会马上去执行 相应的中断,而是等待CPU使能IER寄存器 的相关位,如果IER中的相关位被置位了, 并且INTM的值为0,则中断就会被CPU响 应。在T1PINT的例子里,当IER的第2位即 INT2被置位,INTM为0,则CPU就会响应 定时器T1的周期中断。

10

2812的中断系统

11

2812的中断系统

• • • • IFR外设中断标志寄存器 IER外设中断使能寄存器 PIEACK外设中断状态寄存器 INTM全局中断使能

12

2812的中断系统

中断的执行过程

(1)外设级 假如在程序的执行过程中,某一个外设产生了一个中 断事件,那么在这个外设的某个寄存器中与该中断事件相 关的中断标志位(IF=Interrupt Flag)被置为1。此时,如 果该中断相应的中断使能位(IE=Interrupt Flag)已经被 置位,也就是为1,外设就会向PIE控制器发出一个中断请 求。但是该中断没有被使能(相应的使能位为0),那么 外设就不会向PIE发出中断请求,但是相应的中断标志位 会一直保持置位状态,一旦该中断被使能了,那么外设立 马会向PIE发出中断申请。

25

2812的中断系统

• 我们可以看到,与前两级中断不同,CPU 级的操作都是自动的,不管是中断标志位, 还是中断的使能位。

26

2812的中断系统

27

2812的中断系统

• 一个完整的 一个完整的T1PINT中断过程 中断过程

主程序部分 DINT; IER = 0x0000; IFR = 0x0000; EvaRegs.EVAIMRA.bit.T1PINT = 1; PieCtrlRegs.PIEIER2.bit.INTx4=1; IER |=M_INT2; EINT;

32

2812的中断系统

• 例子

33

30

2812的中断系统

两种中断程序定义方式

第一种方式: • 首先在程序开头声明中断子程序 interrupt void xxx(void); • 然后再将子程序入口地址赋给中断向量表中相应 的中断位 PieVectTable.TINT0 = &xxx;

31

2812的中断系统

第二种方式 直接在TI提供的中断子程序 DSP281x_DefaultIsr.c 中找到所需要的中断程 序进行修改。

19

2812的中断系统

总结一下,在PIE级需要我们手动的地方有:

• PIE中断的使能和屏蔽。需要使能某个外设中断, 就得将其相应组的使能寄存器PIEIERx的相应位 进行置位; • PIE应答寄存器PIEACK相关位的清除,以使得 CPU能够响应同组的其他中断。

20

281Байду номын сангаас的中断系统

• 清除PIE中与T1PINT相关的应答位: PieCtrl.PIEACK.bit.ACK2=1; • 使能PIE中断INT2.4(T1PINT中断): PieCtrlRegs.PIEIER2.all=M_INT4; //M_INT4=0x0008

24

2812的中断系统

• CPU接到了终端的请求,会将相应的IER和 IFR位进行清除,INTM被置位,就是不能 响应其他中断了,CPU向其他中断发出了 通知,正在忙,没空来处理你们的请求了。 然后,CPU会存储返回地址并自动保存相 关的信息,例如将正在处理的数据放入堆 栈等等,做好这些准备工作之后,CPU会 从PIE块中取出对应的中断向量ISR,从而 转去执行中断子程序。

2812的中断系统

1

中断的概念

• 同学们应该都知道中断这个词汇,任何一 款事件驱动型的CPU里面都应该会有中断, 因为中断就是为响应某种事件而存在的。 中断的灵活使用不仅可以实现我们想要实 现的功能,而且合理的中断安排可以提高 事件执行的效率,因此中断在DSP应用中 的地位是很重要的。

2

中断的概念

• 中断(Interrupt)是硬件和软件驱动事件, 它使得CPU暂停当前的主程序,并转而去 执行一个中断服务程序。

3

中断的概念

• 试举例一个电机控制系统中可能用到的中 断。

4

2812的中断系统

• 2812的CPU能 够支持一个不 可屏蔽中断NMI 和16个可屏蔽 16 的中断INT1INT14、 RTOSINT(实 时操作系统中 断)和 DLOGINT(数 据标志中断)

21

2812的中断系统

• 将PIE级的中断和外设级的中断相比较之后 发现,外设中断的中断标志位是需要手工 清除的,而PIE级的中断标志位都是自动置 位或者清除的。但是PIE多了一个PIEACK 寄存器,相当于一个同行的关卡,同一时 间只能放一个中断过去,只有等到这个中 断被响应,给关卡一个放行命令之后,才 能让同组的下一个中断过去,被CPU响应。

17

2812的中断系统

• 和外设级类似的,PIE控制器中的每个 组都会有一个中断标志寄存器PIEIFRx 和和中断使能寄存器PIEIERx。每个寄 存器的低8位对应于8个外设中断,高8 位保留。例如T1PINT对应于PIEIFR2 的第4位和PIEIER2的第4位。

18

2812的中断系统

• PIE模块是多路复用的,那么每一组同一时间应该只能是 一个中断被响应,PIE是怎么做到的呢?PIE还有一个 PIEACK寄存器,它的低12位分别对应着12个组,即 INT1-INT12,高位保留。假如T1的周期中断被响应了, 则PIEACK寄存器的第2位(对应于INT2)就会被置位, 并且一直保持直到手动清除这个标志位。当CPU在响应 T1PNT的时候,PIEACK的第2位一直是1,这时候如果 PIE2组内发生其他的外设中断,则暂时不会被PIE响应送 给CPU,必须等到PIEACK的第2位被复位之后。所以, 每个外设中断被响应之后,一定要对PIEACK的相关位进 行手动服务,否则同组内的其他中断都不会被响应。

14

2812的中断系统

总结一下外设级中断需要我们手动的地方有:

• 外设中断的使能,需要将与该中断相关的外设 寄存中的中断使能位置1; • 外设中断的屏蔽,需要将与该中断相关的外设 寄存中的中断使能位置0; • 外设中断标志位的清除,需要将与该中断相关 的外设寄存中的中断标志位置1;

15

9

2812的中断系统

• 2812的中断是3级中断机制,分别是外设级, PIE级以及CPU级,对于某一个具体的外设 中断请求,任意一级的不许可,CPU最终 都不会执行该外设中断。就像一个文件需 要三级领导批示一样,任意一级领导的不 同意,都不能被送至上一级领导,更不可 能得到最终的批准,中断机制的原理也是 如此。

6

2812的中断系统

• PIE可以支持96个不同的中断,这些中断分 成了12个组,每个组有8个中断,而且每个 组都被反馈到CPU内核的12条中断线中的 某一条上(INT1-INT12),我们平时用到 的所有的外设中断都被归入了这96个中断 中,被分布在不同的组里,这里其实也是 用到了多路复用的原理。