DSP 第四章 DMA

《DSP系统设计及应用》第四章

22

4.4 指令简介

4.4.1 内存寻址方式 C3x系列支持 组寻址方式。 系列支持4 ‘C3x系列支持4组寻址方式。每种寻址方式又支持两种或两种以上 的寻址类型。 的寻址类型。 (1)通用指令寻址方式 指令中包括2个操作数(1 ,1目的 通用指令寻址方式: (1源 目的) (1)通用指令寻址方式:指令中包括2个操作数(1源,1目的) 寄存器寻址:操作数是CPU的寄存器。 CPU的寄存器 寄存器寻址:操作数是CPU的寄存器。 立即数寻址:操作数是16位或24位的立即数。 16位或24位的立即数 立即数寻址:操作数是16位或24位的立即数。 直接寻址:操作数是24位地址指向的内容, 24位地址是由 24位地址指向的内容 位地址是由8 直接寻址:操作数是24位地址指向的内容,这24位地址是由8位的数 据页指针和16位的操作数连接而成。 16位的操作数连接而成 据页指针和16位的操作数连接而成。 间接寻址:通过一个辅助寄存器指示出操作数的地址。 间接寻址:通过一个辅助寄存器指示出操作数的地址。 (2)三操作数指令寻址方式 指令中包括3个操作数(2 ,1目的 三操作数指令寻址方式: (2源 目的) (2)三操作数指令寻址方式:指令中包括3个操作数(2源,1目的) 。 寄存器寻址:同通用指令寻址方式中的寄存器寻址。 寄存器寻址:同通用指令寻址方式中的寄存器寻址。 间接寻址:同通用指令寻址方式中的间接寻址。 间接寻址:同通用指令寻址方式中的间接寻址。 (3)并行指令寻址方式 两条指令并行绝对地址的寻址方式。 并行指令寻址方式: (3)并行指令寻址方式:两条指令并行绝对地址的寻址方式。 寄存器寻址:操作数是增强精度寄存器。 寄存器寻址:操作数是增强精度寄存器。 间接寻址:同通用指令寻址方式中的间接寻址。 间接寻址:同通用指令寻址方式中的间接寻址。 (4)分枝指令寻址方式 根据操作数特定位不同值执行不同操作。 分枝指令寻址方式: (4)分枝指令寻址方式:根据操作数特定位不同值执行不同操作。 寄存器寻址。同通用指令寻址方式中的寄存器寻址。 寄存器寻址。同通用指令寻址方式中的寄存器寻址。 程序记数器相对寻址:在程序计数器指针的基础上加上16位或32 16位或32位 程序记数器相对寻址:在程序计数器指针的基础上加上16位或32位 的偏移量。 的偏移量。

DSP第四章 TMS320C20X系列的寻址方式及汇编指令

LT *0+

执行指令前: ARP=1, (AR1)=100H,(AR0)=3 执行操作: 用AR1所指的数据存储器100H内 容装载暂时寄存器; 执行指令后: ARP=1,(AR1)=103H

⑤减去索引量

方法

举例

指令使用AR内容作

LT *0-

为数据存储器地址,

执行指令后AR内容 执行指令前:

自动减去ARO的内容。 ARP=1, (AR1)=100H,(AR0)=3

执行操作:

用AR1所指的数据存储器100H内

容装载暂时寄存器;

执行指令后:

ARP=1,(AR1)=FEH

⑥加上索引量,反向进位

方法

举例

指令使用AR内容作为 数据存储器地址,执 行指令后AR内容自动 加上AR0的内容,该 加法采用反向进位方 法。 注:主要用于FFT算 法

LT *BR0+

把AR0加到辅助寄存器中时,地址以位倒序的方 式产生,即进位是从左向右,而不是从右向左进位。

LTP ind [,ARn]

MAC MAC pma , dma

乘且累加

MAC pma, ind [ , ARn]

MACD MACD pma, dma

乘且累加,并将被寻址数据移至下一单元

MACD pma, ind [, ARn]

MPY MPY dma

MPY ind [, ARn]

MPYA/MPYS

累加前次乘积,再将TREG与被寻址数相乘

PAC PAC

PREG转入累加器ACC

SPH

存储PREG高16位,直接或间接寻址

SPL

存储PREG低16位,直接或间接寻址

例1:MAC

0FF00H,02H ;DP=6,地址300H~37FH,PM=0, CNF=1

第4章TMS320C54XDSP指令系统10PPT课件

57

中断指令同样可以改变程序指针PC的值,使程序从一个地址跳转 到另一个地址执行。但与调用指令一样,DSP在执行完中断服务程序 后要返回发生中断的地方继续执行原来的程序。当发生中断时,DSP 会置INTM为1,屏蔽所有可屏蔽中断,并在中断标志寄存器IFR中设 置相应的中断标志。

INTR指令使ST1的INTM位(bit11)置1关中断

14

算术运算类指令

’c54x的算术运算指令丰富,且运算能力强大。算术运 算指令用于完成加减乘除等算术运算。按照功能可将算术运算 类指令分为7组:

(1)加法指令(Add) (2)减法指令(Subtract) (3)乘法指令(Multiply) (4)乘加指令(Multiply-accumulate) (5)乘减指令(Multiply-subtract) (6)双字指令(32比特操作数) (7)专用指令(Application-specific)

25

举例:应用 SUBC DATA, A 计算( 8/2)

................................

stm #1001h , AR3 stm #1002h , AR4 ld #20h , DP st #0002h , 00h ld #0008h , A

rpt #15 subc 00h, A stl A,*AR3

;将相减的结果(高16位) ;存入1063地址单元

23

24

利用SUBC实现除法运算

在‘C54X中没有提供专门的除法指令, 一般有两种方法来完成除法。

一种是用乘法来代替,除以某个数相当于乘以其倒 数,所以先求出其倒数,然后相乘。这种方法适用于 除以一个常数。

另一种方法是使用SUBC(条件移位减法)指令, 重复16次减法操作完成一次除法运算。

DSP芯片中双通道DMA的研究与设计

作 ; W/ R - E = 0 时执行读操作 ,对源地址进行加/ 减 1 或者不变的操作 。DMA - E 为内部两通道选通信号 , DMA - E = 1 选通该通道 ,DMA - E = 0 关闭该通道 ; 全

局状态控制寄存器的四个控制位 DECSRC , INCSRC ,

DECDST 和 INCDST 分别表示源地址减 1 、源地址加

系统复位时 ,全局控制寄存器将被清零 ,系统默认

2 . 5 中断的设置和接收单元

CPU 优先 ; 环形仲裁 ,是指设置 CPU 和 DMA 通道的

3 中断的设置 : 对发给 DMA 的来自不同部件的 优先级使它们轮流存取 (但不对等) 。当它们在连续的

中断优先级排序已经在 CPU 中断控制中进行了设定 , 指令周期中发生访问冲突时 , CPU 具有较高的优先

收稿日期 :2007 - 06 - 23 作者简介 :魏建磊 (1982 - ) ,男 ,天津人 ,硕士研究生 ,研究方向为嵌 入式计算机体系结构 ;王 茹 ,硕士研究生 ,研究方向为嵌入式计算 机体系结构 ;导师 :沈绪榜 ,中国科学院院士 。

1 基本框架设计

如果 DMA 要将一数据块从存储器的一个区域传 输至另一个区域 ,应顺序执行以下过程 : CPU 首先对

DSP第四章6概论

1、变换原理 使数字滤波器的频率响应

与模拟滤波器的频率响应相似。

冲激响应不变法、阶跃响应不变法:时域模仿逼近 缺点是产生频率响应的混叠失真

:[,]

1

:

T

,

T

tg 1T 2

z es1T

tg 1T 2

sin 1T 2

cos 1T 2

j 1T

j 1T

e 2 e 2

2 j j 1T

c tg 1T 2

s

c

1 1

z z

1 1

z cs cs

2、变换常数c的选择

1)低频处有较确切的对应关系: 1

1

c

tg

1T 2

c

1T 2

c 2 T

2)某一特定频率严格相对应: c c

c

c tg

1cT 2

c tg c

2

c

cctg

Байду номын сангаас

c

2

特定频率处频率响应严格相等,可以较准确地 控制截止频率位置

4、优缺点

优点:避免了频率响应的混迭现象

c tg

2 s 平面与 z 平面为单值变换

0 0 0 0

缺点:除了零频率附近, 与 之间严重非线性

1)线性相位模拟滤波器 非线性相位数字滤波器

2)要求模拟滤波器的幅频响应为分段常数型,不 然会产生畸变

分段常数型模拟滤波器 经变换后仍为分段常数 型数字滤波器,但临界 频率点产生畸变

j 1T

e 2 e 2

2

j 1T

j 1T

s1T

s1T

s

j

e2

j 1T

e 2

j 1T

DSP原理与应用---第5章 dMAX

可以自己定义的。

22

FIFO 简答

• FIFO的深度:THE DEEPTH,它指的是FIFO可以存储多少个N位的 数据(如果宽度为N)。如一个8位的FIFO,若深度为8,它可以存储 8个8位的数据,深度为12 ,就可以存储12个8位的数据,FIFO的深度 可大可小,个人认为FIFO深度的计算并无一个固定的公式。在FIFO 实际工作中,其数据的满/空标志可以控制数据的继续写入或读出。 在一个具体的应用中也不可能由一些参数算数精确的所需FIFO深度为 多少,这在写速度大于读速度的理想状态下是可行的,但在实际中用 到的FIFO深度往往要大于计算值。一般来说根据电路的具体情况,在 兼顾系统性能和FIFO成本的情况下估算一个大概的宽度和深度就可以 了。而对于写速度慢于读速度的应用,FIFO的深度要根据读出的数据 结构和读出数据的由那些具体的要求来确定。

16

4.1.2 dMAX术语

• Table-based Multi-tap Delay Transfer-基于表格的多级延迟传输:许多语音算法以不连续 的方式访问大的延迟缓冲区。基于表格的多级延迟传输按照预先设定好的延迟偏移读 写FIFO缓冲区的数据单元。基于表格的多级延迟存储器访问,在连续级间有任意的间 隔(由延迟表定义),并且在一级内有可预见的连续间隔(一个级内延迟数据是连续的)。

• PendingEvent-未处理事件:未处理事件是指在DEFR中占据了位置但还没有被dMAX控 制器处理的事件。

• LongDataTransfer-长数据传输:当每个同步事件之后传输的数据单元的个数大于QTSL 时发生长数据传输。

13

4.1.2 dMAX术语

• One-Dimensional (1D) Transfer-一维传输:一组数据单元组成一个一维数据块,可以设 置数据单元的个数以及数据单元之间的间隔(space),指定的间隔与源地址和目的地址无 关,范围是-32768到32767个单元。

DSP原理与应第四章.ppt

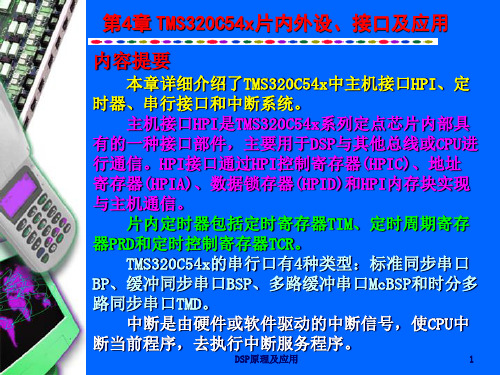

1.HPI与主机的连接

HCNTL0、

主机控制信号,与主机地址线

HCN或TL控1:制线连接,用来选择主机所要寻址的寄

存器。

HCNTL0 HCNTL1

功能说明

0

0

主机可以读/写HPIC寄存器。

主机可以读/写HPID寄存器。

0

1

每读1次,HPIA事后增1;

每写1次,HPIA事先增1。

1

0

主机可以读/写HPIA寄存器。 这个寄存器指向HPI存储器。

可以访问HPI RAM,而’C54x则配置为最小功耗

。 2021年2月25日

DSP原理及应用

4

第4章 TMS320C54x的片内外设、接口及应用

4.1 ’C54x的主机接口

HPI口可以支持主设备与’C54x之间的高速 数据传送。

在SAM工作方式时,若HPI每5个CLKOUT周 期传送一个字节,则主机的运行频率可达(fd×n)/5 。 f在d—H—OM’方C5式4x时的,C主LK机O可UT以频获率得;更高的速度。 即每5n—0n—s寻主址机一每个进字行节一(次即外16部0寻M址bp的s)周,期且数与,通 常 ’nC是543x(的或时4)钟。速度无关。

1.HPI与主机的连接

HPI与主机连接的信号名称和功能:

HD0~HD 双向并行三态数据总线,与主机数据总

7:

线相连。

当不传送数据(HDSx或HCS=1)或EMU1/OFF=0(切 断所有输出)时,HD7~HD0均处于高阻状态。

HCS: 片选信号,与主机地址线或控制线相连。

作为HPI的使能输入端,在每次寻址期间必须 为低电平,而两次寻址之间也可以停留在低电平。

第4章 TMS320C54x片内外设、接口及应用

DMA-DSP 542控制单板

DMA-DSP542 http:第一章DSP542控制單板(LH-091)----------------------------1 1-1單板簡介-----------------------------------------------------------11-2單板硬體功能介紹------------------------------------------------5第二章TLC320AC01功能簡介---------------------------------7 第三章TMS320C542與TLC320AC01之連結及控制-----11第四章以C54XCode Explorer環境代數語言實現TLC320 AC01控制實習------------------------------------------15 第五章以Code Composer Studio環境C語言實現TLC 320AC01控制實習------------------------------------21第一章DSP 542控制單板(LH-091)第1章D S P542控制單板(L H-091)1-1 單板簡介一般單晶片對類比訊號處理的精確度在於其ADC及DAC轉換介面及單晶的處理能力、借由本單板以高階之TI C54X系列DSP直接配合TI含有DAC及ADC轉換介面之TCL320AC01晶片而成的單板控制模組,來驗證C54X系列對類比訊號處理的能力及其測試,同時也可從單板上的預留測試座引用訊號線出來做控制測試,實為方便的專題製作工具。

至於單板上也擁有擴接長高科技出品之DSP LAB STN顯示模組及步進馬達模組和同為TI另一系列之AIC模組等等的強大功能。

而TLC320AC01與TLC32044晶片同為德州儀器(Texas Instrument簡稱TI)製造的ADC,DAC轉換的晶片,唯TLC320AC01於處理信號源的時候僅提供+5V單電源,而TLC32044須另提供-5V之雙電源,可由單板上的μ10電源調整IC取得。

DSP 第四章 DMA

4.3.3

DMA寄存器—目的地址寄存器

1) 24位寄存器 2)通过全局控制寄存器中的DECDST,INCDST实现地址修 改以选通相应固定地址的通信信道 3)只能对该寄存器进行写操作

4.3.3

DMA寄存器—传输计数寄存器

1) 24位寄存器,反映传输字数 2)系统复位时,传输计数寄存器置0 3)完成一次传输,计数器减1,计数值 为0时,若TCINT=1,触发DMA中断 4)当计数寄存器值为0时,DMA通道 没有被挂起,计数寄存器将继续减少到 负值;通道的传输最大字数1000000h (167.77216万次)

4.3.4

DMA中断及同步机制—同步机制

(1)同步禁止,当SYNC=00 时,不产生同步,只要没有 冲突,DMA就可随时执行 读、写操作,所有的中断被 忽略,但DMA中的中断使能 位不会发生改变。

4.3.4

DMA中断及同步机制—同步机制

(2)源同步,当SYNC=01 时,DMA 将与源同步。 DMA接收一次中断执行一次 读操作。之后从总体上禁止 所有的DMA中断。

4.3.4

DMA初始化和重构—同步机制

① 清除DMA的全局控制寄存器START位,使DMA处于保持状态。 ② 配置DMA全局控制寄存器(START=00)以及DMA源、目的寄存器和 传输计数器; ③ 启动DMA。

注意: ① 启动DMA之前应重新配置寄存器; ② DMA和CPU优先级关系,合理分配存储器; ③ 当应用中断同步时,必须确保每一个中断被接收,否则DMA将 无法完成一个数据块的传输; ④ 当执行串行口写/读数据时,需要读、写同步,以保证数据的 有效性; ⑤ DMA完成一组数据的传输后,设置DMA控制寄存器的TCINT位, IF寄存器的EDINT位必须置为1。

DSP原理 第四章

目的:掌握CPU各部分功能 目的:掌握CPU各部分功能 54系列CPU概述参看2-3节 54系列 系列CPU概述参看 概述参看2

本章主要内容

4-1 4-2 4-3 4-4 4-5 4-6 4-7 4-8 CPU状态与控制寄存器 ST CPU状态与控制寄存器----ST0,ST1 状态与控制寄存器---处理器模式状态寄存器PMST 处理器模式状态寄存器PMST 算术与逻辑运算单元— 算术与逻辑运算单元—ALU 累加器A 累加器A和B 滚筒移位寄存器— 滚筒移位寄存器—Barrel Shifter 乘法加法器 比较、选择与存储单元CSSU 比较、选择与存储单元CSSU 指数编码器 EXP

SST:存储饱和位。 SST:存储饱和位。 SST=1 当 SST=1时 , 累加器的结果在存入存储器时进行 饱和操作,而累加器值并不改变。 饱和操作,而累加器值并不改变。 存储器饱和操作: 存储器饱和操作: SXM=0 当 SXM=0 时 , 把 大 于 FFFFFFFFH 的 数 饱 和 成 FFFFFFFFH SXM=1 当 SXM=1 时 , 把 大 于 7 FFFFFFFH 的 数 饱 和 成 7 FFFFFFFH, 把 小 于 8 0 0 0 0 0 0 0 H 的 数 饱 和 成 FFFFFFFH, 80000000H 80000000H

1、ALU结构: ALU结构 结构: ALU输入 ALU输入 X端(DB0~15,S移位寄存器) 移位寄存器) Y端(CB0~15,A,B,T) ALU输出 ALU输出 A,B 2、OVA,OVB,TC,C 参看 CPU状态寄存器 OVA,OVB,TC, 参看CPU 状态寄存器 ST0 3、 OVM,C16参看CPU状态寄存器ST1 OVM, 参看CPU状态寄存器 状态寄存器ST 4、ZA/ZB 用于比较条件指令(A=0,B=0) 用于比较条件指令(A=0 B=0

DSP第四章

TC:复位值为1。 功能:测试/控制标志位。 由TC的状态(1或0)决定条件分支转 移指令、子程序调用以及返回指令是否 执行。

C:复位值为1。功能:进位位。 OVA:复位值为0。功能:累加器A的溢出标 志位。

OVB:复位值为0。功能:累加器B的溢 出标志位。

DP:复位值为0。 功能:数据存储器页指针。这9位字段与指令 字中的低7位结合在一起,形成一个16位直接 寻址存储器的地址。 选用数据页指针DP :ST1中的编辑方式位 CPL=0。 DP可加载。

图4-3 TMS20C542的结构框图

1. 算术逻辑运算单元(ALU):

ALU的输入: 16位、2个16位字、32位字、累加器A (B)输出的40位字数据。 符号位扩展: 16位-> 40位,ST1的SXM=0,高位添0; SXM=1,符号位扩展。

ALU的输出: 40位,送往累加器A或B。 溢出处理(ALU的饱和逻辑):

保存累加器的内容: 利 用 STH 、 STL 、 STLM 和 SACCD (条件,移位,存储)等指令或者用 并行存储指令,将累加器的内容存放 到数据存储器中。 若存储前移位: 右移时,AG和BG中的各数据位分别 移至AH和BH;左移时,AL和BL中的各 数据分别移至AH和BH,低位添0。

例如:累加器A=FF 4321 1234h,求执行带 移位的STH和STL指令后数据存储单元的 TEMP中的结果。 STH A, 8,TEMP ;A中的内容左移8 位后高位字存入TEMP,TEMP=2112h STH A,-8,TEMP ;A中的内容右移8位 后高位字存入TEMP,TEMP=FF43h STL A, 8,TEMP ;A中的内容左移8位 后低位字存入TEMP,TEMP=3400h STL A,-8,TEMP ;A中的内容右移8位 后低位字存入TEMP,TEMP=2112h

dsp5000指导书 第四章

第4章定时器及硬件中断4.1定时器硬件结构原理TMS320VC5509 DSPs有两个独立20-bit的软件可编程通用减数计数定时器,可用于产生周期中断给CPU或给DMA控制器发送周期同步事件或给外部设备提供周期信号,也可以用于外部事件计数。

20-bit的通用定时器是减数计数器,它由两部分组成:4位预分频计数器(PSC)和16位主计数器(TIM),定时器结构框图如图4-1所示。

4-1通用定时器结构框图预分频计数器PSC由输入时钟驱动,可以是内部CPU时钟或外部时钟(当FUNC=11b时使用外部时钟,从TIN/TOUT引脚输入,当FUNC为其它值时使用内部CPU时钟),每输入一个时钟PSC减1。

每当PSC减到0,主计数器TIM减1,每当TIM 减到0,定时器给CPU发出一个中断请求TINT,一个同步事件TEVT给DMA控制器和一个输出到定时器引脚(如果FUNC=01b)。

定时器输出速率为:)1()1++=PRD TDDR TINT (输入时钟频率频率 式中: )1()1(++PRD TDDR >4预分频寄存器PRSC 由两部分组成:预分频周期寄存器TDDR 和预分频器PSC ,如图4-2所示;预分频器PSC 减到0时,当再有一个输入时钟输入时,预分频器PSC 从预分频周期寄存器TDDR 重新装载预分频器PSC ,当定时器设定为自动装载模式时(ARB=1)。

周期寄存器PRD 和计数器TIM 都为16位寄存器。

计数器TIM 减到0时, TIM 从PRD 重新装载,当定时器设定为自动装载模式时(ARB=1)。

定时器控制寄存器TCR 如图4-3所示,使用它的特定位可以实现对定时器进行配置、启动、停止、装载和重新装载等,表4-1是对定时器控制寄存器TCR 每位进行说明。

R=读 W=写 -n=复位值图4-3 定时器控制寄存器TCR定时器引脚功能模式合法转换如图4-4所示,FUNC 位的某些改变会产生一个错误并反映在ERRTIM 位,FUNC = 01b 到 FUNC = 00b 或 11b ,FUNC = 10b 到 FUNC = 00b 或 11b ,FUNC = 11b 到任意值都会产生一个错误,当ERRTIM = 1,复位DSP 并重新初始化定时器。

第4章 实验6-1 利用DSP实现信号滤波-DMA传输

DSP应用课程设计

直接存储器访问DMA寄存器

有2个全局寄存器影响所有通道: 全局控制寄存器(DMAGCR)和全局超时控制寄存器(DMAGTC C5502有6个可独立编程的DMA通道:DMA0~DMA5

每个DMA通道受各自的16个16位寄存器控制: ① DMACCR: 通道控制寄存器 ② DMACICR:中断控制寄存器 ③ DMACSR: 状态寄存器 ④ DMACSDP:源和目的参数 ⑤ DMACSSAL:源起始地址(低部分) ⑥ DMACSSAU:源起始地址(高部分)

25

北京交通大学 国家工科电工电子教学基地

DSP应用课程设计

本滤波实验DMA使用情况(续)

数据采集: A/D 转换的数据按 McBSP1 的设置被送到 DSP 内部接 收寄存器DRR11中,再由DMA通道4将DRR11中的数据读 到指定数据存储区 gBufferRcvPing 和gBufferRcvPong

14

北京交通大学 国家工科电工电子教学基地

DSP应用课程设计

PRIO[6]:DMA通道优先级。

0:优先级低,1:优先级高

SYNC[4:0]:同步控制位。 00000b:DMA无同步事件(缺省); 00101b:DMA与McBSP1接收事件同步; 00110b:DMA与McBSP1发送事件同步。 (接收00101b,发送110b)

6

北京交通大学 国家工科电工电子教学基地

DSP应用课程设计

直接存储器访问DMA寄存器(续)

⑦ ⑧ ⑨ ⑩ 11 12 13 14 15 16

7

DMACDSAL:目的起始地址(低部分) DMACDSAU:目的起始地址(高部分) DMACEN: 元素数目寄存器 DMACFN: 帧数目寄存器 DMACSEI: 源元素索引寄存器 DMACSFI: 源帧索引寄存器 DMACDEI: 目的元素索引寄存器 DMACDFI: 目的帧索引寄存器 DMACSAC: 源地址计数寄存器 DMACDAC: 目的地址计数寄存器

DSP课件第四章-2资料

退出

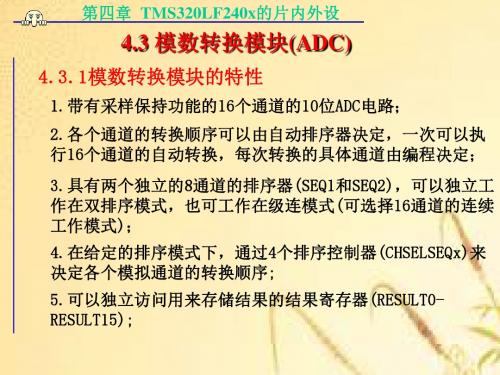

第四章 TMS320LF240x的片内外设 当触发源有效时,按照通道号在CHSELSEQx中的排列顺序, 依次对其进行A/D转换,直到转换完所设置的全部通道数目为 止。 当A/D转换正在进行时,新来的有效触发信号将被挂起,等 待当前转换结束后再启动新的转换。如果在新来的触发信号之 前已经有触发信号被挂起,则后到的触发信号会被丢弃。 1.连续转换方式 当ADC控制寄存器1(ADCTRL1)的CONTRUN位为1时,就设置 成连续转换方式。 当触发信号触发转换时,排序器就根据设置的顺序对所选 的通道进行转换。当最后一个通道转换完后,申请中断。如果 这时CONTRUN位仍为1,则排序器重新指向要转换的第一个通道, 自动进入新一轮的转换。因此用户必须想办法保证将前一轮的 转换结果及时取走,以避免被覆盖。 退出

退出

第四章 TMS320LF240x的片内外设

2.ADC控制寄存器2(ADCTRL2) :地址为70A1h

15 EVB SOC SEQ 7 14 RST SEQ1/ STRT CAL 6 RST SEQ2 13 SOC SEQ1 5 SOC SEQ2 12 SEQ1 BSY 4 11 INT ENA SEQ1(mode1) 3 10 INT ENA SEQ1(mode0 ) 2 INT ENA SEQ2(mode0 ) 9 INT FLAG SEQ1 1 8 EVA SOC SEQ1 0

退出

第四章 TMS320LF240x的片内外设 8通道的双排序和16通道的单排序的工作方式极为相似,为 描述方便,下表列出了SEQ1、SEQ2、SEQ的区别。

特性参数 转换触发源 最多可选择通道 数 触发转换优先级 SEQ1 EVA、软件、外引 脚 8 高 SEQ2 EVB、软件 8 低 SEQ EVA、EVB、软件、 外引脚 16 无

DSP原理及应用课后答案

第二章3、处理器工作方式状态寄存器PMST 中的MP/MC、OVLY 和DROM 三个状态位对C54x的存储空间结构各有何影响?当OVLY= 0 时,程序存储空间不使用内部RAM。

当OVLY= 1 时,程序存储空间使用内部RAM。

内部RAM 同时被映射到程序存储空间和数据存储空间。

当MP/ MC=0 时,4000H~EFFFH 程序存储空间定义为外部存储器;F000H~FEFFH 程序存储空间定义为内部ROM;当MP/ MC=1 时,4000H~FFFFH 程序存储空间定义为外部存储。

DROM=0:0000H~3FFFH——内部RAM ;4000H~FFFFH——外部存储器;DROM=1 :0000H~3FFFH——内部RAM;4000H~EFFFH——外部存储器;F000H~FEFFH——片内ROM;FF00H~FFFFH——保留。

4 、TMS320C54x 芯片的片内外设主要包括哪些电路?①通用I/O 引脚②定时器③时钟发生器④主机接口HPI⑤串行通信接口⑥软件可编程等待状态发生器⑦可编程分区转换逻辑5、TMS320C54x 芯片的流水线操作共有多少个操作阶段?每个阶段执行什么任务?完成一条指令都需要哪些操作周期?六个操作阶段:①预取指P;将PC 中的内容加载PAB ②取指F; 将读取到的指令字加载PB③译码D; 若需要,数据1 读地址加载DAB;若需要,数据2 读地址加载CAB;修正辅助寄存器和堆栈指针④寻址A; 数据1 加载DB;数据2 加载CB;若需要,数据3 写地址加载EAB⑤读数R; 数据1 加载DB;数据2 加载CB;若需要,数据3 写地址加载EAB;⑥执行X。

执行指令,写数据加载EB。

6、TMS320C54x 芯片的流水线冲突是怎样产生的?有哪些方法可以避免流水线冲突?答:’C54x 的流水线结构,允许多条指令同时利用CPU 的内部资源。

由于CPU 的资源有限,当多于一个流水线上的指令同时访问同一资源时,可能产生时序冲突。

DSP第四章TMS320LF240x的数据寻址方式ppt课件

(1)设置数据页面

将当前数据页面〔0~511〕装入DP。可通过LDP指令或其他 能向ST0装入值的任意指令来装载DP。LDP指令仅加载DP而不 影响ST0的其他位,并明确指出装入的DP值。

例:LDP #32 ;初始化数据页面指针

(2)设置偏移量

提供7位偏移量作为指令的操作数。

例:ADD 1h 到累加器

在直接寻址方式中,偏移量是指令中的操作 数,指出某个页面中的某个地址单元,是一个7位 的立即数,是64K数据存储器地址的低7位,DP 值是数据存储器地址的高9位,用来确定数据页, 两者共同形成16位的数据存储器地址。

指令寄存器IR的低7位提供偏移量,指令寄 存器的内容是要执行的下条指令的操作码。指令 寄存器中,“8MSBs〞是指令类型,同时包括指

直接寻址方式下的数据格式

状态寄存器ST0

D15~D13 D12 D11 D10 D9 D8~D0 ARP OV OVM 1 INTM 数据页面指针DP

指令寄存器IR

D15~D8

D7

8MSBs

0

D6~D0 7MSBs

数据存储器地址

D15~D7 页面〔9MSBs)

D6~D0 偏移量〔7MSBs)

使用直接寻址方式的步骤

立即寻址方式,就是指令中的操作数是常数。

两种立即寻址方式:短立即寻址和长立即寻 址。短立即寻址,指令可指定8、9或13位的常数 做操作数,指令只需单个指令字,操作数包含在 这个指令字中。长立即寻址,指令可指定16位的 常数做操作数,需要2个指令字,该常数为第2个 指令字。

立即数寻址指令中在立即操作数前加一个 “#”号,来表示立即数。

*0*0-,ARn *0+ *0+,ARn *BR0+ *BR0+,ARn

《DSP原理》教学大纲(精)

《DSP原理》教学大纲一、课程基本信息1、课程代码:MI3152、课程名称:DSP原理/ Principle of digital signal processors3、学时/学分:18学时/1学分4、先修课程:信号与系统、微机原理、电子技术基础5、面向对象:电气信息类专业6、开课院(系)、教研室:电子信息与电气工程学院信息检测与仪器系7、教材、教学参考书:《数字信号处理》胡广书,清华大学出版社2001《TMS320C6000 USER’S GUIDE》《TMS320C6000DSP原理及应用》,电子工业出版社2001。

二、课程的性质和任务本课程属于电子信息类本科高年级的专业选修课程。

作为扩大知识面,了解最新的DSP技术的发展趋势以及开发流程。

数字信号处理作为信号和信息处理的一个分支学科,已渗透到科学研究、技术开发、工业生产、国防和国民经济的各个领域。

自70年代末80年代初DSP(数字信号处理)芯片诞生以来,数字信号处理系统的运算速度得到了极大的改善,其实时性已接近甚至超过模拟信号处理系统,DSP芯片,也称数字信号处理器,是一种特别适合进行数字信号处理运算的微处理器。

DSP芯片的出现和发展,促进数字信号处理技术的提高,许多新系统、新算法应运而生,其应用领域不断拓展。

目前,DSP芯片已广泛应用于通信、自动控制、航天航空、军事、医疗等领域。

因此,学习和掌握DSP芯片的基本原理和开发流程,对于将来从事电子信息类工作的工科本科生来说是必不可少的。

通过该门课程的学习,期望学生能了解DSP技术的最新发展,了解其与单片机及通用微机处理器的不同,掌握某些特定的DSP芯片的开发流程和方法,扩展学生的知识面,提高学生快速解决问题的能力。

通过布置相关的上机实验和文献综述,要求学生初步了解TI公司的TMS320系列DSP的选型思路、开发流程等理论和方法。

三、课程的教学内容和要求《DSP原理》的教学内容分为五部分,对不同的内容提出不同的教学要求。

DSP中DMA操作的无阻塞请求实现

DSP中DMA操作的无阻塞请求实现DSP中DMA操作的无阻塞请求实现DMA在DSP应用中至关重要,本文给出了DMA操作非阻塞的请求方法,针对TMS320C620x,实现了与CSL中DAT接口一致的驱动模块QDAT,并指出了EDMA相关的高级特征。

在DSP中,DMA控制器实际是一个外设,与其他集成的串口、主机接口、片外内存接口等都在系统外设总线上,也与其他外设一样有一组相关的控制/状态/数据寄存器,CPU可以访问。

非常重要的一点是,DMA通道能够用于内存之间的数据传送。

这里内存都是统一编址的,包括:片上内存,程序和数据分立;接在EMIF上的片外内存,如SDRAM;外设的寄存器也都是内存映射的(memory-mapped),所以DMA通道也可以用于外设和内存之间,进行外设数据接收与发送。

在DSP的处理模型中,所有数据应位于片上供CPU处理,不鼓励CPU直接访问片外数据,因为CPU访问片外资源的时间较长,周期数也不确定,对于实时性和确定性不利。

片上内存有时也能够配置成为缓存(cache),缓存控制器会根据一定策略、使用DMA方式切换片外的数据进出缓存,最终使得用户能够在片上访问数据,这个过程对用户是透明的。

正因为缓存的机制是透明的,所以也是很难控制的。

比如,一段调用频率很高的代码很可能被不常用的部分清出缓存,因为它们映射相同,但随后又很快被调入,这样会造成局部的效率降低。

所以,如果能够明确掌握程序流或数据流的运转特征,不使用缓存模式,用户通过DMA 进行自定义的调度,可能提高效率。

有的处理器不具备缓存控制器,不支持片上内存作为缓存,如C6205的片上数据内存就不能够配置为缓存,所以主动使用DMA移动数据不可避免。

DSP的DMA功能一般也都较为强大,TI C6000系列的DMA通道支持1D-1D、1D-2D、2D-1D 以及常用的2D-2D数据传送,对DMA的合理使用可能替代相当的编程效果,如排序、采样或裁剪。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(6)DMA 传输计数方式:Bit 10

TC=0,计数器减为0,不停止DMA传输;为1,停止DMA传输 (7)DMA 传输计数中断:Bit 11

TCINT=0,传输结束后,DMA中断无效;为1,传输结束后, 启动DMA中断

4.3.3

DMA寄存器—源地址寄存器

1) 24位寄存器 2)通过全局控制寄存器中的DECSRC,INCSRC实现地 址修改以选通相应固定地址的通信信道 3)只能对该寄存器进行读操作

4.3.4

DMA初始化和重构—同步机制

① 清除DMA的全局控制寄存器START位,使DMA处于保持状态。 ② 配置DMA全局控制寄存器(START=00)以及DMA源、目的寄存器和 传输计数器; ③ 启动DMA。

注意: ① 启动DMA之前应重新配置寄存器; ② DMA和CPU优先级关系,合理分配存储器; ③ 当应用中断同步时,必须确保每一个中断被接收,否则DMA将 无法完成一个数据块的传输; ④ 当执行串行口写/读数据时,需要读、写同步,以保证数据的 有效性; ⑤ DMA完成一组数据的传输后,设置DMA控制寄存器的TCINT位, IF寄存器的EDINT位必须置为1。

4.3.3

DMA寄存器—全局控制寄存器

DMA通道控制寄存器 全局控制寄存器控制DMA的操作并反映DMA在每一个周期 内的变化状态。通过对全局控制器的特殊位的操作能够使得 源地址和目的地址增加、减少或者同步。系统复位时,DMA 控制寄存器的所有位都置0。

位 0-1 2-3 4 5 6 7 8-9 10 11 12-31

(3) DMA的字传输 读操作,DMA通道从源地址寄存器中读取一个字,把它写入DMA 通道的临时寄存器中。读操作后,源地址寄存器是否增加、减少或 保持不变取决于DMA全局控制寄存器的INCSRC或DECSRC位的设置。 写操作,DMA将临时寄存器中的值写入到目的地址寄存器指向的 目的地址。写操作后,目的地址寄存器增加减少或保持不变取决于 DMA全局控制寄存器的INCDRC或DECDRC位的设置。

外部或内部存储器 DMA通道 临时寄存器 由DMA源地址寄存 器指向存储器 外部或内部存储器 由DMA目的地址 寄存器指向存储器

每次数据写入时,传输计数器的值减少。当传输计数器减至0时 块传输停止,最后一次传输的写操作完成后,DMA通道设置DMA控制 寄存器的传输计数器中断(TCINT)标志。 数据块传输完后,DMA控制器可以通过编程实现以下事件: ★停止传输,直到重新编程(TC=1),设置传输计数器 ★继续传输数据(TC=0) ★产生一个中断信号告知CPU块传输已经完成(TCINT=1)

例:利用DMA通道,将地址809800H开始的5个数据转存到地址809900H开始的地 址中,传输完向CPU发送一个中断。

分析: 全局寄存器的复位值: 0C50H 源地址寄存器:809800H 目的地址寄存器:809900H 传输寄存器:5 寄存器地址:808000H,808004H,808006H, 808008H 中断允许:IE=400H 中断相应:ST=2000H (GIE=‘1’)

(1)START : Bit 0 1 功能:DMA开始控制位,保证安全退出DMA操作,不至于丢 失数据。 00 DMA完成当前正在进行的操作,禁止任何数据再次被读 入,取消所有悬挂的读写操作,进入复位,以便开始新的执行 任务 01 10 DMA保持,完成当前读、写后,不再进行任何操作 如果DMA的传输已经开始,则完成当前操作(读或写); 如果传输还没有进行,则停止当前操作 11 DMA从复位状态或先前状态开始启动

(2)STAT :Bit 2 3 功能:DMA状态位,显示DMA在每一个机器周期内的变化状态 00 复位状态值,DMA在多次传输过程中处于保持。DMA is being held between DMA transfer (between a write and a read) 01 DMA在当前执行过程中(读、写)保持, DMA is being held in the middle of a DMA transfer (between a read and a write) 10 保留

DMA 小结

1 DMA寄存器 DMA寄存器的位置 DMA全局控制寄存器的结构 DMA的初始化和启动设置 目的、源地址寄存器与传输寄存器间的关系 2 DMA的同步方式 无同步,源同步,目的同步,源和目的同步 3 DMA的操作过程 4 DMA的应用

.data 化过了,在程序中为了处理中断,只对 ST和IE进行了初始化)。 DMA .word 808000h ; DMA全局控制寄存器地址 RESET .word 0C40h ; DMA全局控制寄存器复位初始化值 CONTROL .word 0C43h ; DMA全局控制寄存器初始化 SOURCE .word ZERO ; 数据源地址DATA SOURCE ADDRESS DESTIN . word ARRAY ; 数据的目的地址 COUNT .word 128 ; 传输字的数目 .text START: LDP DMA ;装载数据页指针 LDI @DMA ,AR0 ;指向DMA全局控制寄存器 LDI @RESET,R0 ;复位DMA STI R0,*AR0 LDI @SOURCE,R0 ;初始化DMA源地址寄存器 STI R0,*+AR0(4) LDI @DESTIN,R0 ;初始化DMA目的地址寄存器 STI R0, *+AR0(6) LDI @COUNT,R0 ;初始化DMA传输计数器寄存器 STI R0,*+AR0(8) OR 400h,IE ;使能从DMA到CPU的中断 OR 2000h ,ST ;使能CPU全局中断 LDI @CONTROL,R0 ;初始化DMA全局控制寄存器 STI R0,*AR0 ;启动DMA传输 .END

CPU和DMA控制器的访问操作并行进行。 当CPU和DMA控制器请求同一资源时,CPU具有 更高优先级,即DMA的操作必须等到CPU释放 资源后执行。

4.3.4

DMA中断及同步机制—中断

(1)中断原则:DMA通道传输完毕后通过DMA的全局控制寄存 器的TCINT位发送一个中断给CPU,CPU中断使能寄存器的 EDINT位必须置位,从而允许CPU被DMA中断。 (2)可接收中断:外部中断、定时器、串行口的中断。 (3)DMA通过同步来实现对中断的接收。CPU中断控制寄存器 可以检测到所有的DMA中断,并对中断标志寄存器进行设置。

4.3.3

DMA寄存器—目的地址寄存器

1) 24位寄存器 2)通过全局控制寄存器中的DECDST,INCDST实现地址修 改以选通相应固定地址的通信信道 3)只能对该寄存器进行写操作

4.3.3

DMA寄存器—传输计数寄存器

1) 24位寄存器,反映传输字数 2)系统复位时,传输计数寄存器置0 3)完成一次传输,计数器减1,计数值 为0时,若TCINT=1,触发DMA中断 4)当计数寄存器值为0时,DMA通道 没有被挂起,计数寄存器将继续减少到 负值;通道的传输最大字数1000000h (167.77216万次)

4.3.2 DMA基本操作

操作过程: (1) DMA的寄存器初始化 -----进行DMA传输前的准备(源地址寄存器、 目的地址寄存器、传输计数器、模式加载) (2) DMA的操作开始 -----启动DMA工作 (3) DMA的数据传输 -----完成数据传输

4.3.2 DMA基本操作

(1) DMA的寄存器初始化 将需要读出的存储器单元地址赋给DMA的源地址寄存器。 将需要写入的存储器单元地址赋给DMA的目的地址寄存器。 将需要传输的字长赋给传输计数器。 将DMA通道控制寄存器以适当的模式加载,通过中断的方式 同步DMA控制寄存器的读写。 (2) DMA的开始 设置DMA全局控制寄存器的START位,启动DMA控制器开始 工作。

4.3.3 DMA寄存器

DMA具有4个寄存器。 全局控制寄存器:包含DMA通道的状态和模式信息。 源地址寄存器:包含将要被读出数据的存储器地址。 目的地址寄存器:包含将要被写入数据的存储器地址。 传输计数寄存器:包含将要被移动的块的大小。

808000h 808004h 808006h 808008h DMA全局控制寄存器 DMA源地址寄存器 DMA目的地址寄存器 DMA传输计数器

11 DMA处于工作忙碌中(读、写数据,等待源中断,目的中 断,同步操作)

(3)DMA 源地址改变模式:Bit 4 Bit 5

(4)DMA 目的地址改变模式:Bit 6 Bit 7

(5)DMA 同步控制方式:Bit 9 Bit 8

SYNC = 00 同步禁止,DMA不响应任何同步操作; = 01 源同步,中断允许执行读操作; = 01 目的同步,中断允许执行写操作; =11 源和目的同步,中断允许执行读、写操作。

4.3.2 DMA基本操作

一批数据需要从存储器的一个区域传传输到另一个区域 主要解决以下问题: (1) 数据从哪里来 ——源地址 (2) 数据到哪里去 ——目的地址 (3) 数据量有多少 ——计数器 (4) 传输如何进行 ——全局控制控制器

808000h 808004h 808006h 808008h DMA全局控制寄存器 DMA源地址寄存器 DMA目的地址寄存器 DMA传输计数器

4.3.4

DMA中断及同步机制—同步机制

(1)同步禁止,当SYNC=00 时,不产生同步,只要没有 冲突,DMA就可随时执行 读、写操作,所有的中断被 忽略,但DMA中的中断使能 位不会发生改变。Fra bibliotek4.3.4

DMA中断及同步机制—同步机制

(2)源同步,当SYNC=01 时,DMA 将与源同步。 DMA接收一次中断执行一次 读操作。之后从总体上禁止 所有的DMA中断。

4.3 DMA 控制器(Direct Memory Access)

DMA 是TMS320VC33的可编程外围设备,能够在存储器之 间传输大批量的数据,但不影响CPU操作,使得DSP可以与低速 外部存储器以及外围设备接口,而不降低CPU的运算能力,改进 了系统性能,提高了数据处理能力。 主要内容 DMA控制器的特性 DMA基本操作 DMA寄存器 DMA中断及同步机制 DMA初始化和重构