数字电路基础 第4章

《数字电子技术基础》第五版:第四章 组合逻辑电路

74HC42

二-十进制译码器74LS42的真值表

序号 输入

输出

A3 A2 A2 A0 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 Y8 Y9

0 0 000 0 111111111

1 0 001 1 011111111

2 0 010 1 101111111

3 0 011 1 110111111

4 0 100 1 111011111

A6 A4 A2

A0

A15 A13 A11 A9

A7 A5 A3

A1

I7 I6 I5 I4 I3 I2 I1 I00

S

74LS 148(1)

YS

YEE Y2 Y1

Y0

XX

I7 I6 I5 I4 I3 I2 I1 I0

S

74LS 148(2)

YS

YE Y2 Y1

Y0

X

&

G3

&

G2

&

G3

Z3

Z2

Z1

&

G3

0时1部分电路工作在d0a1a0d7d6d5d4d3d2d1d074ls153d22d20d12d10d23d21s2d13d11s1y2y1a1a0在d4a0a1a2集成电路数据选择器集成电路数据选择器74ls15174ls151路数据输入端个地址输入端输入端2个互补输出端74ls151的逻辑图a2a1a02274ls15174ls151的功能表的功能表a2a1a0a将函数变换成最小项表达式b将使能端s接低电平c地址a2a1a0作为函数的输入变量d数据输入d作为控制信号?实现逻辑函数的一般步骤cpcp000001010011100101110111八选一数据选择器三位二进制计数器33数据选择器数据选择器74ls15174ls151的应用的应用加法器是cpu中算术运算部件的基本单元

数字电子技术基础 第4章

在将两个多位二进制数相加时,除了最低位以外,每一 位都应该考虑来自低位的进位,即将两个对应位的加数 和来自低位的进位3个数相加。这种运算称为全加,所用 的电路称为全加器。

图4.3.26

全加器的卡诺图

图4.3.27 双全加器74LS183 (a)1/2逻辑图 (b)图形符号

二、多位加法器

1、串行进位加法器(速度慢)

数字电子技术基础 第四章 组合逻辑电路

Pan Hongbing VLSI Design Institute of Nanjing University

4.1 概述

数字电路分两类:一类为组合逻辑电路,另一类 为时序逻辑电路。 一、组合逻辑电路的特点

任何时刻的输出仅仅取决于该时刻的输入,与电路原 来的状态无关。 电路中不能包含存储单元。

例4.2.1 P162

图4.2.1

例3.2.1的电路

4.2.2 组合逻辑电路的设计方法

最简单逻辑电路:器件数最少,器件种类最少, 器件之间的连线最少。 步骤:

1、进行逻辑抽象 2、写出逻辑函数式 3、选定器件的类型 4、将逻辑函数化简或变换成适当的形式 5、根据化简或变换后的逻辑函数式,画出逻辑电路 的连接图 6、工艺设计

通常仅在大规模集成电 路内部采用这种结构。 图4.3.7 用二极管与门阵列组成的3线-8线译码器

最小项译码器。

图4.3.8

用与非门组成的3线-8线译码器74LS138

例4.3.2 P177

图4.3.10

用两片74LS138接成的4线-16线译码器

二、二-十进制译码器

拒绝伪码功能。

图4.3.11

4.2.2 组合逻辑电路的设计方法

数字电子技术基础-第四章-触发器

SD——直接置1端,低电平有效。

G2

G1 & Q3 & G3

& Q4 G4 &

Q

Q

L2

CP Q5 & G5 Q6 G6 &

C1 R 1D ∧ S RD SD

RD和SD不受CP和D信

SD

RD

D

号的影响,具有最高的 优先级。

3.集成D触发器74HC74

2Q 2Q 1Q 1Q Vcc 2RD 2D 2CP 2SD 2Q 2Q

2.特性方程

KQn J 0 1 00 01 11 10

0 0

0 0 1 1

0 0

1 1 0 0

0 1

0 1 0 1

0 1

0 0 1 1

0 1

1 1

0 0

0 1

Qn1 JQn KQn

1 1

1 1

0 1

1 0

3.状态转换图

J=1 K=× J=0 K=× 0 J=× K=1 1 J=× K=0

CP=1时, Q2=0,则Q=1, 封锁G1和G3 使得Q2=0,维持置1 同时Q3=1,阻塞置0

Q3

R

&

Q

G6

& Q4

D

G4

置1阻塞、置0维持线

Q3=0,则Q=0, 封锁G4,使得Q4=1, 阻塞D=1进入触发器, 阻塞置1 同时保证Q3=0,维持置0

触发器的直接置0端和置1端

RD——直接置0端,低电平有效;

JK触发器→T(T ′)触发器

Qn+ 1 = TQn + TQn

令J = K = T

D触发器→JK触发器

数字电子基础部分答案(康华光)第04章_组合逻辑习题解答

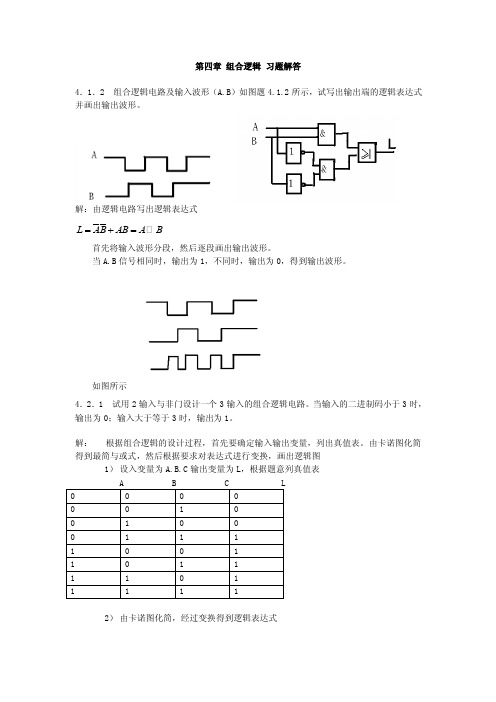

第四章组合逻辑习题解答4.1.2 组合逻辑电路及输入波形(A.B)如图题4.1.2所示,试写出输出端的逻辑表达式并画出输出波形。

解:由逻辑电路写出逻辑表达式=+=L AB AB A B首先将输入波形分段,然后逐段画出输出波形。

当A.B信号相同时,输出为1,不同时,输出为0,得到输出波形。

如图所示4.2.1 试用2输入与非门设计一个3输入的组合逻辑电路。

当输入的二进制码小于3时,输出为0;输入大于等于3时,输出为1。

解:根据组合逻辑的设计过程,首先要确定输入输出变量,列出真值表。

由卡诺图化简得到最简与或式,然后根据要求对表达式进行变换,画出逻辑图1)设入变量为A.B.C输出变量为L,根据题意列真值表2)由卡诺图化简,经过变换得到逻辑表达式L A BC A BC=+=*3)用2输入与非门实现上述逻辑表达式4.2.7 某足球评委会由一位教练和三位球迷组成,对裁判员的判罚进行表决。

当满足以下条件时表示同意;有三人或三人以上同意,或者有两人同意,但其中一人是叫教练。

试用2输入与非门设计该表决电路。

解: 1)设一位教练和三位球迷分别用A和B.C.D表示,并且这些输入变量为1时表示同意,为0时表示不同意,输出L表示表决结果。

L为1时表示同意判罚,为0时表示不同意。

由此列出真值表输入输出A B C D L2)由真值表画卡诺图由卡诺图化简得L=AB+AC+AD+BCD由于规定只能用2输入与非门,将上式变换为两变量的与非——与非运算式 *******L AB AC AD BCD AB AC AD B CD ==3)根据L 的逻辑表达式画出由2输入与非门组成的逻辑电路4.3.3 判断图所示电路在什么条件下产生竞争冒险,怎样修改电路能消除竞争冒险?解: 根据电路图写出逻辑表达式并化简得*L A B BC =+当A=0,C=1时,L B B =+ 有可能产生竞争冒险,为消除可能产生的竞争冒险,增加乘积项使AC ,使 *L A B BC A C =++ ,修改后的电路如图4.4.4 试用74HC147设计键盘编码电路,十个按键分别对应十进制数0~9,编码器的输出为8421BCD码。

(完整版)数字电路基础-阎石第五版-第4章

用与或非门实现

AG R 00 01 11 10

01 0 1 0

Z (RAG RAG RAG)

10 1 1 1

4.3 若干常用的组合逻辑电路

§4.3.1 编码器

编码:用二进制代码来表示某一信息(文 字、数字、符号)的过程。

实现编码操作的电路称为编码器。

编

高?低?

码 器

码?

一、二进制编码器 输入端:2n

(A B)CI

AB

S A B CI CO (A B)CI AB

S A B CI CO (A B)CI AB

这是一个全 加器电路

§4.2.2 组合逻辑电路的设计方法

根据实际逻辑问题

步骤:

确定输入、输出 列出真值表

最简单逻辑电路

设计

选择所需

门电路

写出表达式

并简化

画逻辑电路图

根据设

计要求

分析题意,将设计 要求转化为逻辑关

形式变换

系,这一步为设计

组合逻辑电路的根关据键设计所用

芯片要求

例1:设计三人表决电路(A、B、C)。每人 一个按键,如果同意则按下,不同意则不按。 结果用指示灯表示,多数同意时指示灯亮, 否则不亮。用与非门实现.

解:

1.首先指明逻辑符号取“0”、“1”的含义。三 个按键A、B、C按下时为“1”,不按时为“0”。 输出量为 L,多数赞成时是“1”,否则是“0”。

(( DC A) (DCB) (DCB))

解: Y2 ((DBA)(DC)) DBA DC

Y1 ((DCA)(DCB)(DCB)) DCA DCB DCB

Y0 ((DB)(DC)) DB DC

由真值表知:该电路可用来判别输入的4位二 进制数数值的范围。

数字电子技术基础第四章习题及参考答案

数字电子技术基础第四章习题及参考答案第四章习题1.分析图4-1中所示的同步时序逻辑电路,要求:(1)写出驱动方程、输出方程、状态方程;(2)画出状态转换图,并说出电路功能。

CPY图4-12.由D触发器组成的时序逻辑电路如图4-2所示,在图中所示的CP脉冲及D作用下,画出Q0、Q1的波形。

设触发器的初始状态为Q0=0,Q1=0。

D图4-23.试分析图4-3所示同步时序逻辑电路,要求:写出驱动方程、状态方程,列出状态真值表,画出状态图。

CP图4-34.一同步时序逻辑电路如图4-4所示,设各触发器的起始状态均为0态。

(1)作出电路的状态转换表;(2)画出电路的状态图;(3)画出CP作用下Q0、Q1、Q2的波形图;(4)说明电路的逻辑功能。

图4-45.试画出如图4-5所示电路在CP波形作用下的输出波形Q1及Q0,并说明它的功能(假设初态Q0Q1=00)。

CPQ1Q0CP图4-56.分析如图4-6所示同步时序逻辑电路的功能,写出分析过程。

Y图4-67.分析图4-7所示电路的逻辑功能。

(1)写出驱动方程、状态方程;(2)作出状态转移表、状态转移图;(3)指出电路的逻辑功能,并说明能否自启动;(4)画出在时钟作用下的各触发器输出波形。

CP图4-78.时序逻辑电路分析。

电路如图4-8所示:(1)列出方程式、状态表;(2)画出状态图、时序图。

并说明电路的功能。

1C图4-89.试分析图4-9下面时序逻辑电路:(1)写出该电路的驱动方程,状态方程和输出方程;(2)画出Q1Q0的状态转换图;(3)根据状态图分析其功能;1B图4-910.分析如图4-10所示同步时序逻辑电路,具体要求:写出它的激励方程组、状态方程组和输出方程,画出状态图并描述功能。

1Z图4-1011.已知某同步时序逻辑电路如图4-11所示,试:(1)分析电路的状态转移图,并要求给出详细分析过程。

(2)电路逻辑功能是什么,能否自启动?(3)若计数脉冲f CP频率等于700Hz,从Q2端输出时的脉冲频率是多少?CP图4-1112.分析图4-12所示同步时序逻辑电路,写出它的激励方程组、状态方程组,并画出状态转换图。

数字电子技术基础第四章重点最新版

发

这种触发方式称为边沿触发式。

器

EXIT

集成触发器

主从触发器和边沿触发器有何异同?

空翻可导致电路工作失控。

EXIT

集成触发器

4.3 无空翻触发器

主要要求:

了解无空翻触发器的类型,掌握其工作特点。 能根据触发器符号识别其逻辑功能和触发方式, 并进行波形分析。

EXIT

集成触发器

一、无空翻触发器的类型和工作特点

主

工作特点:CP = 1 期间,主触发器接收

从 输入信号;CP = 0 期间,主触发器保持 CP

EXIT

集成触发器

2. 工作原理及逻辑功能 Q 0 触发器被工置作0原1理Q

G1 11

1 SD

输入 RD SD 00 01 10 11

输出 QQ

01

G2

RD 0 功能说明

触发器置 0

EXIT

2. 工作原理及逻辑功能

集成触发器

Q 1 触发器被置 1 0 Q

G1

0 SD

输入 RD SD 00 01 10 11

触发器置 0 触发器置 1 触发器保持原状态不变

EXIT

2. 工作原理及逻辑功能

Q 1

G1

0 SD

输入 RD SD 00 01 10 11

输出

QQ 不定

01 10 不变

集成触发器

Q

输出既非 0 状态,

1 也非 1 状态。当 RD 和 SD 同时由 0 变 1 时, 输出状态可能为 0,也

G2 可能为 1,即输出状态 不定。因此,这种情况

EXIT

四、一些约定

集成触发器

1态: Qn=1,Qn=0 0态: Qn=0,Qn=1

数字电路(第四章触发器)

同步式触发器——电平触发方式,一般高电平触发; 维持阻塞触发器——边沿触发方式,一般上升沿触发;

边沿触发器——边沿触发方式,一般下降沿触发;

主从触发器——主从触发方式。

14

时钟输入CP: 时钟脉冲输入端,通常输入周期性时钟脉冲。

数据输入端:

又叫控制输入端。四种触发器:SR—S,R;D—D; JK—J,K;T—T。 初态Qn: 可称现态,某个时钟脉冲作用前触发器状态。

38

主从式JK触发器

Q

&1

Q

&2 &4

R'

从触发器

&3

S' Q'

Q'

&5 &7

J

&6

1

CP

主触发器

&8

K

CP

39

主、从触发器都是电平触发的同步式触发器 主从触发器在一个时间脉冲(CP)作用下,工作 过程分两个阶段(双拍工作方式)。

1)CP=1,主触发器接收控制信号J、K,状态反映 在 Q' 和 Q' 上, CP = 0 从触发器被封锁,保持原来状态。 2)在CP下降沿(负跳变时刻),从触发器向主触发器看齐。 负跳变时,主触发器被封锁,保持原状态不变。此时,从 触发器封锁被解除取与主触发器一致的状态。

次态Qn+1:某个时钟作用后触发器的状态。(新状态)

15

描述时钟触发器逻辑功能时,采用四种方式:

功能真值表:(表格形式) 在一定控制输入下,在时钟脉冲作用前后,初态向次态转 化的规律(状态转换真值表) 激励表:(表格形式)

在时钟脉冲作用下,实现一定的状态转换(Qn—Qn+1),应 有怎样的控制输入条件。

数字电子技术基础(第四版)课后习题答案_第四章

第4章触发器[题4.1]画出图P4.1所示由与非门组成的根本RS触发器输出端Q、Q的电压波形,输入端S、R的电压波形如图中所示。

图P4.1[解]见图A4.1图A4.1[题4.2]画出图P4.2由或非门组成的根本R-S触发器输出端Q、Q的电压波形,输出入端S D,R D的电压波形如图中所示。

图P4.2[解]见图A4.2[题4.3]试分析图P4.3所示电路的逻辑功能,列出真值表写出逻辑函数式。

图P4.3 [解]:图P4.3所示电路的真值表S R Q n Q n+1 0 0 0 0 0 0 1 1 0 1 0 0 0 1 1 0 1 0 0 1 1 0 1 1 1 1 0 0* 1 110*由真值表得逻辑函数式 01=+=+SR Q R S Q nn[题4.4] 图P4.4所示为一个防抖动输出的开关电路。

当拨动开关S 时,由于开关触点接触瞬间发生振颤,D S 和D R 的电压波形如图中所示,试画出Q 、Q 端对应的电压波形。

图P4.4[解] 见图A4.4图A4.4[题4.5] 在图P4.5电路中,假设CP 、S 、R 的电压波形如图中所示,试画出Q 和Q 端与之对应的电压波形。

假定触发器的初始状态为Q =0。

图P4.5[解]见图A4.5图A4.5[题4.6]假设将同步RS触发器的Q与R、Q与S相连如图P4.6所示,试画出在CP 信号作用下Q和Q端的电压波形。

己知CP信号的宽度t w = 4 t Pd 。

t Pd为门电路的平均传输延迟时间,假定t Pd≈t PHL≈t PLH,设触发器的初始状态为Q=0。

图P4.6图A4.6[解]见图A4.6[题4.7]假设主从结构RS触发器各输入端的电压波形如图P4.7中所给出,试画Q、Q端对应的电压波形。

设触发器的初始状态为Q=0。

图P4.7[解] 见图A4.7图A4.7[题4.8]假设主从结构RS触发器的CP、S、R、DR各输入端的电压波形如图P4.8所示,1DS。

《数字电子技术基础》复习指导(第四章)

《数字电⼦技术基础》复习指导(第四章)第四章组合逻辑电路⼀、本章知识点(⼀)概念1.组合电路:电路在任⼀时刻输出仅取决于该时刻的输⼊,⽽与电路原来的状态⽆关。

电路结构特点:只有门电路,不含存储(记忆)单元。

2.编码器的逻辑功能:把输⼊的每⼀个⾼、低电平信号编成⼀个对应的⼆进制代码。

优先编码器:⼏个输⼊信号同时出现时,只对其中优先权最⾼的⼀个进⾏编码。

3.译码器的逻辑功能:输⼊⼆进制代码,输出⾼、低电平信号。

显⽰译码器:半导体数码管(LED数码管)、液晶显⽰器(LCD)4.数据选择器:从⼀组输⼊数据中选出某⼀个输出的电路,也称为多路开关。

5.加法器半加器:不考虑来⾃低位的进位的两个1位⼆进制数相加的电路。

全加器:带低位进位的两个 1 位⼆进制数相加的电路。

超前进位加法器与串⾏进位加法器相⽐虽然电路⽐较复杂,但其速度快。

6.数值⽐较器:⽐较两个数字⼤⼩的各种逻辑电路。

7.组合逻辑电路中的竞争⼀冒险现象竞争:门电路两个输⼊信号同时向相反跳变(⼀个从1变0,另⼀个从0变1)的现象。

竞争-冒险:由于竞争⽽在电路输出端可能产⽣尖峰脉冲的现象。

消除竞争⼀冒险现象的⽅法:接⼊滤波电容、引⼊选通脉冲、修改逻辑设计(⼆)组合逻辑电路的分析⽅法分析步骤:1.由图写出逻辑函数式,并作适当化简;注意:写逻辑函数式时从输⼊到输出逐级写出。

2.由函数式列出真值表;3.根据真值表说明电路功能。

(三)组合逻辑电路的设计⽅法设计步骤:1.逻辑抽象:设计要求----⽂字描述的具有⼀定因果关系的事件。

逻辑要求---真值表(1) 设定变量--根据因果关系确定输⼊、输出变量;(2)状态赋值:定义逻辑状态的含意输⼊、输出变量的两种不同状态分别⽤0、1代表。

(3)列出真值表2.由真值表写出逻辑函数式真值表→函数式,有时可省略。

3.选定器件的类型可选⽤⼩规模门电路,中规模常⽤组合逻辑器件或可编程逻辑器件。

4.函数化简或变换式(1)⽤门电路进⾏设计:从真值表----卡诺图/公式法化简。

数字电子技术基础4

0 1 0 1

0 1 1 0

每输入一个脉 冲,输出状态 改变一次

T=1时, 翻转。

Q n1 Q n

如果将T恒接高电平,就构成了一种特殊的触发器T’,它 Q n1 Q n 只是脉冲翻转电路 。

4-2-4. 边沿触发器

为了提高触发器的抗干扰能力,希望触发器的次态仅仅 取决于 CP 作用沿到达时刻输入信号的状态。这样的触发器 称为边沿触发器。 这里,重点介绍利用 CMOS 传输门构成的 边沿 D 触发器

CP=1 时 打 开 CP=0 时 封 锁

Q = Q’

注意:在CP的一个变化周期中,触发器输出状态只改变一次。

3. 特性表 4. 几点说明 1)图示主从RS 触发器 1 触发有效; 2)表中*表示:若 R、S 端同时触发, 则在CP回到0后,输出状态不定; 3)输入端的约束条件为 RS = 0。 CP 0 R X 0 0 1 S X 0 1 0 Qn+1 Qn Qn 1 0

4-2-2. 同步 RS触发器

在数字系统中,如果要求某些触发器在同一时刻动作,就 必须给这些触发器引入时间控制信号,使这些触发器只有在 同步信号到达时才按输入信号改变状态。 时间控制信号也称同步信号,或时钟信号, 或时钟脉冲,简称时钟,用 CP 表示 Q Q 受CP控制的触发器称为时钟触发器。

一、电路结构与工作原理

S CP R

Q

&

Q

触发器在CP控制下正常工作时应使 SD、RD 处于高电平。

&

G4

G2

注意:用SD、RD 将触发器置位或复位应当在CP=0的状态 下进行,否则在SD、RD 返回高电平以后,无法保存预置 的状态。

二. 动作特点

数字电路第四章组合逻辑电路

(3)逻辑表达式:

Y A B C A B C A B C ABC A B CB C A B CB C ABC R AB BC AC AB BC AC

(4)画出电路(见仿真)

2、下图所示是具有两个输入X、Y和三个输出Z1、Z2、 Z3的组合电路。写出当X>Y时Z1 =1;X=Y时 Z2 =1;当X<Y时Z3 =1,写出电路的真值表, 求出输出方程。 解:A、列真值表: B、写出函数表达式:

可在K图中直接圈1化简得最简与或式。再对最简与或式 两次求反进行变换。 A C A B C B C

n 1 n n n n n n

B n Cn A n Cn A n B n B n C n A n Cn A n B n

C、 画出逻辑电路:

4、设计一组合电路,当接收的4位二进制数能被4整除 时,使输出为1。 A 、列真值表:数N=8A+4B+2C+D 注:0可被任何数整除 B、写逻辑函数式:画出F的K图

3、优先编码器

优先编码器常用于优先中断系统和键盘编码。与普 通编码器不同,优先编码器允许多个输入信号同时有效, 但它只按其中优先级别最高的有效输入信号编码,对级 别较低的输入信号不予理睬。

常用的MSI优先编码器有10线—4线(如74LS147)、

8线—3线(如74LS148)。

Cn 1 Cn 1 Bn Cn A n Cn A n Bn

2)、用异或门实现Dn:

An Bn C n An Bn C n An Bn C n

3)、用与非门实现 Cn+1:

Dn An Bn C n An Bn C n An BnC n An BnC n

数字电路与逻辑设计第4章触发器(Flip Flop)

4.1 概述

一、触发器概念

Flip - Flop,简写为 FF, 又称双稳态触发器。

触发器是一种具有记忆功能,能存储1位二进制信息(0 或1)的逻辑电路。

有一个或多个输入,两个互反的输出(Q和Q)。 通常用Q端的状态代表触发器的状态。

二、触发器的分类

基本RS触发器(RSFF)又称SR锁存器,是触发器中最简 单的一种,也是各种其他类型触发器的基本组成部分。

一、TFF

(1)功能表

T

Qn

Qn+1

0

0

0

0

1

1

1

0

1

1

1

0

简化的功能表

(2)特征方程

Qn1 TQn TQ n T Qn

说明:(1)一般不单独生产,由其他触发器转换而得。 (2)触发方式由被转换的触发器决定。

触发器总结

触发器是具有记忆功能的的逻辑电路,每个触发器 能存储一位二进制数据。

(4)波形图

强调触发方式

结构不做要求

边沿JKFF的逻辑符号:

1J C1 1K

J CP K

(下 圆c) 降圈国沿)触标(发小符号

次态方程: 功能表:

一、TFF

三、TFF和TFF

在数字电路中,凡在CP时钟脉冲控制下,根据输入 信号T取值的不同,具有保持和翻转功能的电路,即当 T=0时能保持状态不变,T=1时,每来一个CP的上升沿 (或下降沿),触发器的状态就翻转一次。

1

(6). 波形图 又称时序图,它反映了触发器的输出状态随时间和输

入信号变化的规律。

在任何时刻,输入都能直接改变输出的状态。

2.钟控原理

数字电子技术基础 第04章触发器习题解

Q

Q

R=1、S=0 不管原Q取0还是1使Q=0

R=0、S=1 不管原Q取0还是1使Q=1

R=1、S=1 使两个输出同时为0,是不允许出现 的,作为约束处理。

G1 ≥1

≥1 G2

将原状态作为变量,次态作为

R

S

函数列出特性表

R

S

Q n Q n+1

0

0

00

由状态转换表化简得 到特性方程

0

0

11

0

1

01

0

1

解:(1)特性方程为

Qn+1 1

=

D1 ,Q2n+1

=

D2

1D Q

驱动方程和输出方程为

C1

D1

=

n

Q2 , D2

=

Q1n , F

=

CP

⊕

Q1n

CP

代入得状态方程

Qn+1 1

=

Q

n 2

,

Q2n +

1

=

Q1n

从状态方程可得:

CP

Q1

1D Q

Q2

C1 R

=1 F

Q1

Q2 Q1n+1 Q2n+1 F

Q1

0

0

主从触发器有时钟控制,在CP=1期间接收数据,在 CP后沿发生翻转,不属于完全的时钟沿触发,有 一次变化缺点。

边沿触发器有时钟控制,在CP的边沿接收数据和发 生翻转,是一种较理想的触发器。

4.5 设图4.28中各触发器的初始状态皆为Q=0,画出在CP脉 冲连续作用下个各触发器输出端的波形图。

解:图1,2,5为时钟后沿翻 转,图3为时钟前沿翻转, 图4,6为保持原状态

数字电路第四章答案

数字电路第四章答案【篇一:数字电路答案第四章时序逻辑电路2】p=1,输入信号d被封锁,锁存器的输出状态保持不变;当锁存命令cp=0,锁存器输出q?d,q=d;当锁存命令cp出现上升沿,输入信号d被封锁。

根据上述分析,画出锁存器输出q及 q的波形如习题4.3图(c)所示。

习题4.4 习题图4.4是作用于某主从jk触发器cp、j、k、 rd及 sd 端的信号波形图,试绘出q端的波形图。

解:主从jk触发器的 rd、且为低有效。

只有当rd?sd?1 sd端为异步清零和复位端,时,在cp下降沿的作用下,j、k决定输出q状态的变化。

q端的波形如习题4.4图所示。

习题4.5 习题4.5图(a)是由一个主从jk触发器及三个非门构成的“冲息电路”,习题4.5图(b)是时钟cp的波形,假定触发器及各个门的平均延迟时间都是10ns,试绘出输出f的波形。

cpf cp100ns10nsq(a)f30ns10ns(b)(c)习题4.5图解:由习题4.5图(a)所示的电路连接可知:sd?j?k?1,rd?f。

当rd?1时,在cp下降沿的作用下,且经过10 ns,状态q发生翻转,再经过30ns,f发生状态的改变,f?q。

rd?0时,经过10ns,状态q=0。

根据上述对电路功能的分析,得到q和f的波形如习题4.5图(c)所示。

习题4.6 习题4.6图(a)是一个1检出电路,图(b)是cp及j端的输入波形图,试绘出 rd端及q端的波形图(注:触发器是主从触发器,分析时序逻辑图时,要注意cp=1时主触发器的存储作用)。

cpj(a)qd(c)cp j(b)习题图解:分析习题4.6图(a)的电路连接:sd?1,k?0,rd?cp?q;分段分析习题4.6图(b)所示cp及j端信号波形。

(1)cp=1时,设q端初态为0,则rd?1。

j信号出现一次1信号,即一次变化的干扰,且k=0,此时q端状态不会改变;(2)cp下降沿到来,q端状态变为1,rd?cp,此时cp=0,异步清零信号无效;(3)cp出现上升沿,产生异步清零信号,使q由1变为0,在很短的时间里 rd又恢复到1;(4)同理,在第2个cp=1期间,由于j信号出现1信号,在cp下降沿以及上升沿到来后,电路q端和 rd端的变化与(2)、(3)过程的分析相同,其波形如习题4.6图(c)所示。

数字电子技术基础(第四版)-第4章-组合逻辑电路解析PPT课件

-

54

设计实例2:用2N选一数据选择器实现 N+1个变量的逻辑函数。

设计思想: ①将N个变量接数据选择器的选择输入端(即地址端) ②余下的一个变量作为数据选择器的数据输入端。

-

55

例:用74153实现三变量函数。

F (A ,B ,C ) m (1 ,3 ,5 ,6 )

解一:设B接A1,C接A0。

A

' 0

)

m2

'

...

Y7 ' ( A2 A1A0 ) m 7 '

-

45

-

46

-

47

三、用译码器构成函数发生器P186

例1:

请写出Y的逻辑函数式

Y(Y3'Y4'Y5')' Y3Y4 Y5

m3 m4 m5

m(3, 4,5)

Y A 'B C A B 'C ' A B 'C

-

48

例2:用74138构成下 列函数发生器:

F A 'B 'C A 'B C A B 'C A B C ' 0 B 'C ' ( A ' A ) B 'C A B C ' A 'B C

0 m 0 1 m 1 A m 2 A 'm 3

D 0 m 0 D 1 m 1 D 2 m 2 D 3 m 3

-

56

解二:设A接A1,B接A0。

4)画逻辑图(略)

-

31

三、优先编码器 8线-3线优先编码器

74HC148

-

1、功能表

输入:I 0 ~ I 7 ,共8个输入端

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

A0 H H L H L H L H L H

图中,小圆圈表示低电平有效,各引出端功能如下: 7~0为状态信号输入端,低电平有效,7的优先级别最 高,0的级别最低; A2、A1、A 0为代码(反码)输出端, A2为最高位; EI为使能(允许)输入端,低电平有效;当EI=0时,电 路允许编码;当EI=1时,电路禁止编码,输出A2、A1、A 0均

0

1 0 1 0 1 0 1 0

1

1 1 1 1 1 1 1 1

11

该编码器为输入低电平有效

3. 优先编码器

优先编码器的提出: 如果有两个或更多输 入信号有效,将会出现 输出混乱。 必须根据轻重缓急,规定好这些外设允许操作的 先后次序,即优先级别。

识别多个编码请求信号的优先级别,并进行相应 编码的逻辑部件称为优先编码器。

12

3. 优先编码器

4 线─2 线优先编码器(设计)

(1)列出功能表

输 入 I0 1 × I1 0 1 I2 0 0 1 I3 0 0 0 1 高

13

(2)写出逻辑表达式

输 出

Y1 Y0 0 0 1 1 0 1 0 1

Y1 I 2 I 3 I 3 Y0 I1 I 2 I 3 I 3

1

& ≥1 & 1 & & A2

3个编码 输出端 A2~A0

14

EI

4.1.2 集成电路编码器

2. 优先编码器74148的示意框图、引脚图

4

I0 I1 I2 I3 I4 I5 I6 I7

1 2 3 4

16 15 14 13 12 11 10 9

VCC EO GS 3 2 1 0 A0

5 6 7

EI 74148 EO

译码: 译码是编码的逆过程,即将某个二进制码翻 译成特定的信号,即电路的某种状态。

译码器: 具有译码功能的逻辑电路称为译码器。 译码器的分类:

唯一地址译码器 将一系列代码转换成与之对应的有效信号。

二进制译码器 常见的唯一地址译码器: 二—十进制译码器 显示译码器

代码变换器 将一种代码转换成另一种代码。

4

4.1.1 编码器 (Encoder)的概念与分类

普通编码器 编码器的分类: 优先编码器 普通编码器:任何时候只允许一个编码输入信号有 效,否则输出就会发生混乱。

优先编码器:允许同时输入两个以上的有效编码信 号。当同时输入几个有效编码信号时,优先编码器 能按预先设定的优先级别,只对其中优先权最高的 一个进行编码。

•普通编码器不能同时输 入两个已上的有效编码信 号

9

2. 键盘输入8421BCD码编码器

(1) 逻辑图

十个按键

S0 0 S1 1 S2 2 S3 3 S4 4 S5 5 S6 6 S7 7 S8 8 S9 9

10

VCC 1kΩ ×10

控制使能标志

& GS

≥1 & D

&

C

输出代码

& B

&

A

2. 键盘输入8421BCD码编码器

EO EO

EO EO A 0 A 0 A 1 A 1 1 A 2 1 A 2

74148 ( Ⅰ ) 74148 ( Ⅰ )

1 0

EI EI

EO2 EO2 EI 1 EI 1

1 0

A 0 A 0

74148 (Ⅱ ) 74148 (Ⅱ ) A A 1 2 A A 1 2 GS GS GS 2 GS 2

1 0

1 2 3 4 5 6 7

16 VCC 15 Y 0 14 Y 1 13 Y 2 12 Y 3 11 Y 4 10 Y 5 9

GND 8

Y6

3 个 输 入 端

A

1

1

&

Y5

B

1

1

&

Y6

& C 1 1

Y7

24

一个3线–8线译码器能产生三变量函数的全部最小项。 74138集成译码器功表能 基于这一点用该器件能够方便地实现三变量逻辑函数。 输 入 输 出

H

H Y6 CBA H H

H

H

L

H

H

L

25

H Y7 CBA H H

4.2.2 集成电路译码器

74138的应用举例

例1 用74138组成脉 冲信号变换电路

A B C A B C G1 G2B G2A 74138 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7

E A B C Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7

EI 2 EI 2

GS GS GS 1 GS1

& & A A B B

& &

C C

& & D D

& & GS GS 19

I8 0 ~I7 I ~I15

4.2 译码器 / 数据分配器

4.2.1译码器 的定义与功能

4.2.2 集成电路译码器 4.2.3 数据分配器

20

4.2 译码器 / 数据分配器

4.2.1 译码器的概念与分类

1

1 1 1 1 0 1 1 1

1

1 1 1 0 1 1 1 1

1

1 1 0 1 1 1 1 1

1

1 0 1 1 1 1 1 1

1

0 1 1 1 1 1 1 1

0

1 1 1 1 1 1 1 1

1

1 1 1 1 1 1 1 1

1

0 0 0 0 0 0 0 0

0

1 1 1 1 0 0 0 0

0

1 1 0 0 1 1 0 0

EI 5 A2 6 A1 7

A0

A1

A2

GS

GND

8

示意框图

引脚图

15

4.1.2 集成电路编码器

EI=0,电路工作,输入0~7分别有低电平输入时, EI=0,电路工作,无有效低电平输入, EI=1,电路不工作,GS = EO =1, A2A2 1A1 0为0~7的编码输出,GS =0 , EO =1。 A A A0 A2 A1 A0 =111 1,EO=0 ; =111, GS = 3. 优先编码器74148的逻辑功能表

26

+5V

E

集成译码器74138的应用举例:

例2 用一个3线–8线译码器实现函数

F XY Z XY Z XY Z XYZ

Y0

Z Y X

A B C

74138

Y1 Y2 Y3 Y4 Y5 Y6 Y7 G1 G2A G2B & F

8

4.1.1 编码器 (Encoder)的概念与分类

1. 普通4 线─2线编码器

该电路存在的问题:

& I0 1 ≥1 Y1 I1 1 &

•当所有的输入都为0时,电 路的输出Y1Y0 = ?

Y1Y0 = 00

•和真值表中第一行的输出编 码相同,无法区分是哪个输 入信号的编码。

I2

1 &

≥1 I3 1 & Y0

功能表

EI 1 & y0

&

y1

B

1 & y2

A

1

&

y3

输 入 EI A B H × × L L L L L H L H L L H H

Y0 H L H H H

输出 Y1 Y2 H H H H L H H L H H

Y3 H H H H L

Y0 EI A B

Y1 EI A B

Y3 EI AB

23

Y2 EI AB

4.2.2 集成电路译码器

1. 74138集成译码器

Y0 A B C 74138 Y1 Y2 Y3 Y4 Y5 Y6 Y7 G1 G2A G2B

&

Y0

Hale Waihona Puke 3 个 控 制 端&

Y1

G1 G2A G2B

1 &

&

Y2

&

Y3

&

Y4

8 个 输 出 端

A B C G2A G2B G1 Y7

输 入 输 EI H L L L L L L L L L 0 × H × × × × × × × L 1 × H × × × × × × L H 2 × H × × × × × L H H 3 × H × × × × L H H H 4 × H × × × L H H H H 5 × H × × L H H H H H 6 × H × L H H H H H H 7 × H L H H H H H H H A2 H H L L L L H H H H A1 H H L L H H L L H H 出 GS H H L L L L L L L L EO H L H H H H H H H H

4. 集成电路编码器74148的应用

例4.1.1 用二片74148构成16位输入、4位二进制码输出的优 先编码器如图所示,试分析其工作原理。

无编码请求 有编码请求

I 1 I I 0 1 I 0 I 2 I 2 I 3 I 3 I 4 I 4 I I 5 6 I I 5 6 I 7 I 7 I 8 I 8 I I 9 10 I I 9 10 I I 11 12 I I 11 12 I 13 I 13 I 14 I 14 I 15 I 15

二 进 制 码 输 出

(3)逻辑功能表

I0 1 I1 0 I2 0 I3 0 Y1 Y0 0 0 1 1 0 1 0 1

4 输 入

0

0

1

0

0

1

0

0

0

0

0