高速PCB设计介绍[1]

在高速pcb的线路设计中,信号的参考平面

在高速pcb的线路设计中,信号的参考平面摘要:1.高速PCB线路设计简介2.信号参考平面的作用3.参考平面选取原则4.参考平面设计注意事项5.总结正文:高速PCB线路设计是现代电子工程技术中的一项重要技能,它使得电子设备能够在有限的空间内实现更高的功能和性能。

在高速PCB线路设计中,信号的参考平面起着至关重要的作用。

本文将详细介绍信号参考平面的作用、选取原则以及设计注意事项。

一、高速PCB线路设计简介高速PCB线路设计是指在有限的空间内,利用高速信号线、电源线、地线等元素,实现高速、高频、高密度的电子设备。

在这种设计中,信号的传输速度、传输损耗以及信号完整性等问题尤为关键。

因此,合理选择和设计参考平面对于保证信号质量具有重要意义。

二、信号参考平面的作用1.减小信号反射:参考平面可以有效地减小信号在传输过程中的反射,提高信号的传输质量。

2.抑制干扰:参考平面可以抑制高频干扰、噪声等对信号的干扰,提高信号的纯净度。

3.均衡阻抗:参考平面可以平衡信号传输线上的阻抗,降低信号的传输损耗。

4.提高信号完整性:参考平面有助于保持高速信号的完整性,避免信号失真和误码。

三、参考平面选取原则1.材质选择:通常选择相对介电常数较低、介质损耗角正切值较小的材料作为参考平面。

2.厚度选择:参考平面的厚度应与信号传输线的厚度相匹配,以减小信号的反射和传输损耗。

3.位置选择:参考平面应尽可能地靠近高速信号线,以提高信号的传输质量和完整性。

四、参考平面设计注意事项1.避免大开角走线:大开角走线会导致参考平面与传输线之间的耦合增强,进而影响信号质量。

2.避免走线跨越:参考平面上的走线不应跨越其他信号走线,以免产生电磁干扰。

3.保持参考平面连续性:在设计过程中,确保参考平面在整个PCB区域内的连续性,以提高信号完整性。

4.注意参考平面与电源、地平面的连接:合理设置参考平面与电源、地平面的连接位置,以降低电磁干扰。

五、总结高速PCB线路设计中,信号参考平面对于保证信号质量、提高信号完整性和抑制干扰具有重要意义。

Altium Designer实战攻略与高速PCB设计01

11

软板(FPC)硬板混合结构支持

射频过孔屏蔽缝合

极坐标布局及特殊栅格

Altium designer历史版本中的特色功能

挤推布线

多路布线工具

等长线调节

BGA自动扇出

网络颜色配置

自动过孔逢合

海量在线器件库

从标准元器件,到各种设计模板, Altium提供14万content库。 最丰富的设计“弹药库”为设计提速

• 免费的教程和设计资源共享。

良好的兼容性

为什么选择altium designer 15 •1.解决大量历史版本遗留问题。 •2.全面提升设计效率。 •3. 积极突破技术壁垒改进软件性能。 •4.不断创新满足各类用户需求。

Altium 的设计优势

• • • •

1.工程师用户群最广。 2.用户的使用感受:易上手、直观、方便。 3.软件改进和更新最及时。 4.同类产品的性价比最高。

Altium designer 15新特性

IPC-2581和Gerber X2格式支持

传统的Gerber作为 CAM格式,来源于约35年前发布的RS-274D标准版。使用旧版本 (如Gerber RS-274X)进入制造流程时会遇到数据模糊或丢失等问题。 包括:

- 每个板层都需要一个单独的物理文件(铜箔图像、生产说明、装配图等) - 未定义板层堆栈,需要手动放置图表 - 不包括钻孔信息,需要额外生成钻孔文件 - 不包含电气连通性信息,需要独立的网表用于裸板电气测试 - 不包含元件布局及BOM信息,需要额外生成

Altium 提供整体解决方案

Altium Designer

Vault ADMS

Solution Sales

Training 其他

Subscription

高速pcb设计规则

高速pcb设计规则

高速PCB设计规则是指在设计PCB时需要遵循的一系列规则和原则,以确保信号传输的质量和稳定性。

高速 PCB 的设计需要考虑多

种因素,如信号传输速度、信号波形、传输距离、干扰等等。

以下是一些常见的高速 PCB 设计规则:

1. 避免信号线的走线路径过长,尽可能缩短信号线的长度,以

减小信号传输延迟和损耗。

2. 保证信号线之间的距离足够大,以避免互相干扰,同时也能

降低信号串扰的风险。

3. 使用合适的层次结构设计,尽可能将信号线和电源线分离,

以减少干扰和噪声。

4. 在 PCB 的布线中,保证地线和供电线的宽度足够宽,以确保稳定的供电和地面连接。

5. 在 PCB 的布线中,避免过多的弯曲或拐角,以减小信号传输中的损失和延迟。

6. 选用合适的 PCB 材料和厚度,以满足高速信号传输的需求。

7. 注意 PCB 的电磁兼容性,通过合理的布线和屏蔽来减少干扰。

以上是高速 PCB 设计中的一些基本规则,但实际上,高速 PCB 的设计涉及的方面非常广泛,需要根据具体的应用场景来进行设计。

为了保证高速 PCB 的质量和可靠性,需要有专业的技术人员进行设

计和测试。

- 1 -。

关于PCB高速和低速设计的区别

关于PCB高速和低速设计的区别要判断一个信号是否为高速信号首先要区分几个误区。

误区一:信号周期频率FCLOCK 高的才属于高速设计其实我们在设计时考虑的最高频率往往取决于信号的有效频率(亦称转折频率)Fknee 。

如上图信号周期频率与有效(转折)频率定义为:FCLOCK Tclock = 1/(10% 90%) 0.5/ Fknee = Tr −(实际中多数信号而言)误区二:电容、电感式理想器件在低速领域,电容、电感工作频段比较低,可以认为他们是理想器件。

但在高速领域,PCB 上的电容电感等已经不能简单的视为纯粹的电容电感了。

例如:在低速领域电容我们可以视为断路,而在高速电路中,假设工作频率为F,则电容C 两侧表现出的电抗值为1/ 2πF ×C ,,,,在工作频率很高的情况下电抗值变得很小,电容表现为短路。

认清上面两个误区我们来讨论低速信号和高速信号的问题。

对于低速信号而言,传输路径上的个点的电平近似相同,我们可以采用集总的思维来对待传输路径,即传输路径上的各点状态相同;对于高速信号而言,传输路径上的各点电平不同,需要采用分布式的思维来看待,即各个点的状态不同。

因此,高速低速区分还要看信号传输路径的长度。

一般而言,在信号传输路径的长度(即信号线的长度)小于信号的有效波长的1/6 1/6 1/6 1/6 时,可以认为在该传输路径上,各点的电平状态近似相同。

由信号波长与频率的关系λ= c / F ,我们可以按下面的步骤进行高速低速的区分;1 获得信号的有效频率Fknee 和走线长度L;2 利用Fknee 计算出信号的有效波长λknee ;3 判断LLLL 与1/6 1/6 1/6 1/6λknee的关系,若LLLL>>>>1/6 1/6 1/6 1/6λknee,则信号为高速信号;反之,则为低速信号。

注意:Fknee 的获得方式一是可以直接测量,二是经验值可以假设信号的上升沿时间为信号周期的7%,此时有效频率Fknee 约为周期频率FCLOCK 的7 倍,如周期频率。

高速PCB设计的基本常识(全面)

高速PCB设计的基本常识(一)、电子系统设计所面临的挑战随着系统设计复杂性和集成度的大规模提高,电子系统设计师们正在从事100MHZ以上的电路设计,总线的工作频率也已经达到或者超过50MHZ,有的甚至超过100MHZ。

目前约50% 的设计的时钟频率超过50MHz,将近2020的设计主频超过12020z。

当系统工作在50MHz时,将产生传输线效应和信号的完整性问题;而当系统时钟达到12020z时,除非使用高速电路设计知识,否则基于传统方法设计的PCB将无法工作。

因此,高速电路设计技术已经成为电子系统设计师必须采取的设计手段。

只有通过使用高速电路设计师的设计技术,才能实现设计过程的可控性。

(二)、什么是高速电路通常认为如果数字逻辑电路的频率达到或者超过45MHZ~50MHZ,而且工作在这个频率之上的电路已经占到了整个电子系统一定的份量(比如说1/3),就称为高速电路。

实际上,信号边沿的谐波频率比信号本身的频率高,是信号快速变化的上升沿与下降沿(或称信号的跳变)引发了信号传输的非预期结果。

因此,通常约定如果线传播延时大于1/2数字信号驱动端的上升时间,则认为此类信号是高速信号并产生传输线效应。

信号的传递发生在信号状态改变的瞬间,如上升或下降时间。

信号从驱动端到接收端经过一段固定的时间,如果传输时间小于1/2的上升或下降时间,那么来自接收端的反射信号将在信号改变状态之前到达驱动端。

反之,反射信号将在信号改变状态之后到达驱动端。

如果反射信号很强,叠加的波形就有可能会改变逻辑状态。

(三)、高速信号的确定上面我们定义了传输线效应发生的前提条件,但是如何得知线延时是否大于1/2驱动端的信号上升时间?一般地,信号上升时间的典型值可通过器件手册给出,而信号的传播时间在PCB设计中由实际布线长度决定。

下图为信号上升时间和允许的布线长度(延时)的对应关系。

PCB 板上每单位英寸的延时为 0.167ns.。

但是,如果过孔多,器件管脚多,网线上设置的约束多,延时将增大。

高速pcb设计指南之一

高速p c b设计指南之一The document was prepared on January 2, 2021高速PCB设计指南之一第一篇 PCB布线在PCB设计中,布线是完成产品设计的重要步骤,可以说前面的准备工作都是为它而做的, 在整个PCB中,以布线的设计过程限定最高,技巧最细、工作量最大.PCB布线有单面布线、双面布线及多层布线.布线的方式也有两种:自动布线及交互式布线,在自动布线之前, 可以用交互式预先对要求比较严格的线进行布线,输入端与输出端的边线应避免相邻平行, 以免产生反射干扰.必要时应加地线隔离,两相邻层的布线要互相垂直,平行容易产生寄生耦合.自动布线的布通率,依赖于良好的布局,布线规则可以预先设定, 包括走线的弯曲次数、导通孔的数目、步进的数目等.一般先进行探索式布经线,快速地把短线连通, 然后进行迷宫式布线,先把要布的连线进行全局的布线路径优化,它可以根据需要断开已布的线. 并试着重新再布线,以改进总体效果.对目前高密度的PCB设计已感觉到贯通孔不太适应了, 它浪费了许多宝贵的布线通道,为解决这一矛盾,出现了盲孔和埋孔技术,它不仅完成了导通孔的作用, 还省出许多布线通道使布线过程完成得更加方便,更加流畅,更为完善,PCB 板的设计过程是一个复杂而又简单的过程,要想很好地掌握它,还需广大电子工程设计人员去自已体会, 才能得到其中的真谛.1 电源、地线的处理既使在整个PCB板中的布线完成得都很好,但由于电源、地线的考虑不周到而引起的干扰,会使产品的性能下降,有时甚至影响到产品的成功率.所以对电、地线的布线要认真对待,把电、地线所产生的噪音干扰降到最低限度,以保证产品的质量.对每个从事电子产品设计的工程人员来说都明白地线与电源线之间噪音所产生的原因, 现只对降低式抑制噪音作以表述:1、众所周知的是在电源、地线之间加上去耦电容.2、尽量加宽电源、地线宽度,最好是地线比电源线宽,它们的关系是:地线>电源线>信号线,通常信号线宽为:~0.3mm,最经细宽度可达~0.07mm,电源线为~2.5 mm对数字电路的PCB可用宽的地导线组成一个回路, 即构成一个地网来使用模拟电路的地不能这样使用3、用大面积铜层作地线用,在印制板上把没被用上的地方都与地相连接作为地线用.或是做成多层板,电源,地线各占用一层.2 数字电路与模拟电路的共地处理现在有许多PCB不再是单一功能电路数字或模拟电路,而是由数字电路和模拟电路混合构成的.因此在布线时就需要考虑它们之间互相干扰问题,特别是地线上的噪音干扰.数字电路的频率高,模拟电路的敏感度强,对信号线来说,高频的信号线尽可能远离敏感的模拟电路器件,对地线来说,整人PCB对外界只有一个结点,所以必须在PCB内部进行处理数、模共地的问题,而在板内部数字地和模拟地实际上是分开的它们之间互不相连,只是在PCB与外界连接的接口处如插头等.数字地与模拟地有一点短接,请注意,只有一个连接点.也有在PCB上不共地的,这由系统设计来决定.3 信号线布在电地层上在多层印制板布线时,由于在信号线层没有布完的线剩下已经不多,再多加层数就会造成浪费也会给生产增加一定的工作量,成本也相应增加了,为解决这个矛盾,可以考虑在电地层上进行布线.首先应考虑用电源层,其次才是地层.因为最好是保留地层的完整性.4 大面积导体中连接腿的处理在大面积的接地电中,常用元器件的腿与其连接,对连接腿的处理需要进行综合的考虑,就电气性能而言,元件腿的焊盘与铜面满接为好,但对元件的焊接装配就存在一些不良隐患如:①焊接需要大功率加热器.②容易造成虚焊点.所以兼顾电气性能与工艺需要,做成十字花焊盘,称之为热隔离heat shield俗称热焊盘Thermal,这样,可使在焊接时因截面过分散热而产生虚焊点的可能性大大减少.多层板的接电地层腿的处理相同.5 布线中网络系统的作用在许多CAD系统中,布线是依据网络系统决定的.网格过密,通路虽然有所增加,但步进太小,图场的数据量过大,这必然对设备的存贮空间有更高的要求,同时也对象计算机类电子产品的运算速度有极大的影响.而有些通路是无效的,如被元件腿的焊盘占用的或被安装孔、定们孔所占用的等.网格过疏,通路太少对布通率的影响极大.所以要有一个疏密合理的网格系统来支持布线的进行.标准元器件两腿之间的距离为英寸2.54mm,所以网格系统的基础一般就定为英寸2.54 mm或小于英寸的整倍数,如:英寸、英寸、英寸等.6 设计规则检查DRC布线设计完成后,需认真检查布线设计是否符合设计者所制定的规则,同时也需确认所制定的规则是否符合印制板生产工艺的需求,一般检查有如下几个方面:1、线与线,线与元件焊盘,线与贯通孔,元件焊盘与贯通孔,贯通孔与贯通孔之间的距离是否合理,是否满足生产要求.2、电源线和地线的宽度是否合适,电源与地线之间是否紧耦合低的波阻抗在PCB中是否还有能让地线加宽的地方.3、对于关键的信号线是否采取了最佳措施,如长度最短,加保护线,输入线及输出线被明显地分开.4、模拟电路和数字电路部分,是否有各自独立的地线.5后加在PCB中的图形如图标、注标是否会造成信号短路.6对一些不理想的线形进行修改.7、在PCB上是否加有工艺线阻焊是否符合生产工艺的要求,阻焊尺寸是否合适,字符标志是否压在器件焊盘上,以免影响电装质量.8、多层板中的电源地层的外框边缘是否缩小,如电源地层的铜箔露出板外容易造成短路.第二篇 PCB布局在设计中,布局是一个重要的环节.布局结果的好坏将直接影响布线的效果,因此可以这样认为,合理的布局是PCB设计成功的第一步.布局的方式分两种,一种是交互式布局,另一种是自动布局,一般是在自动布局的基础上用交互式布局进行调整,在布局时还可根据走线的情况对门电路进行再分配,将两个门电路进行交换,使其成为便于布线的最佳布局.在布局完成后,还可对设计文件及有关信息进行返回标注于原理图,使得PCB板中的有关信息与原理图相一致,以便在今后的建档、更改设计能同步起来, 同时对模拟的有关信息进行更新,使得能对电路的电气性能及功能进行板级验证.--考虑整体美观一个产品的成功与否,一是要注重内在质量,二是兼顾整体的美观,两者都较完美才能认为该产品是成功的.在一个PCB板上,元件的布局要求要均衡,疏密有序,不能头重脚轻或一头沉.--布局的检查印制板尺寸是否与加工图纸尺寸相符能否符合PCB制造工艺要求有无定位标记元件在二维、三维空间上有无冲突元件布局是否疏密有序,排列整齐是否全部布完需经常更换的元件能否方便的更换插件板插入设备是否方便热敏元件与发热元件之间是否有适当的距离调整可调元件是否方便在需要散热的地方,装了散热器没有空气流是否通畅信号流程是否顺畅且互连最短插头、插座等与机械设计是否矛盾线路的干扰问题是否有所考虑第三篇高速PCB设计一、电子系统设计所面临的挑战随着系统设计复杂性和集成度的大规模提高,电子系统设计师们正在从事100MHZ以上的电路设计,总线的工作频率也已经达到或者超过50MHZ,有的甚至超过100MHZ.目前约50% 的设计的时钟频率超过50MHz,将近20% 的设计主频超过120MHz.当系统工作在50MHz时,将产生传输线效应和信号的完整性问题;而当系统时钟达到120MHz时,除非使用高速电路设计知识,否则基于传统方法设计的PCB将无法工作.因此,高速电路设计技术已经成为电子系统设计师必须采取的设计手段.只有通过使用高速电路设计师的设计技术,才能实现设计过程的可控性.二、什么是高速电路通常认为如果数字逻辑电路的频率达到或者超过45MHZ~50MHZ,而且工作在这个频率之上的电路已经占到了整个电子系统一定的份量比如说1/3,就称为高速电路.实际上,信号边沿的谐波频率比信号本身的频率高,是信号快速变化的上升沿与下降沿或称信号的跳变引发了信号传输的非预期结果.因此,通常约定如果线传播延时大于1/2数字信号驱动端的上升时间,则认为此类信号是高速信号并产生传输线效应.信号的传递发生在信号状态改变的瞬间,如上升或下降时间.信号从驱动端到接收端经过一段固定的时间,如果传输时间小于1/2的上升或下降时间,那么来自接收端的反射信号将在信号改变状态之前到达驱动端.反之,反射信号将在信号改变状态之后到达驱动端.如果反射信号很强,叠加的波形就有可能会改变逻辑状态.三、高速信号的确定上面我们定义了传输线效应发生的前提条件,但是如何得知线延时是否大于1/2驱动端的信号上升时间一般地,信号上升时间的典型值可通过器件手册给出,而信号的传播时间在PCB设计中由实际布线长度决定.下图为信号上升时间和允许的布线长度延时的对应关系.PCB 板上每单位英寸的延时为 ..但是,如果过孔多,器件管脚多,网线上设置的约束多,延时将增大.通常高速逻辑器件的信号上升时间大约为.如果板上有GaAs芯片,则最大布线长度为7.62mm.设Tr 为信号上升时间, Tpd 为信号线传播延时.如果Tr≥4Tpd,信号落在安全区域.如果2Tpd≥Tr≥4Tpd,信号落在不确定区域.如果Tr≤2Tpd,信号落在问题区域.对于落在不确定区域及问题区域的信号,应该使用高速布线方法.四、什么是传输线PCB板上的走线可等效为下图所示的串联和并联的电容、电阻和电感结构.串联电阻的典型值 ohms/foot,因为绝缘层的缘故,并联电阻阻值通常很高.将寄生电阻、电容和电感加到实际的PCB连线中之后,连线上的最终阻抗称为特征阻抗Zo.线径越宽,距电源/地越近,或隔离层的介电常数越高,特征阻抗就越小.如果传输线和接收端的阻抗不匹配,那么输出的电流信号和信号最终的稳定状态将不同,这就引起信号在接收端产生反射,这个反射信号将传回信号发射端并再次反射回来.随着能量的减弱反射信号的幅度将减小,直到信号的电压和电流达到稳定.这种效应被称为振荡,信号的振荡在信号的上升沿和下降沿经常可以看到.五、传输线效应基于上述定义的传输线模型,归纳起来,传输线会对整个电路设计带来以下效应.· 反射信号Reflected signals· 延时和时序错误Delay & Timing errors· 多次跨越逻辑电平门限错误False Switching· 过冲与下冲Overshoot/Undershoot· 串扰Induced Noise or crosstalk· 电磁辐射EMI radiation反射信号如果一根走线没有被正确终结终端匹配,那么来自于驱动端的信号脉冲在接收端被反射,从而引发不预期效应,使信号轮廓失真.当失真变形非常显着时可导致多种错误,引起设计失败.同时,失真变形的信号对噪声的敏感性增加了,也会引起设计失败.如果上述情况没有被足够考虑,EMI将显着增加,这就不单单影响自身设计结果,还会造成整个系统的失败.反射信号产生的主要原因:过长的走线;未被匹配终结的传输线,过量电容或电感以及阻抗失配.延时和时序错误信号延时和时序错误表现为:信号在逻辑电平的高与低门限之间变化时保持一段时间信号不跳变.过多的信号延时可能导致时序错误和器件功能的混乱.通常在有多个接收端时会出现问题.电路设计师必须确定最坏情况下的时间延时以确保设计的正确性.信号延时产生的原因:驱动过载,走线过长.多次跨越逻辑电平门限错误信号在跳变的过程中可能多次跨越逻辑电平门限从而导致这一类型的错误.多次跨越逻辑电平门限错误是信号振荡的一种特殊的形式,即信号的振荡发生在逻辑电平门限附近,多次跨越逻辑电平门限会导致逻辑功能紊乱.反射信号产生的原因:过长的走线,未被终结的传输线,过量电容或电感以及阻抗失配.过冲与下冲过冲与下冲来源于走线过长或者信号变化太快两方面的原因.虽然大多数元件接收端有输入保护二极管保护,但有时这些过冲电平会远远超过元件电源电压范围,损坏元器件.串扰串扰表现为在一根信号线上有信号通过时,在PCB板上与之相邻的信号线上就会感应出相关的信号,我们称之为串扰.信号线距离地线越近,线间距越大,产生的串扰信号越小.异步信号和时钟信号更容易产生串扰.因此解串扰的方法是移开发生串扰的信号或屏蔽被严重干扰的信号.电磁辐射EMIElectro-Magnetic Interference即电磁干扰,产生的问题包含过量的电磁辐射及对电磁辐射的敏感性两方面.EMI表现为当数字系统加电运行时,会对周围环境辐射电磁波,从而干扰周围环境中电子设备的正常工作.它产生的主要原因是电路工作频率太高以及布局布线不合理.目前已有进行 EMI仿真的软件工具,但EMI仿真器都很昂贵,仿真参数和边界条件设置又很困难,这将直接影响仿真结果的准确性和实用性.最通常的做法是将控制EMI的各项设计规则应用在设计的每一环节,实现在设计各环节上的规则驱动和控制.六、避免传输线效应的方法针对上述传输线问题所引入的影响,我们从以下几方面谈谈控制这些影响的方法.严格控制关键网线的走线长度如果设计中有高速跳变的边沿,就必须考虑到在PCB板上存在传输线效应的问题.现在普遍使用的很高时钟频率的快速集成电路芯片更是存在这样的问题.解决这个问题有一些基本原则:如果采用CMOS或TTL电路进行设计,工作频率小于10MHz,布线长度应不大于7英寸.工作频率在50MHz布线长度应不大于英寸.如果工作频率达到或超过75MHz布线长度应在1英寸.对于GaAs芯片最大的布线长度应为英寸.如果超过这个标准,就存在传输线的问题.合理规划走线的拓扑结构解决传输线效应的另一个方法是选择正确的布线路径和终端拓扑结构.走线的拓扑结构是指一根网线的布线顺序及布线结构.当使用高速逻辑器件时,除非走线分支长度保持很短,否则边沿快速变化的信号将被信号主干走线上的分支走线所扭曲.通常情形下,PCB走线采用两种基本拓扑结构,即菊花链Daisy Chain 布线和星形Star分布.对于菊花链布线,布线从驱动端开始,依次到达各接收端.如果使用串联电阻来改变信号特性,串联电阻的位置应该紧靠驱动端.在控制走线的高次谐波干扰方面,菊花链走线效果最好.但这种走线方式布通率最低,不容易100%布通.实际设计中,我们是使菊花链布线中分支长度尽可能短,安全的长度值应该是:Stub Delay <= Trt .例如,高速TTL电路中的分支端长度应小于英寸.这种拓扑结构占用的布线空间较小并可用单一电阻匹配终结.但是这种走线结构使得在不同的信号接收端信号的接收是不同步的.星形拓扑结构可以有效的避免时钟信号的不同步问题,但在密度很高的PCB板上手工完成布线十分困难.采用自动布线器是完成星型布线的最好的方法.每条分支上都需要终端电阻.终端电阻的阻值应和连线的特征阻抗相匹配.这可通过手工计算,也可通过CAD工具计算出特征阻抗值和终端匹配电阻值.在上面的两个例子中使用了简单的终端电阻,实际中可选择使用更复杂的匹配终端.第一种选择是RC匹配终端.RC匹配终端可以减少功率消耗,但只能使用于信号工作比较稳定的情况.这种方式最适合于对时钟线信号进行匹配处理.其缺点是RC匹配终端中的电容可能影响信号的形状和传播速度.串联电阻匹配终端不会产生额外的功率消耗,但会减慢信号的传输.这种方式用于时间延迟影响不大的总线驱动电路.串联电阻匹配终端的优势还在于可以减少板上器件的使用数量和连线密度.最后一种方式为分离匹配终端,这种方式匹配元件需要放置在接收端附近.其优点是不会拉低信号,并且可以很好的避免噪声.典型的用于TTL输入信号ACT, HCT, FAST.此外,对于终端匹配电阻的封装型式和安装型式也必须考虑.通常SMD表面贴装电阻比通孔元件具有较低的电感,所以SMD封装元件成为首选.如果选择普通直插电阻也有两种安装方式可选:垂直方式和水平方式.垂直安装方式中电阻的一条安装管脚很短,可以减少电阻和电路板间的热阻,使电阻的热量更加容易散发到空气中.但较长的垂直安装会增加电阻的电感.水平安装方式因安装较低有更低的电感.但过热的电阻会出现漂移,在最坏的情况下电阻成为开路,造成PCB走线终结匹配失效,成为潜在的失败因素.抑止电磁干扰的方法很好地解决信号完整性问题将改善PCB板的电磁兼容性EMC.其中非常重要的是保证PCB板有很好的接地.对复杂的设计采用一个信号层配一个地线层是十分有效的方法.此外,使电路板的最外层信号的密度最小也是减少电磁辐射的好方法,这种方法可采用"表面积层"技术"Build-up"设计制做PCB来实现.表面积层通过在普通工艺 PCB 上增加薄绝缘层和用于贯穿这些层的微孔的组合来实现 ,电阻和电容可埋在表层下,单位面积上的走线密度会增加近一倍,因而可降低 PCB的体积.PCB 面积的缩小对走线的拓扑结构有巨大的影响,这意味着缩小的电流回路,缩小的分支走线长度,而电磁辐射近似正比于电流回路的面积;同时小体积特征意味着高密度引脚封装器件可以被使用,这又使得连线长度下降,从而电流回路减小,提高电磁兼容特性.其它可采用技术为减小集成电路芯片电源上的电压瞬时过冲,应该为集成电路芯片添加去耦电容.这可以有效去除电源上的毛刺的影响并减少在印制板上的电源环路的辐射.当去耦电容直接连接在集成电路的电源管腿上而不是连接在电源层上时,其平滑毛刺的效果最好.这就是为什么有一些器件插座上带有去耦电容,而有的器件要求去耦电容距器件的距离要足够的小.任何高速和高功耗的器件应尽量放置在一起以减少电源电压瞬时过冲.如果没有电源层,那么长的电源连线会在信号和回路间形成环路,成为辐射源和易感应电路.走线构成一个不穿过同一网线或其它走线的环路的情况称为开环.如果环路穿过同一网线其它走线则构成闭环.两种情况都会形成天线效应线天线和环形天线.天线对外产生EMI辐射,同时自身也是敏感电路.闭环是一个必须考虑的问题,因为它产生的辐射与闭环面积近似成正比.结束语高速电路设计是一个非常复杂的设计过程,ZUKEN公司的高速电路布线算法Route Editor和EMC/EMI分析软件INCASES,Hot-Stage应用于分析和发现问题.本文所阐述的方法就是专门针对解决这些高速电路设计问题的.此外,在进行高速电路设计时有多个因素需要加以考虑,这些因素有时互相对立.如高速器件布局时位置靠近,虽可以减少延时,但可能产生串扰和显着的热效应.因此在设计中,需权衡各因素,做出全面的折衷考虑;既满足设计要求,又降低设计复杂度.高速PCB设计手段的采用构成了设计过程的可控性,只有可控的,才是可靠的,也才能是成功的。

高速pcb设计注意事项

高速pcb设计注意事项

1. 确定信号层之间适当的间距,以避免串扰和交叉干扰。

2. 选择合适的PCB 材料和厚度,在考虑信号完整性和散热的情况下进行权衡。

3. 尽可能地减小电路板上的回流焊盘和贴片元件之间的距离。

4. 仔细规划电源和信号地面,保证良好的接地和电流分布。

5. 在PCB 设计过程中使用模拟和数字仿真工具来确保信号完整性。

6. 使用独立的点对点连接来减少多层PCB 堆叠中的交叉干扰。

7. 尽可能避免倒角和锐角,并确保尽可能平滑的布线。

8. 做好EMI/EMC 电磁兼容设计,遵循相关国际标准。

9. 在PCB 较大时,在焊盘附近添加焊点来保持稳定连接。

10. 验证PCB 布线是否正确,并遵循相关图像制造指南。

高速PCB设计的相关概念

高速PCB设计的相关概念引言在现代电子技术领域,随着通信技术和计算机技术的飞速发展,高速PCB设计变得越来越重要。

高速PCB设计不仅仅是简单地将电子器件进行布局和连接,而是需要考虑许多复杂的因素,如信号完整性、信号功耗、电磁干扰等。

本文将介绍高速PCB设计的相关概念,以帮助读者理解并应用于实践。

1. PCB设计基础知识PCB(Printed Circuit Board,印刷电路板)是电子设备中非常重要的组成部分,它作为电子器件之间的连接介质,承载着电子器件之间的信号传输和电子能量传输。

在进行高速PCB设计之前,我们需要了解一些基础知识。

PCB层类型常见的PCB层类型包括单层板、双层板和多层板。

单层板只有一层铜层,主要应用于简单的电子电路;双层板有两层铜层,其中一层作为信号层,一层作为地层;多层板则包括三层或更多层,其中内层层与层之间通过电解铜连通,用于提供更多的信号层和电源层。

PCB设计软件在进行高速PCB设计时,我们通常会使用PCB设计软件,如Altium Designer、Cadence Allegro 等。

这些软件提供了丰富的设计工具和功能,使得设计者能够更加方便地进行布局、布线和验证。

电路元件布局电路元件布局是指将各类电子器件放置在PCB 板上的过程。

在高速PCB设计中,电路元件的布局非常重要,它直接影响着信号传输的时间延迟和电磁干涉等因素。

因此,我们需要合理地布置电路元件,使得信号路径尽量短且布满整个PCB 板。

线路布线线路布线是指将电子器件之间的连接线路进行布置的过程。

高速PCB设计中的线路布线需要考虑信号完整性、信号功耗和电磁干扰等因素。

合理的线路布线可以减少信号的传输时间延迟,并降低不必要的干扰。

2. 高速PCB设计的具体概念信号完整性信号完整性是指在高速PCB设计中保持信号在电路中传输的准确性和可靠性。

在高速信号传输中,由于传输速率较快,往返时间较短,因此需要特别注意信号的完整性。

高速电路板的设计方法介绍

高速电路板的设计方法介绍高速电路板的设计方法介绍一、引言高速电路板的设计是现代电子设备设计中的一个重要环节。

随着数字通信、计算机网络和移动通信的迅猛发展,高速电路板的需求也越来越迫切。

在高速电路板设计过程中,如何保证信号传输的稳定性和可靠性是一个非常重要的问题。

本文将介绍一些高速电路板的设计方法,以帮助读者更好地进行高速电路板设计。

二、高速电路板的特点高速电路板的特点是信号频率高、传输速度快、信号波形陡峭。

这些特点造成了以下几个问题:1. 信号完整性:由于信号传输速度快,信号波形陡峭,会导致信号完整性问题,例如信号的反射、串扰、时钟抖动等。

这些问题都会影响信号的传输稳定性,因此需要采取一系列措施来解决。

2. 电磁兼容性:高速电路板上的信号传输往往伴随着电磁辐射和敏感度,因此需要采取一系列电磁屏蔽和抑制方法来保证电磁兼容性。

3. 导线长度和走线布局:在高速电路板设计中,导线长度和走线布局的合理安排对信号传输有很大的影响。

合理的布局可以减小信号传输的延迟和串扰,保证信号的传输稳定性。

三、高速电路板设计的方法1. 信号完整性设计方法:(1)端口匹配:由于高速信号传输速度快,对于驱动输出和接收输入端口的匹配非常重要。

可以通过匹配控制阻抗和使用差分信号传输等方式来提高信号完整性。

(2)布线规则:在布线过程中,需要考虑信号线的走向、长度和层次。

可以采用等长电平、分层布线、减小串扰等方法来提高信号完整性。

(3)控制信号源:信号源的波形和电平控制也是保证信号完整性的重要因素。

需要通过合理的设计来减小信号的反射和串扰。

2. 电磁兼容性设计方法:(1)屏蔽和抑制:可以通过采用屏蔽盒、层间屏蔽、电磁屏蔽材料等方式来减小电磁辐射。

同时,还可以采用电源捶击器、衰减器等抑制器件来减小敏感度。

(2)地线设计:地线是高速电路板设计中的一个重要因素,合理的地线设计能减小电流回路的环路面积,降低电磁辐射。

(3)滤波器设计:可以在高速电路板上增加一些滤波器来减小电磁辐射和敏感度。

PCB设计高速信号走线的九种规则

PCB设计高速信号走线的九种规则1.高速信号走线规则一:保持信号路径短。

信号路径越短,信号传输的延迟越小,干扰和信号衰减的可能性也就越小。

因此,要将高速信号尽可能地在PCB板上靠近彼此地布线。

2.高速信号走线规则二:保持差分信号路径等长。

差分信号是一对相位反向、幅度相等的信号,在高速信号传输中使用较多,通常用于减小干扰和提高传输性能。

为了保持差分信号的平衡,需要使两条差分信号的路径尽可能等长。

3.高速信号走线规则三:保持高速信号路径和地路径并行。

高速信号和地路径的平行布线可以减小信号引起的电磁辐射和接地电压的变化。

因此,高速信号走线时要尽可能与地路径并行,避免交叉和走线交错。

4.高速信号走线规则四:避免信号走线在验证域的边界上。

验证域是指高速信号传输的有效区域。

将信号走线远离验证域的边界,可以降低信号的反射和干扰,提高传输性能。

5.高速信号走线规则五:保持信号走线与平面垂直。

信号走线与地平面垂直布线可以减小信号与地平面的耦合,减少传输中的干扰和信号衰减。

所以,信号走线时应尽量与地平面垂直。

6.高速信号走线规则六:保持信号走线有足够的间距。

高速信号走线之间需要有足够的间距,以减小信号之间的串扰和干扰。

一般来说,走线间距应根据信号频率和走线长度进行选择。

7.高速信号走线规则七:避免锐角弯曲。

锐角弯曲会导致信号的反射和干扰,影响传输性能。

因此,在高速信号走线时应避免使用锐角弯曲,应选择圆弧或平滑的曲线。

8.高速信号走线规则八:避免信号走线在波峰和波谷处交叉。

信号走线在波峰和波谷处交叉会导致信号间的干扰和串扰,影响传输性能。

所以,在高速信号走线时要避免这种情况的发生。

9.高速信号走线规则九:使用合适的信号层。

选择合适的信号层可以改善高速信号的传输性能。

通常情况下,内层信号层是最佳选择,因为内层信号层可以提供更好的屏蔽和隔离效果。

同时,还应考虑信号层之间的层间间距和层间结构,以减小信号的耦合和干扰。

总之,在PCB设计中,遵循这些高速信号走线规则可以提高高速信号的传输性能和可靠性,减小信号的干扰和衰减。

高速PCB设计指南2

高速PCB设计指南2高速pcbo指南高速pcbo指南II第一篇高密度(hd)路的o本文介绍了B和s中的许多人认为晶圆模具的BGA密封B受到Y型sub-B产品所需的空g的限制一可行的解q方案,它同rm足@些b品更高功能c性能的要求。

y型b品的高密度路ob配工著想。

今天的R值正在推动霓虹草鱼子产品B、产品R、性能C、可靠性是第一个测试]。

在@City_L中进行凿毛的用户必须注意B配置的效率,因为@喘振控制成本高。

sub-b产品的技术GM步骤和}s性别的正b增长ω对高密度道路u施工方法的需求。

O需要表面Nb、密集g距离和矢量密封B的EW路径ICR可能需要具有^和^密集g间距的高密度路面板。

然而,展望未来,一些已经提供微旁路孔和序列MB板的公司正在投入大量的容量@高密度子b品的_l者越碓绞艿因素的挑穑何锢恚}s元件上更密的引_g隔、力nb必很精密、和h境s多塑z封b吸潮,造成b配理期g的破裂。

物理因素也包括安b工的}s性c最kb品的可靠性。

m一步的政q定必考]b品⑷绾窝u造和b配o湫率。

^脆弱的引_元件,如0〃50c0〃40mm0〃020″c0〃016″引_g距的sqfpshrinkquadflatpack,可能在so一持m的b配工合格率方面向b配<姨岢鲆挑稹w畛晒φ拈_l是那些已行工jc的路板o指引和工jc的焊p缀涡睢在H环境中,焊接P基于所用sub-b零件的焊接类型。

在可能的情况下,将P形与nκ焊接,使用Mei Mo为B感到羞耻,并以透明的方式工作。

无论零件是安装在板的一侧,还是进行波峰、回流焊或其他焊接,PC零件的焊接尺寸应确保焊接CCZ为CM。

然而,焊接局部放电外壳的尺寸为x,K受B的生存能力水平以及C、G、B或其他l零件的公差限制。

就生物学特性而言,G在CWD病例中的R位置为P。

1、焊p的要求H技术小组委员会tiecinternational ELETROTECH mission的61188收到Jr关于在新H腐蚀下焊接拐角或P凸l零件的不同术语。

allegro 高速pcb设计技巧

allegro 高速pcb设计技巧

在Allegro中进行高速PCB设计时,以下是一些技巧和注意事项:

1. 确保足够的间距:在高速信号线之间保持足够的间距,以减少串扰和信号失真。

2. 避免过长的连线:尽量减少高速信号线的长度,以减少信号传输时间和延迟。

3. 使用合适的线宽:根据信号的频率和电流负载,选择合适的线宽以减小信号的衰减和失真。

4. 考虑使用差分对:对于需要高速传输和高可靠性的信号,可以使用差分对来提高信号质量和抗干扰能力。

5. 避免使用过长的接地线:过长或弯曲的接地线可能会产生额外的电感和电容,影响信号完整性。

6. 考虑使用去耦电容:在关键信号线和电源平面之间添加去耦电容,以减小电源噪声和改善信号完整性。

7. 使用合适的层叠结构:根据设计需求选择合适的层叠结构,包括信号层、电源层和接地层的数量和排列方式。

8. 考虑使用阻抗控制:通过精确控制导线的阻抗,可以减小信号反射和失真。

9. 使用仿真工具进行验证:在布局布线完成后,使用仿真工具进行信号完整性验证,以确保设计满足性能要求。

10. 参考标准和经验:遵循相关的设计标准和经验法则,例如IPC标准、JEDEC标准等,以确保设计的可靠性和一致性。

以上是一些基本的Allegro高速PCB设计技巧,实际设计中可能还需要考虑更多的因素和细节。

建议在设计过程中不断学习和总结经验,以提高设计水平。

高速PCB过孔设计

饭 I 的 一 个 孔 , 它 是 多 层 PCB 设 汁 【l 一 个 重 要 因 素 。 过 孔 可 以 I的 用 来 固 定 安 装 插 接 兀 什 或 连 通 层 间 走 线 。 一 个 过 孔 主 要 由 两 个 部 分 组 成 , 一 是 中

的 , 均 作 为 通 孔 考 虑 。 过 孔 的 分

类 如 2所 示 ( F )。

高 速 板 级设 汁f i 9时 候 就 必 须 考 虑 信 号 完 整 性 问 题 , 掌 握 估 ‘ 憋 完

性 理 论 , 进 而 才 能 指 平 ¨实 现 高

的 f 部 镀 卜涂 层 , 使 之 具 有 导 电

决 定 r过 孔 的 大 小 。 在 印 刷 E 乜路 板 表 面 , 每 个 过 孔 都 要 为 焊 艋 和 焊 盘 恬] 的 问 隙 留 有 额 外 的 空

低 , 所 以 般 印 制 电 路 板 均 使 用 通 孔 , 『i 用 另 外 两 种 过 孔 。 以 f 『 下 所 的 过 孔 , 没 有 特 殊 说 明

西安 71 0 1 07) W eiLil, u ao -iLi H

(M echani caI eI t o ni - ec r c

Engi neer ng nstt e i an i I iut of X di

Unv r i ’ n 7 0 . i a i e st Xi 1 71Chn ) y a 0

看 来 确 的 设 汁 , 在 实 际 PCB设 计 过 程 中 如 朱 处 致 整 个 设 计 欠 败 。 当 , 就 会 导 此 , 进 行

间 , 焊 髓 实 现 过 孔 的 电 镀 内 层 与 印 刷 电 路 板 表 面 ( 内 部 )的 走 线 或

高速电路pcb设计方法与技巧

高速电路pcb设计方法与技巧

高速电路 PCB 设计是非常重要的,因为它可能会对电路性能和信号完整性产生重要影响。

以下是一些高速电路 PCB 设计方法和技巧:

1. 布局规划:确保在 PCB 上正确布局各个电路模块,尽量减少信号路径长度和电流回路,避免交叉干扰和干扰耦合。

2. 地线规划:准确规划地线,减少回流路径和地回流阻抗,以确保信号完整性和抑制噪声。

3. 信号层分离:将信号层和电源层分离,减少干扰和耦合。

在有需要的地方使用地层分离。

4. 绕线规则:使用最短的路径和尽可能直线的路径连接信号源和接收器。

避免锐角和过于绕曲的路径,以减少信号损耗和延迟。

5. 信号完整性:在设计中使用适当的终端电阻、差分线、缓冲器和阻抗匹配等技术,以保持信号完整性和抑制回波和反射。

6. 电源和地线:确保电源和地线的良好连接和分配,减少电源噪声和地回流。

7. 绝缘:在高速电路附近使用绝缘层,以隔离高速信号和其他信号。

8. 过滤和抑制:在输入和输出端口使用合适的滤波器和抑制电路,以减少噪声和干扰。

9. EMI 和 RFI:在设计中采取一些措施来减少电磁干扰和无线干扰,如使用屏蔽层和地平面。

10. 模拟和数字信号分离:将模拟信号和数字信号分离,以减

少干扰和串扰。

总结来说,高速电路PCB 设计需要考虑布局规划、地线规划、信号层分离、绕线规则、信号完整性、电源和地线、绝缘、过滤和抑制、EMI 和 RFI、以及模拟和数字信号分离等因素。

这些方法和技巧可以帮助确保高速电路性能和信号完整性。

关注高速PCB设计

系统缘 何 失敬 ?

这让设计 工程师们 觉得

十分 困惑 : . 没有 任 何的

3信号沿 时 间下 降到 ls ) a 以 后 ,信号 之 间 的 串扰

就成 为 很 重 要的 一 个 问

设 计修 改 , 生产 制造 基 于原始设 计中 . 致的电

子元 器件 。唯 一的 区别

题 。4 当信 号 沿 的时 间 )

件 奇特 的事 : 个 7 年前 就 已经 成功 得新近生 产的每一 个芯 片都 成为高 速 统并 且会出现 各种各样的信 号完整性

设 计 、制造 并 且 上市的产 品 , 直以 器件 , 一 正是这 些 高速 器件 应用 中的 信 方面 的 I 。 司题

来都 能够 非 常稳 定可 靠地 工作 , 而最 号 完 整性 问题 导致 了 系统的 失效 。

维普资讯

\ 毫 子 簟 苛 茸 佬

/

关 注 高 速 PCB 设 计

[1 vd 公 司北 京办 事处 李宝 龙 肖跃龙 r o e, ] 2 a

高速 P B设计 中 的 问题 C

是 由ቤተ መጻሕፍቲ ባይዱ争 灭不断 进 步的 I ll Cf 造技 术 ,  ̄ l

高速 P CB设 计 策 略

而系统设计工程师总是希望 在第一时 芯片同高速系 统进行统一的考虑, 它

目前 高速 P B C 的设 计在 通信 、 计 间使用 最新 型的 高性能 芯 片 , 这样 器 们不 再独 立 工作 ; C 工程 师依据 设 PB 算机 、 图形 图像 处 理 等 领 域 应 用广 件 厂 商 给 出 的 设 计 指 南 可能 并 不 成 计规 则完 成 P B 布局 和布线 j I C 的 工 s 泛。 而在 这 些领域 工程 师们 用的 高速 熟 。 以 有的 器件 厂商 不同时 期 会给 程师主 要负责板级 和系统级的 分析和 所 P B设计 策略 也不一 样 。 C 出多个 版本 的设 计指 南 。 其次 , 器件 验证 ,以及单 扳的 E MC分 析和地 弹

高速PCB设计如何正确选择PCB板材

高速PCB设计如何正确选择PCB板材?(2019-07-09 16:26:52)转载▼标签:pcba生了,特别是高速SerDes 接口,信号具有非常快的上升时间,数字信号可以携带比自身重复频率更高频的能量,这些较高的高频能量成分,用来构造理想的快速转换的数字信号。

今天的高速串行总线,在时钟速率的第5 次谐波上往往有大量的能量集中。

现在有许多高速数字应用,速度为10 Gbit/s或更高。

这些应用使用5 GHz的基频和15 GHz,25 GHz等的谐波。

在此频率范围内,大多数常见的PCB材料在介质损耗(Df)方面会有非常显着的差异,并导致严重的信号完整性的问题。

这是高速数字PCB使用专为高频应用而设计的特殊板材的原因之一。

这些材料的配方具有低损耗因数,在很宽的频率范围内具有最小的变化。

这些板材过去常用于高频RF应用,甚至现在用于77 GHz及更高的应用。

除了介质损耗因素的改进外,这些板材还配有严格的厚度控制和Dk控制,更佳有利于保障信号完整性。

2019台北电脑展上AMD发布第三代Ryzen锐龙处理器的情况,AMD采用7纳米的CPU 除了在性能上开始压制英特尔之外,其配套的X570 芯片组也引入了对PCIe 4.0 的支持,采用PCIe 4.0 NVMe的SSD也开始陆续推向市场,而预计两年后,PCIe 5.0规范也将发布。

PCIe 5.0 的数据速率将达到恐怖的32GT/s,从而加重频率相关的插入损耗。

选择的PCB 材料会对各个区域的插入损耗产生巨大影响。

如果在设计PCB时不考虑板材对高速信号的影响,老司机也会翻车!选择PCB板材时必须在满足PCB设计需求、可量产性、成本中间取得平衡点。

简单而言,设计需求包含电气和结构可靠性这两部分。

通常在设计非常高速的PCB板子(大于GHz的频率)时板材问题才会比较重要。

例如,现在常用的FR-4材质,在几个GHz的频率时的介质损耗Df(Dielectricloss)会很大,可能就不适用。

高速电路pcb设计方法与技巧

高速电路pcb设计方法与技巧高速电路的PCB设计方法和技巧包括以下几个方面:1. 布局设计:将高速信号的传输路径尽量短,减少信号的传播延迟和损耗。

较重要的信号路径应尽量接近直线,减少信号的反射和串扰。

同时,将高速信号路径与低速信号路径、电源路径和地线路径分开布局,减少干扰。

将容易产生电磁干扰的元件,如发射器和接收器,与其他元件远离。

2. 信号线的走线规则:高速信号线应遵循尽量短、尽量宽、尽量平行的原则。

信号线的走线应尽量避免拐弯和角度过多,减少信号的反射和串扰。

信号线之间应保持一定的间距,避免互相干扰。

对于差分信号线,应保持差分对的长度一致,减少时钟抖动。

3. 地线规划:地线是高速电路中非常重要的一部分,对于信号的传输和干扰抑制起着至关重要的作用。

地线的设计应尽量短、宽,减小地电阻和电感。

可以使用填充地方式减小地回流路径。

对于多层PCB,应设计好地引脚和地面的连接方式。

4. 耦合电容与电感:在高速电路中,耦合电容和电感起着衰减高频噪声和滤波的作用。

需要合理选择耦合电容和电感的数值,以满足高速信号的传输需求。

电容和电感的布局也需要注意,尽量靠近需要耦合或滤波的信号线。

5. 电源规划:电源线是高速电路中非常重要的一部分,对于信号的传输和干扰抑制同样起着至关重要的作用。

电源线的设计应尽量短、宽,减小电源电阻和电感。

可以使用填充电源方式减小电源回流路径。

对于多层PCB,应设计好电源引脚和电源面的连接方式。

6. 综合考虑:在PCB设计中,需要考虑到信号的传输需求、干扰抑制、布局和走线的规则等多个方面。

综合考虑这些因素,可以在高速电路的PCB设计中取得较好的效果。

总的来说,高速电路的PCB设计需要充分考虑信号的传输需求和干扰抑制,合理的布局和走线规则是必不可少的。

此外,还需要综合考虑其他因素,如地线规划、耦合电容和电感、电源规划等,以确保高速电路的正常工作。

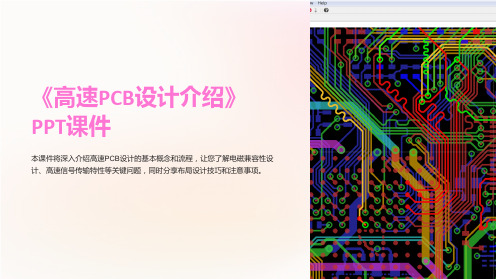

《高速PCB设计介绍》课件

布局设计技巧和注意事项

1 分区设计

根据电路功能和信号特性,将PCB划分为不同的区域。

2 信号与电源分离

避免信号和电源之间的相互干扰,以提高信号完整性。

3 走线技巧

采用合适的走线方式,如避免交叉、减小走线长度等。

差分和阻抗匹配设计

1

差分信号

解释差分信号的概念和用途,以及差分线路的布局和走线规则。

2

解释选择适当的线宽线具

介绍常用的PCB设计软件,如Altium Designer和PADS。

PCB的生产流程

原理图设计

使用EDA软件完成电路原理图的设计与验证。

布局设计

将原理图中的元件转换为PCB上的布局,并 考虑布线和散热等因素。

生成Gerber文件

将PCB设计转换为Gerber文件,供PCB制造 厂商生产。

《高速PCB设计介绍》 PPT课件

本课件将深入介绍高速PCB设计的基本概念和流程,让您了解电磁兼容性设 计、高速信号传输特性等关键问题,同时分享布局设计技巧和注意事项。

PCB设计概述

1

基础知识

了解PCB的基本结构和原理,包括通

设计要求

2

过孔、层叠等概念。

明确设计目标,包括信号完整性、干

扰抑制和散热等要求。

阻抗匹配

介绍阻抗匹配的原理和技巧,以确保信号传输的一致性和稳定性。

3

仿真和验证

使用仿真工具验证差分和阻抗匹配设计的性能,如SIwave和HyperLynx。

板厚、层压板和线宽线距选择

板厚选择

讨论选择适当的PCB板厚度对 布局和走线的影响。

层压板设计

介绍多层PCB的设计和层压板 的配置。

线宽线距选择

组装和焊接

高速pcb设计和apsim仿真工具

高速PCB设计与APSIM仿真的协同工作流程

数据共享

迭代优化

通过将仿真结果反馈给设计工程师,实现高速PCB 设计与仿真的迭代优化,提高设计效率和质量。

APSIM仿真工具能够与高速PCB设计软件进 行数据共享,实现设计数据与仿真数据的无 缝对接。

协同工作

APSIM仿真工具与高速PCB设计软件之间的 协同工作流程能够缩短产品上市时间,提高 设计成功率。

信号完整性分析

在高速PCB设计中,信号完整 性是关键因素,需要进行仿真 分析以确保信号传输的稳定性

和可靠性。

电磁兼容性分析

随着信号速率的提高,电磁干 扰问题愈发突出,需要进行电 磁兼容性仿真以优化PCB布局

和布线。

热分析

高密度集成元器件在高速PCB 中产生大量热量,需要进行热

仿真以优化散热设计。

APSim仿真工具在高速PCB设计中的应用

高速PCB设计与APSIM仿真工具

目录

• 高速PCB设计基础 • APSim仿真工具介绍 • 高速PCB设计与APSIM仿真的结合 • 案例分析 • 结论与展望

01

高速PCB设计基础

PCB设计的基本概念

PCB

印刷电路板,是电子系统中的基础部件,用于实 现电子元器件之间的连接。

PCB设计

根据电路原理图和相关要求,利用设计软件进行 电路板的布局和布线的过程。

地弹

当信号线上的电流发生变化时, 地平面会产生电压波动,称为地 弹。减小地弹的方法包括增加接 地面、使用多层板等。

02

APSim仿真工具介绍

APSim仿真工具概述

APSim(Advanced Printed Circuit Board Simulator)是一款用于高速 PCB(印刷电路板)设计的仿真工具, 它能够模拟电路板中信号的传输、电 磁场和热传导等物理现象。

基于Cadence的高速PCB设计

振荡的现象是反复出现过冲和下冲.信号的振荡和环绕振荡由线上过度的电感和电容引起的接收端与传输线和源端的阻抗不匹配而产生的,通常发生在逻辑电平门限附近,多次跨越逻辑电平门限会导致逻辑功能紊乱.振荡和环绕振荡同反射一样也是由多种因素引起的,振荡可以通过适当的端接或是改变PCB参数予以减小,但是不可能完全消除.

信号完整性是指信号在信号线上的质量.信号具有良好的信号完整性是指当在需要的时候,具有所必需达到的电压电平数值.差的信号完整性不是由某一因素导致的,而是由板级设计中多种因素共同引起的.特别是在高速电路中,所使用的芯片的切换速度过快、端接元件布设不合理、电路的互联不合理等都会引起信号的完整性问题.具体主要包括串扰、反射、过冲与下冲、振荡、信号延迟等.

基于Cadence的高速PCB设计

1 引言

随着人们对通信需求的不断提高,要求信号的传输和处理的速度越来越快.相应的高速PCB的应用也越来越广,设计也越来越复杂.高速电路有两个方面的含义:一是频率高,通常认为数字电路的频率达到或是超过45MHz至50MHz,而且工作在这个频率之上的电路已经占到了整个系统的三分之一,就称为高速电路.另外从信号的上升与下降时间考虑,当信号的上升时间小于6倍信号传输延时时即认为信号是高速信号,此时考虑的与信号的具体频率无关.

2.1.5 信号延迟(delay)

电路中只能按照规定的时序接收数据,过长的信号延迟可能导致时序和功能的混乱,在低速的系统中不会有问题,但是信号边缘速率加快,时钟速率提高,信号在器件之间的传输时间以及同步时间就会缩短.驱动过载、走线过长都会引起延时.必须在越来越短的时间预算中要满足所有门延时,包括建立时间,保持时间,线延迟和偏斜. 由于传输线上的等效电容和电感都会对信号的数字切换产生延迟,加上反射引起的振荡回绕,使得数据信号不能满足接收端器件正确接收所需要的时间,从而导致接收错误.在Cadence的信号仿真软件中,将信号的延迟也放在反射的子参数中度量,有Settledelay、Switchdelay、Propdelay.其中前两个与IBIS模型库中的测试负载有关, 这两个参数可以通过驱动器件和接收器件的用户手册参数得到, 可以将它们与仿真后的Settledelay、Switchdelay加以比较,如果在Slow模式下得到的Switchdelay都小于计算得到的值,并且在Fast的模式下得到的Switchdelay的值都大于计算得到的值,就可以得出我们真正需要的两个器件之间的时延范围Propdelay.在具体器件布放的时候,如果器件的位置不合适,在对应的时延表中那部分会显示红色,当把其位置调整合适后将会变成蓝色,表示信号在器件之间的延时已经满足Propdelay规定的范围了.

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

高速PCB 高速 PCB设计介绍 设计介绍目录• 高速设计方法• 常见问题• 仿真过程目录• 高速设计方法• 常见问题• 仿真过程设计方法比对原理图 原理图 前仿真 参数的 确定 FAIL 布局布线 SI PCB制作 NO 量测 PASS PI 通 过 EMC布局布线YESPCB制 作4SI 工程师要参与设计全过程L i l Logical Design Engineer Logical Design g EngineerPCB L Layout SI Engineer Ph i l Phyiscal Electrical PhyiscalLogoPCB Layout什么是信号完整性Driver 30mil PWR 3 inch long PCB Trace GND 3000mil PWR Receiver GND工程师不得不考量PCB 工程师不得不考量 PCB上走线参上的寄生参数效应对信号的影响 上走线参上的寄生参数效应对信号的影响目录• 高速设计方法• 常见问题• 仿真过程传输线的阻抗匹配1:什 什么是传输线? & 什么是阻抗?Tline l > 1/10 TriseLogoPCB走线经验规则May treat as lumped Capacitance Use this 10:1 ratio for accurate modeling of transmission linesTd < 0.1 TxMay treat as RC on-chip, and treat as LC for PC board interconnectTd < 0.4 TxLogo同种设计 500Mhz,DDR2地址线接收端眼图 错误的端接 经验设计———— 仿真设计———— 500Mhz,DDR2地址线接收端眼图 500 , 地址线接收端眼图 正确的端接 上一板就是 上 板就是这么做的,波形很好,没有问题? 这是个新的案例,影响它的因素有哪些?如 何排除这些影响?该 如何进一步扩大预量? Logo拓扑结构y DDRII y DDRIIIT 形拓扑Fly-by 拓扑y 拓扑结构由信号质量、时序等共同决定,还需考虑芯片本身内部功能。

当前拓扑修改后拓扑串扰DDR2 SDRAM接口在比特率500Mbps时,数据信号的眼图比对:不时数据信号的眼图比对考虑串扰考虑串经验设计———3W,5H扰仿新的案例化真设计———这是个新的案例,叠层线宽有所变化,我们重新分析。

MSL DSL 紧耦合松耦合…………………………y CLK 线的串扰参考面找同一根线分别为不同情y 找同根线分别为不同情况提取S 参数信号跨越分割槽布线跨分割y Conclusion :跨分割会导致信号回流路径的变化。

引起阻抗变化。

y 大幅度增加串扰参考面5G PCIE 差分线观察电容距离不同S 参数电容与传输线:0mil -700mil y conclusion :对于重要走线,如果跨越分割槽,可以通过在两电源平面跨接电容,以提供低回流路径。

S11红色过孔分析F>5GS11:红色S21:蓝色红色S11:红色S21:蓝色GND Vias GND Vias伴地孔为信号在过孔处提供回路;增加地孔数量可以进一步改善性能;2mA驱动能力4mA驱动能力6mA驱动能力最佳8mA驱动能力12mA驱动能力16mA驱动能力不同预加重、均衡值的效果对比:OSCILLOSCOPEDesign file: TS57X_32_CC.FFS Designer: USERHyperLynx V7.5Comment: tvss txlvl='0' txboost='7' rxeqval='0'OSCILLOSCOPEDesign file: TS57X_32_CC.FFS Designer: USERHyperLynx V7.5Comment: tvss txlvl='0' txboost='0' rxeqval='0'100.0200.0300.0V [J18.rxp (at pin)]100.0200.0300.0400.0500.0V o V [J18.rxp (at pin)]OSCILLOSCOPEDesign file: TS57X_32_CC.FFS Designer: USERHyperLynx V7.5Comment: tvss txlvl='31' txboost='0' rxeqval='0'300.0400.0500.0600.0V [J18.rxp (at pin)]-400.0-300.0-200.0-100.0-0.0Vo l t a g e -m V --300.0-200.0-100.0-0.0l t a ge-m V --200.0-100.0-0.0100.0200.0V o l t a g e -m V -Date: Thursday Dec. 13, 2007 Time: 9:45:05Cursor 1, Voltage = -265.0mV, Time = 61.00ps Cursor 2, Voltage = 165.9mV, Time = 61.00ps Delta Voltage = 430.8mV, Delta Time = 0.000s-600.0-500.0-20.000.00020.0040.0060.0080.00100.00120.00140.00160.00Time (ps)Date: Thursday Dec. 13, 2007 Time: 11:04:38Cursor 1, Voltage = -142.6mV, Time = 65.86ps Cursor 2, Voltage = 105.9mV, Time = 65.63ps Delta Voltage = 248.5mV, Delta Time = 231fs-400.0-20.000.00020.0040.0060.0080.00100.00120.00140.00160.00Time (ps)Date: Tuesday Dec. 18, 2007 Time: 8:25:16Cursor 1, Voltage = -195.2mV, Time = 61.46ps Cursor 2, Voltage = 373.9mV, Time = 61.46ps Delta Voltage = 569.2mV, Delta Time = 0.000s -300.0-20.000.00020.0040.0060.0080.00100.00120.00140.00160.00Time (ps)很好好不好电源完整性直流压降yy 交流阻抗DC drop DC drop铺铜数最小电降率铜厚铺铜层数最小电压(V )压降比率0.5OZ 10.82238.63%08601443%1OZ 10.8601 4.43%1OZ20.87912.23%电10VCC 源网络1.0VCC 铜厚:0.5oz 工作电流:27AAC 交流阻抗1.铜面积2.采用S-G-P-S 层叠PDS AssessmentLook from chipLook from package Look from PCB从不同层级看到input impedance 的大小都不同,如何从系统层级的结果再分别求出各层级的阻抗要求是一挑战.无package 及chip 资料下,从PCB 层级是难以规范出高频段阻抗要求.p g p ,无chip 资料下,从package 层级是难以规范出高频段阻抗要求SI SI 分析思路分析思路分析路Trigger on Failing WaveformTriggerDependent on Data?noyesSingle-line Transmission ProblemICPCB Data inIC or PCB?SharedPkg or PwrBus?Problem on Edge?PwrPkgnoyesGround BounceCrosstalkMonotonicityRinging9slew drivers 9stronger drive 9weaker drive 9add filter slew drivers 9move tracesstronger drive 9change topologyweaker drive 9terminations, mismatch 9topologyadd filter 9slew driversEMIy共模辐射POWER TraceGNDy差模辐射POWER GNDTracePCB yPCB边缘共模辐射20H 规则(防止电源层产生边缘辐射)y孤立铜区耦合共模辐射y y串扰耦合共模辐射 非理想接地耦合共模辐射Logo回路设计之差模辐射GND VIA !!Logo数字模拟 之 数模隔离DGND AGND DGND R AGNDDGND LAGND GDGNDAGNDLogo目录• 高速设计方法• 常见问题• 仿真过程仿真过程介绍主要步骤:9需求分析; 9资料阅读; 9寻找模型、进行校验; 9通过仿真确定设计方案; 9最后验证、反馈;Logo仿真过程介绍需求分析:• 分析用户的设计要求、数据流向、功能等。

电源树DC/DC LTM4616LDO TPS51200了解客户要做什么? 了解客户需要什么? 解客户需要什么信号流向Power +5V/12ALDO TPS74401LDO TPS74401LDO TPS74401DC/DC LTM4616LDO TPS74401EV10AQ190DC/DC LTM4616LDO TPS74401DC/DC LTM4616LDO TPS74401DC/DC LTM4616LDO TPS74401LDO TPS74401LDO TPS74401Logo仿真过程介绍资料阅读: 资料阅读• 通过阅读器件手册,对设计中涉及到的主要芯片进行性能的了解,包括DC、AC 参数、各种信号接口、逻辑时序等。

•寻找满足功能的条件 •寻找逻辑判断的依据Logo仿真过程介绍寻找模型、进行校验:• 在仿真中,信号的产生由激励源提供,模型的作用就是模拟激励源与负载的特 性。

• 对于厂商提供的模型会存在错误,此时需要排查。

• 两种模型:普通仿真和高级仿真需要的模型不一致。

IBIS HSPICELogo仿真过程介绍通过仿真确定设计方案:• • • • 层栈分配; 拓扑结构; 信号匹配; 时序匹配;Logo仿真过程介绍最后验证、反馈:• 通过设计方案的约束,布线完毕以后进行验证; • 对于仿真得到的波形,通过和芯片手册上的参数进行比较,从而判断设计合理否;Logo无锡同步CAD部:龚艳鸿手机:186********@Email: feihongfei@Thank you Thank you !!。